## University of Louisville

# ThinkIR: The University of Louisville's Institutional Repository

**Electronic Theses and Dissertations**

12-2014

# Multilayer electret activated by direct contact silicon électrode.

Mark M. Crain University of Louisville

Follow this and additional works at: https://ir.library.louisville.edu/etd

Part of the Electrical and Computer Engineering Commons

### Recommended Citation

Crain, Mark M., "Multilayer electret activated by direct contact silicon electrode." (2014). Electronic Theses and Dissertations. Paper

https://doi.org/10.18297/etd/1719

This Doctoral Dissertation is brought to you for free and open access by ThinkIR: The University of Louisville's Institutional Repository. It has been accepted for inclusion in Electronic Theses and Dissertations by an authorized administrator of ThinkIR: The University of Louisville's Institutional Repository. This title appears here courtesy of the author, who has retained all other copyrights. For more information, please contact thinkir@louisville.edu.

## MULTILAYER ELECTRET ACTIVATED BY DIRECT CONTACT SILICON ELECTRODE

by

### Mark M Crain III

B.S.M.E., Purdue University, 1991 M.S.E.E., University of Louisville, 1999

A Dissertation

Submitted to the Faculty of the

JB Speed Engineering School of the University of Louisville

In Partial Fulfillment of the Requirements

For the Degree of

**Doctor of Philosophy**

Department of Electrical and Computer Engineering University of Louisville Louisville, Kentucky

December 2014

Copyright 2014 by Mark M Crain III

All rights reserved

## MULTILAYER ELECTRET ACTIVATED BY DIRECT CONTACT SILICON ELECTRODE

Ву

## Mark M Crain III B.S.M.E., Purdue University, 1991 M.S.E.E., University of Louisville, 1999

A Dissertation Approved on

November 11, 2014

By the following Dissertation Committee:

| Dissertation Co-Director                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Shamus McNamara, Ph.D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| onamas Meramara, 1 m.D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Dissertation Co-Director                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Robert Keynton, Ph.D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| , and the state of |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Robert Cohn, Ph.D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| D All DID                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Bruce Alphenaar, Ph.D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Camini Sumanasalzana Dh D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Gamini Sumanasekera, Ph.D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Gail DePuy, Ph.D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| dan ber dy, i n.b.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

# DEDICATION

This dissertation is dedicated to my family

Angie, Wyatt, and Andrew.

## **ACKNOWLEDGMENTS**

I would like to thank Dr. Keynton for his mentorship. He has been a great role model for me and countless other students. I appreciate the time and effort that he has put into teaching me how to do research. I would also like to thank Dr. McNamara for his enthusiasm and helpful discussions. From Dr. Cohn, I learned perspective and I appreciate his high quality workmanship. He is a fantastic writer. Dr. Alphenaar is a great teacher, I had been in the microfab business for several years before taking physical electronics in ECE; I was very happy to learn it from him. From Dr. Gamini, I learned to take things in stride; work smart, keep cool; in other words, behave like a physicist. A special "Thank You" to Dr. Depuy for all of the guidance and consultation which has resulted in my learning a great deal about DOE and statistical interpretation of results. A second special "Thank You" to Dr. Baloo for his technical commentary and support.

### **ABSTRACT**

#### MULTILAYER ELECTRET ACTIVATED BY DIRECT CONTACT SILICON ELECTRODE

#### Mark M Crain III

### November 11, 2014

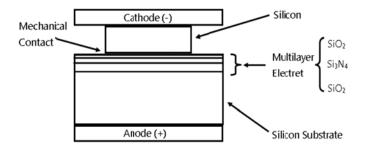

Electrets used in microelectromechanical systems (MEMS) devices are often formed by corona charging, where ionized gases are generated in an electric field to introduce a charge to the electret surface. The purpose of this study was to investigate a new technique for creating an electret from a plasma enhanced chemical vapor deposition (PECVD) multilayer film of  $SiO_2/Si_3N_4/SiO_2$  using a direct contact electrode of silicon. The electret formation takes advantage of deep traps in silicon nitride, which are known to develop from hydrogen interactions with silicon dangling bonds and, in some stoichiometries, nitrogen dangling bonds. The electret activation process has been optimized for maximum effective surface voltage (ESV). The deposition and activation process for the electret has the additional benefit of using commercially available equipment present in many microelectronic fabrication facilities. Standardized processes for depositing the PECVD film stack and activating the electret with a wafer level bonder have been developed.

Using this new process, electret films have been produced with positive and negative effective surface voltages in excess of +/-194.0 V. Extrapolated lifetimes, based on thermal decay studies, are calculated to be 57 years and 23 years for positive and negative electrets respectively if they are maintained in moderate to low humidity environments below 125°C. Activation energy levels in positive and negative electrets are 1.4 eV and 1.2 eV respectively. This new electret multilayer film stack and direct charging method produced thin film electrets with a half-life 5 times greater than that reported in literature by other groups using PECVD multilayer electrets [1, 2].

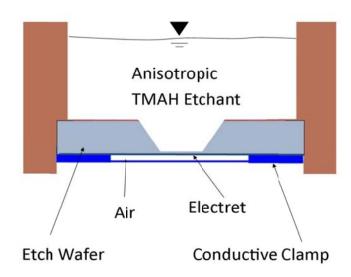

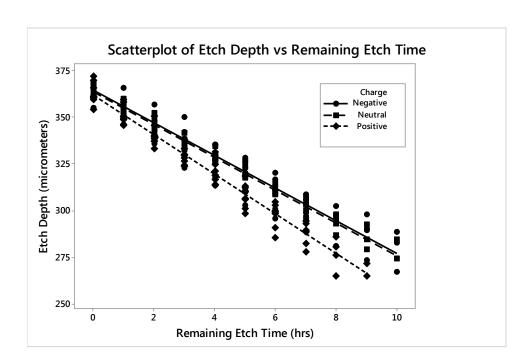

A new application was investigated to see how an electret may benefit semiconductor-liquid interactions. The PECVD electret was used to apply a gate bias to the back side of a double side polished silicon wafer to determine the effect of gate bias on the etch rates of an anisotropic silicon etch in 25% wt. tetramethylammonium hydroxide (TMAH). Our results show that the positively charged electret produced a statistically significant increase in etch rate, when compared to neutral and negatively charged electrets, as the silicon-TMAH interface approached the depletion region produced by the electret. The mean values of the silicon etch rate were evaluated for the last hour of etching with samples categorized by electret potentials as positive, negative or neutral. The positive potential electret had a mean etch rate of 12.0 um/hr for silicon as compared to 8.8 um/hr and 8.6 um/hr for negatively and neutrally charge electrets respectively. The one way Analysis Of Variance (ANOVA) of the silicon etch rates between the neutral

(control) PECVD film and the positive electret had a P value of 0.009 and falls within the 1% significance level, showing that it is very likely that the positive electret film has an effect on the final etch rate of the silicon under null hypothesis testing.

## TABLE OF CONTENTS

| D   | EDICA         | ATION                                                             | iii  |

|-----|---------------|-------------------------------------------------------------------|------|

| A   | CKNO          | WLEDGMENTS                                                        | iv   |

| A.  | BSTR <i>A</i> | ACT                                                               | V    |

| [J] | IST OF        | TABLES                                                            | xii  |

| LJ  | IST OF        | F FIGURES                                                         | xiv  |

| 1   | INT           | TRODUCTION                                                        | 1    |

| 2   | BAG           | CKGROUND                                                          | 5    |

|     | 2.1           | Introduction to Electrets                                         | 5    |

|     | 2.2           | Applications                                                      | 8    |

|     | 2.3           | Insulator, Dielectric, Paraelectric, and Ferroelectric Properties | 9    |

|     | 2.4           | Comparisons of a thin film electret to a parallel plate capacitor | . 13 |

|     | 2.5           | Electric Displacement Field                                       | . 17 |

|     | 2.6           | Effective Surface Voltage Electret Measurement                    | . 21 |

| 2.7   | Electret Formation                                                                              | . 25 |

|-------|-------------------------------------------------------------------------------------------------|------|

| 2.7.1 | Thermally Assisted Poling                                                                       | . 25 |

| 2.7.2 | Corona Charging                                                                                 | . 26 |

| 2.7.3 | Electron Beam Implant                                                                           | . 28 |

| 2.8   | Charge Traps in SiO <sub>2</sub> and Si <sub>3</sub> N <sub>4</sub>                             | . 28 |

| 2.9   | Studies of SiO <sub>2</sub> /Si <sub>3</sub> N <sub>4</sub> Multilayer Electret Activation      | . 30 |

| 2.10  | Charge Trapping in SiO <sub>2</sub> , Si <sub>3</sub> N <sub>4</sub> , and Multilayer Electrets | . 32 |

| 2.11  | Analysis Techniques of Electrets                                                                | . 37 |

| 2.12  | Concepts in Modeling Temperature Dependent Exponential Decay                                    | . 40 |

| 2.13  | Silicon Etching                                                                                 | . 45 |

| 2.14  | Band Diagrams of Silicon with KOH and TMAH                                                      | . 53 |

| 2.15  | Bias Effects on Anisotropic Etching of Silicon                                                  | . 59 |

| FAE   | BRICATION AND METHODS                                                                           | 65   |

| 3.1   | PECVD Deposition of SiO <sub>2</sub> /Si <sub>3</sub> N <sub>4</sub> /SiO <sub>2</sub>          | . 65 |

| 3.2   | Wafer Level Thermally Assisted Poling of Electret                                               | . 67 |

| 33    | Flectret Measurement and Evaluation                                                             | 70   |

3

| 3.4   | Process Optimization, Design of Experiments                     | 71  |

|-------|-----------------------------------------------------------------|-----|

| 3.5   | Electret Characterization                                       | 72  |

| 3.5.1 | Isothermal Potential Decay Sample Preparation                   | 72  |

| 3.5.2 | Isothermal Potential Decay Experiments                          | 73  |

| 3.5.3 | Evaluation of Isothermal Potential Decay Trials                 | 74  |

| 3.6   | Application of Electret as an Electrochemical Etch Stop         | 75  |

| 3.6.1 | Wafer and Die Preparation for Electrochemical Etch Stop         | 76  |

| 3.6.2 | Calculations for the Justification of Strong Inversion          | 79  |

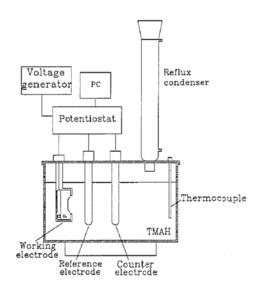

| 3.6.3 | Electrochemical Etch Stop Etch Cells and Environmental Control  | 83  |

| 3.6.4 | Electrochemical Etch Stop Timed Study Overview                  | 85  |

| 3.6.5 | Confirmation of Environmental Etch Conditions                   | 88  |

| 3.6.6 | Electret Stability During Anisotropic Etching                   | 88  |

| RES   | SULTS                                                           | 90  |

| 4.1   | Wafer and Film Dimensions                                       | 90  |

| 4.2   | Characterization and Optimization of Electret Formation Process | 91  |

| 43    | Flectret Characterization                                       | 105 |

4

| 4.4 Application of Electret as an Electrochemical | Etch Stop111 |

|---------------------------------------------------|--------------|

| CONCLUSIONS                                       | 122          |

| REFERENCES                                        | 124          |

| CURRICULUM VITAE                                  | 131          |

## LIST OF TABLES

| TABLES                                                                             | PAGE  |

|------------------------------------------------------------------------------------|-------|

| Table 1. PECVD process parameters                                                  | 66    |

| Table 2. Silicon oxide thickness measurements, mean and standard deviation.        | 91    |

| Table 3. Silicon nitride thickness measurements, mean and standard deviation.      | 91    |

| Table 4. Factorial Regression: Peak versus time, temperature, voltage, CenterPt    | 93    |

| Table 5. Factorial Regression: Peak positive ESV versus time, temperature, vo      | ltage |

|                                                                                    | 103   |

| Table 6. Decay rates for positively charged electrets on four wafers at va         | rying |

| temperatures to predict the mean lifetime of the electrets.                        | 107   |

| Table 7. Decay rates for negatively charged electrets on four wafers at va         | rying |

| temperatures to predict the mean lifetime of the electrets.                        | 108   |

| Table 8. Trial 1 etch depth vs time for neutral, negative, and positive electrets. | 115   |

| Table 9. Trial 2 etch depth vs time for neutral, negative, and positive electrets. | 116   |

| Table 10. Trial 3 etch depth vs time for neutral, negative, and positive electrets. 1 | .17 |

|---------------------------------------------------------------------------------------|-----|

| Table 11. ESV measurements for etch test die in trial 3.                              | 18  |

| Table 12. Final silicon etch rate grouped by neutral, negative, and positive E        | ESV |

| electret.                                                                             | 19  |

| Table 13. Null Hypothesis P Values for the Final Etch Rate with 3 separate 2 samp     | ple |

| T-test using MINITAB 1                                                                | 19  |

## LIST OF FIGURES

| FIGURES                                                                                 |

|-----------------------------------------------------------------------------------------|

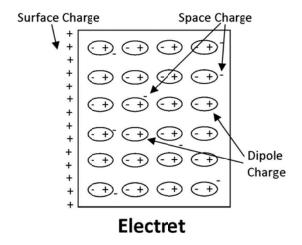

| Figure 1. Electret material displaying fixed surface, volume, and polarized charges. 6  |

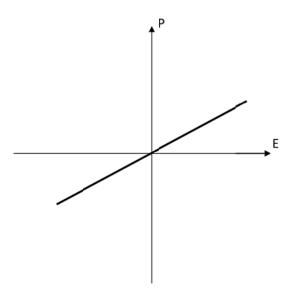

| Figure 2. Dielectric materials exhibit a proportional polarizing electric field in      |

| response to an active external electric field. 10                                       |

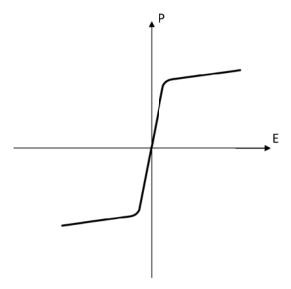

| Figure 3. Paraelectric properties are exhibited by some dielectric materials as a       |

| nonlinear polarization as a function of an external electric field. 10                  |

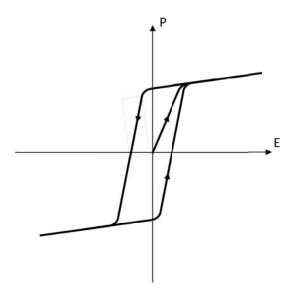

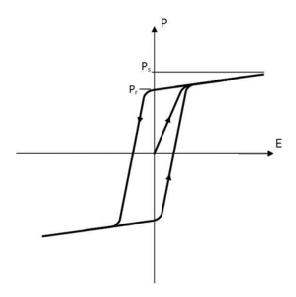

| Figure 4. Ferroelectric properties are exhibited by some paraelectric materials with    |

| residual polarization without an external electric field. 11                            |

| Figure 5. Polarization vs. electric field for a ferroelectric material. Spontaneous and |

| remnant polarization levels are shown. 12                                               |

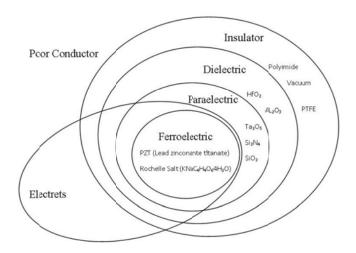

| Figure 6. Venn diagram of insulator classification based on polarization behavior       |

| under the influence of an external electric field. 13                                   |

| Figure 7. (a) Parallel plate capacitor with free space permittivity. (b) Parallel plate |

| capacitor with dielectric material. 15                                                  |

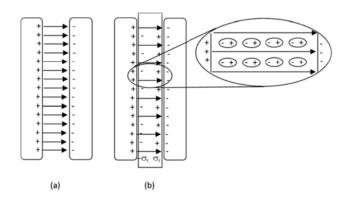

| Figure 8. A dielectric insulator is sandwiched between two metal layers. (a)    |

|---------------------------------------------------------------------------------|

| Opposing charges on conductors generate electric fields (arrows: positive to    |

| negative charges) and produce an opposite polarization by charge migration. (b) |

| The removal of an external electric field on the dielectric reduces the charge  |

| polarization in the dielectric to zero.                                         |

|                                                                                 |

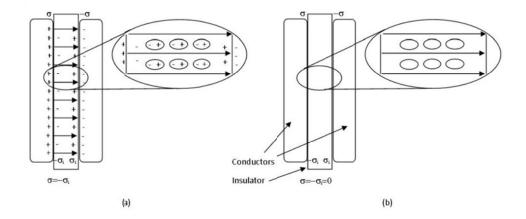

| Figure 9. A ferroelectric insulator is sandwiched between two metal layers. (a) |

| Opposing charges on conductors generate electric fields (arrows: positive to    |

| negative charges) and produce a polarization by charge migration; upper detail  |

| leaking charge, lower detail opposing charge. (b) The removal of an external    |

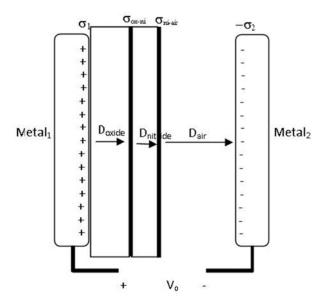

Figure 10. A simple model consisting of a conductive backed multilayer electret of silicon oxide and silicon nitride for modeling effective surface voltage and microphone operational principles.

17

electric field on the insulator does not negate the charge polarization.

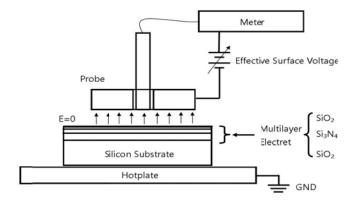

Figure 11. Diagram of null seeking feedback vibrating capacitor field meter with electret and substrate.

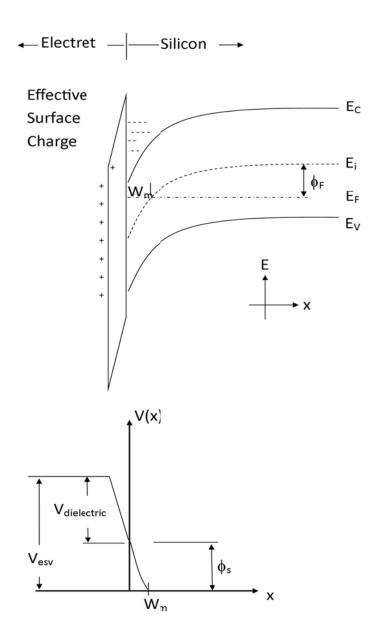

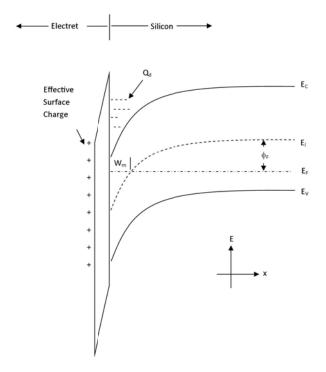

Figure 12. Insulator-silicon band bending due to electret bias modelled as an effective surface charge.

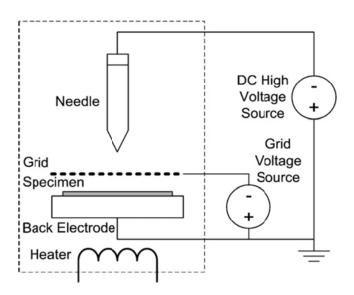

Figure 13. Corona charging schematic with heat assistance [42].

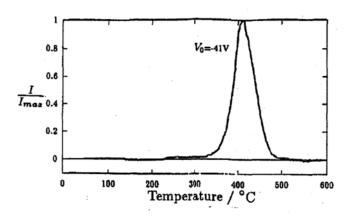

Figure 14. APCVD  $Si_3N_4$  open circuit thermally stimulated decay [50].

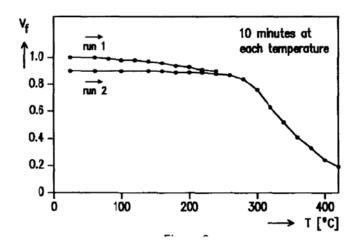

| rigure 15. Normanzed effective surface voltage 15D of corona charged shicon oxid       | лe  |

|----------------------------------------------------------------------------------------|-----|

| electret [52].                                                                         | 32  |

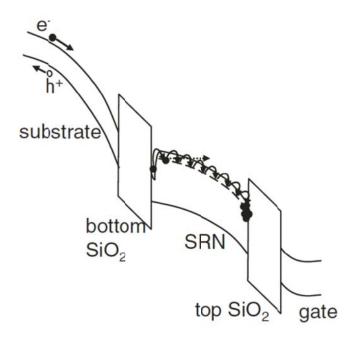

| Figure 16. SONOS band diagram with Poole Frenkel conduction in silicon nitride         | le. |

| Source: [53] 3                                                                         | 34  |

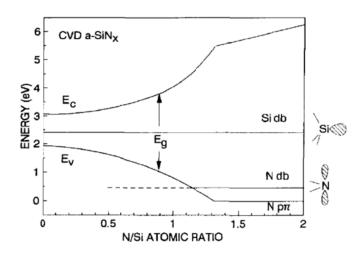

| Figure 17. Nitrogen to silicon ratio effect on silicon nitride band gap is shown wit   | th  |

| silicon dangling bond and nitrogen dangling bond levels [58].                          | 35  |

| Figure 18. Hot carrier electron injection in to silicon dioxide and hydrogen releas    | se  |

| [63].                                                                                  | 37  |

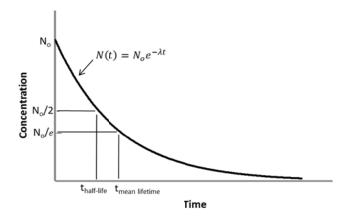

| Figure 19. "Ideal" plot of an exponential decay plot with representations of half-life | fе, |

| mean lifetime and respective concentrations. 4                                         | 13  |

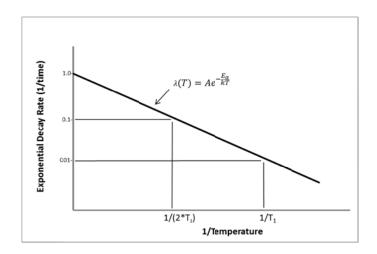

| Figure 20. "Ideal" plot of an Arrhenius function on a semi-log plot of exponentia      | al  |

| decay vs inverse temperature. 4                                                        | 14  |

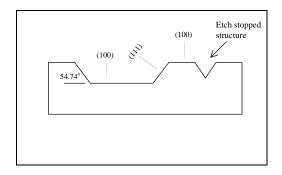

| Figure 21. Anisotropic etching characteristics of (100) silicon wafer.                 | 18  |

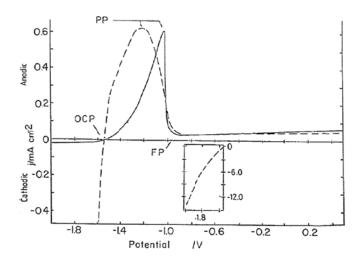

| Figure 22. Voltammogram profile for [100], solid line p-type silicon, dashed line r    | n-  |

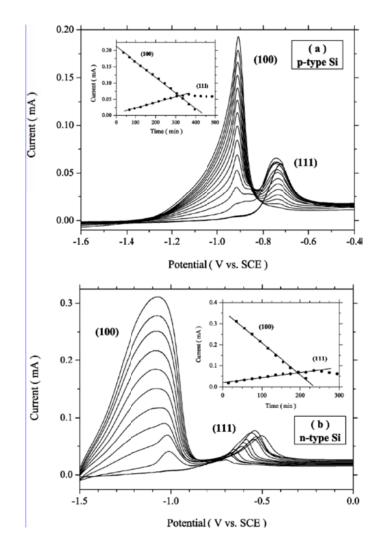

| type silicon in 40% KOH at 60°C [80].                                                  | 50  |

| Figure 23. Voltammogram profile for [100], solid line p-type, dashed line n-typ        | эе  |

| silicon in 25% wt. TMAH at 80°C [81].                                                  | 51  |

| Figure 24. Voltammograms provide insight to etching and passivation potentials o       |

|----------------------------------------------------------------------------------------|

| the [100] and [111] silicon faces in KOH for (a) p-type silicon and (b) n-type silicon |

| Source: [84].                                                                          |

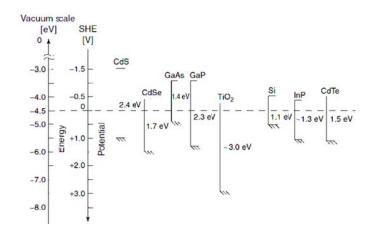

| Figure 25. Common semiconductor band gaps are shown relevant to vacuum scale           |

| and SHE electrode potential [86].                                                      |

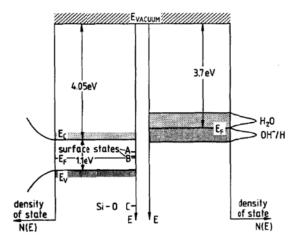

| Figure 26. The band diagram and density of state diagram for silicon and KOH alkal     |

| based etch solution respectively. Source: [66]                                         |

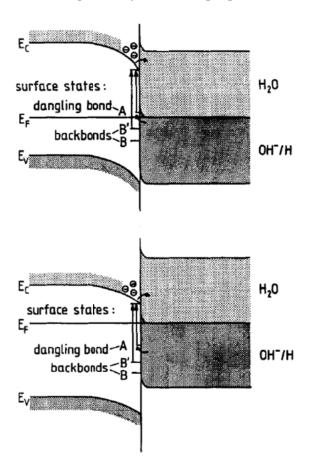

| Figure 27 Band diagram once the silicon is in contact with KOH alkali based etchant    |

| (top) p-type silicon, (bottom) n-type silicon. Source: [66]                            |

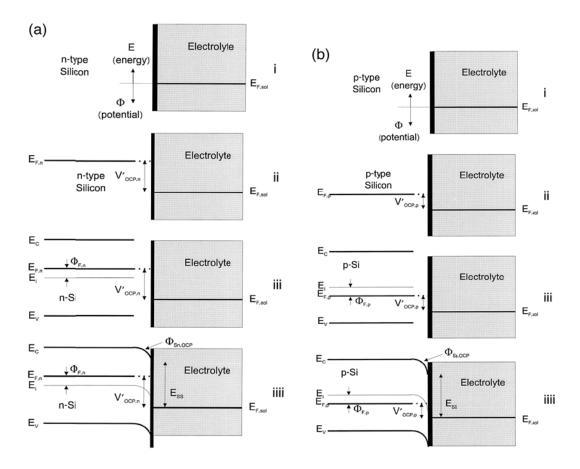

| Figure 28. Band diagram of silicon with 25% TMAH etch solution. (a) n-type             |

| silicon/alkali based electrolyte (b) p-type silicon/alkali based electrolyte. Source   |

| [87].                                                                                  |

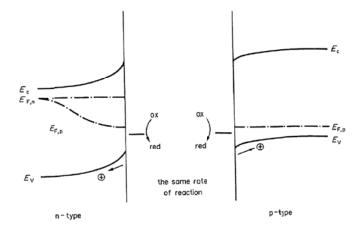

| Figure 29. Semiconductor Fermi levels shown at the interface of electret redox         |

| reaction [88].                                                                         |

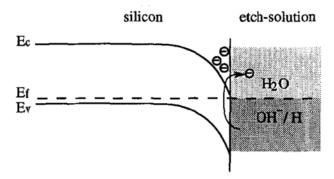

| Figure 30. P-type silicon in anisotropic KOH etchant. Source: [19].                    |

| Figure 31. Anodic bias to P-type silicon in anisotropic KOH etchant. Source: [19] 59   |

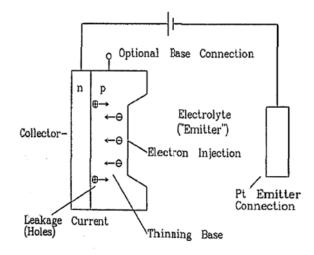

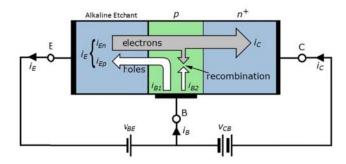

| Figure 32. npn BJT model of pn junction of electrochemical etch stop [91] 60           |

| Figure 33. NPN BJT schematic shown with the base-emitter forward biased and the        |

| base-collector reverse biased [81].                                                    |

| junction [81].                                                                        |

|---------------------------------------------------------------------------------------|

| Figure 35. Biased PN junction etch stop in KOH using a four electrode configuration.  |

| The relative potentials of the work electrode (pn junction), reference electrode, and |

| counter electrode are shown from left to right. Source: [93] 62                       |

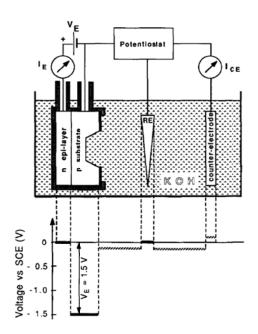

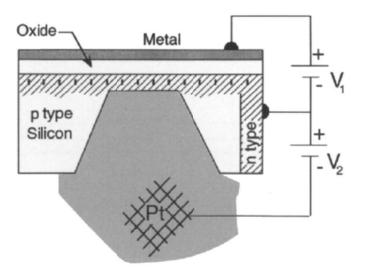

| Figure 36. A MIS electrochemical etch stop configuration in shown for p-type          |

| silicon. A region of n-type silicon is produced for electrical contact to the silicon |

| substrate. A platinum electrode is submerged in the etchant to bias the silicon-      |

| etchant interface [94].                                                               |

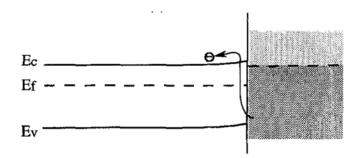

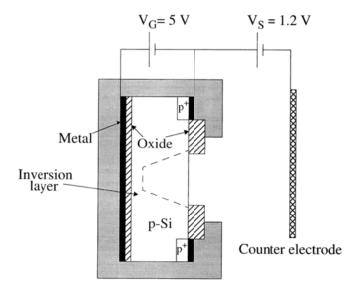

| Figure 37. MIS etch stop produced by inversion layer [82].                            |

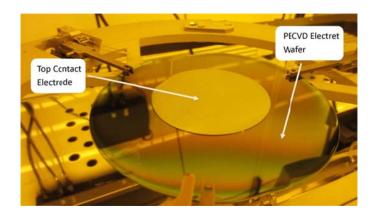

| Figure 38. 100 mm diameter silicon wafer with PECVD dielectric film is loaded with    |

| 2" "cathode" wafer in SUSS SB-6e bonder tooling.                                      |

| Figure 39. Schematic of the setup for the thermally assisted poling of the multilayer |

| film stack on a silicon wafer. 68                                                     |

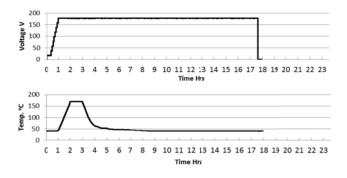

| Figure 40. Example temperature and voltage magnitude profile used for the electret    |

| activation process in the SUSS bonder. 69                                             |

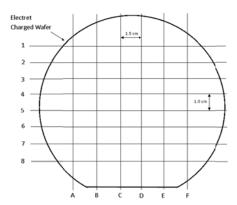

| Figure 41. ESV measurements were made over the wafer surface at the                   |

| intersections of the alpha numeric grid at a pitch of 1.5 cm and 1.0 cm.              |

| Figure 42. Anisotropic wet etch with electret on etch wafer. 76                       |

Figure 34. TMAH based three-electrode electrochemical etch stop using a pn

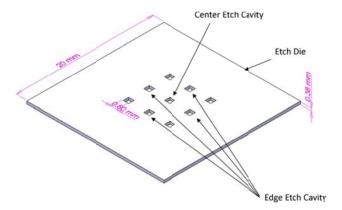

Figure 43. Each of the etch die contain 9 etch cavities for evaluation of effects of the electret on the progression of silicon etching in the cavities.

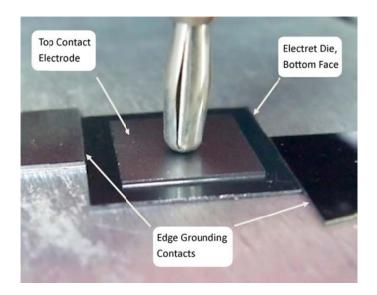

Figure 44. Die level electret activation was performed with sub-sized silicon die on the PECVD film. Small piece of silicon are placed to the edge of the die to improve ground contact between the hot plate and electret die.

79

Figure 45. Electret Oxide Semiconductor band diagram in a state of strong inversion.

81

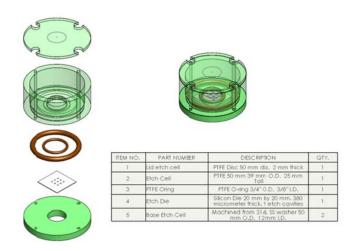

Figure 46. Isometric drawing of the etch cell assembly with sample die.

Figure 47. Nine etch cells are shown on the hot plate in the aluminum enclosure with the lid off to the side. One etch cell is shown with the PTFE lid removed, showing the silicon die and it's 9 respective etch cavities.

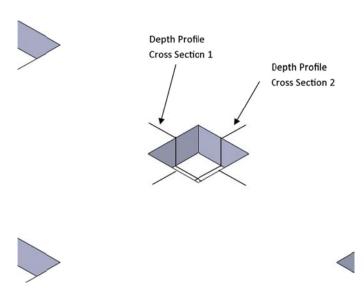

Figure 48. The surface topology is measured for five of the etch cavities on each die.

Two cross sections of each cavity measured provide a total of four etch depth measurements.

Figure 49. A "Modified" ESV measurement is made after each etching period to confirm that the electret is still active.

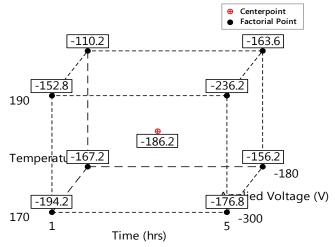

Figure 50. Negative potential ESV "cube" plot of the 2<sup>3</sup> full factorial DOE given the effects of temperature (°C), time (hrs), and applied voltage (V) on the ESV (V). The

| averages  | of the  | five | peak | ESV | values | for | each | wafer | are | shown | at th | e corners | and |

|-----------|---------|------|------|-----|--------|-----|------|-------|-----|-------|-------|-----------|-----|

| center of | the plo | ot.  |      |     |        |     |      |       |     |       |       |           | 93  |

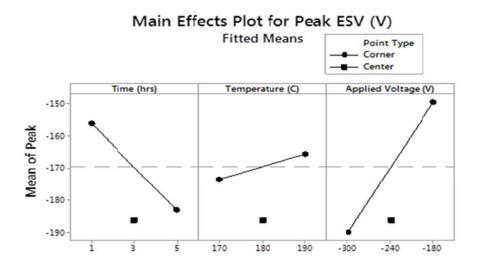

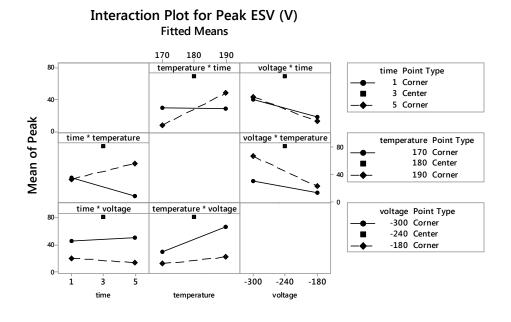

- Figure 51. The "main effects" plot of the negative ESV as a function of temperature (°C), time (hours), applied voltage (V).

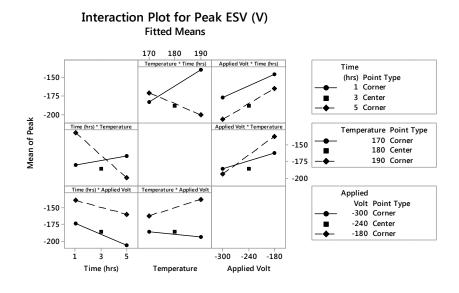

- Figure 52. Negative potential ESV "interaction" plot of temperature (°C), time (hours), applied voltage (V).

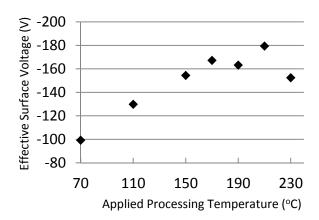

- Figure 53: Effective surface voltage as a function of applied process temperature for samples activated at 180 V for one hour.

97

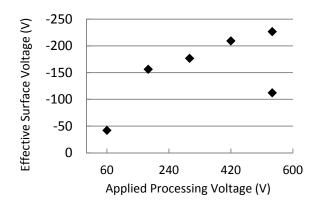

- Figure 54: Electret surface voltage as a function of applied process voltage for samples activated at 170°C for five hours.

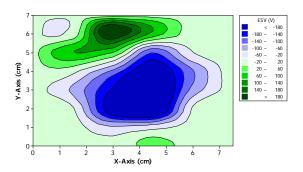

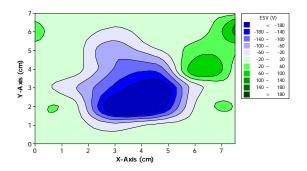

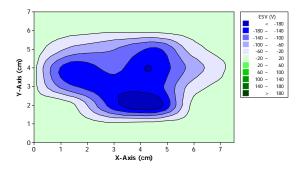

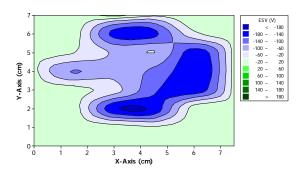

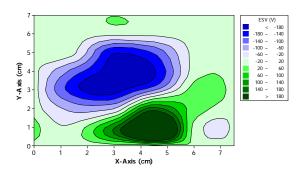

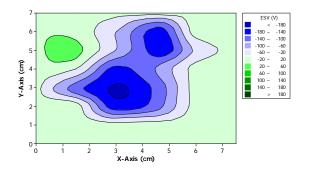

- Figure 55. ESV contour plot with electret activation at -300 V, 5 hrs, 190°C. The color coded legend on the right provides the scale of the ESV at 20 V increments. 99

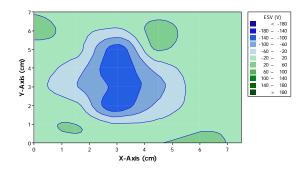

- Figure 56. ESV contour plot with electret activation at -300 V, 1 hrs, 170°C. The color coded legend on the right provides the scale of the ESV at 20 V increments. 99

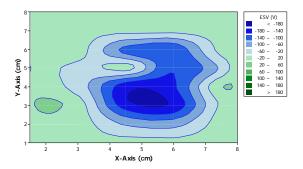

- Figure 57. ESV contour plot with electret activation at -300 V, 5 hrs, 170°C. The color coded legend on the right provides the scale of the ESV at 20 V increments. 99

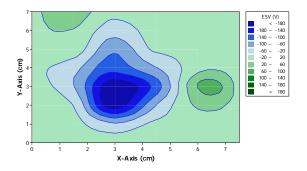

- Figure 58. ESV contour plot with electret activation at -180 V, 1 hrs, 190°C. The color coded legend on the right provides the scale of the ESV at 20 V increments. 100

Figure 59. ESV contour plot with electret activation at -180 V, 5 hrs, 170°C. The color coded legend on the right provides the scale of the ESV at 20 V increments. 100 Figure 60. ESV contour plot with electret activation at -300 V, 1 hr, 190°C. The color coded legend on the right provides the scale of the ESV at 20 V increments. 100 Figure 61. ESV contour plot with electret activation at -180 V, 1 hr, 170°C. The color coded legend on the right provides the scale of the ESV at 20 V increments. 101

Figure 62. ESV contour plot with electret activation at -225 V, 3 hrs, 180°C. The color coded legend on the right provides the scale of the ESV at 20 V increments. 101

Figure 63. ESV contour plot with electret activation at -180 V, 5 hrs, 190°C. The color coded legend on the right provides the scale of the ESV at 20 V increments. 101

Figure 64. Positive potential ESV "cube" plot of the 2³ full factorial DOE given the effects of temperature (°C), time (hrs), and negative applied voltage (V) on the ESV (V). The average of the five peak ESV values for each wafer are shown at the corners and center of the plot.

Figure 65. The "main effects" plot of the positive ESV as a function of temperature (°C), time (hrs), applied voltage (V).

Figure 66. Positive potential ESV "interaction" plot of temperature (°C), time (hrs), and applied voltage (V).

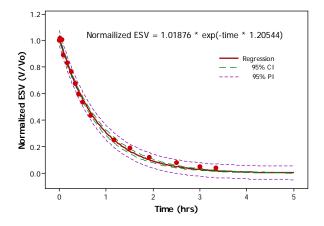

Figure 67. The ITPD plot for a sample from wafer 3 shows the ESV as a function of time, aged at 300°C. The sample was activated at 300 V for 1 hour at 170°C. The best fit regression to the exponential decay is provided with the 95% confidence interval and 95% prediction interval.

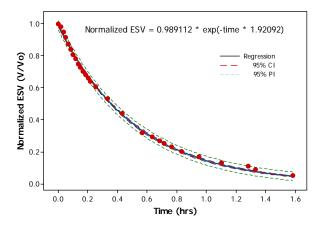

Figure 68. The ITPD plot for a sample from wafer 3 shows the ESV as a function of time, aged at 325°C. The sample was activated at 300 V for 1 hour at 170°C. The best fit regression to the exponential decay is provided with the 95% confidence interval and 95% prediction interval.

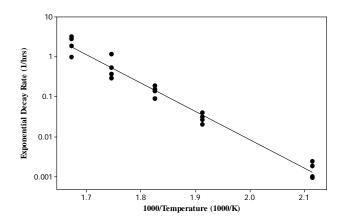

Figure 69. Positively charged electret, semi-log plot of the exponential decay rate vs 1000/Temperature. Samples from each of the 4 wafers were subjected to accelerated aging at 325°C, 300°C, 275°C, 250°C, and 200°C.

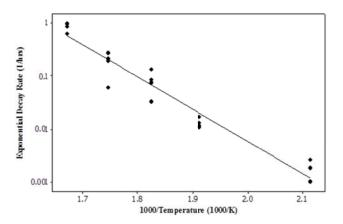

Figure 70. Negatively charged electret, semi-log plot of the exponential decay rate vs 1000/Temperature. Samples from each of the 4 wafers were subjected to accelerated aging at 325°C, 300°C, 275°C, 250°C, and 200°C.

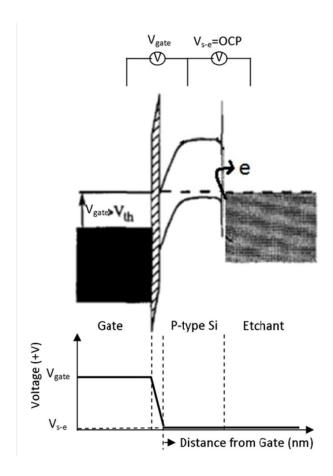

Figure 71. A band diagram of a the MIS etch stop with bias between gate and silicon and in open circuit potential between the silicon and electrolyte, alkali based etchant, showing the drift of electrons into the electrolyte and continuing the etch process with hydroxyl ion generation. The figure is modified from Smith and Soderbarg 1993 [19].

Figure 72. A linear best fit for etch depth samples as a function of the time remaining to the end of the silicon etch are grouped by electret potentials; positive, negative, and neutral.

114

### 1 INTRODUCTION

Electrets are materials with permanent "net" and "polarized" charges that reside on the surface or within the material [3]. Electrets are beneficial for providing a continuous electrostatic potential, over a range of fractional volts to several thousand volts, without the use of an external power supply. The electret provides an apparent potential at its surface, referred to as the effective surface voltage (ESV). Thin film electrets have produced some revolutionary devices such as the electret microphone and nonvolatile memory which remain functional for decades Traditionally, field effect transistor (FET) microphones, also known as electret condenser microphones (ECMs), are made with an electret consisting of a Mylar or Polytetrafluoroethylene (PTFE) [3, 7, 8]. Integration of surface mount electret microphones has been limited due to the inability of the polymer electret to maintain a charge throughout the surface mount reflow process which can be as high at 260°C. Inorganic electret materials, such as silicon oxide and silicon nitride have been shown to provide stable electret charge at elevated temperatures exceeding surface mount reflow process [2, 7-10]. Research has been conducted with these inorganic electret materials to integrate them in to MEMS microphones providing the benefits of system integration and charge stability [8, 9]. mechanical properties, together with the established integration of silicon oxide and silicon nitride films in MEMS platforms, makes these films an excellent choice for integrating electrets into MEMS devices [11]. The benefits of electrets as a permanent or semi-permanent electric field source has been realized in many other applications; Xerography [6, 12], dosimeters [13, 14], pressure sensors [10], energy harvesters [15], electro-active polymer (EAP) actuation [16, 17], and solar cells [18].

Thermally assisted poling, corona charging, and electron beam exposure are three methods frequently used to produce electret materials. Each method has its benefits and limitations; the best choice depends on the material to be charged, the application, and cost effectiveness. Corona charging and electron beam exposure are frequently used in microfabricated devices; corona charging is limited by the requirement of ion exchange, and both corona charging and electron beam exposure are limited by single polarity charging, and custom equipment to form the electret. Thermally assisted poling is the oldest method of electret formation. In this method, a mixture of carnauba wax and colophony (tree sap) is heated to its melting point while a high electric field is applied between two electrodes in contact with the mixture; the mixture is cooled to solidification under the electric field to produce the electret. Direct contact poling is rarely discussed as part of a MEMS based manufacturing process and has not been addressed for multilayer SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub> films. The new process presented does share some similarities to charge trap flash memory devices, with important differences in increased film thickness and the open faced charged film being unique to the electret produced. The purpose of this study is to develop a PECVD  $SiO_2/Si_3N_4/SiO_2$  electret with a direct contact thermally assisted poling process that requires no ionic interface with the PECVD film surface as part of the charging process, can produce both positive and negative effective surface voltages with a single process polarization, and can be conducted with commercially available semiconductor processing equipment. There are three main aims to this study which will be investigated.