## University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

5-2017

# Modeling and Validation of 4H-SiC Low Voltage MOSFETs for Integrated Circuit Design

Shamim Ahmed University of Arkansas, Fayetteville

Follow this and additional works at: http://scholarworks.uark.edu/etd

Part of the Electronic Devices and Semiconductor Manufacturing Commons

## Recommended Citation

Ahmed, Shamim, "Modeling and Validation of 4H-SiC Low Voltage MOSFETs for Integrated Circuit Design" (2017). Theses and Dissertations. 1945.

http://scholarworks.uark.edu/etd/1945

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, ccmiddle@uark.edu.

## A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Engineering with a Concentration in Electrical Engineering

by

## Shamim Ahmed University of Arkansas Master of Science in Electrical Engineering, 2015

## May 2017 University of Arkansas

This dissertation is approved for recommendation to the Graduate Council.

| Dr. H. Alan Mantooth  |  |

|-----------------------|--|

| Dissertation Director |  |

|                       |  |

|                       |  |

| Dr. Jia Di            |  |

| Committee Member      |  |

|                       |  |

|                       |  |

| <i>D</i> G;           |  |

| Dr. Simon Ang         |  |

| Committee Member      |  |

|                       |  |

|                       |  |

| Mr. Tom Vrotsos       |  |

| Committee Member      |  |

#### Abstract

Silicon Carbide is a promising wide bandgap material and gradually becoming the first choice of semiconductor for high density and high efficiency power electronics in medium voltage range (500-1500V). SiC has also excellent thermal conductivity and the devices fabricated with the material can operate at high temperature (~ 400 ° C). Thus, a power electronic system built with SiC devices requires less cooling requirement and saves board space and cost. The high temperature applications of SiC material can also be extended to space exploration, oil and gas rigging, aerospace and geothermal energy systems for data acquisition, sensing and instrumentation and power conditioning and conversion. But the high temperature capability of SiC can only be utilized when the integrated circuits can be designed in SiC technology and high fidelity compact models of the semiconductor devices are a *priori* for reliable and high yielding integrated circuit design.

The objective of this work is to develop industry standard compact models for SiC NMOS and PMOS devices. A widely used compact model used in silicon industry called BSIM3V3 is adopted as a foundation to build the model for SiC MOSFET. The models optimized with the built-in HSPICE BSIM3V3.3 were used for circuit design in one tape-out but BSIM3V3 was found to be inadequate to model all of the characteristics of SiC MOSFET due to the presence of interface trapped charge. In the second tape-out, the models for SiC NMOS and PMOS were optimized based on the built-in HSPICE BSIM4V6.5 and a number of functioning circuits which have been published in reputed journal and conference were designed based on the models. Although BSIM4 is an enhanced version of BSIM3V3, it also could not model a few deviant SiC MOSFET characteristics such as body effect, soft saturation etc. The new model developed for SiC NMOS and PMOS based on BSIM4V7.0 is called BSIM4SIC and can model the entire range of device

characteristics of the devices. The BSIM4SIC models are validated with a wide range of measured data and verified using the models in the simulation of numerous circuits such as op-amp, comparator, linear regulator, reference and ADC/DAC.

©2017 by Shamim Ahmed All Rights Reserved

#### Acknowledgements

I am most thankful to my Ph.D. advisor Dr. H. Alan Mantooth for giving me the opportunity to work in very exciting research projects and his invaluable mentorship all throughout my doctorate program. From him, I have not only learned how to be a good researcher but also how to be a polished professional. My gratitude also goes to my advisory committee member – Dr. Simon Ang, Dr. Jia Di and Tom Vrotsos for their cooperation during my Ph.D. I would especially like to thank Tom for his insight, guidance and cordial support in my modeling work. Dr. Randy Brown helped me so much with my graduate studies at the Electrical Engineering department at the University of Arkansas and I am eternally grateful to him.

I would like to convey my special thanks to Dr. Matt Francis from Ozark IC for his Verilog-A version of the BSIM4 model and great advice on the development of a good compact model. He is one of the most knowledgeable and creative people in the modeling and CAD area. My sincerest gratitude also goes to Jim Holmes from Ozark IC for sharing his vast experience on IC design and semiconductor device characterization. I heartily thank the late Dr. Michael glover (may his soul rest in peace) for helping me become an organized researcher. During my model development on SiC MOSFETs, I got a lot of good suggestions from the circuit designers in our lab and I want to thank them from the bottom of my heart. The suggestions I received from Dr. Paul Shepherd, Dr. Matthew Barlow and Dr. Ashfaqur Rahman immeasurably helped me improve the models. I would also like to thank Aminta and Maria for helping me characterizing a large number of SiC devices. Robert Murphree also deserves heartful gratitude from me as helped me enhance my circuit design knowledge. I am very grateful to Kathy Kirk, Kim Gillow and Gina Swanson for their kind and generous administrative support during my stay at the MSCAD lab.

The research work presented in this dissertation was funded by the National Science Foundation grants #IIP1237816 and #EPS-1003970. I would like to convey my sincere thanks to the NSF for the financial support.

## **Dedication**

To my beloved parents and my little sister Shamima

## **Table of Contents**

| CHA  | PTER 1 | I INTRODUCTION                                      | 1  |

|------|--------|-----------------------------------------------------|----|

| 1.1  | Motiv  | ation                                               | 1  |

| 1.2  | Resea  | rch Objectives                                      | 2  |

| 1.3  | Key C  | Contributions                                       | 3  |

| 1.4  | Disse  | rtation Outline                                     | 4  |

| CHAI | PTER 2 | 2 SIC TECHNOLOGY                                    | 6  |

| 2.1  | Prope  | rties of SiC Material                               | 6  |

| 2    | .1.1   | SiC Crystal structure                               | 6  |

| 2    | .1.2   | Chemical and mechanical properties                  | 8  |

| 2    | .1.3   | Bandgap voltage and intrinsic carrier concentration | 8  |

| 2    | .1.4   | Impact ionization coefficients                      | 11 |

| 2    | .1.5   | Bulk and surface mobility                           | 13 |

| 2.2  | SiC D  | evices and Fabrication Technology                   | 14 |

| 2    | .2.1   | SiC CMOS process                                    | 15 |

| 2    | .2.2   | Power MOSFET                                        | 18 |

| 2    | .2.3   | Other Devices                                       | 19 |

| 2.3  | Sumn   | nary                                                | 20 |

| CHAI | PTER : | AN OVERVIEW OF SEMICONDUCTOR DEVICE MODELING        | 21 |

| 3.1  | Semio  | conductor Device Modeling Using Numerical Method    | 21 |

| 3.2  | Comp   | act Models for Circuit Design and Simulation        | 23 |

| 3.3  | Comp   | act Models of SiC Devices                           | 33 |

| 3    | .3.1   | Lateral MOSFET Models                               | 34 |

| 3    | .3.2   | Power MOSFET Model                                  | 35 |

| 3    | .3.3   | Models of Other SiC Devices                         | 36 |

| 3.4  | Sumn   | nary                                                | 37 |

| CHAI | PTER 4 | CHARACTERIZATION OF SIC MOSFET                      | 38 |

| 4.1  | Test S | tructures                                           | 38 |

| 42   | DC C   | haracterization                                     | 45 |

| 4.2.1      | Characterization of a MOSFET I-V                                    | 47  |

|------------|---------------------------------------------------------------------|-----|

| 4.2.2      | Characterization of Parasitic D/S to Body Diode                     | 50  |

| 4.2.3      | Best Practices of DC Characterization                               | 51  |

| 4.3 C-V (  | Characterization                                                    | 52  |

| 4.3.1      | MOSFET C-V Characterization                                         | 55  |

| 4.3.2      | Diode C-V Characterization                                          | 57  |

| 4.3.3      | Best Practices of C-V Measurement                                   | 57  |

| 4.4 Sumn   | nary                                                                | 61  |

| CHAPTER :  | 5 BSIM3 AND BSIM4 BASED MODELS OF SIC MOSFET                        | 62  |

| 5.1 BSIM   | 13V3 as a Foundation for SiC MOSFET Model Development               | 62  |

| 5.2 Mode   | el Formulation in BSIM3V3                                           | 66  |

| 5.2.1      | Core Model Development of DC Characteristics                        | 66  |

| 5.2.2      | Modeling of the Secondary DC Effects                                | 78  |

| 5.2.3      | Intrinsic Charge Modeling                                           | 89  |

| 5.2.4      | Small Signal Capacitance Modeling                                   | 99  |

| 5.2.5      | Parasitic Capacitance Modeling                                      | 102 |

| 5.2.6      | Parameter Extraction and Optimization with HSPICE BSIM3V3           | 107 |

| 5.2.7      | Model Optimization Results with BSIM3V3                             | 108 |

| 5.2.8      | Limitations of BSIM3V3 in Modeling SiC MOSFET                       | 110 |

| 5.3 BSIM   | 14 for SiC MOSFET Modeling                                          | 111 |

| 5.3.1      | Parameter Extraction and Optimization with HSPICE BSIM4             | 115 |

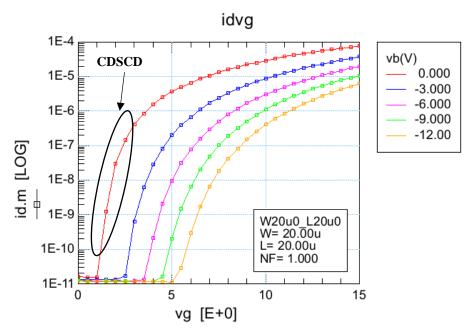

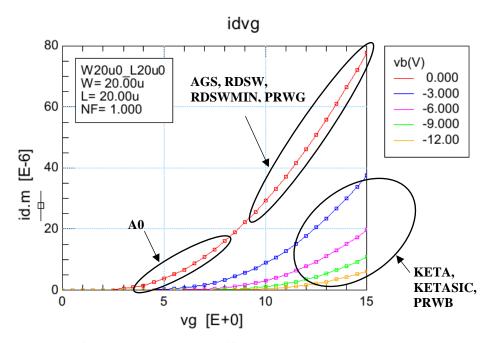

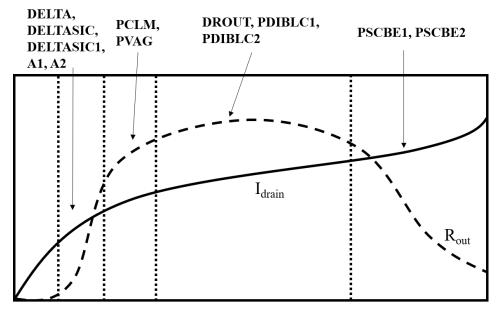

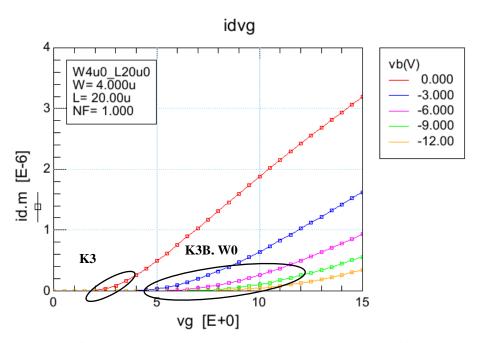

| 5.3.2      | Model Optimization Results of SiC MOSFET with HSPICE BSIM4.6.5      | 119 |

| 5.3.3      | Limitations of BSIM4 in Modeling SiC MOSFET                         | 148 |

| 5.4 Circu  | it Design with BSIM3V3 and BSIM4 Based Models                       | 149 |

| 5.5 Sumn   | nary                                                                | 149 |

| CHAPTER    | 6 EFFECTS OF INTERFACE TRAPS ON SIC MOS DEVICES                     | 150 |

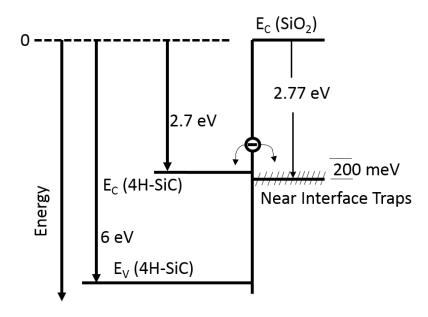

| 6.1 Origin | n of the interface states in SiC MOSFET                             | 150 |

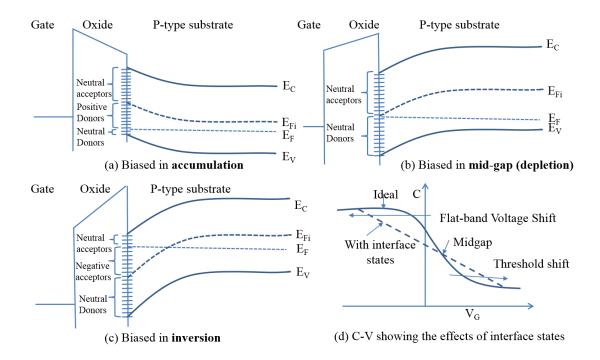

| 6.2 Effect | ts of the interface trapped charge on 4H-SiC MOSFET Characteristics | 152 |

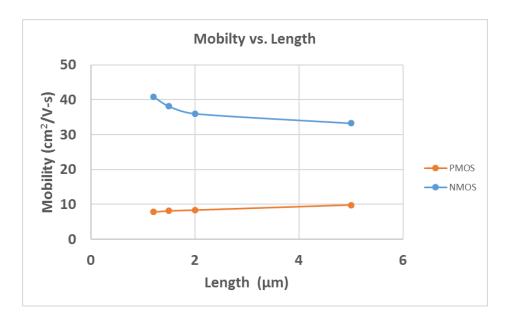

| 6.2.1      | Mobility Reduction                                                  | 154 |

| 6.2.2      | Subthreshold Slope Reduction                                        | 156 |

| 6.2.3      | Body Effect Alteration                                              | 158 |

|            |                                                                     |     |

| 6.3  | Effects on CV Characteristics                         | 161 |

|------|-------------------------------------------------------|-----|

| 6.4  | Soft transition from triode to saturation             | 164 |

| 6.5  | Effects on High Temperature Behavior                  | 164 |

| 6.6  | Summary                                               | 168 |

| CHAF | PTER 7 MODEL DEVELOPMENT OF SIC MOSFET WITH VERILOG-A | 169 |

| 7.1  | Implementation of BSIM470 in Verilog-A                | 169 |

| 7.2  | Modeling of Interface Traps Related Effects           | 170 |

| 7.   | 2.1 Body Effects Modeling                             | 174 |

| 7.   | 2.2 Flat band Voltage Shift Modeling                  | 176 |

| 7.   | 2.3 Modeling of triode-to-saturation soft transition  | 176 |

| 7.   | 2.4 Intrinsic carrier concentration model             | 177 |

| 7.3  | A new parameter extraction method for MOSFET C-V      | 177 |

| 7.4  | Temperature scaling                                   | 182 |

| 7.5  | Geometry Scaling.                                     | 183 |

| 7.6  | Parameter Extraction and Optimization                 | 184 |

| 7.7  | Model Optimization Results                            | 199 |

| 7.8  | Model Verification                                    | 228 |

| 7.9  | Discussion on the model performance                   | 228 |

| 7.10 | Summary                                               | 229 |

| CHAF | PTER 8 CONCLUSION AND FUTURE WORK                     | 230 |

| 8.1  | Research Summary                                      | 230 |

| 8.2  | Major Conclusions                                     | 231 |

| 8.3  | Future Work                                           | 231 |

| BIBL | IOGRAPHY                                              | 232 |

| APPE | NDIX                                                  | 245 |

# **List of Figures**

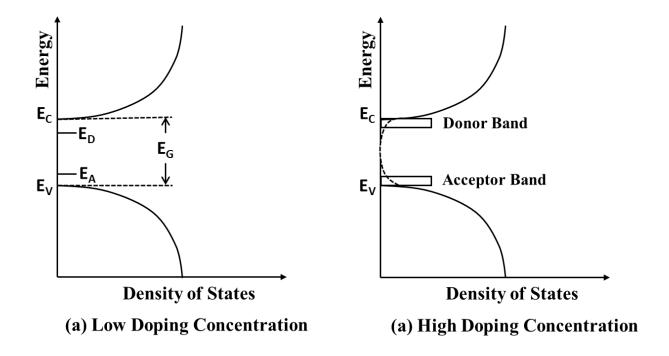

| Fig. 2.1. Energy band profile with respect to density of states: (a) at low doping                     |

|--------------------------------------------------------------------------------------------------------|

| concentration, dopant activation energy ( $E_A$ and $E_D$ ) has discrete values and (b) at high doping |

| concentration dopant energy has continuous range of values in a band [7]                               |

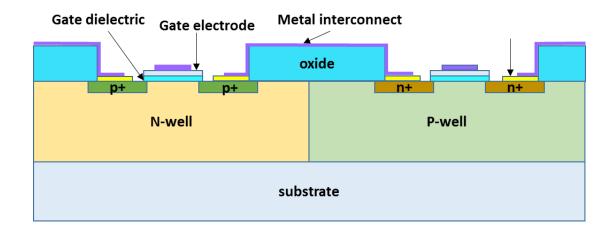

| Fig. 2.2. Simplified cross section of an inverter in the Raytheon high temperature SiC                 |

| CMOS process                                                                                           |

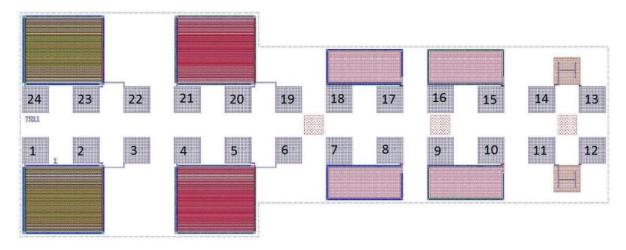

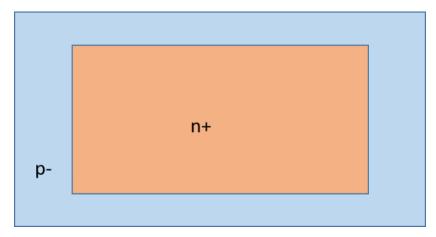

| Fig. 4.1 Test structures of NMOS array with different device widths and lengths 38                     |

| Fig. 4.2. Test structure of PMOS array with different device widths and lengths 40                     |

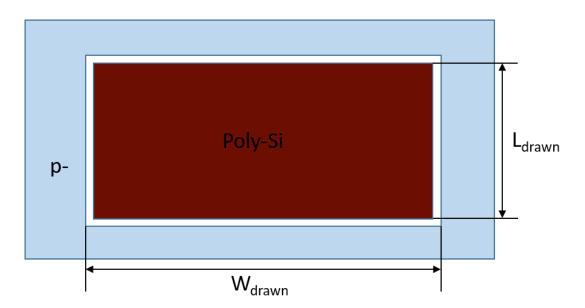

| Fig. 4.3. A typical layout of the MOS cap structure. Gate oxide is underneath the poly Si.             |

| 41                                                                                                     |

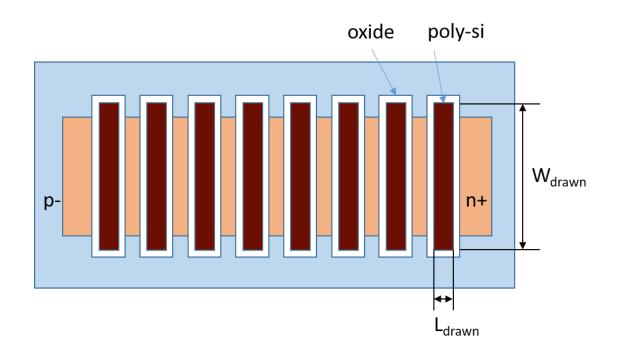

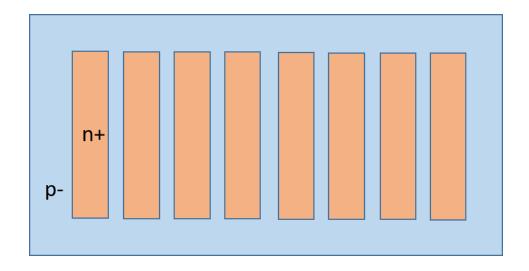

| Fig. 4.4. A typical layout of the multi-fingered MOSFET. Although not shown, the drain                 |

| and source terminals of all the fingers are usually shorted in this type of structure                  |

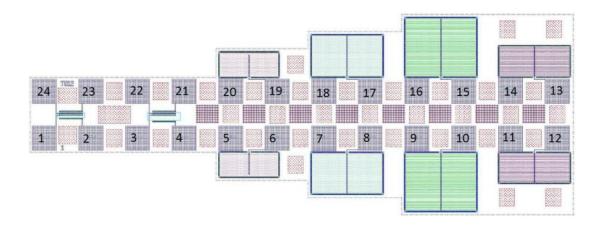

| Fig. 4.5. Test structure for MOSFET C-V measurement. Devices located on the top row                    |

| are used for the capacitance characterization                                                          |

| Fig. 4.6. High area and high perimeter parasitic diode structure of NMOS and PMOS. The                 |

| devices located at the top row are used for characterization                                           |

| Fig. 4.7. Typical layout of a n+/p-well diode with large area and small periphery 44                   |

| Fig. 4.8. Typical layout of a n+/p-well diode with large area and large periphery 45                   |

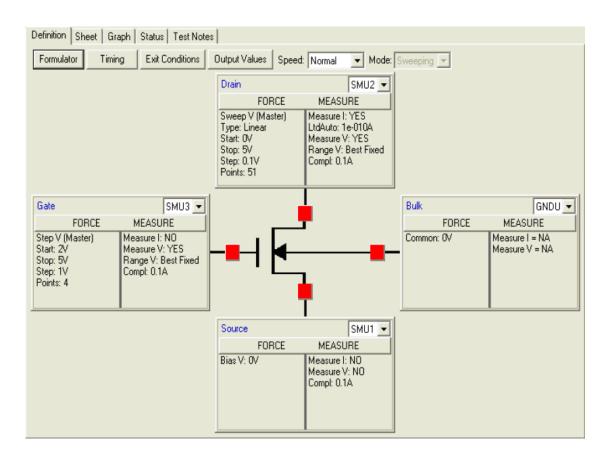

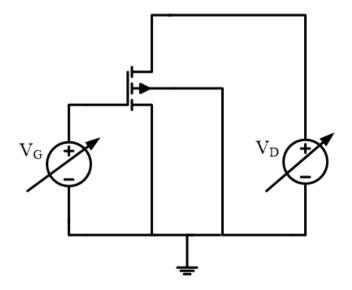

| Fig. 4.9. KITE configuration for MOSFET DC characterization                                            |

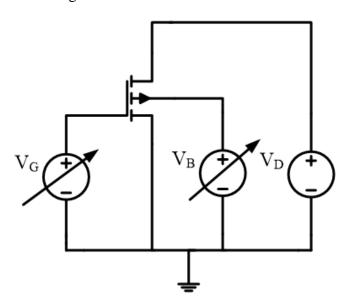

| Fig. 4.10. Test bench for transfer Characteristics characterization                                    |

| Fig. 4.11. Test bench for output characteristics characterization at zero body voltage 48              |

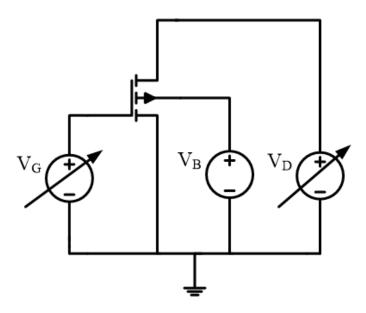

| Fig. 4.12. Test bench for output characteristics characterization at maximum body voltage.             |

| 18                                                                                                     |

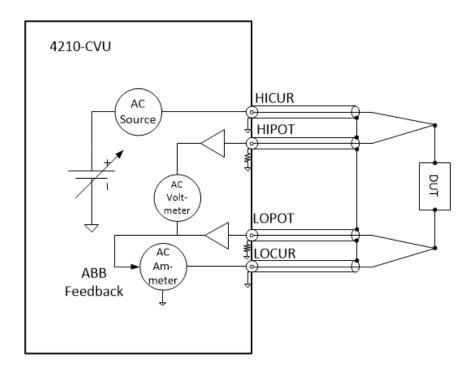

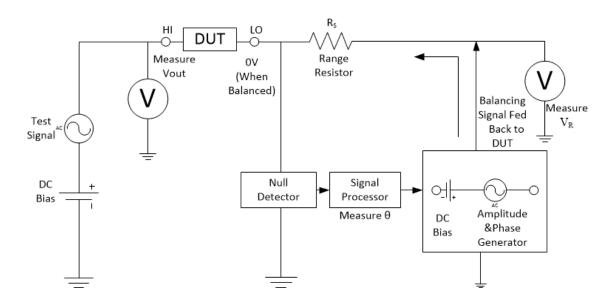

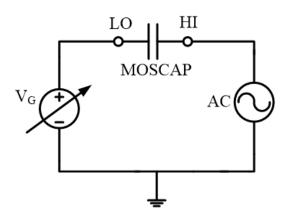

| Fig. 4.13. Simplified connection diagram between the device and C-V meter [109] 53                        |

|-----------------------------------------------------------------------------------------------------------|

| Fig. 4.14. Conceptual block diagram of the auto balance bridge capacitance measurement                    |

| method [110]54                                                                                            |

| Fig. 4.15. Test bench for oxide capacitance (C <sub>ox</sub> ) measurement                                |

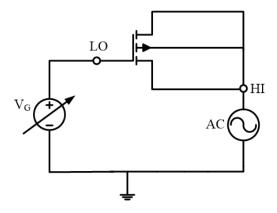

| Fig. 4.16. Test bench for total gate capacitance (C <sub>g-dsb</sub> ) measurement                        |

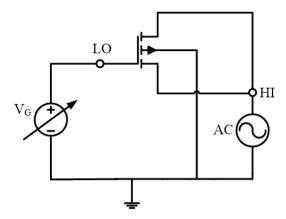

| Fig. 4.17. Test bench for overlap capacitance and intrinsic gate-to-drain/source (C <sub>g-ds</sub> )     |

| measurement                                                                                               |

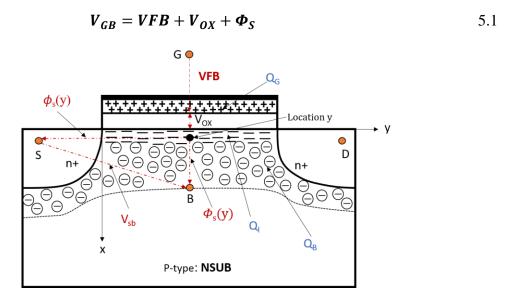

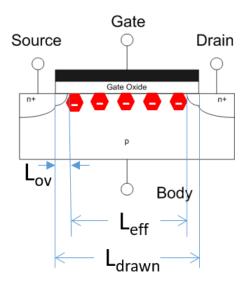

| Fig. 5.1. Simplified cross section of an NMOS structure. The orange circles represent the                 |

| device terminals (gate, source, drain, body) and the dark circle denotes an arbitrary point in the        |

| channel. The voltages and surface potential are identified by red lettered names. The blue lettered       |

| names indicate the charge in the device                                                                   |

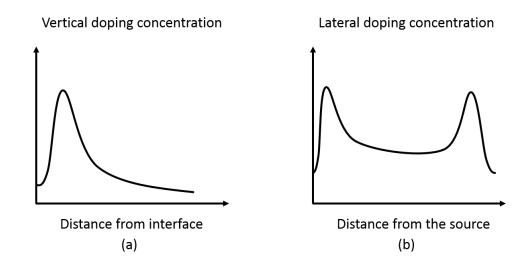

| Fig. 5.2. (a) Vertical doping profile and (b) lateral doping profile in a MOSFET channel.                 |

|                                                                                                           |

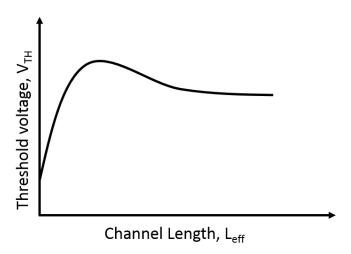

| Fig. 5.3. Combined effects of lateral non-uniform substrate doping concentration and short                |

| channel on threshold voltage                                                                              |

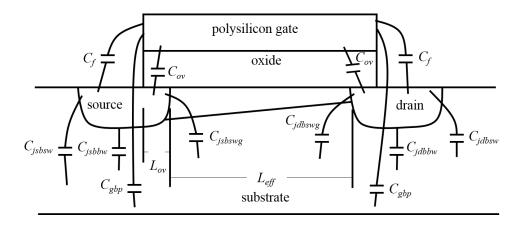

| Fig. 5.4. Parasitic capacitances in a MOSFET device                                                       |

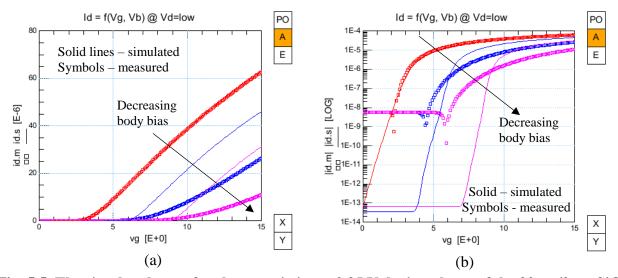

| Fig. 5.5. The simulated transfer characteristics at 0.25 V drain voltage of the $20\mu m/2\mu m$          |

| SiC NMOS are overlaid with the measured characteristics: (a) in linear scale to demonstrate the           |

| strong inversion region and (b) in log scale to demonstrate the subthreshold region 108                   |

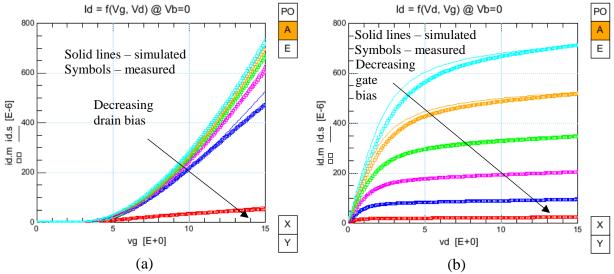

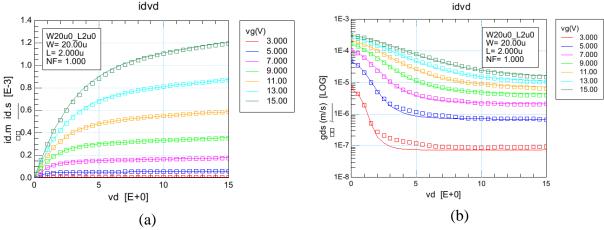

| Fig. 5.6. (a) The measured and simulated $I_d$ – $V_g$ characteristics of the $20\mu m/2\mu m$ NMOS       |

| at different drain voltages and zero body voltage and (b) the output characteristics $(I_d - V_d)$ of the |

| NMOS at different gate biases and zero bulk voltage                                                       |

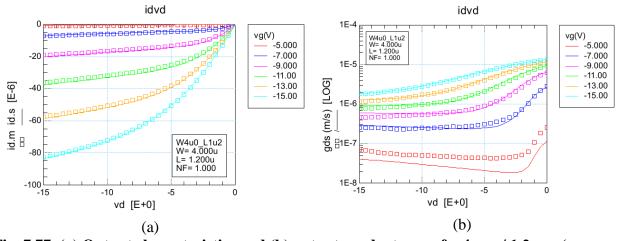

| Fig. 5.7. (a) Transconductance $(g_m)$ vs. gate voltage $(V_g)$ characteristics at different body                  |

|--------------------------------------------------------------------------------------------------------------------|

| bias and (b) output resistance ( $r_{out}$ ) vs. drain voltage ( $V_d$ ) at different gate voltage of the NMOS.    |

|                                                                                                                    |

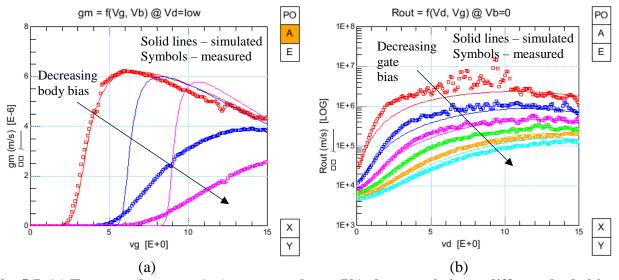

| Fig. 5.8. Simulated and measured (a) oxide capacitance ( $C_{OX}$ ) vs. gate-to-bulk voltage ( $V_{gb}$ )          |

| and (b) total gate capacitance (Cgg) vs. gate-to-drain/source/bulk voltage ( $V_{\text{g-dsb}}$ ). Solid lines and |

| symbols represent simulated and measured characteristics respectively                                              |

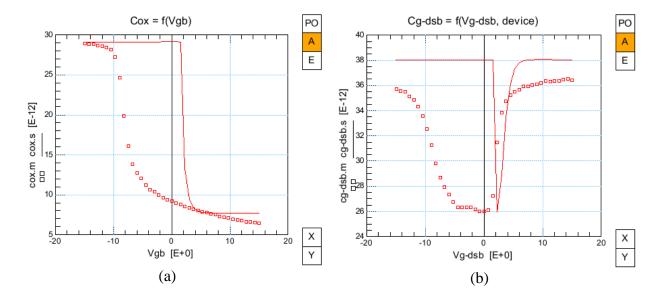

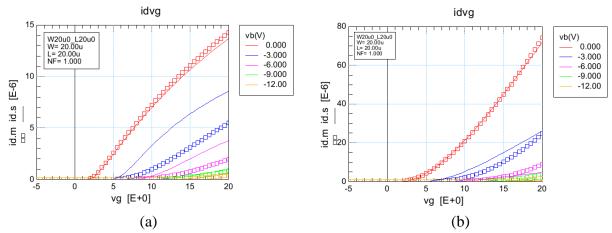

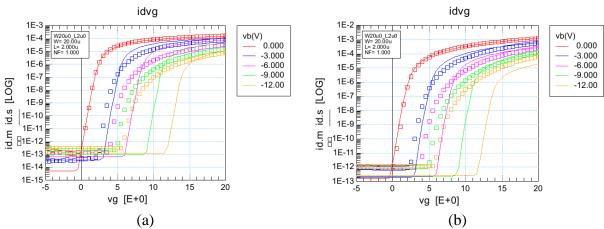

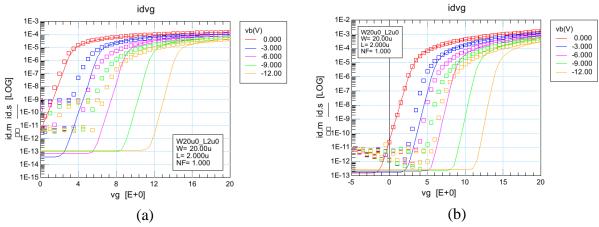

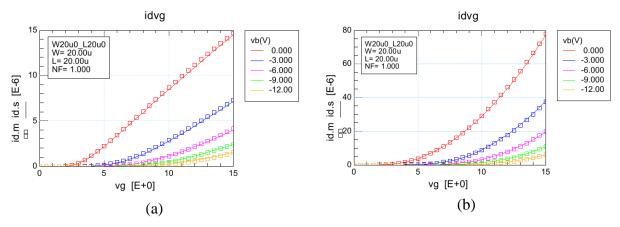

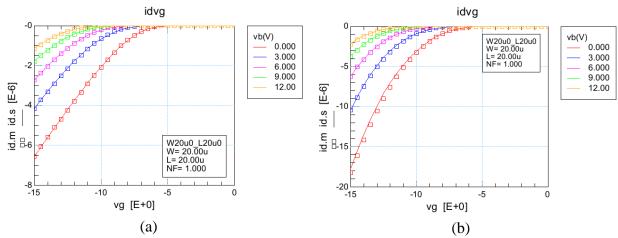

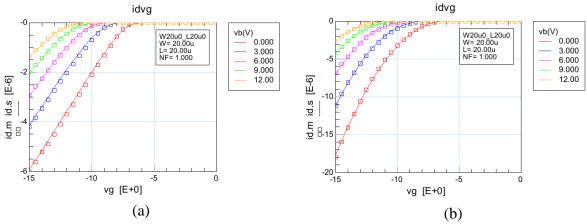

| Fig. 5.9. Transfer characteristics of a 20 $\mu m$ / 20 $\mu m$ (wide and long) NMOS at 25 $^{0}C$ in              |

| strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                                 |

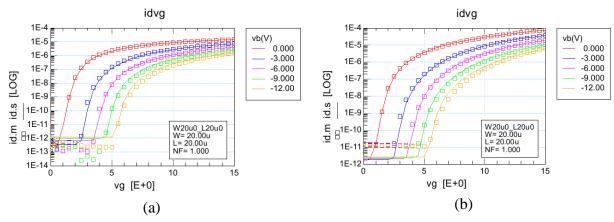

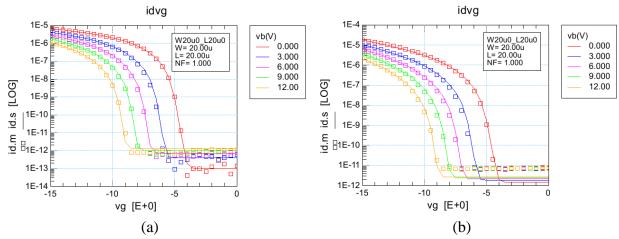

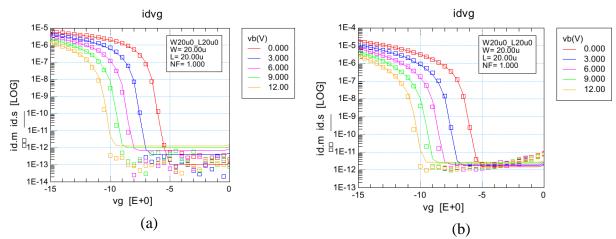

| Fig. 5.10. Transfer characteristics of a 20 $\mu m$ / 20 $\mu m$ (wide and long) NMOS at 25 $^{0}C$ in             |

| subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                                     |

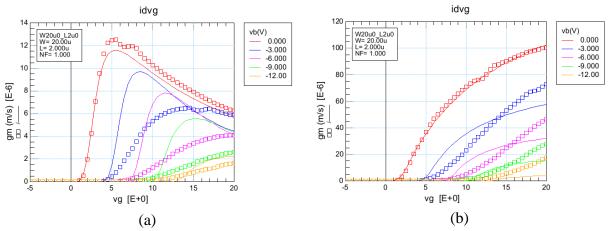

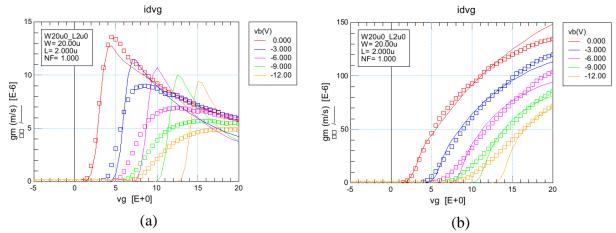

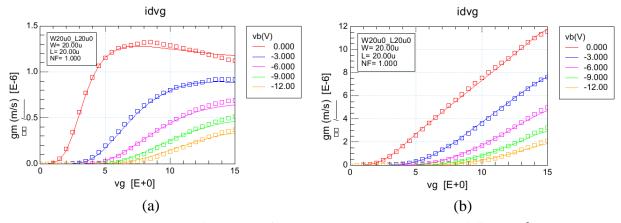

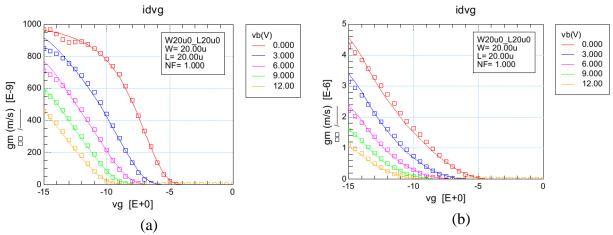

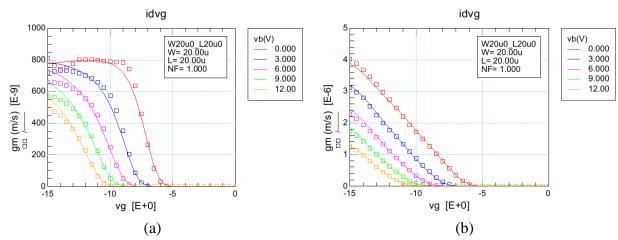

| Fig. 5.11. Transconductance of a 20 $\mu m$ / 20 $\mu m$ (wide and long) NMOS at 25 $^{0}C;$ (a) at                |

| 0.5 V and (b) 15V drain-to-source voltage.                                                                         |

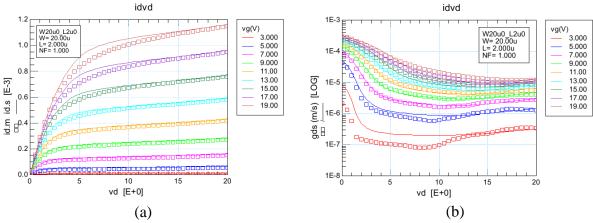

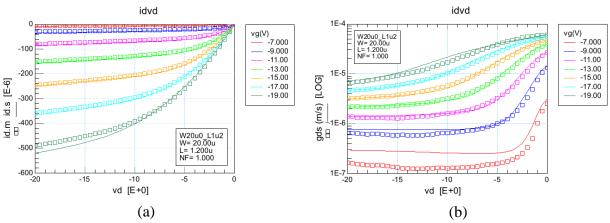

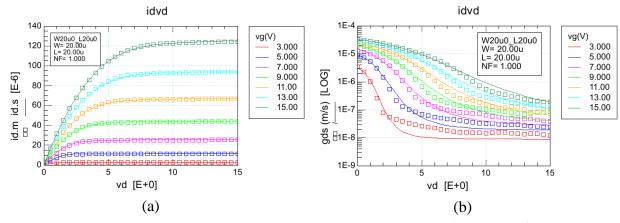

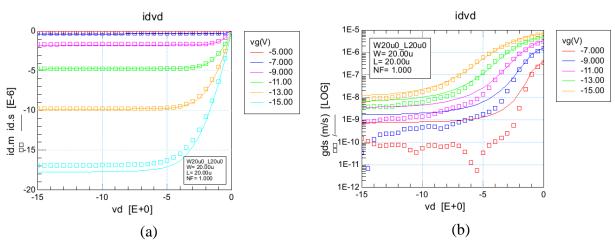

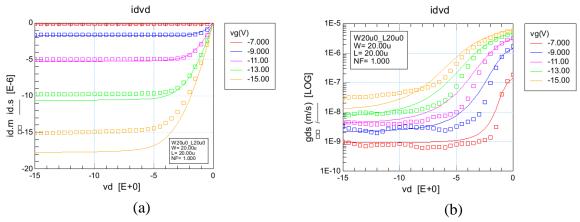

| Fig. 5.12. (a) Output characteristics and (b) output conductance of a 20 $\mu m$ / 20 $\mu m$ (wide                |

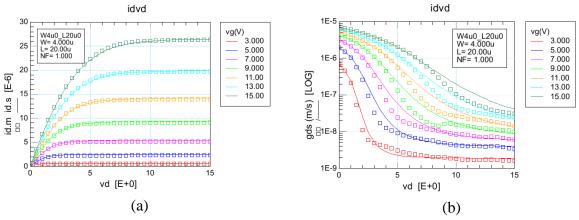

| and long) NMOS at 25 <sup>0</sup> C                                                                                |

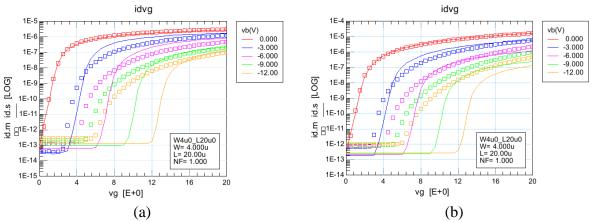

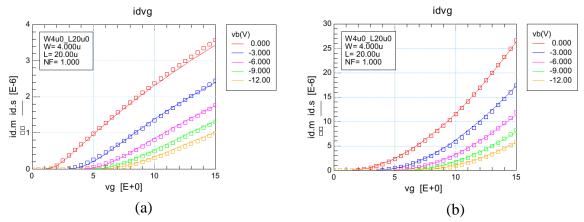

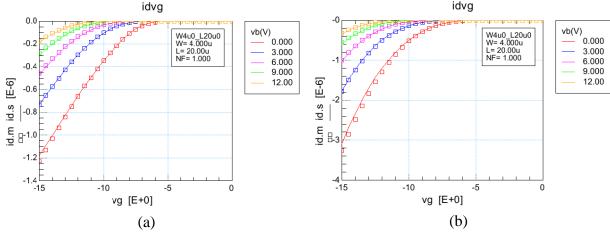

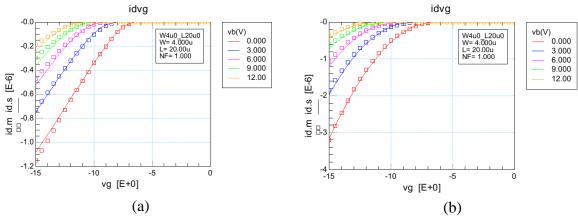

| Fig. 5.13. Transfer characteristics of a 4 $\mu m$ / 20 $\mu m$ (narrow and long) NMOS at 25 $^{0}C$ in            |

| strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                                 |

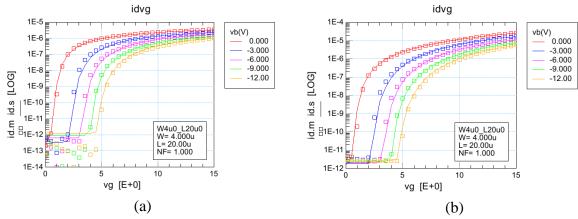

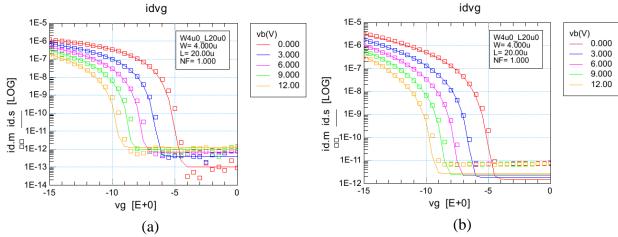

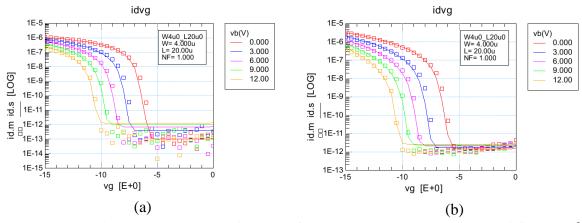

| Fig. 5.14. Transfer characteristics of a 4 $\mu m$ / 20 $\mu m$ (narrow and long) NMOS at 25 $^{0}C$ in            |

| subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                                     |

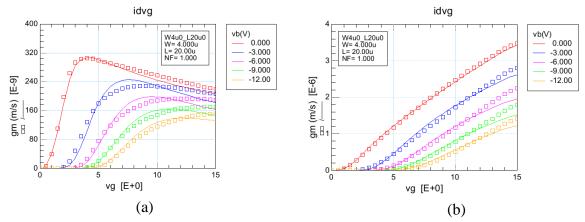

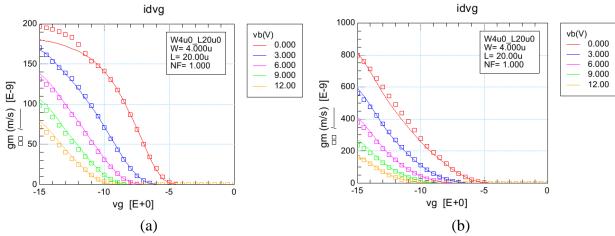

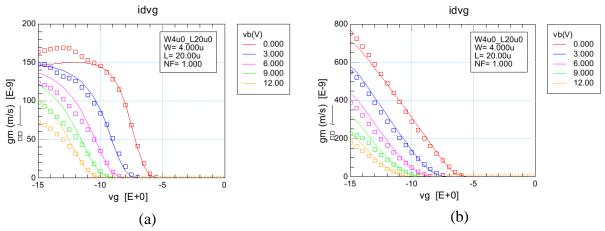

| Fig. 5.15. Transconductance of a 4 $\mu m$ / 20 $\mu m$ (narrow and long) NMOS at 25 $^{0}C;$ (a) at               |

| 0.5 V and (b) 15V drain-to-source voltage                                                                          |

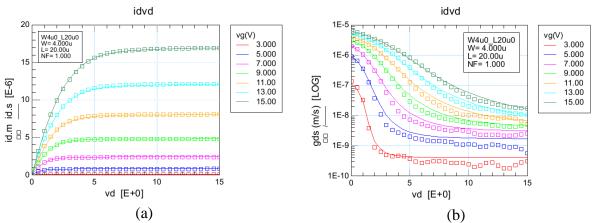

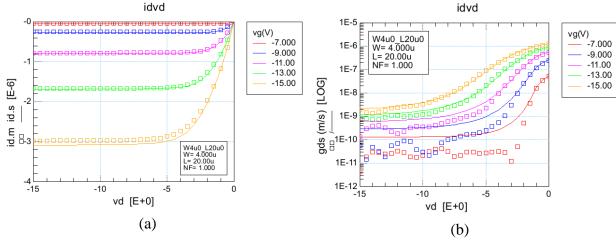

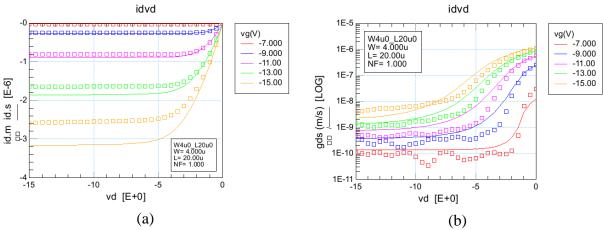

| Fig. 5.16. (a) Output characteristics and (b) output conductance of a 4 $\mu m$ / 20 $\mu m$ (narrow               |

| and long) NMOS at 25 °C                                                                                            |

| Fig. 5.17. Transfer characteristics of a 20 $\mu$ m / 2 $\mu$ m NMOS at 25 $^{0}$ C in strong inversion; |

|----------------------------------------------------------------------------------------------------------|

| (a) at 0.5 V and (b) 15V drain-to-source voltage.                                                        |

| Fig. 5.18. Transfer characteristics of a 20 $\mu$ m / 2 $\mu$ m NMOS at 25 $^{0}$ C in subthreshold; (a) |

| at 0.5 V and (b) 15V drain-to-source voltage.                                                            |

| Fig. 5.19. Transconductance of a 20 $\mu m$ / 2 $\mu m$ NMOS at 25 $^{0}C;$ (a) at 0.5 V and (b) 15V     |

| drain-to-source voltage. 124                                                                             |

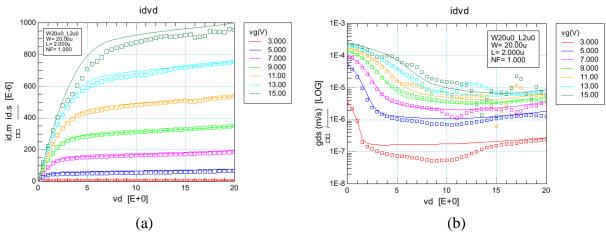

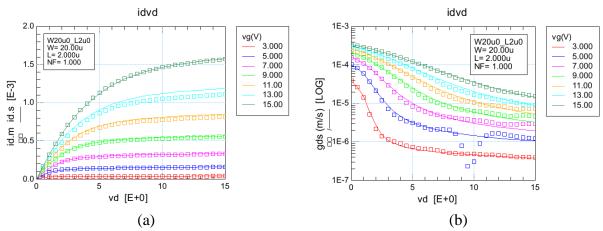

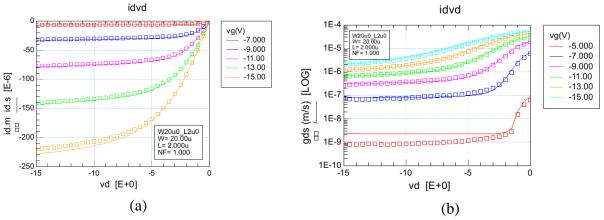

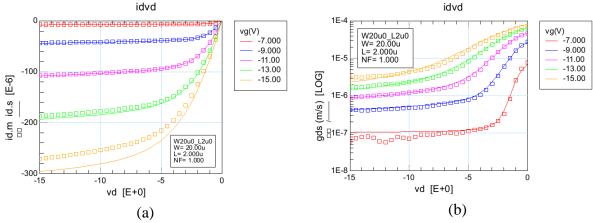

| Fig. 5.20. (a) Output characteristics and (b) output conductance of a 20 $\mu m$ / 2 $\mu m$ NMOS        |

| at 25 °C                                                                                                 |

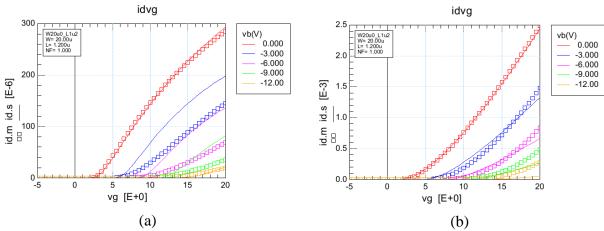

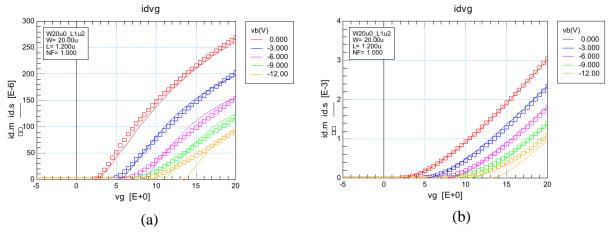

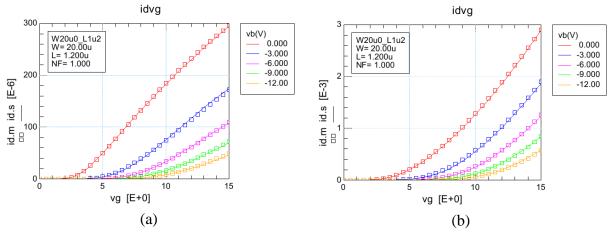

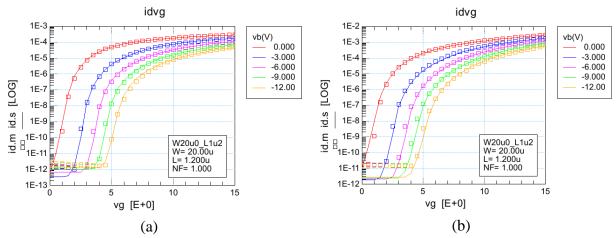

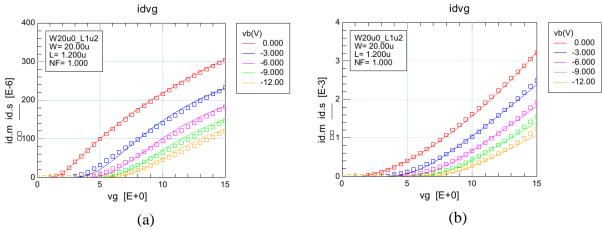

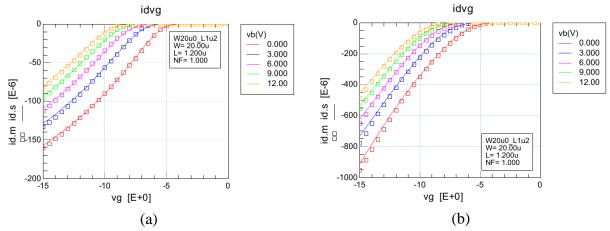

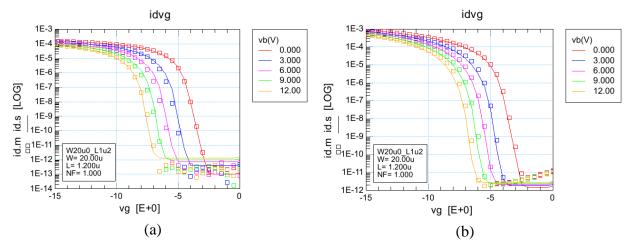

| Fig. 5.21. Transfer characteristics of a 20 $\mu m$ / 1.2 $\mu m$ (wide and short) NMOS at 25 $^{0}C$ in |

| strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                       |

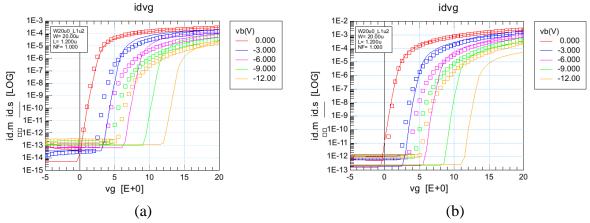

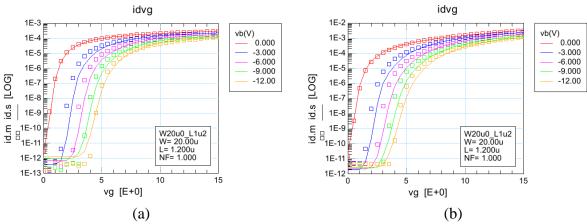

| Fig. 5.22. Transfer characteristics of a 20 $\mu m$ / 1.2 $\mu m$ (wide and short) NMOS at 25 $^{0}C$ in |

| subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                           |

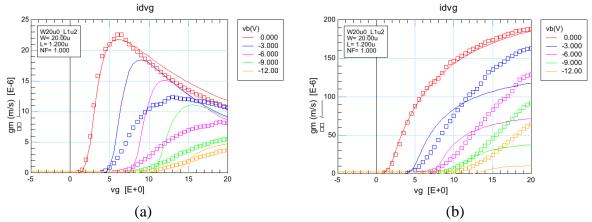

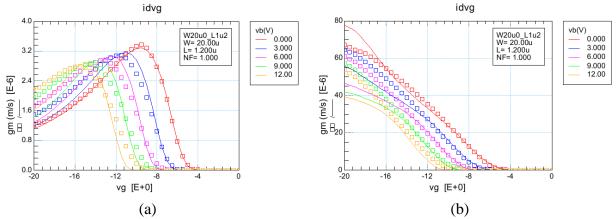

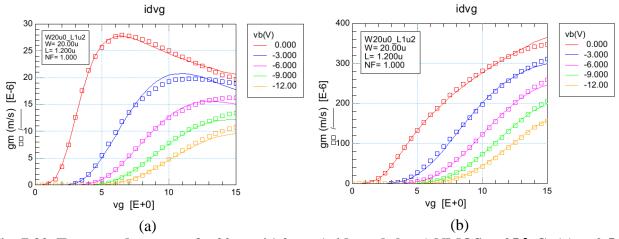

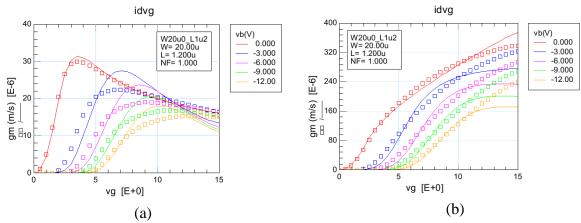

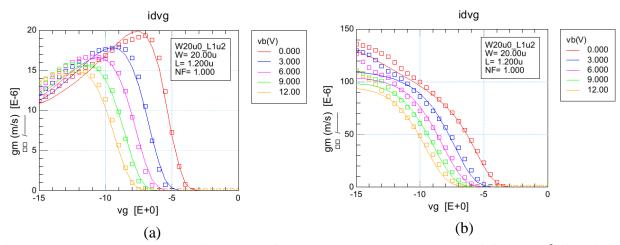

| Fig. 5.23. Transconductance of a 20 $\mu m$ / 1.2 $\mu m$ (wide and short) NMOS at 25 $^{0}C;$ (a) at    |

| 0.5 V and (b) 15V drain-to-source voltage.                                                               |

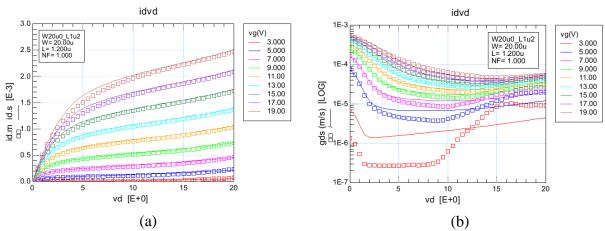

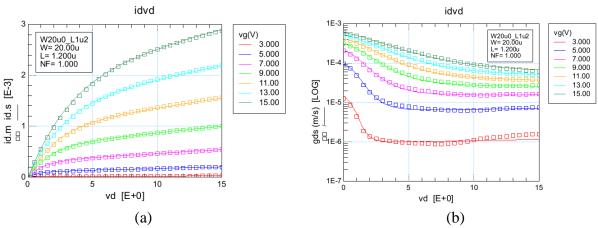

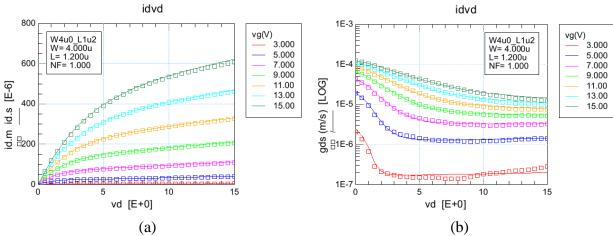

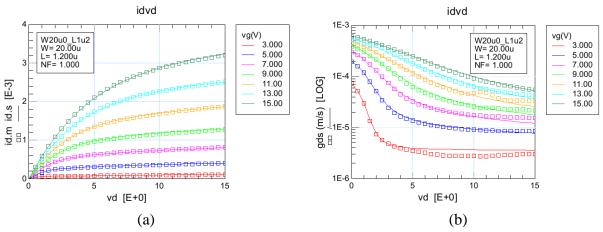

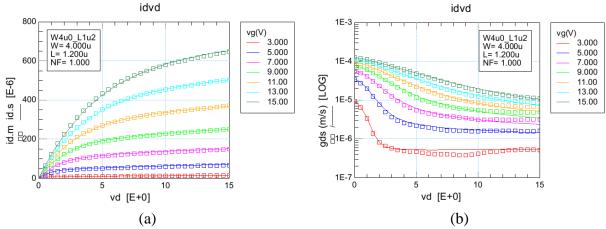

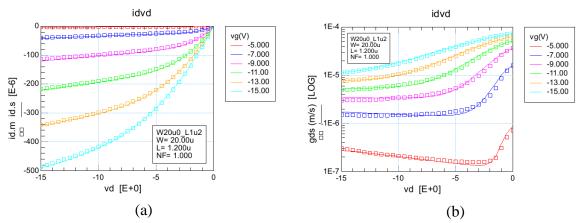

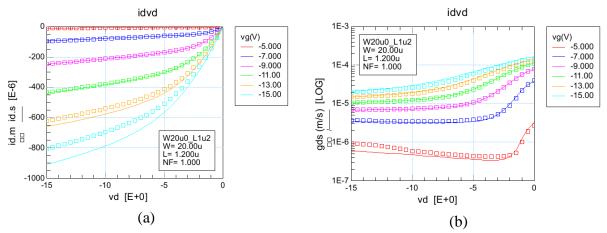

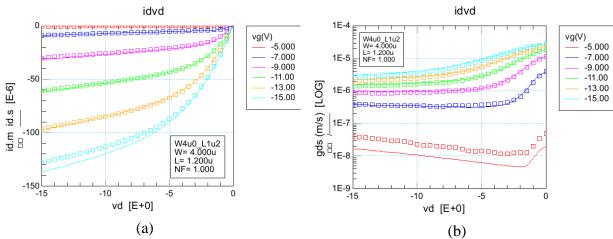

| Fig. 5.24. (a) Output characteristics and (b) output conductance of a 20 $\mu m$ / 1.2 $\mu m$ (wide     |

| and short) NMOS at 25 °C                                                                                 |

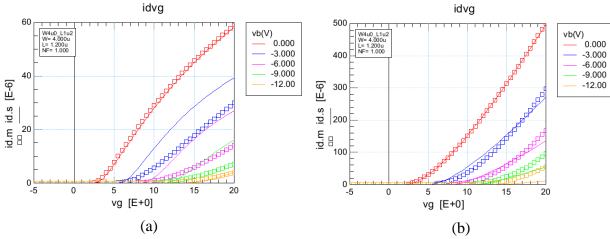

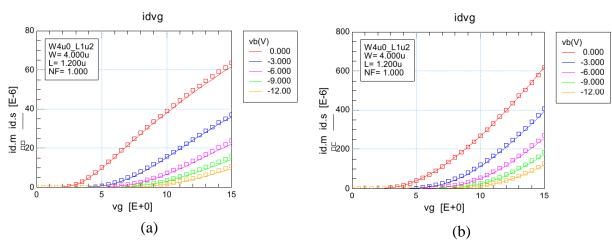

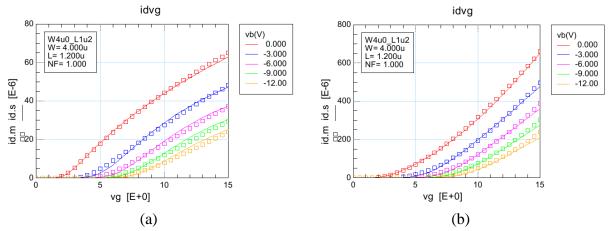

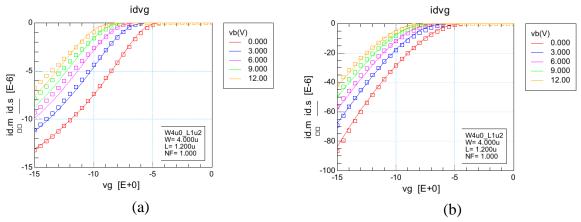

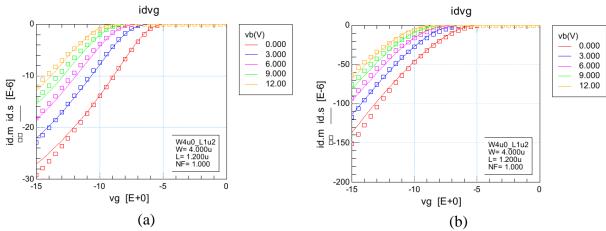

| Fig. 5.25. Transfer characteristics of a 4 $\mu m$ / 1.2 $\mu m$ (narrow and short) NMOS at 25 $^{0}C$   |

| in strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                    |

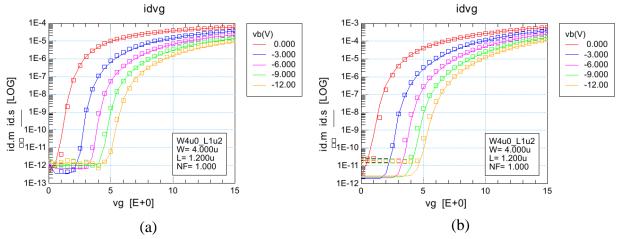

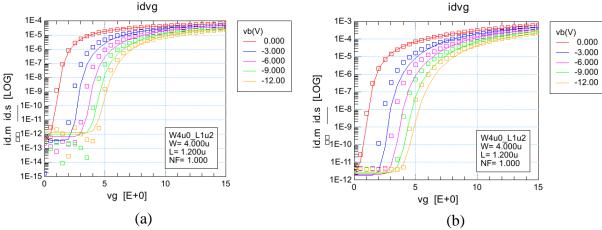

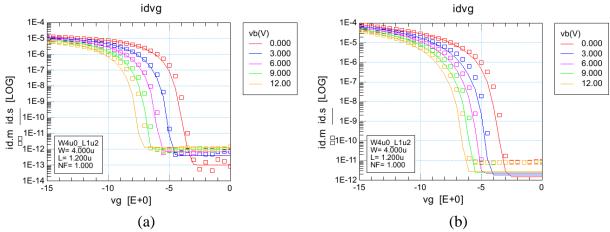

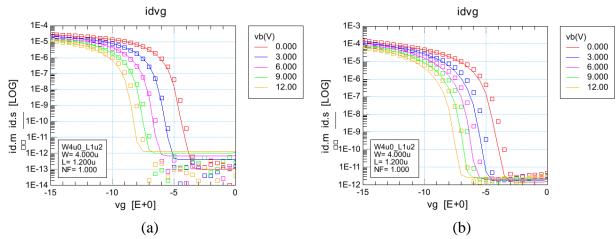

| Fig. 5.26. Transfer characteristics of a 4 $\mu m$ / 1.2 $\mu m$ (narrow and short) NMOS at 25 $^{0}C$   |

| in subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                        |

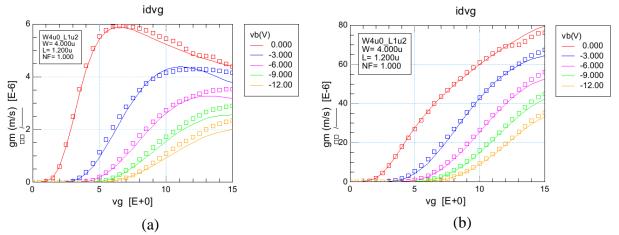

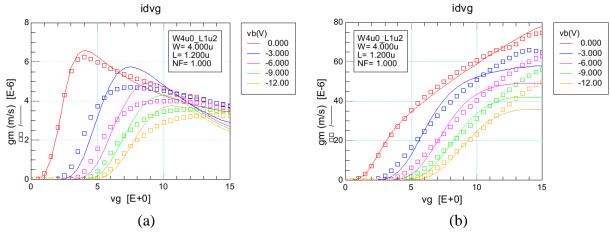

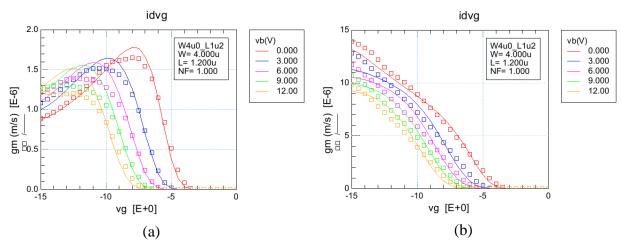

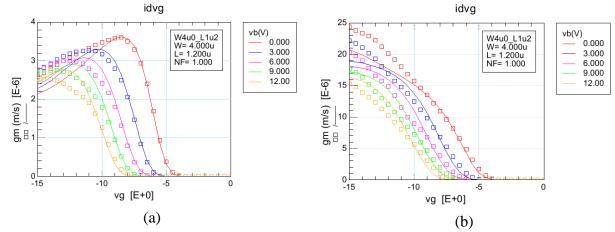

| Fig. 5.27. Transconductance of a 4 $\mu$ m / 1.2 $\mu$ m (narrow and short) NMOS at 25 $^{0}$ C; (a) at  |

| 0.5 V and (b) 15V drain-to-source voltage.                                                               |

|                                                                                                          |

| Fig. 5.28. (a) Output characteristics and (b) output conductance of a 4 $\mu$ m / 1.2 $\mu$ m (narrow     |

|-----------------------------------------------------------------------------------------------------------|

| and short) NMOS at 25 °C                                                                                  |

| Fig. 5.29. Transfer characteristics of a 20 $\mu m$ / 20 $\mu m$ (wide and long) NMOS at 300 $^{0}C$ in   |

| strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                        |

| Fig. 5.30. Transfer characteristics of a 20 $\mu m$ / 20 $\mu m$ (wide and long) NMOS at 300 $^{0}C$ in   |

| subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                            |

| Fig. 5.31. Transconductance of a 20 $\mu m$ / 20 $\mu m$ (wide and long) NMOS at 300 $^{0}C;$ (a) at      |

| 0.5 V and (b) 15V drain-to-source voltage.                                                                |

| Fig. 5.32. (a) Output characteristics and (b) output conductance of a 20 $\mu m$ / 20 $\mu m$ (wide       |

| and long) NMOS at 300 °C                                                                                  |

| Fig. 5.33. Transfer characteristics of a 20 $\mu m$ / 2 $\mu m$ NMOS at 300 $^{0}C$ in strong inversion;  |

| (a) at 0.5 V and (b) 15V drain-to-source voltage                                                          |

| Fig. 5.34. Transfer characteristics of a 20 $\mu$ m / 2 $\mu$ m NMOS at 300 $^{0}$ C in subthreshold; (a) |

| at 0.5 V and (b) 15V drain-to-source voltage.                                                             |

| Fig. 5.35. Transconductance of a 20 $\mu m$ / 2 $\mu m$ NMOS at 300 $^{0}C;$ (a) at 0.5 V and (b) 15V     |

| drain-to-source voltage                                                                                   |

| Fig. 5.36. (a) Output characteristics and (b) output conductance of a 20 $\mu m$ / 2 $\mu m$ NMOS         |

| at 300 °C                                                                                                 |

| Fig. 5.37. Transfer characteristics of a 20 $\mu$ m / 1.2 $\mu$ m (wide and short) NMOS at 300 $^{0}$ C   |

| in strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                     |

| Fig. 5.38. Transfer characteristics of a 20 $\mu$ m / 1.2 $\mu$ m (wide and short) NMOS at 300 $^{0}$ C   |

| in subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                         |

|                                                                                                           |

| Fig. 5.39. Transconductance of a 20 $\mu m$ / 1.2 $\mu m$ (wide and short) NMOS at 300 $^{0}C$ ; (a) at |

|---------------------------------------------------------------------------------------------------------|

| 0.5 V and (b) 15V drain-to-source voltage.                                                              |

| Fig. 5.40. (a) Output characteristics and (b) output conductance of a 20 $\mu m$ / 1.2 $\mu m$ (wide    |

| and short) NMOS at 300 °C                                                                               |

| Fig. 5.41. Transfer characteristics of a 4 $\mu m$ / 1.2 $\mu m$ (narrow and short) NMOS at 300 $^{0}C$ |

| in strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                   |

| Fig. 5.42. Transfer characteristics of a 4 $\mu m$ / 1.2 $\mu m$ (narrow and short) NMOS at 300 $^{0}C$ |

| in subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                       |

| Fig. 5.43. Transconductance of a 4 $\mu m$ / 1.2 $\mu m$ (narrow and short) NMOS at 300 $^{0}C;$ (a)    |

| at 0.5 V and (b) 15V drain-to-source voltage.                                                           |

| Fig. 5.44. (a) Output characteristics and (b) output conductance of a 4 $\mu m/1.2\mu m$ (narrow        |

| and short) NMOS at 300 °C                                                                               |

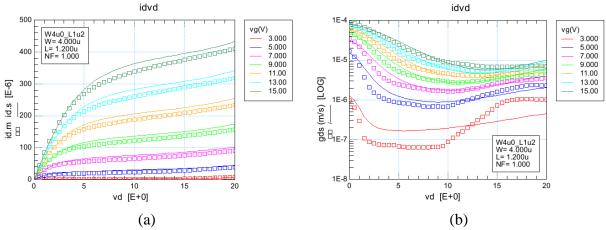

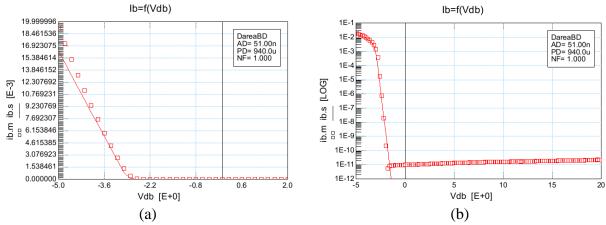

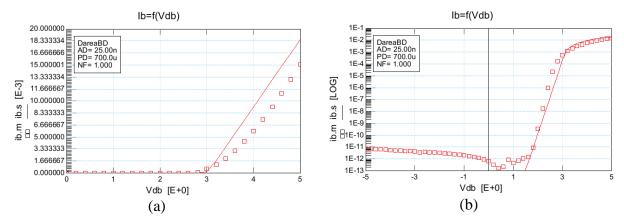

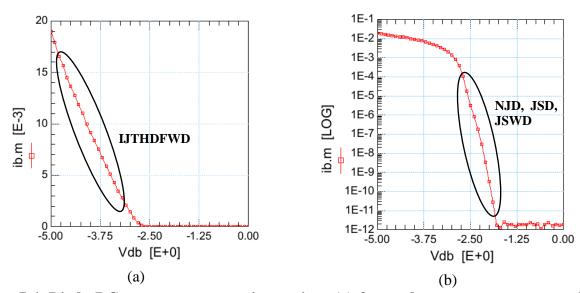

| Fig. 5.45. Drain/source (n+)-to-body (p-well) diode I – V characteristics in (a) linear scale           |

| and (b) log scale.                                                                                      |

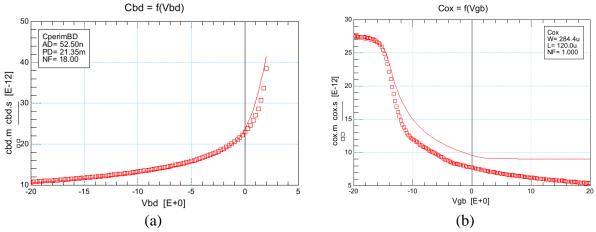

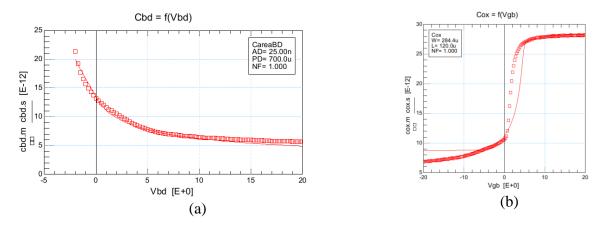

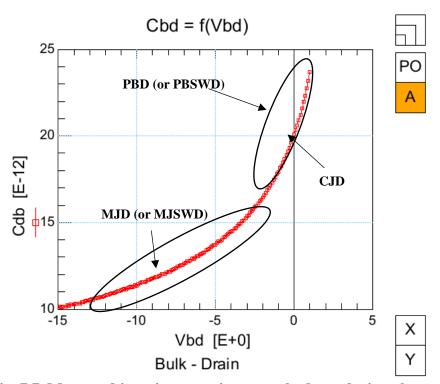

| Fig. 5.46. (a) Drain/source (n+)-to-body (p-well) junction diode C – V and (b) NMOS oxide               |

| capacitance                                                                                             |

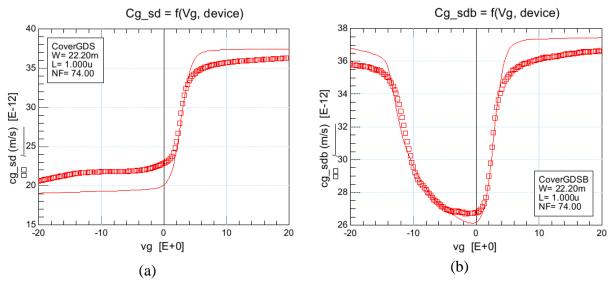

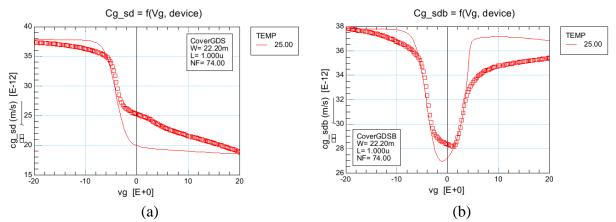

| Fig. 5.47. (a) Gate-to-drain/source overlap and intrinsic capacitance and (b) gate-to-                  |

| drain/source/body total capacitance of an NMOS                                                          |

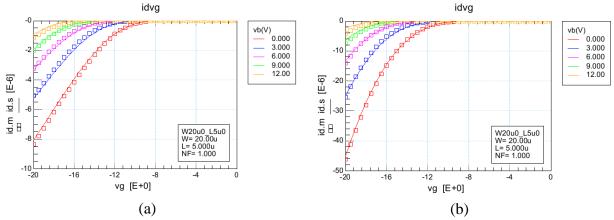

| Fig. 5.48. Transfer characteristics of a 20 $\mu m$ / 5 $\mu m$ (wide and long) PMOS at 25 $^{0}C$ in   |

| strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                      |

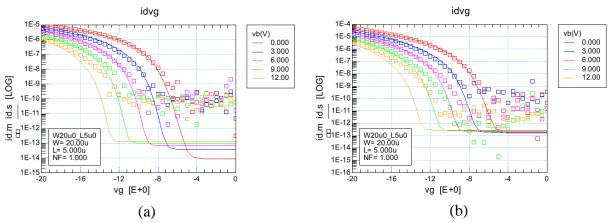

| Fig. 5.49. Transfer characteristics of a 20 $\mu m$ / 5 $\mu m$ (wide and long) PMOS at 25 $^{0}C$ in   |

| subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                          |

| Fig. 5.50. Transconductance of a 20 $\mu m$ / 5 $\mu m$ (wide and long) PMOS at 25 $^{0}C;$ (a) at 0.5      |

|-------------------------------------------------------------------------------------------------------------|

| V and (b) 15V drain-to-source voltage                                                                       |

| Fig. 5.51. (a) Output characteristics and (b) output conductance of a 20 $\mu m$ / 5 $\mu m$ (wide          |

| and long) PMOS at 25 °C.                                                                                    |

| Fig. 5.52. Transfer characteristics of a 20 $\mu m$ / 2 $\mu m$ PMOS at 25 $^{0}C$ in strong inversion;     |

| (a) at 0.5 V and (b) 15V drain-to-source voltage                                                            |

| Fig. 5.53. Transfer characteristics of a 20 $\mu m$ / 2 $\mu m$ PMOS at 25 $^{0}C$ in subthreshold; (a)     |

| at 0.5 V and (b) 15V drain-to-source voltage.                                                               |

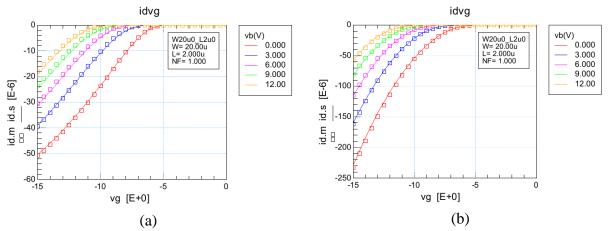

| Fig. 5.54. Transconductance of a 20 $\mu m$ / 2 $\mu m$ PMOS at 25 $^{0}C;$ (a) at 0.5 V and (b) 15V        |

| drain-to-source voltage                                                                                     |

| Fig. 5.55. a) Output characteristics and (b) output conductance of a 20 $\mu m$ / 2 $\mu m$ PMOS            |

| at 25 °C                                                                                                    |

| Fig. 5.56. Transfer characteristics of a 4 $\mu$ m / 2 $\mu$ m PMOS at 25 $^{0}$ C in strong inversion; (a) |

| at 0.5 V and (b) 15V drain-to-source voltage.                                                               |

| Fig. 5.57. Transfer characteristics of a 4 $\mu$ m / 2 $\mu$ m PMOS at 25 $^{0}$ C in subthreshold; (a) at  |

| 0.5 V and (b) 15V drain-to-source voltage.                                                                  |

| Fig. 5.58. Transconductance of a 4 $\mu m$ / 2 $\mu m$ PMOS at 25 $^{0}C;$ (a) at 0.5 V and (b) 15V         |

| drain-to-source voltage                                                                                     |

| Fig. 5.59. a) Output characteristics and (b) output conductance of a 4 $\mu m$ / 2 $\mu m$ PMOS at          |

| 25 °C                                                                                                       |

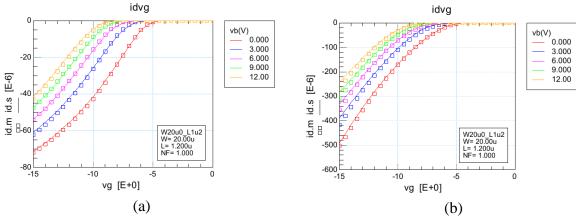

| Fig. 5.60. Transfer characteristics of a 20 $\mu m$ / 1.2 $\mu m$ (wide and short) PMOS at 25 $^{0}C$ in    |

| strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                          |

|                                                                                                             |

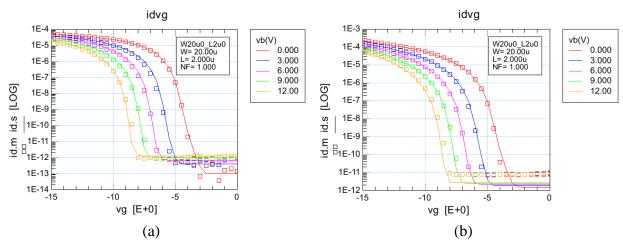

| Fig. 5.61. Transfer characteristics of a 20 $\mu m$ / 1.2 $\mu m$ (wide and short) PMOS at 25 $^{0}C$ in |

|----------------------------------------------------------------------------------------------------------|

| subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                           |

| Fig. 5.62. Transconductance of a 20 $\mu m$ / 1.2 $\mu m$ (wide and short) PMOS at 25 $^{0}C;$ (a) at    |

| 0.5 V and (b) 15V drain-to-source voltage.                                                               |

| Fig. 5.63. a) Output characteristics and (b) output conductance of a 20 $\mu m/1.2~\mu m$ (wide          |

| and short) PMOS at 25 °C                                                                                 |

| Fig. 5.64. Transfer characteristics of a 4 $\mu m$ / 1.2 $\mu m$ (narrow and short) PMOS at 25 $^{0}C$   |

| in strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                    |

| Fig. 5.65. Transfer characteristics of a 4 $\mu m$ / 1.2 $\mu m$ (narrow and short) PMOS at 25 $^{0}C$   |

| in subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                        |

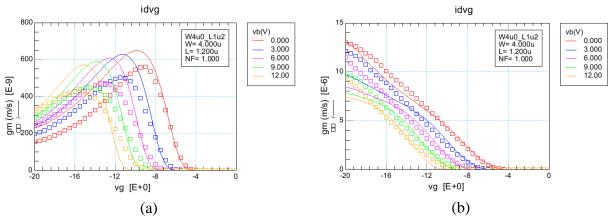

| Fig. 5.66. Transconductance of a 4 $\mu$ m / 1.2 $\mu$ m (narrow and short) PMOS at 25 $^{0}$ C; (a) at  |

| 0.5 V and (b) 15V drain-to-source voltage.                                                               |

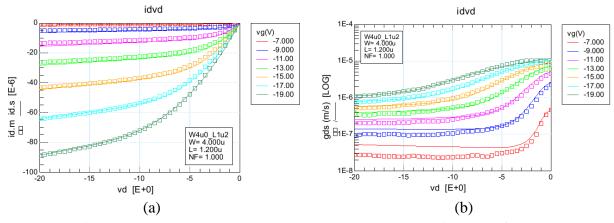

| Fig. 5.67. a) Output characteristics and (b) output conductance of a 4 $\mu m$ / 1.2 $\mu m$ (narrow     |

| and short) PMOS at 25 °C                                                                                 |

| Fig. 5.68. Transfer characteristics of a 20 $\mu m$ / 5 $\mu m$ (wide and long) PMOS at 300 $^{0}C$ in   |

| strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                       |

| Fig. 5.69. Transfer characteristics of a 20 $\mu m$ / 5 $\mu m$ (wide and long) PMOS at 300 $^{0}C$ in   |

| subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                           |

| Fig. 5.70. Transconductance of a 20 $\mu m$ / 5 $\mu m$ (wide and long) PMOS at 300 $^{0}$ C; (a) at     |

| 0.5 V and (b) 15V drain-to-source voltage                                                                |

|                                                                                                          |

| Fig. 5.71. a) Output characteristics and (b) output conductance of a 20 $\mu$ m / 5 $\mu$ m (wide        |

| Figure 5.72. Transfer characteristics of a 20 $\mu$ m / 2 $\mu$ m PMOS at 300 $^{0}$ C in strong inversion; |

|-------------------------------------------------------------------------------------------------------------|

| (a) at 0.5 V and (b) 15V drain-to-source voltage                                                            |

| Fig. 5.73. Transfer characteristics of a 20 $\mu m$ / 2 $\mu m$ PMOS at 300 $^{0}C$ in subthreshold; (a)    |

| at 0.5 V and (b) 15V drain-to-source voltage                                                                |

| Fig. 5.74. Transconductance of a 20 $\mu m$ / 2 $\mu m$ PMOS at 300 $^{0}C;$ (a) at 0.5 V and (b) 15V       |

| drain-to-source voltage                                                                                     |

| Fig. 5.75. a) Output characteristics and (b) output conductance of a 20 $\mu m$ / 2 $\mu m$ PMOS            |

| at 300 °C                                                                                                   |

| Fig. 5.76. Transfer characteristics of a 4 $\mu m$ / 2 $\mu m$ PMOS at 300 $^{0}C$ in strong inversion;     |

| (a) at 0.5 V and (b) 15V drain-to-source voltage                                                            |

| Fig. 5.77. Transfer characteristics of a 4 $\mu m$ / 2 $\mu m$ PMOS at 300 $^{0}C$ in subthreshold; (a)     |

| at 0.5 V and (b) 15V drain-to-source voltage.                                                               |

| Fig. 5.78. Transconductance of a 4 $\mu m$ / 2 $\mu m$ PMOS at 300 $^{0}C;$ (a) at 0.5 V and (b) 15V        |

| drain-to-source voltage                                                                                     |

| Fig. 5.79. a) Output characteristics and (b) output conductance of a 4 $\mu m$ / 2 $\mu m$ PMOS at          |

| 300 °C                                                                                                      |

| Fig. 5.80. Transfer characteristics of a 20 $\mu m$ / 1.2 $\mu m$ (wide and short) PMOS at 300 $^{0}C$      |

| in strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                       |

| Fig. 5.81. Transfer characteristics of a 20 $\mu m$ / 1.2 $\mu m$ (wide and short) PMOS at 300 $^{0}C$      |

| in subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                           |

| Fig. 5.82. Transconductance of a 20 $\mu m$ / 1.2 $\mu m$ (wide and short) PMOS at 300 $^{0}C;$ (a) at      |

| 0.5 V and (b) 15V drain-to-source voltage.                                                                  |

| Fig. 5.83. a) Output characteristics and (b) output conductance of a 20 $\mu m$ / 1.2 $\mu m$ (wide     |

|---------------------------------------------------------------------------------------------------------|

| and short) PMOS at 300 °C                                                                               |

| Fig. 5.84. Transfer characteristics of a 4 $\mu m$ / 1.2 $\mu m$ (narrow and short) PMOS at 300 $^{0}C$ |

| in strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                   |

| Fig. 5.85. Transfer characteristics of a 4 $\mu m$ / 1.2 $\mu m$ (narrow and short) PMOS at 300 $^{0}C$ |

| in subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                       |

| Fig. 5.86. Transconductance of a 4 $\mu m$ / 1.2 $\mu m$ (narrow and short) PMOS at 300 $^{0}$ C; (a)   |

| at 0.5 V and (b) 15V drain-to-source voltage.                                                           |

| Fig. 5.87. a) Output characteristics and (b) output conductance of a 4 $\mu m/1.2\mu m$ (narrow         |

| and short) PMOS at 300 °C                                                                               |

| Fig. 5.88. Drain/source (p+)-to-body (n-well) diode I – V characteristics in (a) linear scale           |

| and (b) log scale                                                                                       |

| Fig. 5.89. a) Drain/source (p+)-to-body (n-well) junction diode C – V and (b) PMOS oxide                |

| capacitance                                                                                             |

| Fig. 5.90. (a) Gate-to-drain/source overlap and intrinsic capacitance and (b) gate-to-                  |

| drain/source/body total capacitance of a PMOS                                                           |

| Fig. 6.1. Illustration of near interface trap sites in an n-type SiC MOS structure [132]. 151           |

| Fig. 6.2. Energy band diagram including the distribution of interface states of a MOS cap               |

| drawn along perpendicular direction of the oxide-semiconductor interface; (a) in accumulation, (b)      |

| in depletion, (c) in inversion and (d) the smeared C - V curve in presence of interface trapped         |

| charge [140]                                                                                            |

| Fig. 6.3. Mobility of SiC MOSFETs for different channel lengths at 25 °C. Width is 20                   |

| μm                                                                                                      |

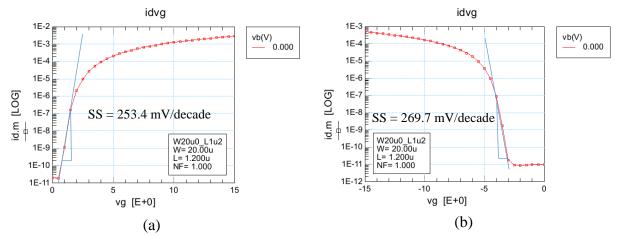

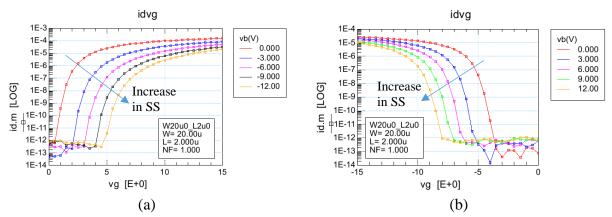

| Fig. 6.4. Subthreshold slope of SiC MOSFET; (a) NMOS and (b) PMOS 157                                 |

|-------------------------------------------------------------------------------------------------------|

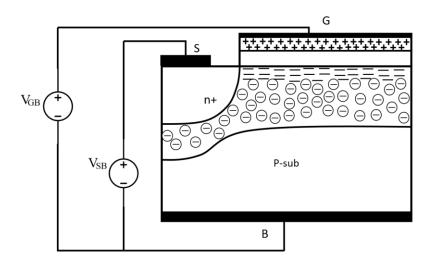

| Fig. 6.5. Illustration of body effect when the gate and the source terminals are biased with          |

| respect to the body terminal in a hypothetical three terminal MOS structure                           |

| Fig. 6.6. Illustration of body effect when the gate and the body terminals are biased with            |

| respect to the source terminal in a hypothetical three terminal MOS structure                         |

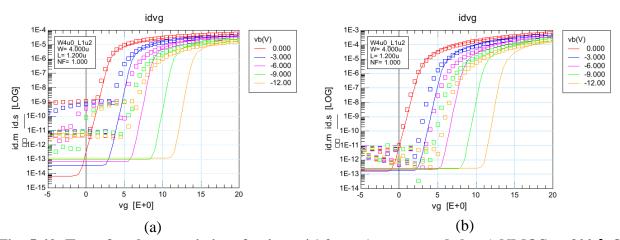

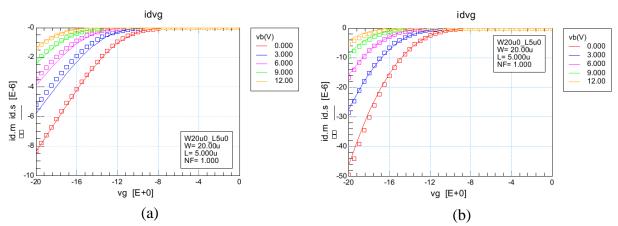

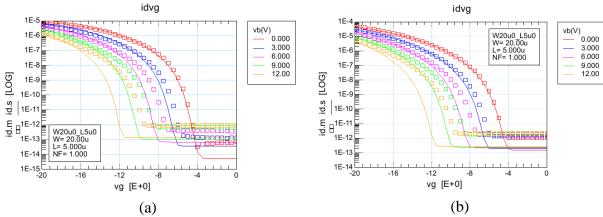

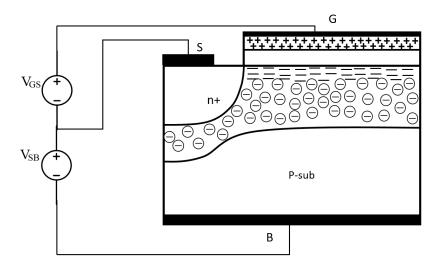

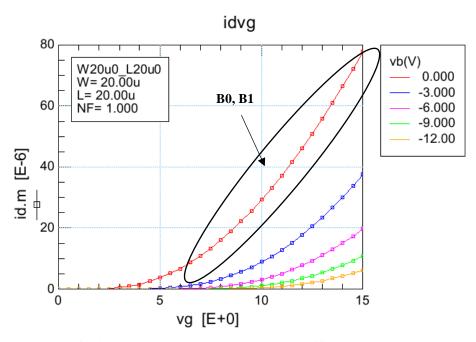

| Fig. 6.7. Transfer charteristics in strong inversion of SiC (a) NMOS and (b) PMOS 161                 |

| Fig. 6.8. Transfer charteristics in subthreshold of SiC (a) NMOS and (b) PMOS 161                     |

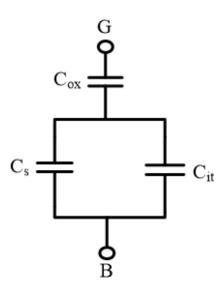

| Fig. 6.9. Equivalent circuit representation of the gate capacitance of a MOSFET device in             |

| presence of interface trapped charge                                                                  |

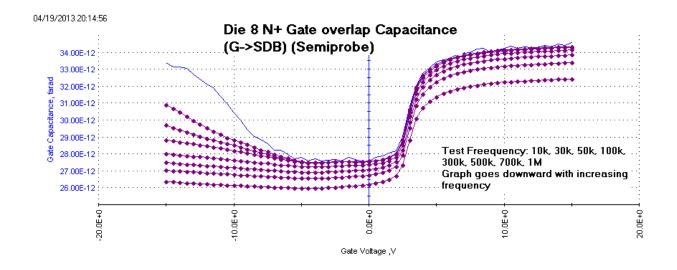

| Fig. 6.10. Measured gate-to-drain/source/body (total gate capacitance) of SiC NMOS at                 |

| different frequencies                                                                                 |

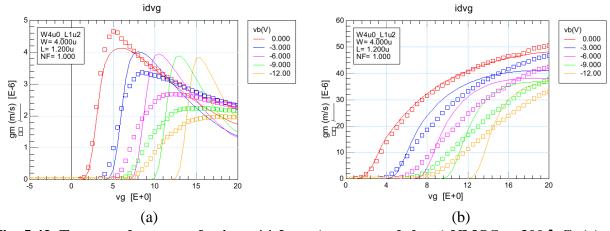

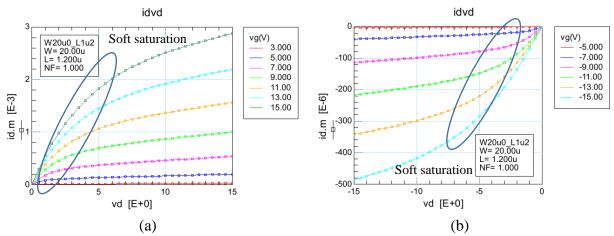

| Fig. 6.11. Illustration of soft saturation in SiC (a) NMOS and (b) PMOS 164                           |

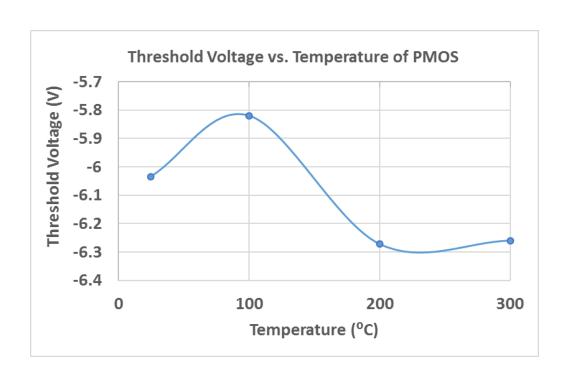

| Fig. 6.12. The threshold voltage of a 20 µm/2µm SiC PMOS over temperature showing                     |

| aging issues                                                                                          |

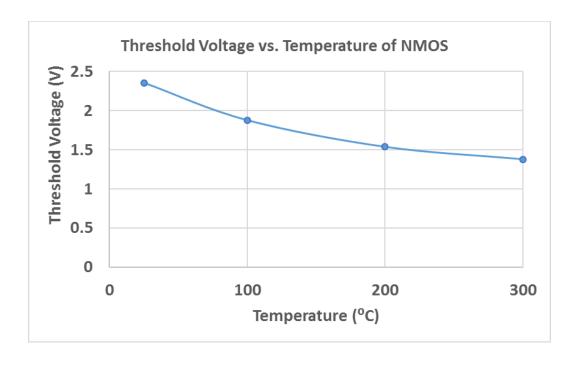

| Fig. 6.13. The threshold voltage of a 20µm/2µm SiC NMOS over temperature 166                          |

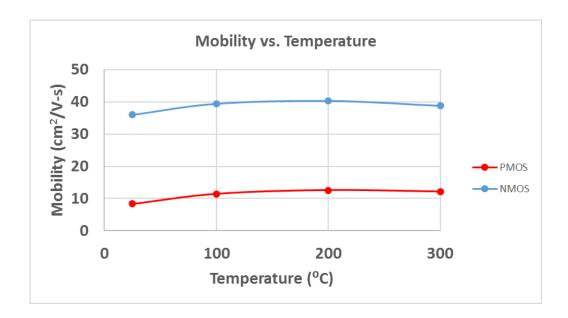

| Fig. 6.14. Mobility of 20 μm/2μm SiC NMOS and PMOS over temperature                                   |

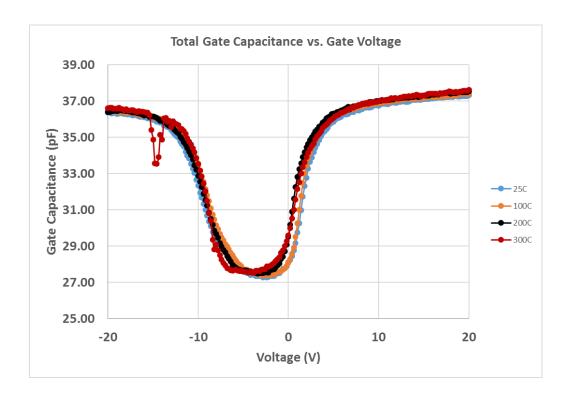

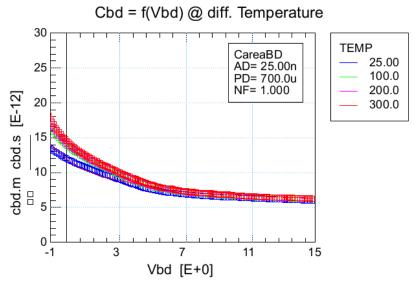

| Fig. 6.15. The measured total gate capacitance (C <sub>g-dsb</sub> ) of an NMOS over temperature. 168 |

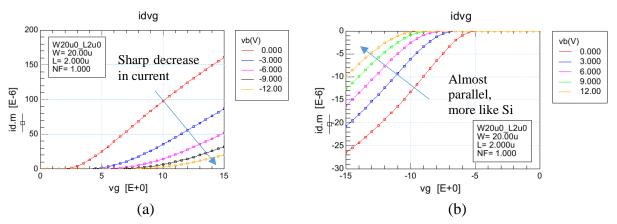

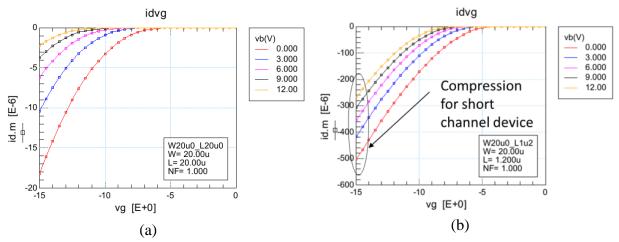

| Fig. 7.1. Transfer characteristics of SiC PMOS in saturation; (a) long channel and (b) short          |

| channel device                                                                                        |

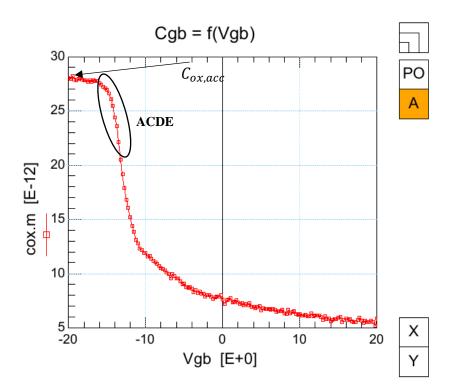

| Fig. 7.2. Measured oxide capacitance vs. gate-to-body voltage an NMOS cap                             |

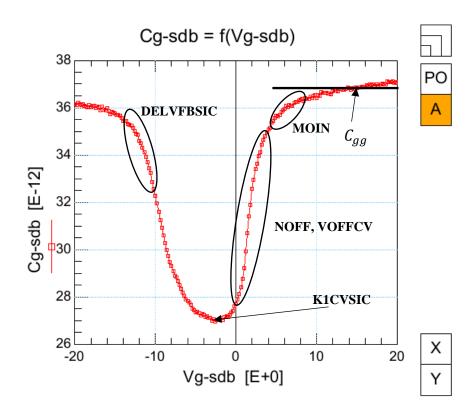

| Fig. 7.3. Measured total gate capacitance vs. gate-to-drain/source/body voltage 179                   |

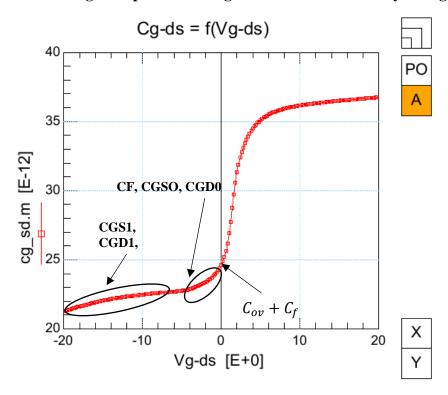

| Fig. 7.4. Measured gate-to-drain/source capacitance vs. gate-to-drain/source voltage of an            |

| n-type MOSFET                                                                                         |

|                                                                                                       |

| Fig. 7.5. The definitions of drawn, effective and overlap length dimension in a MOSFET                 |

|--------------------------------------------------------------------------------------------------------|

| device                                                                                                 |

| Fig. 7.6. Diode DC parameter extraction region; (a) forward current parameter and (b)                  |

| emission coefficient and reverse saturation current density parameter                                  |

| Fig. 7.7. Measured junction capacitance vs. body-to-drain voltage                                      |

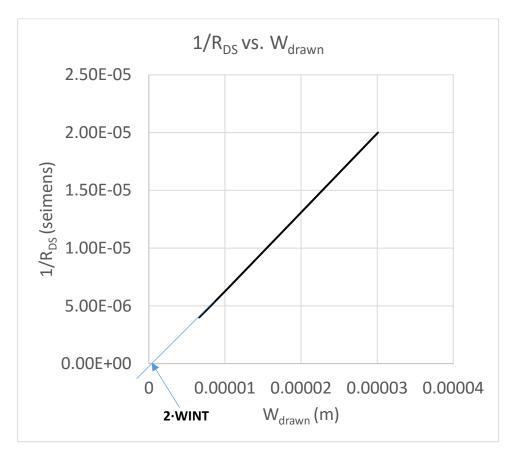

| Fig. 7.8. Inverse of the drain-to-source resistance vs. drawn channel width. The length of             |

| the devices should be long                                                                             |

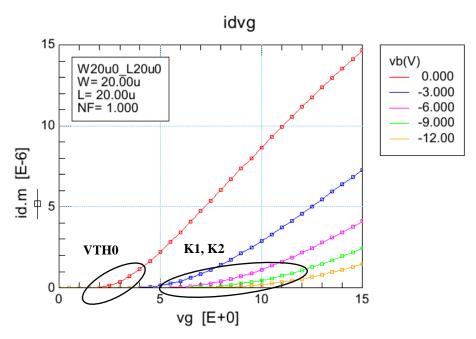

| Fig. 7.9. Bias independent threshold voltage parameter VTH0 and body effect parameters                 |

| K1 and K2 extraction. 188                                                                              |

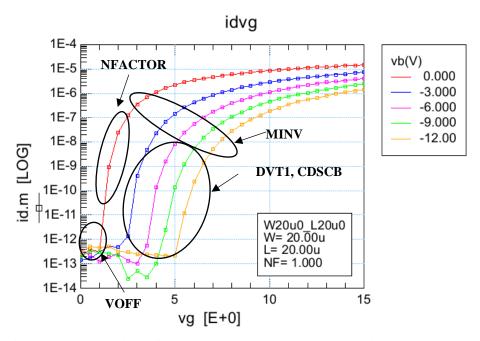

| Fig. 7.10. Extraction of the weak and moderate inversion parameters                                    |

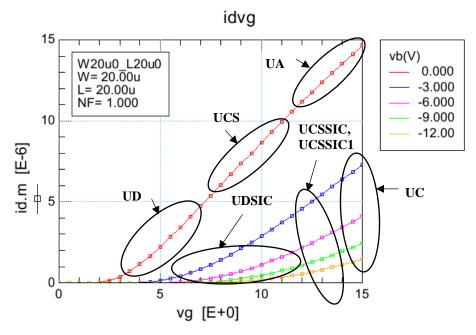

| Fig. 7.11. Extraction of the mobility parameters                                                       |

| Fig. 7.12. Extraction of the threshold shift parameters due to drain induced barrier                   |

| lowering                                                                                               |

| Fig. 7.13. Subthreshold slope adjustment in $I_d$ – $V_g$ curve in saturation                          |

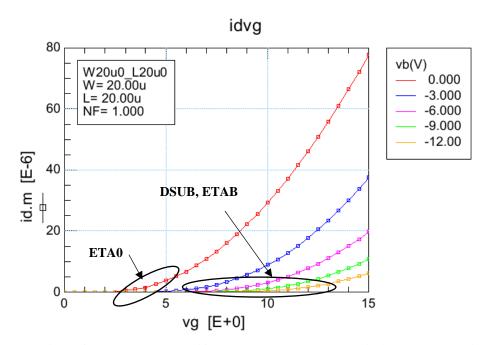

| Fig. 7.14.Extraction of the bulk charge coefficient parameters and $R_{DS}$ related parameters.        |

|                                                                                                        |

| Fig. 7.15. Optimization regions for output conductance related parameters                              |

| Fig. 7.16. Extraction of the narrow width related threshold voltage shift parameters 194               |

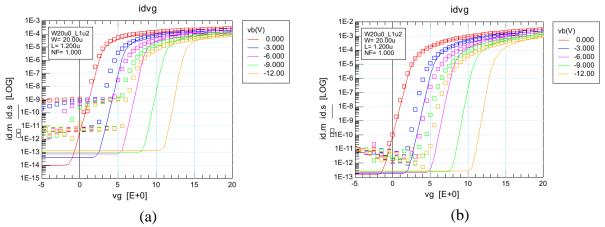

| Fig. 7.17. Extraction of width dependent bulk charge coefficient parameters                            |

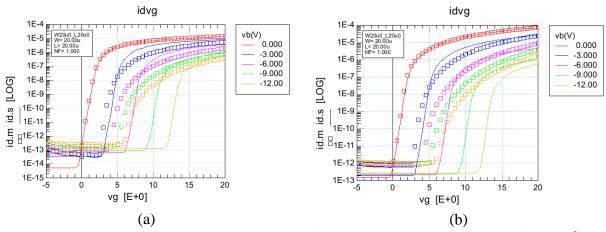

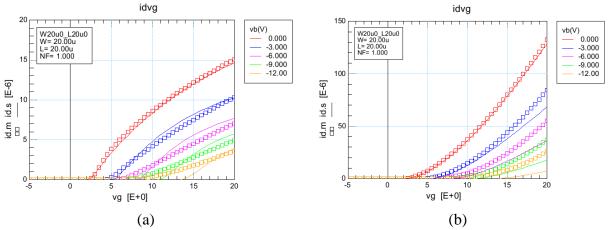

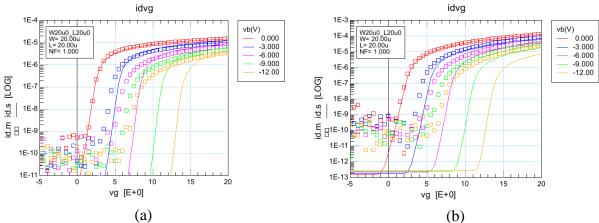

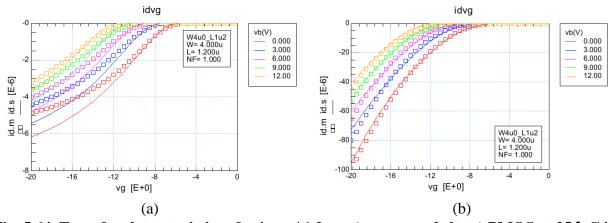

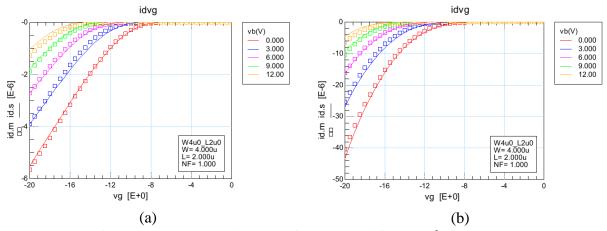

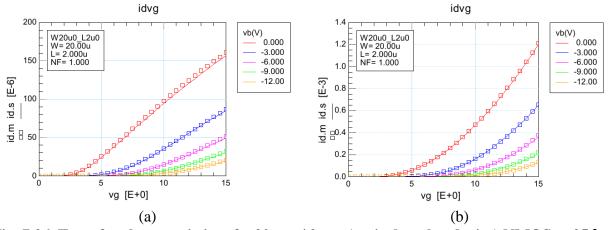

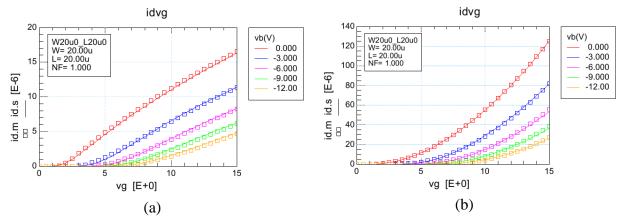

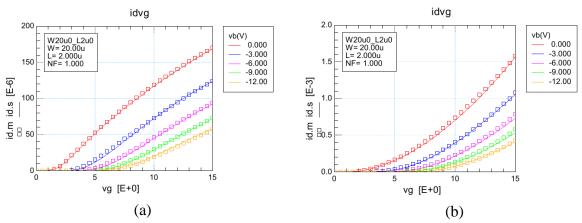

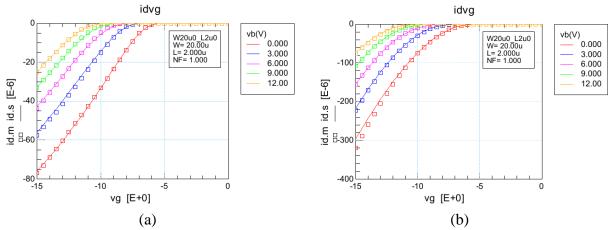

| Fig. 7.18. Transfer characteristics of a 20 $\mu m$ / 20 $\mu m$ (wide and long) NMOS at 25 $^{0}C$ in |

| strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                     |

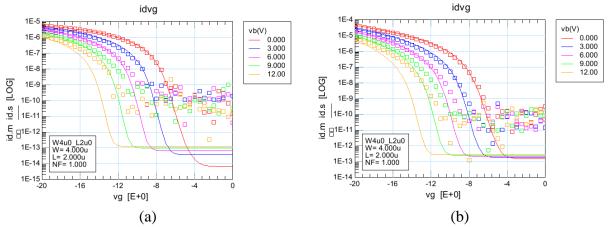

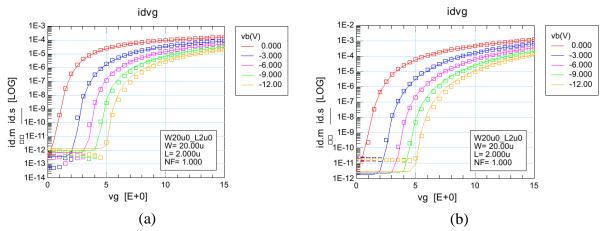

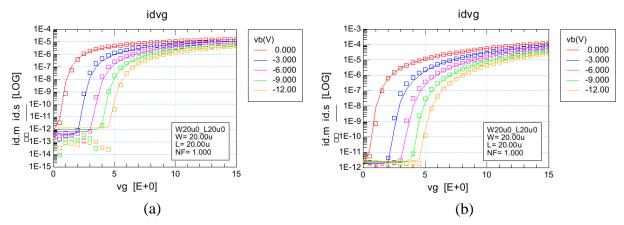

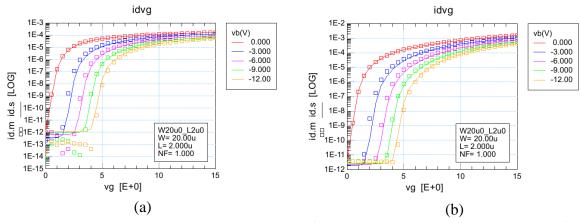

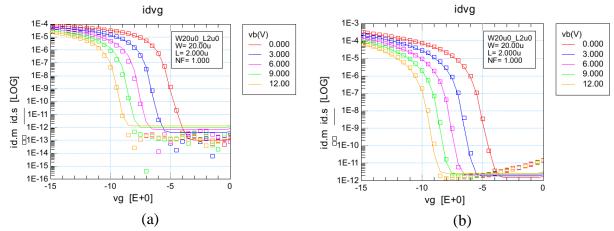

| Fig. 7.19. Transfer characteristics of a 20 $\mu m$ / 20 $\mu m$ (wide and long) NMOS at 25 $^{0}C$ in |

| subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                         |

|                                                                                                        |

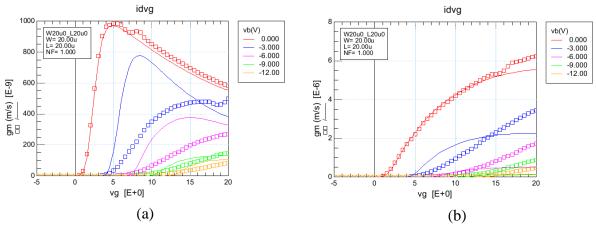

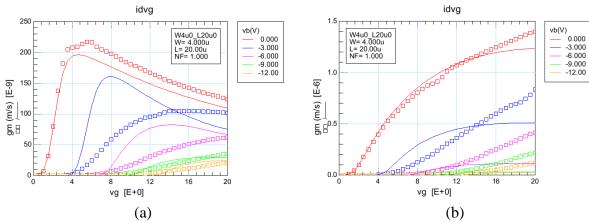

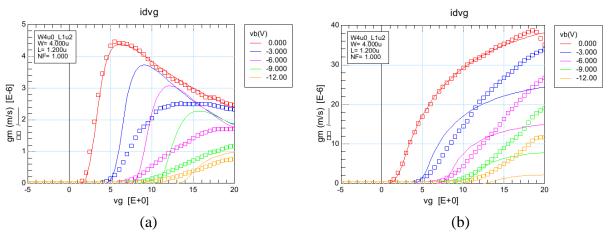

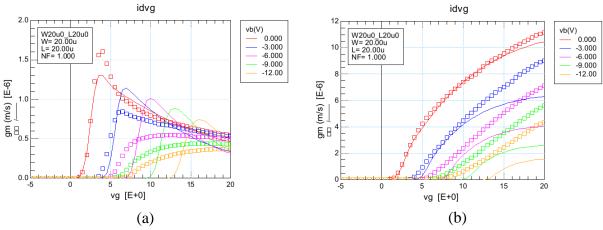

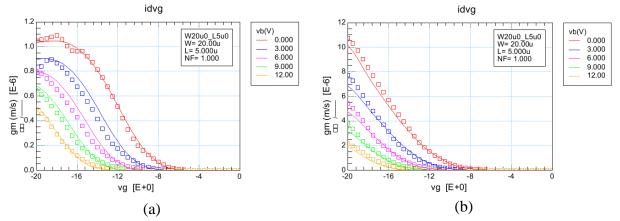

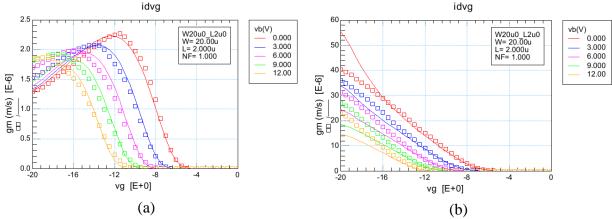

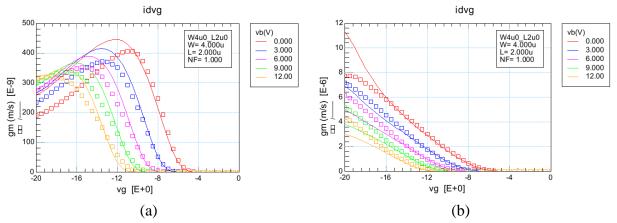

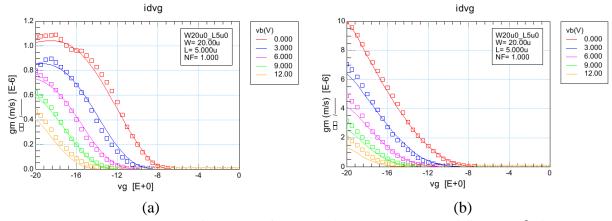

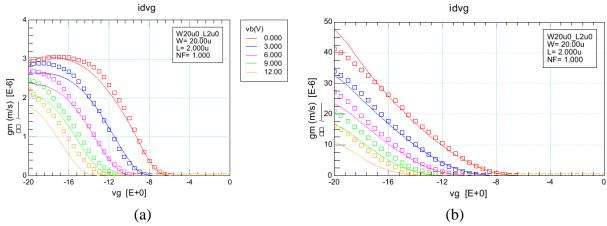

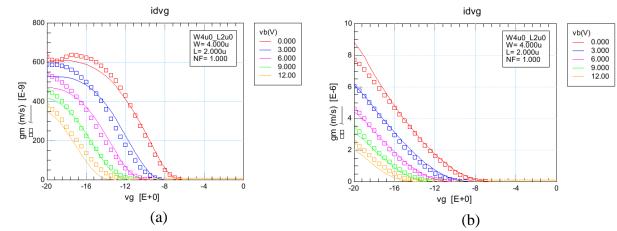

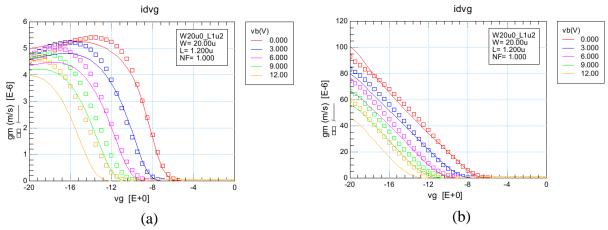

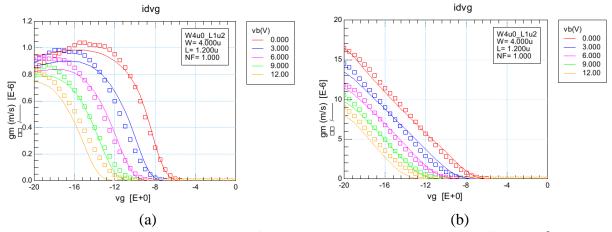

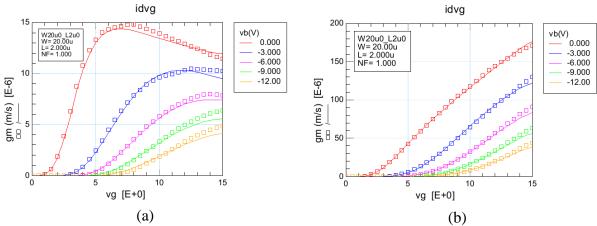

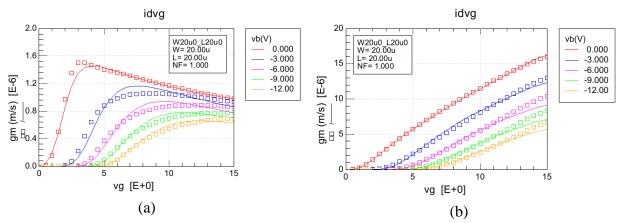

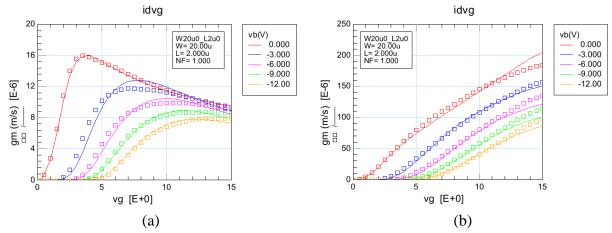

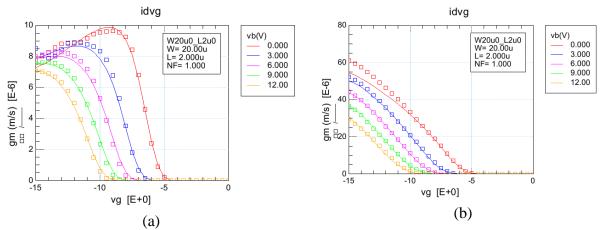

| Fig. 7.20. Transconductance of a 20 $\mu m$ / 20 $\mu m$ (wide and long) NMOS at 25 $^{0}C$ ; (a) at     |

|----------------------------------------------------------------------------------------------------------|

| 0.5 V and (b) 15V drain-to-source voltage.                                                               |

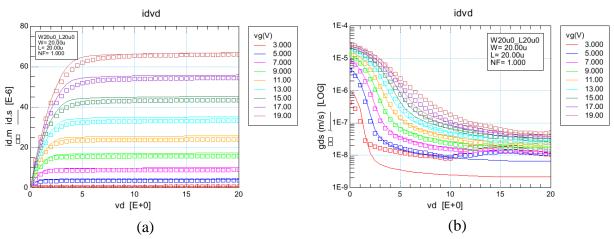

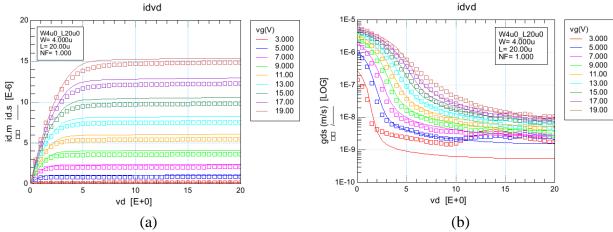

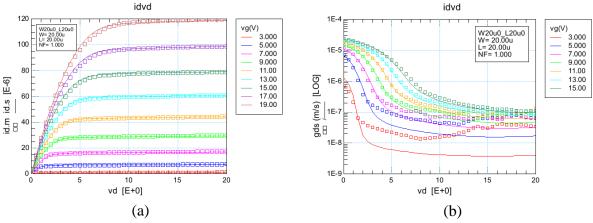

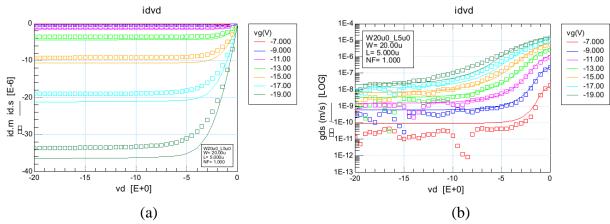

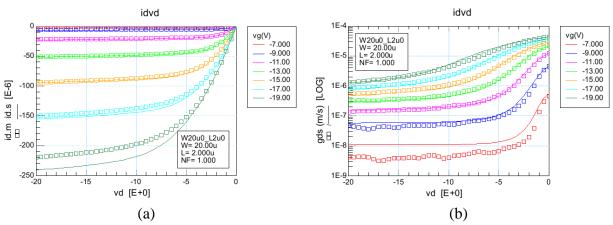

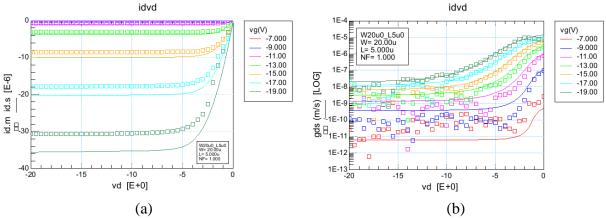

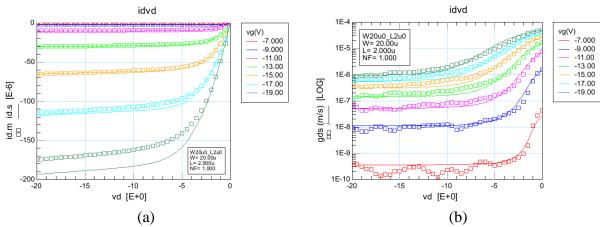

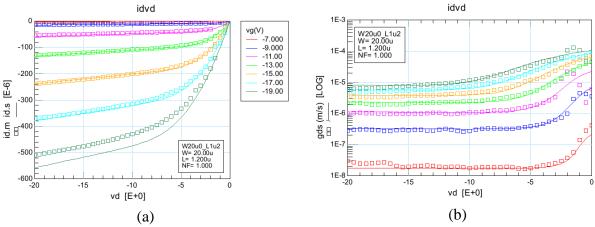

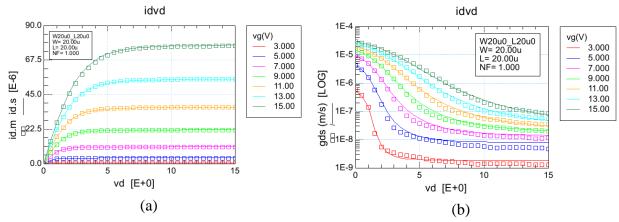

| Fig. 7.21. (a) Output characteristics and (b) output conductance of a 20 $\mu m$ / 20 $\mu m$ (wide      |

| and long) NMOS at 25 °C                                                                                  |

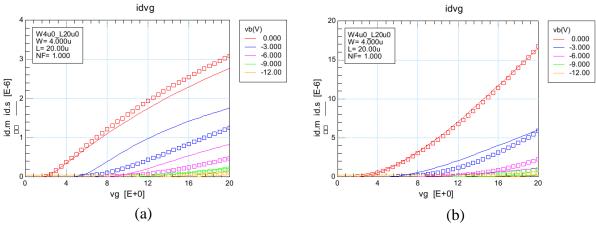

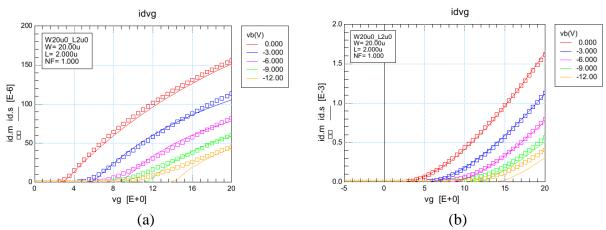

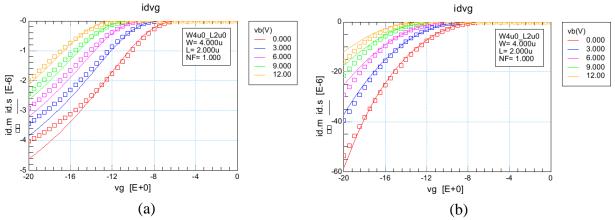

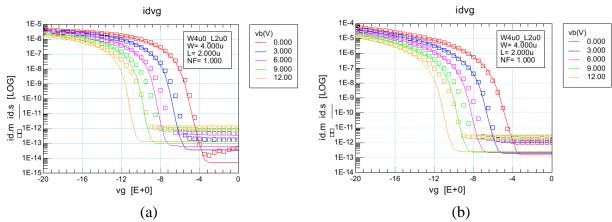

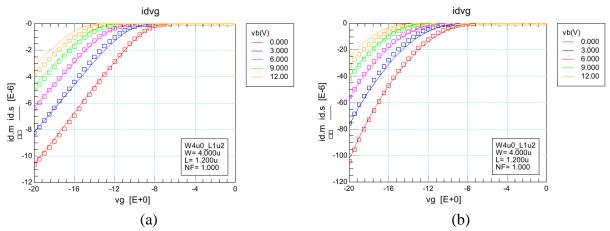

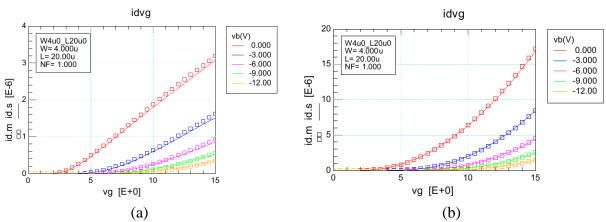

| Fig. 7.22. Transfer characteristics of a 4 $\mu$ m / 20 $\mu$ m (narrow and long) NMOS at 25 $^{0}$ C in |

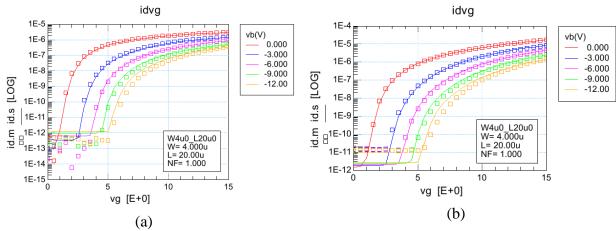

| strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                       |

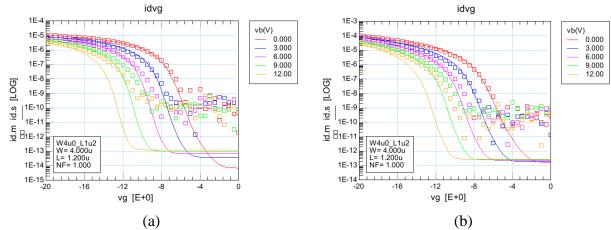

| Fig. 7.23. Transfer characteristics of a 4 $\mu$ m / 20 $\mu$ m (narrow and long) NMOS at 25 $^{0}$ C in |

| subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                           |

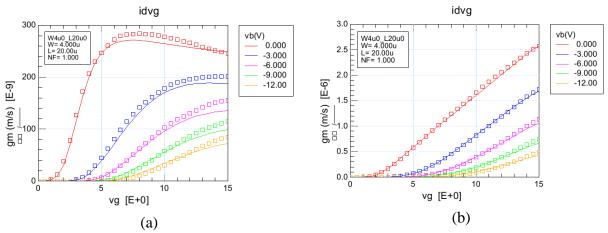

| Fig. 7.24. Transconductance of a 4 $\mu m$ / 20 $\mu m$ (narrow and long) NMOS at 25 $^{0}C;$ (a) at     |

| 0.5 V and (b) 15V drain-to-source voltage.                                                               |

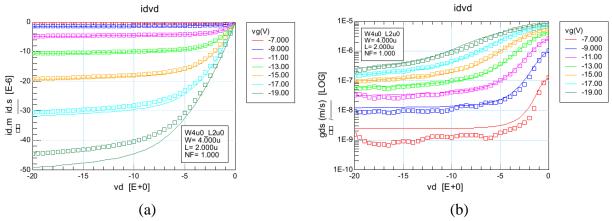

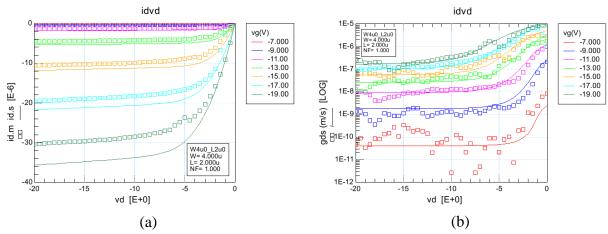

| Fig. 7.25. (a) Output characteristics and (b) output conductance of a 4 $\mu m$ / 20 $\mu m$ (narrow     |

| and long) NMOS at 25 °C                                                                                  |

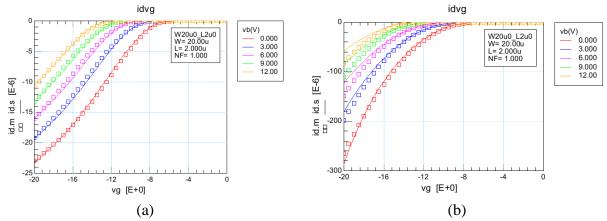

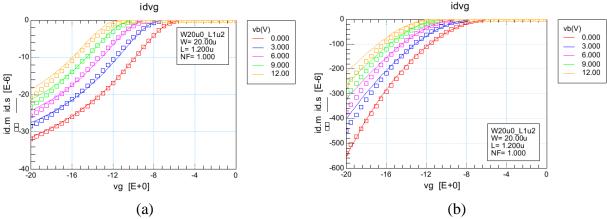

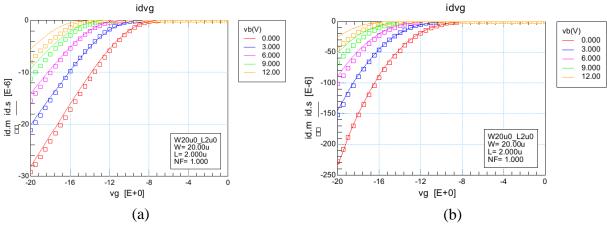

| Fig. 7.26. Transfer characteristics of a 20 $\mu m$ / 2 $\mu m$ (typical analog device) NMOS at 25       |

| <sup>0</sup> C in strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                     |

| Fig. 7.27. Transfer characteristics of a 20 $\mu m$ / 2 $\mu m$ (typical analog device) NMOS at 25       |

| <sup>0</sup> C in subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                         |

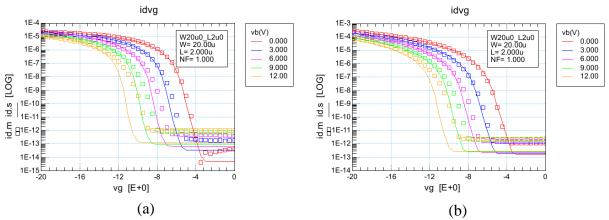

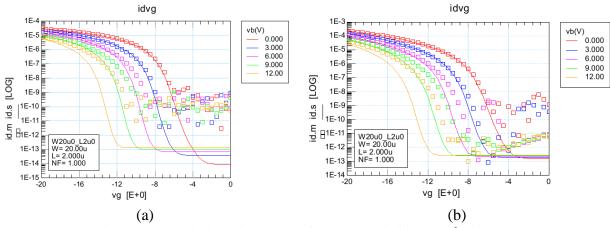

| Fig. 7.28. Transconductance of a 20 $\mu$ m / 2 $\mu$ m (typical analog device) NMOS at 25 $^{0}$ C      |

| (a) at 0.5 V and (b) 15V drain-to-source voltage                                                         |

| Fig. 7.29. (a) Output characteristics and (b) output conductance of a 20 $\mu m$ / 2 $\mu m$ (typical    |

| analog device) NMOS at 25 °C                                                                             |

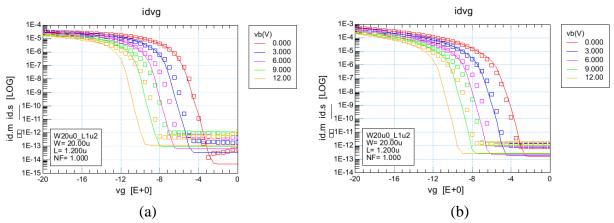

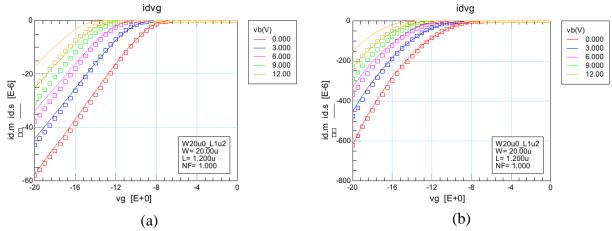

| Fig. 7.30. Transfer characteristics of a 20 $\mu m \times 1.2~\mu m$ (wide and short) NMOS at 25 $^{0}C$ |

| in strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                    |

|                                                                                                          |

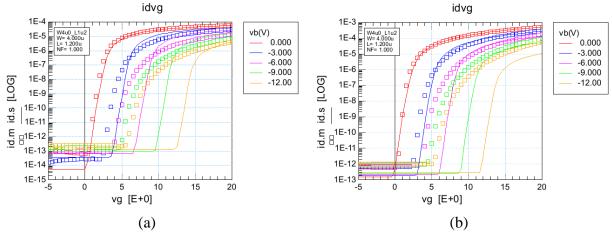

| Fig. 7.31. Transfer characteristics of a 20 $\mu m \times 1.2~\mu m$ (wide and short) NMOS at 25 $^{0}C$ |

|----------------------------------------------------------------------------------------------------------|

| in subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                        |

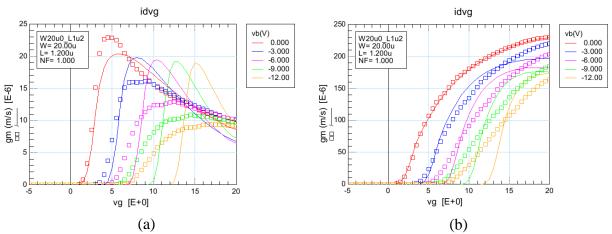

| Fig. 7.32. Transconductance of a 20 $\mu m$ / 1.2 $\mu m$ (wide and short) NMOS at 25 $^{0}C;$ (a) at    |

| 0.5 V and (b) 15V drain-to-source voltage.                                                               |

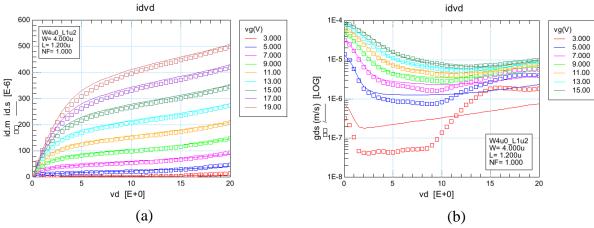

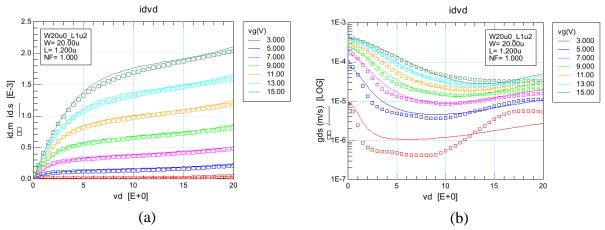

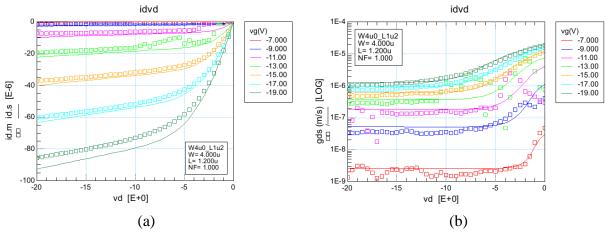

| Fig. 7.33. (a) Output characteristics and (b) output conductance of a 20 $\mu m$ / 1.2 $\mu m$ (wide     |

| and short) NMOS at 25 °C                                                                                 |

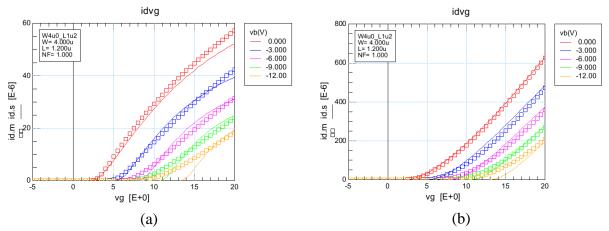

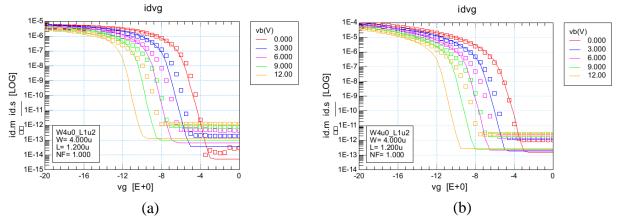

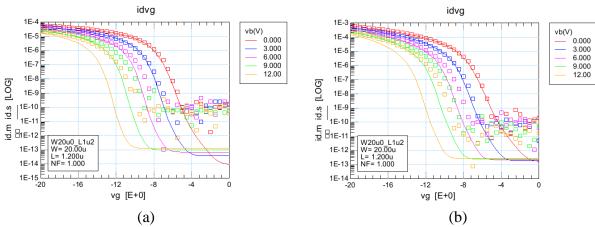

| Fig. 7.34. Transfer characteristics of a 4 $\mu m$ / 1.2 $\mu m$ (narrow and short) NMOS at 25 $^{0}C$   |

| in strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                    |

| Fig. 7.35. Transfer characteristics of a 4 $\mu m$ / 1.2 $\mu m$ (narrow and short) NMOS at 25 $^{0}C$   |

| in subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                        |

| Fig. 7.36. Transconductance of a 4 $\mu m$ / 1.2 $\mu m$ (narrow and short) NMOS at 25 $^{0}C$ ; (a) at  |

| 0.5 V and (b) 15V drain-to-source voltage. 206                                                           |

| Fig. 7.37. (a) Output characteristics and (b) output conductance of a 4 $\mu m  /  1.2  \mu m$ (narrow   |

| and short) NMOS at 25 °C                                                                                 |

| Fig. 7.38. Transfer characteristics of a 20 $\mu m$ / 20 $\mu m$ (wide and long) NMOS at 300 $^{0}C$ in  |

| strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                       |

| Fig. 7.39. Transfer characteristics of a 20 $\mu m$ / 20 $\mu m$ (wide and long) NMOS at 300 $^{0}C$ in  |

| subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                           |

| Fig. 7.40. Transconductance of a 20 $\mu m$ / 20 $\mu m$ (wide and long) NMOS at 300 $^{0}C$ ; (a) at    |

| 0.5 V and (b) 15V drain-to-source voltage                                                                |

| Fig. 7.41. (a) Output characteristics and (b) output conductance of a 20 $\mu m$ / 20 $\mu m$ (wide      |

|                                                                                                          |

| Fig. 7.42. Transfer characteristics of a 4 $\mu m$ / 20 $\mu m$ (narrow and long) NMOS at 300 $^{0}C$   |

|---------------------------------------------------------------------------------------------------------|

| in strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                   |

| Fig. 7.43. Transfer characteristics of a 4 $\mu m$ / 20 $\mu m$ (narrow and long) NMOS at 300 $^{0}C$   |

| in subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                       |

| Fig. 7.44. Transconductance of a 4 $\mu m$ / 20 $\mu m$ (narrow and long) NMOS at 300 $^{0}C$ ; (a) at  |

| 0.5 V and (b) 15V drain-to-source voltage                                                               |

| Fig. 7.45. (a) Output characteristics and (b) output conductance of a 4 $\mu m$ / 20 $\mu m$ (narrow    |

| and long) NMOS at 300 °C                                                                                |

| Fig. 7.46. Transfer characteristics of a 20 $\mu m$ / 2 $\mu m$ (typical analog device) NMOS at 300     |

| <sup>0</sup> C in strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                    |

| Fig. 7.47. Transfer characteristics of a 20 $\mu m$ / 2 $\mu m$ (typical analog device) NMOS at 300     |

| <sup>0</sup> C in subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                        |

| Fig. 7.48. Transconductance of a 20 $\mu$ m / 2 $\mu$ m (typical analog device) NMOS at 300 $^{0}$ C;   |

| (a) at 0.5 V and (b) 15V drain-to-source voltage                                                        |

| Fig. 7.49. (a) Output characteristics and (b) output conductance of a 20 $\mu m$ / 2 $\mu m$ (typical   |

| analog device) NMOS at 300 °C                                                                           |

| Fig. 7.50. Transfer characteristics of a 20 $\mu m$ / 1.2 $\mu m$ (wide and short) NMOS at 300 $^{0}C$  |

| in strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                   |

| Fig. 7.51. Transfer characteristics of a 20 $\mu m$ / 1.2 $\mu m$ (wide and short) NMOS at 300 $^{0}C$  |

| in subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                       |

| Fig. 7.52. Transconductance of a 20 $\mu$ m / 1.2 $\mu$ m (wide and short) NMOS at 300 $^{0}$ C; (a) at |

| 0.5 V and (b) 15V drain-to-source voltage                                                               |

| Fig. 7.53. (a) Output characteristics and (b) output conductance of a 20 $\mu m$ / 1.2 $\mu m$ (wide    |

|---------------------------------------------------------------------------------------------------------|

| and short) NMOS at 300 °C                                                                               |

| Fig. 7.54. Transfer characteristics of a 4 $\mu m$ / 1.2 $\mu m$ (narrow and short) NMOS at 300 $^{0}C$ |

| in strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                   |

| Fig. 7.55. Transfer characteristics of a 4 $\mu m$ / 1.2 $\mu m$ (narrow and short) NMOS at 300 $^{0}C$ |

| in subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                       |

| Fig. 7.56. Transconductance of a 4 $\mu m$ / 1.2 $\mu m$ (narrow and short) NMOS at 300 $^{0}$ C; (a)   |

| at 0.5 V and (b) 15V drain-to-source voltage.                                                           |

| Fig. 7.57. (a) Output characteristics and (b) output conductance of a 4 $\mu m  /  1.2  \mu m$ (narrow  |

| and short) NMOS at 300 °C                                                                               |

| Fig. 7.58. Transfer characteristics of a 20 $\mu m$ / 20 $\mu m$ (wide and long) PMOS at 25 $^{0}C$ in  |

| strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                      |

| Fig. 7.59. Transfer characteristics of a 20 $\mu m$ / 20 $\mu m$ (wide and long) PMOS at 25 $^{0}C$ in  |

| subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                          |

| Fig. 7.60. Transconductance of a 20 $\mu m$ / 20 $\mu m$ (wide and long) PMOS at 25 $^{0}C;$ (a) at     |

| 0.5 V and (b) 15V drain-to-source voltage. 214                                                          |

| Fig. 7.61. (a) Output characteristics and (b) output conductance of a 20 $\mu m$ / 20 $\mu m$ (wide     |

| and long) PMOS at 25 °C                                                                                 |

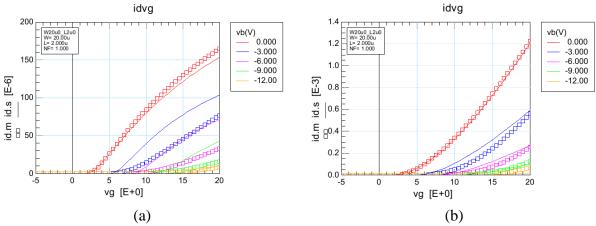

| Fig. 7.62. Transfer characteristics of a 4 $\mu m$ / 20 $\mu m$ (narrow and long) PMOS at 25 $^{0}C$ in |

| strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                      |

| Fig. 7.63. Transfer characteristics of a 4 $\mu m$ / 20 $\mu m$ (narrow and long) PMOS at 25 $^{0}C$ in |

| subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                          |

| Fig. 7.64. Transconductance of a 4 $\mu m$ / 20 $\mu m$ (narrow and long) PMOS at 25 $^{0}C$ ; (a) at    |

|----------------------------------------------------------------------------------------------------------|

| 0.5 V and (b) 15V drain-to-source voltage.                                                               |

| Fig. 7.65. (a) Output characteristics and (b) output conductance of a 4 $\mu m$ / 20 $\mu m$ (narrow     |

| and long) PMOS at 25 °C                                                                                  |

| Fig. 7.66. Transfer characteristics of a 20 $\mu m$ / 2 $\mu m$ (typical analog device) PMOS at 25       |

| <sup>0</sup> C in strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                     |

| Fig. 7.67. Transfer characteristics of a 20 $\mu m$ / 2 $\mu m$ (typical analog device) PMOS at 25       |

| <sup>0</sup> C in subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                         |

| Fig. 7.68. Transconductance of a 20 $\mu$ m / 2 $\mu$ m (typical analog device) PMOS at 25 $^{0}$ C; (a) |

| at 0.5 V and (b) 15V drain-to-source voltage.                                                            |

| Fig. 7.69. (a) Output characteristics and (b) output conductance of a 20 $\mu m$ / 2 $\mu m$ (typical    |

| analog device) PMOS at 25 °C. 217                                                                        |

| Fig. 7.70. Transfer characteristics of a 20 $\mu m$ / 1.2 $\mu m$ (wide and short) PMOS at 25 $^{0}C$ in |

| strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                       |

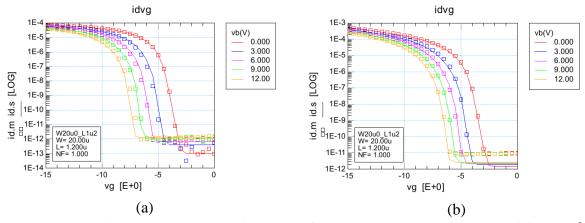

| Fig. 7.71. Transfer characteristics of a 20 $\mu m$ / 1.2 $\mu m$ (wide and short) PMOS at 25 $^{0}C$ in |

| subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                           |

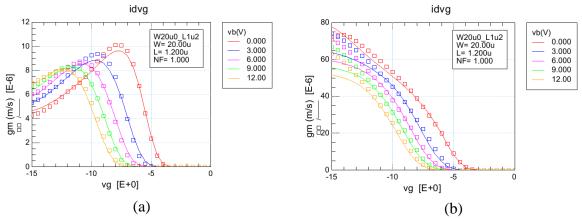

| Fig. 7.72. Transconductance of a 20 $\mu m$ / 1.2 $\mu m$ (wide and short) PMOS at 25 $^{0}C$ ; (a) at   |

| 0.5 V and (b) 15V drain-to-source voltage.                                                               |

| Fig. 7.73. (a) Output characteristics and (b) output conductance of a 20 $\mu m/1.2\mu m$ (wide          |

| and short) PMOS at 25 °C.                                                                                |

| Fig. 7.74. Transfer characteristics of a 4 $\mu m$ / 1.2 $\mu m$ (narrow and short) PMOS at 25 $^{0}C$   |

| in strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                    |

|                                                                                                          |

| Fig. 7.75. Transfer characteristics of a 4 $\mu m$ / 1.2 $\mu m$ (narrow and short) PMOS at 25 $^{0}C$  |

|---------------------------------------------------------------------------------------------------------|

| in subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                       |

| Fig. 7.76. Transconductance of a 4 $\mu$ m / 1.2 $\mu$ m (narrow and short) PMOS at 25 $^{0}$ C; (a) at |

| 0.5 V and (b) 15V drain-to-source voltage.                                                              |

| Fig. 7.77. (a) Output characteristics and (b) output conductance of a 4 $\mu m$ / 1.2 $\mu m$ (narrow   |

| and short) PMOS at 25 °C                                                                                |

| Fig. 7.78. Transfer characteristics of a 20 $\mu m$ / 20 $\mu m$ (wide and long) PMOS at 300 $^{0}C$ in |

| strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                      |

| Fig. 7.79. Transfer characteristics of a 20 $\mu m$ / 20 $\mu m$ (wide and long) PMOS at 300 $^{0}C$ in |

| subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                          |

| Fig. 7.80. Transconductance of a 20 $\mu m$ / 20 $\mu m$ (wide and long) PMOS at 300 $^{0}$ C; (a) at   |

| 0.5 V and (b) 15V drain-to-source voltage.                                                              |

| Fig. 7.81. (a) Output characteristics and (b) output conductance of a 20 $\mu m$ / 20 $\mu m$ (wide     |

| and long) PMOS at 300 °C                                                                                |

| Fig. 7.82. Transfer characteristics of a 4 $\mu m$ / 20 $\mu m$ (narrow and long) PMOS at 300 $^{0}C$   |

| in strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                   |

| Fig. 7.83. Transfer characteristics of a 4 $\mu m$ / 20 $\mu m$ (narrow and long) PMOS at 300 $^{0}C$   |

| in subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                       |

| Fig. 7.84. Transconductance of a 4 $\mu m$ / 20 $\mu m$ (narrow and long) PMOS at 300 $^{0}C;$ (a) at   |

| 0.5 V and (b) 15V drain-to-source voltage.                                                              |

| Fig. 7.85. (a) Output characteristics and (b) output conductance of a 4 $\mu m$ / 20 $\mu m$ (narrow    |

|                                                                                                         |

| Fig. 7.86. Transfer characteristics of a 20 $\mu$ m / 2 $\mu$ m (typical analog device) PMOS at 300      |

|----------------------------------------------------------------------------------------------------------|

| <sup>0</sup> C in strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                     |

| Fig. 7.87. Transfer characteristics of a 20 $\mu$ m / 2 $\mu$ m (typical analog device) PMOS at 300      |

| <sup>0</sup> C in subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                         |

| Fig. 7.88. Transconductance of a 20 $\mu m$ / 2 $\mu m$ (typical analog device) PMOS at 300 $^{0}$ C;    |

| (a) at 0.5 V and (b) 15V drain-to-source voltage                                                         |

| Fig. 7.89. (a) Output characteristics and (b) output conductance of a 20 $\mu m$ / 2 $\mu m$ (typical    |

| analog device) PMOS at 300 °C                                                                            |

| Fig. 7.90. Transfer characteristics of a 20 $\mu m$ / 1.2 $\mu m$ (wide and short) PMOS at 300 $^{0}C$   |

| in strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                    |

| Fig. 7.91. Transfer characteristics of a 20 $\mu m$ / 1.2 $\mu m$ (wide and short) PMOS at 300 $^{0}C$   |

| in subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                        |

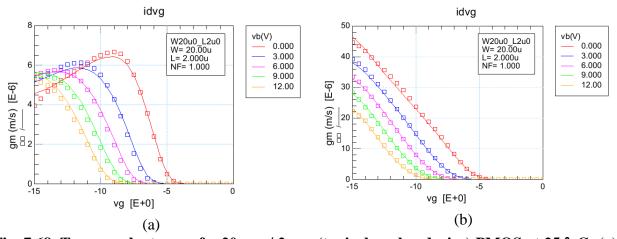

| Fig. 7.92. Transconductance of a 20 $\mu$ m / 1.2 $\mu$ m (wide and short) PMOS at 300 $^{0}$ C; (a) at  |

| 0.5 V and (b) 15V drain-to-source voltage.                                                               |

| Fig. 7.93. (a) Output characteristics and (b) output conductance of a 20 $\mu m$ / 1.2 $\mu m$ (wide     |

| and short) PMOS at 300 °C.                                                                               |

| Fig. 7.94. Transfer characteristics of a 4 $\mu m$ / 1.2 $\mu m$ (narrow and short) PMOS at 300 $^{0}$ C |

| in strong inversion; (a) at 0.5 V and (b) 15V drain-to-source voltage                                    |

| Fig. 7.95. Transfer characteristics of a 4 $\mu m$ / 1.2 $\mu m$ (narrow and short) PMOS at 300 $^{0}$ C |

| in subthreshold; (a) at 0.5 V and (b) 15V drain-to-source voltage                                        |

| Fig. 7.96. Transconductance of a 4 $\mu m$ / 1.2 $\mu m$ (narrow and short) PMOS at 300 $^{0}$ C; (a)    |

| at 0.5 V and (b) 15V drain-to-source voltage.                                                            |

|                                                                                                          |

| Fig. 7.97. (a) Output characteristics and (b) output conductance of a 4 $\mu$ m / 1.2 $\mu$ m (narrow                           |

|---------------------------------------------------------------------------------------------------------------------------------|

| and short) PMOS at 300 °C                                                                                                       |

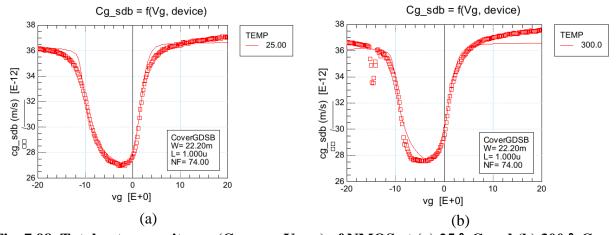

| Fig. 7.98. Total gate capacitance ( $C_{g\text{-dsb}}$ vs. $V_{g\text{-dsb}}$ ) of NMOS at (a) 25 $^{0}$ C and (b) 300 $^{0}$ C |

|                                                                                                                                 |

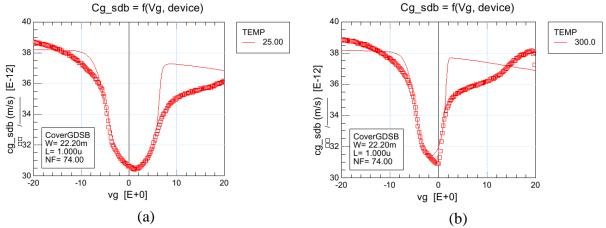

| Fig. 7.99. Total gate capacitance ( $C_{g-dsb}$ vs. $V_{g-dsb}$ ) of PMOS at (a) 25 $^{0}$ C and (b) 300 $^{0}$ C               |

|                                                                                                                                 |

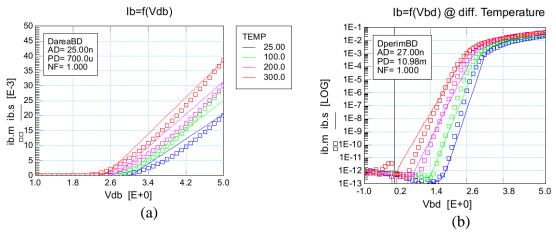

| Fig. 7.100. The DC current characteristics of P+/N-well diode in (a) linear scale and (b)                                       |

| log scale                                                                                                                       |

| Fig. 7.101. The junction capacitance of P+/N-well diode at different temperatures 227                                           |

|                                                                                                                                 |

## List of tables

| Table 2.1. Comparison of SiC Polytype Electronic Properties with Si, GaAs and GaN. Data    |

|--------------------------------------------------------------------------------------------|

| are compiled from the information found in [9], [17], [18], [19] and [20]                  |

| Table 2.2 Fitting parameter values of hole and electron impact ionization coefficients for |

| 4H-SiC [34]                                                                                |

| Table 2.3. Some pertinent process and device parameters of Raytheon HiTSiC SiC CMOS        |

| process                                                                                    |

| Table 4.1. Geometry information and corresponding pad location of NMOS devices 39          |

| Table 4.2. Geometry information and corresponding pad location of NMOS devices 40          |

| Table 4.3. Device dimensions and probe pad location of devices used for capacitance        |

| measurement                                                                                |

| Table 4.4. Parasitic diode test structure with device dimension and probe pad locations.45 |

| Table 4.5. Applied bias voltage ranges at NMOS terminals. The source terminal was          |

| connected to ground                                                                        |

| Table 4.6. Applied bias voltage range at PMOS terminals. The source terminal was           |

| connected to ground                                                                        |

| Table 4.7. Parameter values for optimum MOSFET C-V characterization                        |

| Table 5.1. Parameter extraction steps of SiC NMOS using HSPICE BSIM4.6.5 117               |

| Table 7.1. Model parameter extraction of overlap and fringing capacitances                 |

| Table 7.2. MOSFET models parameters used for temperature scaling                           |

| Table 7.3. Extraction sequence of the BSIM4SIC model for SiC NMOS and PMOS 195             |

| Table 7.4. Description of the length bins extracted for SiC NMOS and PMOS                  |

#### **CHAPTER 1 INTRODUCTION**

#### 1.1 Motivation

In recent times, the 4H poly-type of SiC has already been proven as a very useful wideband gap material for power semiconductor device fabrication. SiC power MOSFETs [1], Schottky diodes [2], Super Junction Bipolar Transistor (SJT) [3] are already being used in commercial applications such as motor drives [4], data centers [5], hybrid electrical vehicles [6] etc. Since SiC has a large band gap and higher critical electric field compared to Si [7], SiC power devices offer low on-resistance (10's of m $\Omega$ ) even with a large blocking voltage (several kilovolts) and smaller device capacitances which allows high frequency operation. This in turn reduces the size of passives in a power electronics system and significantly increases power density and efficiency. Besides, SiC devices can be operated at very high temperature (up to 400°C) [8] as it has superior thermal conductivity and very low intrinsic carrier concentration at room temperature. Also, being a radiation-hard material, SiC shows promise in harsh environment electronics application [9]. But, until recently, SiC power devices have been commercialized only for their capability for high power density and high efficiency. The use of SiC devices in harsh environment applications such as space exploration, oil and gas, avionics, automobile and geo-thermal is still in the research and development phase mainly due to a lack of reliable high temperature (more than 300°C) operation and a matured low voltage CMOS process. In order to utilize SiC devices to their full merit in analog and mixed signal domain for sensing, conditioning, instrumentation and power conversion applications, the following are necessary:

Reliable SiC power devices that can operate efficiently at more than 300°C.

Currently commercial SiC devices cannot operate beyond 175°C.

- Matured and reliable low voltage SiC CMOS process with high quality SiC-SiO<sub>2</sub> interface with a smooth surface at the interface.

- Well-developed Process Design Kit (PDK) with accurate and predictive models of NMOS, PMOS, diode, BJT, resistors, capacitors and parasitics.

- High temperature packaging solution both for die and module.

- High temperature passives and PCB.

Development of low voltage SiC process began in 90's but until recently the process was limited to NMOS. Wolfspeed (formerly known as Cree) launched a 2 μm NMOS process in 2010 [10]. General Electric also has a SiC NMOS process [8]. Raytheon UK announced the world first SiC CMOS process in 2012 [11]. At the University of Arkansas, integrated circuits using Raytheon high temperature 1.2 μm SiC CMOS process were designed as a part of National Science Foundation project called Building Innovation Capacity (BIC). But since the process is still maturing and in the research and development phase, Raytheon does not have accurate device models in the process design kit (PDK). This serves as the motivation of developing accurate models for SiC MOSFETs which are of paramount importance in designing sensitive analog, mixed-signal and power integrated circuits.

### 1.2 Research Objectives

The objective of this research is to develop a geometry and temperature scalable compact model of 4H-SiC MOSFETs for integrated circuit design and simulation. The characteristics of SiC MOSFETs are significantly different than their Si counterparts primarily due to the presence of trap sites in the SiC-SiO<sub>2</sub> interface. Also, the interface is not as smooth as the Si-SiO<sub>2</sub> one. Surface roughness and trapped charge in the interface alter the MOSFET characteristics by altering the flat band voltage, threshold voltage, mobility, subthreshold slope, body effect, thermal and

geometry behavior. Also, the presence of slow traps influence the small and large signal dynamics and the gate capacitance becomes frequency dependent in the accumulation region. This poses significant challenges not only in developing a compact model for SiC MOSFETs but also in characterizing their static and dynamic behavior. The purpose of this research is threefold – 1) accurate DC and CV characterization of SiC MOSFETs, 2) development of an accurate model for interface trap related device characteristics and global temperature and geometry scaling and 3) development of an easy parameter extraction and optimization routine for model card generation.

#### 1.3 Key Contributions

- Development of accurate DC and CV characterization methods at high temperature in the presence of non-ideal conditions i.e. probe station parasitics, cable leakage, cable inductance and capacitance, thermal current etc.

- Verilog-A version development of BSIM470 model.

- Modification of BSIM470 Verilog-A model for SiC MOSFETs.

- Comprehensive ICCAP module development for parameter extraction and optimization.

- Extraction of slow trap information from Id-Vg characteristics.

- Development of a body bias dependent mobility model in order to take into account the effect of interface trapped charge and surface roughness.

- Significant improvement in body effect modeling of SiC NMOS and PMOS.

- Modeling of the soft transition of SiC MOSFETs from the triode region to the saturation region.

- Inclusion of interface trapped charge effects on C-V characteristics.

- Development of a new parameter extraction routine for C-V characteristics optimization.

- New parameter extraction method development for model optimization of SiC MOSFETs.

- Global scaling of temperature and geometry behavior of SiC MOSFETs

#### 1.4 Dissertation Outline

The contents of this dissertation are divided into eight chapters and organized in the following manner:

- Chapter 2: SiC Technology The fundamental material properties of SiC are presented and current state of device fabrication technology on SiC wafer is reviewed.

- Chapter 3: SiC Compact Models for Circuit Design Definition of compact models

and their usefulness in circuit design are described. Compact models available for

different SiC devices are surveyed and their merits and demerits are discussed.

- Chapter 4: Characterization of SiC MOSFET The test structure which is used for MOSFET and parasitic diode characterization is presented. An accurate DC and CV characterization method is also provided.

- Chapter 5: BSIM3 and BSIM4 based models of SiC MOSFET Modeling activity

based on BSIM3 and BSIM4 is presented. Parameter extraction and optimization

method is provided and fitting results are shown. Limitations of BSIM3 and BSIM4

in modeling SiC MOSFETs are also provided.

- Chapter 6: Effects of interface traps on SiC MOS Device The origin of interface states in SiC MOS structure and their effects on DC, CV and transient characteristics are presented.

- Chapter 7: Model development of SiC MOSFET with Verilog-A Development of Verilog-A model based on BSIM4 is presented. Detail description of step by step parameter extraction is provided and fitting results are shown.

- Chapter 8: Conclusion and Future Work The summary of the dissertation and scope of future work are presented.

### **CHAPTER 2 SIC TECHNOLOGY**

## 2.1 Properties of SiC Material

SiC is one of the emerging wide band-gap materials which has shown tremendous potential in high voltage, high temperature and highly efficient circuits and systems specifically for power electronics applications. Besides having higher breakdown voltage, lower intrinsic carrier concentration, better thermal conductivity, the SiC substrate is suitable for growing high quality oxide [12]. This is partially why SiC has become primary material of choice for medium voltage (1200V) power MOSFET fabrication. In this section, fundamental material properties of silicon carbide are discussed and a brief overview of SiC process technology and semiconductor devices are outlined.

## 2.1.1 SiC Crystal structure

Although there are over one hundred crystalline structures (commonly known as polytypes) of SiC in nature, only a few of them are reproducible and hence are attractive for semiconductor device fabrication [13]. Also, different polytypes have different electrical characteristics despite the fact that each of the polytypes consists of 50% Si and 50% C atoms. As a result, there are only three useful SiC polytypes for electronics application which are known as 3C-SiC, 4H-SiC and 6H-SiC. SiC atomic crystal structure is composed of Si-C bilayers [14]. These bilayers are stacked in a vertical direction with different sequences and hence give rise to various polytypes. In each bilayer, one atom is covalently bonded with three neighboring atoms in the same layer and only one atom in the vertical layer. The unit cell of 4H polytype contains four Si-C bilayers in the stacking direction while the 6H polytype unit cell contains six bilayers. Both of the polytypes have a hexagonal lattice structure. SiC is a polar semiconductor which indicates that one bilayer surface normal to the vertical axis terminates in Si atoms and the opposite surface terminates in carbon

atoms. The 3C-SiC is the only polytype which has the cubic crystal lattice structure. Table 2.1 lists the fundamental electrical characteristics of different SiC polytypes. Material properties of other semiconductors are also listed in order to provide comparison. From the table, it is found that 4H-SiC has a larger bandgap, better thermal conductivity, lower intrinsic carrier concentration and higher electron and hole mobility compared to other two polytypes. Also 4H-SiC wafer has superior manufacturability and manufacturers have been successful in reducing the micropipe density and increasing the size of the wafer. This is why it has become the primary choice for SiC device fabrication [15]-[16].

Table 2.1. Comparison of SiC Polytype Electronic Properties with Si, GaAs and GaN. Data are compiled from the information found in [9], [17], [18], [19] and [20].

| Property                                                 | 4H-SiC            | 6H-SiC            | 3C-SiC  | Si        | GaAs              | GaN     |

|----------------------------------------------------------|-------------------|-------------------|---------|-----------|-------------------|---------|