# University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

12-2017

# Power Interface Design and System Stability Analysis for 400 V DC-Powered Data Centers

Yuzhi Zhang University of Arkansas, Fayetteville

Follow this and additional works at: http://scholarworks.uark.edu/etd Part of the <u>Electrical and Electronics Commons</u>, and the <u>Power and Energy Commons</u>

**Recommended** Citation

Zhang, Yuzhi, "Power Interface Design and System Stability Analysis for 400 V DC-Powered Data Centers" (2017). *Theses and Dissertations*. 2568. http://scholarworks.uark.edu/etd/2568

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, ccmiddle@uark.edu.

Power Interface Design and System Stability Analysis for 400 V DC-Powered Data Centers

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Engineering with a concentration in Electrical Engineering

by

Yuzhi Zhang The Second Artillery Engineering College Bachelor of Science in Electrical Engineering, 2008 Xi'an University of Technology Master of Science in Electrical Engineering, 2011 University of Arkansas Master of Science in Electrical Engineering, 2015

#### December 2017 University of Arkansas

This dissertation is approved for recommendation to the Graduate Council.

H. Alan Mantooth, Ph.D. Dissertation Director

Juan C. Balda, Ph.D. Committee Member Simon S. Ang, Ph.D. Committee Member

Roger Dougal, Ph.D. Ex-officio Member

#### ABSTRACT

The demands of high performance cloud computation and internet services have increased in recent decades. These demands have driven the expansion of existing data centers and the construction of new data centers. The high costs of data center downtime are pushing designers to provide high reliability power supplies. Thus, there are significant research questions and challenges to design efficient and environmentally friendly data centers with address increasing energy prices and distributed energy developments.

This dissertation work aims to study and investigate the suitable technologies of power interface and system level configuration for high efficiency and reliable data centers.

A 400 V DC-powered data center integrated with solar power and hybrid energy storage is proposed to reduce the power loss and cable cost in data centers. A cascaded totem-pole bridgeless PFC converter to convert grid ac voltage to the 400 V dc voltage is proposed in this work. Three main control strategies are developed for the power converters. First, a model predictive control is developed for the cascaded totem-pole bridgeless PFC converter. This control provides stable transient performance and high power efficiency. Second, a power loss model based dual-phaseshift control is applied for the efficiency improvement of dual-active bridge converter. Third, an optimized maximum power point tracking (MPPT) control for solar power and a hybrid energy storage unit (HESU) control are given in this research work. The HESU consists of battery and ultracapacitor packs. The ultracapacitor can improve the battery lifetime and reduce any transients affecting grid side operation.

The large signal model of a typical solar power integrated datacenter is built to analyze the system stability with various conditions. The MATLAB/Simulink<sup>TM</sup>-based simulations are used

to identify the stable region of the data center power supply. This can help to analyze the sensitivity of the circuit parameters, which include the cable inductance, resistance, and dc bus capacitance. This work analyzes the system dynamic response under different operating conditions to determine the stability of the dc bus voltage. The system stability under different percentages of solar power and hybrid energy storage integrated in the data center are also investigated. © 2017 Yuzhi Zhang All Rights Reserved

#### ACKNOWLEDGMENTS

First and foremost, I would like to express my sincere appreciation to my advisor, Prof. H. Alan Mantooth, who inspires my study, work, and life so much with his insightful vision, broad knowledge, professionalism, and creative thinking. I benefit a lot from Prof. Mantooth not only in many good projects but also his great personalities and leadership. I really enjoyed my five years of study and work with Prof. Mantooth's guidance and mentorship. He will be an inspiring role model for my future career growth.

I am very grateful to my other committee members, Prof. Juan C. Balda, Prof. Simon S. Ang, and Prof. Roger Dougal for their technical assistance, valuable suggestions and helpful discussion during my Ph.D. study. I'd like to offer my special thanks to Prof. Balda for his technical support, time and encouragement for my Ph.D. project. I'd also like thank Prof. Ang for his help for my Little Box Challenge project. I want to thank Prof. Dougal, at the University of South Carolina, for his help regarding my projects in the GRAPES NSF research center.

I am thankful to all my colleagues with whom I have worked together on many interesting projects. I'd like to thank Chris Farnell and Sayan Seal in regard to the Arkansas Powerbox project. I also appreciate the help from my other professors, colleagues, and friends: Prof. Yue Zhao, Prof. Roy A. McCann, Prof. Shui-Qing (Fisher) Yu, Prof. Randy Brown, Mrs. Connie Howard, Dr. Tao Yang, Haoyan Liu, Janviere Umuhoza, Joe Moquin, Tavis Clemmer, Shuang Zhao, Audrey Dearien, Ramchandra Kotecha, Nan Zhu, Yusi Liu and Fahad Hossain. I'd also like to thank Dr. Liang Jia, Udaya Kiran Ammu, and Neilus O'Sullivan for their help and guidance during my internship at Google's Mountain View office. I'd like to thank Shan Xu for supporting me through days and nights spent accomplishing my research work and making my Ph.D. study a happy journey.

Finally, and most importantly, I am extremely grateful to the University of Arkansas for supporting me during my Ph.D. Study.

#### DEDICATION

This dissertation is dedicated to my parents, Naizhu Zhang and Xiange Guo. My heartfelt gratitude goes to them for their everlasting love, strength and support through my entire life. This dissertation is also dedicated to my brother, Yuhua Zhang and my sisters, Qingxiu Zhang, Qingmei Zhang, Guiqing Zheng, Xinhua Zhang.

# TABLE OF CONTENTS

| CHAPTER          | R 1 INTRODUCTION AND THEORETICAL BACKGROUND                                     | . 1 |

|------------------|---------------------------------------------------------------------------------|-----|

| 1.1              | Background: The Challenge and Opportunity of Data Center Power Conversion       | . 1 |

| 1.1.1            | Quantity and capacity expansion of data centers                                 | . 1 |

| 1.1.2            | Climbing electricity price                                                      | . 2 |

| 1.1.3            | High cost of data center power supply downtime                                  | . 3 |

| 1.2 I            | Previous Research                                                               | . 4 |

| 1.2.1            | Power distribution bus: 120 VAC or 400 VDC                                      | . 4 |

| 1.2.2            | Integration with renewable energy and stability consideration                   | . 5 |

| 1.2.3            | Energy storage in data center                                                   | . 6 |

| 1.3 l            | Proposed 400 V DC-powered Data Center with Solar Power Integration              | . 8 |

| 1.4 l            | Problem Definitions                                                             | 10  |

| 1.4.1            | Topology consideration                                                          | 10  |

| 1.4.2<br>Control | Controller consideration: Proportional-Integral Control vs Model Predicti<br>11 | ive |

| 1.4.3            | Efficiency consideration                                                        | 12  |

| 1.4.4            | Green data center                                                               | 14  |

| 1.5 0            | Outline                                                                         | 14  |

| 1.6 l            | Reference                                                                       | 16  |

| CHAPTER          | R 2 DESIGN, MODELING AND CONTROL OF RECTIFIER STAGE                             | 17  |

| 2.1              | Introduction and Motivation                                                     | 17  |

| 2.1.1            | Ac/dc voltage conversion with low-frequency transformer                         | 17  |

| 2.1.2            | Ac/dc voltage conversion with high-frequency transformer                        | 21  |

| 2.1.3            | Design of cascaded scaled-down totem-pole multilevel converter                  | 33  |

| 2.2              | Control Strategy: PI Control vs Model Predictive Control                        | 35  |

| 2.2.1            | Conventional PI control                                                         | 35  |

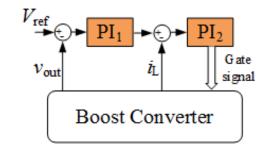

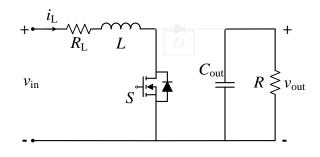

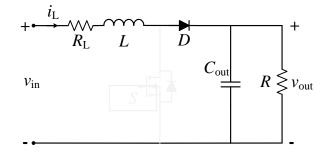

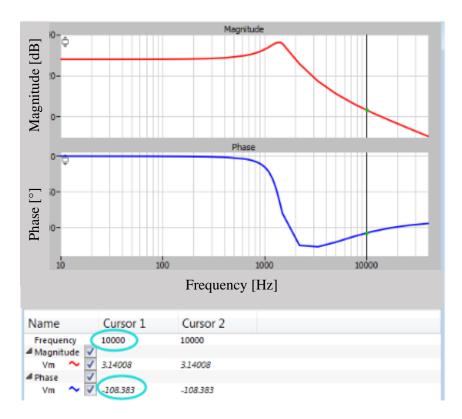

| 2.2.2            | Conventional PI controller design steps for a boost converter                   | 37  |

| 2.2.3            | Model predictive control                                                        | 40  |

| 2.2.4            | Discretization method: from continuous-time domain to discrete-time domain.     |     |

| 2.2.5            | Comparison of PI and MPC                                                        | 44  |

| 2.3              | MPC design for Cascaded Bridgeless Totem-Pole Multilevel Converter              | 45  |

| 2.3.1            | Cascaded totem-pole converter modeling                                          | 46  |

|    | 2.3.2  | Cost function of totem-pole converter                            | 48  |

|----|--------|------------------------------------------------------------------|-----|

|    | 2.3.3  | Block diagram of controllers                                     | 53  |

|    | 2.3.4  | Simulation and experiment verification                           | 54  |

| 2. | .4     | Conclusion                                                       | 58  |

| 2. | .5     | Reference                                                        | 60  |

|    |        | R 3 MODELING AND CONTROL OF SOLID STATE TRANSFORMER DC           |     |

|    |        | ICIENCY IMPROVEMENT                                              |     |

| 3. |        |                                                                  |     |

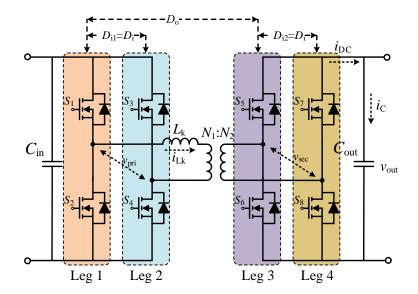

| 3. |        | Dual Active Bridge Operation                                     |     |

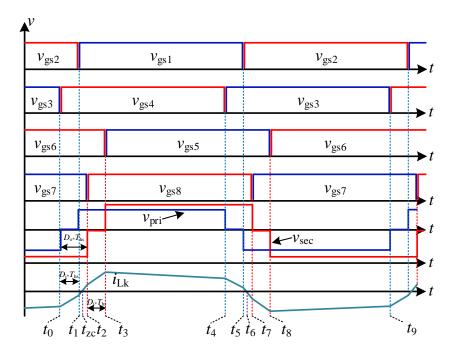

|    | 3.2.1  | Single phase-shift control                                       |     |

|    | 3.2.2  | Extended phase-shift control                                     |     |

|    | 3.2.3  | Dual-phase-shift control                                         |     |

|    | 3.2.4  | Triple phase-shift control                                       |     |

|    | 3.2.5  | Conclusion                                                       |     |

| 3. |        | Efficiency Optimization Methods                                  |     |

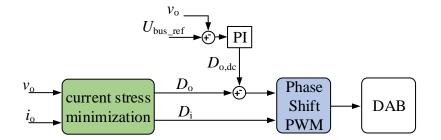

|    | 3.3.1  | Current stress minimization method                               |     |

|    | 3.3.2  | Circulating power reduction method                               |     |

| 3. |        | SiC MOSFET-based DAB Operation Principle                         |     |

| 3. |        | Simplified Power Loss Model and Improved Power Loss Model        |     |

|    | 3.5.1  | Switching loss analysis and modeling                             |     |

|    | 3.5.2  | Conduction loss analysis and modeling                            |     |

|    | 3.5.3  | The power loss from the transform and auxiliary inductor         |     |

| 3. |        | The Total Loss Model                                             |     |

| 3. |        | Efficiency Optimized Method: Lagrangian Objective Function       |     |

|    | 3.7.1  | Power delivery capability                                        |     |

|    | 3.7.2  | Minimum power loss design                                        | 87  |

|    | 3.7.3  | Control strategy of DAB with loss model                          |     |

| 3. | .8     | Experimental Verification                                        | 88  |

|    | 3.8.1  | Same $V_{out\_ref}$ and same load power, different $V_{in}$      | 89  |

|    | 3.8.2  | Same V <sub>in</sub> , different load power                      | 90  |

| 3. | .9     | Loss Model Based Efficiency Improvement Conclusion               | 90  |

| 3. | .10    | Transient Performance Improvement Methods                        | 91  |

|    | 3.10.  | I Introduction                                                   | 91  |

|    | 3.10.2 | 2 Proposed K-Factor control with the virtual capacitor for a DAB | 94  |

|    | 3.10.3 | 3 Comparative analysis of transit response characterization      | 106 |

| 3.10           | 0.4 Hardware experimental validation of the proposed control                          | 114        |

|----------------|---------------------------------------------------------------------------------------|------------|

| 3.10           | 0.5 Conclusion of virtual capacitor based K-factor control                            | 117        |

| 3.11           | Other Testing Results                                                                 | 117        |

| 3.12           | Reference                                                                             | 121        |

|                | ER 4 DISTRIBUTED ENERGY INTEGRATION AND HYBRID<br>1ENT STRATEGY FOR 400 V DATA CENTER |            |

| 4.1            | Introduction and Motivation                                                           | 126        |

| 4.2            | Description of Green Data Center                                                      | 127        |

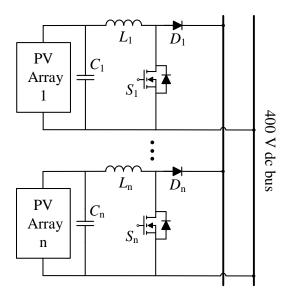

| 4.3            | PV Topology and MPPT Control                                                          | 128        |

| 4.4            | PV Power Spectrum Analysis                                                            |            |

| 4.5            | Hybrid Energy Storage                                                                 |            |

| 4.5.2<br>packs | 1 Controller design of the buck/boost converter for the battery and ultr<br>135       | acapacitor |

| 4.5.2          | 2 Power reference calculation                                                         |            |

| 4.6            | Grid-Side Converter Design                                                            |            |

| 4.7            | Case Study and Simulation Verification                                                | 139        |

| 4.7.           | 1 Data center integrated with solar power and hybrid energy storage                   |            |

| 4.7.2          | 2 Different percentages of solar power in data center                                 |            |

| 4.8            | Conclusion                                                                            |            |

| 4.9            | Reference                                                                             |            |

| CHAPTI         | ER 5 SYSTEM LEVEL STABILITY ANALYSIS FOR 400 V DATA CEN                               | NTER 150   |

| 5.1            | Stability Issue in a Data Center                                                      | 150        |

| 5.2            | Mathematical Model: Large Signal Modeling of Large-Scale Data Center                  | 150        |

| 5.3            | Stability Criterion Introduction                                                      | 152        |

| 5.4            | Simulation Results and Stability Analysis                                             |            |

| 5.5            | Conclusion                                                                            | 156        |

| 5.6            | References                                                                            | 157        |

| CHAPTI         | ER 6 CONCLUSION FUTURE WORK                                                           | 158        |

| 6.1            | Conclusion                                                                            | 158        |

| 6.2            | Future work                                                                           | 159        |

## LIST OF FIGURES

| Fig. 1-1 Total Electricity Consumption of Data Centers in U.S. [1.1]                      |

|-------------------------------------------------------------------------------------------|

| Fig. 1-2 Annual Average Retail Price of Electricity [1.2]                                 |

| Fig. 1-3 Traditional ac Distribution Efficiency                                           |

| Fig. 1-4 Efficiency of 400 V DC Distribution Architecture                                 |

| Fig. 1-5 Cable Size Comparison between 48 V and 400 V with 100 kW Load                    |

| Fig. 1-6 Ultracapacitor Consumption by Market [1.5]7                                      |

| Fig. 1-7 Ultracapacitor Module from Schneider [1.5]7                                      |

| Fig. 1-8 Conventional AC-powered Data Center9                                             |

| Fig. 1-9 400 V DC-powered Data Center Integrated with Solar Power and Energy Storage 9    |

| Fig. 1-10 A Typical Power Losses in a Data Center [1.3]13                                 |

| Fig. 2-1 Ac/dc Power Conversion: with Low-Frequency Transformer Application 17            |

| Fig. 2-2 Classic Boost-type Rectifier                                                     |

| Fig. 2-3 Totem-pole Bridgeless PFCs with Wide Bandgap Devices                             |

| Fig. 2-4 Simulation Results of Efficiency Comparison: 240 V ac to 400 V dc with 5 kW Load |

|                                                                                           |

| Fig. 2-5 System Configuration Using Medium- or High-frequency Transformer21               |

| Fig. 2-6 Five-level NPC ac/dc Topology                                                    |

| Fig. 2-7 Modular Multilevel PFC Converters                                                |

| Fig. 2-8 Multi-Cell Boost Topology with Four Input Series Output Parallel Connected       |

| Converter                                                                                 |

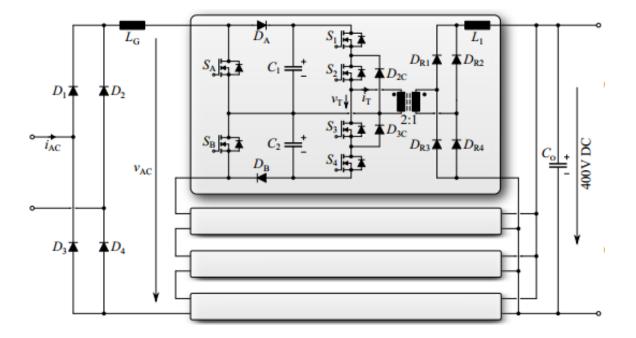

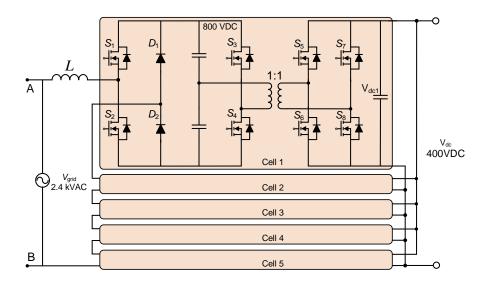

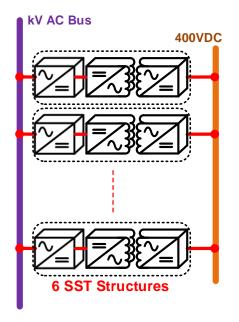

| Fig. 2-9 Proposed Topology for 1 MW Power Data Center                                     |

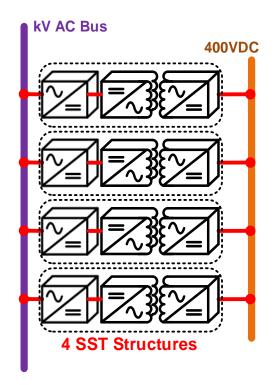

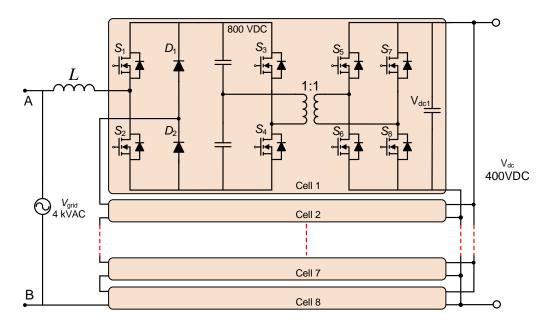

| Fig. 2-10 Proposed Topology for 10 MW Power Data Center                                   |

| Fig. 2-11 Proposed Topology for 30 MW Power Data Center                                   | 2  |

|-------------------------------------------------------------------------------------------|----|

| Fig. 2-12 Totem-pole Bridgeless PFC Converter, Two Cells                                  | 3  |

| Fig. 2-13 Boost Converter Topology as Example                                             | 6  |

| Fig. 2-14 Equivalent Circuits with Switch On and Off                                      | 7  |

| Fig. 2-15 Bode-plot of a Boost Converter in PLECS                                         | 9  |

| Fig. 2-16 The Procedure to Choose the Proper Switching State                              | 3  |

| Fig. 2-17 Design Flowcharts of PI and MPC Control 4                                       | .4 |

| Fig. 2-18 Scaled-down Prototype: ac/dc Stage, Two Cells 4                                 | 5  |

| Fig. 2-19 Simulation Results of 400 dc Bus Balance Performance                            | 0  |

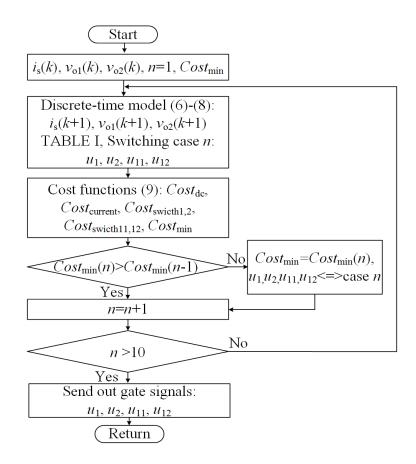

| Fig. 2-20 The Flowchart of MPC5                                                           | 3  |

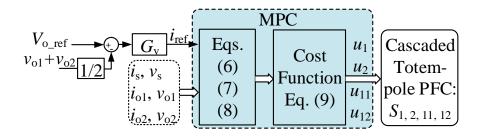

| Fig. 2-21 The Block Diagram of MPC and Conventional PI for the Proposed Topology 5        | 4  |

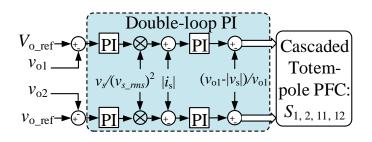

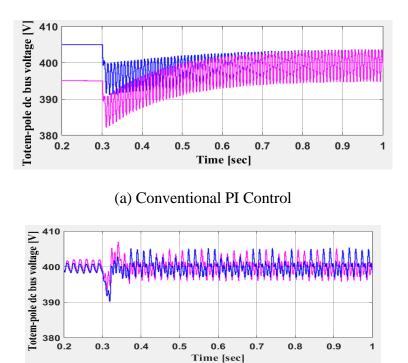

| Fig. 2-22 Normal Operation to Step-up Load of the Two Controllers                         | 5  |

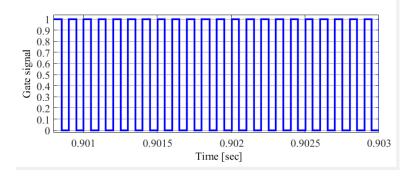

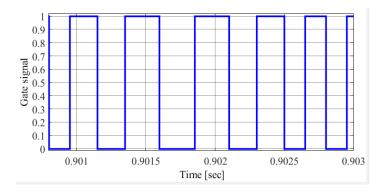

| Fig. 2-23 Gate Signals For a Selected Switch Position For Conventional PI Control5        | 6  |

| Fig. 2-24 Gate Signals for a Selected Switch Position for Model Predictive Control        | 6  |

| Fig. 2-25 Experimental Setup: Typhoon Simulator and DSP Control Card5                     | 7  |

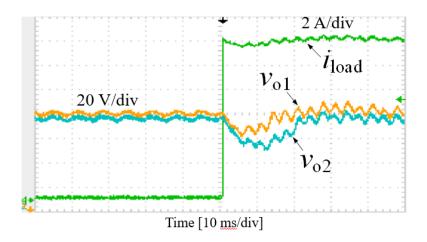

| Fig. 2-26 Hardware-In-Loop Testing Results of Conventional PI Control (Time: 25 ms/div    | v, |

| $v_{01} = v_{02} = 400 \text{ V}, i_{\text{load}}: 0 \text{ to } 12.5 \text{ A})$         | 8  |

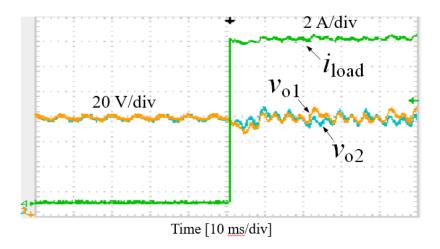

| Fig. 2-27 Hardware-In-Loop Testing Results of The Proposed Model Predictive Control (Time | e: |

| 25 ms/div, $v_{01}=v_{02}=400$ V, $i_{10ad}$ : 0 to 12.5 A)                               | 8  |

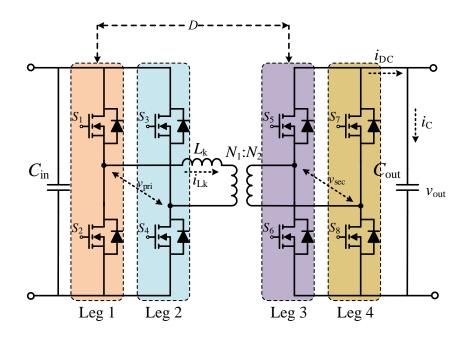

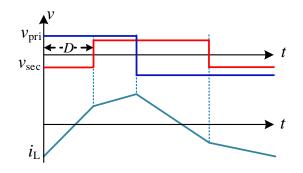

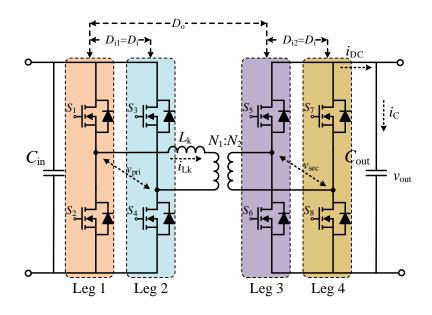

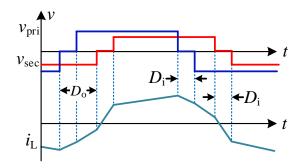

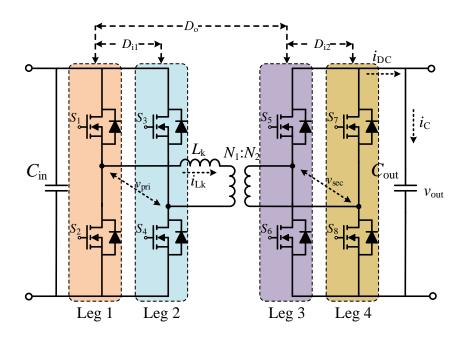

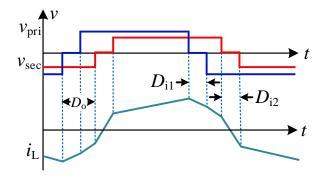

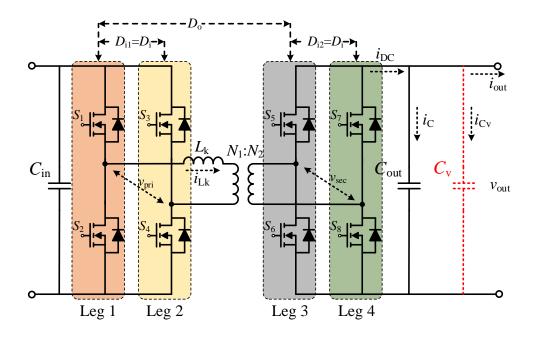

| Fig. 3-1 Dual-Active Bridge with Single Phase-Shift Control                               | 5  |

| Fig. 3-2 Single Phase-Shift Control: The Transformer Input/Output Voltage and Inductor L  | k  |

| Current                                                                                   | 6  |

| Fig. 3-3 Dual-Active Bridge with Extended Phase-Shift Control                             | 7  |

| Fig. 3-4 Extended Phase-Shift Control: The Transformer Input/Output Voltage and Inductor          |

|---------------------------------------------------------------------------------------------------|

| <i>L</i> <sub>k</sub> Current                                                                     |

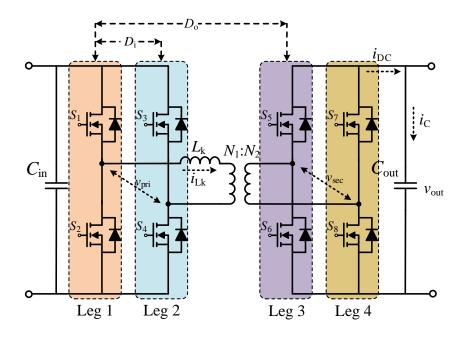

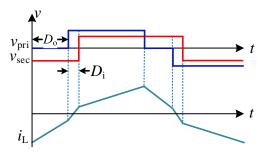

| Fig. 3-5 Dual-Active Bridge with Dual Phase-Shift Control                                         |

| Fig. 3-6 Dual Phase-Shift Control: The Transformer Input/Output Voltage and Inductor $L_k$        |

| Current                                                                                           |

| Fig. 3-7 Dual-Active Bridge with Triple Phase-Shift Control                                       |

| Fig. 3-8 Triple Phase-Shift Control: The Transformer Input/Output Voltage and Inductor Lk         |

| Current                                                                                           |

| Fig. 3-9 Control Diagram of Current Stress Minimization                                           |

| Fig. 3-10 Control Diagram of Circulating Power Reduction                                          |

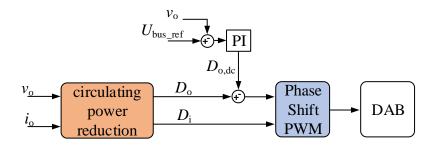

| Fig. 3-11 Control Signal and Circuits Waveform when <i>D</i> <sub>i</sub> < <i>D</i> <sub>o</sub> |

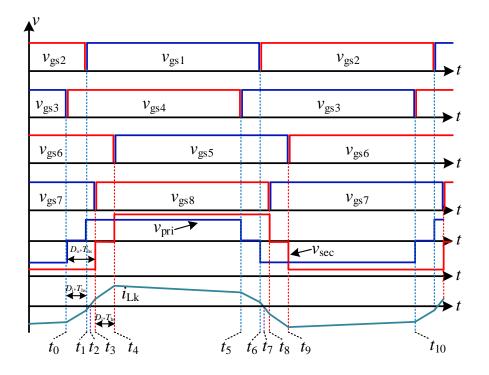

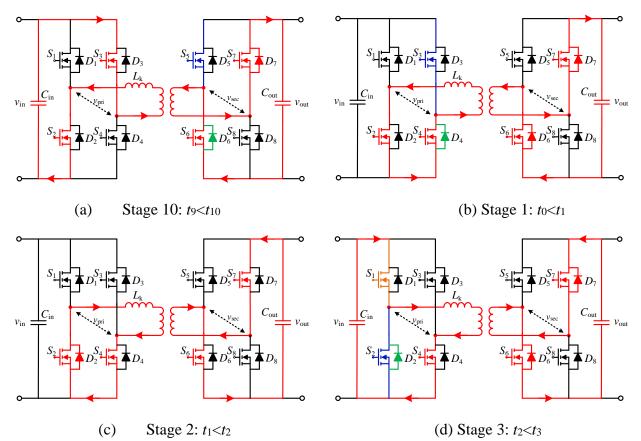

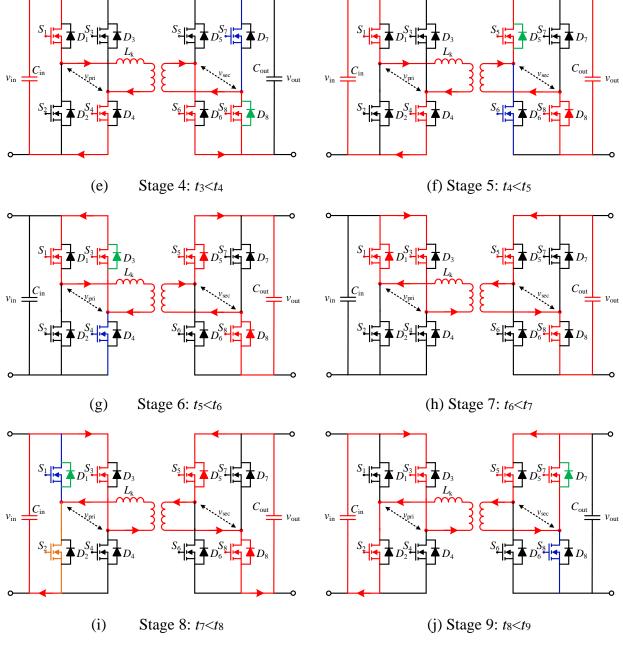

| Fig. 3-12 10 Operational Stages when <i>D</i> <sub>i</sub> < <i>D</i> <sub>0</sub>                |

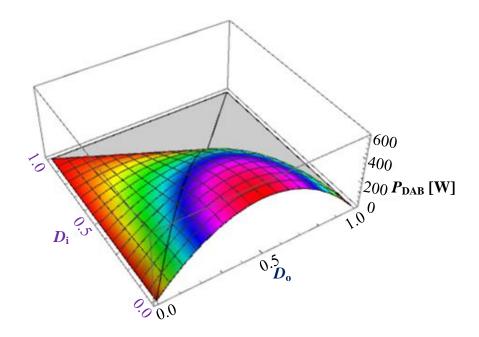

| Fig. 3-13 Power Curve of the DAB with Dual-Phase-Shift Control                                    |

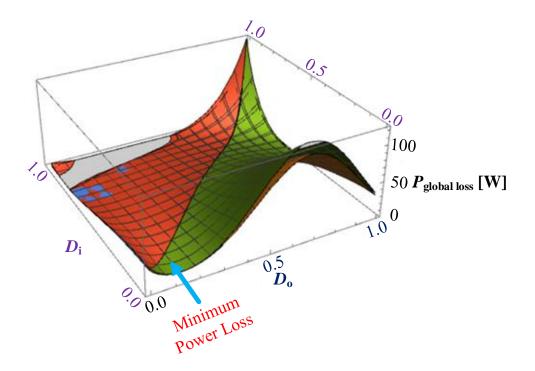

| Fig. 3-14 Power Loss 3D Plot when DAB with Dual-Phase-Shift Control                               |

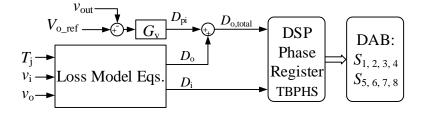

| Fig. 3-15 Control Diagram of Power Loss Minimization                                              |

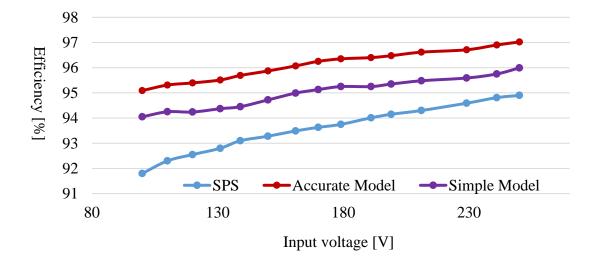

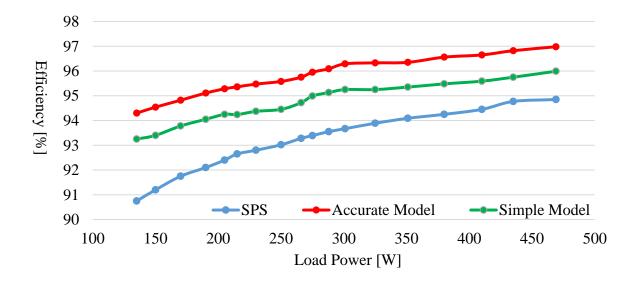

| Fig. 3-16 Efficiency Testing Results of SPS, Accurate Model and Simple Model with Vary            |

| Input Voltage                                                                                     |

| Fig. 3-17 Efficiency Testing Results of SPS, Accurate Model and Simple Model with Varying         |

| Load Power                                                                                        |

| Fig. 3-18 DAB Converter with Phase-Shift Control                                                  |

| Fig. 3-19 Transformer Primary and Secondary Voltages, DAB Inductor Current with DPS               |

| Control                                                                                           |

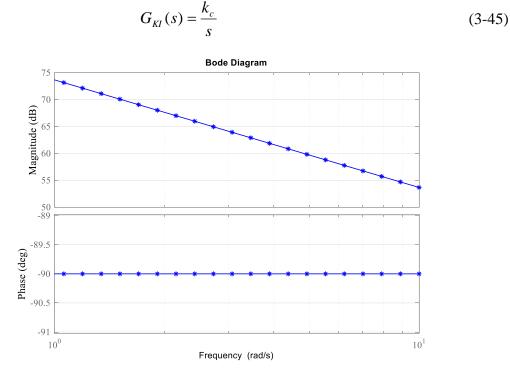

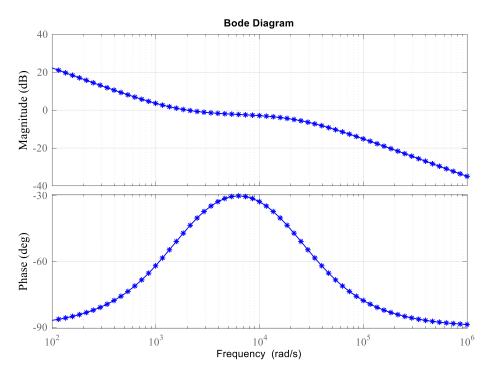

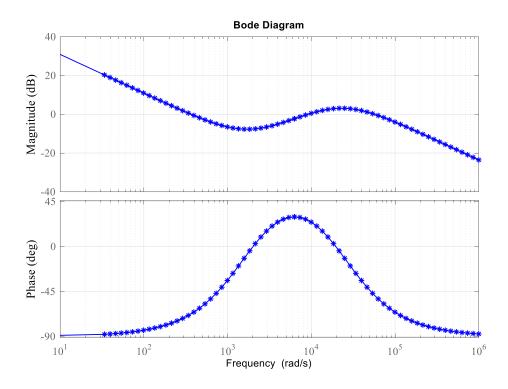

| Fig. 3-20 Bode plot of Type I K-factor controller                                                 |

|    | Fig. 4-5 Frequency Spectrum Analysis of PV Power Over A 24-Hour Period       | . 134  |

|----|------------------------------------------------------------------------------|--------|

|    | Fig. 4-6 Circuit Diagram of the Energy Storage Packs                         | . 135  |

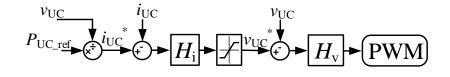

|    | Fig. 4-7 Control Diagram of the Battery Pack                                 | . 136  |

|    | Fig. 4-8 Control Diagram of the Ultracapacitor Pack                          | . 136  |

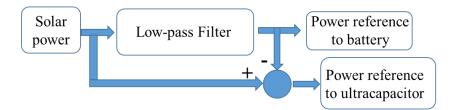

|    | Fig. 4-9 Power Reference Generation for Battery and Ultracapacitor           | . 137  |

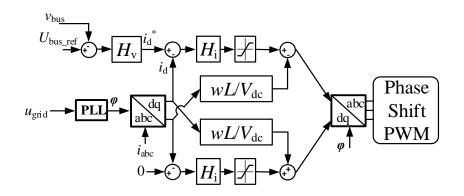

|    | Fig. 4-10 Block Diagram of the Grid-Side Converter                           | . 138  |

|    | Fig. 4-11 The Control Algorithm of the Grid-side Converter                   | . 138  |

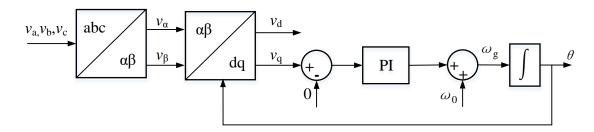

|    | Fig. 4-12 Control Strategy of PLL                                            | . 139  |

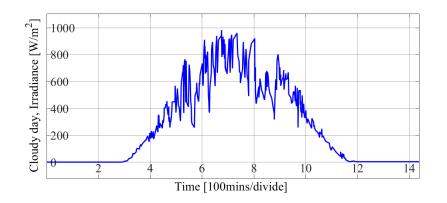

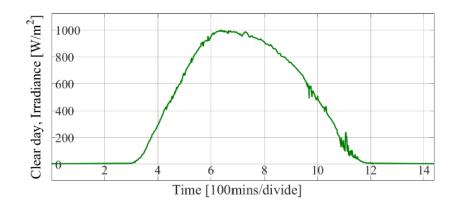

|    | Fig. 4-13 Solar Irradiance on a Cloudy Day                                   | . 139  |

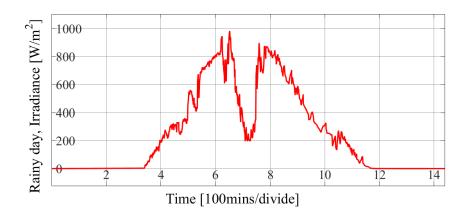

|    | Fig. 4-14 Solar Irradiance on a Rainy Day                                    | . 140  |

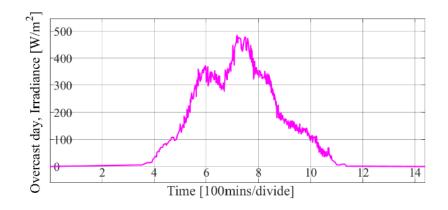

|    | Fig. 4-15 Solar Irradiance on an Overcast Day                                | . 140  |

|    | Fig. 4-16 Solar Irradiance on a Clear Day                                    | . 140  |

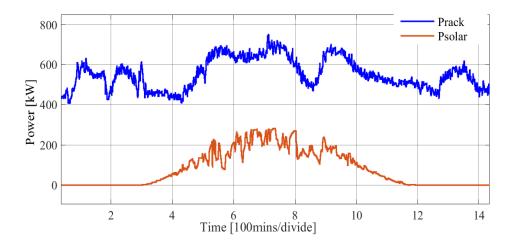

|    | Fig. 4-17 Rack Power and PV Power on a Cloudy Day Over 24 Hours              | . 141  |

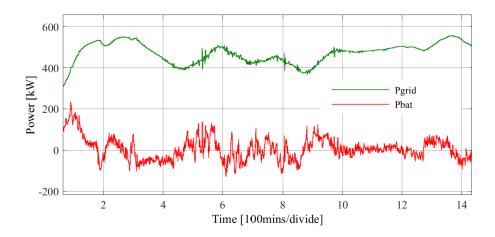

|    | Fig. 4-18 Power Flows of the Grid and Battery without Ultracapacitor Pack    | . 141  |

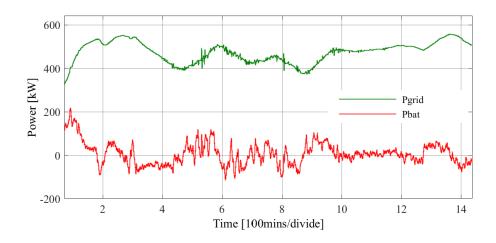

|    | Fig. 4-19 Power Flows of the Grid and Battery with Ultracapacitor Pack       | . 142  |

|    | Fig. 4-20 The 400-V DC Bus Voltage without Ultracapacitor Compensation       | . 143  |

|    | Fig. 4-21 The 400-V DC Bus Voltage and Ultracapacitor Powers with Ultracapa  | ncitor |

| Co | mpensation                                                                   | . 143  |

|    | Fig. 4-22 DC Bus Voltage Performance of 0.5 MW, 1.5 MW, and 3 MW Data Center | with   |

| So | lar Power                                                                    | . 146  |

|    | Fig. 5-1 Large Signal Model of 400 V DC-Powered Data Center                  | . 151  |

|    | Fig. 5-2 The Specification of Pole Location [5.6]                            | . 153  |

|    | Fig. 5-3 System Stability: Eigenvalue and Voltage Response                   | . 153  |

|    |                                                                              |        |

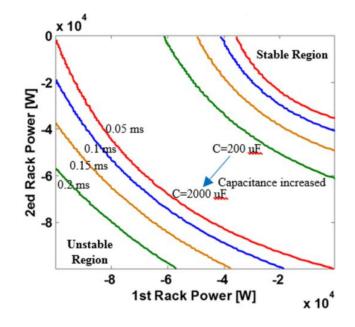

| Stable Boundary of Different dc Bus Cable Impedance 155                               |    |

|---------------------------------------------------------------------------------------|----|

| Stable Boundary of DC Bus Capacitor. 200µF: 0.2 ms (Green), 0.15 ms (Orange), 0.1     |    |

| 0.05 ms (Red). 2000μF: 0.2 ms (Green), 0.15 ms (Orange), 0.1 ms (Blue), 0.05 ms (Red) | ms |

|                                                                                       |    |

## LIST OF TABLES

| Table 2.1 Comparison of Three Typical PFC Converters                    | 20  |

|-------------------------------------------------------------------------|-----|

| Table 2.2 Switch Specification in 1 MW Data Center                      | 28  |

| Table 2.3 Switch Specification in 10 MW Data Center                     | 31  |

| Table 2.4 Switch Specification in the Scaled-down ac/dc Converter       | 34  |

| Table 2.5 Switching Cases of Cascaded Bridgeless Totem-pole PFC         | 51  |

| Table 3.1 The Inductor $L_k$ Current Equations, $D_i < D_0$             | 77  |

| Table 3.2 The Switching Actions in One Switching Period                 | 79  |

| Table 3.3 The Conduction Actions in One Switching Period                | 79  |

| Table 3.4 Parameters for Simulation                                     | 107 |

| Table 3.5 Circuit Parameters for the Scaled Down Prototype              | 118 |

| Table 4.1 The PV Panels Simulation Parameters                           | 132 |

| Table 4.2 DC Bus Ripple of 0.5 MW Data Center with Variable Solar Power | 144 |

| Table 4.3 DC Bus Ripple of 1.5 MW Data Center with Variable Solar Power | 144 |

| Table 4.4 DC Bus Ripple of 3 MW Data Center with Variable Solar Power   | 145 |

| Table 5.1 Simulation Parameters                                         | 154 |

#### **CHAPTER 1**

#### INTRODUCTION AND THEORETICAL BACKGROUND

#### **1.1 Background: The Challenge and Opportunity of Data Center Power Conversion**

#### 1.1.1 Quantity and capacity expansion of data centers

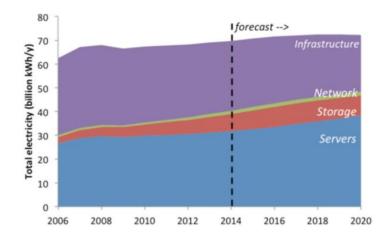

The popularity of internet services and cloud computing is leading to continuous expansion of data centers. To meet the demands of high computation speed and data storage capacity, the quantity and capacity of data centers is rapidly increasing. Larger IT companies such as Microsoft, Google, Facebook, Alibaba, and Baidu are building more data centers around the world. At the same time, the energy required by data centers is climbing very quickly. The Lawrence Berkeley National Laboratory, in collaboration with experts at Stanford, Carnegie Mellon, and Northwestern published a figure showing the rising energy consumption by data centers, which is given in Fig. 1-1 [1.1]. In 2013, the electricity used by data centers increased to 70 billion kilowatt-hours (kWh). The amount of 70 billion kWh is close to 1.8% of total electricity usage in the U.S. in 2014. The report shows the electricity consumption is expected to continue increasing to up to 4% of total electricity usage of the U.S. by 2020.

Fig. 1-1 Total Electricity Consumption of Data Centers in U.S. [1.1]

#### 1.1.2 Climbing electricity price

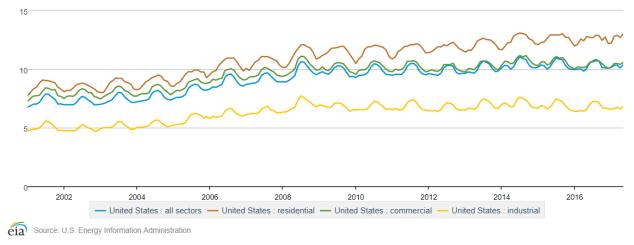

From the electricity data provided by the U.S. Energy Information Administration, illustrated in Fig. 1-2 [1.2], the energy prices are climbing every year. From 2001 to 2014, the average retail price of industrial electricity increased from 5.05 cents per kWh to 7.1 cents per kWh. For example, the actual monthly critical average power of a 10 MW data center often is 4-6 MW [1.3]. The monthly average power is selected as 5 MW. The industrial electricity price is 7.1 cents per kWh. If the power converter reaches 5% power loss reduction, then the electricity cost reduction will be \$155,098 per data center per year, and the related cost will also be further reduced, like the costs of operational and cooling systems.

Fig. 1-2 Annual Average Retail Price of Electricity [1.2]

The efficiency is the key element to reduce the total power consumption, increase the power density and lead to small footprint of data centers. The design of high efficiency data centers includes power transmission, conversion, and distribution development.

#### 1.1.3 High cost of data center power supply downtime

Due to the power capacity and expansion of data centers, the reliability of data centers is becoming increasingly important. Due to the growing quantity and density of data centers, the consequences of outages are increasing. Emerson Company reports, data centers have an average downtime of 2.34 hours, and an average of 2.5 outages per year [1.4]. For 500,000 data centers, the Emerson Company estimated \$2.84 million in annual outage costs for data centers. Designing a more reliable power supply would reduce expensive downtime and avoid associated costs.

To meet the requirements of high performance and low power loss, many researchers have been working on power topology development, integration with renewable energy, system level stability analysis, etc. The detailed research status is summarized in the following section.

#### 1.2 Previous Research

#### 1.2.1 Power distribution bus: 120 VAC or 400 VDC

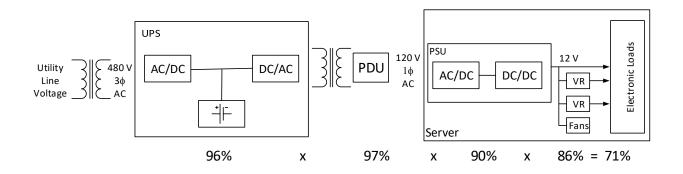

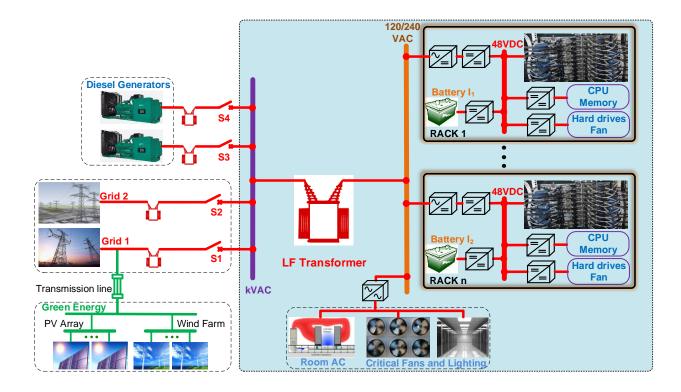

The typical efficiencies obtainable through the ac system technologies in data centers are given in Fig. 1-3. A traditional Uninterruptible Power Supply (UPS) architecture is utilized. It employs at least two stages. Ac voltage from the grid side is converted to dc voltage first. An energy storage device, like lead-acid batteries, is connected to the dc bus. The dc bus is then inverted to an ac bus which is the Power Distribution Unit (PDU). The advantage of this traditional four stages architecture is robustness. However, the end-to-end efficiency is a relatively low 71%. From article [1.3], about 15% of data center's power is wasted and dissipated as heat.

Fig. 1-3 Traditional ac Distribution Efficiency

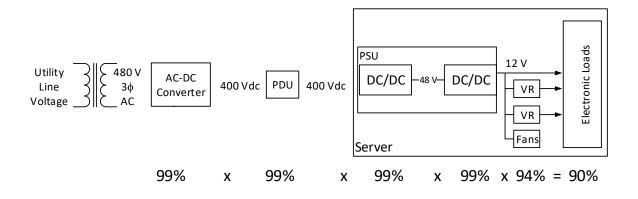

Dc distribution is attractive, it eliminates at least one power inversion stage, resulting in higher efficiency. The efficiency performance of dc distribution is shown in Fig. 1-4. Compared with the ac distribution, the efficiency is improved from 71% to 90%. This 19% efficiency increase leads to significant cost reduction of the cooling system. What's more, as the power distribution voltage is increased to 400 V dc, the conduction loss can be reduced, allowing the use of lighter and more economic cables. The power cable comparison between 48 V dc and 400 V dc is shown in Fig. 1-5.

Fig. 1-4 Efficiency of 400 V DC Distribution Architecture

Fig. 1-5 Cable Size Comparison between 48 V and 400 V with 100 kW Load

Another merit of the dc distribution architecture is its ease in integrating with distributed energy sources, such as solar photovoltaic, wind turbine, fuel cell, etc. In current commercial technologies, dc equipment is available, but the costs are higher than comparable ac equipment.

In this dissertation, a 400 V bus is selected due to higher efficiency consideration. The power topology development and design is analyzed and designed in detail in Chapters 2 to 5.

#### 1.2.2 Integration with renewable energy and stability consideration

Usually, data centers are built in a place with reliable and sustainable sources of power; protected from hazards, environment friendly and so on. Unfortunately, those places are not the best choice for renewable energy generation where the data center has better efficiency performance. What's more, data center operation needs reliable power, but solar power is only available during the daytime and wind power is only available when the wind is blowing. The truth of the 'Green Data Center' mentioned from the industrial side is that these companies purchase at least an equivalent amount of power from renewable energy companies and sell the energy back into the grid at a wholesale price [1.3]. Given the large size of many data centers, the large roofs offer excellent real estate for solar panel placement. This dissertation considers solar panels on the roof as green power and utilizes energy storage to reduce the electricity cost and the non-green emissions from the grid. Due to the randomness and fluctuation of solar power generation, the effects to the system stability will be investigated in this dissertation.

#### 1.2.3 Energy storage in data center

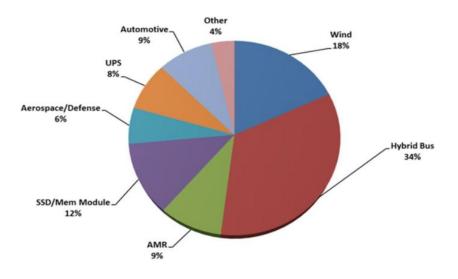

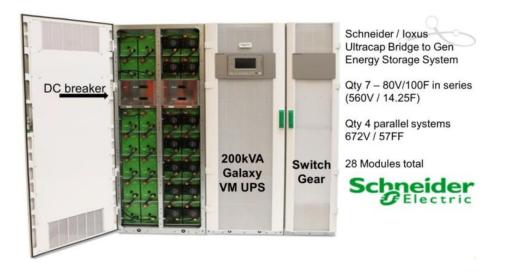

Energy storage, such as batteries, play an important role in the UPS system. It supplies the uninterrupted power to critical loads. Power transients, due to solar irradiance transients or load changes, need to be smoothed by the energy storage. Lead-acid batteries are widely used in the data center due to their low cost. However, rapid charging and discharging degrade the life expectancy of a battery pack. To overcome this drawback, ultracapacitor packs are considered in this work. The ultracapacitor application market is shown in Fig. 1-6 [1.5]. The global ultracapacitor consumption is fast growing. This market is expected to grow from \$500M in 2015 to \$1.5B around 2020. One type of ultracapacitor module from Schneider is shown in Fig. 1-7. With more technological advancements, both the cost and maintenance of ultracapacitors have gone down.

Fig. 1-6 Ultracapacitor Consumption by Market [1.5]

Fig. 1-7 Ultracapacitor Module from Schneider [1.5]

Ultracapacitors allow more charge/discharge cycles and have a higher power density, which are desirable for fast power smoothing. In this dissertation, an investigation is conducted for the design of high frequency ripple reduction and battery lifetime improvment, which are both compensated by ultracapacitors.

#### **1.3** Proposed 400 V DC-powered Data Center with Solar Power Integration

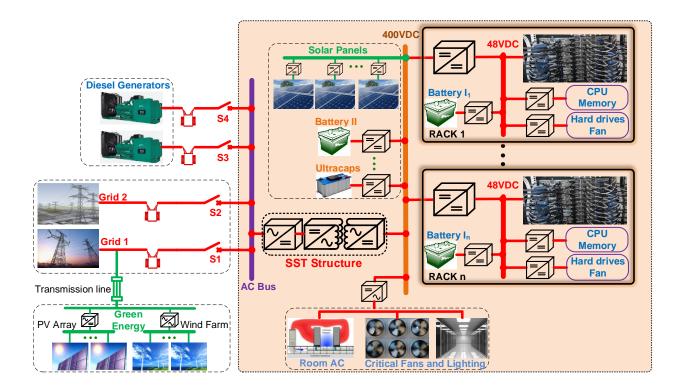

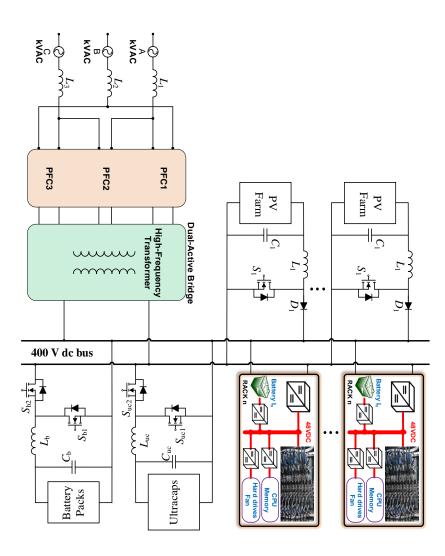

As mentioned, the traditional ac bus data center configured as shown in Fig. 1-8 has low efficiency in the distribution unit. For high efficiencies and high power densities, high-power dc distribution, such as 400 V in DC-powered data centers, is becoming more attractive. Due to the high power levels of data centers, the input of the ac/dc converter is usually connected to a medium-voltage power grid through bulky low-frequency step-up transformers. Recently, highfrequency transformers in multilevel converters are investigated due to their small size, light weight, high power density and capability for integrating multiple functions [1.6][1.7]. The proposed 400 V DC-powered data center is shown in Fig. 1-9. Compared with traditional ac bus data centers, the low-frequency transformer is replaced by a solid-state transformer and the power distribution is improved with a higher voltage 400 V bus, thus the current in the bus bars are decreased. The conduction power loss and cable cost in the distribution bus bars are reduced as well. To reduce the voltage stresses on switches and increase the current carrying capabilities, different multilevel converter topologies have been investigated by various groups [1.8][1.9]. Some topologies utilize high breakdown voltage IGBTs. However, IGBTs are inherently slow devices and have a tail current. The tens of kV power MOSFETs are rarely available in the market and mostly under investigation in the research environment. For high efficiency and switching speed considerations, commercial SiC power MOSFETs rated from 0.9 kV to 1.7 kV are adopted in this paper.

Fig. 1-8 Conventional AC-powered Data Center

Fig. 1-9 400 V DC-powered Data Center Integrated with Solar Power and Energy Storage

Furthermore, to build a real 'green' data center and reduce the energy consumption from grid side, in the evaluated system the locally produced solar power is interfaced to the 400 V dc bus through dc/dc converters. To maintain the 400 V dc bus, the battery and ultracapacitor packs are interfaced with the same 400 V dc bus through dc/dc converters. A high-power active-front-end rectifier is utilized at the grid side. The existing 48 V telecom power supply is recognized as a more economical and practical option. To minimize the revision from the existing power supply in data center, 48-V dc bus is kept in the rack. The battery as back-up energy is on the 48-V dc bus as well. A dc/dc converter steps down 400 V to 48 V in the server racks.

#### **1.4 Problem Definitions**

There are many research topics in a data center. The high reliability, efficiency and green data center are identified as the main topics in this dissertation.

#### 1.4.1 Topology consideration

#### 1.4.1.1 The issue in ac/dc voltage conversion

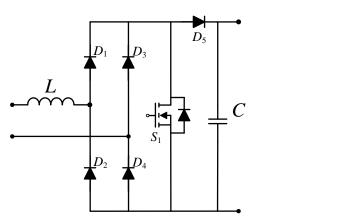

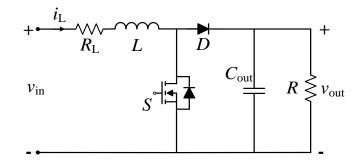

For ac/dc voltage conversion, Power Factor Correction (PFC) converters are widely adopted. The most popular and conventional PFC converter is the diode bridge rectifier in series with a boost converter. The benefit of this topology is that just one switch needs to be controlled. The drawback is that at least two diodes are on in every power delivery circle, leading to inefficient power conversion. Some soft-switching controllers are investigated to reduce the reverse recovery of Si diodes [1.10][1.11]. Complicated auxiliary circuits and more complex controls are needed to realize soft-switching.

#### 1.4.1.2 Proposed solution for ac/dc voltage conversion

In this dissertation, two different types of bridgeless PFC converters are carefully compared with the diode full bridge rectifier. The dual boost bridgeless PFC (DBP) converter has better efficiency performance by reducing the conduction loss on the diodes. It requires more components, which means the need of auxiliary gate drivers and higher cost. Two high frequency diodes are required in the DBP converter.

Another bridgeless PFC converter is the totem-pole bridgeless PFC (TPBP) converter. The challenge of TPBP converter is that it usually works in discontinuous-current mode (DCM) or critical-current mode (CRM) due to efficiency consideration. The poor reverse recovery time of MOSFETs are reduced in SiC MOSFETs and the on-state resistance of SiC MOSFETs are also less than the Si MOSFET. These two features allow the TPBP converter to work in continuous-current mode (CCM) with much greater efficiency. The TPBP converter has the lowest volume of components. If the two diodes in the TPBP converter are switched at ac voltage frequency, then the power loss is further reduced.

# 1.4.2 Controller consideration: Proportional-Integral Control vs Model Predictive Control

#### 1.4.2.1 The issue in controller design for load or voltage transient

In the power supply design of power converters for data center applications, the transient response capability is the key requirement. The conventional proportional-integral (PI) control is very popular in the area of power converter controller design. Usually, it has two loops: voltage loop and current loop. The challenge in regarding PI controllers is that different load power or voltage transient needs different phase and gain compensation, thus the controller design varies

from light load to heavy load. What's more, the controller complexity is increased if compensating for the aforementioned load variances.

#### *1.4.2.2 Proposed solution for transient performance*

To overcome these disadvantages, a model predictive control (MPC) is proposed in this dissertation. MPC is a real time control algorithm. It predicts the expected control variable and determines the optimized control period. The mathematical model of the controlled converter is utilized in MPC control. Different from the conventional PI control, the frequency of MPC control is variable which is dependent on the feedback. However, the maximum frequency can be less or equal to the conventional PI control, thus MPC can improve the efficiency. Another merit of MPC is that the multi-goal control can be realized. The coefficient of different goals need to be investigated.

#### 1.4.3 *Efficiency consideration*

#### 1.4.3.1 Issue in power conversion efficiency

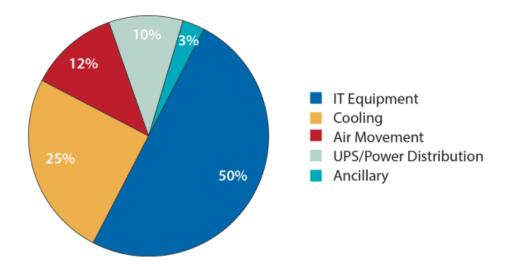

The typical total energy usage of a conventional datacenter includes the IT equipment, cooling system, uninterrupted power supply (UPS), power distribution, and ancillary systems. The detailed percentages of different power consumption is given in Fig. 1-10. The power usage effectiveness (PUE) presents the ratio of IT power to the total power, which reflects the efficiency of a datacenter infrastructure. The IT power is the power consumed by the servers. The power converter is the key factor to improve the power efficiency, thus guaranteeing lower PUE. Many researches have been working on the efficiency improvement in power converters in the data center, such as development of new power topology, soft switching, control strategy, etc. For example, there are two popular efficiency improvement methods for the isolated dc/dc power converter known as the

dual-active bridge (DAB). The first method is a current stress optimizing algorithm and the second is a flow-back power minimization strategy. The DAB is used in final stage of the proposed topology in this work.

Fig. 1-10 A Typical Power Losses in a Data Center [1.3]

#### 1.4.3.2 Proposed solution for efficiency improvement

In this dissertation, the improvement of the efficiency performance in a dual-active bridge for the data center power supply is discussed. Different from the reported methods, an accurate loss model is developed in this work for the power converter to find the expected phase-shift angle for the switches. The accurate loss model method is developed from three aspects which are the conduction loss model, switching loss model, and a high frequency transformer loss model. The better loss model leads to the more accurate prediction of phase-shift in the dual-active bridge, and thus smaller losses.

#### 1.4.4 Green data center

#### 1.4.4.1 Issue in current 'green' data centers

The integration of solar power and data centers can highly reduce the electricity cost and emissions of data centers. However, solar power is not stable and heavily depends on the environment. Battery energy storage has relatively high energy density. It is usually utilized to smooth the power output from solar systems. However, the lifetime of batteries is a major issue, leading to cost increases.

#### 1.4.4.2 Proposed solution for ac/dc voltage conversion

The ultracapacitor has a high power density and can be quickly charged and discharged without harming its lifetime. In this dissertation, the battery and ultracapacitor are used as hybrid energy storage devices to smooth the solar power. The controller design for each energy storage device is developed as well to achieve high performance.

#### 1.5 Outline

Chapter 2 describes the rectifier power stage and the control strategies for the cascaded totem -pole PFC converter. The conventional PI control design and the proposed model predictive control are developed, analyzed and compared. A discrete time mode of a cascaded totem-pole PFC converter is derived and utilized to design the model predictive control. The control goals include unity power factor, dc bus voltage balance, power loss minimization, etc.

Chapter 3 illustrates the dc/dc stage in the proposed topology. The operation principle of a dual-active bridge converter is analyzed. The single and dual phase-shift control is compared. To improve the efficiency performance, the backflow power reduction and current stress minimization methods are given. The loss model optimization method is proposed to achieve better efficiency

performance. Simulation and testing results are given to verify the proposed control strategy. For the control of transient performance, the conventional PI control and proposed K-factor control are designed and compared. A scaled-down prototype is tested to verify the proposed K-factor control.

Chapter 4 is about the solar power and hybrid energy storage integration in the data center. The controllers for solar power, battery, ultracapacitor and data center loads are developed. The simulation results are given to validate the effectiveness of the proposed topology and its control strategies.

Chapter 5 shows the system level stability analysis of a data center. The large signal model of a large-scale data center is built. The stability criterion is introduced and the stable region is given through the MATLAB/Simulink<sup>TM</sup> simulation results.

Chapter 6 is the summary of this dissertation and the outlook of the future work.

#### **1.6 Reference**

- [1.1] "United States Data Center Energy Usage Report." [Online]. Available: https://eta.lbl.gov/publications/united-states-data-center-energy.

- [1.2] "U.S. Electric System Operating Data." [Online]. Available: http://www.eia.gov/electricity/data.cfm.

- [1.3] L. A. Barroso, J. Clidaras, and U. Hölzle. The Datacenter as a Computer: An Introduction to the Design of Warehouse-Scale Machines. Morgan & Claypool Publishers, 2nd edition, 2013.

- [1.4] "Cost of Data Center Outages." [Online]. Available: http://www.datacenterknowledge.com/archives/2013/12/03/study-cost-data-centerdowntime-rising/.

- [1.5] "Ultracapacitors: Energy Storage on Steroids." [Online]. Available: https://register.gotowebinar.com/register/2974984168360253956.

- [1.6] D. Rothmund, G. Ortiz, T. Guillod and J. W. Kolar, "10kV SiC-based isolated DC-DC converter for medium voltage-connected Solid-State Transformers," in *Proc. 2015 IEEE Applied Power Electronics Conference and Exposition (APEC)*, Charlotte, NC, pp. 1096-1103, 2015.

- [1.7] B. Reese, M. Schupbach, A. Lostetter, B. Rowden, R. Saunders and J. Balda, "High voltage, high power density bi-directional multi-level converters utilizing silicon and silicon carbide (SiC) switches," *Applied Power Electronics Conference and Exposition*, 2008. APEC 2008. Twenty-Third Annual IEEE, Austin, TX, pp. 252-258, 2008.

- [1.8] P. Bakas *et al.*, "A Review of Hybrid Topologies Combining Line-Commutated and Cascaded Full-Bridge Converters," in *IEEE Transactions on Power Electronics*, vol. 32, no. 10, pp. 7435-7448, Oct. 2017.

- [1.9] S. Debnath, J. Qin, B. Bahrani, M. Saeedifard and P. Barbosa, "Operation, Control, and Applications of the Modular Multilevel Converter: A Review," in *IEEE Transactions on Power Electronics*, vol. 30, no. 1, pp. 37-53, Jan. 2015.

- [1.10] D. Y. Jung, Y. H. Ji, S. H. Park, Y. C. Jung and C. Y. Won, "Interleaved Soft-Switching Boost Converter for Photovoltaic Power-Generation System," in *IEEE Transactions on Power Electronics*, vol. 26, no. 4, pp. 1137-1145, April 2011.

- [1.11] T. Zhan, Y. Zhang, J. Nie, Y. Zhang and Z. Zhao, "A Novel Soft-Switching Boost Converter With Magnetically Coupled Resonant Snubber," in *IEEE Transactions on Power Electronics*, vol. 29, no. 11, pp. 5680-5687, Nov. 2014.

#### **CHAPTER 2**

#### DESIGN, MODELING AND CONTROL OF RECTIFIER STAGE

#### 2.1 Introduction and Motivation

#### 2.1.1 Ac/dc voltage conversion with low-frequency transformer

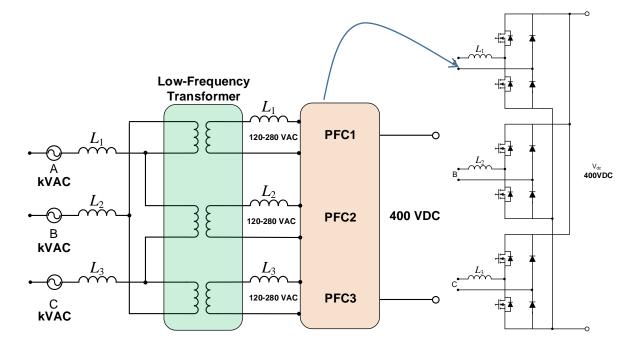

Fig. 2-1 Ac/dc Power Conversion: with Low-Frequency Transformer Application

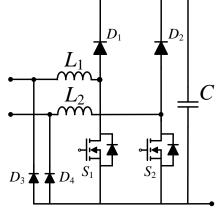

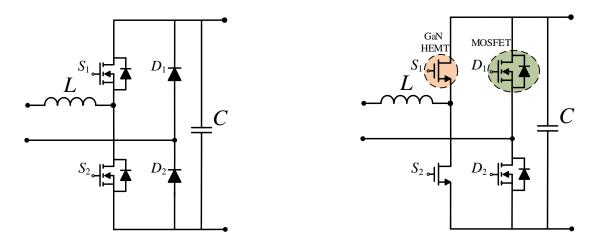

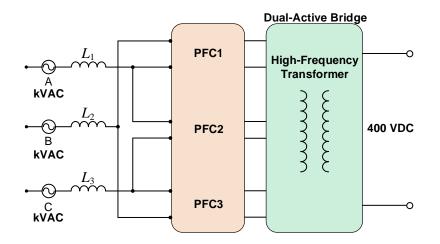

A typical system configuration is shown in Fig. 2-1. A Low-Frequency Transformer (LFT) is utilized to step down the high ac voltage to the low ac voltage, then the low ac voltage is rectified to 400 V dc. To reduce the voltage stress and increase the current carrying capability, each PFC topology can be connected in series or parallel. For single-phase ac/dc voltage conversion in data centers, the Power Factor Correction (PFC) converter is widely adopted. The conventional PFC converter is diode bridge rectifier. The efficiency needs to be improved for these devices due to the power loss from diodes. To eliminate the requirement of using a diode bridge rectifier, bridgeless PFC topologies are reviewed. There are two popular topologies: Dual-boost Bridgeless PFC (DBP) which is shown in Fig. 2-2 (a) and totem-pole bridgeless PFC (TPBP) which is given in Fig. 2-3 [2.1]-[2.3]. Both DBP and TPBP have only two switches conducting in every cycle. Compared with the classic PFC converter, the DBP converter has good efficiency performance, but it needs two more choke coils and two more diodes to reduce the large common-mode noise, thus the size and cost are increased. Due to the poor reverse recovery performance of the body diode in Si switches, the TPBP topology did not attract widespread implementation in the past, especially in the continuous-current mode (CCM). With the advent of wide bandgap devices, such as GaN or SiC switches, which have very good reverse recovery characteristics and relative low on-state resistance [2.4]-[2.6], the TPBP topology has better efficiency performance and has attracted more widespread attention [2.7]-[2.9]. If the two diodes are replaced by two active switches, the conduction loss caused by diodes can be further reduced.

(b) Dual-Boost Bridgeless PFC

Fig. 2-2 Classic Boost-type Rectifier

(a) Totem-pole Bridgeless PFC

(b) Totem-pole Bridgeless PFC with SiC and GaN Devices

Fig. 2-3 Totem-pole Bridgeless PFCs with Wide Bandgap Devices

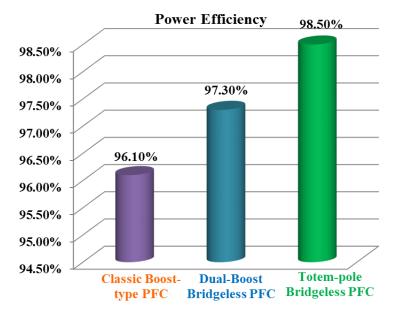

The four typical types of PFC stage are summarized in Table 2.1. To further investigate the efficiency performance of different PFC converters, the efficiency simualtion is performed in the simulator PLECS<sup>TM</sup>. Three toplogies are adopted in the simulation: (a) Classic boost-type rectifier, (b) Dual-Boost Bridgeless PFC, and (c) Totem-pole Bridgeless PFC only with one leg using SiC MOSFETs. The power loss model of the MOSFET is from Wolfspeed which is built in PLECS<sup>TM</sup>. The efficiency simulation results are shown in Fig. 2-4. It shows that the totem-pole PFC converter has the highest efficiency performance.

Fig. 2-4 Simulation Results of Efficiency Comparison: 240 V ac to 400 V dc with 5 kW Load

| Topology             | (1) Classic<br>PFC                                      | (2) Dual-Boost<br>Bridgeless PFC<br>without GaN                                                                                                                |                                                                                              | (4) Totem-pole<br>Bridgeless PFC<br>with GaN                |

|----------------------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Number of components | 7                                                       | 8                                                                                                                                                              | 5                                                                                            | 5                                                           |

| Device               | 5 Si Diodes<br>1 Si MOSFET<br>1 Inductor<br>1 Capacitor | <ul> <li>4 Si Diodes(2 are grid voltage frequency, 2 are switching frequency)</li> <li>2 Si MOSFETs</li> <li>2 Choke Inductors</li> <li>1 Capacitor</li> </ul> | 2 SiC Diodes<br>(grid voltage<br>frequency)<br>2 SiC<br>MOSFETs<br>1 Inductor<br>1 Capacitor | 4 GaN FETs or<br>4 SiC MOSFETs<br>1 Inductor<br>1 Capacitor |

| Loss on<br>Diodes    | 1 recovery and<br>2 conduction<br>losses                | 1 recovery and 2 conduction losses                                                                                                                             | 1 conduction<br>loss                                                                         | None                                                        |

| Efficiency           | 95-97%                                                  | 96-97%                                                                                                                                                         | 97-98%                                                                                       | 98-99%                                                      |

Table 2.1 Comparison of Three Typical PFC Converters

## 2.1.2 Ac/dc voltage conversion with high-frequency transformer

The disadvantage of Fig. 2-1 is the necessity of a large foot print, high weight and bulky transformer. High-frequency transformers attract attention due to their small size, light weight and high power density. They also can work as both a bus bar voltage regulator and a reactive power compensator. The challenge of using high-frequency transformers is that the control complexity is increased and more semiconductor devices are needed. However, the cost of high-frequency transformers is high and the efficiency is somehow lower than the low-frequency transformer. The system configuration with a medium- or high-frequency transformer is given in Fig. 2-5.

Fig. 2-5 System Configuration Using Medium- or High-frequency Transformer

The PFC converter in high-frequency transformer applications can be divided to three types as shown below.

## 2.1.2.1 Non-modular topology

In the non-modular topology, it usually requires high breakdown voltage rated switches to rectify high ac voltage to dc voltage. The advantage of this topology is that less switches are required and which leads to less complexity and control effort. For example, a five-level ac/dc

topology is given in Fig. 2-6, which is reported by ETH Zurich [2.10]-[2.12]. The voltage stresses of switches are relatively high and it usually requires many switches connected in series to increase the breakdown voltage. Thus, the auxiliary driver circuits are required to symmetrically turn-on or off the switches.

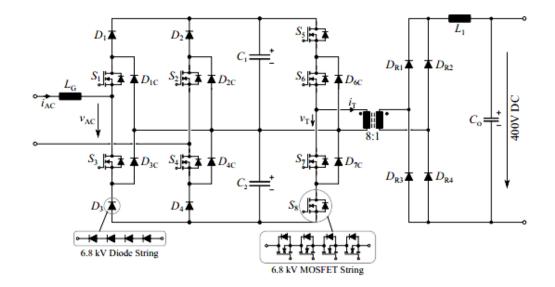

Fig. 2-6 Five-level NPC ac/dc Topology

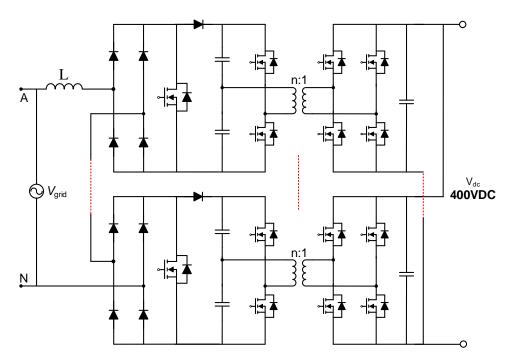

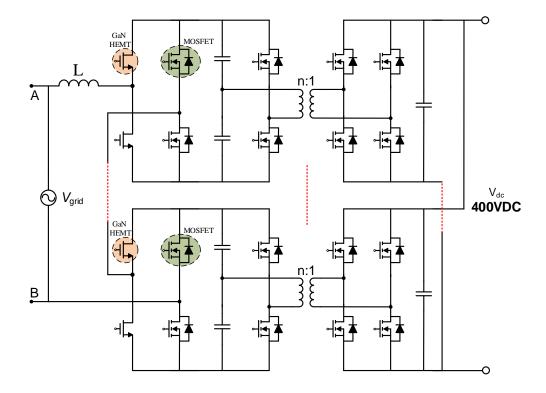

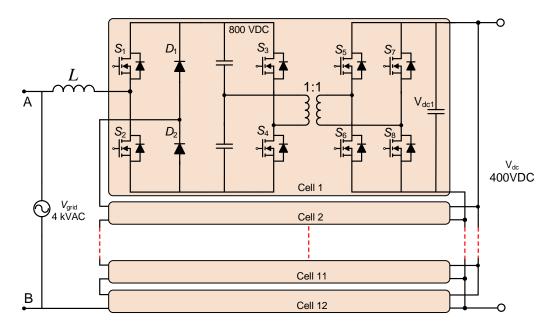

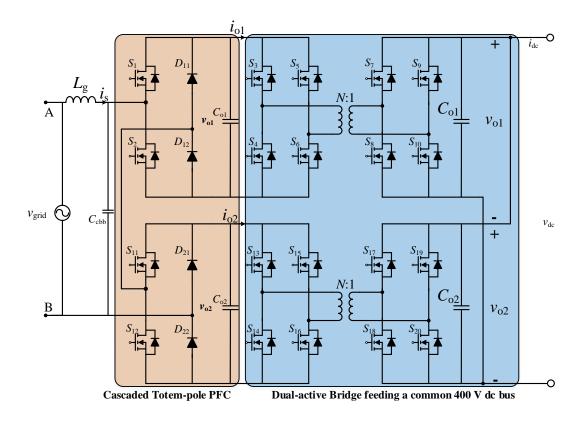

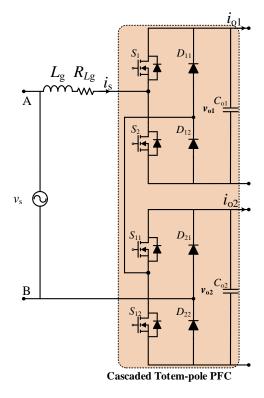

### 2.1.2.2 Modular multilevel topology

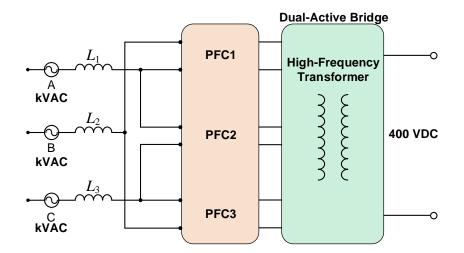

The modular multilevel topology attracts attention due to it being scalable and modular. The voltage stress is decided by the amplitude of input ac voltage level and the levels of modulation. Low voltage switches can be utilized in this topology. Three typical topologies are shown in Fig. 2-7. To reduce the number of switches and further improve the efficiency performance, a cascaded bridgeless totem-pole PFC through a dual-active bridge feeding a common 400-V dc bus is proposed as shown in Fig. 2-7 (b) and (c). Different from most of the recent literature, which is focused on the single TPBC or interleaved TPBC [2.13]-[2.15], is that there are several totem-pole bridgeless PFC converters connected in series. The dc voltage will be divided by the number of PFC converters. Hence, voltage stresses of the switches can be reduced to a more managable value.

For example, if the PFC output voltage is controlled to 400 V, then 650 V rated devices can be utilized. The output voltage of PFC converters are integrated with dual-active bridges connected in parallel to increase the current capability. The galvanic isolation is provided by high-frequency transformer. There are two differences between Fig. 2-7 (b) and (c): (1) Si MOSFET is replaced by wide bandgap devices such as GaN or SiC, to overcome the reverse recovery problem; (2) Diodes are replaced by Si MOSFETs for better efficiency performance.

In the dc/dc stage, cascaded totem-pole converters convert grid voltages to primary dc-bus voltages  $v_{0i}$  dual-active bridges, whose outputs are connected in parallel to increase the current capability, produce a secondary dc output voltage. In the dual-active bridge stage, it can be a half-bridge or a full-bridge on the primary or secondary side. Regarding the kV-level input ac voltage, the full-bridge of the DAB primary side may be replaced by a half-bridge topology to further reduce the high-frequency transformer turns ratio.

(a) Series Diode Bridge and Boost PFC

(b) Proposed Series Totem-pole Bridgeless PFC with SiC MOSFET

(c) Proposed Series Totem-pole Bridgeless PFC with GaN HEMT and Si MOSFET

Fig. 2-7 Modular Multilevel PFC Converters

## 2.1.2.3 Hybrid topology

As shown the configuration of Fig. 2-8 [2.11], the input ac of the hybrid topology is rectified by a diode full bridge, then through a modular isolated dc/dc converter to generate the dc bus to loads. The diodes, with appropriate voltage ratings, are required in the hybrid topology.

Fig. 2-8 Multi-Cell Boost Topology with Four Input Series Output Parallel Connected Converter In summary, a modular multilevel H-bridge converter topology and series dual-boost bridgeless PFC are investigated in this dissertation. Compared with existing topologies in Fig. 2-6,

Fig. 2-7(a) and Fig. 2-8, along with the modularity and scalability, the proposed topology has additional merits such as:

(a) Better reverse recovery performance of diode by utilizing wide bandgap devices to improve efficiency performance;

(b) In each cell, two switches are operated at line frequency thereby further reducing power losses;

(c) Fewer active switches. The auxiliary gate driver circuit and power supply are reduced;

(d) Low complexity and low control effort.

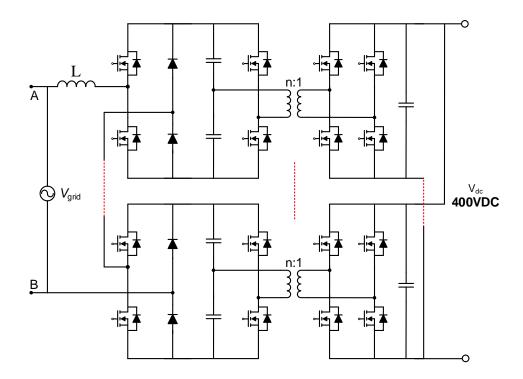

#### 2.1.2.4 The proposed topology in low, medium and high power rated data centers

According to [2.16] and [2.17], the sizes of data centers vary widely. Two thirds of data centers in US are rated at less than 1 MW critical power. To reduce the construction and operation cost of data centers, multiple companies are sharing one data center, the resulting arrangement is called co-location data centers. The critical power of co-location data center is usually rated from 10-20 MW. Very few data centers exceed a power rating of 30 MW. At different power ratings, the prosed topology is modular to achieve high power capability. Three examples are given in the flowing sections for 1 MW, 10 MW and 30 MW power data centers.

### 2.1.2.4.1 Low power rating data center ( $\leq 1 MW$ )

The proposed topology for a 1 MW data center is shown in Fig. 2-9. If the grid side voltage is 2.4 kV per phase, then the minimum dc bus voltage in the rectifier stage is 3.771 kV. The dc reference voltage of each totem-pole PFC is set as 800 V, thus at least five cells of totem-pole PFC converters connected in series to realize 800 V dc output in each PFC stage. To step down 800 V to 400 V and provide galvanic isolation, a dual-active bridge converter is applied in dc/dc stage. The 1.2 kV or 1.7 kV SiC MOSFET can be utilized in the proposed topology.

Fig. 2-9 Proposed Topology for 1 MW Power Data Center

The rectifier dc bus voltage is calculated below:

The rms voltage of the input ac voltage  $v_{ac.rms}$  is 2400 V, if the modulation index *M* is selected as 0.9, then the minimum voltage of the rectifier dc bus should be:

$$v_{ac2dc} = \frac{\sqrt{2}v_{ac.rms}}{M} = \frac{\sqrt{2} \times 2400}{0.9} V = 3.771 kV$$

(2-1)

The reference voltage of each PFC dc bus is selected as 800 V, then the stages of PFC converter is:

$$n_{PFC,ideal} = \frac{3.771kV}{800V} = 4.71 \tag{2-2}$$

So at least a 5-stage PFC is required. In the three-phase ac grid connected to a 1 MW data center with a desired efficiency of 99%, the power rating of each stage of the dual-active bridge or PFC converter is:

$$p_{PFC,DAB} = \frac{1MW}{3 \times 99\%} = 0.3367MW \tag{2-3}$$

Then the rms current rating for each phase is calculated as shown below:

$$i_{ac,rms} = \frac{p_{PFC,DAB}}{v_{ac,rms}} = \frac{0.3367MW}{2400V} = 140.3A$$

(2-4)

The peak current is:

$$i_{ac,peak} = \sqrt{2}i_{ac,rms} = \sqrt{2} \times 140.3A = 198.4A$$

(2-5)

If the secondary side dc bus voltage of the dual-active bridge is 400 V, then the current rating of the switching is:

$$i_{DAB,out} = \frac{p_{PFC,DAB}}{n_{PFC}v_{ac,ms}} = \frac{0.3367MW}{5 \times 400V} = 168.35A$$

(2-6)

The voltage/current stress and the available manufacturer of switches are summarized in Table 2.2.

| Switch            | <i>S</i> <sub>1</sub> - <i>S</i> <sub>2</sub> , <i>S</i> <sub>3</sub> - <i>S</i> <sub>4</sub> | $D_1 \sim D_2$ | <i>S</i> 5- <i>S</i> 6, <i>S</i> 7- <i>S</i> 8 |  |

|-------------------|-----------------------------------------------------------------------------------------------|----------------|------------------------------------------------|--|

| Voltage<br>stress | 800 V                                                                                         | 800 V          | 400V                                           |  |

| Current<br>stress | 198.4 A                                                                                       | 198.4 A        | 168.35 A                                       |  |

| Manufacturer      | CREE, Wolfspeed                                                                               | Powerex Inc.   | CREE, Wolfspeed                                |  |

| Part No.          | CAS300M17BM2                                                                                  | LS411860       | CAS300M17BM2                                   |  |

| Voltage<br>Rating | 1.7 kV                                                                                        | 1.8 kV         | 1.7 kV                                         |  |

| Current<br>Rating | 225 A(90 °C), 325 A(25 °C)                                                                    | 600 A(25 °C)   | 225 A(90 °C), 325<br>A(25 °C)                  |  |

# Table 2.2 Switch Specification in 1 MW Data Center

|                   | ROHM                       | IXYS                                         | ROHM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------|----------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Manufacturer      |                            | -000                                         | and the second s |

| Part No.          | BSM300D12P2E001            | MDO500-22N1                                  | BSM300D12P2E001                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Voltage<br>Rating | 1.2 kV                     | 1.8 kV                                       | 1.2 kV                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Current<br>Rating | 300 A(60°C)                | 560 A(25 °C)                                 | 300 A(60 °C)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

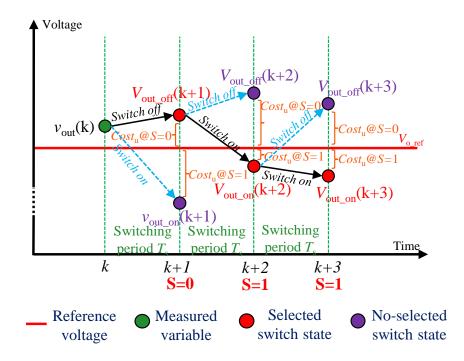

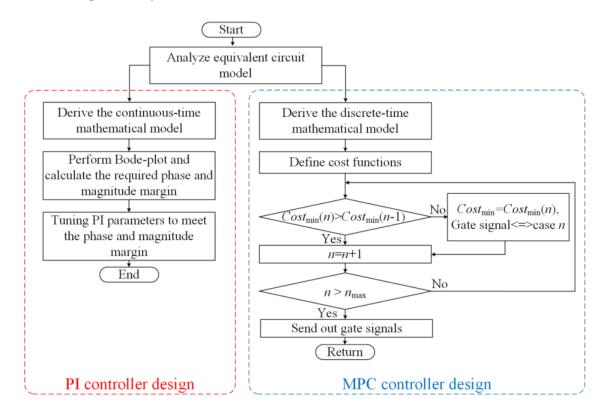

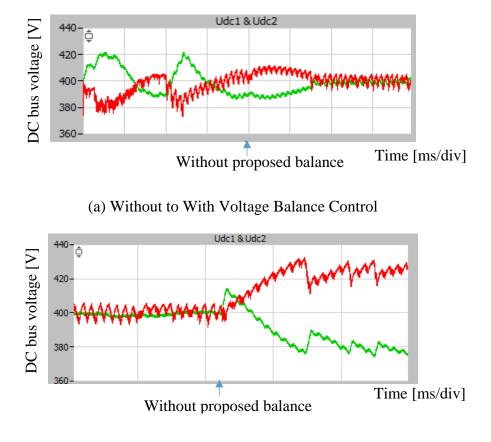

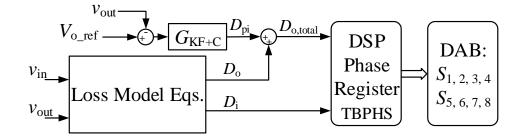

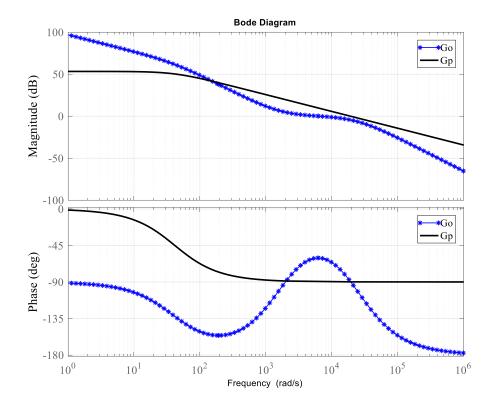

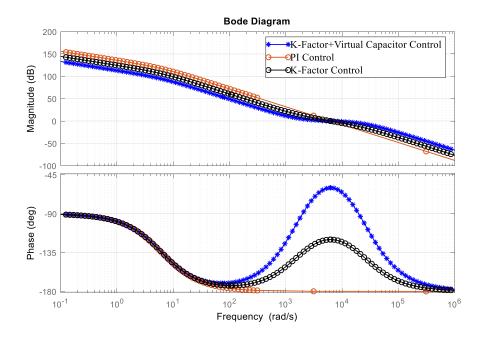

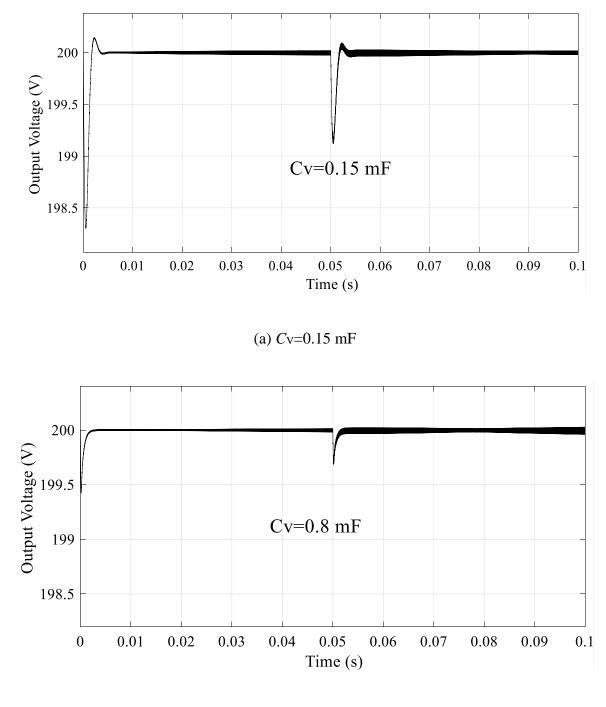

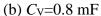

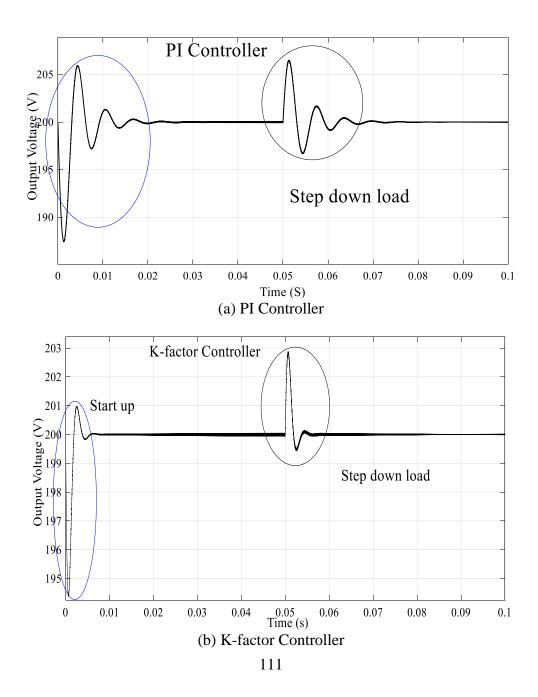

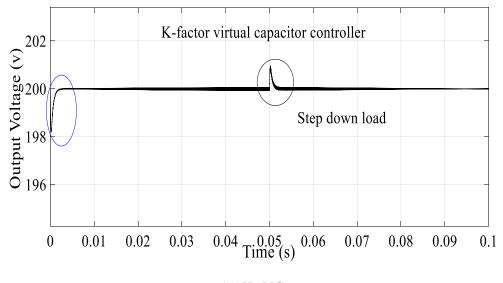

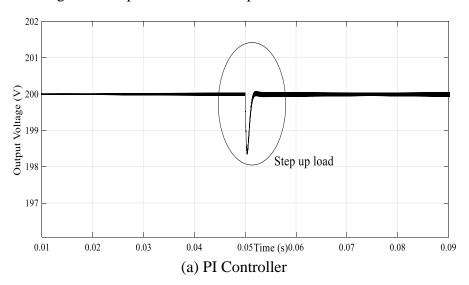

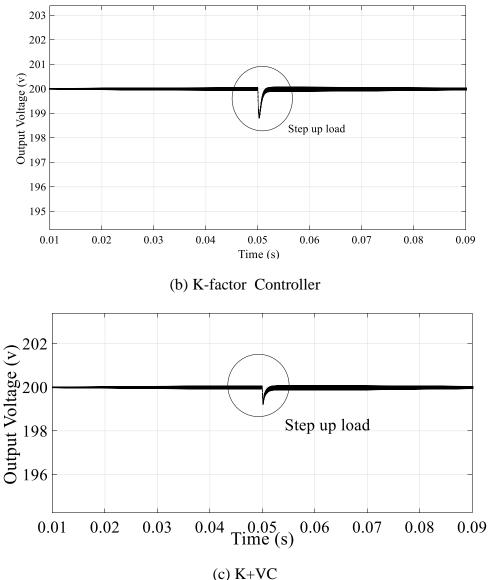

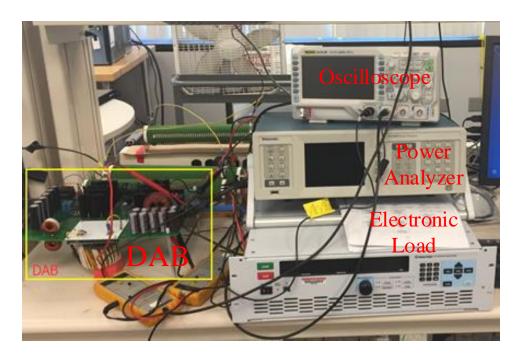

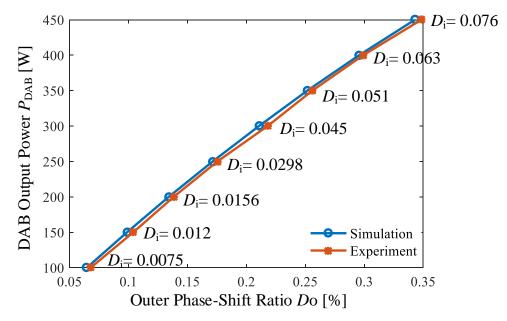

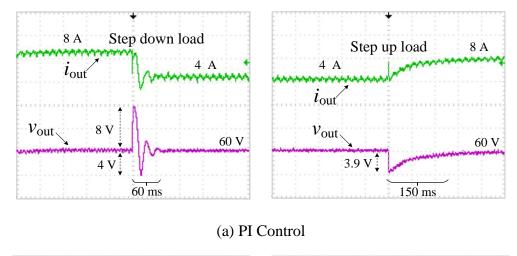

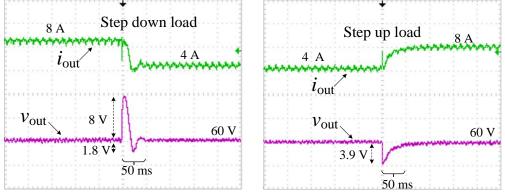

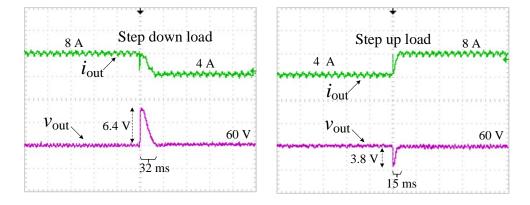

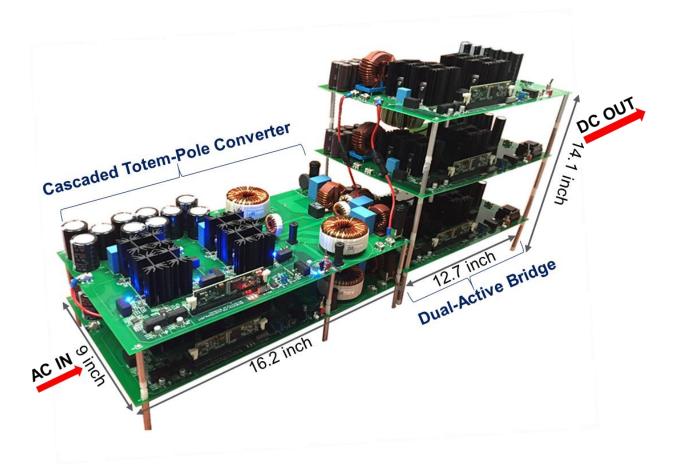

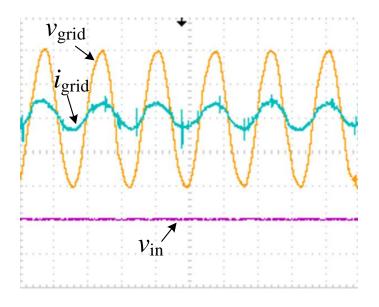

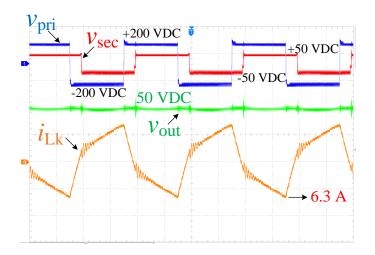

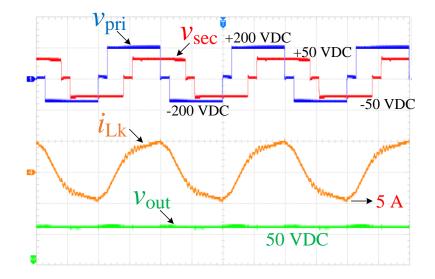

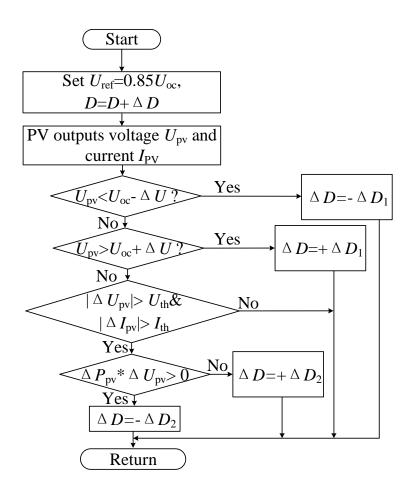

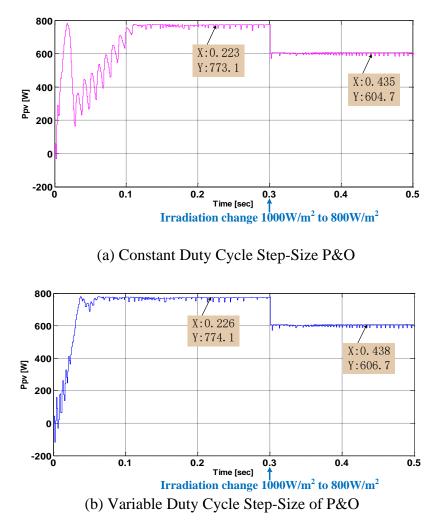

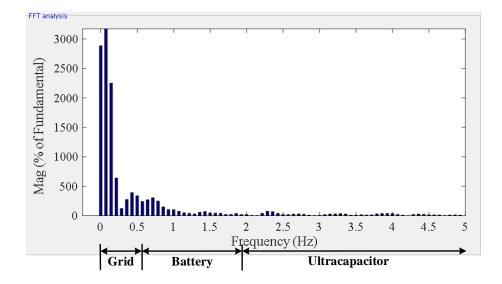

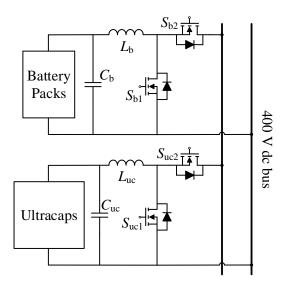

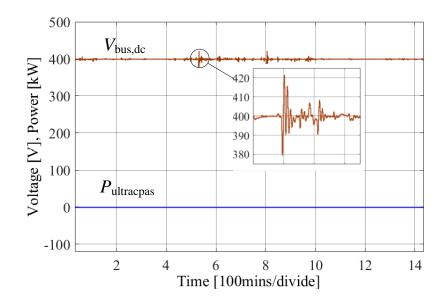

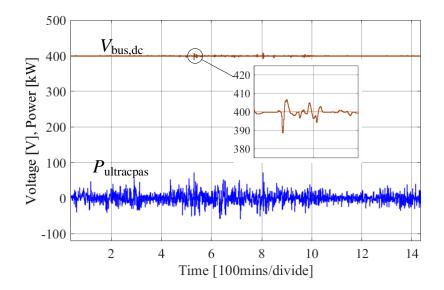

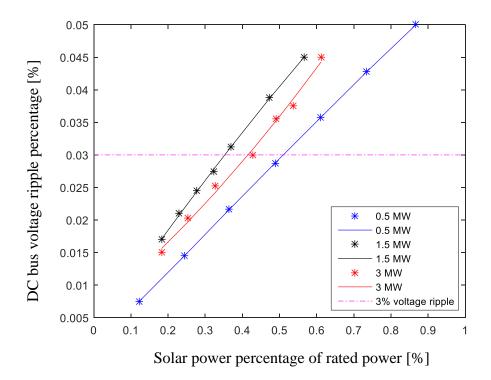

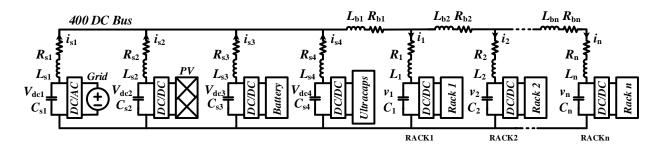

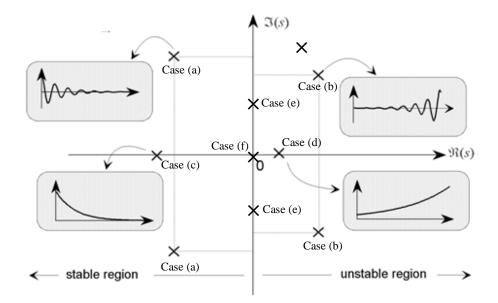

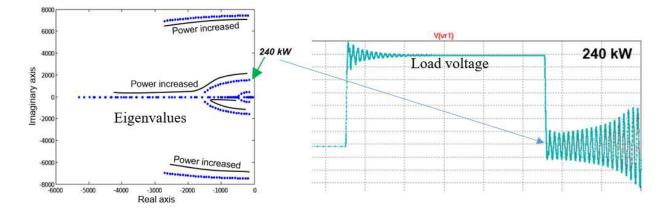

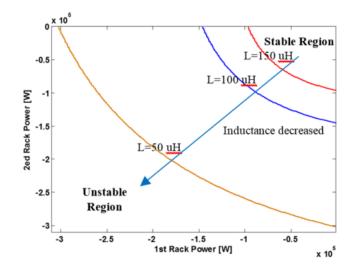

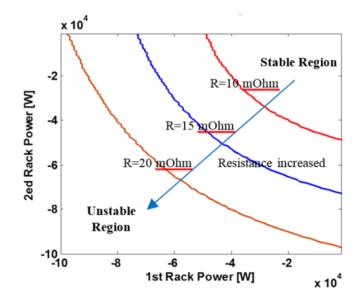

|                   | Semikron                   | Microsemi Power<br>Products Group            | Semikron                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |