# University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

5-2016

# Achieving a better balance between productivity and performance on FPGAs through Heterogeneous Extensible Multiprocessor Systems

Abazar Sadeghian University of Arkansas, Fayetteville

Follow this and additional works at: http://scholarworks.uark.edu/etd Part of the <u>Digital Circuits Commons</u>, and the <u>Other Electrical and Computer Engineering</u> <u>Commons</u>

#### **Recommended** Citation

Sadeghian, Abazar, "Achieving a better balance between productivity and performance on FPGAs through Heterogeneous Extensible Multiprocessor Systems" (2016). *Theses and Dissertations*. 1584. http://scholarworks.uark.edu/etd/1584

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, ccmiddle@uark.edu.

Achieving a better balance between productivity and performance on FPGAs through Heterogeneous Extensible Multiprocessor Systems

> A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Computer Engineering

> > By

## Abazar Sadeghian Iran University of Science and Technology Master of Science in Electrical and Electronics Engineering, 2007

## May 2016 University of Arkansas

This thesis is approved for recommendation to the Graduate Council

Dr. David Andrews, Ph.D. Thesis Director

Dr. Miaoqing Huang, Ph.D. Committee Member Dr. Gordon Beavers, Ph.D. Committee Member

#### Abstract

Field Programmable Gate Arrays (FPGAs) were first introduced circa 1980, and they held the promise of delivering performance levels associated with customized circuits, but with productivity levels more closely associated with software development. Achieving both performance and productivity objectives has been a long standing challenge problem for the reconfigurable computing community and remains unsolved today. On one hand, Vendor supplied design flows have tended towards achieving the high levels of performance through gate level customization, but at the cost of very low productivity. On the other hand, FPGA densities are following Moore's law and and can now support complete multiprocessor system architectures. Thus FPGAs can be turned into an architecture with programmable processors which brings productivity but sacrifices the peak performance advantages of custom circuits. In this thesis we explore how the two use cases can be combined to achieve the best from both.

The flexibility of the FPGAs to host a heterogeneous multiprocessor system with different types of programmable processors and custom accelerators allows the software developers to design a platform that matches the unique performance needs of their application. However, currently no automated approaches are publicly available to create such heterogeneous architectures as well as the software support for these platforms. Creating base architectures, configuring multiple tool chains, and repetitive engineering design efforts can and should be automated. This thesis introduces Heterogeneous Extensible Multiprocessor System (HEMPS) template approach which allows an FPGA to be programmed with productivity levels close to those associated with parallel processing, and with performance levels close to those associated with customized circuits. The work in this thesis introduces an ArchGen script to automate the generation of HEMPS systems as well as a library of portable and self tuning polymorphic functions. These tools will abstract away the HW/SW co-design details and provide a transparent programming language to capture different levels of parallelisms, without sacrificing productivity or portability.

## Acknowledgment

I would like to thank Dr. David Andrews for giving me the opportunity to work in his research laboratory. Additionally, I would like to thank my thesis committee, Dr. Huang and Dr. Beavers. Finally, I would like to thank my labmates in the CSDL lab for all the team work we had during the last 5 years.

# Contents

| 1 | Mot  | ivation                                                           | 1  |

|---|------|-------------------------------------------------------------------|----|

|   | 1.1  | Abstracting away the complexities of CAD tools                    | 6  |

|   | 1.2  | Abstracting away the details of HW platform: Portable code        | 8  |

|   | 1.3  | Easy integration of accelerators into the existing system         | 9  |

|   |      |                                                                   | 10 |

|   |      | 6                                                                 | 10 |

|   | 1.4  |                                                                   | 12 |

| 2 | Intr | oduction                                                          | 15 |

|   | 2.1  | The need for making FPGA's accessible to SW developers            | 16 |

|   | 2.2  | Dark Silicon challenge                                            | 17 |

|   | 2.3  | Modeling and abstracting the accelerators in a CHMPS architecture | 18 |

|   | 2.4  |                                                                   | 24 |

|   | 2.5  |                                                                   | 28 |

|   | 2.6  |                                                                   | 34 |

|   | 2.7  | 1                                                                 | 39 |

|   | 2.8  |                                                                   | 40 |

| 3 | Bac  | kground                                                           | 43 |

| C | 3.1  |                                                                   | 46 |

|   | 3.2  |                                                                   | 49 |

|   | 3.3  |                                                                   | 51 |

|   | 3.4  |                                                                   | 55 |

|   | 3.5  | <b>.</b>                                                          | 56 |

|   |      |                                                                   | 56 |

|   |      |                                                                   | 57 |

|   |      |                                                                   | 59 |

|   |      |                                                                   | 64 |

|   |      |                                                                   | 64 |

|   |      | 1                                                                 | 66 |

|   |      |                                                                   | 66 |

|   |      | 1                                                                 | 69 |

|   |      | i C                                                               | 71 |

|   |      |                                                                   | 74 |

|   |      |                                                                   | 75 |

|   |      |                                                                   | 76 |

| 4 | Svet | em Design                                                         | 78 |

| • | 4.1  | 8                                                                 | 80 |

|   | 111  | •                                                                 | 80 |

|   |      |                                                                   | 83 |

|   |      |                                                                   | ~~ |

|    |        | 4.1.3 Data path                                                                            | 1 |

|----|--------|--------------------------------------------------------------------------------------------|---|

|    | 4.2    | Automating the generation of a HEMPs system                                                | 5 |

|    | 4.3    | Polymorphic functions library                                                              |   |

| 5  | Resi   | llts 11                                                                                    | 1 |

|    | 5.1    | Extensible processor node Verification                                                     | 1 |

|    |        | 5.1.1 HAL comparison                                                                       |   |

|    |        | 5.1.2 Performance                                                                          |   |

|    | 5.2    | HEMPS platform results                                                                     |   |

|    |        | 5.2.1 Scalability                                                                          |   |

|    |        | 5.2.2 Synthesis time and resource usage                                                    |   |

|    |        | 5.2.3 Partial reconfiguration                                                              |   |

|    | 5.3    | Polymorphic functions                                                                      |   |

|    | 5.5    | 5.3.1         Portability proof         12                                                 |   |

|    |        | 5.3.1       Fortability proof       121         5.3.2       Performance analysis       121 |   |

|    |        | •                                                                                          |   |

|    |        | 5.3.3 Evaluating Run Time Profiling                                                        | I |

| 6  | Con    | clusion 14                                                                                 | 4 |

|    | 6.1    | Research Contributions                                                                     | 5 |

|    | 6.2    | Future Work                                                                                |   |

| Re | eferen | ces 14                                                                                     | 9 |

# List of Figures

| 1.1  | Three areas that should be addressed to achieve abstraction in FPGAs | 2  |

|------|----------------------------------------------------------------------|----|

| 1.2  | The entire flow from C code to final binary file                     | 4  |

| 1.3  | Loosely coupled accelerators Vs. Extensible processor.               | 12 |

| 2.1  | Extensible processor node enables                                    | 16 |

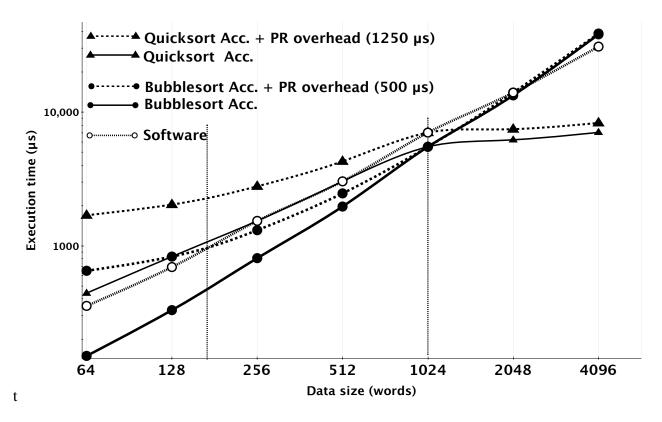

| 2.2  | Performance Vs. complexity of the system                             | 27 |

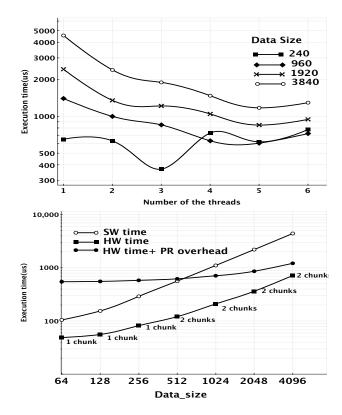

| 2.3  | Performance of different implemnation of Sort in HW and SW           | 37 |

| 2.4  | Data level parallelism Vs. Thread level parallelism                  | 38 |

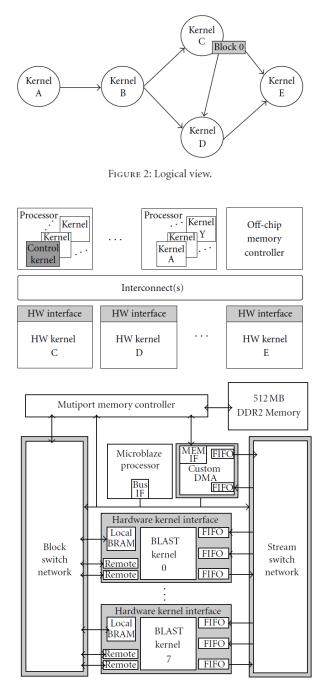

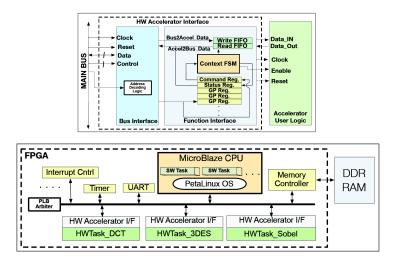

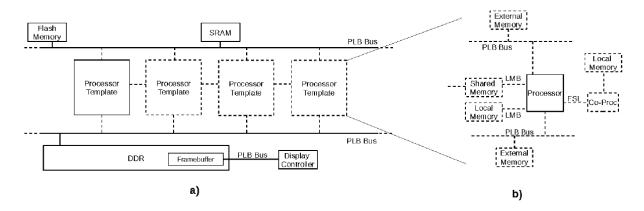

| 3.1  | RedSharc System [41]                                                 | 58 |

| 3.2  | FUSE [39]                                                            | 59 |

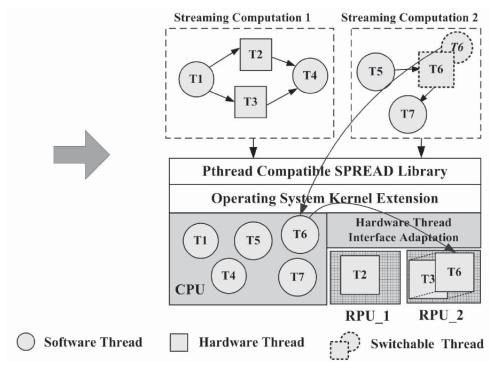

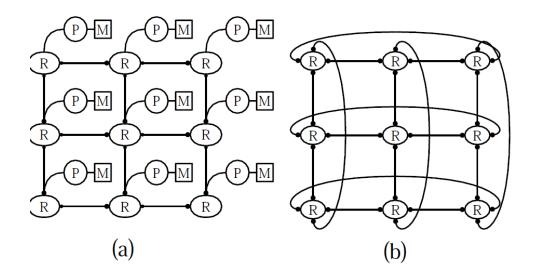

| 3.3  | SPREAD [65]                                                          | 60 |

| 3.4  | SPREAD system with three HW accelerators [65]                        | 61 |

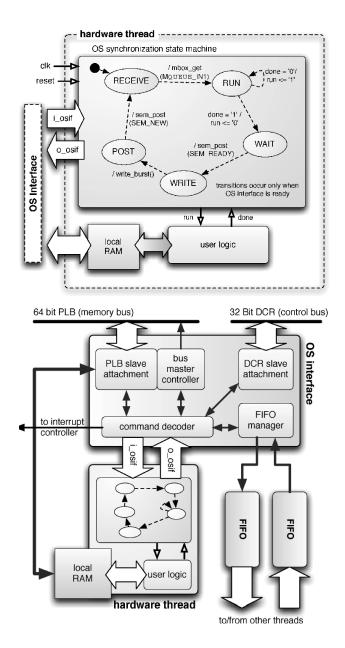

| 3.5  | Left: A HW thread in ReconOS . Right:OSIF interface [45]             | 63 |

| 3.6  | Left: ReconOS Two HW threads. Right: thread-to-thread interface [45] | 65 |

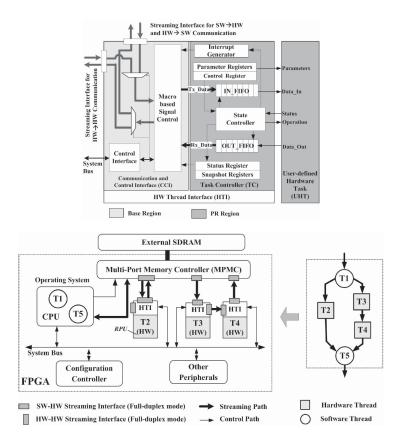

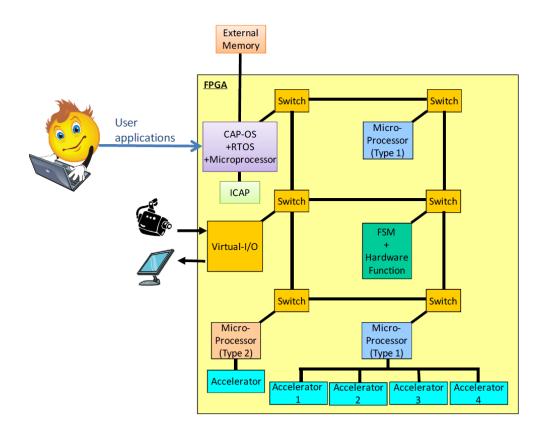

| 3.7  | Left: High level view of CAP-OS [32]                                 | 67 |

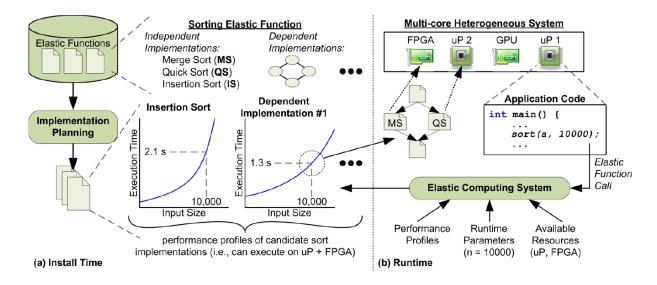

| 3.8  | Elastic Computing [67]                                               | 70 |

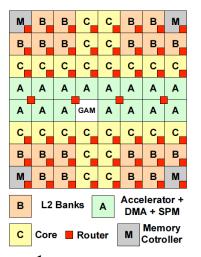

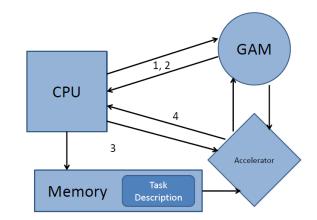

| 3.9  | ARC approach [24]                                                    | 72 |

| 3.10 | The processor template in TBES [25]                                  | 73 |

| 3.11 | TBES tool chain [25]                                                 | 73 |

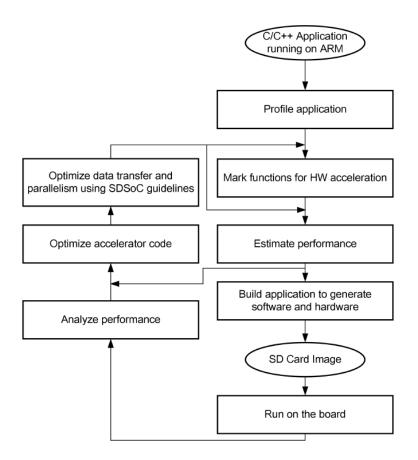

| 3.12 | SDSoC environmental flow [71]                                        | 75 |

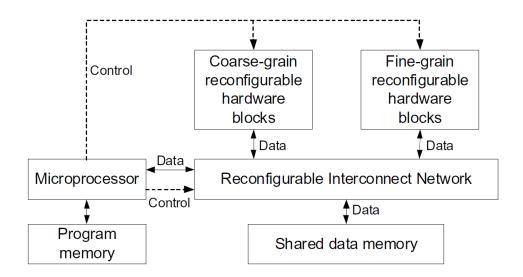

| 3.13 | ICN approach [46]                                                    | 76 |

| 3.14 | Generic reconfigurable platform architecture in [30]                 | 77 |

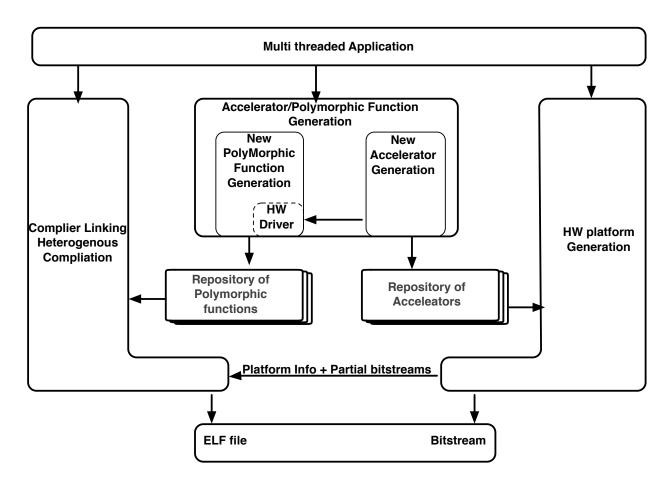

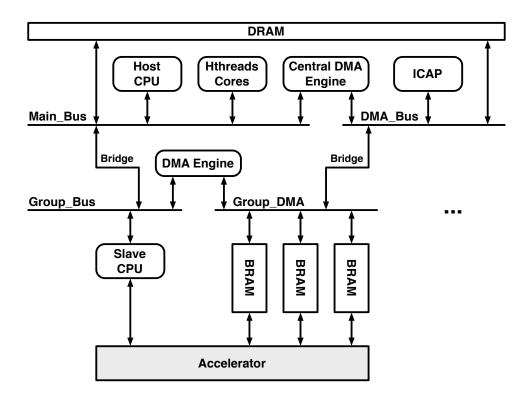

| 4.1  | General flow of HW/SW codesign in a HEMPS system                     | 79 |

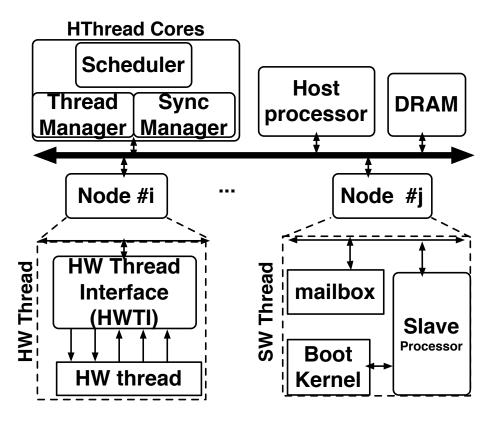

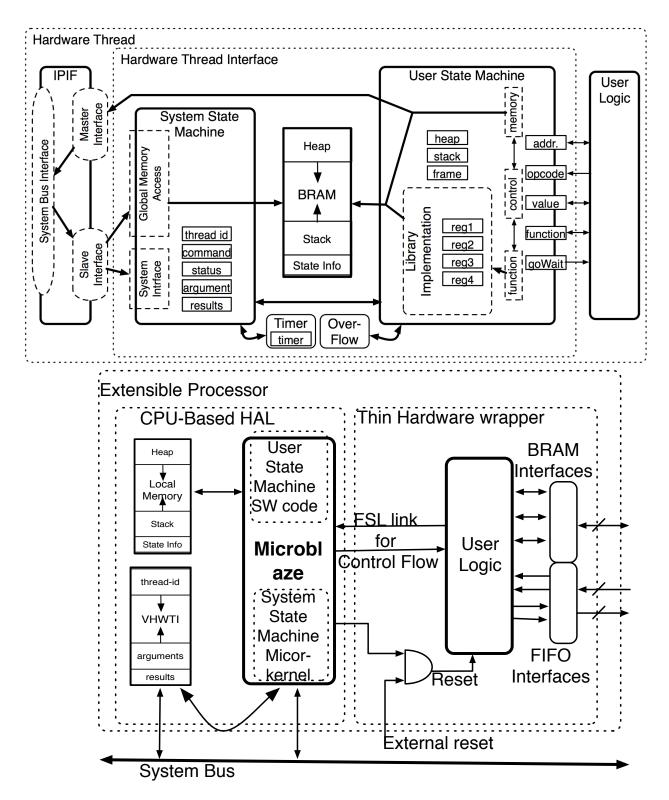

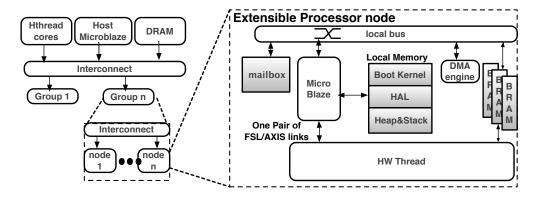

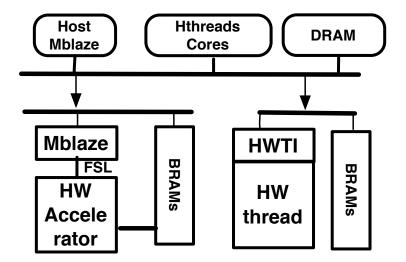

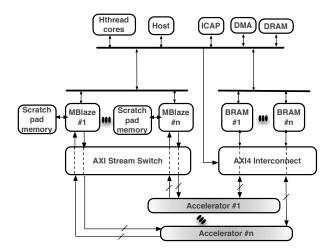

| 4.2  | High level view of Hthread system                                    | 81 |

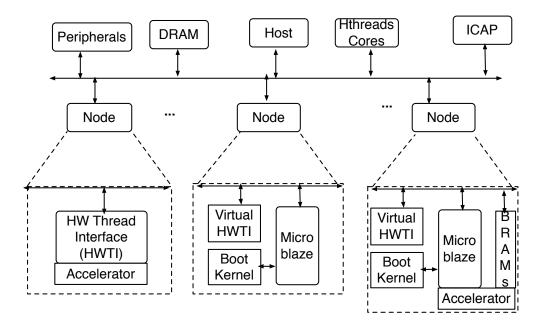

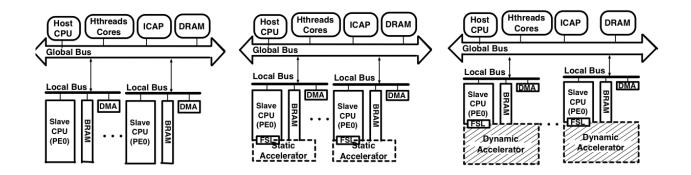

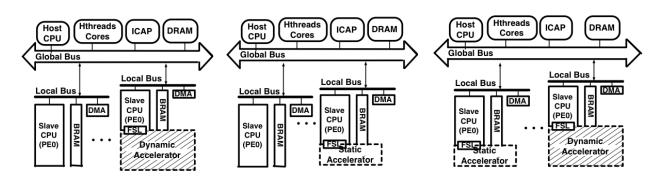

| 4.3  | A Typical Hthread system with different computational nodes        |

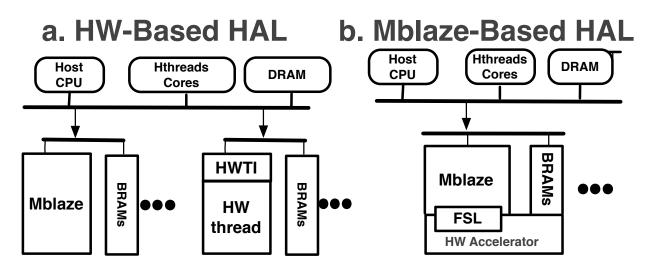

|------|--------------------------------------------------------------------|

| 4.4  | a. HWTI b.Micoblaze-based HWTI                                     |

| 4.5  | HWTI Implementation [15] Vs. Extensible processor                  |

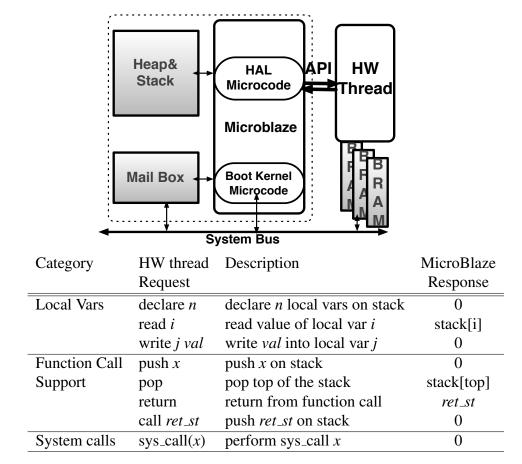

| 4.6  | API protocol Across FSL links between MicroBlaze and HW thread     |

| 4.7  | Snippet of VHDL Wrapper Code                                       |

| 4.8  | Snippet of Operating System Interface Code                         |

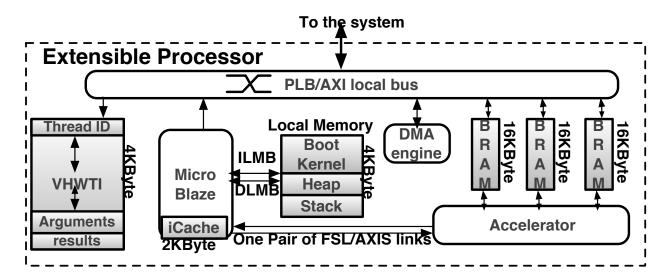

| 4.9  | Extensible processor node with only one accelerator                |

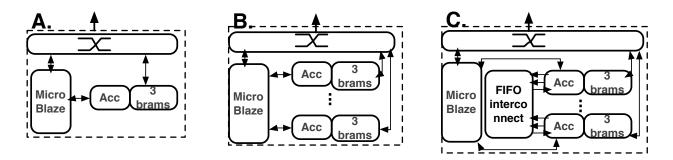

| 4.10 | The three potential architectures of an extensible processor node  |

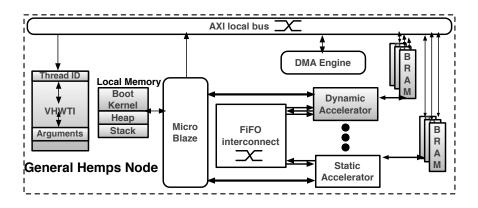

| 4.11 | Architecture of a Simple HEMPs node                                |

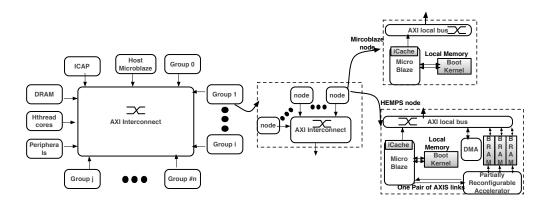

| 4.12 | Right: The HEMPS platform. Left: Extensible Processor Node         |

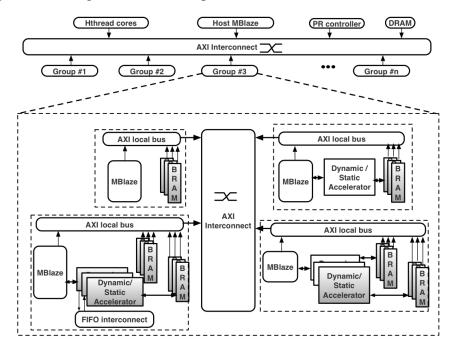

| 4.13 | The overall architecture of a HEMPS system                         |

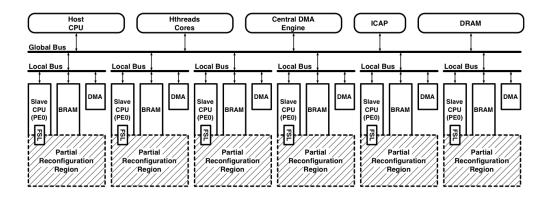

| 4.14 | The high level view architecture of a HEMPS HW platform            |

| 4.15 | Node Architecture                                                  |

| 4.16 | A HEMPS system with 6 nodes                                        |

| 4.17 | The high level specification config file                           |

| 4.18 | Archgen in the cloud                                               |

| 4.19 | Archgen in the cloud: Customizing the nodes                        |

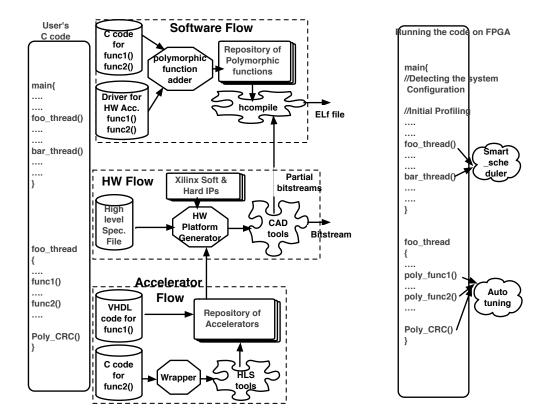

| 4.20 | SW toolchain for polymorphic functions                             |

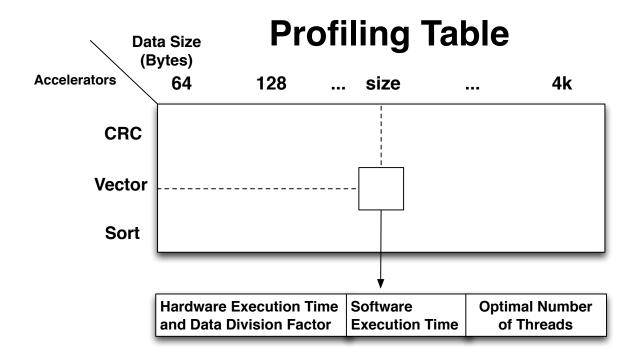

| 4.21 | Profiling table                                                    |

| 4.22 | A Multi-threaded application with polymorphic functions            |

| 4.23 | The thread running on PE #n calls a polymorphic function           |

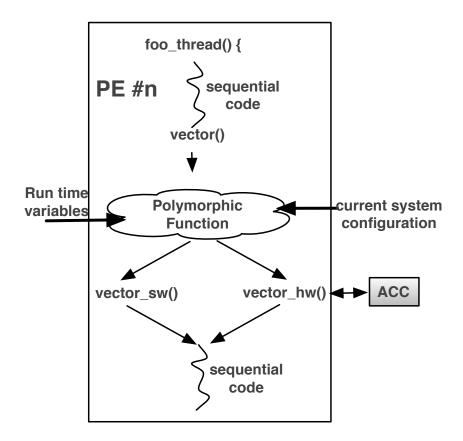

| 4.24 | Designing an Accelerator using FSM                                 |

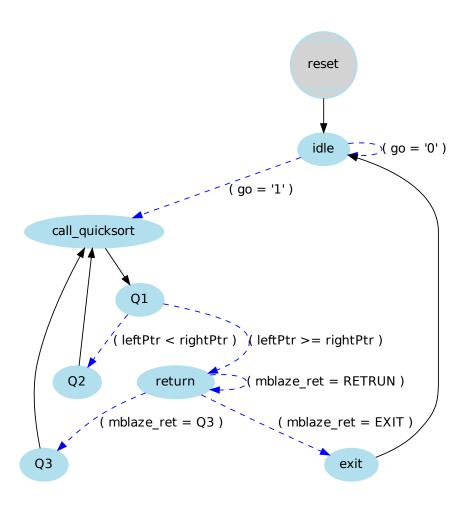

| 4.25 | Designing an Accelerator using Vivado HLS                          |

| 5.1  | The test platform built for evaluation                             |

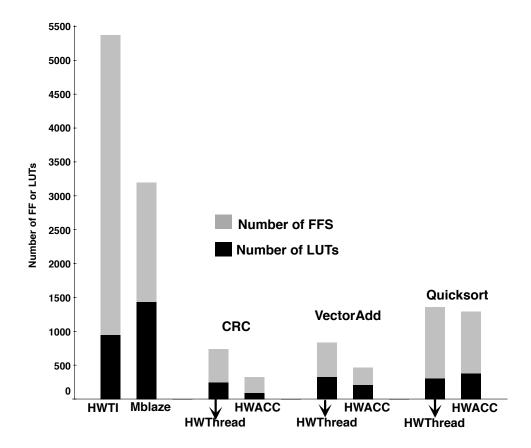

| 5.2  | Resource utilization comparison                                    |

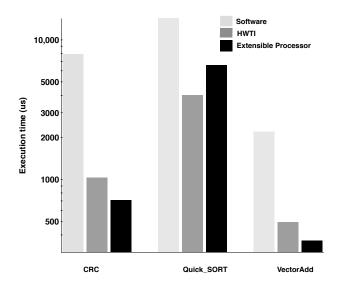

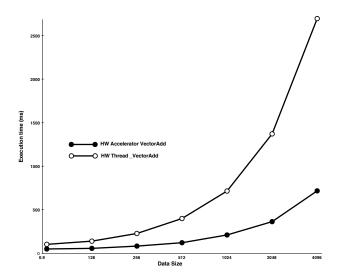

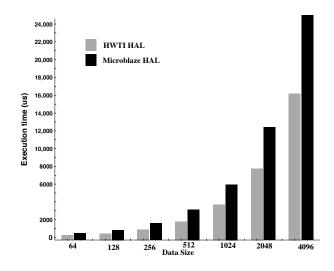

| 5.3  | Execution time for SW threads, HW threads and extensible processor |

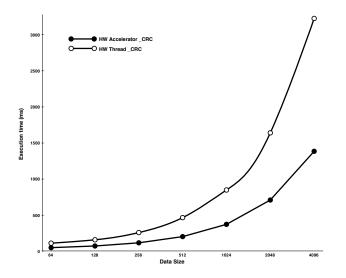

| 5.4  | CRC HW thread Vs. CRC hw accelrator                                |

| 5.5  | Vector HW thread Vs. CRC Vector accelrator                                                                            |

|------|-----------------------------------------------------------------------------------------------------------------------|

| 5.6  | Quicksort HW thread Vs. Quicksort hw accelrator                                                                       |

| 5.7  | Performance comparison for Quicksort HW thread                                                                        |

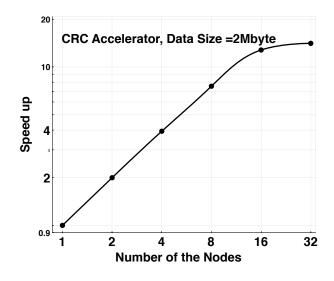

| 5.8  | CRC, strong scalability                                                                                               |

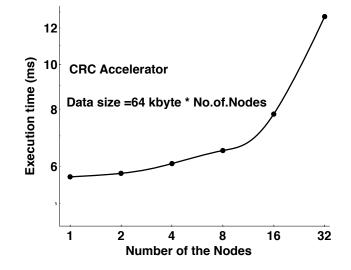

| 5.9  | CRC, Weak scalability                                                                                                 |

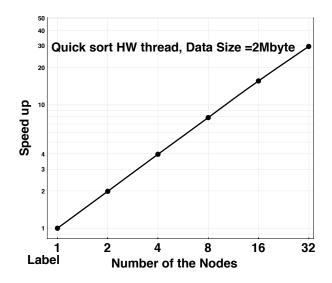

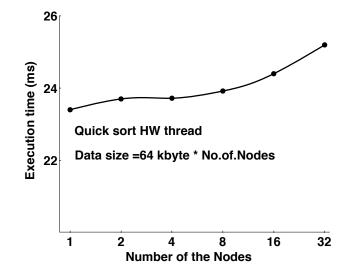

| 5.10 | Quicksort, strong scalability                                                                                         |

| 5.11 | Quicksort, Weak scalability                                                                                           |

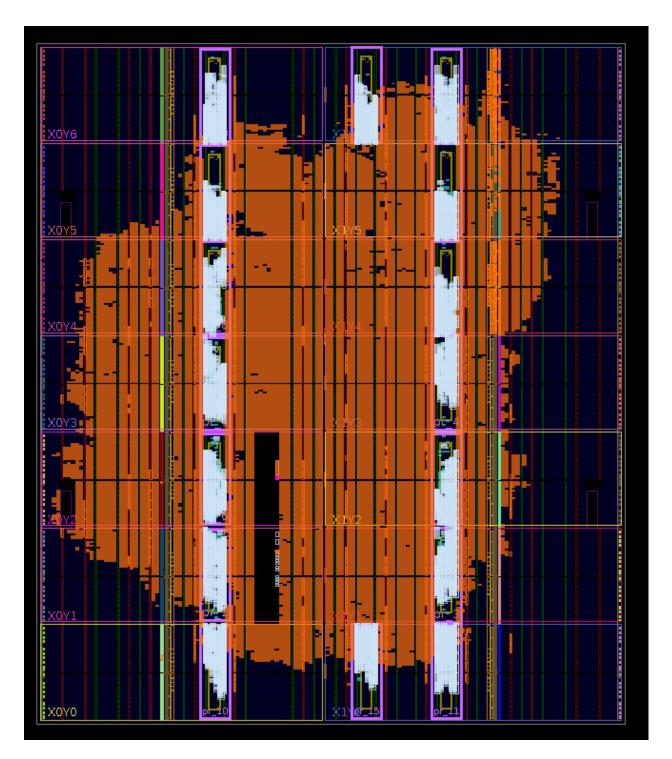

| 5.12 | Floorplan of a PR system with 16 nodes                                                                                |

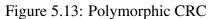

| 5.13 | Polymorphic CRC                                                                                                       |

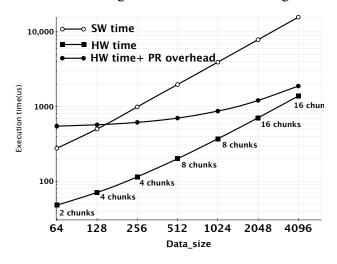

| 5.14 | Polymorphic VECTOR                                                                                                    |

| 5.15 | Polymorphic SORT                                                                                                      |

| 5.16 | A simple program creating threads that invoke poly_crc function                                                       |

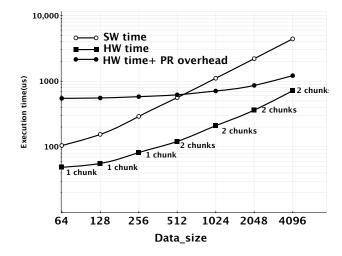

| 5.17 | A mixed system with 6 nodes                                                                                           |

| 5.18 | A system with 6 nodes and no accelerators                                                                             |

| 5.19 | A static system with 6 nodes                                                                                          |

| 5.20 | A dynamic system with 6 nodes                                                                                         |

| 5.21 | Platfrom configuration 1                                                                                              |

| 5.22 | Platfrom configuration 2                                                                                              |

| 5.23 | Pseudo code for the synthetic benchmark                                                                               |

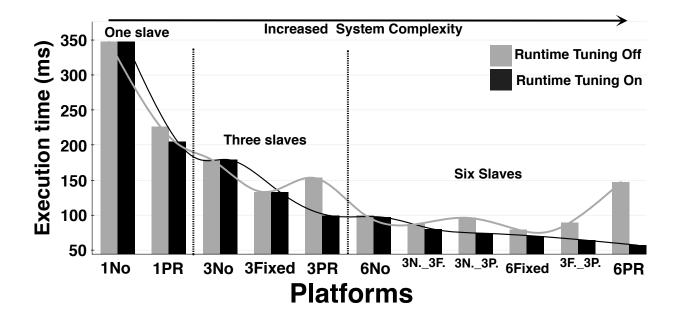

| 5.24 | Execution time for the Synthetic benchmark                                                                            |

| 5.25 | Synthetic benchmark on Platform <sub>6PR</sub> : First accelerator hit ratio $\ldots \ldots \ldots \ldots \ldots 138$ |

| 5.26 | Synthetic benchmark on Platform <sub>6PR</sub> : Speedup                                                              |

| 5.27 | Synthetic benchmark on Platform <sub>6PR</sub> : PR ratio                                                             |

| 5.28 | 120 Threads                                                                                                           |

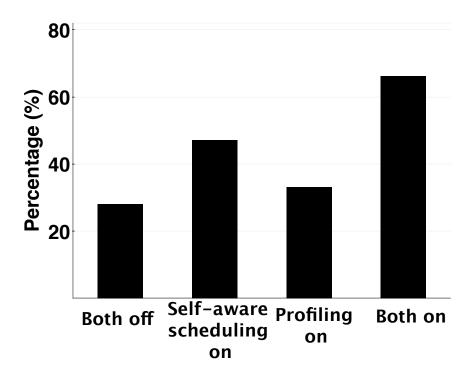

| 5.29 | Evaluating profiling effects on polymorphic calls                                                                     |

| 6.1  | HEMPS with loosely coupled accelerators                                                                               |

## List of Tables

| 5.1  | Comparison of the HAL functionality                                                  |

|------|--------------------------------------------------------------------------------------|

| 5.2  | Comparison between resource utilization of different implementation of HAL 112       |

| 5.3  | Size of selected HWTI system calls [19]                                              |

| 5.4  | Comparison of system services latencies                                              |

| 5.5  | Resource Utilization of Accelerators                                                 |

| 5.6  | the optimization methods provided to three different HW circuits by MicroBlaze . 121 |

| 5.7  | Synthesis time                                                                       |

| 5.8  | resource utilization                                                                 |

| 5.9  | PR overhead                                                                          |

| 5.10 | Sorting time comparison                                                              |

| 5.11 | resource usage for two different sorting accelerators                                |

#### **Terms and Definitions**

- **HEMPS** Heterogeneous Extensible Multiprocessor Systems

- ESL Electronic system Level design, tools and methods to abstract the HW details away.

- SoC System-on-Chip. A system in which all components are co-located on a single chip.

- MPSoC Multi-processor System-on-Chip. A system-on-chip having multiple processors.

- AMBA Advanced Microcontroller Bus Architecture

- AXI Advanced eXtensible Interface

- **IP** Intellectual Property

- VLSI Very-large-Scale Integration

- **VHDL** VHSIC Hardware Description Language

- Tcl Tool Command Language

- **DMA** Direct Memory Access. Often referring to hardware devices that can perform memory-tomemory operations without processor assistance.

- **ABI** Application Binary Interface. Refers to the calling convention and data layout of a particular processor-compiler pair.

- **API** Application Programmer Interface. The defined interface of a piece of software, often times a library or operating system.

- CISC Complex Instruction Set Computer.

- **RISC** Reduced Instruction Set Computer.

- **CLB** Configurable Logic Block. A programmable block within the architecture of Field Programmable Gate Arrays (FPGAs).

- **DSP** Digital Signal Processor. A processor specialized for signal processing, often featuring vector and multiply-accumulate operations.

- **FIFO** First-In, First-Out. A hardware component or data structure that exhibits First-In, First-Out behavior (e.g. a queue).

- **FPGA** Field Programmable Gate Array. A hardware chip whose functionality can be changed post-fabrication.

- GPU Graphics Processing Unit. A hardware component specialized for graphics processing.

- **HAL** Hardware Abstraction Layer. A layer of software used to hide hardware-specific implementation details.

- HW Abbreviation for Hardware.

- SW Abbreviation for Software.

- ISA Instruction Set Architecture. Also known as the instruction set of a particular processor.

- **IPC** Inter-Process Communication, when referring to software; or Inter-Processor Communication, when referring to hardware systems.

Kernel The core component(s) of an operating system.

- **OS** Operating System.

- **RPC** Remote-Procedure Call.

- **RTL** Register Transfer Level. An abstraction level of the hardware design process.

- LUT Lookup Table. A digital building block used to implement N-bit binary functions via lookup operations.

ASIC Application Specific Integrated Circuit.

- **CPU** Central Processing Unit. A hardware component, often referred to as processor or core that processes instructions of a program.

- **DLP** Data Level Parallelism. A form of parallelization that emphasizes distribution of data on parallel processing elements.

- **TLP** Task/Thread -Level Parallelism. A form of parallelization that emphasizes on the distribution of threads/tasks across parallel processing elements.

- **FSM** Finite State Machine. Model of behavior of a finite number of states that includes actions and transitions between states.

- **HAL** Hardware Abstraction Layer. A layer of software used to hide hardware-specific implementation details.

- HDL Hardware Description Language (e.g. VHDL or Verilog).

- HWTI Abbreviation for Hardware Thread Interface.

- V-HWTI Abbreviation for Virtual Hardware Thread Interface.

- **MPI** Message Passing Interface.

- **OTS** Off-the-Shelf.

- **RTOS** Abbreviation for Real-time Operating System.

- **MIMD** Multiple-Instruction, Multiple-Data. A category of parallel programming/computational model in Flynn's Taxonomy that is represented by systems capable of executing different instruction streams that are able to operate on different streams of data simultaneously. Multiprocessor (multi-core) systems fit into the MIMD category.

- **MISD** Multiple-Instruction, Single-Data. A category of parallel programming/computational model in Flynn's Taxonomy that is represented by a machine that executes multiple instructions on a single piece of data. It can be argued that pipelines and systolic arrays fit into this category.

- **MMIO** Memory-Mapped I/O. The process of performing I/O through memory-mapped interactions such as reads and writes (loads and stores).

- **SIMD** Single-Instruction, Multiple-Data. A category of parallel programming/computational model in Flynn's Taxonomy that is represented by a vector processor that executes a single instruction on multiple data at once.

- **SISD** Single-Instruction, Single-Data. A category of parallel programming/computational model in Flynn's Taxonomy that is represented by a typical scalar processor.

#### **Chapter 1**

#### Motivation

ESL (Electronic system level) Design is an umbrella term for tools and methods that allow designers with software programming skills to easily implement their ideas in programmable hardware (like FPGAs) without having to learn traditional hardware design techniques. This enables programmers to access the performance potential of the FPGA through standard programming models on a heterogeneous chip multiprocessor system. This augments the FPGA traditional ability to provide performance increases through custom circuit implementations to bringing performance through scalable parallelism. The use of programmable components and runtime systems brings advancements in application portability and platform reuse. It also brings increased designer productivity; the historical Achilles heel of FPGA hardware design flows. Similarly, HLS tools are bringing similar performance and productivity advancements through their ability in generating custom circuit from sequential code to designers, even those with no hardware design expertise, to rapidly create accelerators. Recent work in middleware and operating systems support for dynamic reconfiguration is bringing new abilities to increase system performance and increase gate utilizations under a more unified virtual machine model. Although existing physical FPGA components can support these capabilities together, no unifying design flows, abstractions, programming models or runtime systems have yet evolved to enable their simultaneous use. As a result these capabilities are still treated largely as distinct and stand alone use cases for FPGA's. The ability to combine these capabilities can bring significant performance advantages to a widening group of designers, and that is what we are trying to address in this thesis work.

The big motivation here is basically how to make FPGAs as accessible as a typical CPU to SW developers. In other words, when a SW developer writes his application code on a typical CPU, they can simply compile the code, no matter which system they are using, and all the complexities of the CPU architecture is abstracted away from him. For example, the software developer does

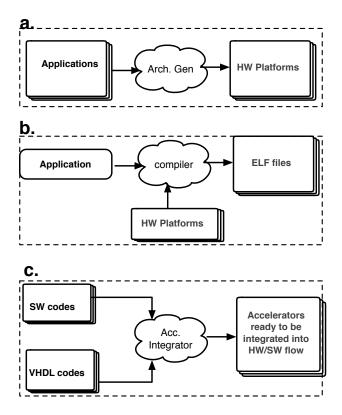

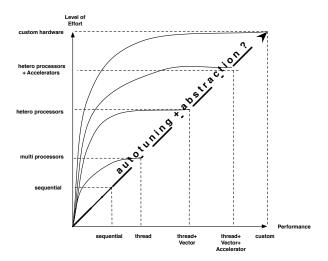

Figure 1.1: Three areas that should be addressed to achieve abstraction in FPGAs

not have to know if the system has a quad core intel CPU, or just a single core AMD CPU. Also he/she does not have to know about memory hierarchy or bus interconnect or DMA controller, etc. This all comes form abstraction. Basically, all the details of HW architecture is abstracted away from SW developer and the compiler tool chain takes care of enabling the notion of "Writing code once and running it everywhere".

However, despite this great productivity and portability brought to SW developers by a typical CPU, the performance still remains an issue. First off, the HW can not be customized to accelerate some portions of the code to take advantage of data level parallelism. Also, the number of general purpose processors is fixed and limited, hence limiting the maximum thread level parallelism available in user's code. Here is when FPGAs unique capabilities can help with both customized HW to leverage data level parallelism, and customized multi-core processor system to leverage thread level parallelism. Unlike other alternatives such as GPU boards that require the SW developer to rewrite the whole code in other languages like CUDA, there is no such hassle when it comes to

heterogeneous multiprocessor systems on FPGA.

FPGA's complexity and reconfigurability comes with a price that if not addressed and abstracted away from the end users, will dramatically reduce their usage in SW developers community. In order to work with FPGAs, one should have some basic information about HW architecture and Digital design, and most SW developers lack this knowledge. The ideal case would be to have the same productivity and portability as a typical CPU, therefor three areas should be addressed:

- Generating the HW platform bitstream requires broad knowledge in HW architecture and digital design and familiarity with CAD tools. All of these complexities should be automated. This can be done by a HW tool-chain which receives a high level specification file (like the number and type of processors, accelerators,etc) and spits out the final bitstream. This high-level specification file is either manually written or automatically extracted from user's code. Fig 1.1.a shows this first side of abstraction.

- The application code should be compiled to run on any CHMPs platform without the need for the user to change the application. This compilation flow should be aware of the platform details to generate an optimized binary file. Also, during runtime the operating system should smartly auto-tune the application to fully leverage the resources available on this platform including general purpose processors, customized accelerators and partial reconfiguration slots. Fig 1.1.b illustrates this aspect of abstraction.

- In order to transparently take advantage of customized HW circuits (aka accelerators), the integration of new accelerators to the existing HW/SW flow should be fully automated. In other words, the SW developer should only provide the C code for the function they want to accelerate (or even the VHDL code, if available) and they should not be concerned about how this accelerator is going to be modeled, integrated and communicate with the rest of the system. Fig 1.1.c show this crucial part of abstraction.

In sum, abstraction is the key if FPGA's are going to be widely used and accepted in SW developers community. The HW/SW flow should be automated and optimized based on application

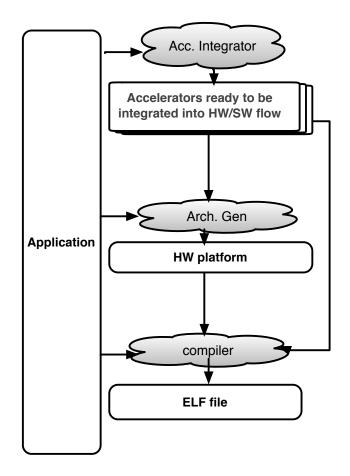

Figure 1.2: The entire flow from C code to final binary file

code to abstract away the details from SW developer. This thesis tries to investigate how this productivity and portability can be achieved in FPGA-based CHMPs. The entire flow is shown if Figure 1.2. First of all, the accelerators are extracted from the C code and then they are used to generate the HW platform. Finally, the HW platform along with the accelerator drivers is used to compile the application into final binary file.

In this thesis, I will argue that the formation of CHMPs system with extensible processor nodes, defined as a processor plus partial reconfigurable slot, can be automated and will cover a very broad range of accelerator use cases with minimal performance loss compared to a fully custom designed architecture. The complexities of different organizations of accelerators can be made transparent and portable through operating system and middleware abstractions. I believe that Heterogeneous Extensible Multiprocessor Systems (HEMPS) can address dark silicon without sacrificing portability and productivity. HEMPS systems are flexible and general enough to abstract the platform complexities from SW developers and also their generation can be automated. They provide the SW users with the HW architecture which supports different levels of parallelism and a transparent programming language.

Designers of real time and embedded systems are continually challenged to provide new system capabilities that can meet the expanding requirements and increased computational needs of each new proposed system, but at a decreasing price/performance ratio. FPGAs have become important components contributing to the creation of a family of Commercial Off the Shelf (COTS) hardware platforms for future real time and embedded systems. FPGAs densities are maturing to allow a complete CHMPS system. The system software for FPGAs must provide a fairly general set of capabilities to support the widening range of applications, but must also be capable of providing the specialized support required to satisfy a particular application's interfacing and performance needs. Creating such a capability for real time and embedded systems applications is a difficult challenge in part, because it requires the simultaneous satisfaction of apparently contradictory forces; generalization and specialization. However new architecture and run time systems support is needed to enable the model to scale within systems containing 10's to 100's of compute components. This thesis investigates the run time services and new architecture to enable developers to express applications that seamlessly scale across specialized large CHMPs systems using the generalized scalable and portable multi-threaded programming model.

Current HW/SW co-design in FPGA-based CHMP systems lack portability and productivity. These two issues has made SW developers community reluctant to switch to FPGAs from general purpose processors. To achieve portability the platform complexities like partial reconfiguration, custom HW circuits and soft and hard IPs should be abstracted away from SW developers . This makes the FPGAs capabilities transparent to the end users. There are also some challenges in the way of productivity. First off, dealing with the CAD tools require a fair amount understanding of HW architecture and digital design, which calls for automating the generation of HW platform . Secondly, as the system grows in complexity, fine/coarse grained hand partitioning of the tasks

among different computational nodes gets more time consuming. Finally, there has not been much effort in providing accelerators with stack management and pointer support as SW programmers are used to C-like capabilities.

At the same time, lack of parallelism and power issues has led to Dark silicon problem, forcing general purpose community to consider heterogeneous systems. This great potential opportunity for FPGAs has not been exploited due to lack of both a transparent programming language to capture different levels of parallelism, and the HW architecture which supports different levels of parallelism. There has been a large efforts in how to seamlessly integrate accelerators in a heterogeneous system to combine thread level parallelism and data level parallelism. However, most often this has led to decreasing the productivity and portability. There are three challenges in addressing both efficiency and accessibility at the same time: Abstracting away the complexities of CAD tools, Abstracting away the details of HW platform and finally easy integration of accelerators to the existing system.

#### 1.1 Abstracting away the complexities of CAD tools

One of the main advantages of a FPGA is it's ability to allow designers to create custom circuits at design time. This same advantage has also been one of its main disadvantages; the use of FPGAs requires hardware design skills and the use of hardware centric Computer Aided Design (CAD) tools. This makes FPGAs unaccessible for most software programmers and domain experts. One of the challenges in reconfigurable computing for over two decades has been focused on how FPGAs can be accessed and used through more generalized software development languages, tools, and development flows.

To begin with, one might ask whether generating a general HW platform be automated to spare users from dealing with CAD tools? In other words, based on a high-level specification file that specifies the number of processors, type of accelerators and the type of interconnect we want to generate the final bitstream that is ready to be download on FPGA. Ideally this specification file should be tailored for the SW developer's code. This spares users from dealing with CAD tools, which require a fair amount understanding of HW architecture and digital design. Automating this type of effort will enable researchers to address scientific questions quicker, and with an enhanced ability to increase experimentation across a broader range of configurations. Automating the creation of standard CHMPs architectures also makes it easier to port and maintain the standard operating systems and middleware that bring the fundamental software engineering tenets of portability and reuse onto FPGA based CHMPs system. In the absence of this automated flow, each CHMP system must be created by hand within a CAD tool. For such custom systems this results in long development times and limits the creation of parallel architectures to hardware designers who possess knowledge of digital design, HW/SW co-design, and parallel computer architectures. Additional efforts are required to either create a new, or modify and port an existing operating system and standard middleware run time libraries for each CHMP system. The level of effort to recreate base hardware architectures and run time protocol stacks by hand also makes it nearly impractical for different researchers to reproduce systems to make fair comparisons; a fundamental component of good scientific experimentation.

New design flows for CHMP systems will be required that are architecture centric and exist an abstraction level above High Level Synthesis. These types of architecture centric flows are now trending within System on Chip (SoC) design practices. These practices follow a two phase design process that minimizes hardware development time and effort. In the first phase a base platform is constructed with standard programmable processor cores, memory hierarchies and interconnects. This first phase minimizes design costs through IP reuse and replacement of custom components with re-programmable processor cores. These base platforms are then optimized in the second phase through tuning of extensible cores and finally the addition of a small number of custom components necessary to enable the system to meet all performance requirements. The malleability of the FPGA fabric combined with the increased transistor densities allow designers to follow this same approach for constructing CHMP systems. First a base system can be constructed with soft IP programmable processor cores, and support components available through vendor specific as well as free libraries such as opencores [36]. Once the base system is configured designers

can optimize components and create any additional accelerators that would be required to meet a specific applications performance requirements. While current FPGA vendors are addressing IP reuse and component integration within their CAD tools automating the creation of a base system would be better performed outside of any specific vendor flow to maintain design portability. To achieve true vendor neutrality will require new intermediate representations of system architectures that can then be translated into multiple vendor specific formats. The new flow for generating hardware platform should provide following benefits:

- Complexity/Productivity by automating the generation of flexible CHMP systems automated

- *Portability* Should be able to provide HW architecture for "write code once and run anywhere".

- *Avoiding Dark Silicon* Transistor Utilization and Efficiency (or Dark Silicon), through partial reconfigurable accelerators and/or power aware thread scheduling

#### 1.2 Abstracting away the details of HW platform: Portable code

The second challenge in FPGAs is lack of abstraction, productivity and accessibility. To achieve portability the platform complexities like partial reconfiguration, custom HW circuits and soft and hard IPs and HLS tools should be abstracted away from SW developers. This makes the FPGAs capabilities transparent to the end users. While the general purpose processors provide users with more productivity and more abstraction compared to FPGAs, the FPGAs capabilities are not transparent to the users. This leads to less productivity in FPGAs. Therefore, abstracting both HW/SW design in FPGAs is the key to popularize FPGAs among SW developers community. Emerging programming models for CHMP systems elevate architecture details up into the source code. This increases the complexity of the design process, eliminates portability and can result in inefficient designs.

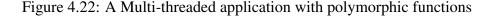

One way to tackle this problem is to create libraries that abstract the need for programmers to be aware of processors/accelerators and how they are configured within a particular heterogeneous platform. These callable compute patterns should self tune for each system. These calls are running on extensible processor nodes and enable the reusing through high level architecture abstraction and runtime tuning. We call these *Polymorphic functions*.

Polymorphic functions remain portable across CHMP systems, and enable a transparent and autonomous fine-grained HW/SW partitioning. This approach reinstates portability through polymorphic functions, and provides infrastructure for an adaptive runtime system that can perform runtime profiling and dynamic scheduling across systems with different combinations of heterogeneous resources. The combination of polymorphic functions, runtime profiling and adaptive heterogeneous scheduling eliminates the need for designers to exhaustively explore a multidimensional search through static profiling and can result in better resource utilization and performance for CHMP systems with different combinations of processors, and static and partially reconfigurable accelerators. This new portable programming model based on Polymorphic functions can abstract all heterogeneous resource differences out of the source code. Also the run time system profiles and adaptively partitions the high level application onto any combination of available heterogeneous resources.

#### **1.3** Easy integration of accelerators into the existing system

FPGA densities continue to follow Moore's law and are now sufficient to support large CHMP systems. These systems can be populated with tailored mixes of compute resources, such as scalar, single instruction multiple data (SIMD) and vector processors, as well as custom accelerators to meet the specialization needs of each application. This combination of heterogeneous computational nodes allow a complete CHMPS system on FPGAs. However, the side effect of this complexity is how to integrate the customized circuit into CHMPs. On one hand, the accelerator developer should not be concerned about low level details of how the accelerator is going to communicate and transfer data with the rest of the system. On the other hand, the accelerator developer should be given a flexibility in the number of BRAMs and FIFO interfaces needed. Also, how the accelerator is going to be accessed and harnessed should not left to the end user. The challenge

is how to make the integration of the accelerator into the existing system as easy and efficient as possible. This helps with both productivity and performance.

#### **1.3.1** Modeling accelerators

On-chip accelerators can be classified into two classes: 1)tightly coupled accelerators where the accelerator is attached to a particular core and can only be accessed by that core. 2) loosely coupled accelerators, which the accelerator is an independent entity which can be shared and accessed among multiple cores [24]. There have been many proposals on how to model, program, and integrate accelerators into a scalable multiprocessor framework. At one end of the spectrum are loosely coupled accelerators that can be viewed as shared system components. At the other end of the spectrum are tightly coupled accelerators that can be viewed as extensions of a single processors ISA. To date, these two ends of the spectrum have been viewed as distinct classes of accelerators, with separate requirements for how the interface into system services, how they should be abstracted for programmers, what granularity of parallelism each type can efficiently support.

Meanwhile, The multithreaded programming model has evolved to enable programmers to combine software threads running on a processor with hardware threads implemented as custom accelerators within the reconfigurable fabric. Enabling hardware accelerators to be represented as threads was a significant step in enabling software programmers to access the potential of an FPGA from a familiar scalable parallel programming model. Traditional approaches provided a finite state machine version of a Hardware Abstraction Layer (HAL) to allow hardware threads to interface into the multithreaded programming model. So the accelerators used a custom HW finite state machine version of a Hardware Abstraction Layer to interface into the multithreaded programming model.

#### 1.3.2 The traditional solution: FSM based HAL for loosely coupled accelerators

While the policies of the multithreaded programming model were defined to explicitly allow the expression of scalable parallelism, HALs as supporting mechanisms make inefficient use of hard-

ware resources and impose restrictions on the level of parallelism that can be exploited. HALs are defined to provide system services for accelerators that are modeled at the coarse grained thread level. This can lead designers to synthesize a thread that includes sequential instructions that occupy gates and provide little to no performance increases.

While FSM based HALs for loosely coupled accelerators were appropriate for platform FPGA's with small numbers of processors and hardware threads, the implementation approaches are not viable for todays larger CHMP systems. The model supported a thread as the finest granularity of concurrent component supported. This required FPGA resources to support the sequential portions of a thread, and limited the thread to contain only a subset of functionality that could be synthesized. Implementations used finite state machines within a custom hardware interface to provide each thread with the system functionality required to interface and interact with the operating system. The size of the custom hardware interface grew as more state machines were added to provide a full range of functionality. FSM based HALs was acceptable for interfacing a thread but has limitations for next generation systems that may require moving functionality across the HW/SW boundary, better support of languages such as C that require a stack, ease of expansion and modification.

An FSM based HALs for loosely coupled accelerators abstracted custom HW as a hardware resident thread that accessed key operating system services such as mutex operations, as well as providing access to a linear address space, through a series of hardware based finite state machines encapsulated within a virtual abstraction layer. This allowed a complete thread body to be implemented as a hardware thread and seamlessly interact with all other software and hardware resident threads throughout the system. This model proves inefficient in resource usage, restrictive in supporting different accelerator models and for dynamic scheduling and resource allocation. First, any change to the operating system services required a redesign and re synthesis of the hardware resident virtual abstraction layer. Further the size of the virtual abstraction layer quickly grows greater than the size of a standard processor such as MicroBlaze. Additionally resources are required to implement the complete, and not just the computationally intensive portions of the thread

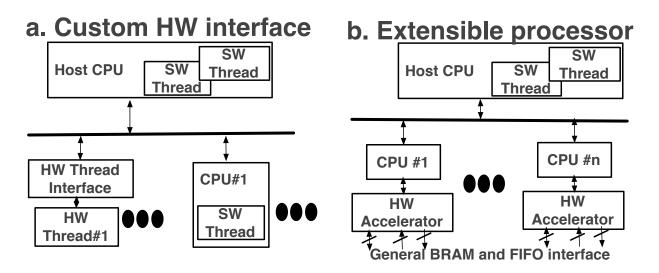

Figure 1.3: Loosely coupled accelerators Vs. Extensible processor.

yielding large accelerators. In sum, the drawbacks of HW threads implemented as loosely coupled accelerators with FSM based HAL approach are:

- changing or adding new features to HW thread interface requires HDL re-designing and re-synthesizing. It is not only time consuming, but also results in a bigger size Hardware.

- There is no fine grained HW/SW partitioning. The entire thread should be either run in HW or SW, which as a side effect results in a bigger HW threads with no added benefit for the sequential part of the thread.

- There is no support for Stack management for HW accelerator, which stops some algorithms like Quicksort to be implemented in hardware.

- Integrating new HW cores into system with different interfaces is hindered by what HW thread interface dictates.

#### **1.4 Extensible processor**

Can a single processor-accelerator combination unify the varying use cases of accelerators within FPGA based CHMPs systems? This node can work as the basic block of automatically generated

CHMPs systems, as well as autonomously executing the portable code targeting these systems. A processor-based HAL has the potential to unify hardware and software threads, provides stack management and pointer support plus distributed OS and RPC services for the accelerator. Implementing the HAL using a general purpose processor instead of a custom finite state machine provides increased flexibility and productivity. Also Using a general purpose processor as a front end in place of a custom circuit eliminates the need to distinguish between a hardware and software thread. All system components can be viewed as extensible processors and support any combination of hardware and software threads. Using a general purpose processor as a front end to the hardware accelerator turns a dedicated hardware thread into a much more flexible extensible processor. This extensible processor nodes can be combined to form a HEMPS system and directly ties to our first argument of automating the generation of CHMPS systems. A CHMP system can be built using extensible processors with static or partially reconfigurable accelerators, and DMA controllers for fast data transfers. It unifies both models of loosely coupled and tightly coupled accelerator in one architecture, as well as providing portability for applications. Figure 1.3.b shows a high level view of an Extensible processor

Allowing the accelerator to be connected directly to a processor also extends the earlier model of loosely coupled accelerators across a system bus to also include tightly coupled access from the processor's register set. Each extensible processor can be used as both a loosely coupled or tightly coupled accelerator. This unifies the two models that have traditionally been treated separately. In short, an extensible processor model provides a more efficient implementation of a HW-based HAL, provides capabilities needed to standard programming models and languages, allows systems to scale, and extends the accelerator's use case.

Moreover, there has not been much effort in providing accelerators with stack management and pointer support as SW programmers are used to C-like capabilities. Extensible general purpose processors serves two purposes : Running the sequential part of the thread and autonomously assigning only the parallelizable part of it its attached HW accelerator. The general purpose processor in this node has the potential to provide stack management and other optimization services like RPC, overlapping data transfer with computation, etc for the HW accelerator.

#### Chapter 2

#### Introduction

The continued increase in fabrication densities of FPGAs are yielding devices that can support CHMPs architectures. Current generations of FPGA's such as the Xilinx VC707 can support over a hundred processors on a chip. As an example, the hthreads in the cloud project now makes bitstreams publicly downloadable for systems with up to 150 Microblaze processors. Bitstreams for accelerator rich MPSoPC's are available for systems with up to 36 Microblaze processors plus 36 partial reconfiguration slots are also available [21]. FPGA based CHMPs systems offer the advantage of allowing designers to include custom compute components such as accelerators into systems with scalable numbers of programmable processors to meet challenging application performance needs. To increase designer productivity commercially available C to HDL tools are available to translate portions of the application C code, such as loops, to be synthesized into accelerators [11]. Even though the transistor densities of commercially available FPGA's contain sufficient gates to support large and heterogeneously diverse MPSoPC systems, and C to gates capabilities are becoming common, how to form and program such large and heterogeneously diverse architectures is not fully understood. The question is *who and how* is going to use these resources available on FPGAs?

CHMP systems represent a new era in reconfigurable computing with system architectures that can bring the performance benefits of an application specific design but driven and accessible through familiar scalable programming models. Enabling these systems to be used by application developers will require new capabilities in processor centric design automation, more adaptive runtime systems, and new middleware abstractions within concurrent programming models.

To explore this thesis statement of this work, I want to investigate the following set of questions:

• Can the creation of CHMPS systems with programmable processors plus custom accelerators be automated without sacrificing the ability to customize systems ?

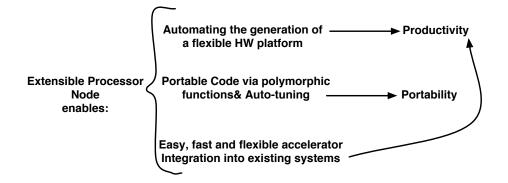

Figure 2.1: Extensible processor node enables

- Can the platform complexities of an accelerator rich CHMPs system be abstracted to reenable the notion of "writing code once, and run everywhere"?.

- Can a single processor-accelerator combination unify the varying use cases of accelerators within FPGA based CHMPs systems ?

#### 2.1 The need for making FPGA's accessible to SW developers

The United States Bureau of Labor Statistics reported that in 2010 there were approximately 82,000 hardware engineers and over 1.2 M software programmers [10]. Although the densities and capabilities of FPGAs continue to grow, the lack of standard operating systems support and software centric programming models has continued to hinder their adoption by this large cadre of software programmers. FPGA based operating systems researchers have addressing the issue of FPGA accessibility for software programmers for the better part of two decades.

SW programmers should be spared of details of hardware platform in FPGAs. This is a multifaceted problem. First off, there should be a model as to how to integrate custom HW into a multicore system. Second, how to automate the generation of such a heterogeneous multi core system. And finally, how to compile the application for different heterogeneous multi core systems without the need to change the application or putting platform-specific details up into the application. Having said all of these, the basic question is what should a basic computational node look like in a heterogeneous multi node system? The organization of the computation node would be the basic block for generating the HW platform as well as the compile flow. Most recently the architecture community has been advocating accelerator rich heterogeneous multiprocessor architectures called chip heterogeneous multiprocessors (CHMPs). These types of systems are gaining interest within the FPGA community as well. One open research issue is how custom accelerators should be interfaced into CHMPS architectures and abstracted within a higher level programming model.

#### 2.2 Dark Silicon challenge

The increased capabilities offered by a CHMP system does come at the costs of increased complexity for designers in constructing the base system, decreased code/design portability, and an increased potential to fall victim to "dark silicon" [28]. Dark Silicon refers to transistors on a chip that are not used due to two inter-related issues; lack of available parallelism and fixed power budgets [28]. Dark silicon places limits on an applications ability to achieve desired speedups and prevents the application from scaling across generations of chips that can provide increased transistor densities. In response to dark silicon the general purpose computing community has already transitioned from homogeneous many-cores to *chip heterogeneous multiprocessors*. These systems contain scalable mixes of CPU's, GPU's, extensible processors and accelerators to better exploit all levels of parallelism and provide better energy efficiencies [42]. Reconfigurable computing bases, such as FPGA's are not immune from dark silicon. FPGA densities are already sufficient to host a complete heterogeneous chip multiprocessor [12, 58]. This use case represents an interesting convergence between the general purpose and reconfigurable computing communities, albeit from opposite directions.

Current dark silicon concerns for FPGA's stem more from a lack of available parallelism than fixed power budgets. Current process technologies are not yet violating Dennard scaling [26], where achievable transistor density levels would require turning off a portion of the chip to meet fixed power budgets. Chip vendors are now seeking to use modern process technologies such as Intel's 14nm fabrication lines that may cause FPGA densities to violate Dennard scaling in the near future. Current dark silicon concerns for FPGA's result from idle transistors that are not supporting

parallelism. Dark silicon can appear even within heterogeneous chip multiprocessor systems. First, mismatches between the user visible higher level programming model and the actual capabilities of the heterogeneous resources will result in underutilization. Second, changes in runtime behaviors of the application or underlying system can lower utilization. Third, modifications or updates to the original application can effect the underlying architectures ability to exploit new behaviors. Thus a key challenge in keeping transistors at high utilization levels becomes a runtime issue.

FPGA components support the capability of allowing portions of the gates to be dynamically reconfigured during runtime. This promises to address the issue of "dark silicon" or portions of the chip that are not being used that now plague standard manycore architectures. Accelerators and components can be paged into the silicon on demand by the operating system during runtime. Reconfiguring transistors during runtime has the potential to increase transistor utilization. This is conceptually similar to current multithreading techniques that context switch multiple threads across a shared processor resource to increase utilization. The difference is primarily in what is swapped in and out; binary executables or bitstreams. The same application that has been partitioned into hardware and software components, profiled and tuned for maximum performance on a specific architecture will have to be re-tuned, partitioned, profiled and optimized if the configuration of the underlying CHMP changes. This is counter to the software worlds desire to write once, run anywhere.S Applications optimized for one particular architecture configuration may not run well on another. Architecture configurations can vary during runtime . A partitioning that is optimized based on the availability of accelerators or a vector processor would not perform efficiently if these resources were busy and the application was alternatively mapped onto a set of general purpose processors. Further programmers cannot know how the system will exhibit non-deterministic behaviors during runtime.

#### 2.3 Modeling and abstracting the accelerators in a CHMPS architecture

One avenue of research has focused on using the multithreaded programming model as a unifying abstraction over Hardware/Software co-designed applications within an FPGA. This approach was

proposed in 2003 by [49, 63] and has continued to gain in popularity [45, 19, 39, 65, 41]. The appeal of the model is it's ability to view physical accelerators as abstract threads. The model defines standard policies such as mutex and semaphore operations that allow multiple accelerators to run concurrently within the FPGA, synchronize with other threads (accelerators) and share data. The HAL was required to provide hardware threads with equivalent system call interfaces into standard Pthreads APIs. This includes as acquiring and releasing a mutex, transferring data, and support communications with other threads running throughout the system. One of the promises of FPGAs was the ability to deliver performance levels close to those associated with custom circuits, and this has to be harnessed by SW programmers.

The FPGA based operating systems research community has been investigating the use of the multithreaded programming model as a unifying framework. In this model custom hardware accelerators are abstracted as detached hardware threads. The flexibility of the model allows multiple accelerators to be defined and operate concurrently within the FPGA. This extends the earlier use case of FPGA as a single detached accelerator treated as as co-processor to an external CPU.

An important aspect of the model is the separation of policy and mechanism. Policies such as those defined in the Pthreads standard, are accessed through Application Programmer Interface (API) calls. System designers are free to implement the APIs using platform specific mechanisms. On commercial desktop systems, mechanisms are built using existing hardware and protocols, the processors Instruction Set Architecture (ISA) and Application Binary Interface (ABI) definitions, and standard software protocol stacks. FPGA operating systems researchers had no such set of predefined hardware components, protocol stacks, or ISA and ABI's. Thus a challenge for first generation efforts focused on defining these standard types of mechanisms encapsulated within an additional hardware component call a Hardware Abstraction Layer (HAL). The HAL served to provide a set of standard register interfaces to replace soft traps for access to the mechanisms, and sets of finite state machines to replace non-existent software system service libraries. These first generation efforts were successful in validating the approach. However this HAL suffers resource inefficiencies, limits the granularity of parallelism that can be supported, and presents difficulties in modifying and updating the system service interfaces and mechanisms.

This model extended the historical view of a FPGA as a single accelerator by allowing accelerators to operate concurrently with other software and hardware threads. Operating system services were provided for the hardware threads through HAL, which extend OS services to hardware accelerators connected on the system bus. The HAL Abstraction layers have evolved for supporting a standalone custom HW such as a thread. These HALs are implemented as a series of finite state machines that provide the hardware threads with the equivalent of libraries of linkable software system calls. The HAL allowed the hardware thread to request standard operating system services such as acquiring and releasing a mutex, or share data with other software and hardware threads running throughout the system. It also allowed the accelerator to be viewed as a schedulable detached thread by the runtime system. The HAL was fundamental in allowing programmers to use the multithreaded programming model to create multiple accelerators. Those accelerators can operate as concurrent threads running independently throughout the FPGA fabric.

The definition and use of the HAL has enabled accelerators to be viewed a threads, and has allowed the accelerator access to important policies such as requesting mutexes and semaphores that are critical to the model. However it does not remain faithful to the full separation of policy versus mechanism which is important for portability. The use of a HAL indirectly requires application developers to code and treat hardware threads differently from software threads. The run time system must also distinguish and schedule hardware and software threads differently. The size HAL will grows as additional functionality or system services are added. Finally, unlike system software that can be easily modified and quickly compiled, changes to the HW-based HAL required low level circuit design skills and resynthesis. In other words, while this approach successfully abstracted the HW/SW boundary from the programmer and enables multiple loosely coupled accelerators to interact with the runtime system, it suffered several disadvantages. First, the granularity of the computation mapped into the accelerator was at the coarse grained thread level. Sequential sections of code contained within the thread body became synthesized as part of the hardware accelerator. This results an inefficient use of the FPGA resources. Second, the size of

a HW-based HAL can become large if sufficient OS service functionality is included to allow the accelerator to appear to the system as an independent stand alone detached thread. Additionally, unlike system software that can be easily modified and quickly compiled, changes to the HW-based HAL required low level circuit design and resynthesis. Each time more functionality is added the size of HAL increases.

In this thesis we try to see if a hardware HAL can be replaced with more flexible and programmable *extensible* processors. On our Xilinx based systems, we form an extensible processor with a Microblaze, set of standard FSL links, and three scratch pad BRAMs. The extensible processor provides the following additional capabilities over the first generation hardware based HAL. First, The size of a HAL will grow in proportion to the functionality placed into the HAL. Current HAL's routinely occupy more gates than a soft IP processor such as the Microblaze. Changes or additions to the system services requires hardware redesign and synthesis, a level of hardware design skill that is beyond most operating systems designers. The use of a hardware HAL has the secondary effect of imposing inefficient usage of transistors within the user code that was mapped and synthesized within the accelerator; even the sequential portion of the thread needs synthesized. The use of the HAL also required the accelerator house the complete thread. This places restrictions on the application code within the thread body to be synthesized. Most hardware HALs do not include the additional finite state machines and local memories to provide stack support for the hardware thread. This prevents designers from mapping thread code that contained function calls or allocated locate variables from a stack into hardware. Either the thread body must be re-written or the thread designated as a software thread.

We want to investigate whether the hardware HAL that sits in front of an accelerator can be replaced with a programmable processor to form a much more flexible and efficient *extensible processor*. The extensible processor allows the uniformity of the multithreaded programming model to be restored. Programmers no longer need to draw a distinction between threads that will run in software or hardware. All types of threads can run on an extensible processor. The run time scheduler can then map any thread onto any available extensible processor. An extensible pro-

cessor allows a single thread to be split across the HW/SW boundary. The sequential portions of the thread run on the processor, and the computationally intensive portions of the thread can run on the accelerator to leverage data level parallelism. We investigate the possible resource savings this approach can provide over hardware based HALs, as well as the HW/SW partitioning which might provide interesting counter intuitive run time results. I think replacing custom hardware with a programmable processor can result in increased performance. Finally we try to see how the extensible processors stack can be used by the accelerator to allow code that contains function calls and local variables to be synthesized and mapped into the accelerator. This can increase the usage of the accelerator to threads that contain function calls, recursion, and local variables. We also explore performance results for systems built on extensible processor to see if it can scale into 100's of processors and accelerators, and can be programmed using concurrent threads.

As far as providing accelerators with operating system services goes, there are two approaches. One approach used a full Linux stack running on a master processor [63, 45, 39, 65]. Operating system services are executed on the Linux stack on behalf of the accelerators. This approach required the HAL to include RPC call support to communicate with wrapper functions that executed on the Linux stack running on the master. This approach introduced additional latencies for accelerators accessing the OS services running on the master node, and from sequentializing service requests. The second approach sought to reduce latencies by distributing more OS services into the HAL [19]. This approach reduced access latencies and eliminated the sequential server bottleneck. In the work, we follow the second approach as it is more scalable.

In this thesis, we try to show how a HW-based HAL can be replaced by a CPU-based HAL. Without any loss of functionality we show how a general purpose processor such as a MicroBlaze can be used as a plug-in replacement for a HW-based HAL. Replacing custom hardware with a programmable processor brings the obvious benefits of increased productivity and flexibility. Changes and updates to system services can be achieved through software compilation instead of hardware synthesis. Interestingly hardware savings are provided as the MicroBlaze processor requires fewer gates than a typical HW-based HAL [15]. Also the size of the accelerator can be reduced by moving the sequential portion of the thread out of hardware and into the MicroBlaze. Importantly combining a general purpose processor with an accelerator forms a very flexible *extensible processor*. Replacing the custom hardware based HAL with a programmable processor can increase performance, productivity and flexibility, while reducing overall area size. The extensible processor can still be used in it's original role of providing system services to a detached hardware accelerator thread. It also allows the accelerator to become more tightly coupled with the processor. This allows the size of the accelerator to be reduced by moving the sequential portion of the thread out of hardware and execute on the Microblaze.

An extensible processor is in a better position to support the needs of higher level programming languages as well as better support scalability within the system and multithreaded programming model. The standard processor's stack can be used to support function calls and recursion within the accelerator. The ability to migrate additional OS services into the HAL without increasing circuit size allows each extensible processor to assume more autonomous behavior. This eliminates the need for a HW-based HAL to provide remote procedural calls (RPC) to system services that are provided within a full OS stack running remotely on a master processor. An extensible processor also removes the need to draw distinction between a hardware and software thread; an extensible processor can execute any combination of software and hardware.

We try to remodel the accelerator as an extensible processor implemented through a tight coupling between the static or dynamic accelerator and a front end processor. This model has the potential to be resource efficient, portable, and better supports dynamic partitioning and allocation of resources. Without any loss of functionality the Microblaze can be simply viewed as a plug in replacement for the hardware virtual abstraction layer. Changes to the operating system can be realized through software compilation in place of hardware synthesis. Further resource savings are achieved as the sequential portion of a thread can be migrated out of hardware and into software executing within the Microblaze. An extensible processor model now widens the use of the accelerator to exploit a greater range of parallelism, from fine grained data level parallelism, through VLIW, and instruction fusion. Importantly this allows better resource utilization and support for dynamic tuning. Each extensible processor is now available to run any thread, with the choice of using an accelerator being made autonomously on each processor. Under dynamic reconfiguration each processor can make an independent decision to download a new bitstream into it's partial reconfiguration area. After introducing this notion of Extensible processor, we use it in a multiprocessor system with ICAP and DMA engines tailored to each node.

#### 2.4 Need for a general heterogeneous multiprocessor system

We try to integrate multiple extensible processors to form a new class of multiprocessor architecture we call Heterogeneous Extensible Multiprocessor Systems (HEMPS). HEMPS systems support both thread level parallelism (TLP) through the multiple processors, as well as data level parallelism (DLP) within the accelerator extensions. The operating system for HEMPS should support the seamless use of static or partially reconfigurable accelerators to enable portability across different heterogeneous multiprocessor systems. Our standard HEMPS systems include multiple DMA controllers to support fast transfer of data between memory as well as partial bitstreams. HEMPS system unifies both models of loosely and tightly coupled accelerators. From an architecture perspective a HEMPS system is chip heterogeneous multiprocessor system built on extensible processor nodes. This allows the system to exploit a wide range of parallelism from coarse grained threads running across the scalable numbers of processors, to fine grain parallelism within the accelerator extensions to each processor. The HEMPS model allows accelerators to be included statically or dynamically by the operating system under partial reconfiguration rules. The static or dynamic accelerators are both visible by the operating system as schedulable sharable resources, or as dedicated extensions to a processors ISA. Within a HEMPS system any accelerator can be used in both roles. The HEMPS architecture provides portability and efficiency over CHMPS. In a HEMPS system we target an MIMD/accelerator model. The MIMD model provides thread level parallelism across the multiple processors, with the ability to accelerate execution of each thread by extending each processor with custom accelerators. However, required designer skills necessary to construct a complex heterogeneous multiprocessor systems change from digital logic to those associated with creating a complete parallel architecture.

The fact that FPGAs support a complete CHMP system within a single programmable chip [23], represents an interesting convergence with the general purpose computing community. General purpose computing community is pursuing heterogeneous manycore architectures to combat dark silicon [28]. The malleability of the FPGA fabric offers designers the advantage of tailoring a CHMP system with different numbers and types of processing elements and accelerators to meet the specific performance needs of each application. This allows FPGA-based CHMPs to be built that are tailored to the exact types of parallelism that may be available in each application. However, creating these systems would be too hard for a typical SW developer. So from the HW point of view, automating the generation of CHMP systems is a must. Moreover, From SW point of view, familiar concurrency models such as asynchronous threads can be used over scalable numbers of general purpose programmable processors. Data level parallelism can then be exploited on programmable vector and array processors as well as within co-processor accelerators. This type of automation allows the creation of complex heterogeneous chip multiprocessors by software designers and significantly reduces the time and complexity of creating complete Systems on chip (SoC) systems. As far as Hardware design goes for these CHMP systems, creating the base architecture within the FPGA is becoming easier. Through the availability of standard IP components, and tools that can automate the assembly of the IP components into a complete CHMP architecture. Vendors routinely supply soft IP components such as buses, interrupt and I/O components as well as programmable processors such as the MicroBlaze [4].Community efforts are providing additional soft IP components such as vector processors as well as libraries of open source accelerators [36].

Vendor tools allow users to build systems with dynamically reconfigurable accelerators. All of these, care calling for automated tools to eliminate the need to hand assemble architectures within vendor CAD tools. From the application designers perspective, FPGA based CHMPs systems hold the promise of exploiting any and all levels of parallelism that may exist in their application. Familiar concurrency models such as asynchronous threads can be used over scalable numbers of general purpose programmable processors. Data level parallelism can then be exploited on programmable vector and array processors as well as within co-processor accelerators. Even Very Long Instruction Word (VLIW) and custom, or fused, instructions can be supported in hardware accelerators.

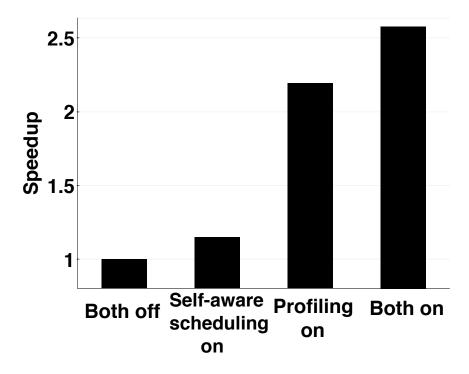

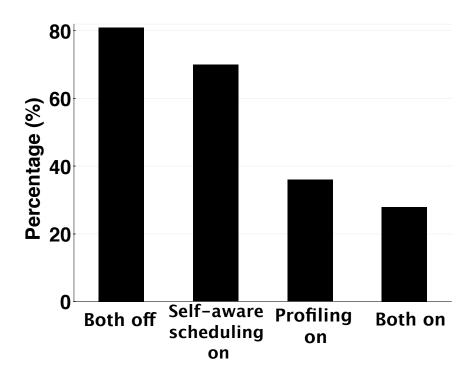

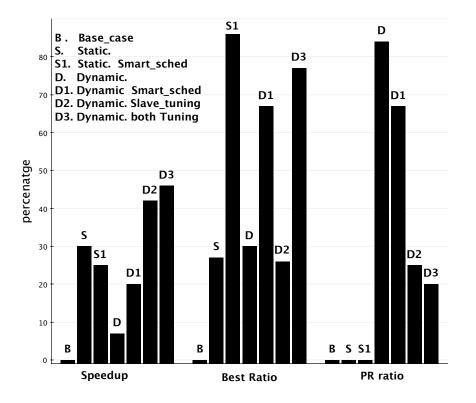

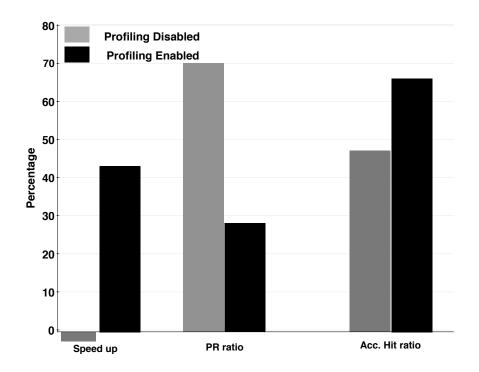

CHMPs systems hold the promise of providing a rich set of scalable general purpose and customizable processing components for designers to field systems that can meet challenging real time functionality, timing, and energy requirements. The malleability of the FPGA substrate allows designers to reduce design time by first adopting reusable base systems of scalable heterogeneous programmable processors and then augment these base systems with additional performance boosting custom accelerators or tuned processors. Partial reconfiguration, or the ability to swap accelerators into and out of a running system adds additional advantages for future FPGA based CHMP systems. The use of partial reconfiguration techniques can boost overall system efficiency through increasing the utilization of transistors. This may well become an important factor in addressing energy efficiency [44], and play an important role in offsetting "dark silicon" or transistors that cannot be used due to lack of parallelism or chip power restrictions [28].