## University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

1-2018

# A Proposed Approach to Hybrid Software-Hardware Application Design for Enhanced Application Performance

Alex Shipman University of Arkansas, Fayetteville

Follow this and additional works at: http://scholarworks.uark.edu/etd Part of the <u>Computer and Systems Architecture Commons</u>, <u>Graphics and Human Computer</u> <u>Interfaces Commons</u>, and the <u>Hardware Systems Commons</u>

#### **Recommended** Citation

Shipman, Alex, "A Proposed Approach to Hybrid Software-Hardware Application Design for Enhanced Application Performance" (2018). *Theses and Dissertations*. 2698. http://scholarworks.uark.edu/etd/2698

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, ccmiddle@uark.edu.

## A Proposed Approach to Hybrid Software-Hardware Application Design for Enhanced Application Performance

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Computer Engineering

by

## Alex Shipman University of Arkansas Bachelor of Science in Computer Engineering, 2008

## May 2018 University of Arkansas

This thesis is approved for recommendation to the Graduate Council.

J. Patrick Parkerson, Ph. D. Thesis Director

Gordon Beavers, Ph. D. Committee Member Jia Di, Ph. D. Committee Member

#### Abstract

One important aspect of many commercial computer systems is their performance; therefore, system designers seek to improve the performance next-generation systems with respect to previous generations. This could mean improved computational performance, reduced power consumption leading to better battery life in mobile devices, smaller form factors, or improvements in many areas. In terms of increased system speed and computation performance, processor manufacturers have been able to increase the clock frequency of processors up to a point, but now it is more common to seek performance gains through increased parallelism (such as a processor having more processor cores on a single chip or an increased number of physical processors in the system) rather than increased processor frequency.

This paper proposes an additional strategy for increasing system performance by allowing application developers to design custom circuitry for either their whole application or at least some portions of it that are on the critical path or that are computationally expensive. This will improve application performance by avoiding executing application instructions on a general-purpose CPU and instead executing on a specialized circuit designed to perform the desired algorithm, offloading tasks from the CPU (thereby reducing the overall system load) and enabling true parallelism for applications that can take advantage of a more parallel architecture.

For this paper, an Altera Cyclone II FPGA is used, but in practice, a higher performance and higher density FPGA should be used. ©2018 by Alex Shipman All Rights Reserved

## Acknowledgements

I thank my advisor, Dr. Parkerson, for his teaching and encouragement during this process. Additionally, I thank Dr. Beavers and Dr. Di for taking the time to be on my committee. I would also like to thank all of the professors who have taught me so many things.

## Dedication

I would like to dedicate this paper to my parents who have supported and encouraged me in so many ways and without whom I would not be writing this paper.

## Table of Contents

| 1 | Intr | oduction                                   | 1  |

|---|------|--------------------------------------------|----|

|   | 1.1  | General-Purpose Processors                 | 3  |

|   | 1.2  | General-Purpose Graphics Processing Units  | 7  |

|   | 1.3  | Full Custom Circuits                       | 7  |

|   | 1.4  | Hybrid Applications                        | 8  |

|   | 1.5  | Paper Structure                            | 11 |

| 2 | Req  | uirements and Design                       | 13 |

|   | 2.1  | New Instructions                           | 13 |

|   | 2.2  | Example Usage of New Instructions          | 20 |

|   | 2.3  | General Interface                          | 22 |

| 3 | Imp  | lementation                                | 27 |

|   | 3.1  | Control Unit Modifications                 | 27 |

|   | 3.2  | Processor Modifications                    | 29 |

|   | 3.3  | System-Level Integration                   | 30 |

|   | 3.4  | FPGA Implementation                        | 31 |

|   | 3.5  | Sample Program Design Block Implementation | 34 |

| 4 | Res  | ults                                       | 39 |

|   | 4.1  | Simulation Process                         | 40 |

|   | 4.2  | Example: Sum M to N, Inclusive             | 41 |

|   | 4.3  | Example: Parity Checker                    | 48 |

| 5 | Futi | ure Work                                   | 55 |

| 5.1   | Use a Higher Capacity FPGA                    | 55 |

|-------|-----------------------------------------------|----|

| 5.2   | Add FPGA Instructions to the Instruction Set  | 56 |

| 5.3   | Add the FPGA to the System                    | 57 |

| 5.4   | Operating System Modifications                | 57 |

| 5.5   | Memory Access                                 | 59 |

| 5.6   | Programming Language Integration              | 60 |

| 5.7   | IDE Support                                   | 61 |

| 6 Wo  | orks Cited                                    | 62 |

| 7 App | pendix                                        | 63 |

| 7.1   | Instruction Format Reference                  | 63 |

| 7.2   | MIPS Instruction Set (Patterson and Hennessy) | 66 |

## Table of Figures

| Figure 1 - A Single Cycle Datapath (Patterson and Hennessy 287) | 4  |

|-----------------------------------------------------------------|----|

| Figure 2 – High-level conceptual CPU to FPGA diagram            | 11 |

| Figure 3 - Hybrid Program to Sum an Array                       | 21 |

| Figure 4 - Traditional Program to Sum an Array                  | 22 |

| Figure 5 - High-Level FPGA Design                               | 24 |

| Figure 6 - A Conceptual View of a Program Design Block          | 25 |

| Figure 7 Control Unit Modifications                             |    |

| Figure 8 Processor Modifications                                |    |

| Figure 9 System-level integration                               | 31 |

| Figure 10 FPGA Implementation                                   |    |

| Figure 11 PDB Control Unit                                      |    |

| Figure 12 Sample Program Design Block                           | 35 |

| Figure 13 Sample PDB Logic Unit                                 |    |

| Figure 14 FPGA Register File                                    |    |

| Figure 15 Assembler                                             | 41 |

| Figure 16 Software-only summation program                       | 42 |

| Figure 17 Hybrid summation program                              | 43 |

| Figure 18 Summation program PDB                                 | 44 |

| Figure 19 Summation program logic unit                          | 45 |

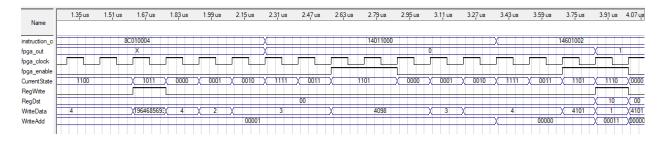

| Figure 20 Software-only summation program waveform              | 46 |

| Figure 21 Hybrid summation program waveform                     | 46 |

| Figure 22 Software-only parity checker                          | 49 |

| Figure 23 Hybrid parity checker                           | 50 |

|-----------------------------------------------------------|----|

| Figure 24 Parity checker program PDB                      | 51 |

| Figure 25 Parity checker program logic unit               | 52 |

| Figure 26 Software-only parity checker program waveform   | 53 |

| Figure 27 Hybrid parity checker program waveform          | 53 |

| Figure 28 - MIPS Instruction Set (Patterson and Hennessy) | 66 |

#### 1 Introduction

Field programmable gate arrays (FPGAs) have been used in a wide variety of applications and have many uses, such as teaching digital logic design, prototyping designs to verify their correctness and practicality, along with a great many other uses. This paper proposes an additional use of FPGAs to improve overall system performance by allowing application developers to implement parts of their application, or potentially the whole application, on the FPGA and to call it just like one would call a normal function in a programming language.

The performance of a system or an application could mean many things, such as the rate at which it performs a task, the amount of power it uses, the amount of memory it uses, along with other possible metrics. For the purpose of this paper, however, the concepts of performance and optimization will strictly refer to the speed of an application or a system, unless otherwise stated. But this paper is focused on optimizing applications, so they will be able to take less time to perform some task than would otherwise have been required.

Application designers have a wide variety of ways to optimize an application. Some of the more typical options include, but are not limited to, choosing more efficient data structures and algorithms, improving database performance for database-driven applications, reducing network latency or reducing the number of network calls for applications that call web services or are otherwise network dependent, choosing a compiled language over an interpreted language when possible, enabling compiler optimizations, multi-threading data access and computations that are parallelizable, implementing a caching strategy rather than making the same database or service calls repeatedly, along with many other ways to improve application performance depending on the specifics and architecture of the application.

Furthermore, some languages, such as C and C++, allow the developer the ability to write directly in assembly language as a way of conceivably optimizing critical portions of applications, although modern compilers employ sophisticated optimization techniques and are oftentimes very good and they are able to take advantage of optimizations like instruction reordering and replacing instructions with machine-specific instructions, along with a large number of other optimization techniques that might be difficult to perform by hand. But the idea is that a person who knows the architecture of the system for which they are writing the application, and who is good at writing assembly language, will be able to increase application performance by hand-optimizing portions of the application to take advantage of system-specific characteristics by specifying exactly which instructions will be executed. The idea proposed in this paper is similar to this idea except rather than writing a program that runs on a generalpurpose CPU, the developer will be able to bypass the CPU altogether and directly implement a circuit to perform the necessary algorithm, thereby improving the performance of the application by not having to go through all of the steps that a general-purpose CPU has to go through to lookup an instruction and execute it. The custom circuit, since it is designed to solve a single problem, is able to be optimized more than a general-purpose circuit.

When commencing a design, a software engineer has the choice to develop software for a general-purpose central processing unit (CPU) using languages such as C++ and Java, or to target a general-purpose graphics processing unit (GPGPU) using frameworks and libraries, such as OpenCL or CUDA, which are designed to target the massively parallel architecture of GPUs, or to implement the design in hardware. This paper proposes yet another choice: the hybrid hardware-software application.

#### 1.1 General-Purpose Processors

Most applications will be written using high-level programming languages such as C, C++, Java, or a wide assortment of other languages depending on the requirements of the application, the familiarity of the developers with the language, the portability requirements, along with other factors. Some of the main reasons of doing this are because of ease of development, reduced development and support costs, the simplicity of distributing the software, portability reasons, and because it is fast enough for most applications. These applications will consist of, at the most basic level, instructions that are executed by a processor. For interpreted languages, such as Python or scripting languages, such as shell scripts or JavaScript, the interpreter will parse the statements in the program and then execute those on the processor, but the interpreter itself, or some other program executing the interpreter, will be executed natively on the processor. For the processor implemented in this paper, it is based on the MIPS (Microprocessor without Interlocked Pipeline Stages) instruction set architecture (ISA) developed by MIPS Technologies. This has a datapath with five different stages that each instruction goes through (shown in Figure 1). This leads to some inefficiency.

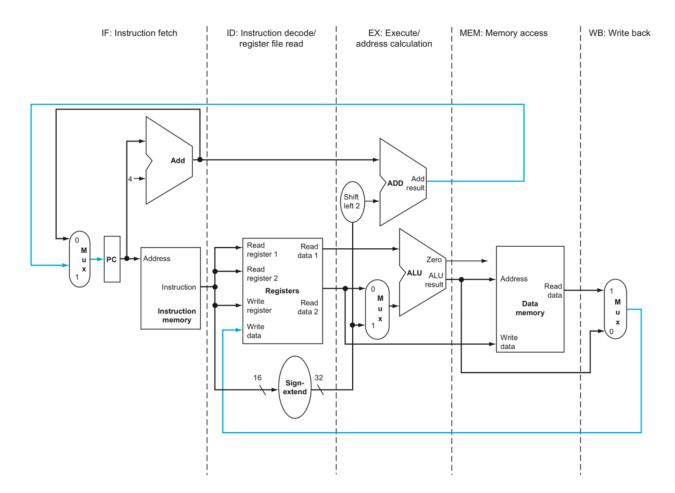

Figure 1 - A Single Cycle Datapath (Patterson and Hennessy 287)

The previous figure shows the datapath that is used for this paper. It has five stages, which are shown. The first stage is the "instruction fetch" stage. This is where the instruction is loaded from memory or disk and loaded into the instruction register. Next is the "instruction decode" step. This is where the instruction, which was previously loaded, is decoded so the processor knows what to do with it. The instruction will have different parts, such as the opcode, as defined in the instruction set architecture, and these different parts will be examined in the control unit to figure out what needs to be done with the instruction (such as whether to add two operands or to load a value from memory). The third is the actual execution phase. This is where, for some types of instructions, the instruction is actually performed (such as for ALU-based instructions like add or shift instructions). Next is the memory access step. This is where, as the

name implies, memory values are loaded or written for instructions that access memory values. Finally, the "write back" step is where any necessary values are written to the register file, if necessary.

To see an example of an instruction going through this datapath, consider the add instruction. The instruction **add** \$1, \$2, \$3 gets executed and takes five clock cycles to get through the datapath. It takes one clock cycle to load the instruction from disk or memory, which may be an expensive operation as disk IO rates are usually fairly low relative to the frequency of the clock used to drive the processor. Next, the instruction is decoded according to the instruction set architecture of the processor and the register file is read. Third, the instruction is executed. In this case, it uses the adder circuit in the arithmetic logic unit (ALU) to add the contents of registers two and three. Fourth, nothing happens as the next step is the memory access step, but memory is not being accessed for this instruction. Finally, the result of the computation is written to register three in the write-back step.

So, in this architecture, the add instruction takes five clock cycles to execute. The overall throughput of the system may be improved by using a pipelined datapath, but the individual instruction latency will still take five clock cycles for this add instruction.

If the only goal of this application was to add two numbers and return the sum, then a simple full adder could be built just to take the two addends and return their sum. This full adder would be the same as the full adder that is likely implemented in the ALU in the MIPS processor, but it would not need to fetch any instructions or decode the instruction or do the memory access or write back steps. It would simply be able to execute the add instruction in one clock cycle, the equivalent to the execute step of the MIPS datapath. Therefore, the latency of the instruction would go from five clock cycles to just one clock cycle. And some modern processor

architectures use pipelines that are much deeper pipelines - some go up to 17 pipeline stages, so even more of a reduction would be seen in such an architecture. Moreover, pipeline hazards, such as read after write data hazards or branch prediction errors, can lead to pipeline stalls and an even less efficient utilization of the hardware.

As another example, if the goal of the instruction is to only perform a logical left shift of the input by n-bits (such as the sll MIPS assembly instruction), the instruction still has to go through all the different stages in the datapath, such as trying to figure out what the instruction even is, before it will be able to perform the shift. This is true even if the processor has a barrel shifter implemented to perform the shifts in one clock cycle. It still must take the requisite number of clock cycles to get through the datapath.

But these examples are overly simple and not that useful for most applications. Most applications will likely use the add and shift instructions, but the goal of the application will be much more complicated than only that. What would really be helpful for improving the performance of an application would be to remove the overhead of the datapath of the generalpurpose processor and to implement the required functionality directly as a circuit that could be called, or invoked, like a function. This could be portions of an application, which are computationally expensive, or even the whole application for some cases. To get the best performance gains, more of the application should be written as hardware. At least, more contiguous chunks of it, such as an entire function. For example, if just an add statement or a shift statement is implemented as a circuit, then there would not be any gains over the instruction already implemented in the processor, and likely the performance would suffer because of the additional overhead involved with the communication between the processor and the circuit. More about this is discussed in chapter three.

#### **1.2 General-Purpose Graphics Processing Units**

Some applications, particularly those of a scientific or a mathematically-intensive nature and, perhaps unsurprisingly, graphically-intense applications, such as games, photo editing software, 3D animation software, along with other similar types of applications, may be able to take advantage of the massively parallel architecture of modern graphics processing units. Highend modern graphics processing units tend to have thousands of cores, each of which is usually very good at carrying out floating point arithmetic. Operations, such as matrix multiplication, matrix addition, and other mathematical operations that are parallelizable and of large size, are able to take advantage of the massively parallel architecture of GPUs. But for traditional nonscientific and single threaded applications, or applications of small size, the GPU may not help much or might be counterproductive for some problems. Even though the GPU has potentially hundreds or thousands of times the number of cores that are in the CPU, each core is a much simpler core than a core in the CPU and the GPU cores are not necessarily meant to execute individual instructions very quickly, but rather they focus on speed gains by executing a large number of small chunks of the problem simultaneously. Furthermore, GPUs can add extra expense to the overall system and can use a substantial amount of power. Additionally, development and debugging of such applications is typically much more difficult and is best suited for engineers that are trained and experienced in GPU programming, leading to higher maintenance costs for the companies who own the applications.

#### **1.3 Full Custom Circuits**

For some applications that have critical performance requirements, application designers may opt to design a full-custom application-specific integrated circuit (ASIC) to realize the application logic. While this should give the absolute best performance, it is extremely cost prohibitive as the upfront manufacturing costs can be in the millions of dollars and, once the circuit is developed, it is more difficult to distribute than a software-only application and it is not possible to provide updates without replacing the IC. As a result of these negatives, even though the performance would be much better than the same thing implemented on a general-purpose processor, the majority of companies and application developers will not choose this option unless it is absolutely necessary.

#### **1.4 Hybrid Applications**

This paper aims to bridge the gap between the ability to configure higher-level programs developed for general-purpose processors and the speed and efficiency of a direct hardware implementation by offering the ability for application developers to implement different portions, or functions, of their application directly in hardware, using an FPGA, while still being able to write the remainder of their application in normal programming languages. FPGAs are not as fast as a custom ASIC, but they are reconfigurable. The ability to reconfigure the device is important as this is meant to be deployed as part of a traditional software application, which will likely receive updates, and the hardware portion of the application may receive updates too. Furthermore, there will only be a certain amount of FPGA space for the entire system, so the operating system has to be able to load and unload functions dynamically to make room for currently running applications. To support a high number of concurrent program design blocks, modern FPGAs are dense in that they provide a high number of logic elements in a small footprint due to technologies such as 3D FPGAs, where layers of FPGAs are stacked on top of each other in the same package. So, by using an FPGA with a large number of logic elements, the system may provide more program design blocks to be used by applications.

Running the application logic on an FPGA would provide the benefit of being able to optimize portions of an application so they do not need to execute instructions anymore that need to go through all of the steps of the datapath, as was described earlier in this paper, but rather are able to invoke a specially designed circuit that realizes the necessary logic for the function. Furthermore, the application developer is no longer restricted to only the instructions that are in the instruction set of the processor but are rather able to directly implement whatever logic is required for their situation and, as a result, are able to execute more than one processor instruction per clock cycle.

In addition to the aforementioned benefits, a hardware implementation is able to take advantage of true parallelism, only limited by the size of the FPGA. For example, if an application needs to add more than one number at a time, then the hardware implementation could contain more than one full adder. Or if it needs to be able to do something more complicated than that in parallel, then likewise the circuitry of the required logic could be duplicated as required. A traditional application is limited in the parallelism it is capable of by the number of actual physical cores in the CPU (or, for GPGPU applications, then the number of cores in the GPU). It is possible for an application to be using more threads than the number of cores in the system, but if this happens, then the operating system will employ time slicing, or some other technique, to divvy up the time between all of the threads. This is fine for some situations where a thread may be stalled waiting for something to happen, but it does still limit the actual true parallelism of a system based on the number of physical cores available.

One downside to implementing the application logic directly in hardware, however, is that it may be more difficult to maintain and support. This is similar to the languages that allow inline assembly language to be used as an optimization technique. To support those applications, developers need to understand assembly language as well as the primary language the application is written in (likely C or C++). In a similar fashion, implementing part of the application in hardware could make it more difficult to support the application because then the developers would need to understand digital logic design. And while it is likely true that most software engineers would not have the necessary skillset to implement arbitrary logic as a circuit, or to be able to debug those systems, those parts of the application could be developed and supported by a team of hardware engineers while the rest of the application is developed and supported by software engineers.

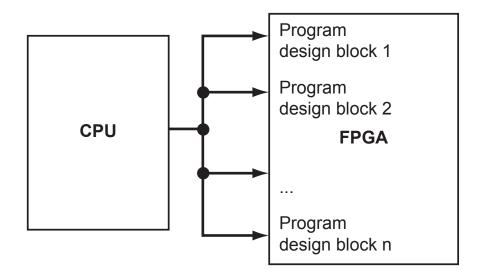

To achieve this goal of allowing arbitrary functions to be embedded in hardware directly, an FPGA will be added, alongside the CPU, and the two will be connected in a way such that special instructions in the CPU's instruction set will be able to issue different commands to the FPGA, such as being able to pass parameters to a function in the FPGA and to be able to enable and start a function in the FPGA. For the purpose of this paper, each function implemented in the FPGA will be referred to as a program design block. Refer to Figure 2 for a high-level depiction of what this looks like. This simplifies the actual implementation because it does not show any controller or how exactly the CPU is able to issue instructions to each program design block. The design and implementation details of this are provided in chapter 2 and chapter 3, but for now, it is just shown that the CPU is able to communicate with any of the program design blocks.

#### Figure 2 – High-level conceptual CPU to FPGA diagram

A given application may use one, or more program design blocks if necessary, and these program design blocks need to be able to be dynamically reprogrammed, as is deemed necessary by the operating system, to make room for newly loaded applications.

#### **1.5** Paper Structure

This chapter provided an overview of what the goal of this thesis is. That is, to allow application developers the ability to embed certain functions of their application directly in hardware. Chapter two further explains the idea by stating specifically what it is that the finished version of this project should be able to do (the requirements) and the high-level design of how this will be achieved. After this, chapter three discusses the actual implementation, with schematics and other details that show how the project was actually realized. Chapter four provides a few sample programs that were tested, along with the results of running those on just the CPU as a software-only application and the results of writing them as hybrid applications and converting portions of the application to hardware and running that on the FPGA. Chapter five describes what else could have been done to make the implementation in this project better or what would be necessary for this to be turned into a more production-ready implementation and possibly what could be some of the difficulties or issues faced trying to implement this in a production system. Chapter six is the appendix, where a full listing of supported instructions and the HDL and schematics that make up the processor used in this project may be found.

#### 2 Requirements and Design

To support hybrid applications as proposed in this paper, some modifications will be required to the processor to support communicating with the program design blocks on the FPGA. This includes additional instructions in the instruction set and a connection between the processor and the FPGA. This chapter presents the requirements of this project along with the corresponding design for each requirement.

#### 2.1 New Instructions

The instruction set and the instruction format used in the processor in this paper are based on the MIPS instruction set presented in (Patterson and Hennessy), which is shown in section 7.2. Additionally, a complete list of the implemented instructions may be found in the appendix in section 7.1.

The functional requirements around the new instructions are:

- 1. There needs to be a way to send arbitrary input (function parameters) to the program design block.

- 2. There needs to be a way to start the function implemented by the program design block. This will actually begin the processing.

- There needs to be a way to handle arbitrary output (the function return value) from the program design block.

- There needs to be a way to stop the program design block once it has been started.

This may be used by the program itself or the operating system.

- There needs to be a way to check if the program design block is done or if it is still processing.

The following set of instructions is introduced to satisfy the previous requirements. All of these instructions use a modified version of the R (register) instruction format presented in (Patterson and Hennessy). The instructions in this paper have the following fields in their machine language representations:

| ор     | rs     | rt     | 000    | index  | shamt  | funct  |

|--------|--------|--------|--------|--------|--------|--------|

| 6 bits | 5 bits | 5 bits | 3 bits | 2 bits | 5 bits | 6 bits |

- op this is the op-code of the instruction. It is used to differentiate this instruction from other instructions. Note, however, that it is possible for more than one instruction to have the same op-code. So, the op-code is not necessarily a one-to-one mapping to an instruction. For example, in the processor implemented in this paper, several instructions use op-code zero. If more than one instruction uses the same op-code, the distinction is then made based on the value in the funct field. For this paper, all of the new instructions will use an op-code of five (000101<sub>2</sub>) as this op-code is unused currently. Even though these instructions do not use the rd register, like the other r-type instructions, it would still be possible to reuse the same op-code that other r-type instructions use and just use a different value for the funct field, but a different op-code was selected because it better logically groups the new instructions together and allows for easier expansion to include new fpga\_\* instructions, if there is a need for that, without having to be concerned about no more possible funct values being available for the selected op-code.

- rs this is a source register. Depending on the instruction, it can have different meanings.

- rt this is another source register. Again, just like with rs, depending on the instruction, it can have different meanings.

- index this is a two-bit literal representing the index of the program design block that this instruction will use. In (Patterson and Hennessy) this, along with the three preceding bits, was the destination register, or rd. This was where the result of the instruction's computation or memory operation was stored. For these new instructions, however, only the two lower order bits will be used and this will tell FPGA unit which program design block is being used. This could have been a register so it would be more like the R-type instructions, but there are only going to be four program design blocks for this paper, which are addressable in two bits instead of requiring the full 32-bits that comes with the register, so rather than trying to read from possibly three registers at once or spreading out the register with the literal two bits required for the index. For future enhancements, there are the three unused bits that could be used as well, supporting up to 32 program design blocks if necessary.

- shamt the shift amount. This field is not used by any of these instructions and will always be zero. It would be possible to repurpose this field if necessary so it could be used for some instruction-specific purpose or to expand the funct field or the index field if necessary, but for the purpose of this paper, this field will be ignored.

- funct the function being implemented. This is used to make it possible to reuse the same op-code for more than one instruction. For all of the new r-type

instructions that will be added, they will all use an op-code of five. So, to allow the hardware to understand whether it is looking at an fpga\_set or an fpga\_call (these instructions will be explained next), the value of the funct field will allow this distinction.

**fpga\_set index, rs, rt** – This satisfies requirement one and it sets a parameter at the index specified by the source register, rs, to the value stored in the other source register, rt, for the program design block specified by the index operand. It is up to the program design block on how to handle parameters and how it stores them. One possible way of handling the storing of parameters is to have a register, or a collection of registers, or possibly even a memory block depending on how many parameters are required for the function.

Here is the machine language representation of the instruction, where rs, rt, and rd will be the five-bit representation of the register number used for those fields.

| 000101 | rs | rt | 000 | index | 00000 | 000000 |

|--------|----|----|-----|-------|-------|--------|

|--------|----|----|-----|-------|-------|--------|

To support arbitrary function parameters, such as lists, sets, maps, or other collections along with strings and other data types, it is up to the program design block how it interprets the inputs. For example, if an array of values needs to be passed to the program design block, then there could be two parameters supplied: one for the starting address in memory of the array and the other parameter could indicate the number of elements in the array, similar to how an array in C is passed. But how the program design block interprets and uses the parameter values that are supplied to it by the application are up to the application designer. Whether one parameter is interpreted as a literal value or an address pointing to a location in memory is an applicationspecific design decision. But with this level of flexibility, it is possible to pass arbitrary arguments, whether simple primitive data types or complicated data structures. Just for more complicated data structures, it might require more than one parameter to be passed to indicate the location, or locations, in memory to look for the actual data.

Example: fpga\_set 1, \$2, \$3, where 1 is the program design block index, \$2 is the index of the parameter (as is determined by the program design block controller), and \$3 is the value of the parameter. This will be assembled as 000101 00010 00011 000 01 00000 000000.

**fpga\_call index** – This satisfies requirement two and it invokes the program design block with the index specified by the index operand. This should be called after all of the parameters have been set using the fpga\_set instruction. Here is the machine language representation of the instruction, where index will be the two-bit representation of the program design block index. The values of the rs and rt fields are shown as zero, though it is inconsequential what is stored in those fields because they will not be used.

| 000101 |

|--------|

|--------|

Example: fpga\_call 1, where 1 is the index of the program design block to invoke. This would get assembled as 000101 00000 00000 000 01 00000 000001.

**fpga\_get index, rs** – This satisfies the third requirement and it gets the return value of the program design block specified by index and stores the return value in rs. For this instruction, the program design block should have the result ready to output within the same clock cycle when asked for it. If the computation is not done yet and the program design block is asked for the result, then the results are undefined. Depending on how the program design block is designed, it could be an intermediate result, or it could be some indeterminate value. Before calling this

instruction, it is best to call the fpga\_status instruction to make sure the program design block is done with its work.

Here is the machine language representation of the instruction, where rs will be the fivebit representation of the register number of where to store the results and index is the two-bit index of the program design block to query. The value of the rt field is shown as zero, though it does not matter what value is stored in that field because it will not be used.

| 000101 | rs | 00000 | 000 | index | 00000 | 000010 |  |

|--------|----|-------|-----|-------|-------|--------|--|

|--------|----|-------|-----|-------|-------|--------|--|

This instruction will only be able to return a single word. For longer return values, the program design block could write to memory and then return the starting memory address in the register rs for the application to be able to load from memory and process as required. It is up to the program design block and the application to determine how to handle the return value.

Example: fpga\_get 1, \$2, where \$2 holds the return value from the program design block and 1 is the index of the program design block from which to get the return value. This will be assembled as 000101 00010 00000 000 01 00000 000010.

**fpga\_halt index** – This is for the fourth requirement and it tells the program design block at the specified index to stop executing. The program design block could perform cleanup or reset itself so that it is ready for another invocation, though that is not required by this design. This is up to the application requirements and the actual responsibilities of the program design block itself. For example, if the program design block just takes in two numbers and sums them, then there probably is not much state to clear before being ready for subsequent invocations.

Here is the machine language representation of the instruction, where index will be the two-bit representation of the program design block index. The values of the rs and rt fields are shown as zero, though the contents of those fields are inconsequential because they will not be used.

| 000101 0 | 00000 00000 | 000 index | x 00000 | 000011 |

|----------|-------------|-----------|---------|--------|

|----------|-------------|-----------|---------|--------|

If this instruction is issued before processing is complete, then this will cause any return value retrieved by fpga\_get to be undefined, unless the program design block implements some special logic to be able to return some return value after halting. This may be used to stop the program design block from running, either because the application decides it does not require the result anymore, because the operating system kills the application for whatever reason, or for other reasons. If this is issued after the circuit is done processing, then this has no effect, unless the program design block is implemented such that it listens to halt instructions even when it is not processing, such as for the purpose of resetting the state of the program design block.

Example: fpga\_halt 1, where 1 is the index of the program design block to stop. This will be assembled as 000101 00000 00000 000 01 00000 000011.

**fpga\_status index, rs** – This is for the fifth requirement and it tells whether or not the program design block at the index specified by the index operand is done processing and rs is where the status indicator is stored. The program design block needs to be ready to respond to this query in the same clock cycle.

Here is the machine language representation of the instruction, where rs will be the fivebit representation of the register number used for storing the result of the instruction and index is the two-bit index of the program design block. The values of the rt field is shown as zero, though it is irrelevant what is stored in it because it will not be considered for this instruction.

| 000101 | rs | 00000 | 000 | index | 00000 | 000100 |  |

|--------|----|-------|-----|-------|-------|--------|--|

|--------|----|-------|-----|-------|-------|--------|--|

This instruction may actually be used as more than just a way to determine if the program design block has completed processing or not. This instruction may be used to return any status indicator to the calling program that it needs to. This includes error codes, warning codes, success codes, or whatever else the application designer wants to return. For the purpose of this paper, however, it will always be used just to return the ready indicator, unless otherwise documented. That is, for this paper, this instruction will always return a zero when it is not ready yet (the program design block is still processing) or a one when it is done. Error handling and error codes will not be returned in this paper for simplicity, but this use case is still permitted for more production-ready designs. The values returned and what they mean are defined and interpreted on an application-specific basis, so it is up to the application designer to fully define the return values of this instruction.

#### 2.2 Example Usage of New Instructions

To get a better idea of what the instructions do and how they are used, an example program listing is shown here that uses the new instructions. This program listing will just show the code that would be used, but not actually execute it. For this sample, the goal will be to take an array of integers and to sum the values in the array. The program design block is installed at index zero for the purpose of this example, though the program design block is not shown here. Also, the intermediate registers are not stored and restored after this function is over for the purpose of brevity. In a real production method, it would be typical to store and restore the intermediate registers (the registers that are not parameters or return values).

```

lw $1, 100

1

fpga set 0, $0, $1

2

3

addi $1, $0, 1

4

5

addi $2, $0, 101

fpga_set 0, $1, $2

6

7

fpga call $0

8

9

10 wait:

11 fpga status 0, $1

12 beq $1, $0, wait

13

14 fpga_get 0, $1

15

16 ;$1 now holds the sum of the array

17 ret

18

19 :100

20 data 3 ;the number of elements in the array

21 data 2

22 data 3

23 data 5

_

```

#### Figure 3 - Hybrid Program to Sum an Array

The previous code sample illustrates using the new instructions to call the necessary program design block. First, the parameters are set. The program design block takes two parameters. The first parameter is the number of elements in the array and the second parameter is the starting position in memory of the array. So first, parameter zero is set to the length of the array and parameter one is set to the memory address of the start of the array. Then it calls the program design block and then it waits for it to be done. The waiting is just a simple polling mechanism for this program, but depending on the nature of the problem, it may be more efficient to continue processing while the program design block is working and only check back on a sufficient schedule. But for the simplicity of this example and the fact that the whole purpose of this example is to compute the sum of the array and nothing else, a simple polling strategy was selected. Finally, after it is done computing the sum of the array, the sum is then placed in \$1.

As a contrast, here is the same program, but not written as a hybrid application, rather it is just a normal application. For this example, there probably would not be much of a performance boost at all to using the hybrid application because the size of the array is so small, but the purpose of this example is just to illustrate how to use the new instructions.

```

1

and $1, $0, $0 ;$1 holds the sum

addi $2, $0, 100 ;$2 is the memory address

2

lw $3, $2(0) ;$3 is the number of elements in the array

3

beg $3, $0, after

4

5

6

loop:

addi $2, $2, 1

7

lw $4, $2(0) ;$4 is the array element value

8

9

add $1, $1, $4

10 addi $3, $3, -1

11 bgt $3, $0, loop

12

13 after:

14 ; $1 now holds the sum of the array

15

16 ret

17

18 :100

19 data 3 ; the number of elements in the array

20 data 2

21 data 3

22 data 5

```

Figure 4 - Traditional Program to Sum an Array

#### 2.3 General Interface

For all of the new instructions described in section 2.1 to be possible, each program design block will need to conform to a general interface so that the processor will know how to

issue each instruction across any program design block. For this, it is likely that each program design block will implement a controller circuit that will accept the input from the processor and then determine how to handle that request. Several of these new instructions are very application-specific and do not have much in terms of defined requirements that they must meet, such as the fpga\_status instruction, which may return anything as long as the calling program understands it. But even though there is not much structure defined around the return value of those instructions or how they are implemented, each program design block will still need to recognize when it is being asked for the fpga\_status as opposed to the fpga\_get instruction. The processor will need to know how to communicate with the program design blocks, and as a result, each program design block will have to understand the same set of instructions.

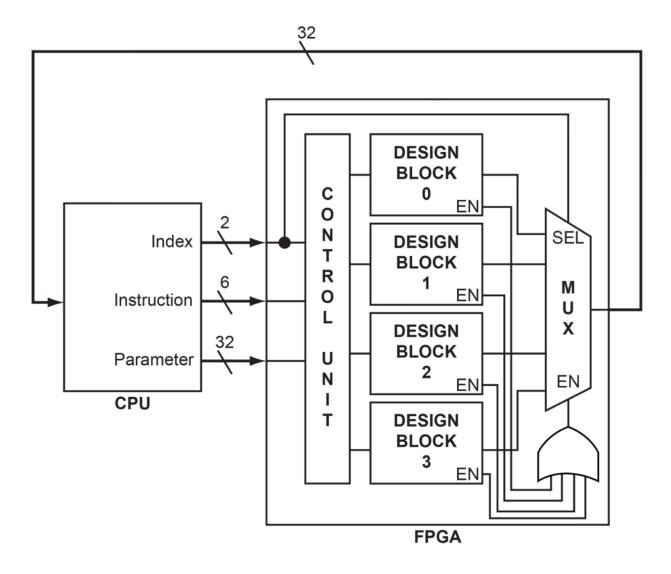

To fulfill this requirement, the processor will pass along the six-bit instruction field to the program design block, which will then need to take the appropriate actions to fulfill the request. A high-level block diagram is shown in Figure 5.

#### Figure 5 - High-Level FPGA Design

The previous figure shows a high-level diagram of the CPU-FPGA interconnects and the overall FPGA layout. It shows there only being four design blocks. While that is all that is being done for this paper, in an actual production-ready system, it should support more than four. In a production-ready system, the index line should likely be at least four or five bits, depending on the size of the FPGA used. But for simplicity and as a proof-of-concept, only four design blocks will be supported in this paper.

The control unit in the FPGA is used to select which design block to send the signals to. Other than that, it will just pass through the instruction and the parameter inputs. Each program design block outputs a value (for the fpga\_get and fpga\_status instructions) and it outputs an enable line. The enable line is used to turn on or off the multiplexer which is used to return a value to the CPU. Based on the index input, the multiplexer will output the output from the correct program design block if it is enabled.

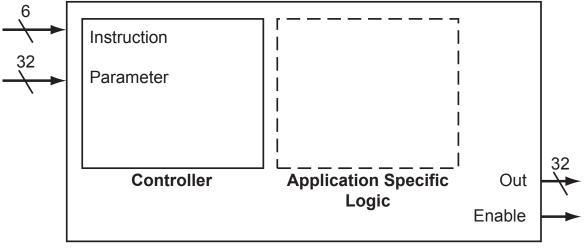

Each program design block will need to have a controller that will take in the instruction and the parameter inputs and then take the necessary action based on the inputs it receives. This controller is how each program design block will conform to the interface mentioned in this requirement. Figure 6 shows a very conceptual diagram of what a program design block should consist of.

Program Design Block

#### Figure 6 - A Conceptual View of a Program Design Block

The program design block has to take in the instruction input, so it knows what it is being asked to do, and it has to take in the parameter input, even though not all instructions will make use of the parameter input. Actually, only the fpga\_set instruction will supply this input. Based

on these inputs, the controller circuit will need to cause the application specific logic to do whatever is being asked. Figure 6 does not show any outputs from the controller and there are no inputs or outputs shown from the application specific logic. This is because it is completely up to the application designer how everything works inside the program design block. The only requirement is that it has the specified inputs and outputs and that it takes the requested action when asked to do so. Other than that, how it is actually implemented is not defined in this design.

#### 3 Implementation

This project was implemented and simulated using Altera Quartus II Version 7.2 Build 207 03/18/2008 SJ Web Edition. The circuit is designed to run on the Terasic DE2 board, which has the Altera Cyclone II EP2C35F672C6 FPGA.

To implement the project requirements as described in the previous chapter, a few modifications to the processor described in (Patterson and Hennessy) were necessary, all of which are described in this chapter. This includes the modifications to the control unit to handle the new instructions and the processor make use of the new control lines for the FPGA instructions. Additionally, this chapter shows how the FPGA unit was integrated with the rest of the system, such as the processor. Finally, the FPGA unit is shown along with a sample program design block.

#### 3.1 Control Unit Modifications

The control unit in the processor is a state machine that has been implemented in VHDL. To support the new FPGA instructions, three new states have been added: FPGA, FPGA\_READ, and FPGA\_DELAY. The FPGA state enables the FPGA unit and then, depending on whether the FPGA instruction is a read instruction or not, it goes to either the FPGA\_READ or FPGA\_DELAY state, respectively. The FPGA\_READ state sets the MemtoReg and RegDst outputs so that the output from the program design block is written to the register specified by bits 25..21 of the instruction (the rs register). The FPGA\_DELAY is added so that necessary FPGA register writes have the time to write the value to the necessary register.

```

entity control_unit is

port(

...

fpga_enable : out std_logic

);

end control unit;

```

```

architecture behavior of control unit is

type state type is (..., FPGA, FPGA READ, FPGA DELAY);

case y is

...

when B =>

elsif Op="000101" then --FPGA-related opcode

y<=FPGA;

•••

end if;

when FPGA =>

CurrentState<="1101";</pre>

fpga enable<='1';</pre>

--fpga get or fpga status

if funct="000010" or funct="000100" then

y<=FPGA READ;

else

y<=FPGA DELAY;

end if;

when FPGA READ => --fpga get or fpga_status

CurrentState<="1110";</pre>

--these instructions need to read the

--value produced by the FPGA

--and store this value in the register A

MemtoReg<="100"; --use the output from the FPGA

RegWrite<='1';</pre>

--this chooses register A (instruction[25..21])

--as the destination register

ReqDst<="10";</pre>

fpga enable<='1';</pre>

y<=A;

when FPGA DELAY =>

--this just delays the instruction to give

--the FPGA time to perform the necessary action

CurrentState<="1101";</pre>

y<=A;

```

#### Figure 7 Control Unit Modifications

The FPGA\_DELAY state could have been removed by increasing the clock frequency of the clock signal for the FPGA unit so that it is approximately at least twice the frequency of the

processor's clock signal. This would allow there to be a rising edge of the clock, necessary for the FPGA unit to write to its register, during one clock cycle of the processor's clock. This was not done because, for performance comparison purposes, it was desirable to have the same clock frequency driving the FPGA unit, though in a productionized system, it could supply a higher frequency clock signal to the FPGA unit if there is one available.

Another way to remove the extra delay state is to phase shift the clock signal about half a period or so. This could be done using something like a phase locked loop (PLL) or simply negating the clock signal, which would essentially phase shift the clock signal by half a period, or, equivalently, the falling edge of the clock could have been used to trigger the register writes. These options were not selected because the risk that the half clock cycle time for the write instruction to propagate to the FPGA unit was not worth just losing one extra clock cycle and being guaranteed the write would have time to get to the FPGA unit. Again, in a production system, something like this would probably be more closely evaluated, but for the purposes of this paper, a one extra clock cycle delay was not significant enough to warrant the extra risk.

#### **3.2 Processor Modifications**

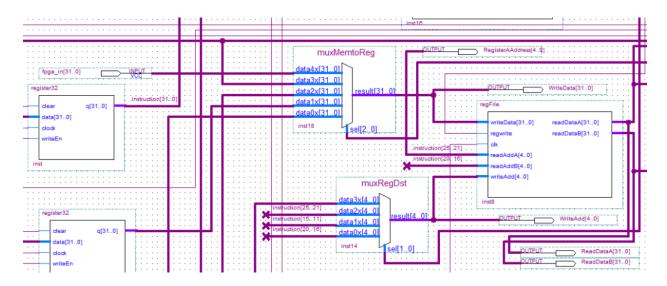

To support the requirement to have the FPGA read instructions (fpga\_status and fpga\_get) to be able to read from the FPGA program design blocks and write the result to a register, it is necessary to modify the multiplexor which controls the data that is written to the register file. The extra input, called fpga\_in, is added to the memory-to-register multiplexor as input four (100<sub>2</sub>). In the previous section, the control unit was modified to set the MemtoReg output to a value of four to select the value that is coming from the FPGA.

## Figure 8 Processor Modifications

The FPGA read instructions, fpga\_get and fpga\_status, which use this new input, write to the rs register, as was specified in the requirements in the previous chapter. The rs register is specified by instruction[25..21], select line two (10<sub>2</sub>) of the register destination multiplexor.

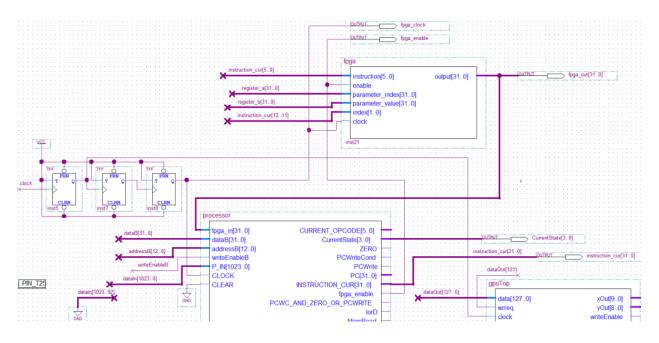

## 3.3 System-Level Integration

Outside the processor, the FPGA unit needs to be connected and integrated with the rest of the system. To do this, an output signal from the processor, fpga\_enable, was added that will enable the FPGA unit to receive new instructions. This is turned on from the control unit of the processor and is only enabled for two clock cycles during an FPGA instruction. Without the enable input being high, the FPGA program design blocks will still be able to perform their work, it is just that no new instructions will be able to be received as long as the fpga\_enable line is not high.

In addition to the output from the processor, there is an input to the processor too that comes from the FPGA unit. This is called the fpga\_in bus and it is 32 bits wide to match the size of the registers, since these values will be written to the register specified by the instruction. This is used for instructions that read from the FPGA, such as the fpga\_get and fpga\_status instructions. This is just the output from those instructions. For example, for the fpga\_get instruction, this would be the computed return value. For the fpga\_status instruction, this could be the current status (either not done or done) or it could be a percentage complete, or it could contain an error code, or whatever else the application designer would deem useful.

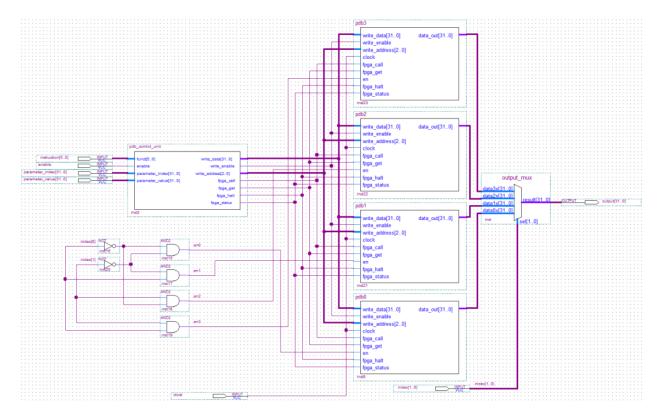

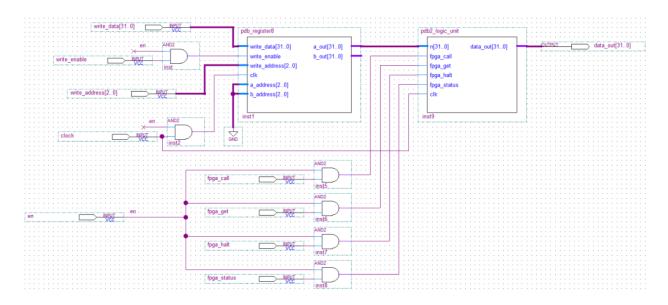

## 3.4 FPGA Implementation

Inside the FPGA unit, only four program design blocks are shown for simplicity. However, in a real production implementation of this, more program design blocks should be allowed as this is to be possibly shared by more than one currently active application, as defined or permitted by the operating system. The operating system will also be responsible for loading and unloading the individual program design blocks and assigning them to an index in the FPGA unit, but the modification of the operating system to support dynamically loading and unloading these program design blocks is outside the scope of this paper.

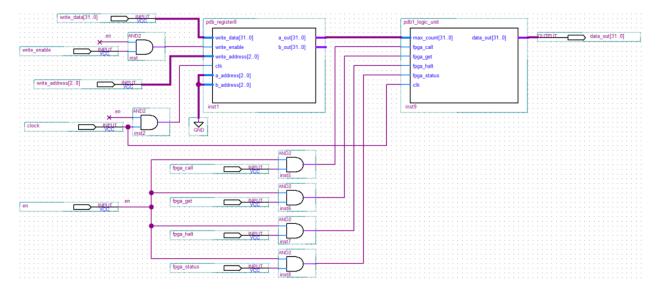

# Figure 10 FPGA Implementation

A simple line decoder is implemented to gate access to the correct program design block, based on the index input. Only one program design block may be accessed (read from or written to) in a single clock cycle. The enable input that goes to the pdb\_control\_unit will turn on or off writes along with the functionality in the program design block and the enable that comes from the index decoder will turn on only the program design block at the specified index, while turning off the other units. This means that no matter what the inputs are from the control unit, if the index is not the same as the index of the program design block, then the program design block will ignore the inputs. If it was already processing, however, it will still be able to continue processing. This allows more than one PDB to be processing concurrently. Only writes to or reads from the program design block are limited to one per clock cycle.

The pdb\_control\_unit is simple and just determines which FPGA instruction is being

issued and whether to write to the register file of the specified program design block, as is shown

```

in Figure 11.

library ieee;

use ieee.std logic 1164.all;

use ieee.std logic arith.all;

use ieee.std logic signed.all;

entity pdb control unit is

port(

funct : in std logic vector(5 downto 0);

enable : in std logic; --active high enable signal

parameter index : in std logic vector(31 downto 0);

parameter value : in std logic vector(31 downto 0);

write data : out std logic vector(31 downto 0);

write enable : out std logic;

write address : out std logic vector(2 downto 0);

fpga call : out std logic;

fpga get : out std logic;

fpga halt : out std logic;

fpga status : out std logic

);

end pdb control unit;

architecture behavior of pdb control unit is

begin

process(funct, enable, parameter index, parameter value) begin

if enable='1' then

if funct="000000" then -- fpga set

write enable<='1';</pre>

write address<=parameter index(2 downto 0);</pre>

write data<=parameter value;</pre>

fpga call<='0';</pre>

fpga get<='0';</pre>

fpga halt<='0';</pre>

fpga status<='0';</pre>

elsif funct="000001" then -- fpga call

write enable<='0';</pre>

fpga call<='1';</pre>

fpga get<='0';</pre>

fpga halt<='0';</pre>

fpga status<='0';</pre>

```

```

elsif funct="000010" then -- fpga get

write enable<='0';</pre>

fpga get<='1';</pre>

fpga call<='0';</pre>

fpga halt<='0';</pre>

fpga status<='0';</pre>

elsif funct="000011" then -- fpga halt

write enable<='0';</pre>

fpga halt<='1';</pre>

fpga call<='0';</pre>

fpga get<='0';</pre>

fpga status<='0';</pre>

elsif funct="000100" then -- fpga status

write enable<='0';</pre>

fpga status<='1';</pre>

fpga call<='0';</pre>

fpga get<='0';</pre>

fpga halt<='0';</pre>

end if;

else

write enable<='0';</pre>

end if;

end process;

end behavior;

```

Figure 11 PDB Control Unit

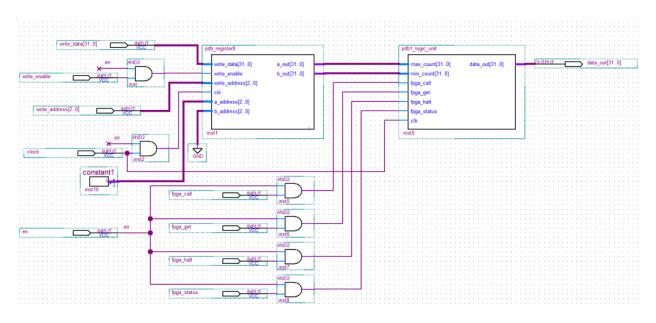

# 3.5 Sample Program Design Block Implementation

How the individual program design blocks are implemented is an application-specific detail, but Figure 12 shows a simple reference implementation. Most program design blocks should probably look somewhat similar to this as there is no application logic here, though the choice of how to store parameters may vary. For example, here a register file with eight registers is used even though only one register is actually used. The reason for this is to allow all of the examples in this paper to reuse this register file design without having to design a separate register file for each example. But in a production system, this could likely be synthesized by the design tools so that the application designer does not need to specify the program design block

implementation. Instead, they would be able to focus on the implementation of the logic unit, which is where the application-specific logic goes. The register file is shown in Figure 14.

# Figure 12 Sample Program Design Block

The pdb\_logic\_unit is where the application-specific logic goes. It takes the value(s) in from the register along with the signals from the pdb\_control\_unit, which indicate the current instruction, and it processes the data as is required by application requirements. Figure 13 shows a template of a simple implementation. This does not show any actual logic, but rather just a template of how to handle the inputs. A complete implementation will be shown in chapter 4.

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_signed.all;

entity pdb_logic_unit is

port(

max_count : in std_logic_vector(31 downto 0);

fpga_call : in std_logic;

fpga_get : in std_logic;

fpga_halt : in std_logic;

fpga_status : in std_logic;

clk : in std_logic;

data out : out std logic vector(31 downto 0)

```

```

);

end pdb logic unit;

architecture behavior of pdb logic unit is

signal enable : std logic;

--Application-specific signals or variables

begin

process(clk) begin

if clk'event and clk='1' then

if enable='1' then

--This is where the application-specific processing

--could go. Perform necessary computations as long

--as the processing is not complete.

end if;

if fpga halt = '1' then

enable <= '0';</pre>

--Perform any application-specific cleanup here, or

--that could be performed in the fpga call statement.

elsif fpga status = '1' then

--Populate the data out output with the application-

--specific status codes. This could be as simple as

--zero means not done, and one means done, or it could

--have error codes or different status codes, such as

--a percent complete, if available. This is completely

--up to the application designer.

elsif fpga get = '1' then

--Populate the data out output with the current

--computation results. If the computation is not

--complete, then the return value here is undefined

--and it is up to the application designer how to handle

--this.

elsif fpqa call = '1' then

enable <= '1';</pre>

--Start the computation process. This could also

--perform any cleanup or resetting that needs

--to be done between invocations.

end if;

end if;

end process;

end behavior;

```

#### Figure 13 Sample PDB Logic Unit

The register file used here contains eight registers that are each 32-bits wide, and it allows reading from two registers at once. The dual port register file is used in one of the

examples in the next chapter that takes in two parameters. In general, for each parameter the circuit requires, a new read port would be added to the register file to accommodate the additional parameter.

This register file is used for all of the examples in this paper, even though not all of the examples actually use all of the registers. This is so that it will not be necessary to design separate register files for each example. In a real, production-ready, system however, a more appropriate register system would most likely be selected. For example, if only one parameter is used, then a single register could be used, instead of eight. As has been previously mentioned, this is also something that would likely be automated and abstracted away from the application developer and synthesized by the design tools. All the application developer should have to focus on is the implementation of the logic unit.

```

1 library ieee;

use ieee.std logic 1164.all;

2

use ieee.std logic arith.all;

3

use ieee.std logic signed.all;

4

5

6

--This is used to store the parameters of a FPGA program

7

--design block (pdb) but it is just a register file.

8 entity pdb register8 is

9

port(

10

write_data : in std_logic_vector(31 downto 0);

11

write enable : in std logic;

12

write address : in std logic vector(2 downto 0);

clk : in std logic;

13

14

a_address : in std_logic_vector(2 downto 0);

15

b address : in std logic vector(2 downto 0);

16

17

a_out : out std_logic_vector(31 downto 0);

18

b out : out std logic vector(31 downto 0)

19

);

20

end pdb register8;

21

22 architecture behavior OF pdb register8 IS

type register file is array (0 to 7) of std logic vector(31 downto 0);

23

24

signal register_array : register_file;

25

26 Ebegin

27

a out<=register array(CONV INTEGER(a address));</pre>

28

b_out<=register_array(CONV_INTEGER(b_address));</pre>

29

30

process begin

31

wait until clk'event and clk='1';

32 🔳

if write enable='l' then

33

register array(CONV INTEGER(write address))<=write data;</pre>

34

end if;

35

end process;

36

end behavior;

```

Figure 14 FPGA Register File

#### 4 Results

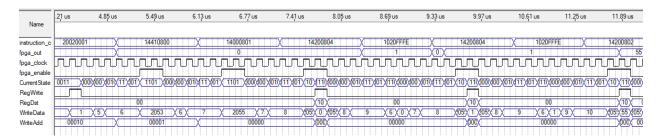

This section of the paper shows the performance differences between the software-only application and the hybrid software-hardware application. The processor used in this paper is not pipelined, so each instruction takes several clock cycles to complete and the clock frequency used to drive the processor is 6.25MHz. Both of these factors affect the speed of the program that is simulated and in a modern commercial system, the processor would be pipelined, and the clock frequency would be much higher than the frequency used for this paper. However, neither of these factors affect the ability to compare the software-only implementation and the hybrid implementation. Both implementations are run on the same processor.

If the processor was pipelined, then it would be possible to have an average rate of one clock cycle per instruction, which is known as a scalar processor. As is, the average rate of clock cycles per instruction is much more than one, or sub-scalar. But this is true for the new FPGA instructions as well as for the regular instructions, since they are all running on the same processor. The comparisons in this section count the number of instructions that are used by the software-only implementation and the hybrid implementation. This way the results are not tied to how many clock cycles each example takes to complete, as this would vary between a sub-scalar and scalar processor, but rather the number of instructions executed, which is a more fair comparison as it is not dependent on the architecture of the processor on which the program is run.

This section shows the hybrid implementation outperforms the software-only implementation because the hardware logic is not limited to only the instructions in the instruction set of the processor, but rather can implement any arbitrary logic. This allows something that would normally take several processor instructions to complete to execute in a single instruction. For example, the parity computation performed in section 4.3 illustrates this concept by performing a bitwise exclusive-or on all 32 bits of the input in one instruction, whereas the software-only implementation takes several instructions per bit. This is just one example. But one of the benefits of the hybrid approach is that application-specific logic that normally takes many instructions on a general-purpose processor to execute can be executed much more efficiently since it is not limited by the instruction set of the processor.

#### 4.1 Simulation Process

The programs in this paper were all assembled using a custom assembler made for this processor, shown in Figure 15. This produces a memory initialization file that is loaded into the memory unit from which the processor reads. The program is then simulated using the simulator provided in Altera Quartus II 7.2.

This same simulation process is followed for both the software-only program and the hybrid software-hardware program. The results of the simulation are then compared by examining the number of instructions required by each version of the program.

| 🕌 MIPS As:                                                                                                                                                                                                               | embler - C:\th                                                                                                                                                                                       | esis\sum                                                                                            | - 🗆                                                                                                                                                                                     | $\times$ |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| <u>File Edit E</u>                                                                                                                                                                                                       | Build <u>T</u> ools                                                                                                                                                                                  |                                                                                                     |                                                                                                                                                                                         |          |

| 1 2                                                                                                                                                                                                                      |                                                                                                                                                                                                      |                                                                                                     |                                                                                                                                                                                         |          |

| Source Edi                                                                                                                                                                                                               | tor - sum 🛛 🖡                                                                                                                                                                                        | Project Assembly                                                                                    |                                                                                                                                                                                         |          |

| 2 addi \$2<br>3 addi \$3<br>4<br>5 loop:<br>6 add \$1,<br>7 addi \$2<br>8 bge \$3,<br>9<br>10 ;\$1 non<br>11 exit<br>12<br>13<br>14 ;;this<br>15 ;addi \$<br>16 ;fpga_1<br>20 ;fpga_2<br>21 ;<br>22 ;loop:<br>23 ;fpga_2 | <pre>c, \$2, 1<br/>\$2, loop<br/>r holds the<br/>calls pdb1<br/>s1, \$0, 1<br/>set 1, \$0, 1<br/>set 1, \$0, 10<br/>s2, \$0, 10<br/>set 1, \$2, \$<br/>sall 1<br/>status 1, \$<br/>; \$0, loop</pre> | f<br>sum M + (M+1) + + N<br>to sum the integers between 1 and \$1<br>;1                             | fpga_set<br>fpga_set<br>fpga_status<br>hex_digiti<br>jal<br>jmp<br>jr<br>lcd_char<br>lcd_chari<br>ldb<br>ldby<br>ldhw<br>ldw<br>ldw<br>lw<br>mod<br>modi<br>modu<br>modui<br>mov<br>mul |          |

| 27 ;exit                                                                                                                                                                                                                 |                                                                                                                                                                                                      |                                                                                                     | muli<br>mulu<br>mului                                                                                                                                                                   | -        |

| Branch on Gre                                                                                                                                                                                                            |                                                                                                                                                                                                      | offset16<br>ial - Branch to (pc+offset16) if \$compare1 >= \$compare2, else go to next instruction. |                                                                                                                                                                                         |          |

| Туре                                                                                                                                                                                                                     | Line                                                                                                                                                                                                 | Decription                                                                                          |                                                                                                                                                                                         |          |

| INFO                                                                                                                                                                                                                     | Ling                                                                                                                                                                                                 | Assembling file: sum                                                                                |                                                                                                                                                                                         |          |

| INFO                                                                                                                                                                                                                     | 5                                                                                                                                                                                                    | The current address of line 5 is 3                                                                  |                                                                                                                                                                                         |          |

| TIMING                                                                                                                                                                                                                   |                                                                                                                                                                                                      | Completed in 0.001187719 seconds                                                                    |                                                                                                                                                                                         |          |

| OUTPUT                                                                                                                                                                                                                   |                                                                                                                                                                                                      | Writing to: C:\thesis\sum.mif                                                                       |                                                                                                                                                                                         |          |

| SUMMARY                                                                                                                                                                                                                  |                                                                                                                                                                                                      | Success, 0 errors and 0 warnings during assembly.                                                   |                                                                                                                                                                                         |          |

Figure 15 Assembler

# 4.2 Example: Sum M to N, Inclusive