# University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

12-2014

# A Phase-Locked Loop in High-Temperature Silicon Carbide and General Design Methods for Silicon Carbide Integrated Circuits

Paul Shepherd University of Arkansas, Fayetteville

Follow this and additional works at: http://scholarworks.uark.edu/etd

Part of the VLSI and Circuits, Embedded and Hardware Systems Commons

#### Recommended Citation

Shepherd, Paul, "A Phase-Locked Loop in High-Temperature Silicon Carbide and General Design Methods for Silicon Carbide Integrated Circuits" (2014). Theses and Dissertations. 2013. http://scholarworks.uark.edu/etd/2013

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, ccmiddle@uark.edu.

# A Phase-Locked Loop in High-Temperature Silicon Carbide and General Design Methods for Silicon Carbide Integrated Circuits

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

by

Paul Darrow Shepherd

University of Arkansas

Bachelor of Science in Electrical Engineering, 2001

University of Texas

Master of Science in Electrical Engineering, 2008

## December 2014 University of Arkansas

| This dissertation is approved for recomm   | mendation to the Graduate Council. |  |

|--------------------------------------------|------------------------------------|--|

| Dr. H. Alan Mantooth Dissertation Director |                                    |  |

| Dr. A. Matthew Francis Committee Member    | Dr. Roy McCann<br>Committee Member |  |

| Dr. Simon Ang                              | Dr. Jia Di Committee Member        |  |

#### **ABSTRACT**

Silicon carbide (SiC) has long been considered for integrated circuits (ICs). It offers several advantages, including wider temperature range, larger critical electric field, and greater radiation immunity with respect to Silicon (Si). At the same time, it suffers from challenges in fabrication consistency and lower transconductance which the designer must overcome. One of the recent SiC IC processes developed is the Raytheon High-Temperature Silicon Carbide (HTSiC) complementary MOSFET process. This process is one of the first to offer P channel MOSFETs and, as a result, a greater variety of circuits can be built in it.

The behavior of SiC MOSFETs has some important differences with Si MOSFETs.

Models such as the Shichman-Hodges, EKV, and Short-channel models have been developed over time to address the important behaviors observed in Si MOSFETs, but none of these captures all of the important effects in SiC. In this work, an improved Shichman-Hodges model that incorporates the body-charge effect, mobility reduction, and a nonlinear channel modulation is developed for SiC CMOS IC devices. The importance of considering these effects is demonstrated with a simple design exercise.

This dissertation also describes the design and testing of the first-ever phase-locked loop (PLL) in SiC. This PLL is suitable for use as a general circuit building block such as in a clock recovery circuit. The fabricated circuit operates between 600 kHz and 1.5 MHz, and at temperatures up to 300 °C. Testing results also show that output jitter and locking are negatively impacted at higher temperatures, and an improved design is proposed and analyzed.

©2014 by Paul Shepherd All Rights Reserved

#### ACKNOWLEDGEMENTS

Every doctoral student is product of the environment in which he or she works. The University of Arkansas Mixed-Signal CAD lab is very much a community and a team. I would like to thank Dr. Alan Mantooth for his foresight and leadership in creating and growing this program and for finding the unique individuals and research opportunities that exist here. I would also like to thank the students who were both co-workers and comrades-in-arms: Caleb Gutshall, Kacie Woodmansee, Chris Lee, Mihir Mudholkar, Javier Valle-Mayorga, Michael Glover, Matt Barlow, Nick Chiolino, Ashfaqur Rahman, Andrew Taylor, Dillon Kaiser and others.

Through research partnerships with industry, I have also had the opportunity to learn a great deal from several individuals outside the UA: Ty McNutt at APEI, Nance Ericson at ORNL, Adam Barkley and Sei-Hyung Ryu at Cree, and Ewan Ramsey and Robert A. R. Young at Raytheon.

Finally, I would like to thank Dr. Matt Francis and Jim Holmes at Ozark Integrated Circuits. They have been both mentors and friends during my academic career.

Perhaps more important than the academic support a doctoral student receives is the personal support. For that I can never give enough thanks to my sister, Dr. Stephanie Shepherd, and my wife, Laura-Rose Russell Shepherd.

# **DEDICATION**

This dissertation is dedicated to my daughter, River April Shepherd, who will always be my greatest contribution to the world.

# TABLE OF CONTENTS

| Chapter 1 – Introduction                                                         |

|----------------------------------------------------------------------------------|

| 1.1 Applications of Phase-Locked Loops                                           |

| 1.2 Organization of this dissertation                                            |

| Chapter 2 - Background                                                           |

| 2.1 Wide Bandgap Materials5                                                      |

| 2.2 The Raytheon Silicon Carbide CMOS Process                                    |

| 2.3 Phase-Locked Loops                                                           |

| 2.3.1 Phase Frequency Detectors                                                  |

| 2.3.2 Charge Pumps                                                               |

| 2.3.3 Voltage-Controlled Oscillators                                             |

| 2.2.4 Delay Stage Topologies                                                     |

| Chapter 3 – Device Parameters for Silicon Carbide CMOS                           |

| 3.1 Using the Standard Shichman-Hodges Model with SiC                            |

| 3.2 Parameter Estimation, Bias Point Selection, and Standard Device Sizes in the |

| Standard Shichman-Hodges Model                                                   |

| 3.3 An Improved Shichman-Hodges Model for SiC MOSFETs                            |

| 3.4 Summary of Relevant Short Channel Behaviors for SiC MOSFETs                  |

| 3.4.1 Mobility Reduction                                                         |

| 3.4.2 Bulk Charge Effect                                                         |

| 3.4.3 Soft Saturation                                              |

|--------------------------------------------------------------------|

| 3.4.4 Nonlinear Channel Modulation                                 |

| 3.5 Large- and Small-Signal Equations                              |

| 3.6 Improved Shichman-Hodges Parameters for HTSiC devices          |

| 3.7 Design Implications of the Improved Shichman-Hodges Parameters |

| Chapter 4 – Circuit Design, Simulation, and Layout                 |

| 4.1 Design Heuristics for SiC CMOS                                 |

| 4.2 PLL System Topology65                                          |

| 4.3 The Phase-Frequency Detector                                   |

| 4.4 Charge Pump and Loop Filter                                    |

| 4.5 Voltage-Controlled Oscillator                                  |

| 4.6 System Design and Simulation                                   |

| 4.7 Circuit Layout91                                               |

| Chapter 5 – Circuit Testing                                        |

| 5.1 VCO Yield Testing at Room Temperature                          |

| 5.2 Charge Pump DC Testing at Room Temperature                     |

| 5.3 Basic Functional Testing of the Phase-Frequency Detector       |

| 5.4 VCO Simulations and Frequency at Room Temperature              |

| 5.5 Complete PLL Transient Testing across Temperature              |

| Chapter 6 – Improved Design of a SiC Phase-Locked Loop             |

| 6.1 Modifications to the PFD                       | 115 |

|----------------------------------------------------|-----|

| 6.2 Modifications to the Charge Pump               | 117 |

| 6.3 Modifications to the VCO                       | 118 |

| 6.4 Complete System Design                         | 123 |

| 6.5 PLL Layout for Tapeout 2                       | 129 |

| Chapter 7 – Conclusions and Future Work            | 133 |

| 7.1 Conclusions                                    | 133 |

| 7.2 Future Work                                    |     |

| Bibliography                                       | 136 |

| Appendix A – Modified Shichman-Hodges Fitting Code | 140 |

# LIST OF FIGURES

| Fig. 1.1. (a) A PLL motor speed control system and (b) PLLs used in a serial data                     |

|-------------------------------------------------------------------------------------------------------|

| communication scheme                                                                                  |

| Fig. 1.2. An isolated data transmission system utilizing the described PLL along with a               |

| comparator and D flip-flop                                                                            |

| Fig. 2.1. Drift Regions in Lateral and Vertical MOSFETs                                               |

| Fig. 2.2. Simplified cross-section of the Raytheon HTSiC CMOS process                                 |

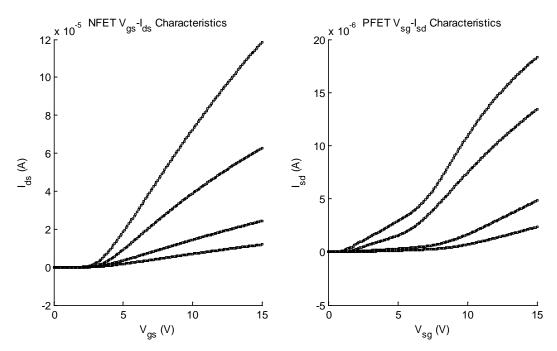

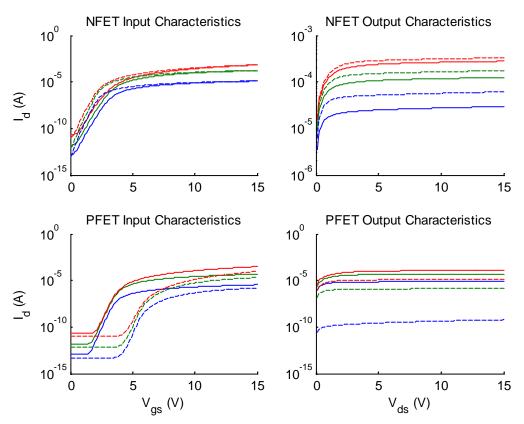

| Fig. 2.3. NFET and PFET characteristics at $V_{gs}\left(V_{sg}\right)=5$ V at room temperature. W/L = |

| $20~\mu m/1.2~\mu m, 20~\mu m/2~\mu m, 20~\mu m/5~\mu m, and 20~\mu m/10~\mu m.$ $12$                 |

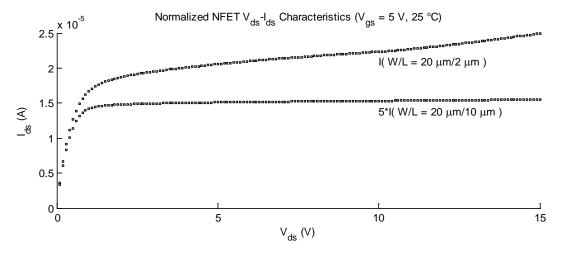

| Fig. 2.4. NFET $V_{ds}$ - $I_{ds}$ curves normalized for W/L                                          |

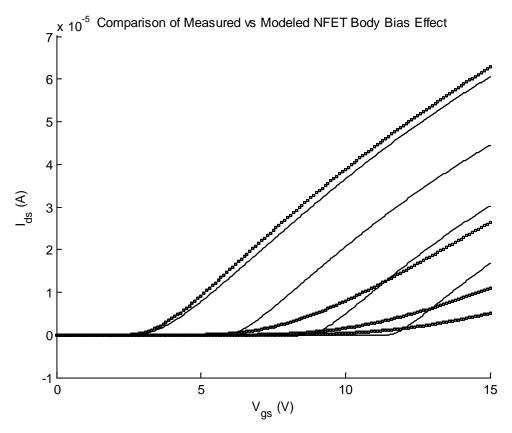

| Fig. 2.5. Comparison of measured and modeled body bias effects in the NFET with W/L                   |

| = 20 $\mu m/2~\mu m$ at $V_{gs}$ = 5 V. $V_{sb}$ = 0 V, 3 V, 6 V, and 9 V                             |

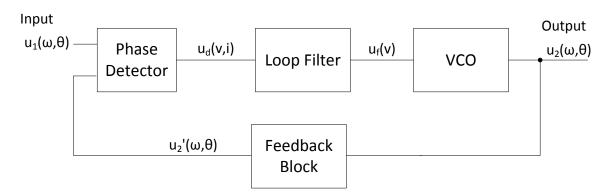

| Fig. 2.6. General control-loop topology of a PLL                                                      |

| Fig. 2.7. Control loop implementation of the charge-pump PLL and the resulting Laplace-               |

| domain transfer function, natural frequency and damping ratio                                         |

| Fig. 2.8. State Diagram of the PFD                                                                    |

| Fig. 2.9. Time-averaged output functions for different phase detectors versus input phase.            |

|                                                                                                       |

| Fig. 2.10. Functional diagram of the charge pump                                                      |

| Fig. 2.11. LC Tank (Hartley) Oscillator (a), Relaxation (Source-Coupled) Oscillator (b),              |

| and Ring (Current-starved Inverter) Oscillator (c)                                                    |

| Fig. 2.12. Barkhausen criterion applied to single-ended and differential ring oscillators of          |

| N stages.                                                                                             |

| Fig. 2.13. Current-starved inverter delay stage                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------|

| Fig. 2.14. Differential delay cell with resistive loads                                                                        |

| Fig. 2.15. Maneatis delay cell found in differential VCOs                                                                      |

| Fig. 2.16. Symmetric load output behavior at different values of $V_{\text{control}}$ with respect to $V_{t}$ .                |

|                                                                                                                                |

| Fig. 2.17. Half-buffer replica biasing circuits for the Maneatis delay cell. The circuit in                                    |

| (a) has a single control input voltage that sets the bias current and the delay cell output swing,                             |

| while the circuit in (b) forces the output swing to be fixed at $V_{\text{ref}}$ , and $V_{\text{bias,in}}$ is provided to the |

| delay cells as well                                                                                                            |

| Fig. 3.1. Measured output characteristic of a SiC N-channel MOSFET at $V_{\rm gs}$ values of 5,                                |

| 7, 9, 11, 13, and 15 V                                                                                                         |

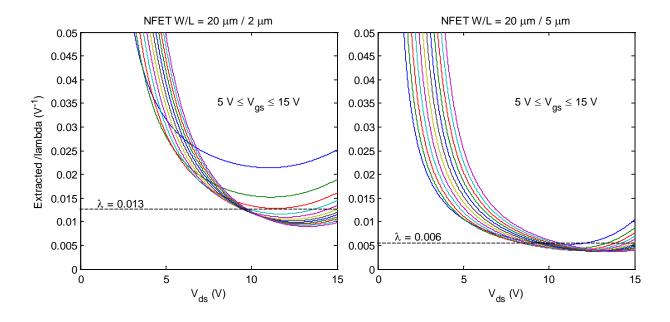

| Fig. 3.2. Estimation of $\lambda$ for NFETs                                                                                    |

| Fig. 3.3. Estimation of $\lambda$ for PFETs                                                                                    |

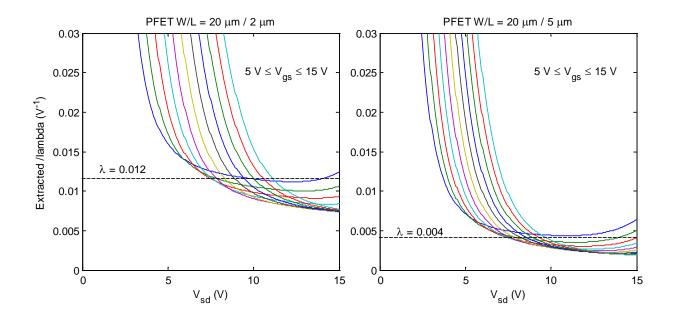

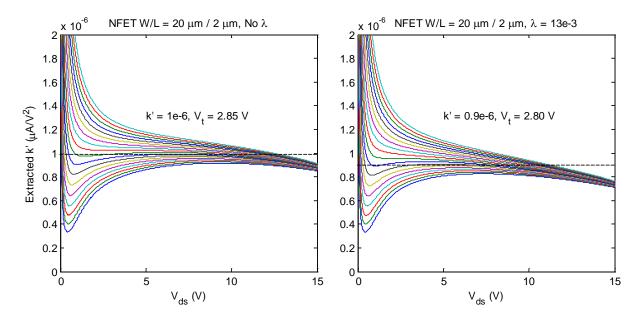

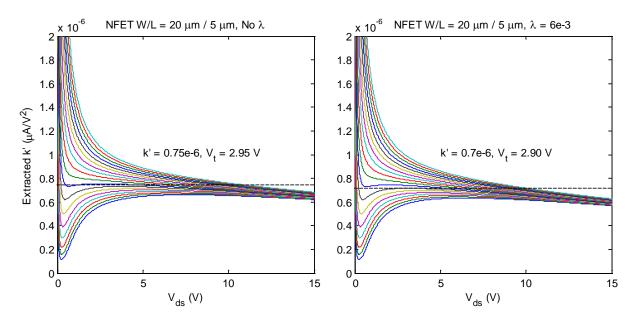

| Fig. 3.4. Estimation of $V_t$ and $k^{\prime}$ for 20 $\mu m$ / 2 $\mu m$ NFETs                                                |

| Fig. 3.5. Estimation of $V_t$ and $k^{\prime}$ for 20 $\mu m$ / 5 $\mu m$ NFETs                                                |

| Fig. 3.6. Estimation of $V_t$ and $k^{\prime}$ for 20 $\mu m$ / 2 $\mu m$ PFETs                                                |

| Fig. 3.7. Estimation of $V_t$ and $k^{\prime}$ for 20 $\mu m$ / 5 $\mu m$ PFETs                                                |

| Fig. 3.8. Selection of NFET Bias Current for W/L = 20 $\mu$ m / 2 $\mu$ m device                                               |

| Fig. 3.9. Selection of PFET Bias Current for W/L = 20 $\mu$ m / 2 $\mu$ m device                                               |

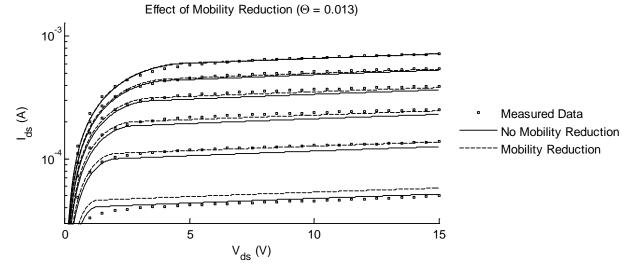

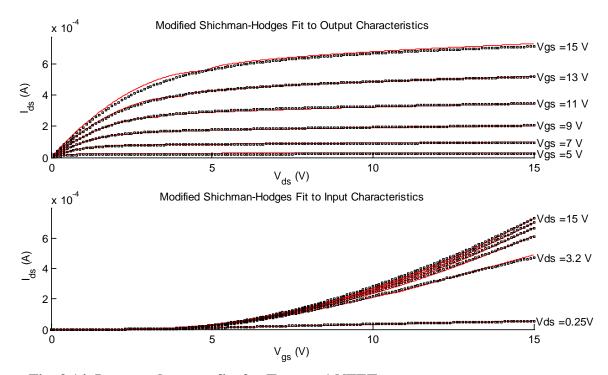

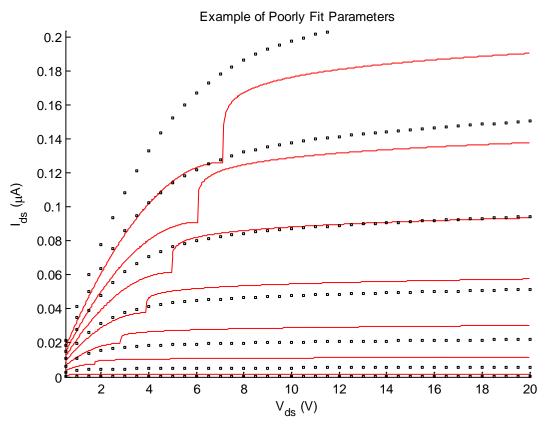

| Fig. 3.10. Effect of mobility reduction on curve fitting for NFETs for tapeout 2 with                                          |

| $v_{gs}$ =5, 7, 9, 11, 13, and 15 V. Some improvement in fitting is visible from 7 V and up, but at 5 V,                       |

| the fit without mobility reduction is better                                                                                   |

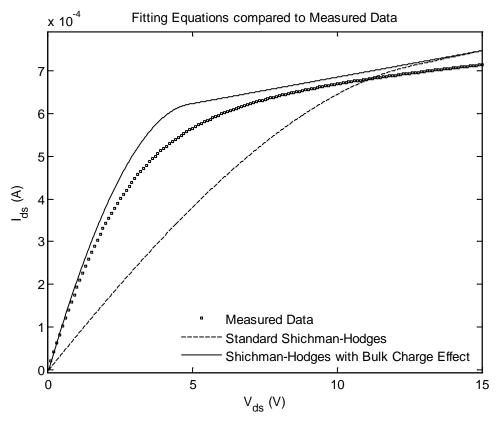

| Fig. 3.11. Improvement in device fitting with the addition of the bulk charge effect 44                                        |

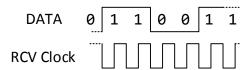

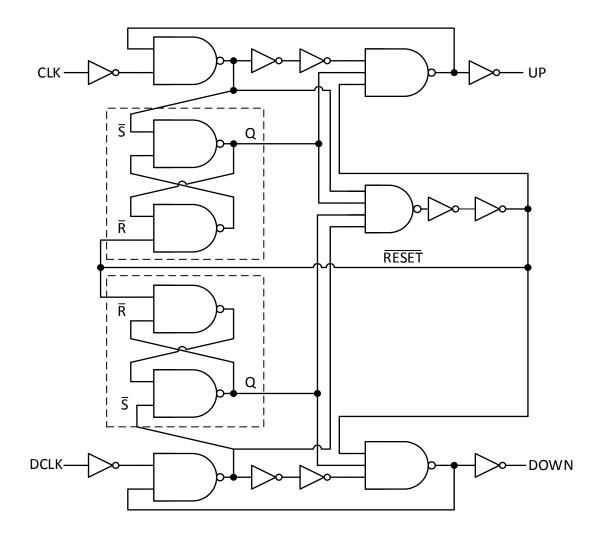

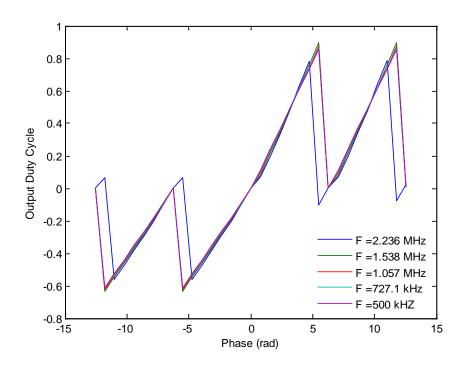

| Fig. 4.2. Desired receiver clock for non-return-to-zero (NRZ) serial data                         | 66             |

|---------------------------------------------------------------------------------------------------|----------------|

| Fig. 4.3. Schematic of the standard PFD showing the internal SR NAND latches and                  |                |

| the RESET signal.                                                                                 | 68             |

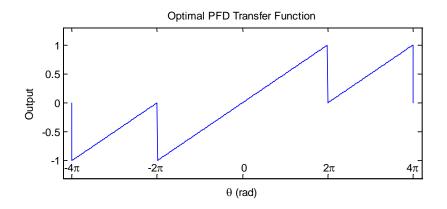

| Fig. 4.4. Optimal transfer function for a phase-frequency detector                                | 69             |

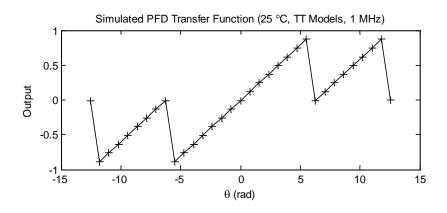

| Fig. 4.5. Simulated transfer function of the standard PFD.                                        | 69             |

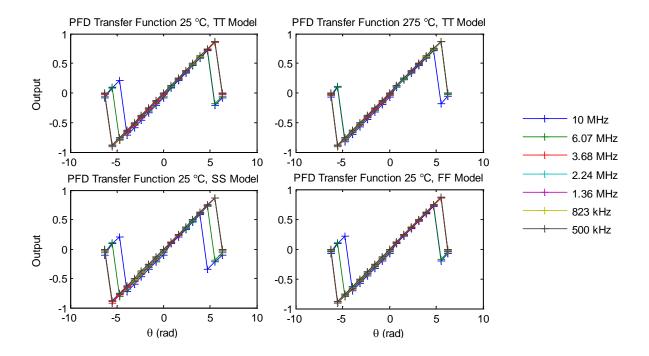

| Fig. 4.6. Simulated transfer functions of standard PFD across process corners and at hig          | ;h             |

| temperature. Data points are marked for increased clarity.                                        | 70             |

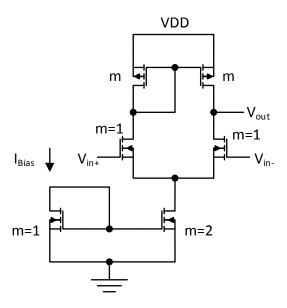

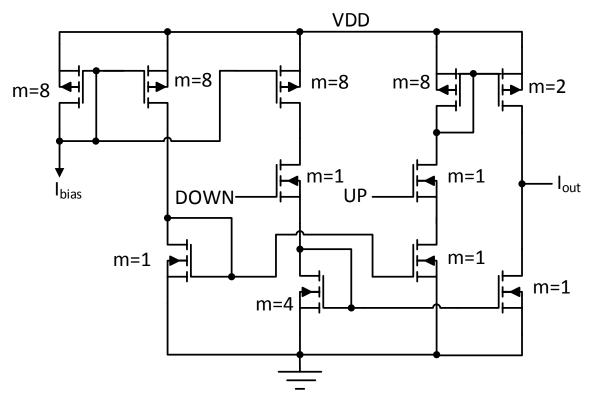

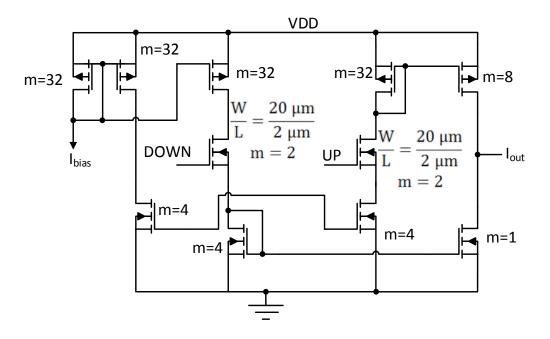

| Fig. 4.7. Charge pump schematic showing device multiplicity.                                      | 72             |

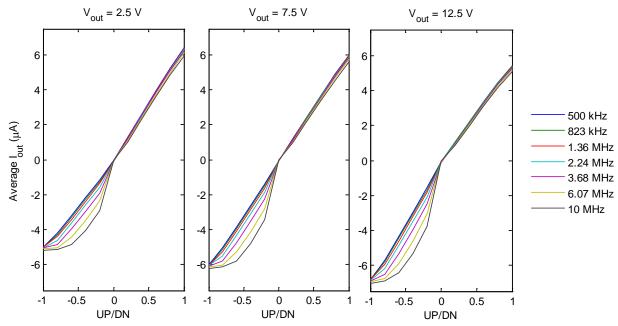

| Fig. 4.8. Simulated transfer functions of the charge pump across frequencies and output           |                |

| voltages. Data points are not marked for increased clarity.                                       | 73             |

| Fig. 4.9. Simulated transfer functions of the charge pump operating at 1 MHz across               |                |

| model corner and temperature at various output voltages. Data points are not marked for clarity   | <sup>7</sup> . |

|                                                                                                   | 73             |

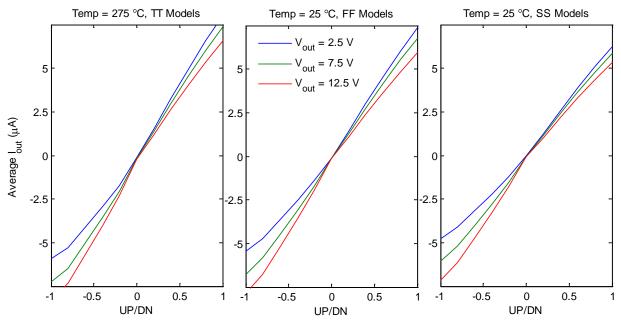

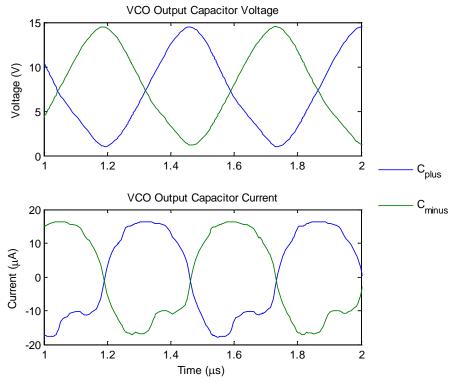

| Fig. 4.10. Differential delay cell with current source loads                                      | 75             |

| Fig. 4.11. Simulated voltage and current waveforms on the load capacitors of the                  |                |

| differential delay stage.                                                                         | 76             |

| Fig. 4.12. Linearized Voltage-to-Current Converter.                                               | 79             |

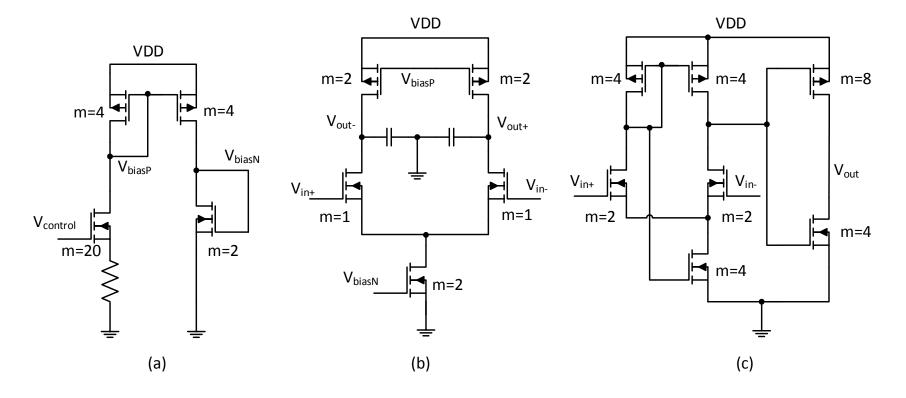

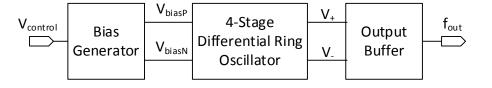

| Fig. 4.13. Blocks of the Voltage Controlled Oscillator. (a) Bias generator (b) Differentia        | al             |

| delay cell (c) Output buffer                                                                      | 80             |

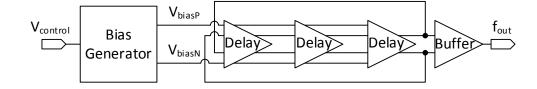

| Fig. 4.14. Block-level diagram of the Voltage Controlled Oscillator                               | 80             |

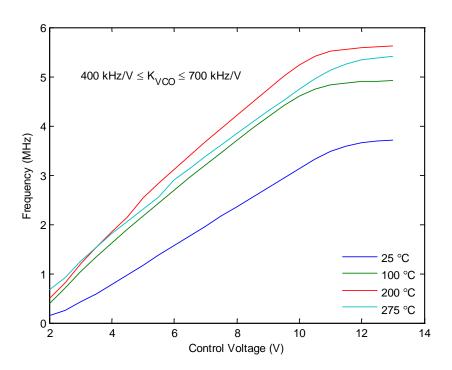

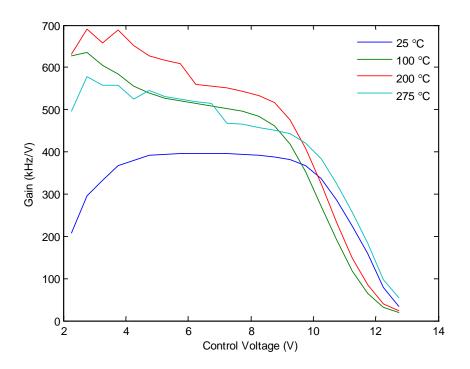

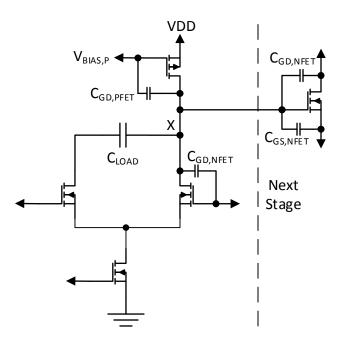

| Fig. 4.15. Simulated VCO transfer function across temperature. $K_{\text{VCO}}$ is estimated from |                |

| the smoothed derivative.                                                                          | 81             |

| Fig. 4.16. Smoothed simulated VCO gain.                                                           | 82             |

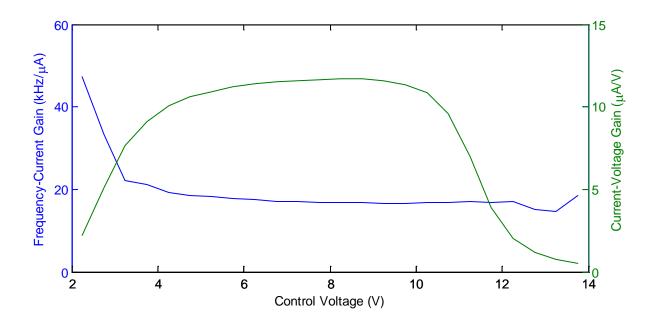

| Fig. 4.17. Simulated Gains of the 3 delay cells (left axis) and the bias-generator (right                       |

|-----------------------------------------------------------------------------------------------------------------|

| axis)                                                                                                           |

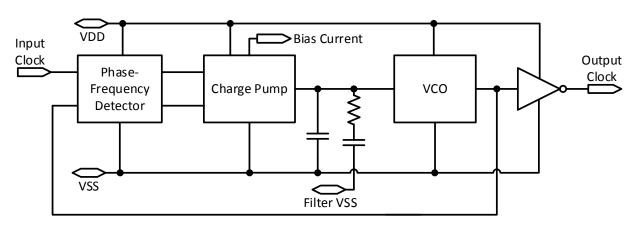

| Fig. 4.18. Final system diagram used for layout                                                                 |

| Fig. 4.19. Output Frequency of the PLL when a +90° input phase step is introduced at                            |

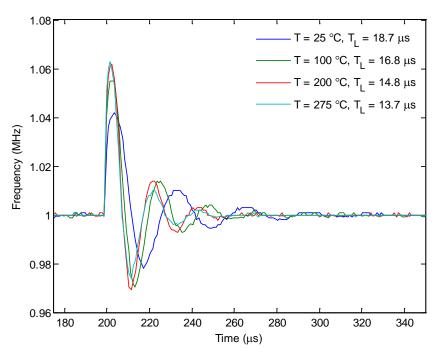

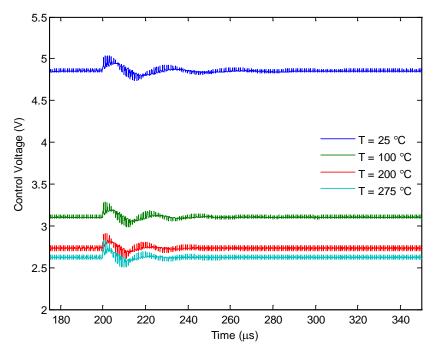

| $200~\mu s.$ Lock Time ( $T_L$ ) is calculated by taking the $2\%$ settling time                                |

| Fig. 4.20. Control voltages during the +90° input phase step                                                    |

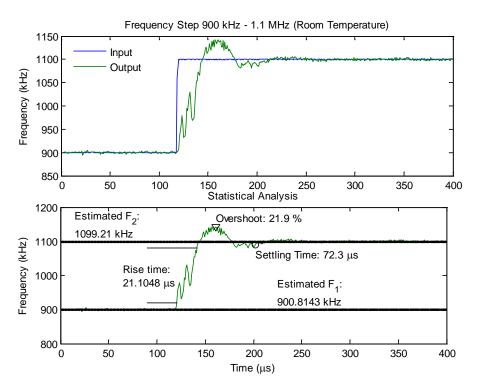

| Fig. 4.21. Output response to an input frequency-step from 900 kHz to 1.1 MHz 90                                |

| Fig. 4.22. Output response to an input- stair-step to determine maximum operating                               |

| frequency                                                                                                       |

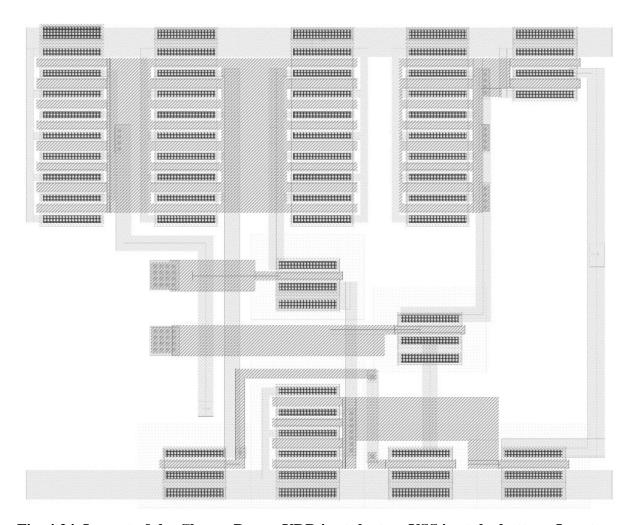

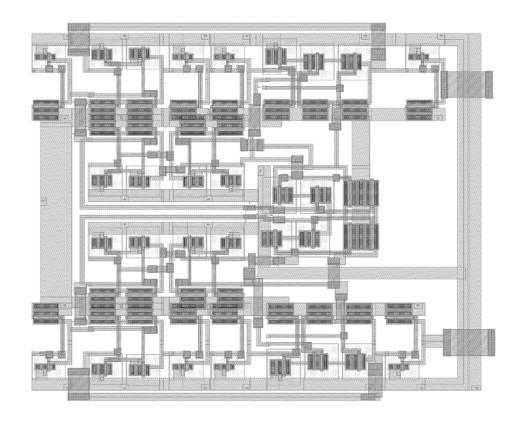

| Fig. 4.23. Layout of the Phase Frequency Detector. Input and VSS connection are on the                          |

| left, while the outputs and VDD connection are on the right                                                     |

| Fig. 4.24. Layout of the Charge Pump. VDD is at the top, VSS is at the bottom, Inputs are                       |

| on the left, and the output is on the right.                                                                    |

| Fig. 4.25. Layout of the VCO. VDD runs along the top and VSS runs along the bottom.                             |

| The current-mirror load delay cells are in the center. The bias generator and $V_{\text{control}}$ input are on |

| the left. The output buffer is on the right. 93                                                                 |

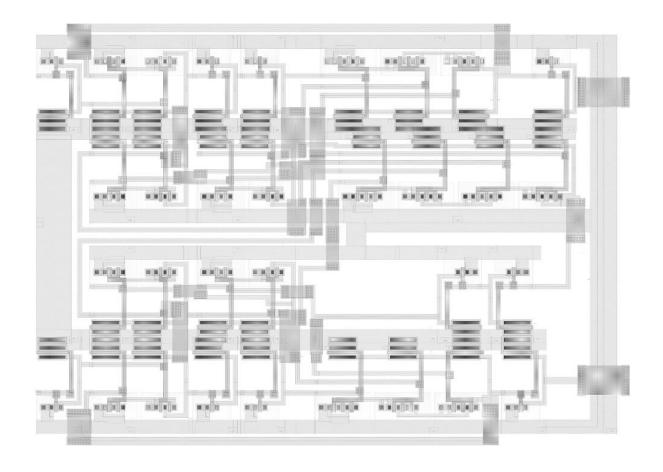

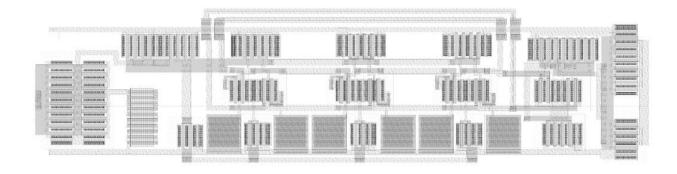

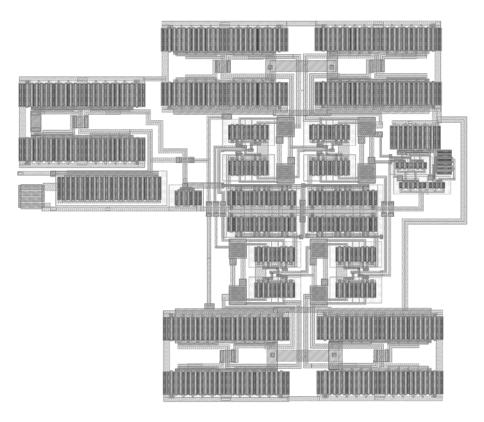

| Fig. 4.26. Complete PLL layout. The PFD is on the top left, the charge pump is at top                           |

| center, and the VCO, rotated 180°, is in the lower left. On the right is the 54 pF capacitor broken             |

| into 36 1.5 pF tiled capacitors. The secondary capacitor, consisting of 4 1.5 pF tiled capacitors, is           |

| seen in the middle                                                                                              |

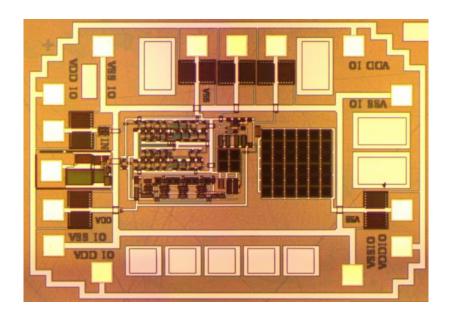

| Fig. 5.1. Die micrograph of the fabricated PLL including the pad ring                                           |

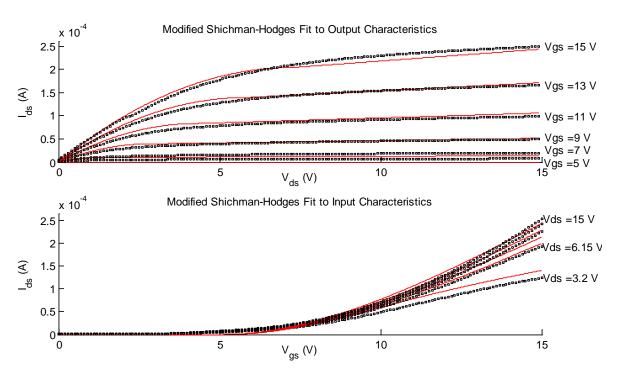

| Fig. 5.2. Comparison of input and output characteristics between pre- and post-tapeout 1                        |

| models. Solid lines are pre-tapeout 1, and dashed lines are post-tapeout 1                                      |

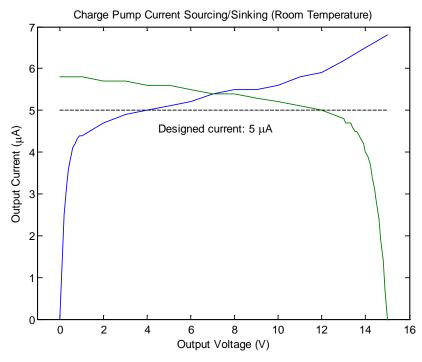

| Fig. 5.3. Current drive from the charge pump at DC and room temperature. Blue is the                 |

|------------------------------------------------------------------------------------------------------|

| current-sinking mode, and green is the current-sourcing mode                                         |

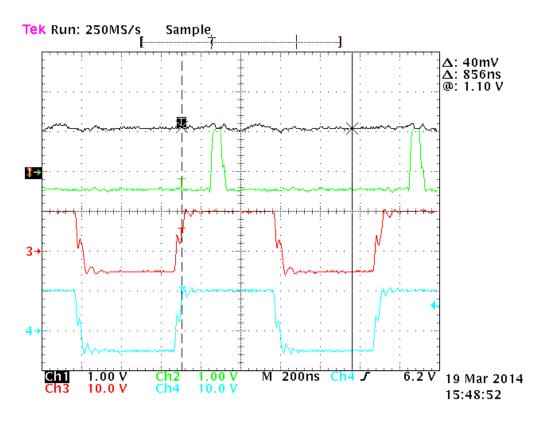

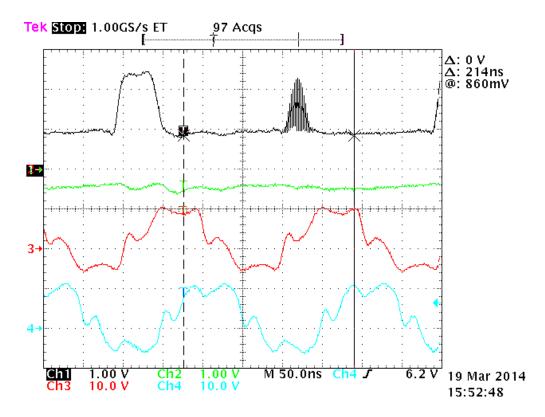

| Fig. 5.4. Transient testing of the PFD at 1 MHz. Ch1 (black) is the DOWN output, Ch2                 |

| (green) is the UP output, Ch3 (red) is the DCLK input, and Ch4 (blue) is the CLK input. In this      |

| case, the CLK input very slightly leads the DCLK input, and after some delay, the UP output is       |

| asserted before resetting. Ch1 and Ch2 are measured by 10x active probes, so the voltage scale is    |

| actually 10 V/div, and there is a DC offset (DOWN is always logic 0)                                 |

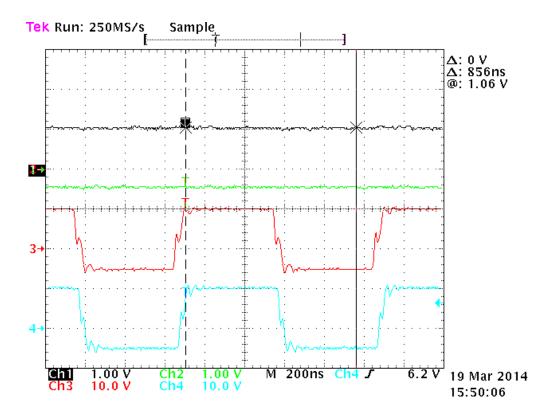

| Fig. 5.5. Transient testing of the PFD at 1 MHz. Channel assignments are the same as the             |

| previous figure. In this case, the DCLK input very slightly leads the CLK input, and neither         |

| output is asserted                                                                                   |

| Fig. 5.6. Transient Testing of the PFD at 5 MHz. Channel assignments are the same as                 |

| the previous figure. In this case, DCLK input leads the CLK input, and the DOWN output is            |

| properly being asserted at one time, but is glitching at another time. The poor quality of the input |

| waveforms is due to reflected waveforms from the PFD input (there is no terminating 50-ohm           |

| impedance for matching coaxial inputs)                                                               |

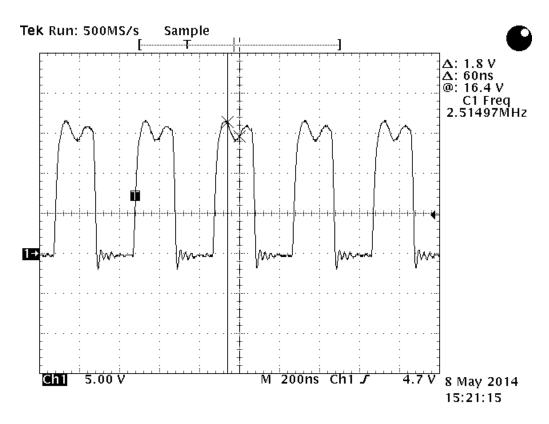

| Fig. 5.7. VCO from Reticle C3, R4 operating at a maximum frequency of 2.5 MHz at                     |

| room temperature. 102                                                                                |

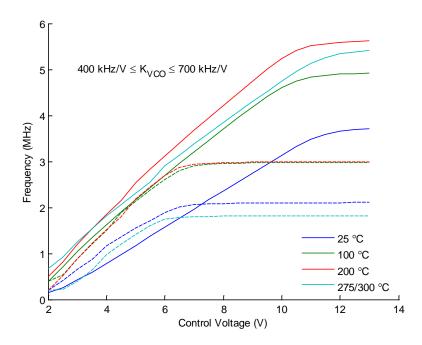

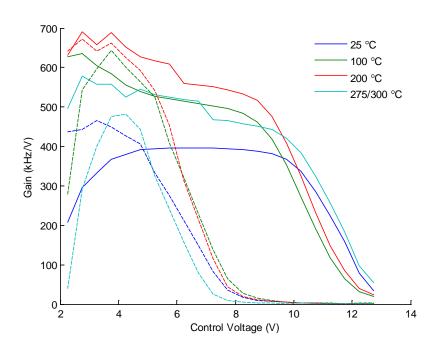

| Fig. 5.8. Simulation of the VCO with models before Tapeout 1 (solid lines) and models                |

| derived from test devices returned on Tapeout 1 (dashed lines). Although the gain is similar in      |

| the controllable region, the large shift in the PFET threshold voltage limits the VCO to an          |

| operating frequency of 2-3 MHz                                                                       |

| Fig. 5.9. Smoothed simulated gain before (solid) and after (dashed) Tapeout 1. The range             |

| of gain is similar, but the operating region is limited to a control voltage of 5 V or less 103      |

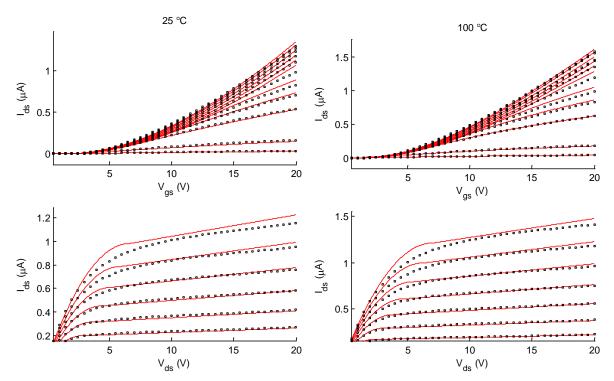

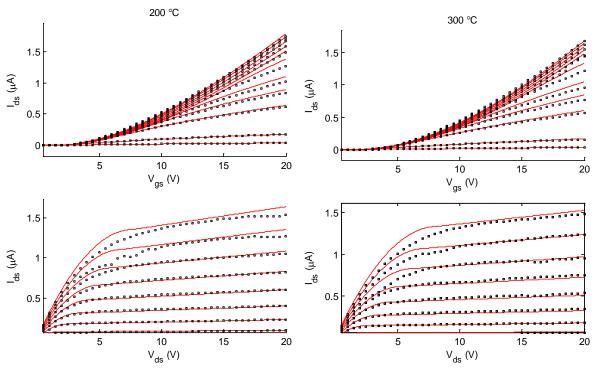

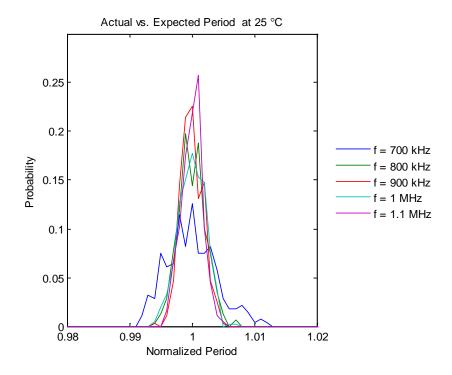

| Fig. 5.10. Jitter at 25 °C                                                         | 107    |

|------------------------------------------------------------------------------------|--------|

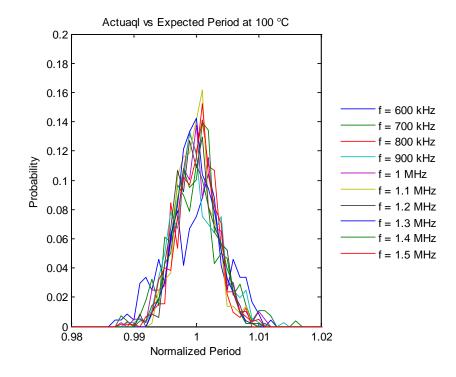

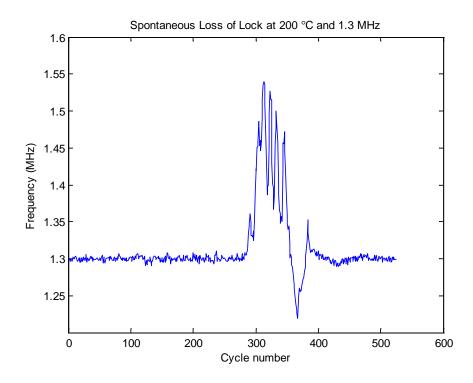

| Fig. 5.11. Jitter at 100 °C                                                        | 107    |

| Fig. 5.12. Jitter at 200 °C.                                                       | 108    |

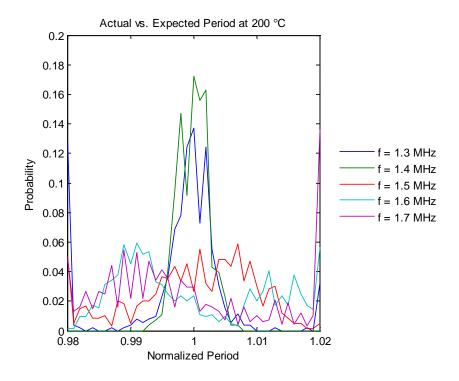

| Fig. 5.13. Spontaneous loss of lock at 200 °C.                                     | 108    |

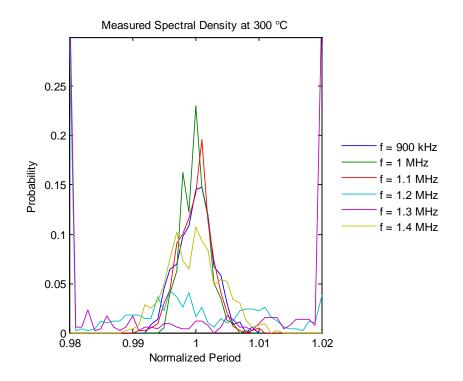

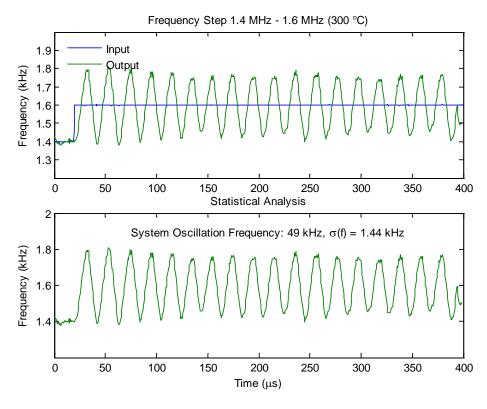

| Fig. 5.14. Normalized jitter at 300 °C.                                            | 109    |

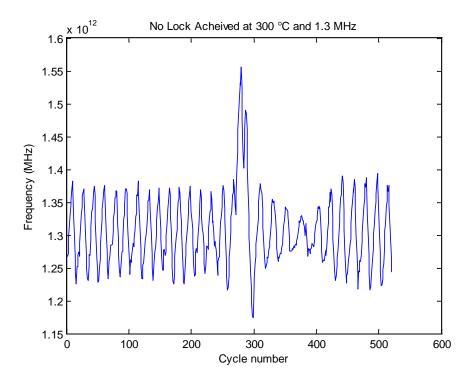

| Fig. 5.15. Failure to lock at 300 °C                                               | 109    |

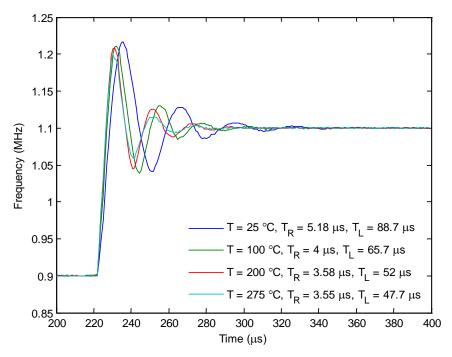

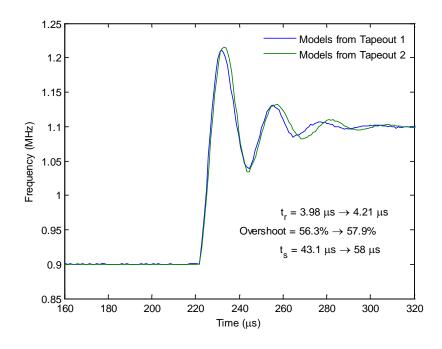

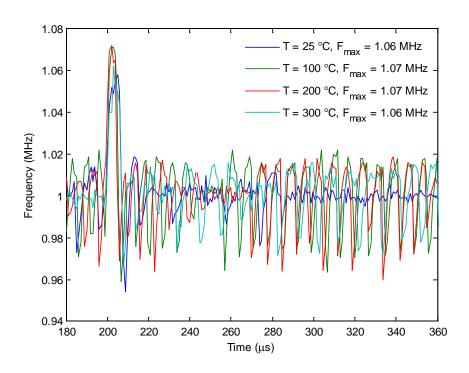

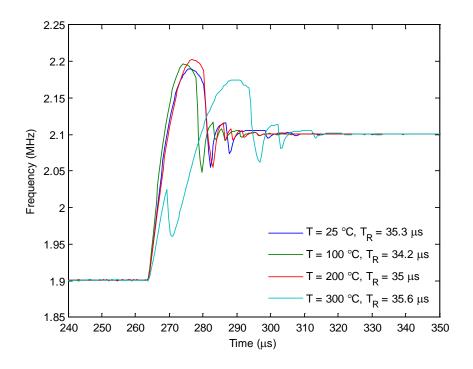

| Fig. 5.16. Simulated Step Response at 100 °C for the original models, and the BSIM | Л4     |

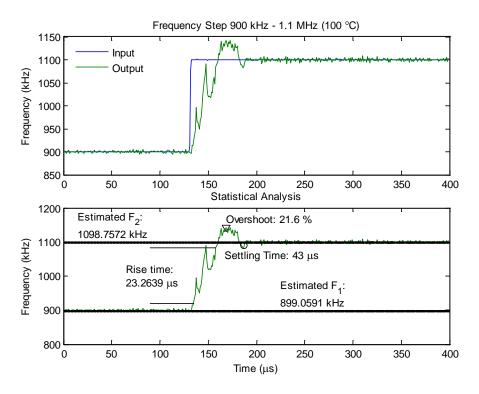

| models generated from Tapeout 1 devices (Tapeout 2 models).                        | 111    |

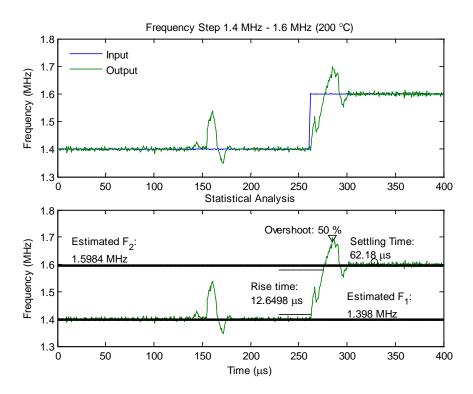

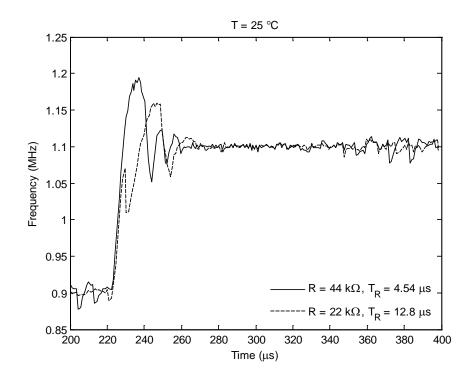

| Fig. 5.17. Step Response of the PLL at room-temperature                            | 111    |

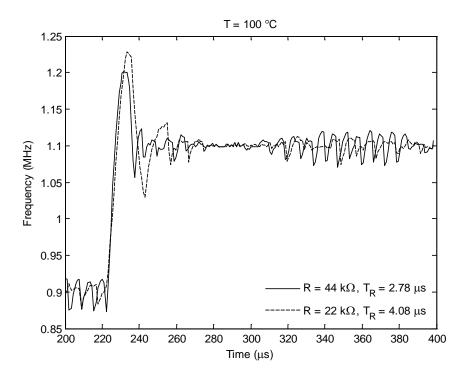

| Fig. 5.18. Step Response of the PLL at 100 °C.                                     | 112    |

| Fig. 5.19. Step Response of the PLL at 200 °C.                                     | 113    |

| Fig. 5.20. Step Response of the PLL at 300 °C.                                     | 113    |

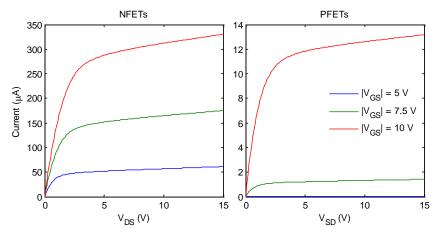

| Fig. 6.1. Comparison of Drain current between NFETs and PFETs (W/L = $20 \mu m/2$  | 2 μm). |

|                                                                                    | 114    |

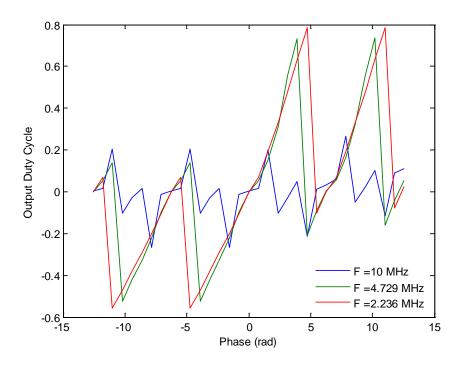

| Fig. 6.2. PFD Gain at room temperature up to 2.2 MHz.                              | 116    |

| Fig. 6.3. PFD gain at room temperature and 2.2 MHz and above.                      | 116    |

| Fig. 6.4. Updated charge pump schematic for tapeout 2.                             | 117    |

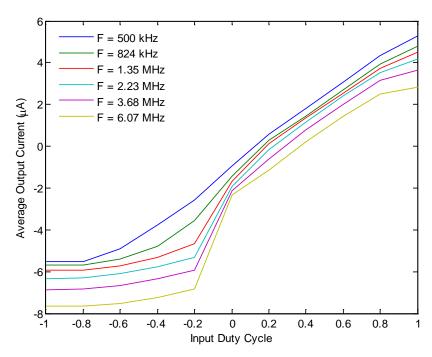

| Fig. 6.5. Simulated charge pump transfer function with parasitics for tapeout 2    | 118    |

| Fig. 6.6. Updated block diagram of the tapeout 2 VCO.                              | 119    |

| Fig. 6.7. Updated Block Schematics for the VCO for tapeout 2. (a) Bias generator   | (b)    |

| Differential delay stage, and (c) output buffer.                                   | 119    |

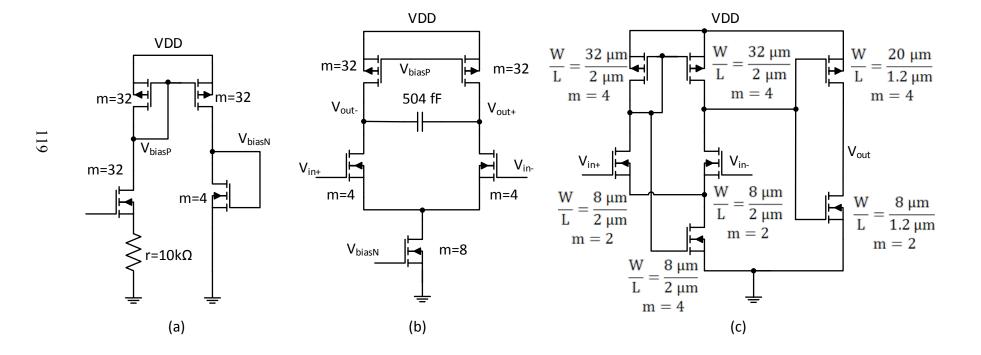

| Fig. 6.8. Significant capacitances in the differential delay stage for tapeout 2   | 120    |

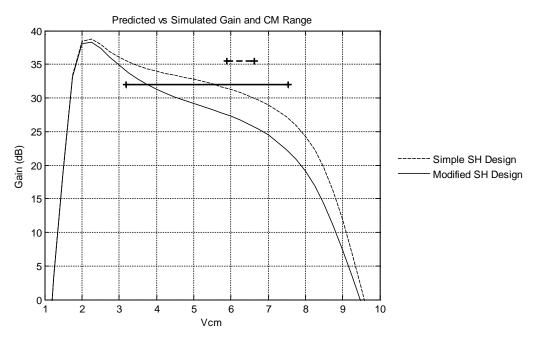

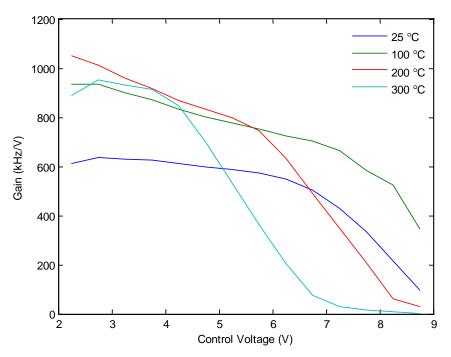

| Fig. 6.9. VCO Transfer Function for tapeout 2                                      | 122    |

| Fig. 6.10. VCO gain vs control voltage for tapeout 2                                                        |

|-------------------------------------------------------------------------------------------------------------|

| Fig. 6.11. Frequency step at 25 °C with two different values of damping resistor 126                        |

| Fig. 6.12. Frequency Step at 100 °C with two different values of damping resistor 126                       |

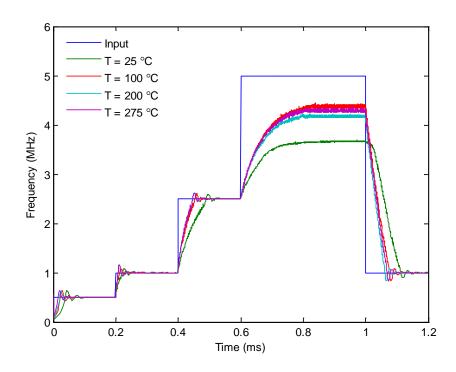

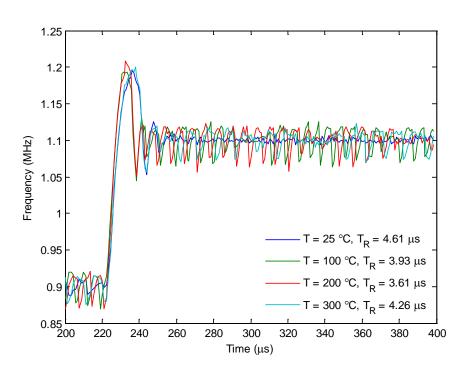

| Fig. 6.13. Frequency Step Response of the PLL for Tapeout 2 with an input frequency                         |

| step from 900 kHz to 1.1 MHz                                                                                |

| Fig. 6.14. Phase Step Response of the PLL with an input frequency phase step of 90°. 128                    |

| Fig. 6.15. Frequency step response of the PLL for Tapeout 2 with an input frequency step                    |

| from 1.9 MHz to 2.1 MHz                                                                                     |

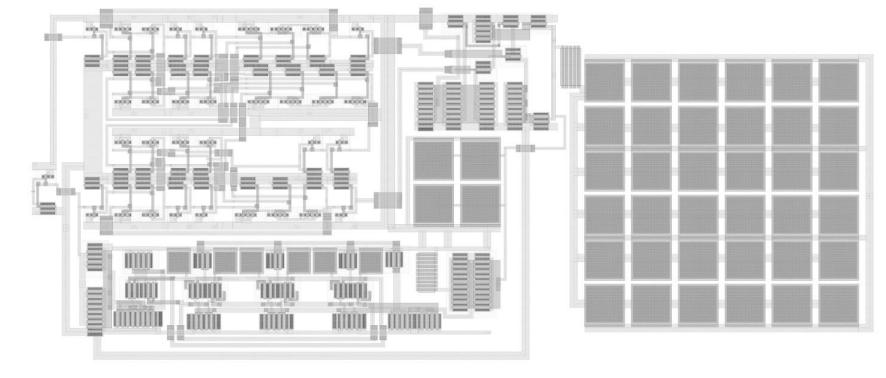

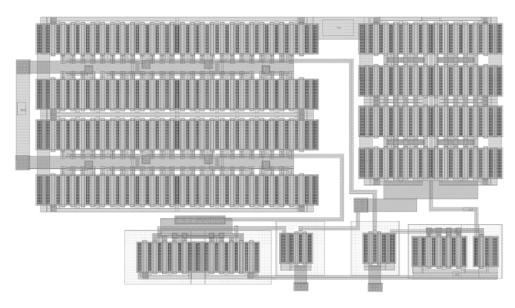

| Fig. 6.16. Layout of the PFD for Tapeout 2                                                                  |

| Fig. 6.17. Layout of the Charge Pump for Tapeout 2. Inputs have been relocated to the                       |

| bottom                                                                                                      |

| Fig. 6.18. Layout of the VCO for Tapeout 2. The bias generator is on the left, and the                      |

| output buffer is on the right                                                                               |

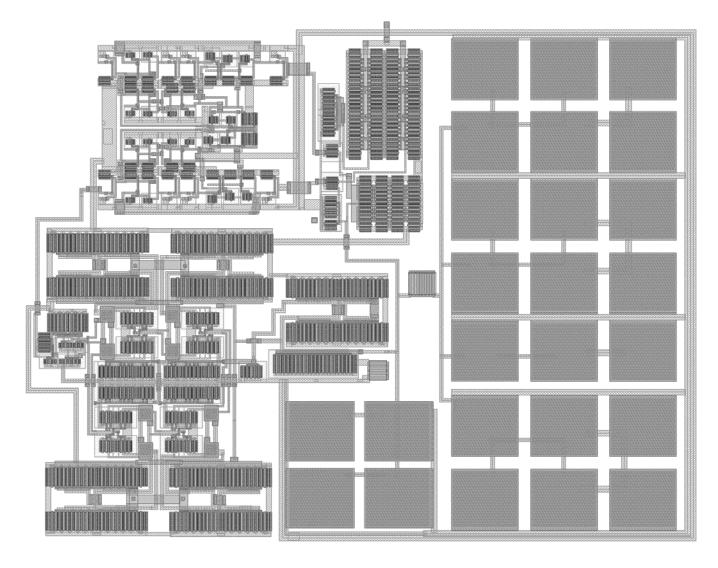

| Fig. 6.19. Complete PLL for Tapeout 2. The PFD is on the top left, the Charge Pump is                       |

| rotated $90^{\circ}$ and is in the top middle. The primary loop capacitor is on the right and the VCO is on |

| the lower left                                                                                              |

#### TABLE OF ACRONYMS

APEI Arkansas Power Electronics International

BJT Bipolar Junction Transistor

BSIM Berkley Short-Channel IGFET Model

CAD Computer-Aided Design

CMOS Complementary Metal-Oxide-Semiconductor

DC Direct Current

EKV Enz, Krummenacher, and Vittoz

ESR Equivalent Series Resistance

FET Field-Effect Transistor

FOM Figure of Merit

HTSiC High-Temperature Silicon Carbide

IC Integrated Circuit

IGFET Insulated-Gate Field-Effect-Transistor

JFET Junction Field-Effect Transistor

LET Linear Energy Transfer

MOS Metal-Oxide-Semiconductor

MOSFET Metal-Oxide-Semiconductor Field-Effect Transistor

NFET N-channel (MOS) Field-Effect Transistor

NMOS N-channel Metal-Oxide-Semiconductor (FET)

NPN N-type/P-type/N-type

NRZ Non Return-to-Zero

ORNL Oak Ridge National Laboratory

PD Phase Detector

PFD Phase-Frequency Detector

PFET P-channel (MOS) Field-Effect Transistor

PLL Phase-Locked Loop

PMOS P-channel Metal-Oxide-Semiconductor (FET)

RC Resistor-Capacitor

SEE Single-Event Effects

SPICE Simulation Program with Integrated Circuit Emphasis

SR Set-Reset

TID Total Ionizing Dose

UA University of Arkansas

VCO Voltage-Controlled Oscillator

#### **CHAPTER 1 – INTRODUCTION**

Silicon carbide (SiC) has a long history as a semiconducting material, but has mostly been eclipsed by silicon Each decade, new research has pushed the state of the art in SiC materials and devices further, but these advances also reveal new challenges in material processing, device design, consistency, and even our understanding of the device physics [1]–[6]. With the commercial availability of discrete SiC power devices emerging over the last seven years, SiC integrated circuits finally appear close to delivering on the long held promise of commercial applicability. Significant work has recently taken place at the University of Arkansas in the field of SiC complementary metal oxide semiconductor (CMOS) integrated circuits (ICs) [7]–[9]. The work in this dissertation reflects another step in the development of SiC IC design processes, design-tools and methods, and is the first ever implementation of a phase-locked loop (PLL) in SiC.

#### 1.1 Applications of Phase-Locked Loops

Phase-locked loops are a class of circuits that appear in a multitude of systems. They may be completely analog, completely software, mixed-signal, or even some combination of these [10]. In work to develop a class of SiC integrated circuits for power electronic systems, a PLL was developed as a fundamental building block [11].

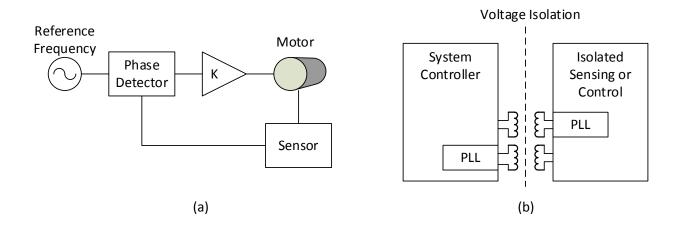

Phase-locked loops have several applications useful for power electronics. A PLL can be used as a motor drive as shown in Fig. 1.1a, encompassing the power electronics, load, and control circuitry.

PLLs can also be used to synchronize a receiver with an incoming data stream.

Transmission of serial data without a clock is particularly beneficial in power electronics where voltage isolation may be necessary since it results in fewer isolation components as seen in Fig. 1.1(b). PLLs can also be used to generate control signals via phase or frequency modulation [12].

Fig. 1.1. (a) A PLL motor speed control system and (b) PLLs used in a serial data communication scheme

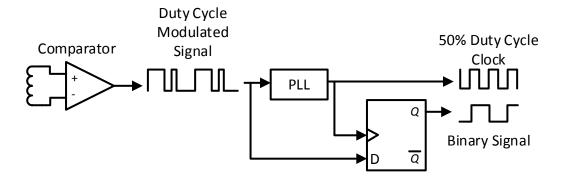

Although there are many applications for a PLL with additional or modified internal components, the PLL to be described in this dissertation can be applied in the system described in Fig. 1.1(b) without modification. Fig. 1.2 shows a block diagram of a receiving element as shown in Fig. 1.1 (b). The coil drives a comparator which generates a square-wave output. The square-wave output can be duty-cycle encoded, with the positive transitions as the clock edges, and the duty cycle less than or greater than 50% indicating a digital 0 or 1, respectively. The PLL generates a nearly 50% duty cycle clock signal from the input, and then a D flip-flop can generate a clocked logic signal from the duty-cycle encoded square wave. The only requirements are that the input frequency fall within the tuning range of the PLL and the duty cycles chosen for encoding be sufficiently far away from 50% that there are no timing errors.

Fig. 1.2. An isolated data transmission system utilizing the described PLL along with a comparator and D flip-flop.

#### 1.2 Organization of this dissertation

This dissertation is organized in a topical, not chronological, format. Chapter 2 covers a wide range of topics informing and leading up to the design of the phase-locked loops in SiC. Chapter 3 describes the state of the art in hand analysis of circuits using SiC MOSFETs, and proposes several ways in which existing models may be improved to lend additional precision and increase the designer's intuition. In addition, the important behaviors identified in Chapter 3 provide a platform for discussion between design engineers, fabrication engineers, and model developers for future work on SiC CMOS processes.

Chapters 4 through 6 trace the development of the phase-locked loop in SiC, and much of the work does not rely on the work in Chapter 3. This is for two reasons. The first is that the work of Chapter 3 took place throughout the design process, including after the final design submission took place. The second, and equally important, reason was the significant variability that still exists in SiC IC processes. By selecting topologies which did not rely on accurate device parameters to function, the probability of a functioning circuit in the presence of large variability was greatly improved, and the design process could be further improved by the

lessons learned in these pioneering circuits. Chapter 4 discusses the initial design of the PLL, Chapter 5 discusses the testing of the first fabricated PLL, and Chapter 6 describes changes made to the design in light of the findings of Chapter 5 and improved device models.

A comment about plots of measured MOSFET data in this dissertation is in order. In many cases, measured MOSFET data is compared to a mathematical model. In order to visually demonstrate the sampled nature of the MOSFET data, a  $\Box$  (box symbol) is used at each data point without connecting lines between data points. Mathematical models are denoted by lines that may be solid or dashed. For consistency, the MOSFET data is always shown the same way, even when no mathematical model is shown in the plot. Sampled data from circuit simulations often have fewer data points, and linear connecting lines between data points are used to make plots easier to interpret.

#### **CHAPTER 2 - BACKGROUND**

### 2.1 Wide Bandgap Materials

The term "wide bandgap" refers to semiconductors with a bandgap energy significantly greater than that of silicon (Si). SiC and gallium nitride (GaN) are the most common wide bandgap materials in use at this time. Bandgap energy is the amount of energy that is necessary to raise electrons from the valence band to the conduction band, thus allowing current to flow. This increased energy threshold has implications for critical electric field, thermal capability, and radiation susceptibility. SiC can form in multiple polytypes, but, unless otherwise noted, only the 4H polytype is described in this dissertation. Table I compares properties for Si, SiC, and GaN [13].

**TABLE I.**COMPARISON OF MATERIAL PROPERTIES FOR SI, SIC, AND GAN

| Parameter                                                                   | Silicon                | 4H-SiC               | GaN                         |

|-----------------------------------------------------------------------------|------------------------|----------------------|-----------------------------|

| Bandgap Energy W <sub>g</sub> (eV)                                          | 1.12                   | 3.26                 | 3.39                        |

| Critical Electric Field E <sub>crit</sub> (MV/cm)                           | 0.23                   | 2.2                  | 3.3                         |

| Relative Permittivity $\varepsilon_r$                                       | 11.8                   | 9.7                  | 9.0                         |

| Electron Mobility $\mu_n$ (cm <sup>2</sup> /V·s)                            | 1400                   | 950                  | 800/1700 <sup>†</sup>       |

| Intrinsic Carrier Concentration n <sub>i</sub> at 300 K (cm <sup>-3</sup> ) | 1e10                   | 8e-9                 | 2e-10                       |

| Thermal Conductance λ (W/cm <sup>2</sup> ·K)                                | 1.5                    | 3.8                  | 1.3 <sup>‡</sup>            |

| Baliga FOM $\varepsilon_r \mu_n E_C^3$ (V <sup>2</sup> /cm·s)               | $2.0 \text{x} 10^{20}$ | 9.8x10 <sup>22</sup> | 2.6x10 <sup>23</sup> (bulk) |

<sup>&</sup>lt;sup>†</sup> The lower value is for bulk doped GaN, and the higher value is for the 2-Dimensional Electron Gas that forms the channel of a GaN/AlGaN High-Electron Mobility Transistor.

<sup>&</sup>lt;sup>‡</sup> This value is for epitaxial GaN grown on a dissimilar substrate, which is far more common than bulk GaN.

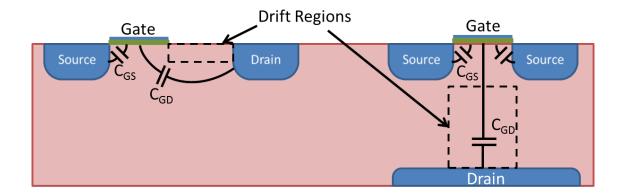

The higher critical electric field of wide bandgap materials leads to improvements in both power and low-voltage semiconductor devices. For both lateral and vertical insulated-gate devices, the gate oxide is the primary limitation on the gate-source voltage. To achieve drain-source voltage (blocking voltage) ratings significantly more than the gate-source voltage, an additional separation between the gate and drain of the devices, termed the drift region, is necessary. The cost of adding the drift region is additional on-state resistance ( $r_{DS,on}$ ), and optimizing the tradeoff between blocking voltage and  $r_{DS,on}$  is fundamental to the design of the device. The specific on-resistance of the ideal drift region is described by Baliga in [14], and is given by:

$$R_{on-ideal} = \frac{4BV^2}{\varepsilon_r \mu_n E_C^3} \tag{2.1}$$

As can be seen, the critical electric field,  $E_C$ , is a cubic term in the denominator, and therefore has a large effect on the on-resistance of the drift region. The Baliga Figure of Merit (BFOM) is the denominator of Eq. (2.1), and is included in Table I. The ideal on-resistance of a SiC device is nearly 500 times lower than that of a Si device. Fig. 2.1 shows the location of the drift region in both lateral and vertical MOSFETs.

Fig. 2.1. Drift Regions in Lateral and Vertical MOSFETs.

A larger critical electric field allows SiC devices to have shorter drift regions for the same blocking voltage as Si devices. Although SiC has a lower mobility than Si (Table I), this is outweighed by the reduced drift length and the device will ultimately have a lower on-resistance. For vertical devices, the channel area can also be reduced, corresponding to a reduced gate area and ultimately, total gate capacitance. The disadvantage of reducing the drift-region length in vertical devices is an increase in gate-drain capacitance with respect to the gate-source capacitance. The change in this capacitance ratio allows Miller currents to charge the gate-source capacitance to a higher voltage, and increases the device's susceptibility to parasitic turn-on.

As seen in Table I, the intrinsic carrier-concentration  $(n_i)$  of wide bandgap materials is much lower than Si. This is the source of the increase in thermal capability of these materials. A doped semiconductor is effective as long as the  $n_i$  is much lower than the doped (extrinsic) carrier concentration  $(n_o)$  [15]. Wide bandgap materials will not reach this crossover point until much higher temperatures.

Radiation effects in integrated circuits are categorized into three primary categories: displacement damage, single-event effects (SEE), and total-ionizing dose (TID). Displacement

damage is a physical change in the crystal lattice of the material due to strikes by energetic particles. The Si-Si dissociation energy of 310 kJ/mol, whereas the dissociation energy of Si-C is 447 kJ/mol, both at 298 K [16]. This indicates that SiC will be less susceptible to displacement damage than Si. Single-event effects occur when radiation strikes generate currents in devices through the mechanism known as linear energy transfer (LET). The larger bandgap of SiC indicates that a larger LET is necessary to create the same current. Both of these effects are reduced with respect to Si directly by the material properties of SiC. TID is caused by an accumulation of charge in the oxide for insulated-gate devices such as MOSFETs and has the effect of shifting the threshold voltage of the device. Although TID is not inherently reduced in SiC, the reduction of transconductance and increase of power supply and threshold voltage reduce the influence of TID [17].

SiC has long been considered as a viable material for ICs [1], [18]. The first integrated circuits began to appear in the 1990s and utilized the 6H polytype of SiC. This period of interest lasted from the mid-1990s through the early 2000s, and was concentrated at a few places like Cree, Purdue University and Cornell University [19]–[22]. Since that time, the 4H polytype has, for the most part, supplanted 6H, and several new groups have contributed to the body of work. The variety of integrated circuit processes spans bipolar transistors, JFETs, and MOSFETs, with NPN BJTs, N-type JFETs and MOSFETs being common, and depletion-mode NFETs or PFETs being available as a complementary device in some processes, but only processes with PFETs can be considered true CMOS technology.

A group at Case Western University has focused on JFET-based ICs in 6H SiC, and has demonstrated operation at temperatures in excess of 550 °C [23]. At the GE Global Research

Center, they have focused on both analog and digital NFET-based circuits including packaging them for high temperature operation and reliability [24]. A partnership between the University of Arkansas, Oak Ridge National Lab, and Cree was driven by a desire to integrate low-voltage processing and control with a high-voltage power device [25]–[27]. Finally, previous work at Raytheon System Limited UK (the foundry) has focused on creating a more commercially-viable high-temperature SiC (HTSiC) CMOS IC process [28], [29]. The work described in this dissertation utilizes a variant of the Raytheon HTSiC CMOS process.

There are several challenges common to all SiC IC processes which must be overcome to design functional circuits. First and foremost, SiC MOSFETs exhibit transconductances significantly lower than might be assumed by examining the material bulk mobility [30]. Referring back to Table I, the bulk electron mobility of 4H SiC is around 2/3 that of bulk Si. Instead of the observed transconductance being 1/3 less than common Si integrated NFETs, it may be around a factor of 100 less. Transconductances in SiC and Si PFETs follow a similar trend.

The diffusion coefficient of SiC is also extremely low, and high-energy ion implantation is the only feasible way of creating selectively doped regions necessary for the drains and sources of MOSFETs. After implantation, a high temperature (1200-1800 °C) anneal is necessary to activate the dopants and repair damage to the lattice from the implantation. This high temperature step destroys oxide and polysilicon, so the gate must be applied afterwards [30]. The gate must overlap the source and drain regions by a significant amount so that a misalignment during processing will not reduce device yield. This is unlike modern Si processing, where the gate is used as a masking layer for source and drain diffusion, commonly referred to as a self-

aligned gate. The result is increased gate-drain and gate-source capacitance with respect to Si.

This, combined with the limited current drive due to lower transconductance, significantly limits the high-speed operation of SiC ICs.

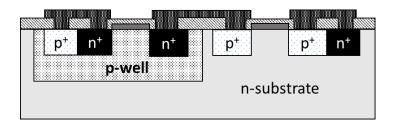

#### 2.2 The Raytheon Silicon Carbide CMOS Process

The HTSiC CMOS process utilizes an n-type substrate suitable for creating PFET devices. In this substrate, a p-well can be implanted as a base for NFET devices. The lack of an isolated n-well means that all PFET devices have their body terminals connected to the positive voltage supply. The process uses a polysilicon (poly) gate similar to Si processes, and there is a second polysilicon layer which can be used in conjunction with the lower poly to form a capacitor, or grown with high resistivity to form resistors. The process offers one metal layer. A simplified process cross-section is shown in Fig. 2.2.

Fig. 2.2. Simplified cross-section of the Raytheon HTSiC CMOS process.

The Raytheon HTSiC process, like all SiC IC processes, is still undergoing development. The test devices that were delivered to the University of Arkansas during Winter 2013 consisted of a variety of fabrication profiles and performances. The circuit design team (consisting of the UA and Ozark Integrated Circuits) identified a set of performance targets for the NFET and PFET devices, focusing on device lengths of 1.2, 2, 5, and 10 µm. After discussion with the foundry, several NFET and PFET device models were generated at the UA. The NFET device

models were based on specific test devices, whereas the PFET device models were based on a set of devices, but integrated expected improvements in behavior with respect to existing devices.

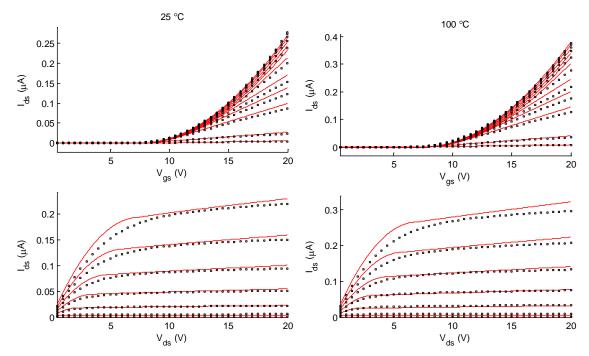

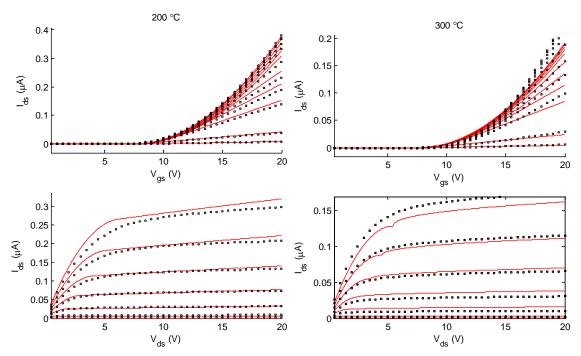

Fig. 2.3 shows the measured data from the chosen test devices at room temperature.

Several challenges in using the HTSiC process were observed while measuring devices for modeling efforts. The target NFET and PFET devices were chosen from different wafers, so at design time, it had not been proven that these device profiles could be fabricated on the same wafer. The PFET data in Fig. 2.3 show a flat slope unusual for a MOSFET. This portion of the data was not modeled, since Raytheon expected to remove this behavior in the circuits fabrication run (referred to as Tapeout 1 throughout the remainder of this dissertation).

Circuit designers usually use one of several simplified models to help them understand the devices available for circuit design. Foremost among these is the Shichman-Hodges model, which states that for a MOSFET in saturation (see Eq. (2.2)), the current is inversely proportional to L. Fig. 2.4 shows the normalized current through a long (L=  $10 \mu m$ ) and short (L= $2 \mu m$ ) device. Some difference will be expected since the channel modulation parameter,  $\lambda$ , is a function of length. The vertical offset observed in Fig. 2.4 indicates that the transconductance, k', is also a function of length.

$$i_D = \frac{k'W}{2L}(v_{GS} - V_t)^2 [1 + \lambda (v_{DS} - v_{gS} + V_t)] \quad v_{DS} \ge v_{GS} - V_t$$

(2.2)

Fig. 2.3. NFET and PFET characteristics at  $V_{gs}$   $(V_{sg})=5$  V at room temperature. W/L = 20  $\mu m/1.2$   $\mu m,$  20  $\mu m/2$   $\mu m,$  20  $\mu m/5$   $\mu m,$  and 20  $\mu m/10$   $\mu m.$

Fig. 2.4. NFET  $V_{ds}$ - $I_{ds}$  curves normalized for W/L.

Fig. 2.5. Comparison of measured and modeled body bias effects in the NFET with W/L =  $20~\mu m/2~\mu m$  at  $V_{gs}$  = 5 V.  $V_{sb}$  = 0 V, 3 V, 6 V, and 9 V.

Fig. 2.5 shows a challenge that became apparent during the device modeling. The BSIM3v3 model that was used could not be accurately fit to the observed body-bias effect. This meant that simulations could not be expected to predict device performance when the transistors had  $V_{SB} \neq 0$  V.

#### 2.3 Phase-Locked Loops

PLLs are a fundamental building block of many types of systems. There are many variations of PLLs but, at their core, they are control systems which seek to force an output signal to have the same phase as an input or reference signal. The derivative of phase with

respect to time is the instantaneous frequency, so a PLL is also a control system which forces the output (or feedback) frequency to match the input frequency [31].

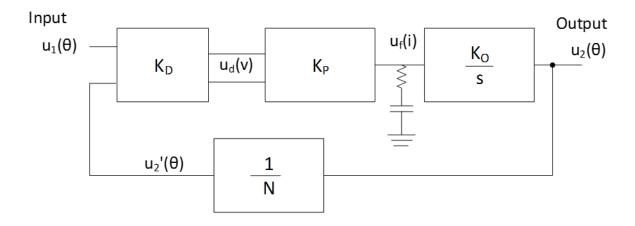

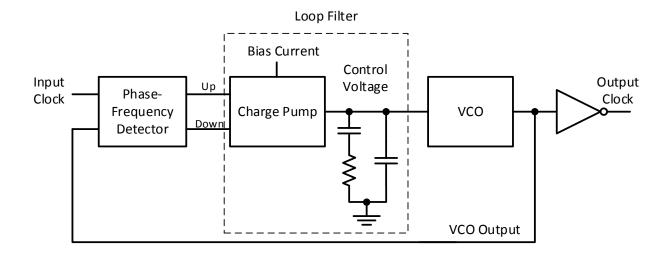

Fig. 2.6 shows the topology of a PLL suitable for implementation in a CMOS integrated circuit. The input,  $u_1$  is a nominally periodic signal with properties radial frequency,  $\omega$ , and phase,  $\theta$ . The phase detector, which serves the function of generating an error signal, has an output  $u_d$ , which is electrical, and has properties of both voltage and current. The loop filter acts on the signal  $u_d$  and to produce output  $u_f$ . The voltage-controlled oscillator (VCO), will have a MOSFET input, so the input  $u_f$  will have a negligible current. The VCO generates another nominally periodic signal,  $u_2$ , as the loop output. In the feedback path, there may be a feedback block which converts  $u_2$  into another signal  $u_2$ . This feedback block is most commonly a divide-by-N counter, which will make the output signal,  $u_2$ , N times greater than the input signal  $u_1$ .

Fig. 2.6. General control-loop topology of a PLL.

The charge-pump PLL, shown in Fig. 2.7, is a circuit implementation of the general topology shown in Fig. 2.6. The loop filter in Fig. 2.6 is split into two separate blocks, a mixed-signal block called the charge pump, and a passive block consisting of resistor(s) and capacitor(s). The charge pump nomenclature should not be confused with a capacitor-based DC-to-DC converter which is also commonly used in ICs and referred to as a charge pump. In the

case of a PLL, the charge pump is actually a digitally controlled current source/sink. The loop filter in a charge-pump PLL is a series RC circuit, which converts the current sourced or sunk by the charge pump into the voltage which drives the VCO input. In Fig. 2.7, the gains  $K_D$ ,  $K_P$ , and  $K_O$  correspond to the digital phase frequency detector (PFD), the charge pump, and the VCO, and have units  $1/(2\pi \text{ radians})$ , Amps and (radians/second)/volt. The Laplace-domain transfer function is Eq. (2.3) and the characteristic frequency and damping coefficient are Eqs. (2.4) and (2.5).

$$H(s) = \frac{K_D K_P K_O (1 + sRC)}{s^2 NC + sK_D K_P K_O RC + K_D K_P K_O}$$

(2.3)

$$\omega_n^2 = \frac{\kappa_D \kappa_P \kappa_O}{NC} \tag{2.4}$$

$$\zeta = \frac{\omega_n RC}{2} \tag{2.5}$$

Fig. 2.7. Control loop implementation of the charge-pump PLL and the resulting Laplace-domain transfer function, natural frequency and damping ratio.

#### **2.3.1 Phase Frequency Detectors**

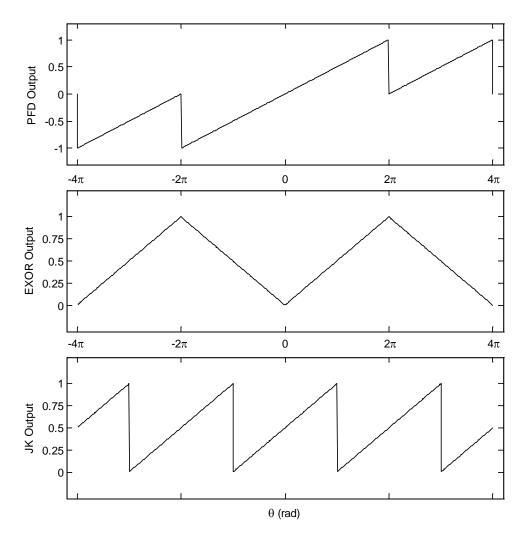

Best describes four types of phase detectors (PDs): Multipliers, EXOR gates, JK-flip-flop gates, and Phase-Frequency Detectors in [10]. The multiplier PD is the only one appropriate for sinusoidal input signals, but it can also be used with square wave (digital) input signals.

Although it is very flexible, it is also much slower than the Phase-Frequency Detector to achieve lock.

The EXOR and JK-flip-flop PDs are the digital gates one would expect, without any extra circuitry. The EXOR PD achieves lock when the input and output signals are near 90° out-of-phase, while the JK-flip-flop achieves lock with input signals in-phase. Both of these types have a single, logic-level output which is used to drive the loop filter.

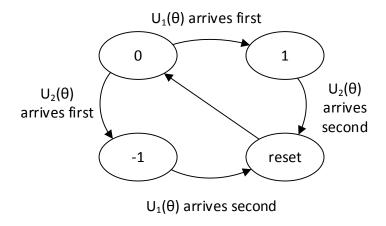

The final type of phase detector is the Phase-Frequency Detector or PFD. The complete operation of the PFD is described in Chapter 4, but it is the only PD that has a tri-state output capable of driving a charge pump. The three states of the PFD are 0, +1, and -1, which indicate the frequency requires NO CHANGE, speed UP, or slow DOWN (or DN). For this work, a charge-pump PLL topology was chosen, so the phase detector was a PFD. Fig. 2.8 shows the state transition diagram. The PFD starts at NO CHANGE, and transitions to UP or DN when the CLK and DCLK signals are asserted, respectively. After that, the PFD holds its' state until the other input signal is asserted (DCLK or CLK following the pattern described). The PFD then enters a transient reset state before returning to the NO CHANGE state.

Fig. 2.8. State Diagram of the PFD.

Fig. 2.9 shows a comparison of the output functions for these three PDs. The EXOR and JK PDs are often used with active filters which can remove the DC offset in the transfer function. Without an active filter, the phase error of PLLs incorporating these PDs will not be zero except when the output frequency corresponds to a PD output of 0.5. The PFD, being bipolar, does not require an active amplifier in the loop filter in order to achieve theoretical zero phase error if it is driving a charge pump.

Fig. 2.9. Time-averaged output functions for different phase detectors versus input phase.

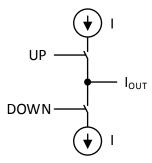

# 2.3.2 Charge Pumps

The charge pump can only be paired with a PFD-type of phase detector. It requires the bipolar input, but in return, it offers a high-impedance state when the input is zero. The high-impedance state allows the PFD-charge pump combination to achieve theoretically zero phase error at any frequency. Fig. 2.10 shows the simple functional diagram of the charge pump. The current output of the charge pump (which can be positive or negative), is converted into a voltage by the RC network to ground as seen in Fig. 2.7.

Fig. 2.10. Functional diagram of the charge pump.

## 2.3.3 Voltage-Controlled Oscillators

The VCO is the heart of the phase-locked loop. The perfect VCO has several characteristics:

- Large tuning range

- Low tuning gain (to minimize the effect of input noise)

- Low internal timing jitter/phase noise (High Q)

- Low supply-noise sensitivity

These characteristics are not universally achievable, and in fact, large tuning range and low tuning gain are somewhat exclusive. Ultimately, though, the VCO must provide the needed output frequency for the PLL, and not vary significantly due to input noise, internal noise, or power supply noise. The various topologies available for VCOs balance these requirements against complexity, size, and the ability to be fully integrated on an integrated circuit.

In [32], the authors classify VCOs into three categories: resonant-tank, relaxation, and ring oscillators. Resonant-tank oscillators can be built with either a crystal or LC tank. Crystals are not available in IC processes, and inductors are generally not practical for integration on ICs

for frequencies below 1 GHz. Even then, the low Q associated with IC inductors reduces the benefit of the resonant-tank oscillator: minimum jitter (maximum Q). Resonant-tank oscillators also have limited tuning range due to the methods of realizing variable capacitors on-chip. Relaxation oscillators may be the most space efficient depending on the energy storage element (usually a capacitor). They also have a much wider tuning range than resonant-tank oscillators. The downfall of relaxation oscillators is that they utilize a regenerative switching element which increases the timing jitter. Ring oscillators strike a balance between larger area and higher complexity with respect to relaxation oscillators, while being fully realizable on an IC and having a broader tuning range than resonant-tank oscillators. Examples of all three types of voltage controlled oscillators are shown in Fig. 2.11.

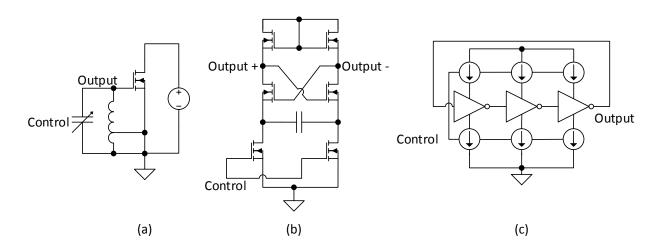

Fig. 2.11. LC Tank (Hartley) Oscillator (a), Relaxation (Source-Coupled) Oscillator (b), and Ring (Current-starved Inverter) Oscillator (c).

Voltage-controlled ring oscillators may be either single-ended or differential, and consist of a number of individual stages (called delay stages). To be classified as a ring oscillator, the number of delay stages must be three or more. The Barkhausen stability criterion, originally identified in the 1920s, assumes a linear system, and therefore cannot be considered an accurate

predictor of oscillation frequency. It remains, however, a useful heuristic to design the gain stages of a ring oscillator to support spontaneous oscillation. The Barkhausen criterion relates the forward loop gain A to the feedback gain  $\beta$ , and can be considered a necessary, but not sufficient, condition for oscillation:

$$|\beta A| = 1$$

$\angle \beta A = 2\pi n, n \in [0,1,2,3,...]$  (2.6)

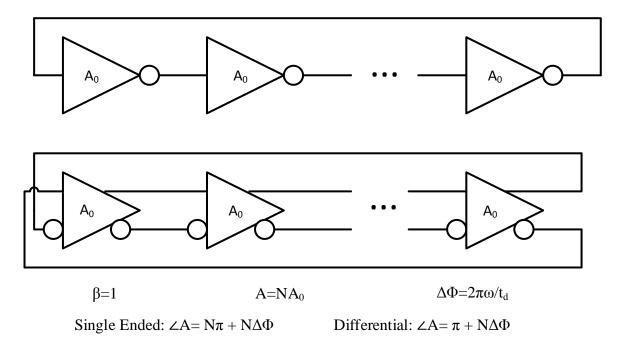

Since each delay stage will have a finite, but non-zero, time delay  $t_d$ , it will have an equivalent phase delay at its frequency of operation,  $\Delta\Phi$ . If a ring oscillator is connected so that the angle criterion is inherently satisfied, which is the case when a single-ended ring oscillator has an even number of stages ( $2n\pi$  for n stages), then  $\Delta\Phi$  must be zero, which is equivalent to a finite non-zero delay only at DC. Hence, single-ended ring oscillators must always have an odd number of stages. Similarly, differential ring oscillators must have an inversion present in the ring, but this is created by cross connecting the signals at one stage, and any number of stages greater than two can be used. Fig. 2.12 shows the Barkhausen criterion as it applies to both single-ended and differential ring oscillators.

Fig. 2.12. Barkhausen criterion applied to single-ended and differential ring oscillators of N stages.

Further, the Barkhausen criterion equations are often used to determine the minimum gain necessary to stimulate oscillation from a quiescent condition. The delay stages are assumed to have a first order response with a -3 dB frequency  $\omega_0$ , and the gain at the oscillation frequency  $A_{osc}$  must be 1. The minimum DC gain is calculated for N stages:

$$\Delta \Phi = \frac{\pi}{N} = \tan^{-1} \frac{\omega_{osc}}{\omega_0}$$

(2.7)

$$\omega_{osc} = \omega_0 \tan \frac{\pi}{N} \tag{2.8}$$

$$1 = |A_{osc}| = \frac{A_{DC}\omega_0}{\sqrt{\omega_0^2 + \omega_{osc}^2}} = \frac{A_{DC}\omega_0}{\sqrt{\omega_0^2 + \omega_0^2 \tan \frac{\pi}{N}}}$$

(2.9)

$$A_{DC} = \sqrt{1 + \left(\tan\frac{\pi}{N}\right)^2} \tag{2.10}$$

The equality in Eq. (2.10) is often generalized as a minimum, and the equation rewritten as

$$A_{DC} \ge sec\left(\frac{\pi}{N}\right) \tag{2.11}$$

Eq. (2.11) is referred to as the secant criterion [33], [34]. The result of this analysis shows a minimum DC gain of 2 for three stages,  $\sqrt{2}$  for four stages, and so on asymptotically approaching a DC gain of 1 for an infinite number of stages. This minimum gain is not trivial in SiC IC processes, and can be used as one method to test the robustness of the delay stage design.

## 2.2.4 Delay Stage Topologies

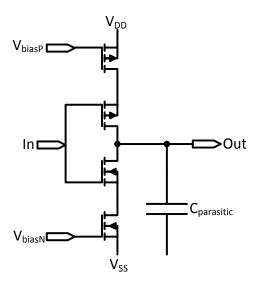

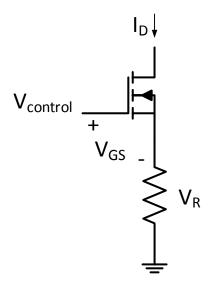

Several delay cell topologies are popular for voltage-controlled ring oscillators. The simplest is the current-starved inverter as shown in Fig. 2.11(c). The individual delay stage schematic is shown in Fig. 2.13. This delay cell is a popular single-ended delay stage for use in ring oscillators. At the center of the stack is an inverter, and the top and bottom FETs act as current sources to limit the slew rate going into the parasitic load capacitance. Ring oscillators built from current starved inverters have several benefits: simple biasing, compact layouts, rail-to-rail signal swing and straightforward design. The current-starved inverter ring oscillator suffers from the same drawbacks as all single-ended ring oscillators, namely poor supply-noise rejection and the requirement for an odd number of stages.

Fig. 2.13. Current-starved inverter delay stage.

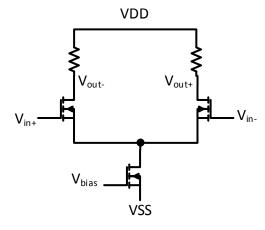

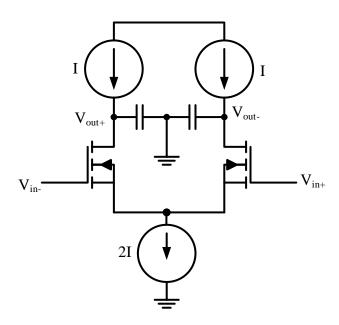

Another class of delay cells are the differential delay cells. These cells generally resemble differential-pair amplifier stages, although there are many variations [35]. Fig. 2.14 shows the simplest of these: a differential input cell with resistive loads. The delay can be controlled by adjusting the bias voltage to the tail current source, with smaller currents causing greater delays. The capacitive loading on this cell is the input gates of the next cell, just as it was for the current-starved inverter.

Fig. 2.14. Differential delay cell with resistive loads.

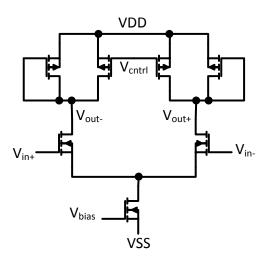

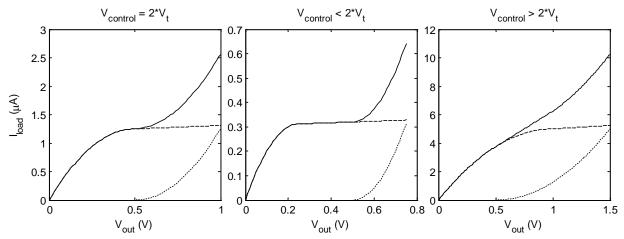

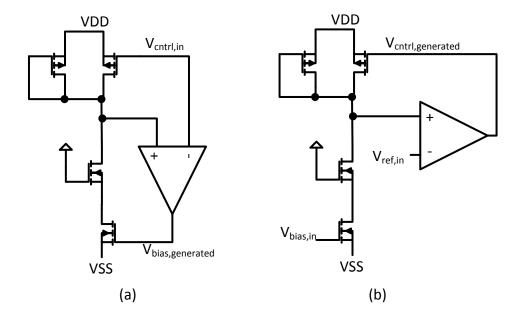

The Maneatis delay cell (Fig. 2.15) is extremely popular in the design of differential VCOs [33], [35]–[38]. This differential delay cell utilizes a load described as a symmetric load. Each leg has a pair of equally-sized PMOS devices, one diode-connected, and one separately-connected. The name "symmetric load" comes from the fact that the I-V characteristic is odd-symmetric about the middle point of the output voltage swing. Fig. 2.16 shows the I-V characteristic of a notional symmetric load including a finite output resistance. In the symmetric load,  $V_{cntrl}$  must be generated by a special biasing circuit to achieve the desired output swing when all of the cell current (2I<sub>D</sub>) is passing through a single load. Two versions of this biasing circuit, called a half-buffer replica, are shown in Fig. 2.17 [39].

Fig. 2.15. Maneatis delay cell found in differential VCOs.

The bias of the symmetric load can be generated in two different ways. In many cases, the control voltage input of the PLL is used to generate a bias voltage for the tail current sources in the Maneatis delay cells as shown in Fig. 2.17(a) [36]–[38]. It is also possible to use a fixed value for  $V_{ref}$  to set the swing of the delay cells while controlling the tail current independently, as shown in Fig. 2.17(b) [40].

Fig. 2.16. Symmetric load output behavior at different values of  $V_{control}$  with respect to  $V_t$ .

Fig. 2.17. Half-buffer replica biasing circuits for the Maneatis delay cell. The circuit in (a) has a single control input voltage that sets the bias current and the delay cell output swing, while the circuit in (b) forces the output swing to be fixed at  $V_{ref}$ , and  $V_{bias,in}$  is provided to the delay cells as well.

#### CHAPTER 3 – DEVICE PARAMETERS FOR SILICON CARBIDE CMOS

Despite the existence of advanced models for computer simulation, and algorithms for computer-based circuit design, effective hand-design models and methods are still very valuable. Hand-design work allows the designer to develop intuition, investigate design trade-offs, and prove important causal relationships while investigating a circuit topology. Since its publication in 1968, the Shichman and Hodges Insulated Gate FET model<sup>1</sup> has been the standard bearer for designing circuits with these devices [41].

$$I_{D} = \frac{\mu C_{ox} \frac{W}{L} \left[ (V_{GS} - V_{T}) V_{DS} - \frac{V_{DS}^{2}}{2} \right] (1 + \lambda V_{DS})}{\frac{\mu C_{ox}}{2} \frac{W}{L} (V_{GS} - V_{T})^{2} (1 + \lambda V_{DS})} \qquad V_{DS} > V_{GS} = V_{T}$$

(3.1)

As device channel lengths grew smaller and smaller, Shichman and Hodges' model became inaccurate for predicting MOSFET behavior. Work done in the first half of the 1980s by individuals at MIT, Bell Labs, and UC Berkeley showed that carrier velocity saturation led to a very different equation for drain current [42], and the omnipresent UC Berkeley modeling and simulation group further developed this into a model suitable for short channel MOSFETs in 1996 [43]. This work is the seed for all short-channel design methods since that time [40]. Short channel devices can be described physically as devices where the gate length is comparable to the source and drain depletion region width, indicating that edge effects cannot be ignored in

27

<sup>&</sup>lt;sup>1</sup> In modern texts, it has become common to drop the lambda term in the triode equation  $(V_{DS} \le V_{GS} - V_T)$  because the primary physical mechanism that defines lambda, channel pinchoff, only occurs in the saturation region. The original Shichman and Hodges model, however, includes lambda in both regions. The SPICE level 3 model *also* includes lambda in both equations in order to avoid a discontinuity in the first derivative. In this work, both versions are used, but the modern version, where the triode equation has no lambda term and the saturation equation lambda term is 1+λ( $V_{DS}$ - $V_{GS}$ + $V_T$ ) is used unless otherwise noted.

analyzing their behavior. Empirically, short channel devices show several effects not seen in long channel devices. These include, among others, velocity saturation, drain-induced barrier lowering (DIBL), the short channel effect (which has a similar behavior to DIBL), mobility reduction, and bulk-charge effects.

Arguably, the single effect which defines the difference between short- and long-channel behaviors is velocity saturation. Mobility is defined as the relationship between the drift velocity of the charge carrier and the applied electric field:

$$v_d = \mu E \tag{3.2}$$

Without velocity saturation, the drift velocity increases linearly with electric field, the mobility stays constant, and the drain current increases with the square of  $v_{gs}$ - $V_t$  as seen in Eq. (3.1). When the carrier velocity saturates, however, the observed mobility has a negative slope which cancels the increase in electric field. Drain current is no longer dependent on device length, and is approximately linearly dependent on applied gate voltage [42]:

$$I_d = WC_{ox}v_{SAT}(v_{gs} - V_t - V_{ds,sat})$$

(3.3)

Other models, such as the EKV model, have been proposed for both short- and long-channel devices [44]. These generally address specific deficiencies in the basic models such as the sub-threshold region. While these models enable new design methods in Si ICs, it will be demonstrated here that significant improvements can be made without abandoning the Shichman-Hodges framework.

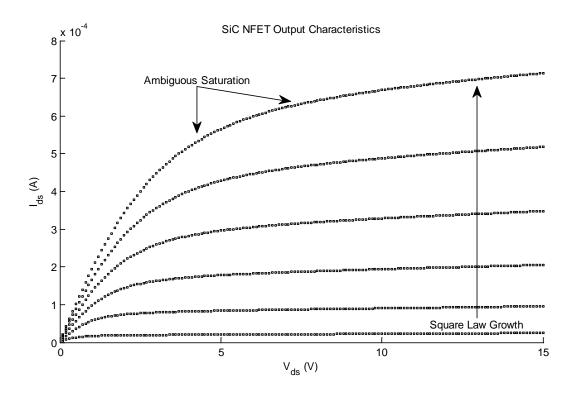

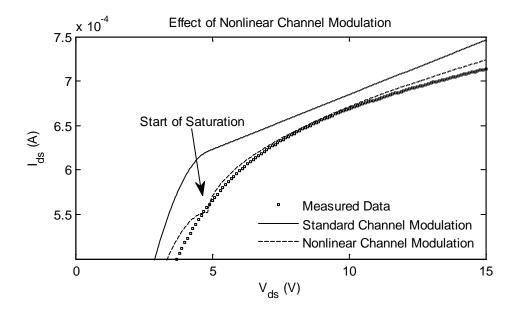

A brief inspection of SiC MOSFET output curves in Fig. 3.1 shows what these devices are not. SiC MOSFETs of the type described in this work do not show signs of velocity

saturation. They are clearly not short-channel devices from this perspective. At the same time, they begin to show signs of saturation at drain-source voltages much less than the overdrive voltage,  $v_{gs}$ - $V_t$ , and there is no exactly identifiable transition point between triode and saturation operation. This soft transition between triode and saturation has been observed in at least one other SiC IC process [8], [9]. In this dissertation, a variety of approaches to understanding the SiC MOSFET are examined, and an improved Shichman and Hodges model is formed empirically. This analysis forms the basis of designs and methods presented in later chapters.

Fig. 3.1. Measured output characteristic of a SiC N-channel MOSFET at  $V_{\rm gs}$  values of 5, 7, 9, 11, 13, and 15 V.

#### 3.1 Using the Standard Shichman-Hodges Model with SiC

The documentation provided even for commercially available long-channel Si IC fabrication processes often does not contain recommended values for the Shichman-Hodges parameters  $k'_p$ ,  $k'_n$ ,  $\lambda_p$ ,  $\lambda_n$ ,  $V_{t,p}$ , and  $V_{t,n}$ . For long channel processes, these parameters are easily extracted from simulation. For short channel processes, a target operating point is usually selected, and the small-signal parameters are estimated for this bias point from simulation data [40].

When trying to fit SiC devices, the poor fidelity to the existing long channel models limits the range that can be used with hand-design parameters. Early SiC IC design efforts relied on a level 3 SPICE model, so parameters were extracted over the entire operating range of the devices, whether it fit actual device behavior or not [45], [46]. Experience at the University of Arkansas has shown that emulating the short-channel method, where a device operating point is selected from data, and small- and large-signal parameters matching the local region around this operating point, can lead to successful designs [8], [9]. In preparing for the first tapeout with the HTSiC process, a similar method was utilized. In contrast with previous methods employed at the UA, a graphical method of estimating parameters was used, which also gave an intuitive understanding of where these parameters would be more and less accurate.

# 3.2 Parameter Estimation, Bias Point Selection, and Standard Device Sizes in the Standard Shichman-Hodges Model

Before beginning the design process, the simulation device models most likely to be used for analog design (W = 20  $\mu$ m, and L=2  $\mu$ m and 5  $\mu$ m) were characterized using a simulation testbench. This process involved developing estimates for the basic Shichman-Hodges

parameters  $k'_p$ ,  $k'_n$ ,  $\lambda_p$ ,  $\lambda_n$ ,  $V_{t,p}$ , and  $V_{t,n}$ . The goal was to allow hand calculations using the parameters which would give a reasonable match to the bias-point and transient results obtained during simulation.

The first parameter estimated,  $\lambda$ , was calculated from Eq. (3.4). This calculation could be done without assumptions about any other Shichman-Hodges parameters, since it only requires sweeping  $v_{DS}$  and measuring  $i_{DS}$  of the device model. To obtain the best estimate of  $\lambda$ ,  $v_{GS}$  of the devices was stepped from 5 to 15 V, and a single value that would approximately minimize error was chosen visually. For the PFET case, values were kept positive, and the sources were connected to apply  $v_{SG}$  and  $v_{SD}$  instead. The visual estimations based on calculated  $\lambda$  curves for NFETs and PFETs are shown in Fig. 3.2 and Fig. 3.3, respectively.

$$\lambda = \frac{\partial i_D}{\partial v_{DS}} * \frac{1}{i_D} \tag{3.4}$$

Fig. 3.2. Estimation of  $\lambda$  for NFETs.

Fig. 3.3. Estimation of  $\lambda$  for PFETs.

With an estimation of  $\lambda$  complete, two different methods of estimating  $V_t$  and k' were used. The first, corresponding to the modern channel modulation formulation in the saturation equation (Eq. (3.5)) and the second corresponding to the original formulation (Eq. (3.6)).

$$i_D = k' \frac{W}{L} (v_{GS} - V_t)^2 [1 + \lambda (v_{DS} - (v_{GS} - V_t))] \quad v_{DS} \ge v_{GS} - V_t$$

(3.5)

$$i_D = k' \frac{W}{L} (v_{GS} - V_t)^2 [1 + \lambda v_{DS}] \quad v_{DS} \ge v_{GS} - V_t$$

(3.6)

To obtain the estimations of  $V_t$  and k',  $v_{DS}$  was swept, and  $V_t$  was stepped in 50 mV steps (effectively "guessing" a value of  $V_t$  at each step). The value of  $v_{gs}$  was set equal to  $v_{DS}+V_t$  to maintain the devices exactly in saturation (and negating  $\lambda$  for the modern formulation). For NFETs,  $V_t$  was stepped from 2.5 to 3.35 V. And for PFETs  $V_t$  was stepped from 3.2 to 4 V. To select an estimate of  $V_t$ , the plots were visually inspected and the  $V_t$  corresponding to the flattest

line was chosen. Then, a value of k' was selected visually to approximately minimize the error. Fig. 3.4 through Fig. 3.7 show these simulation results and parameter estimations. The modern channel-modulation formulation is labelled "No  $\lambda$ ".

Table II contains the parameter values selected for the four devices after the procedure described above. These values were selected from the plots using the modern channel modulation formulation.

Fig. 3.4. Estimation of  $V_t$  and  $k^\prime$  for 20  $\mu m$  / 2  $\mu m$  NFETs.

Fig. 3.5. Estimation of  $V_t$  and k' for 20  $\mu m$  / 5  $\mu m$  NFETs.

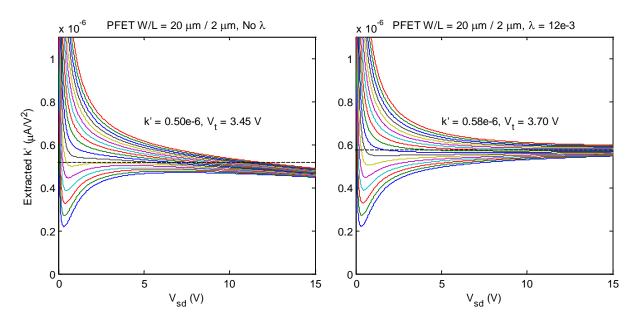

Fig. 3.6. Estimation of  $V_t$  and  $k^\prime$  for 20  $\mu m$  / 2  $\mu m$  PFETs.

Fig. 3.7. Estimation of  $V_t$  and  $k^\prime$  for 20  $\mu m$  / 5  $\mu m$  PFETs.

**TABLE II.**EXTRACTED SHICHMAN-HODGES PARAMETERS FOR HTSIC MOSFETS

| Device                 | Parameter               | Value                   |  |

|------------------------|-------------------------|-------------------------|--|

| NFET<br>W/L=20 μm/2 μm | $V_{t}(V)$              | 2.85                    |  |

|                        | k' (μΑ/V <sup>2</sup> ) | 1.0x10 <sup>-6</sup>    |  |

|                        | $\lambda (V^{-1})$      | 0.013                   |  |

| NFET<br>W/L=20 μm/5 μm | $V_{t}(V)$              | 2.90                    |  |

|                        | $k'(\mu A/V^2)$         | 0.75x10 <sup>-6</sup>   |  |

|                        | λ (V <sup>-1</sup> )    | 0.006                   |  |

| PFET<br>W/L=20 μm/2 μm | $V_{t}(V)$              | 3.45                    |  |

|                        | k' (μΑ/V <sup>2</sup> ) | $0.50 \text{x} 10^{-6}$ |  |

|                        | λ (V <sup>-1</sup> )    | 0.012                   |  |

| PFET<br>W/L=20 μm/5 μm | $V_{t}(V)$              | 3.65                    |  |

|                        | k' (μΑ/V <sup>2</sup> ) | $0.30 \times 10^{-6}$   |  |

|                        | λ (V <sup>-1</sup> )    | 0.004                   |  |

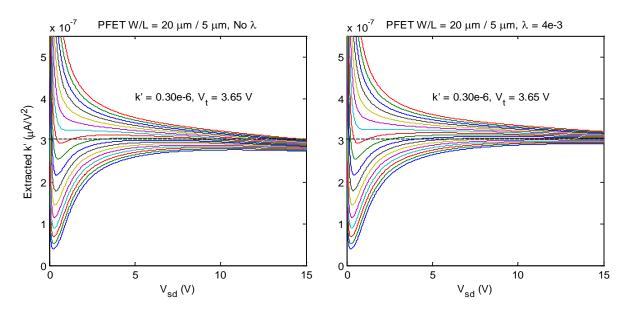

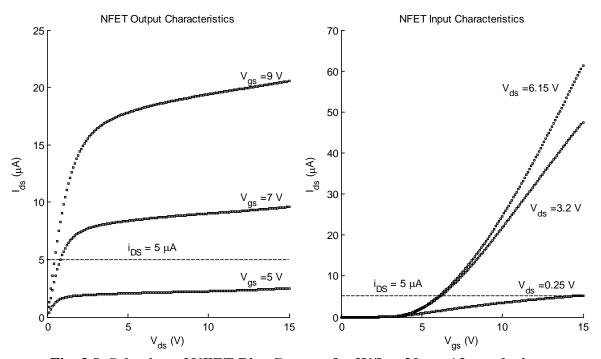

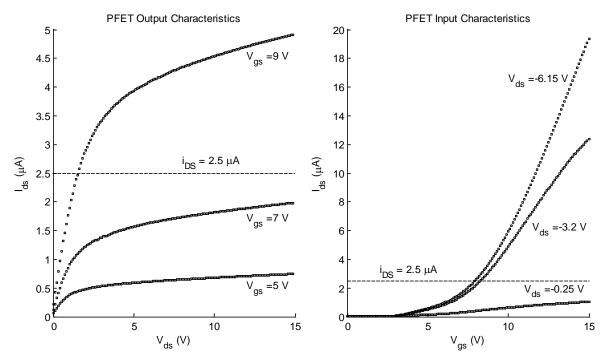

Beyond estimating the Shichman-Hodges parameters, a general bias point was identified from the test device measurements. The NFET and PFET W/L =  $20~\mu m$  /  $2~\mu m$  device curves were examined, and bias currents of  $5~\mu A$  and  $2.5~\mu A$  were chosen, respectively. Fig. 3.8 and Fig. 3.9 show the input and output curves, and the selected currents for the devices. This also indicates a sizing ratio of 1:2 for the NFETs and PFETs with L =  $2~\mu m$ .

Fig. 3.8. Selection of NFET Bias Current for W/L =  $20 \mu m / 2 \mu m$  device.

Fig. 3.9. Selection of PFET Bias Current for W/L =  $20 \mu m / 2 \mu m$  device.

In Baker's *CMOS: Circuit Design, Layout, and Simulation*, the author recommends choosing  $v_{DS}$ , sat equal to 5% of VDD, which for this process would be 750 mV [40]. Alternately, calculating  $v_{DS,sat}$  using Eq. (3.7), yields an approximate value of 707 mV for the chosen current.

$$v_{DS,sat} \approx \sqrt{\frac{i_D}{k'} \frac{L}{W}}$$

(3.7)

The resulting standard device operating points, including a set of bias points for W/L =  $20 \mu m / 5 \mu m$  devices is shown in Table III. This is analogous to Table 9.1 in Baker's text [40]. Although the self-gain,  $g_m r_o$ , of the L =  $5 \mu m$  devices is significantly higher than the L =  $2 \mu m$  devices, the order of magnitude increase in the gate area to achieve the same bias current causes a significant reduction in the transition frequency,  $f_T$ , so the L =  $5 \mu m$  devices are unsuitable for any applications requiring transient performance.

**TABLE III.**HTSIC MOSFET PARAMETERS FOR GENERAL ANALOG DESIGN

| Parameter                                 | NFET<br>20μm / 2μm                | PFET<br>20μm / 2μm | NFET<br>20μm / 5μm | PFET<br>20μm / 5μm |  |

|-------------------------------------------|-----------------------------------|--------------------|--------------------|--------------------|--|

| Bias Current                              | 5 μΑ                              |                    |                    |                    |  |

| W/L                                       | 20/2                              | 40/2               | 60/5               | 160/5              |  |

| m                                         | 1                                 | 2                  | 3                  | 8                  |  |

| V <sub>DS,sat</sub> , V <sub>SD,sat</sub> | 707 mV                            | 707 mV             | 745 mV             | 722 mV             |  |

| $V_{GS}, V_{SG}$                          | 3.56 V                            | 4.16 V             | 3.65 V             | 4.37 V             |  |

| $V_t$                                     | 2.85 V                            | 2.90 V             | 3.45 V             | 3.65 V             |  |

| k'                                        | $1.0~\mu\text{A/V}^2$             | $0.5 \mu A/V^2$    | $0.75 \ \mu A/V^2$ | $0.3 \mu A/V^2$    |  |

| C'ox                                      | $0.86 \text{ fF} / \mu\text{m}^2$ |                    |                    |                    |  |

| $C_{ox}$                                  | 34.5 fF                           | 69.0 fF            | 259 fF             | 690 fF             |  |

| $C_{gsn}, C_{sgp}$                        | 23 fF                             | 46.0 fF            | 173 fF             | 460 fF             |  |

| $C_{gdn}, C_{dgp}$                        | 11.5 fF                           | 23.0 fF            | 86.3 fF            | 230 fF             |  |

| $g_m$                                     | 10 μA/V                           | 10 μA/V            | 9.5 μΑ/V           | 9.8 μΑ/V           |  |

| $r_o$                                     | 15.4 ΜΩ                           | 16.7 ΜΩ            | 33.3 ΜΩ            | 50.0 MΩ            |  |

| $g_m r_o$                                 | 154 V/V                           | 167 V/V            | 316 V/V            | 490 V/V            |  |

| λ                                         | 0.013                             | 0.012              | 0.006              | 0.004              |  |

| $f_T$                                     | 69.2 MHz                          | 34.6 MHz           | 8.73 MHz           | 3.39 MHz           |  |

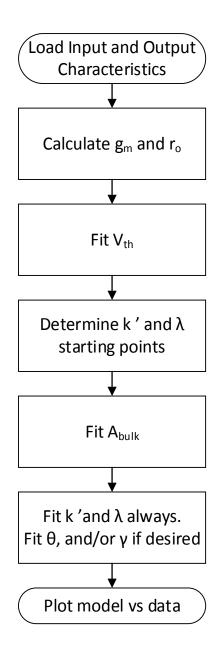

# 3.3 An Improved Shichman-Hodges Model for SiC MOSFETs

Although successful design work has been presented with the existing hand-design models, there is still a need for a hand-design model with more fidelity. Current models are

limited to a single bias-point, meaning that they are not very useful for large-signal analysis. The rest of this chapter will be dedicated to improvements in the existing Shichman-Hodges model.

Before formulating an improved model for hand-design using SiC MOSFETs, it is important to explicitly state goals for an optimal hand-design model:

- A solution should exist for each variable. The equation(s) should have a directly computable equation for each individual terminal voltage or current given all of the other terminal voltages and currents.

- 2. An expression for the partial derivative with respect to gate-source or drain-source voltage ( $g_m$  and  $r_o$ ) should exist and fulfill criteria number 1.

- 3. If piecewise-defined functions are necessary (such as in Shichman-Hodges), it should be possible to determine if the correct region of operation was assumed *a posteriori*.