# University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

5-2012

# Characterization and Modeling of 4H-SiC Low Voltage MOSFETs and Power MOSFETs

Mihir Mudholkar University of Arkansas, Fayetteville

Follow this and additional works at: http://scholarworks.uark.edu/etd

Part of the VLSI and Circuits, Embedded and Hardware Systems Commons

## Recommended Citation

Mudholkar, Mihir, "Characterization and Modeling of 4H-SiC Low Voltage MOSFETs and Power MOSFETs" (2012). Theses and Dissertations. 268.

http://scholarworks.uark.edu/etd/268

This Dissertation is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, ccmiddle@uark.edu.

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical Engineering

By

Mihir Mudholkar

Indian Institute of Technology

Bachelor of Technology, 2006

May 2012

University of Arkansas

#### **Abstract**

The integration of low voltage and high voltage circuits on SiC has profound applications. SiC power devices have proved their superiority in terms of high temperature operation, faster switching frequencies and larger power densities when compared with Si power devices. The control of SiC power devices however, lies in the hands of low voltage circuits built on Si. Thus, there exists a separation in the overall system between the low voltage and high voltage side, which increases system cost, weight and reduces efficiency. With the advancement in low voltage SiC processing technology, low voltage control circuits can be made on the same die as power devices, and power systems will become compact, robust and more efficient.

A new low voltage process in 4H-SiC has been characterized and modeled. In order to design circuits with the low voltage process, designers need accurate device models for simulation. Currently, there exist no compact models in the public domain for low voltage SiC MOSFETs. This work aims at filling that void, by providing a modified PSP model for SiC MOSFETs. In addition, a new compact model for SiC power MOSFETs has also been developed and validated with characterization data from a commercially available 1200 V, 20 A power MOSFET. A gate driver chip has been designed and fabricated in 4H-SiC using the developed models. The gate driver chip will drive commercially available power MOSFETs in an integrated AC/DC converter application.

| This dissertation is approved for      |

|----------------------------------------|

| recommendation to the Graduate Council |

| Graduite Council                       |

|                                        |

| Dissertation Director:                 |

|                                        |

|                                        |

|                                        |

| Dr. H. A. Mantooth                     |

|                                        |

|                                        |

|                                        |

| Dissertation Committee:                |

|                                        |

|                                        |

|                                        |

| Dr. S. Ang                             |

|                                        |

|                                        |

|                                        |

| Dr. J. C. Balda                        |

|                                        |

|                                        |

|                                        |

| Dr. R. McCann                          |

| DI. K. MCCann                          |

|                                        |

|                                        |

|                                        |

| Dr. G. Niu                             |

©2012 by Mihir Mudholkar

All Rights Reserved

# **Dissertation Duplication Release**

| I hereby auth  | orize the University of Arkansas Libraries to duplicate this |

|----------------|--------------------------------------------------------------|

| dissertation v | when needed for research and/or scholarship.                 |

|                |                                                              |

|                |                                                              |

| Agreed         |                                                              |

|                | Mihir Mudholkar                                              |

#### Acknowledgements

Completing a Doctoral degree is a culmination of several factors that help shape the path of the research. It requires guidance, inspiration, financial support, support from family, helpful colleagues and friends. I would like to take this opportunity to thank everyone who helped me shape the path of my research.

First of all, a big thanks is due to Dr. Mantooth who has been a source of inspiration throughout this journey. He has helped me mentally become capable of thinking like a responsible scientist, provided me with financial support and guided me throughout my graduate process.

I would like to thank my committee members - Dr. Ang, Dr. Balda, Dr. McCann, and Dr. Niu for providing me with insightful thoughts a and feedback on my graduate work. A special thanks to Dr. Niu who has been very involved with my graduate work over numerous projects, and guided me technically in a number of areas.

I would like to also thank my parents - Neeraj and Rijuta Mudholkar who have believed in this endeavour from the first day and have supported me with everything.

Special thanks are due to my wife Iti, who has been a source of patience, encouragement, unconditional love and has been with me through the best and worst of times.

Finally, I would also like to thank my teammates at the University of Arkansas MSCAD Lab, who have toiled in the sand with me on a numerous occasions, given me valuable technical assistance and have made my graduate days very enjoyable and memorable.

# **Contents**

| 1  | Intr  | oduction                             | 1   |

|----|-------|--------------------------------------|-----|

|    | 1.1   | Motivation                           | 1   |

|    | 1.2   | SiC Power MOSFET Modeling            | 6   |

|    | 1.3   | SiC Low Voltage MOSFET Modeling      | 8   |

|    | 1.4   | Dissertation Structure               | 9   |

| 2  | Bac   | kground                              | 10  |

|    | 2.1   | SiC Material Properties              | 10  |

|    | 2.2   | SiC Power MOSFET                     | 15  |

|    | 2.3   | Development Challenges               |     |

|    | 2.4   | Device Modeling                      | 23  |

| 3  | SiC   | Low Voltage Process                  | 30  |

|    | 3.1   | Test Chip Design                     |     |

|    | 3.2   | Substrate Types                      |     |

|    | 3.3   | Device Doping Profiles               | 40  |

|    | 3.4   | Depletion MOSFET Characterization    | 51  |

|    | 3.5   | Enhancement MOSFET Characterization  | 66  |

| 4  | SiC   | PSP Model                            | 86  |

|    | 4.1   | Surface Potential Relation           | 90  |

|    | 4.2   | Modeling Interface Traps             |     |

|    | 4.3   | Parameter Extraction                 | 112 |

|    | 4.4   | Depletion MOSFET Model Performance   |     |

|    | 4.5   | Enhancement MOSFET Model Performance | 136 |

| 5  | Pow   | ver MOSFET Model                     | 155 |

|    | 5.1   | Introduction                         |     |

|    | 5.2   | Model Description                    | 158 |

|    | 5.3   | Parameter Extraction                 | 165 |

|    | 5.4   | Model Performance                    | 177 |

| 6  | Mod   | del Simulation Verification          | 185 |

|    | 6.1   | 1.5 V Reference Circuit              | 186 |

| 7  | Con   | iclusion And Future Work             | 192 |

|    | 7.1   | Summary                              | 192 |

|    | 7.2   | Primary Contributions                | 194 |

|    | 7.3   | Future Work                          | 194 |

|    | 7.4   | Conclusion                           | 196 |

| Re | feren | nces                                 | 197 |

# **List of Figures**

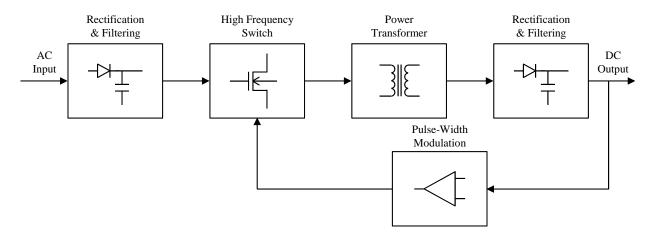

| 1.1  | General schematic of a Switch-Mode Power Supply                                           | 2  |

|------|-------------------------------------------------------------------------------------------|----|

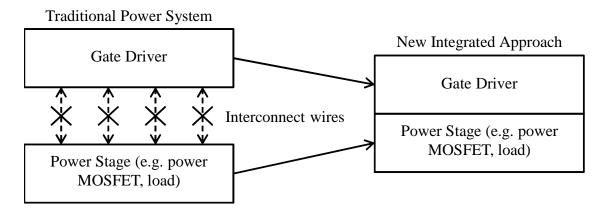

| 1.2  | Integration of gate driver with the power MOSFET                                          | 5  |

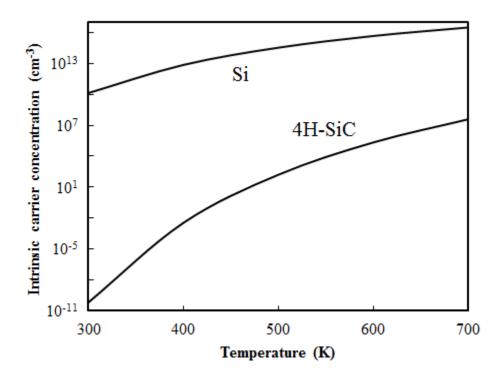

| 2.1  | Intrinsic carrier concentration of Si and 4H-SiC over temperature                         | 12 |

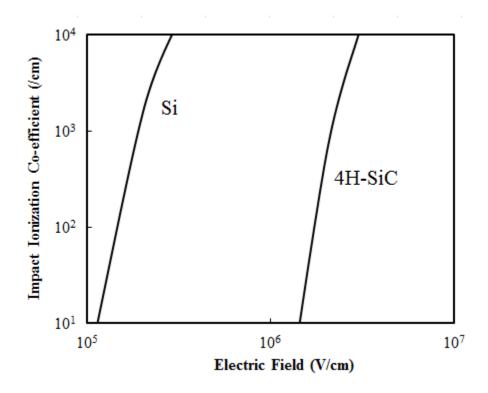

| 2.2  | Impact ionization coefficients of Si and 4H-SiC at room temperature                       | 14 |

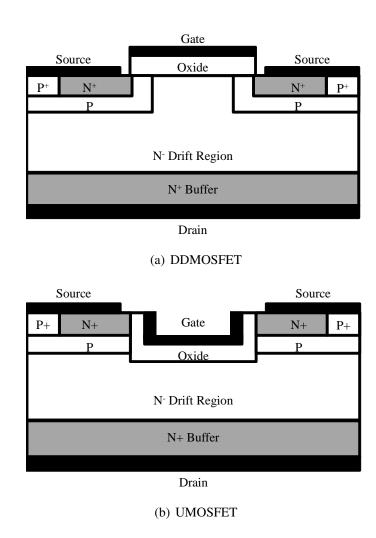

| 2.3  | Power MOSFET structures                                                                   | 17 |

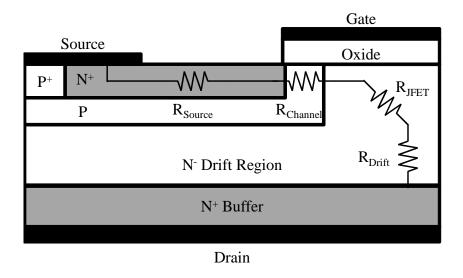

| 2.4  | Contributions to the on-state resistance in a DMOSFET structure                           | 18 |

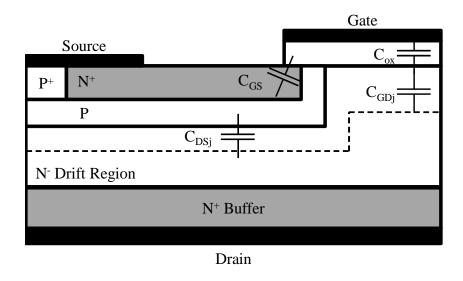

| 2.5  | Internal capacitances in the power MOSFET                                                 | 22 |

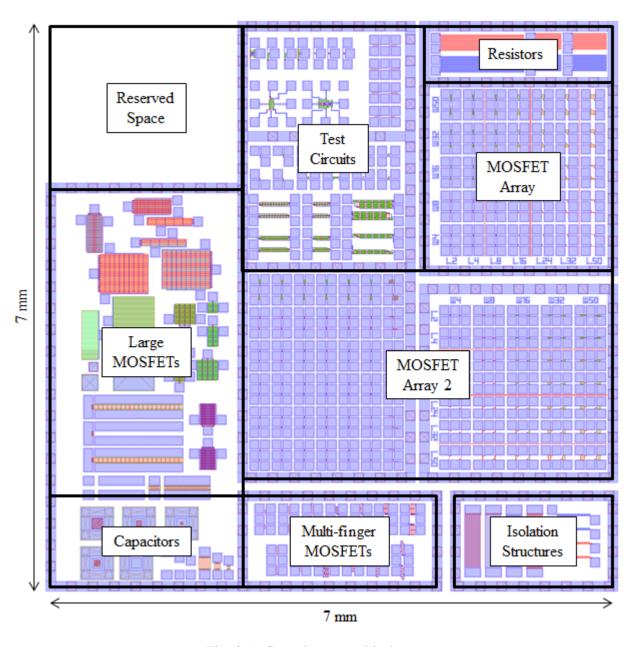

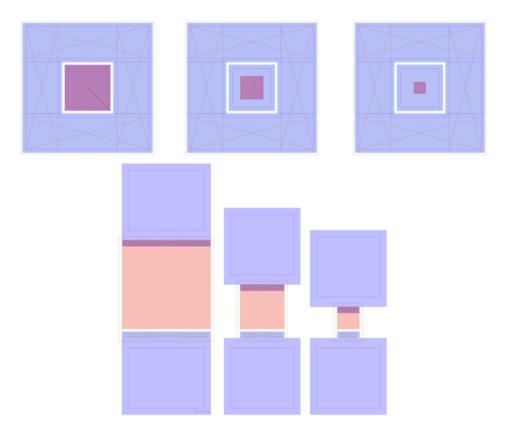

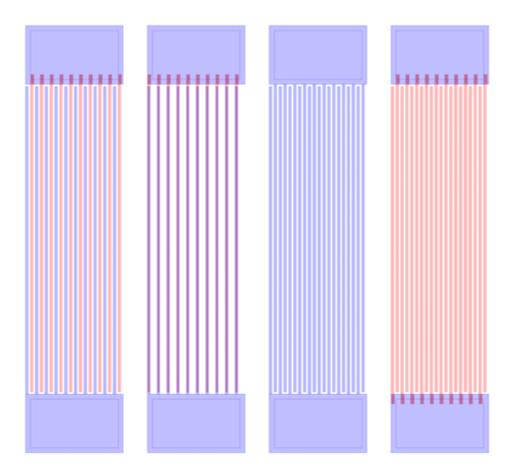

| 3.1  | Complete test-chip layout                                                                 | 32 |

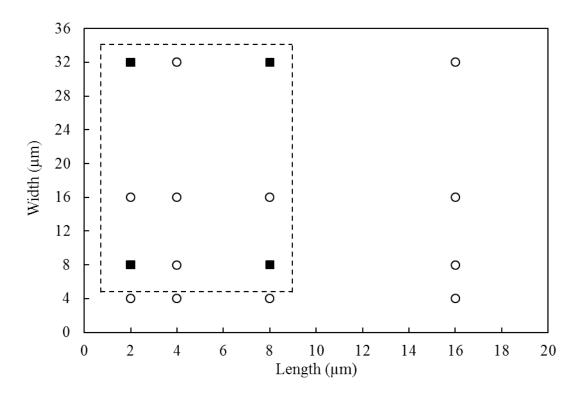

| 3.2  | Device sizes in the device array                                                          | 33 |

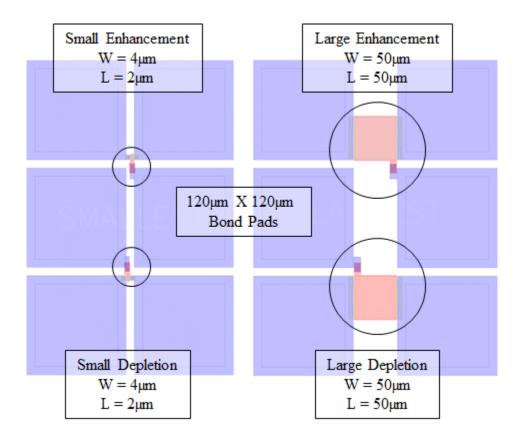

| 3.3  | Layout of the smallest and largest device                                                 | 34 |

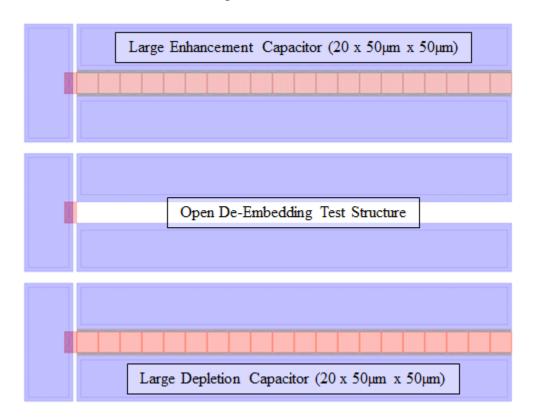

| 3.4  | Large device capacitance structure with open de-embedding                                 | 35 |

| 3.5  | Metal-substrate capacitor test structure                                                  | 36 |

| 3.6  | Metal-poly capacitor test structures                                                      | 37 |

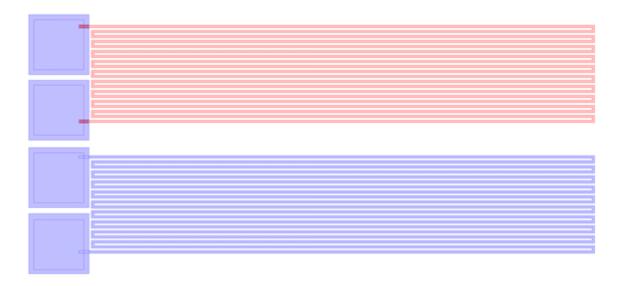

| 3.7  | Wound resistors in poly (top) and metal (bottom)                                          | 38 |

| 3.8  | Isolation test structures                                                                 | 39 |

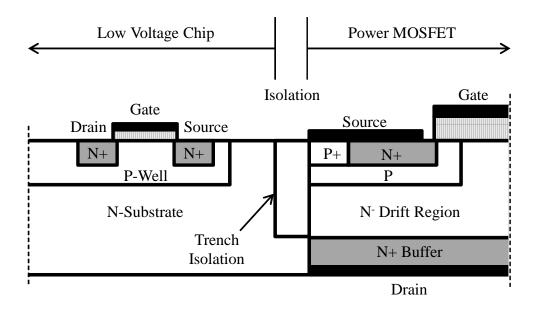

| 3.9  | Integration of the power MOSFET and low voltage process                                   | 40 |

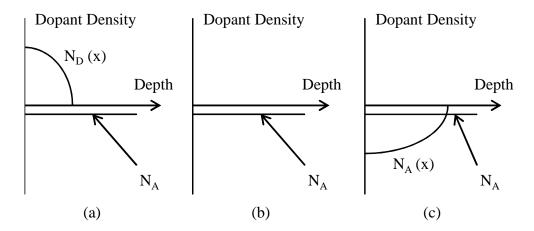

| 3.10 | Doping profiles of (a) Depletion, (b) Enhancement without threshold adjust and            |    |

|      | (c) Enhancement with threshold adjust devices                                             | 41 |

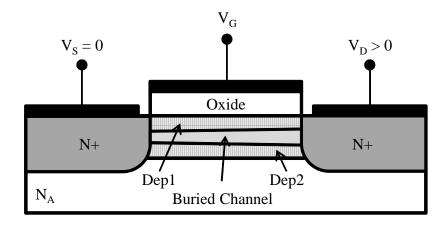

| 3.11 | Double depletion layers and buried channel in a depletion MOSFET                          | 42 |

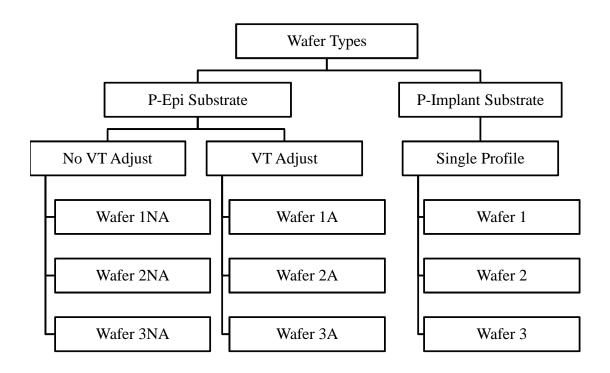

| 3.12 | Different wafer types available in the LV process                                         | 43 |

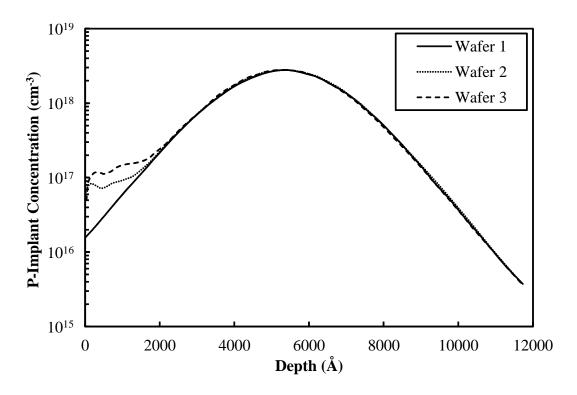

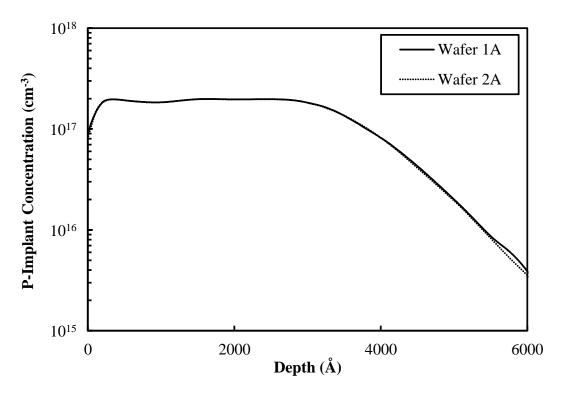

| 3.13 | P-implant profile on P-Implant well                                                       | 44 |

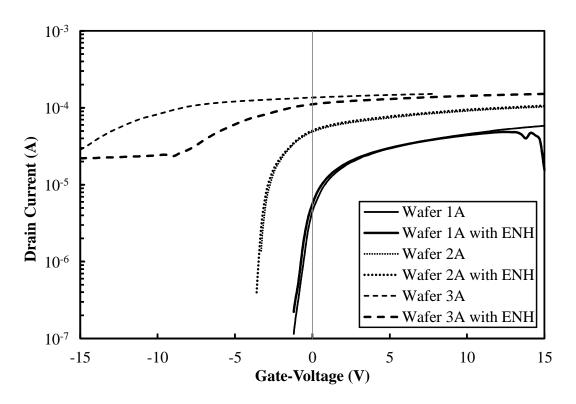

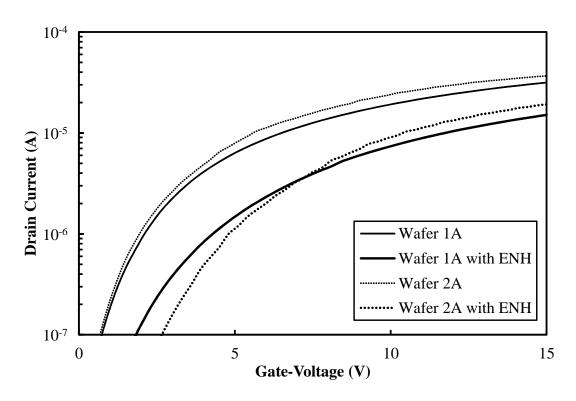

| 3.14 | $I_D - V_{GS}$ of 32 $\mu$ m $\times$ 2 $\mu$ m enhancement MOSFET of type P-Implant well | 45 |

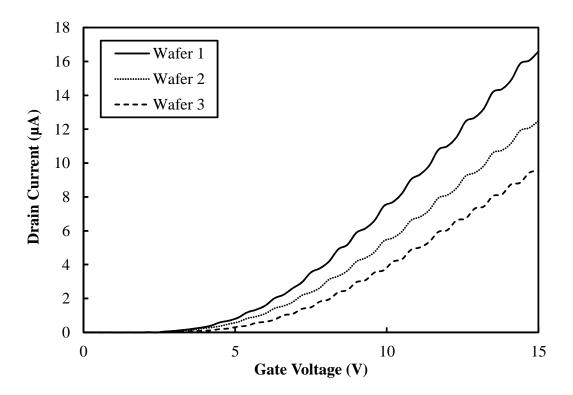

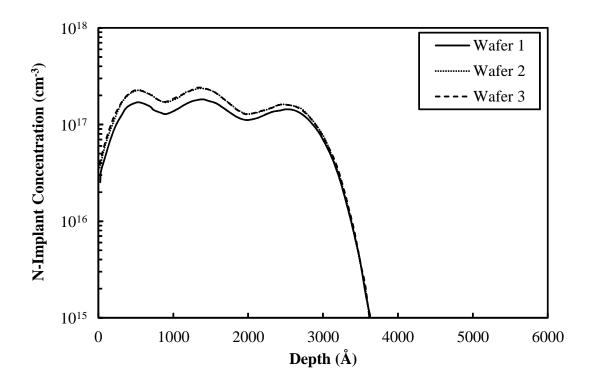

| 3.15 | N-implant profile on P-Implant well                                                       | 46 |

| 3.16 | $I_D - V_{GS}$ of 32 $\mu$ m $\times$ 2 $\mu$ m depletion MOSFET of type P-Implant well   | 47 |

| 3.17 | N-implant profile on P-Epi well                                                                                        | 48 |

|------|------------------------------------------------------------------------------------------------------------------------|----|

| 3.18 | $I_D - V_{GS}$ of 32 $\mu$ m $\times$ 2 $\mu$ m depletion MOSFET of type P-Epi well                                    | 49 |

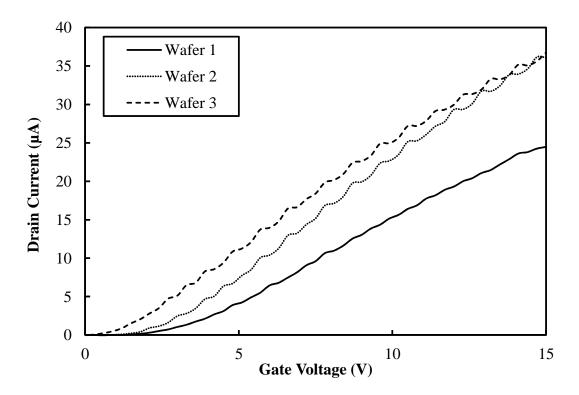

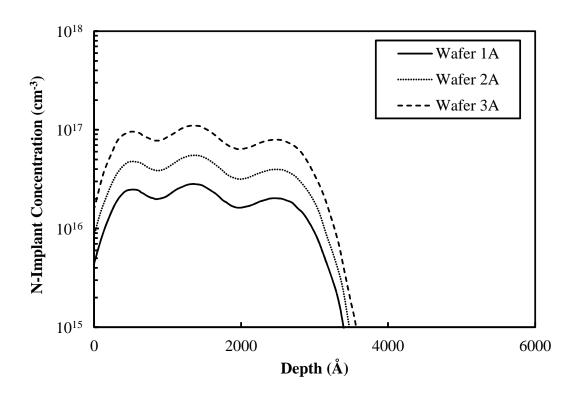

| 3.19 | P-implant ENH profile on P-Epi well                                                                                    | 49 |

| 3.20 | $I_D - V_{GS}$ of 32 $\mu$ m $\times$ 2 $\mu$ m enhancement MOSFET of type P-Epi well                                  | 50 |

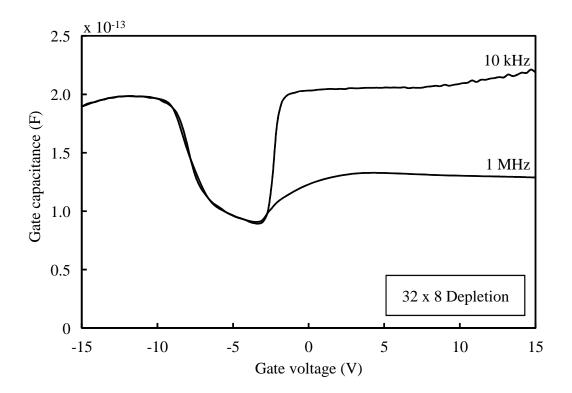

| 3.21 | Scaled $C_{GG} - V_G$ characteristics of a $32\mu m \times 8\mu m$ depletion MOSFET at 25 °C                           | 53 |

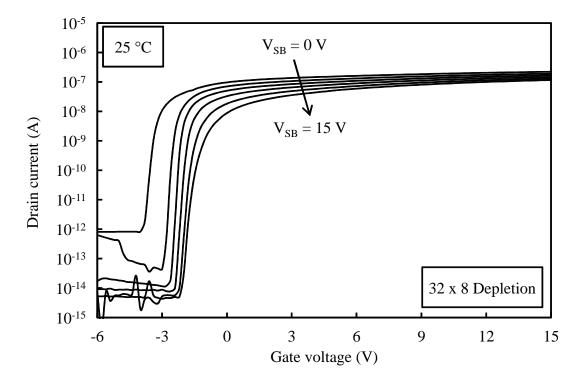

| 3.22 | $I_D - V_{GS}$ characteristics of $32\mu m \times 8\mu m$ depletion MOSFET at 25 °C                                    | 54 |

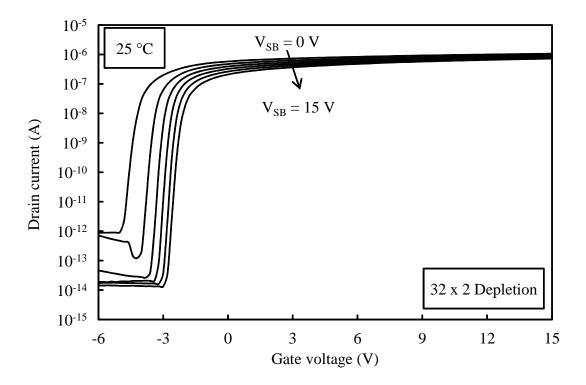

| 3.23 | $I_D - V_{GS}$ characteristics of $32\mu m \times 2\mu m$ depletion MOSFET at 25 °C                                    | 55 |

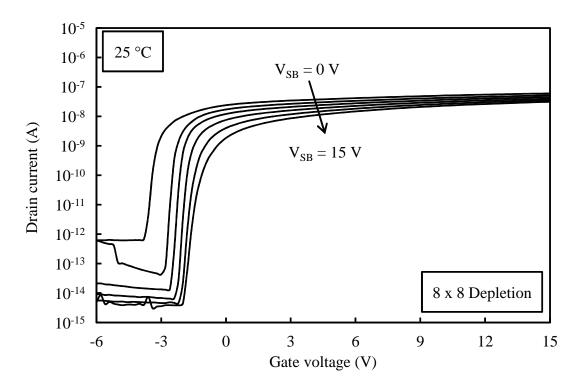

| 3.24 | $I_D - V_{GS}$ characteristics of $8\mu m \times 8\mu m$ depletion MOSFET at 25 °C                                     | 56 |

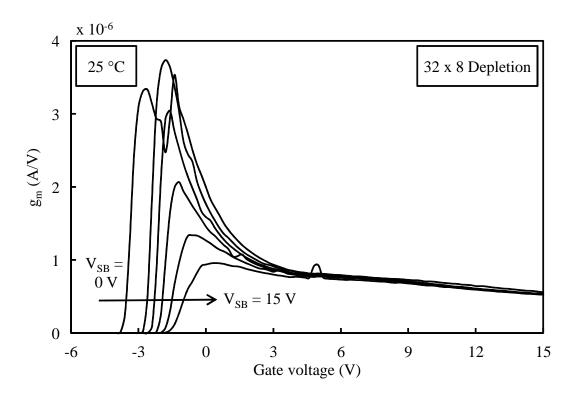

| 3.25 | $g_m - V_{GS}$ characteristics of $32\mu m \times 8\mu m$ depletion MOSFET at 25 °C                                    | 57 |

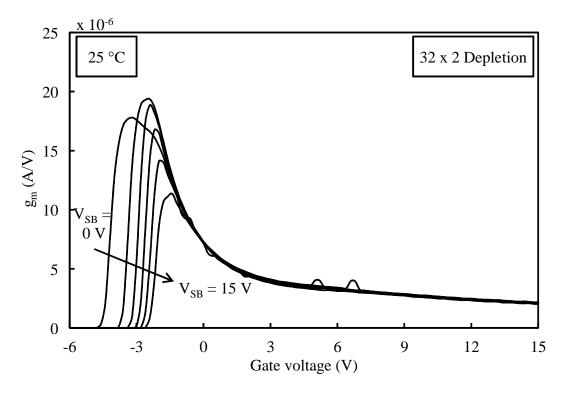

| 3.26 | $g_m - V_{GS}$ characteristics of $32\mu m \times 2\mu m$ depletion MOSFET at 25 °C                                    | 57 |

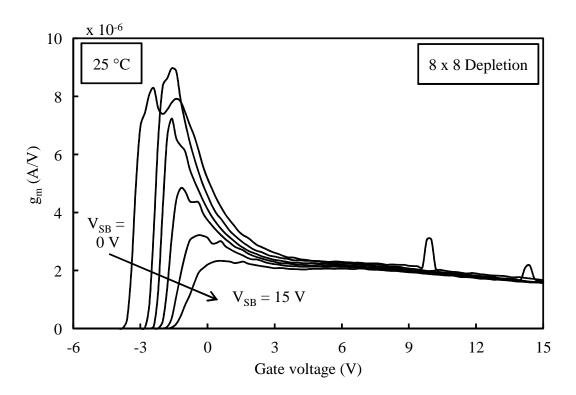

| 3.27 | $g_m - V_{GS}$ characteristics of $8\mu m \times 8\mu m$ depletion MOSFET at 25 °C                                     | 58 |

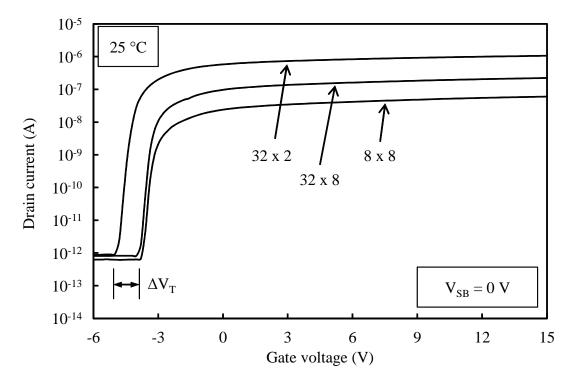

| 3.28 | Comparison of $I_D - V_{GS}$ characteristics ( $V_{SB} = 0 \ V$ ) of $32\mu m \times 8\mu m$ , $32\mu m \times 2\mu m$ |    |

|      | and 8μm×8μm depletion MOSFETs at 25 °C                                                                                 | 58 |

| 3.29 | $I_D - V_{GS}$ characteristics of $32\mu m \times 8\mu m$ depletion MOSFET at 25 °C, 125 °C and                        |    |

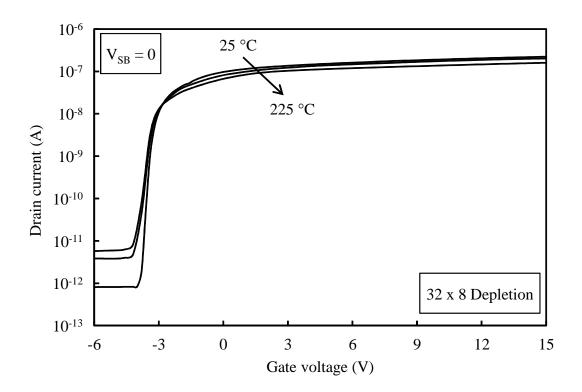

|      | 225 °C                                                                                                                 | 59 |

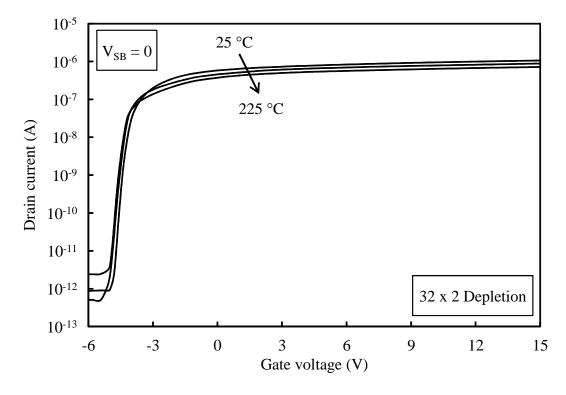

| 3.30 | $I_D - V_{GS}$ characteristics of $32\mu m \times 2\mu m$ depletion MOSFET at 25 °C, 125 °C and                        |    |

|      | 225 °C                                                                                                                 | 59 |

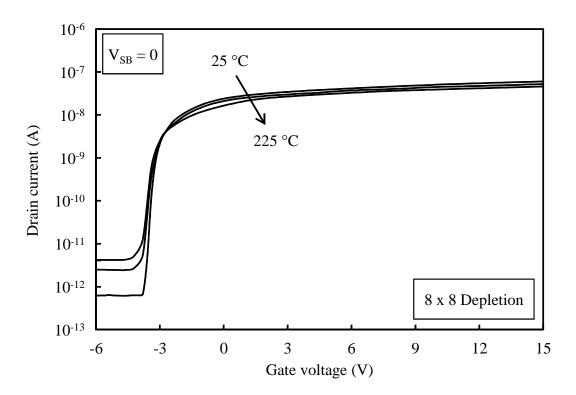

| 3.31 | $I_D-V_{GS}$ characteristics of $8\mu m\times 8\mu m$ depletion MOSFET at 25 °C, 125 °C and                            |    |

|      | 225 °C                                                                                                                 | 60 |

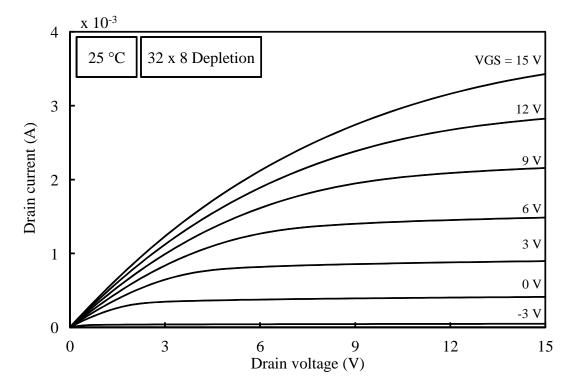

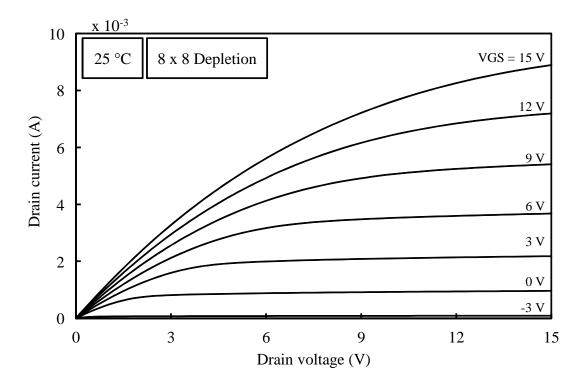

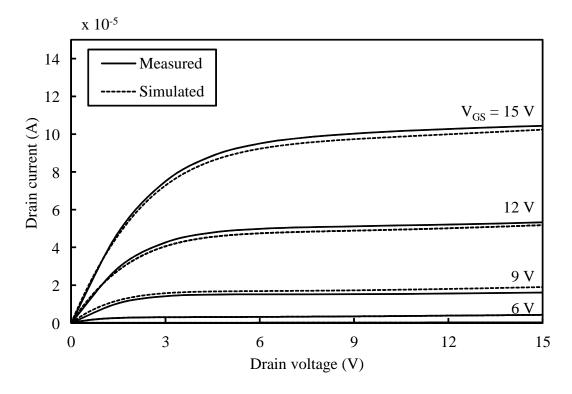

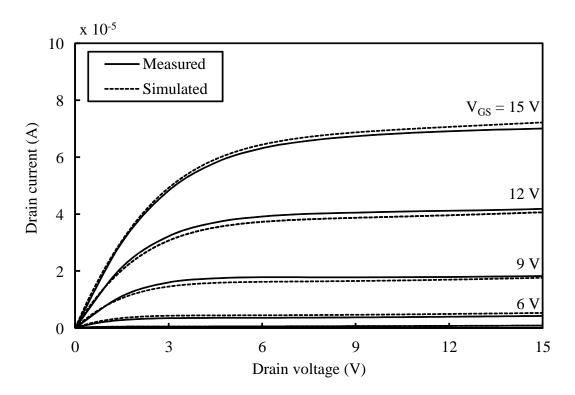

| 3.32 | $I_D - V_{DS}$ characteristics of $32\mu m \times 8\mu m$ depletion MOSFET at 25 °C                                    | 60 |

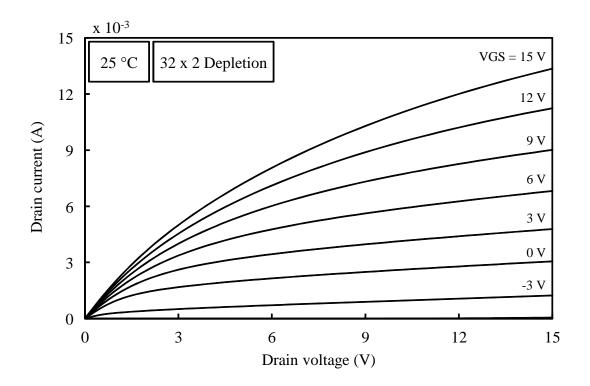

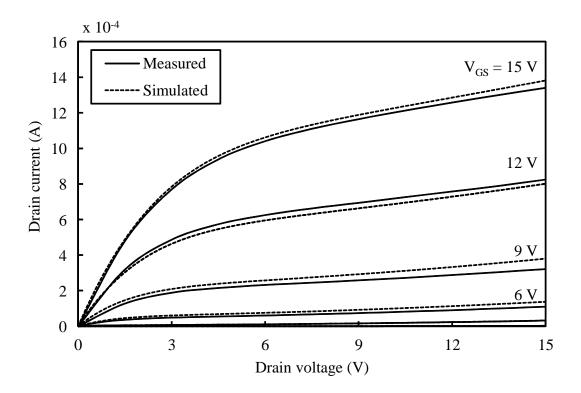

| 3.33 | $I_D - V_{DS}$ characteristics of $32\mu m \times 2\mu m$ depletion MOSFET at 25 °C                                    | 61 |

| 3.34 | $I_D - V_{DS}$ characteristics of $8\mu m \times 8\mu m$ depletion MOSFET at 25 °C                                     | 61 |

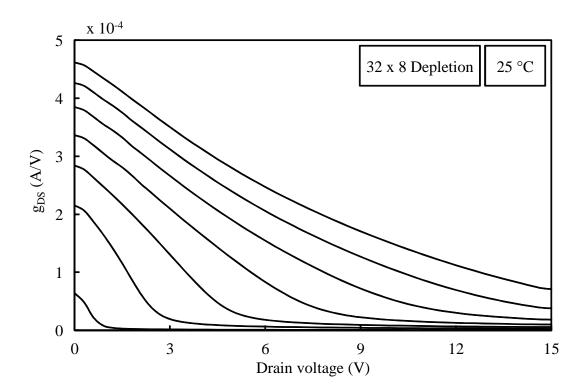

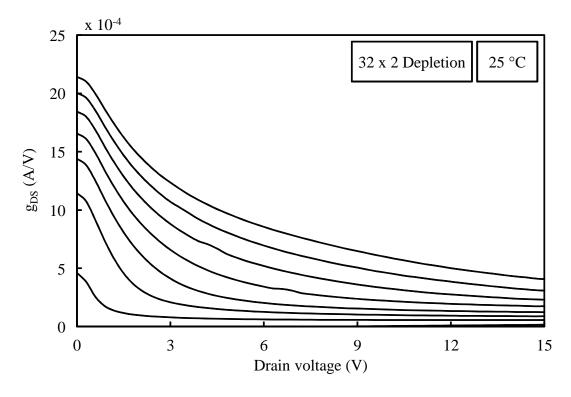

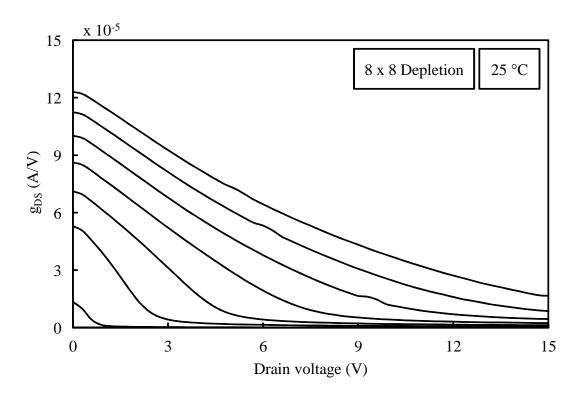

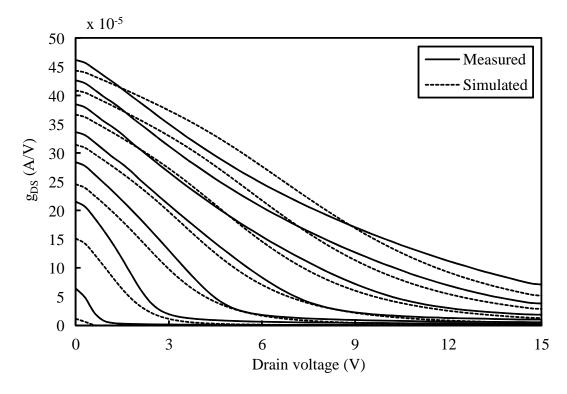

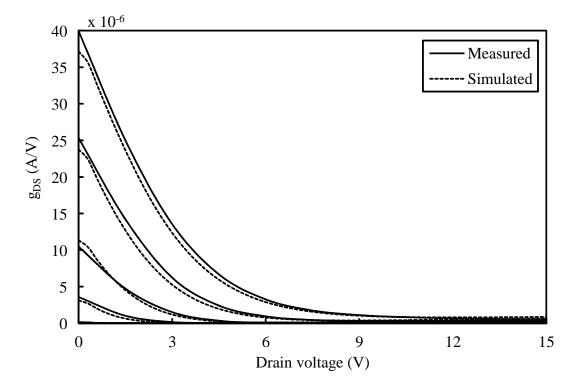

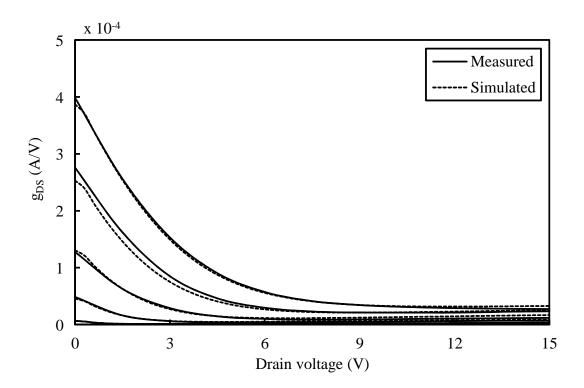

| 3.35 | $g_{DS} - V_{DS}$ characteristics of $32\mu m \times 8\mu m$ depletion MOSFET at 25 °C                                 | 62 |

| 3.36 | $g_{DS} - V_{DS}$ characteristics of $32\mu m \times 2\mu m$ depletion MOSFET at 25 °C                                 | 62 |

| 3.37 | $g_{DS} - V_{DS}$ characteristics of $8\mu m \times 8\mu m$ depletion MOSFET at 25 °C                                  | 63 |

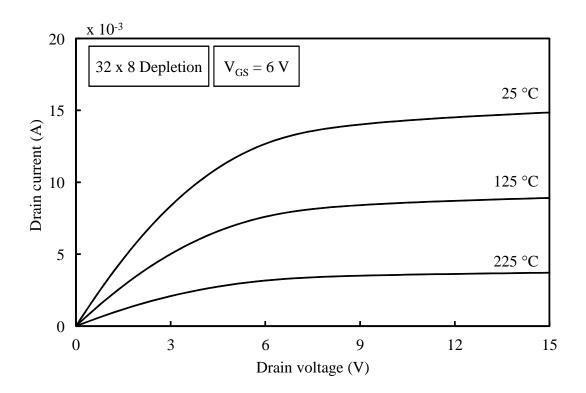

| 3.38 | $I_D - V_{DS}$ characteristics of $32\mu m \times 8\mu m$ depletion MOSFET over temperature                            | 64 |

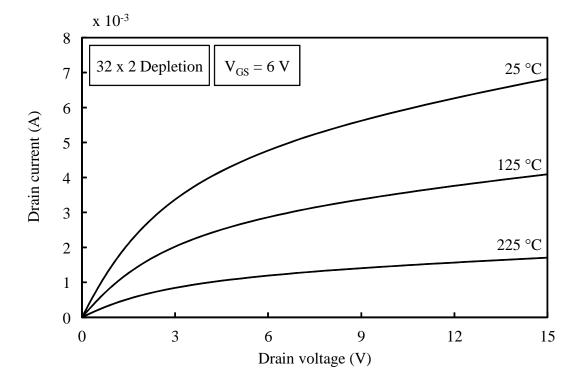

| 3.39 | $I_D - V_{DS}$ characteristics of $32\mu m \times 2\mu m$ depletion MOSFET over temperature                            | 64 |

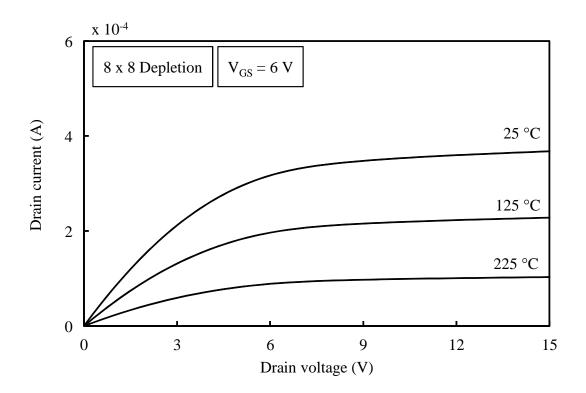

| 3.40 | $I_D - V_{DS}$ characteristics of $8\mu m \times 8\mu m$ depletion MOSFET over temperature                                                           | 65 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.41 | Comparison of $I_D - V_{DS}$ characteristics ( $V_{GS} = 6 \text{ V}$ ) of $32\mu\text{m} \times 8\mu\text{m}$ , $32\mu\text{m} \times 2\mu\text{m}$ |    |

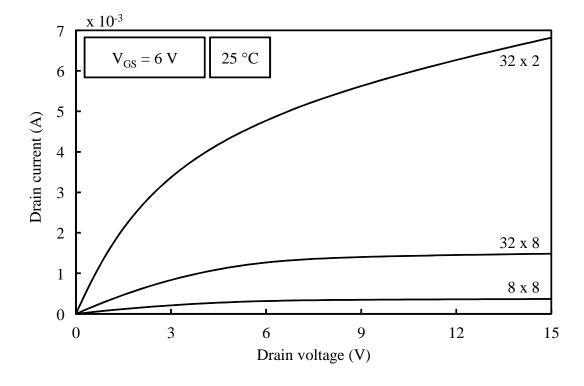

|      | and 8μm×8μm depletion MOSFETs at 25 °C                                                                                                               | 65 |

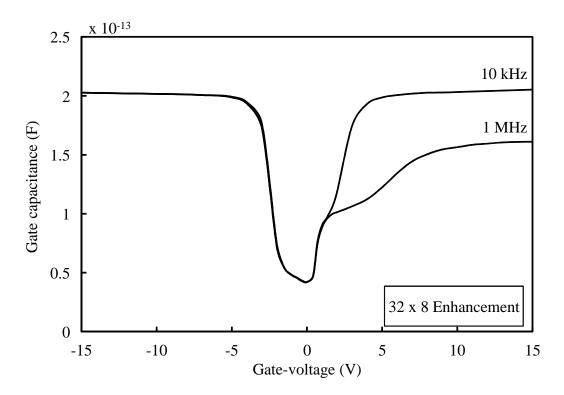

| 3.42 | Scaled $C_{GG} - V_G$ characteristics of a $32\mu m \times 8\mu m$ enhancement MOSFET at 25 °C .                                                     | 67 |

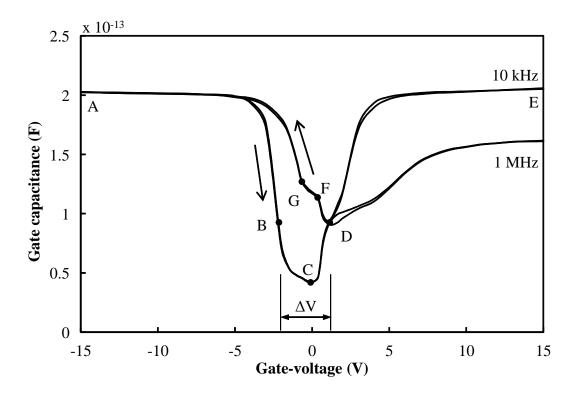

| 3.43 | $C_{GG} - V_G$ of a $32\mu m \times 8\mu m$ inversion-channel enhancement MOSFET. Bias sweep                                                         |    |

|      | rate is 0.1 V/s                                                                                                                                      | 69 |

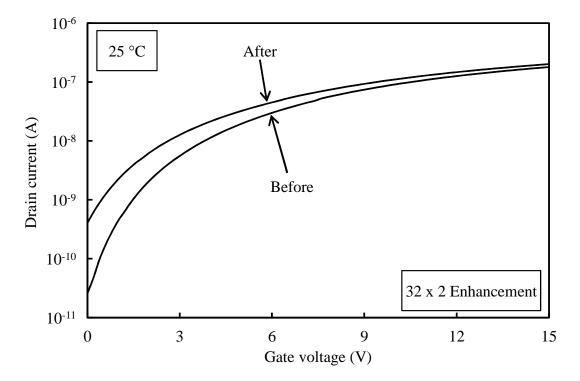

| 3.44 | Change in the $I_D - V_{GS}$ characteristics of a $32\mu m \times 2\mu m$ enhancement MOSFET, on                                                     |    |

|      | a fresh device (Before) and after some electrical measurements (After) at 25 $^{\circ}\text{C}~$                                                     | 72 |

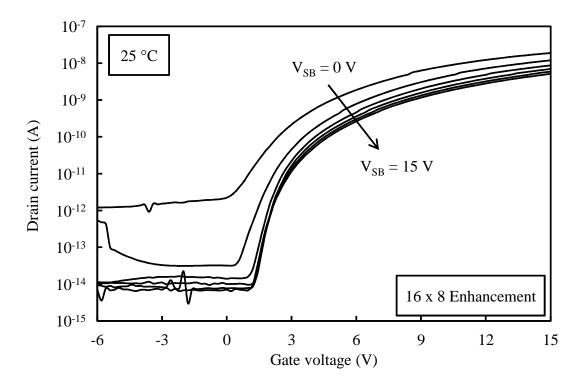

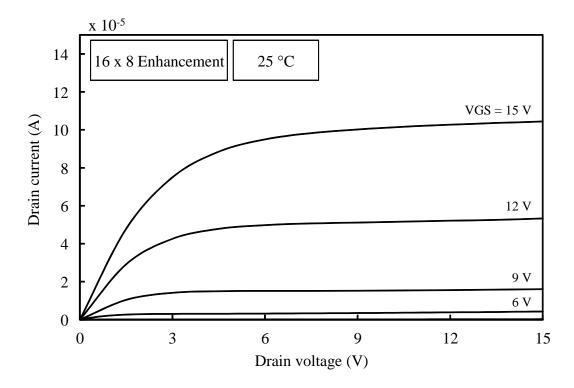

| 3.45 | $I_D - V_{GS}$ characteristics of $16\mu m \times 8\mu m$ enhancement MOSFET at 25 °C                                                                | 74 |

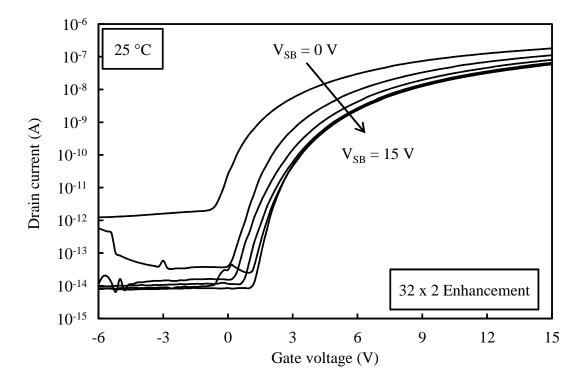

| 3.46 | $I_D - V_{GS}$ characteristics of $32\mu m \times 2\mu m$ enhancement MOSFET at 25 °C                                                                | 75 |

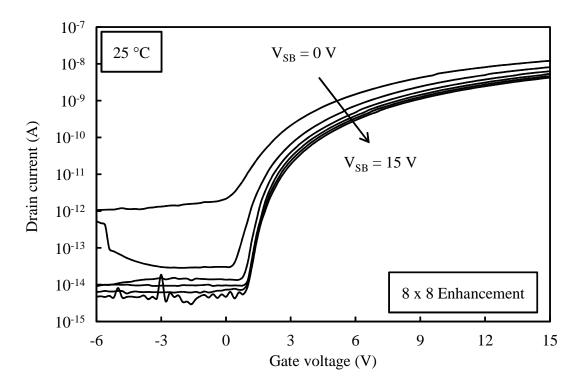

| 3.47 | $I_D - V_{GS}$ characteristics of $8\mu m \times 8\mu m$ enhancement MOSFET at 25 °C                                                                 | 76 |

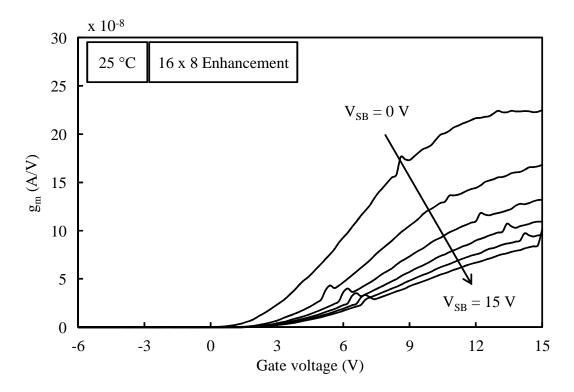

| 3.48 | $g_m - V_{GS}$ characteristics of $16\mu m \times 8\mu m$ enhancement MOSFET at 25 °C                                                                | 77 |

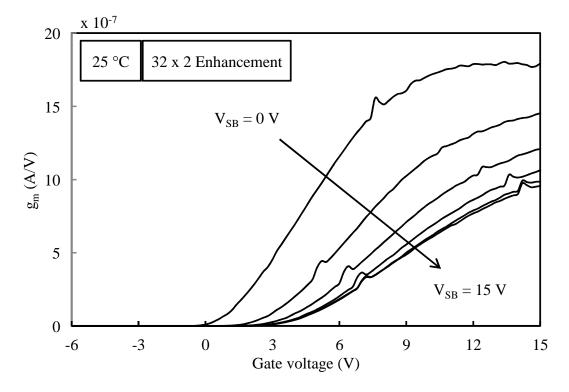

| 3.49 | $g_m - V_{GS}$ characteristics of $32\mu m \times 2\mu m$ enhancement MOSFET at 25 °C                                                                | 77 |

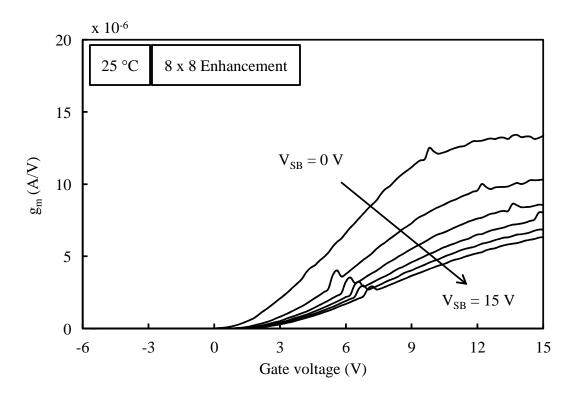

| 3.50 | $g_m - V_{GS}$ characteristics of $8\mu m \times 8\mu m$ enhancement MOSFET at 25 °C                                                                 | 78 |

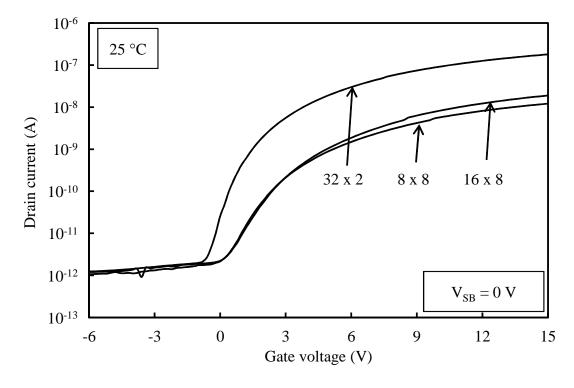

| 3.51 | Comparison of $I_D - V_{GS}$ characteristics ( $V_{SB} = 0 \ V$ ) of $16\mu m \times 8\mu m$ , $32\mu m \times 2\mu m$                               |    |

|      | and $8\mu m \times 8\mu m$ enhancement MOSFETs at 25 °C                                                                                              | 78 |

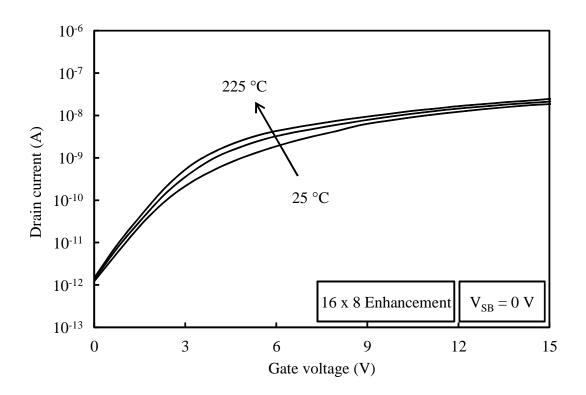

| 3.52 | $I_D - V_{GS}$ characteristics of $16\mu m \times 8\mu m$ enhancement MOSFET at 25 °C, 125 °C                                                        |    |

|      | and 225 $^{\circ}C$                                                                                                                                  | 79 |

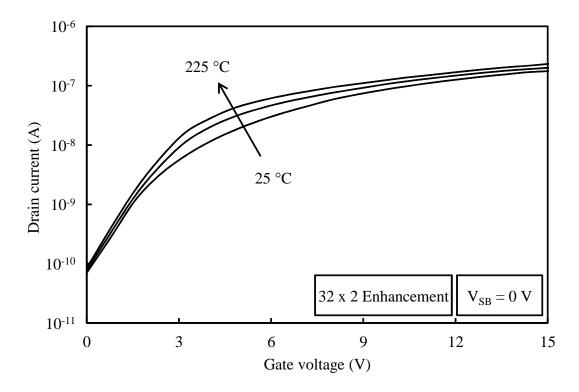

| 3.53 | $I_D - V_{GS}$ characteristics of $32\mu m \times 2\mu m$ enhancement MOSFET at 25 °C, 125 °C                                                        |    |

|      | and 225 $^{\circ}C$                                                                                                                                  | 79 |

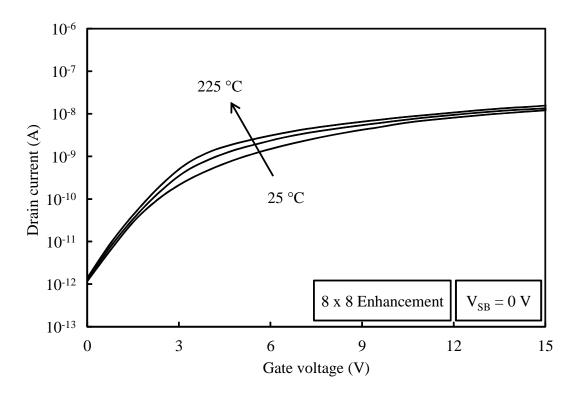

| 3.54 | $I_D - V_{GS}$ characteristics of $8\mu m \times 8\mu m$ enhancement MOSFET at 25 °C, 125 °C and                                                     |    |

|      | 225 °C                                                                                                                                               | 80 |

| 3.55 | $I_D - V_{DS}$ characteristics of $16\mu m \times 8\mu m$ enhancement MOSFET at 25 °C                                                                | 80 |

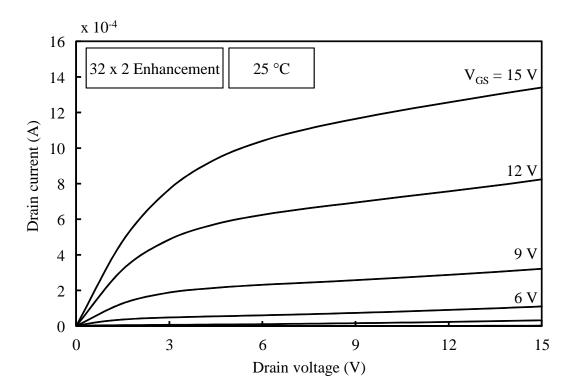

| 3.56 | $I_D - V_{DS}$ characteristics of $32\mu m \times 2\mu m$ enhancement MOSFET at 25 °C                                                                | 81 |

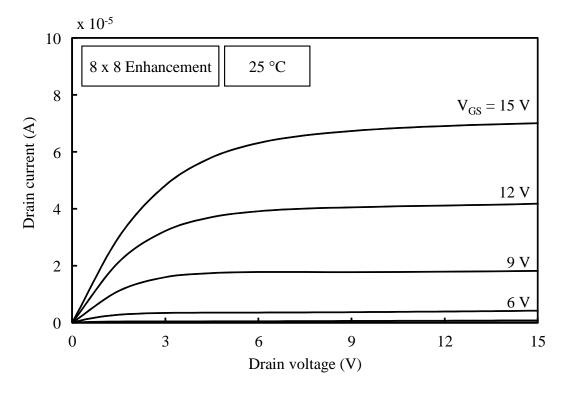

| 3.57 | $I_D - V_{DS}$ characteristics of $8\mu m \times 8\mu m$ enhancement MOSFET at 25 °C                                                                 | 81 |

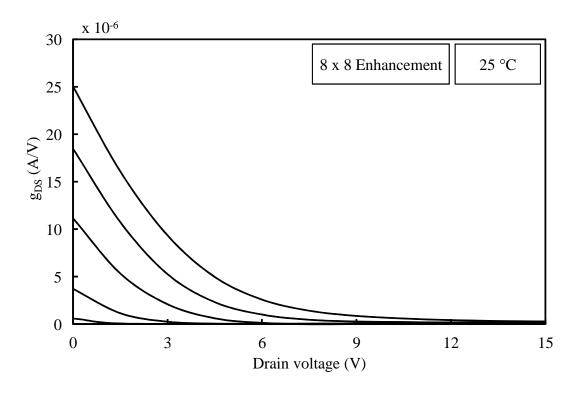

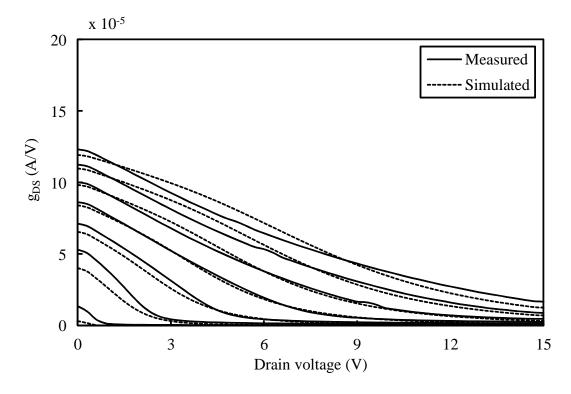

| 3.58 | $g_{DS} - V_{DS}$ characteristics of $16\mu m \times 8\mu m$ enhancement MOSFET at 25 °C                                                             | 82 |

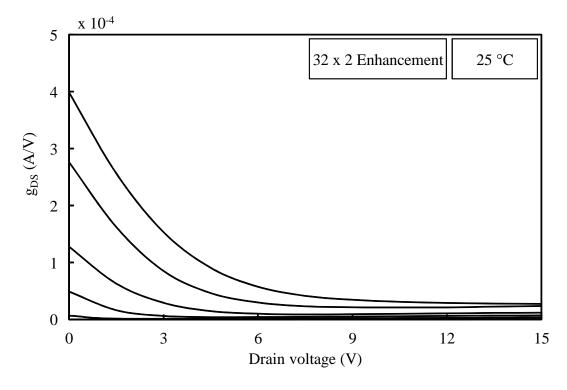

| 3.59 | $g_{DS} - V_{DS}$ characteristics of $32\mu m \times 2\mu m$ enhancement MOSFET at 25 °C                                                             | 82 |

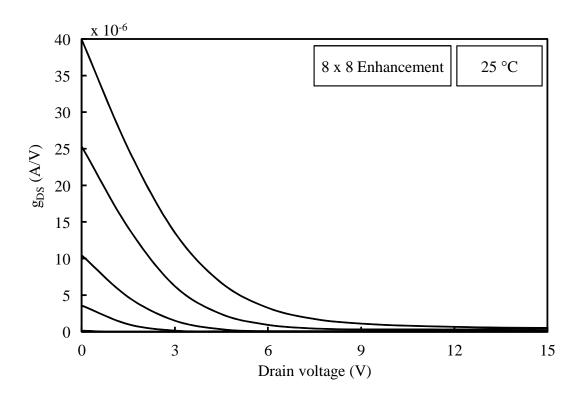

| 3.60 | $g_{DS} - V_{DS}$ characteristics of $8\mu m \times 8\mu m$ enhancement MOSFET at 25 °C 83                                |

|------|---------------------------------------------------------------------------------------------------------------------------|

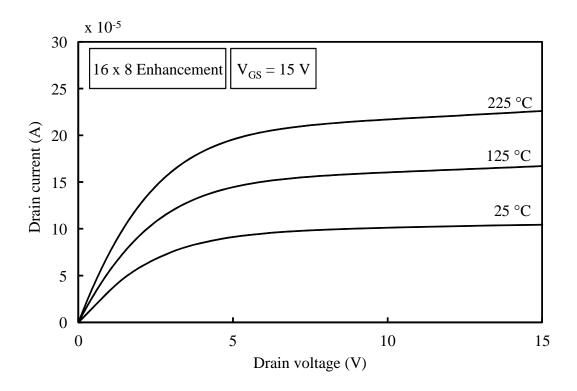

| 3.61 | $I_D - V_{DS}$ characteristics of $16\mu m \times 8\mu m$ enhancement MOSFET over temperature 84                          |

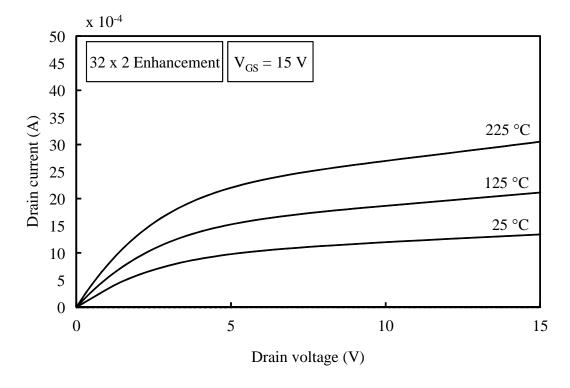

| 3.62 | $I_D - V_{DS}$ characteristics of $32\mu m \times 2\mu m$ enhancement MOSFET over temperature 84                          |

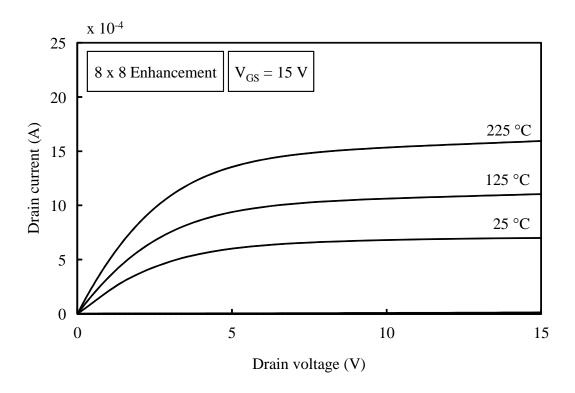

| 3.63 | $I_D - V_{DS}$ characteristics of $8\mu m \times 8\mu m$ enhancement MOSFET over temperature 85                           |

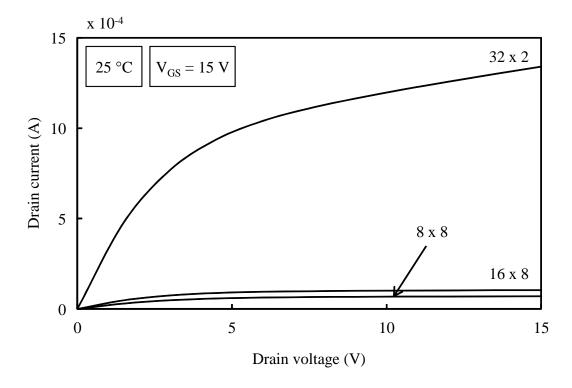

| 3.64 | Comparison of $I_D - V_{DS}$ characteristics ( $V_{GS} = 15 V$ ) of $16 \mu m \times 8 \mu m$ , $32 \mu m \times 2 \mu m$ |

|      | and $8\mu m \times 8\mu m$ enhancement MOSFETs at 25 °C                                                                   |

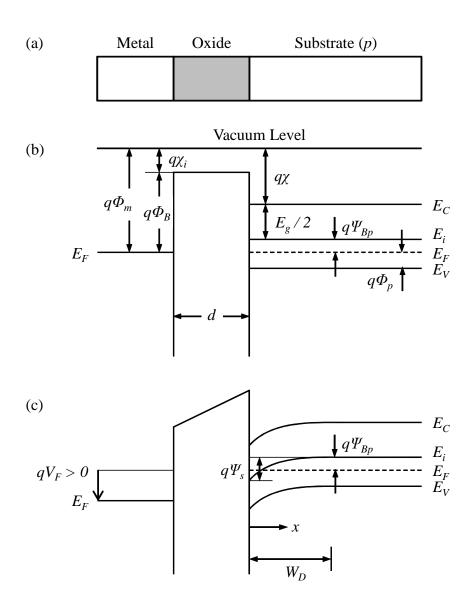

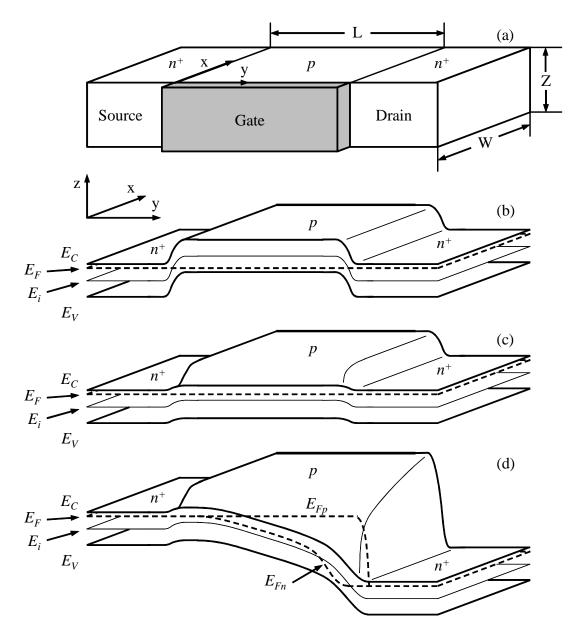

| 4.1  | Ideal MOS-CAP with (a) 2-D structure. (b) Energy band diagram at flat-band. (c)                                           |

|      | Energy band diagram with positive gate-voltage                                                                            |

| 4.2  | 2-D energy band diagram of a MOSFET with (a) Device structure. (b) Band di-                                               |

|      | agram for zero gate bias equilibrium condition ( $V_{DS}=0$ ). (c) Band diagram for                                       |

|      | positive gate bias at equilibrium condition ( $V_{DS} = 0$ ). (d) Band diagram for posi-                                  |

|      | tive gate bias at non-equilibrium ( $V_{DS} > 0$ )                                                                        |

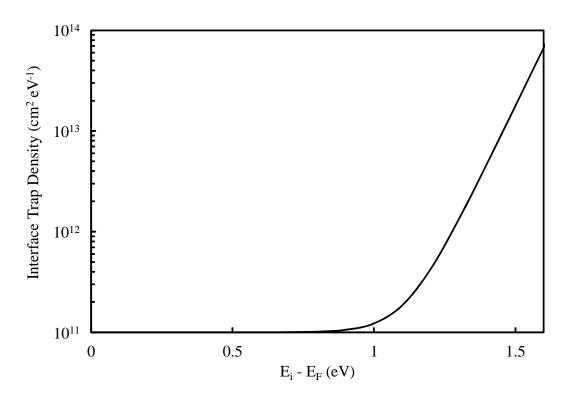

| 4.3  | Interface state density distribution within the band-gap                                                                  |

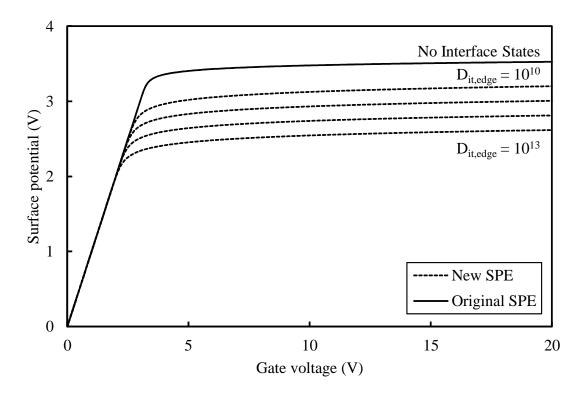

| 4.4  | Calculated surface potential using the original (4.36) and new surface potential                                          |

|      | equations (4.61)                                                                                                          |

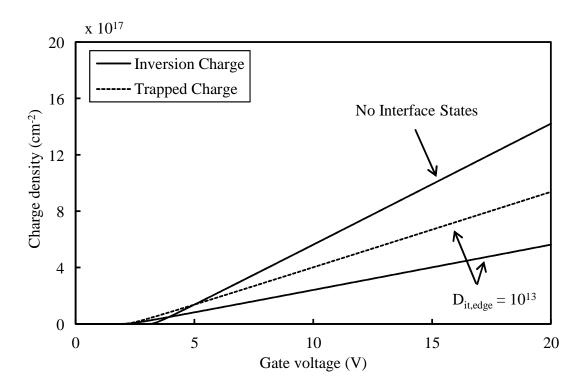

| 4.5  | Calculated inversion charge using the original (4.36) and new surface potential                                           |

|      | equations (4.61)                                                                                                          |

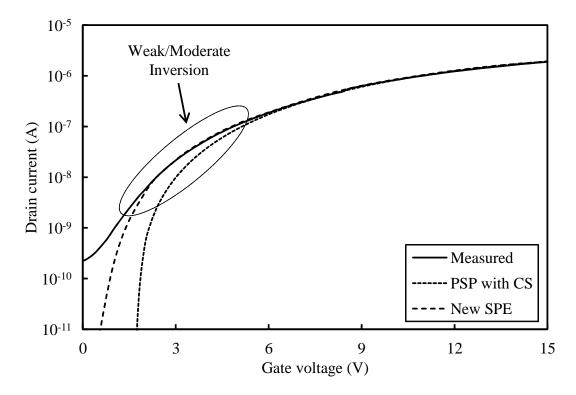

| 4.6  | Measured (solid) and Calculated (dashed) drain currents using the native PSP                                              |

|      | model with $\textbf{CS}$ and the new SPE (4.61)                                                                           |

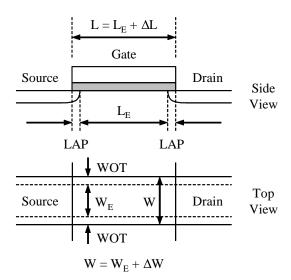

| 4.7  | Layout and physical dimensions in a MOSFET structure                                                                      |

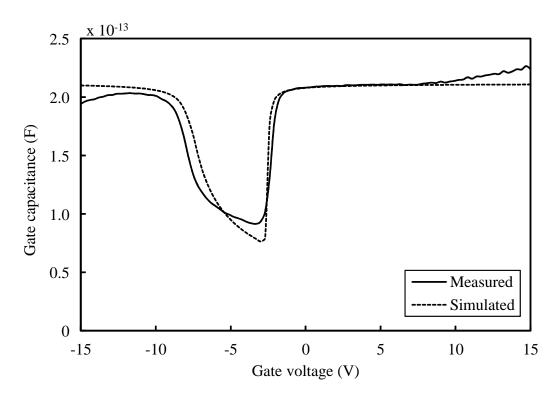

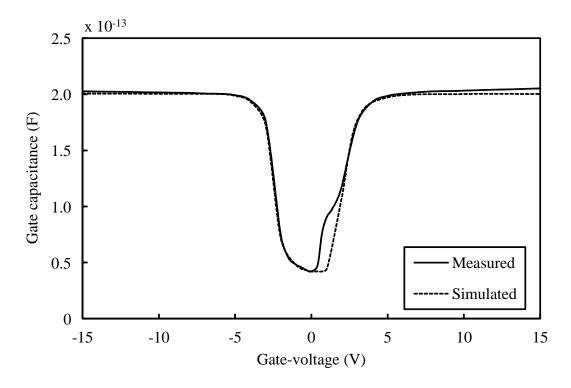

| 4.8  | Measured (solid) and simulated (dash) $C_{GG} - V_G$ characteristics of $32\mu m \times 8\mu m$                           |

|      | depletion MOSFET at 25 °C                                                                                                 |

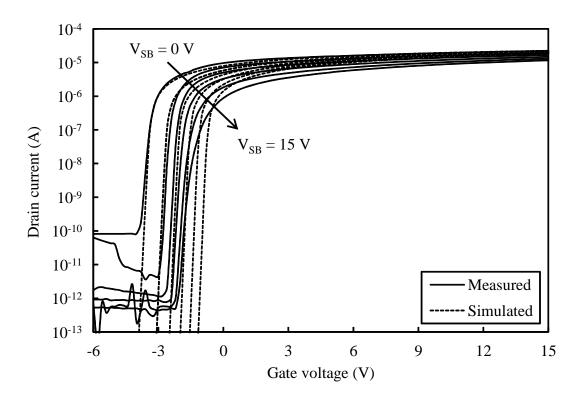

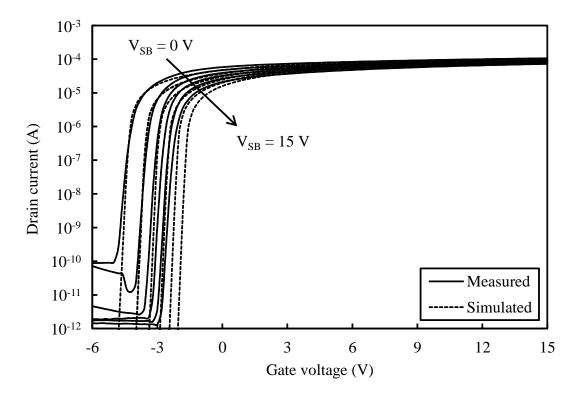

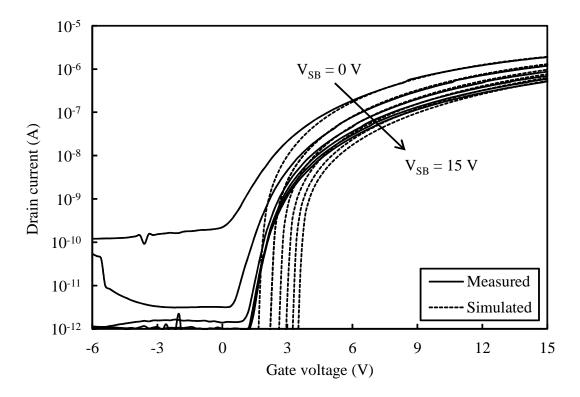

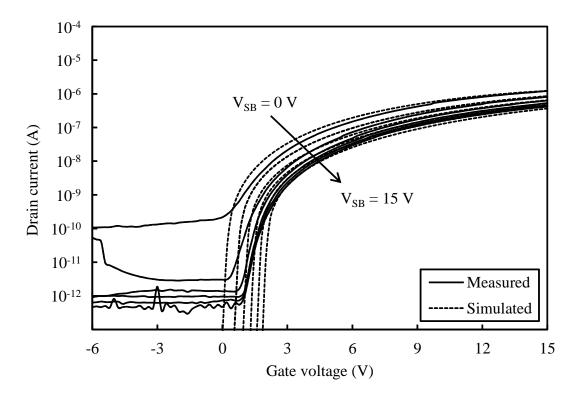

| 4.9  | Measured (solid) and simulated (dash) $I_D - V_{GS}$ characteristics of $32\mu m \times 8\mu m$ de-                       |

|      | pletion MOSFET at 25 °C                                                                                                   |

| 4.10 | Measured (solid) and simulated (dash) $I_D - V_{GS}$ characteristics of $32\mu m \times 2\mu m$ de-                       |

|      | pletion MOSFET at 25 °C                                                                                                   |

|      |                                                                                                                           |

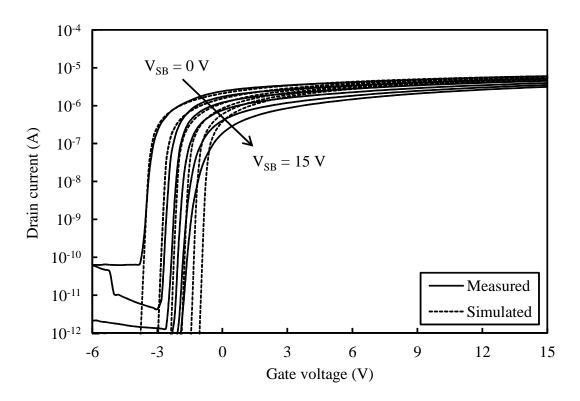

| 4.11  | Measured (solid) and simulated (dash) $I_D - V_{GS}$ characteristics of $8\mu m \times 8\mu m$ de-  |

|-------|-----------------------------------------------------------------------------------------------------|

|       | pletion MOSFET at 25 °C                                                                             |

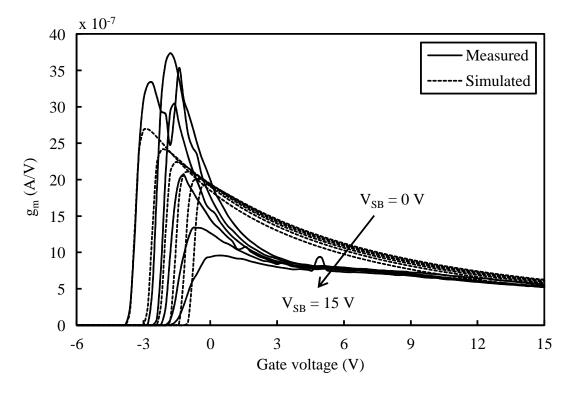

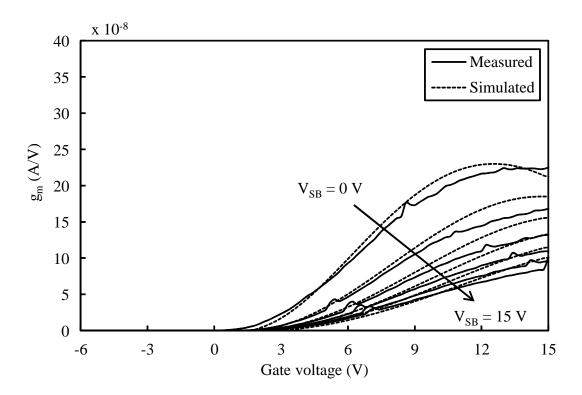

| 4.12  | Measured (solid) and simulated (dash) $g_m - V_{GS}$ characteristics of $32\mu m \times 8\mu m$     |

|       | depletion MOSFET at 25 °C                                                                           |

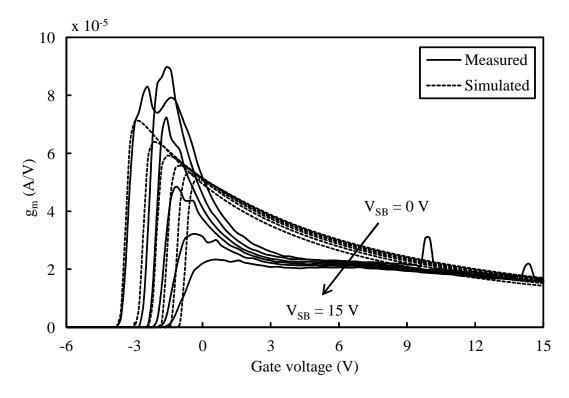

| 4.13  | Measured (solid) and simulated (dash) $g_m - V_{GS}$ characteristics of $32\mu m \times 2\mu m$     |

|       | depletion MOSFET at 25 °C                                                                           |

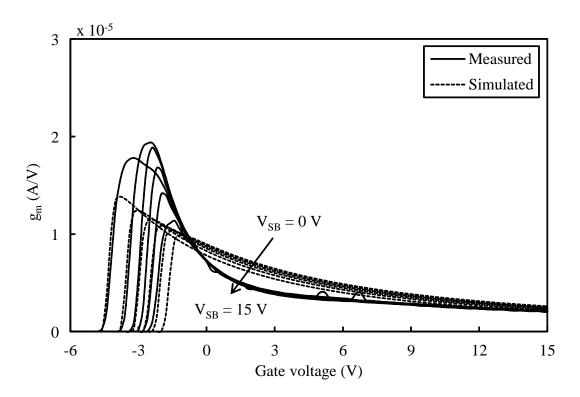

| 4.14  | Measured (solid) and simulated (dash) $g_m - V_{GS}$ characteristics of $8\mu m \times 8\mu m$ de-  |

|       | pletion MOSFET at 25 °C                                                                             |

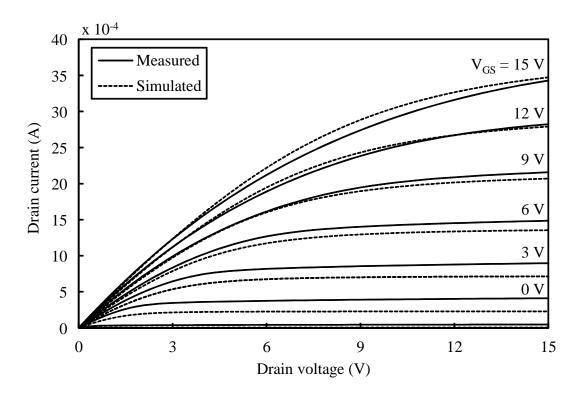

| 4.15  | Measured (solid) and simulated (dash) $I_D - V_{DS}$ characteristics of $32\mu m \times 8\mu m$ de- |

|       | pletion MOSFET at 25 °C                                                                             |

| 4.16  | Measured (solid) and simulated (dash) $I_D - V_{DS}$ characteristics of $32\mu m \times 2\mu m$ de- |

|       | pletion MOSFET at 25 °C                                                                             |

| 4.17  | Measured (solid) and simulated (dash) $I_D - V_{DS}$ characteristics of $8\mu m \times 8\mu m$ de-  |

|       | pletion MOSFET at 25 °C                                                                             |

| 4.18  | Measured (solid) and simulated (dash) $g_{DS} - V_{GS}$ characteristics of $32\mu m \times 8\mu m$  |

|       | depletion MOSFET at 25 °C                                                                           |

| 4.19  | Measured (solid) and simulated (dash) $g_{DS} - V_{GS}$ characteristics of $32\mu m \times 2\mu m$  |

|       | depletion MOSFET at 25 °C                                                                           |

| 4.20  | Measured (solid) and simulated (dash) $g_{DS}-V_{GS}$ characteristics of $8\mu m \times 8\mu m$     |

|       | depletion MOSFET at 25 °C                                                                           |

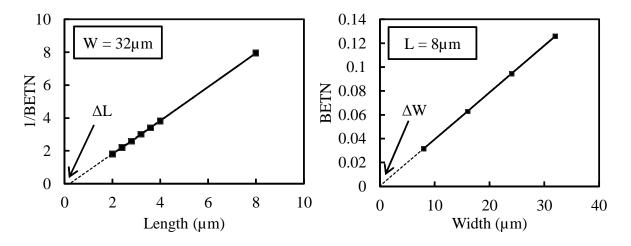

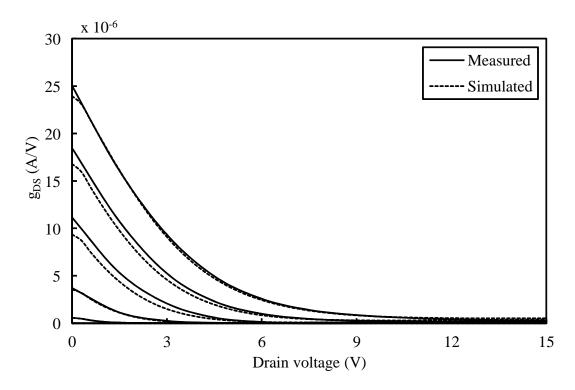

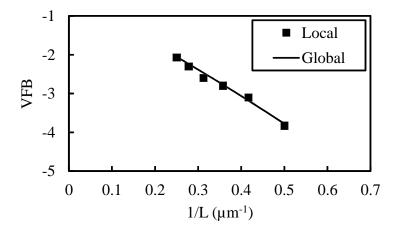

| 4.21  | Extraction of $\Delta L$ and $\Delta W$ from <b>BETN</b>                                            |

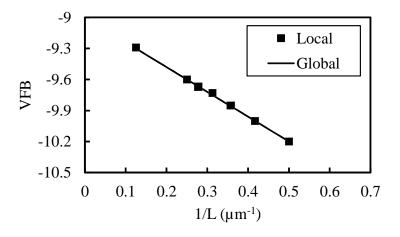

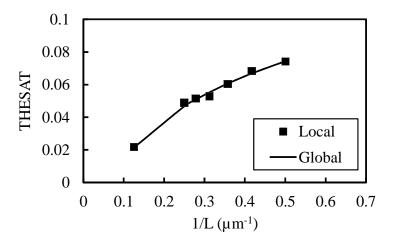

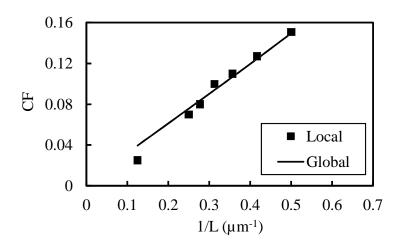

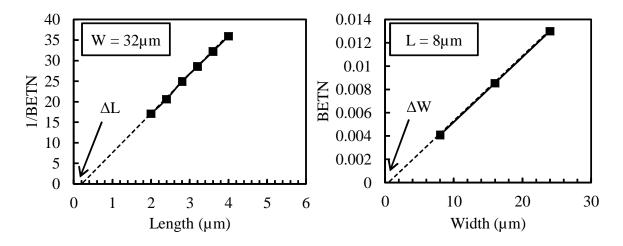

| 4.22  | Variation of <b>VFB</b> with 1/L                                                                    |

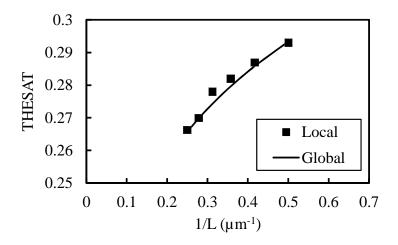

| 4.23  | Variation of <b>THESAT</b> with 1/L                                                                 |

| 4.24  | Variation of <b>CF</b> with 1/L                                                                     |

| 4 0 5 |                                                                                                     |

| 4.25  | Measured (solid) and simulated (dash) $I_D - V_{GS}$ characteristics of $32\mu m \times 8\mu m$ de- |

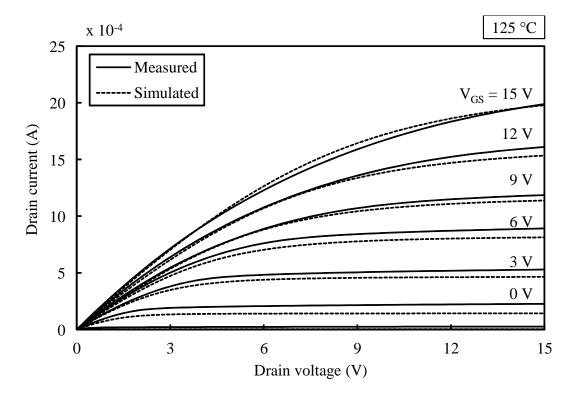

| 4.20 | Measured (solid) and simulated (dash) $I_D - V_{DS}$ characteristics of $32\mu m \times 8\mu m$ de- |     |

|------|-----------------------------------------------------------------------------------------------------|-----|

|      | pletion MOSFET at 125 °C                                                                            | 133 |

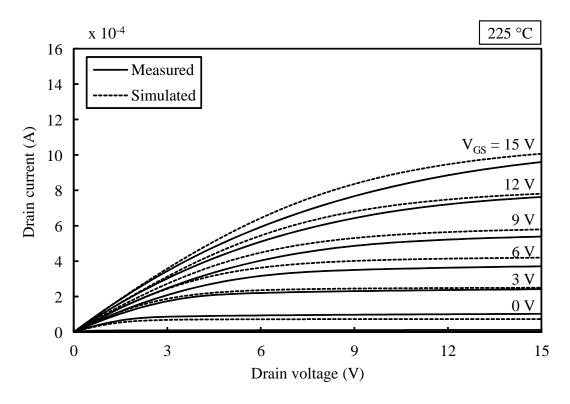

| 4.27 | Measured (solid) and simulated (dash) $I_D - V_{DS}$ characteristics of $32\mu m \times 8\mu m$ de- |     |

|      | pletion MOSFET at 225 °C                                                                            | 134 |

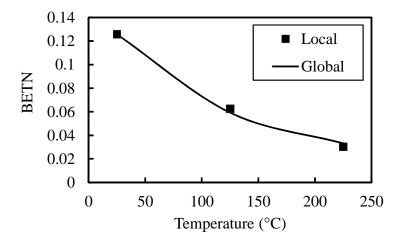

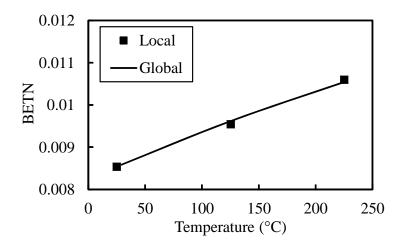

| 4.28 | Temperature scaling of <b>BETN</b> for the $32\mu m \times 8\mu m$ depletion MOSFET                 | 134 |

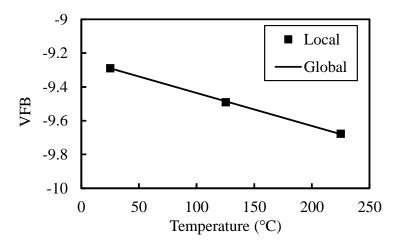

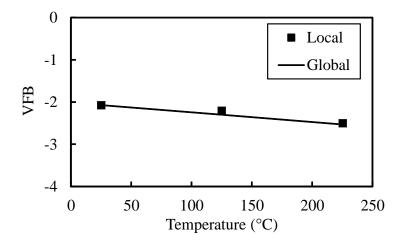

| 4.29 | Temperature scaling of <b>VFB</b> for the $32\mu m \times 8\mu m$ depletion MOSFET                  | 135 |

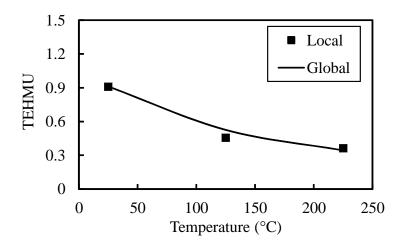

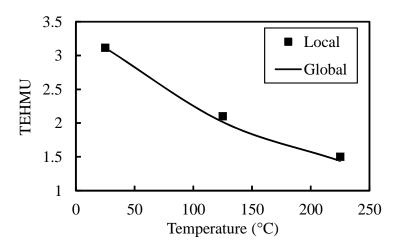

| 4.30 | Temperature scaling of <b>THEMU</b> for the $32\mu m \times 8\mu m$ depletion MOSFET                | 136 |

| 4.31 | Measured (solid) and simulated (dash) $C_{GG} - V_G$ characteristics of $32\mu m \times 8\mu m$     |     |

|      | enhancement MOSFET at 25 °C                                                                         | 137 |

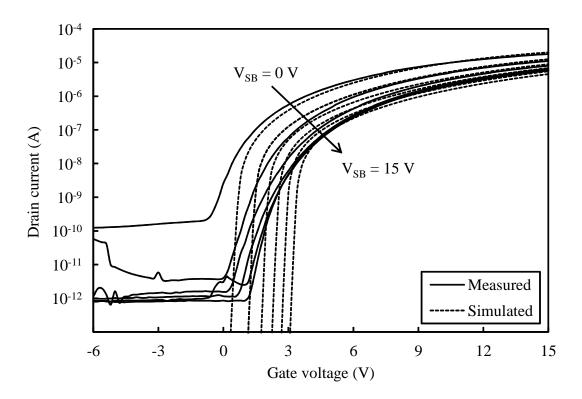

| 4.32 | Measured (solid) and simulated (dash) $I_D - V_{GS}$ characteristics of $16\mu m \times 8\mu m$ en- |     |

|      | hancement MOSFET at 25 °C                                                                           | 138 |

| 4.33 | Measured (solid) and simulated (dash) $I_D - V_{GS}$ characteristics of $32\mu m \times 2\mu m$ en- |     |

|      | hancement MOSFET at 25 °C                                                                           | 139 |

| 4.34 | Measured (solid) and simulated (dash) $I_D - V_{GS}$ characteristics of $8\mu m \times 8\mu m$ en-  |     |

|      | hancement MOSFET at 25 °C                                                                           | 139 |

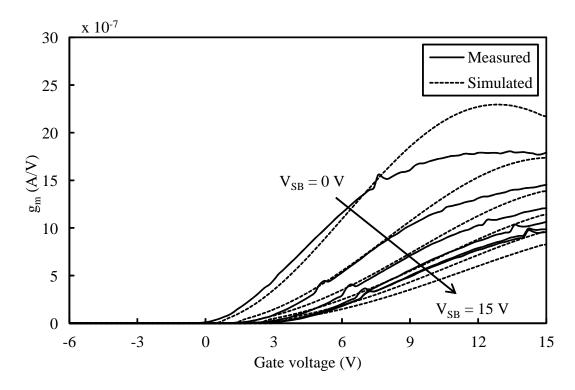

| 4.35 | Measured (solid) and simulated (dash) $g_m - V_{GS}$ characteristics of $16\mu m \times 8\mu m$     |     |

|      | enhancement MOSFET at 25 °C                                                                         | 140 |

| 4.36 | Measured (solid) and simulated (dash) $g_m - V_{GS}$ characteristics of $32\mu m \times 2\mu m$     |     |

|      | enhancement MOSFET at 25 °C                                                                         | 140 |

| 4.37 | Measured (solid) and simulated (dash) $g_m - V_{GS}$ characteristics of $8\mu m \times 8\mu m$ en-  |     |

|      | hancement MOSFET at 25 °C                                                                           | 141 |

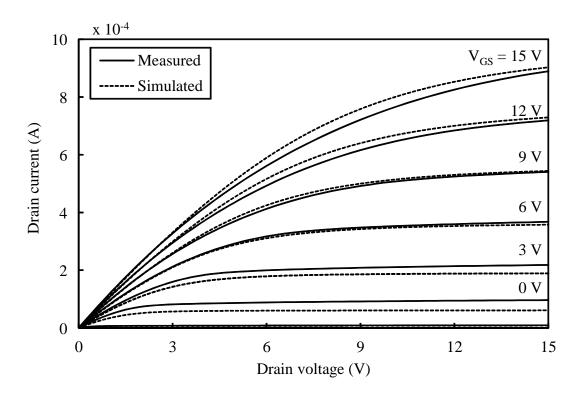

| 4.38 | Measured (solid) and simulated (dash) $I_D - V_{DS}$ characteristics of $16\mu m \times 8\mu m$ en- |     |

|      | hancement MOSFET at 25 °C                                                                           | 142 |

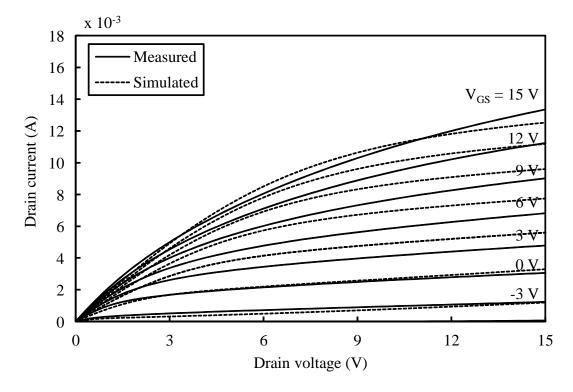

| 4.39 | Measured (solid) and simulated (dash) $I_D - V_{DS}$ characteristics of $32\mu m \times 2\mu m$ en- |     |

|      | hancement MOSFET at 25 °C                                                                           | 143 |

| 4.40 | Measured (solid) and simulated (dash) $I_D - V_{DS}$ characteristics of $8\mu m \times 8\mu m$ en-  |     |

|      | hancement MOSFET at 25 °C                                                                           | 144 |

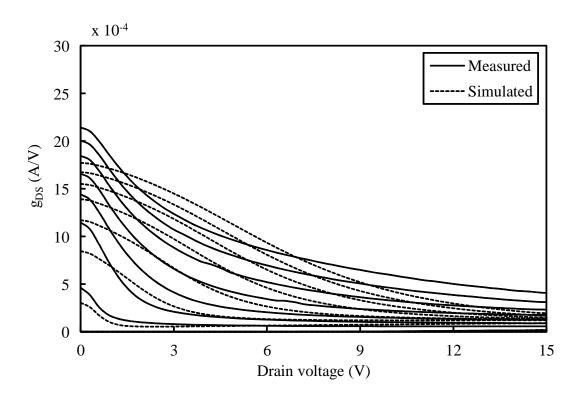

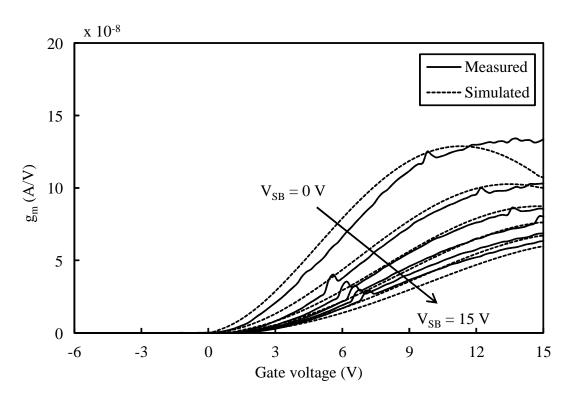

| 4.41 | Measured (solid) and simulated (dash) $g_{DS} - V_{GS}$ characteristics of $16\mu m \times 8\mu m$  |  |

|------|-----------------------------------------------------------------------------------------------------|--|

|      | enhancement MOSFET at 25 °C                                                                         |  |

| 4.42 | Measured (solid) and simulated (dash) $g_{DS}-V_{GS}$ characteristics of $32\mu m \times 2\mu m$    |  |

|      | enhancement MOSFET at 25 °C                                                                         |  |

| 4.43 | Measured (solid) and simulated (dash) $g_{DS}-V_{GS}$ characteristics of $8\mu m \times 8\mu m$     |  |

|      | enhancement MOSFET at 25 °C                                                                         |  |

| 4.44 | Extraction of $\Delta L$ and $\Delta W$ from <b>BETN</b>                                            |  |

| 4.45 | Variation of <b>VFB</b> with 1/L                                                                    |  |

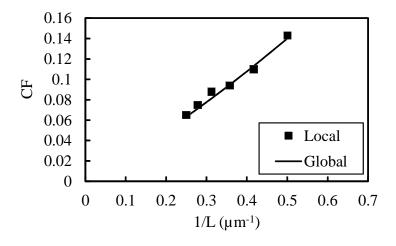

| 4.46 | Variation of <b>THESAT</b> with 1/L                                                                 |  |

| 4.47 | Variation of <b>CF</b> with 1/L                                                                     |  |

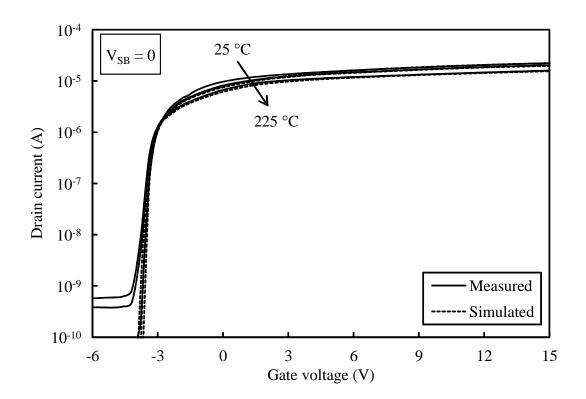

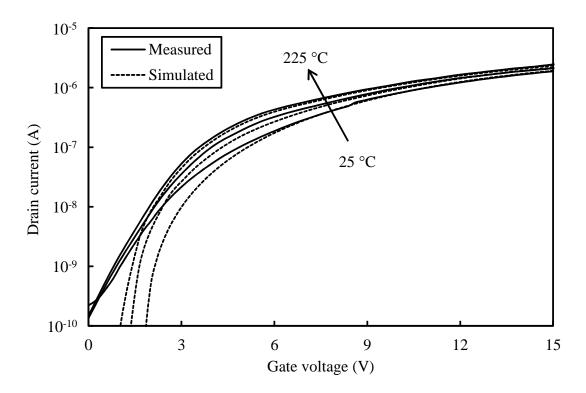

| 4.48 | Measured (solid) and simulated (dash) $I_D - V_{GS}$ characteristics of $16\mu m \times 8\mu m$ en- |  |

|      | hancement MOSFET over temperature                                                                   |  |

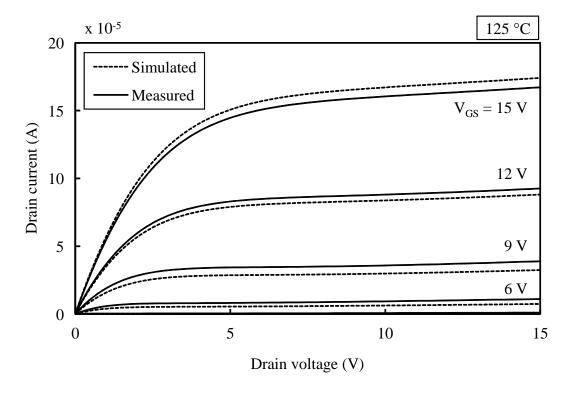

| 4.49 | Measured (solid) and simulated (dash) $I_D - V_{DS}$ characteristics of $16\mu m \times 8\mu m$ en- |  |

|      | hancement MOSFET at 125 °C                                                                          |  |

| 4.50 | Measured (solid) and simulated (dash) $I_D - V_{DS}$ characteristics of $16\mu m \times 8\mu m$ en- |  |

|      | hancement MOSFET at 225 °C                                                                          |  |

| 4.51 | Temperature scaling of <b>BETN</b> for the $16\mu m \times 8\mu m$ enhancement MOSFET 151           |  |

| 4.52 | Temperature scaling of <b>VFB</b> for the $16\mu m \times 8\mu m$ enhancement MOSFET 151            |  |

| 4.53 | Temperature scaling of <b>THEMU</b> for the $16\mu m \times 8\mu m$ enhancement MOSFET 151          |  |

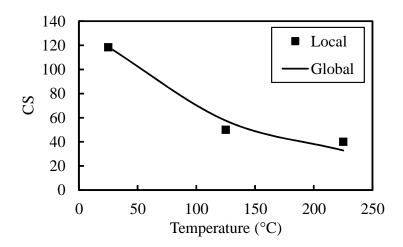

| 4.54 | Temperature scaling of <b>CS</b> for the $16\mu m \times 8\mu m$ enhancement MOSFET 152             |  |

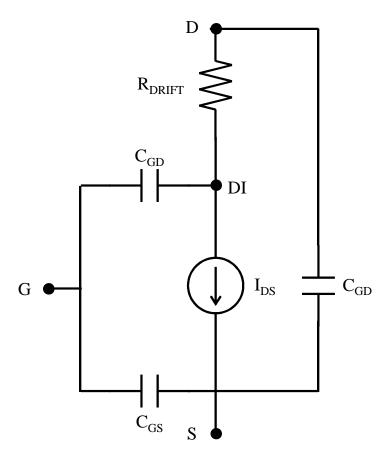

| 5.1  | Topology of the power MOSFET model                                                                  |  |

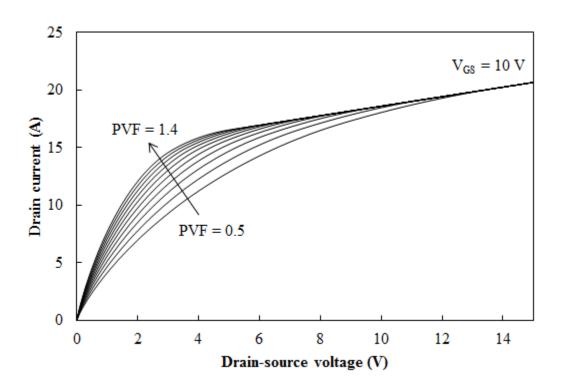

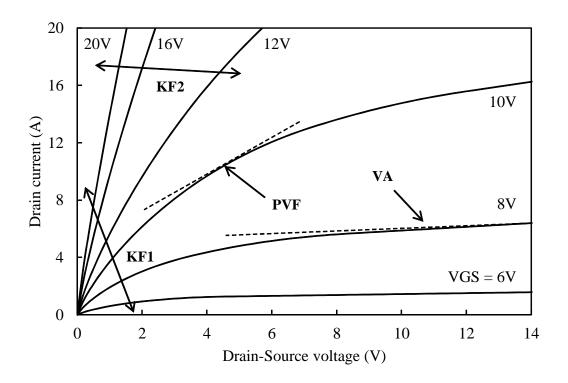

| 5.2  | Controlling transition from linear to saturation using <b>PVF</b>                                   |  |

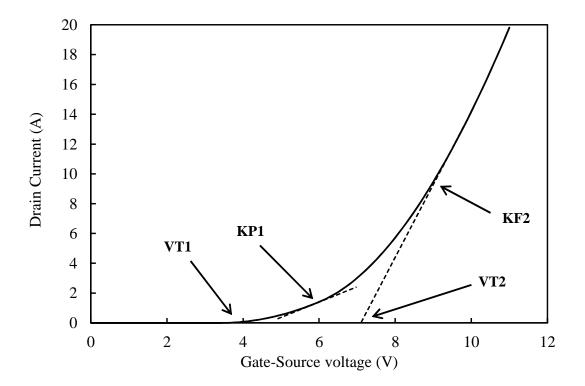

| 5.3  | Extraction of VT1, VT2, KP1 and KP2                                                                 |  |

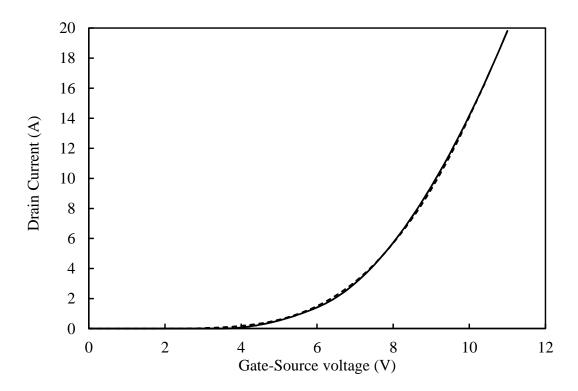

| 5.4  | Measured (dash) and simulated (solid) input characteristics at room temperature 170                 |  |

| 5.5  | Extraction of <b>KF1</b> , <b>KF2</b> , <b>PVF</b> and <b>VA</b>                                    |  |

| 5.6  | Measured (dash) and simulated (solid) output characteristics at room temperature . 172              |  |

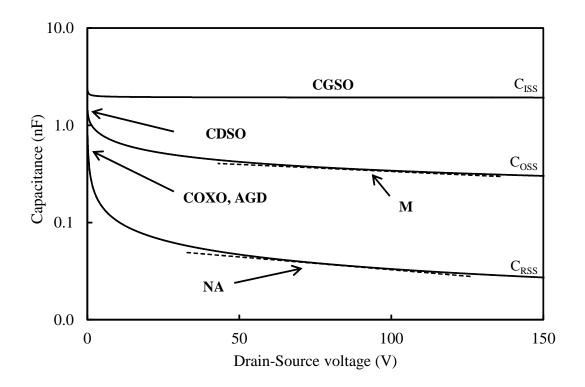

| 5.7  | Extraction of capacitance parameters                                                                |  |

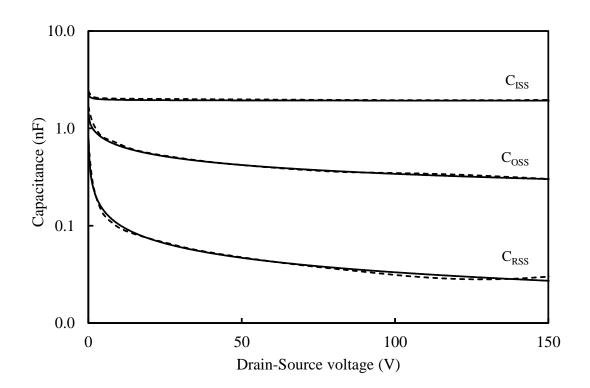

| 5.8  | Measured (dash) and simulated (solid) C-V characteristics at room temperature 17        | 75             |

|------|-----------------------------------------------------------------------------------------|----------------|

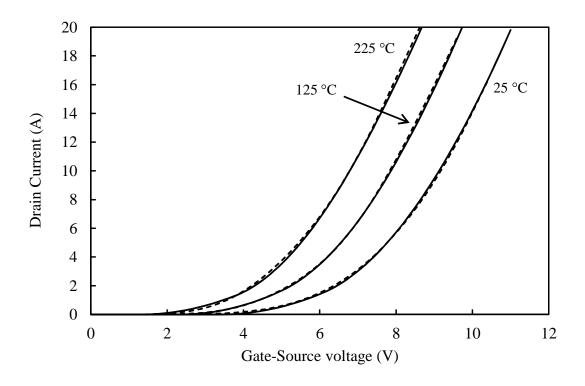

| 5.9  | Measured (dashed) and simulated (solid) input characteristics over temperature 17       | 78             |

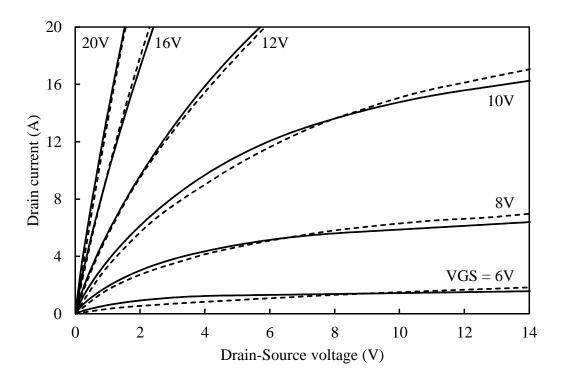

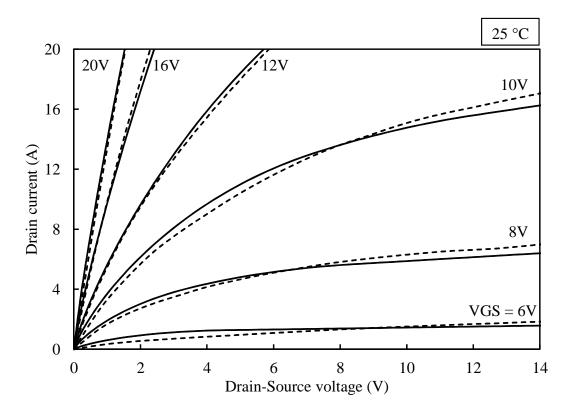

| 5.10 | Measured (dashed) and simulated (solid) output characteristics at 25 $^{\circ}C$ 17     | 79             |

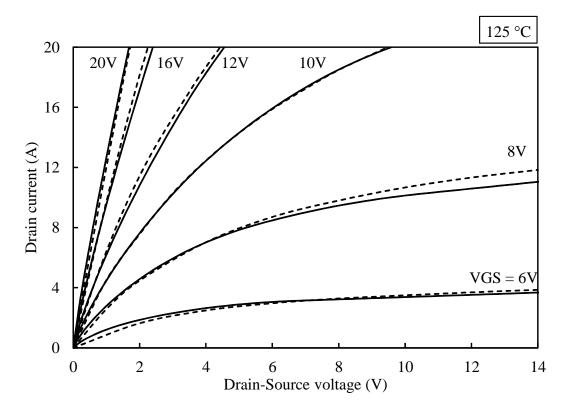

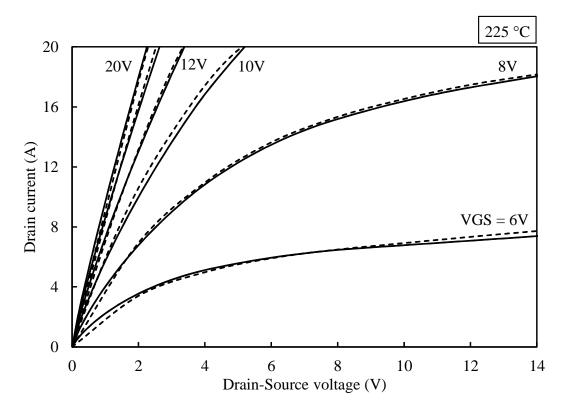

| 5.11 | Measured (dashed) and simulated (solid) output characteristics at 125 $^{\circ}C$ 18    | 30             |

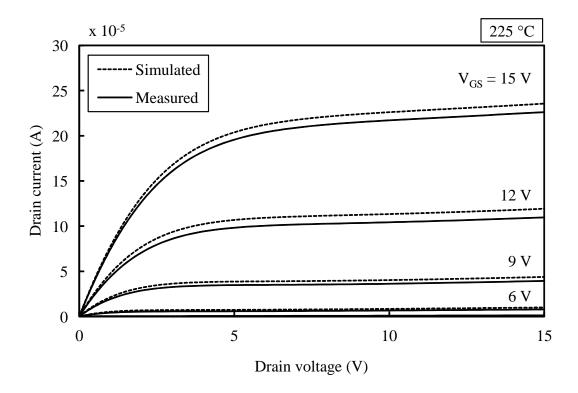

| 5.12 | Measured (dashed) and simulated (solid) output characteristics at 225 $^{\circ}$ C 18   | 31             |

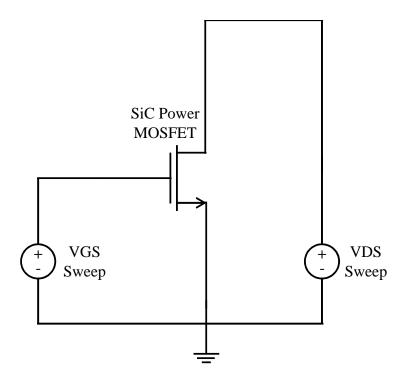

| 5.13 | Schematic for DC characterization                                                       | 32             |

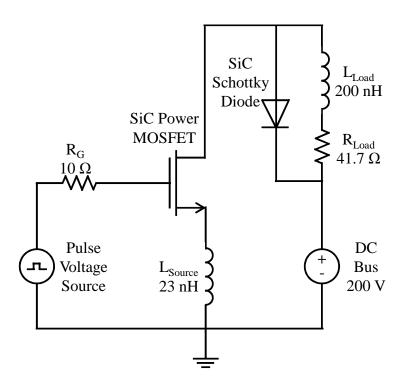

| 5.14 | Schematic for the resistive load switching test                                         | 32             |

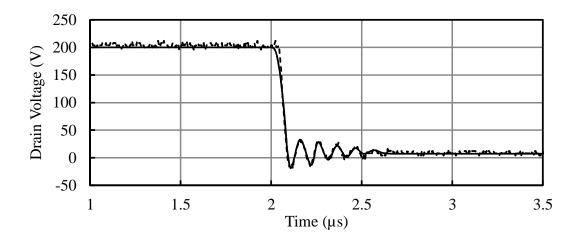

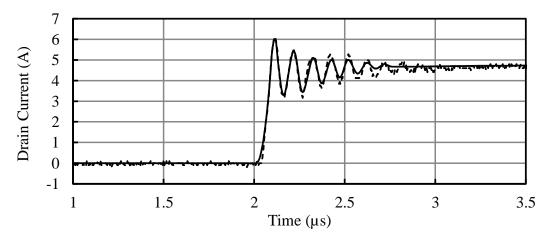

| 5.15 | Measured (dash) and simulated (solid) drain voltage waveform during turn-on 18          | 33             |

| 5.16 | Measured (dash) and simulated (solid) drain current waveform during turn-on 18          | 33             |

| 5.17 | Measured (dash) and simulated (solid) gate voltage waveform during turn-on 18           | 33             |

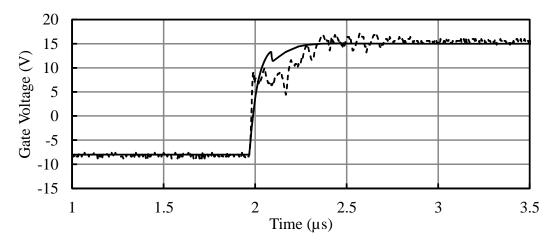

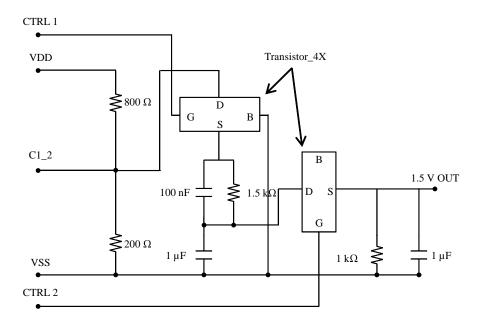

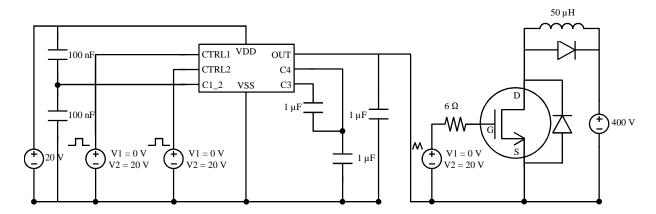

| 6.1  | Schematic of the 1.5 V reference circuit                                                | 36             |

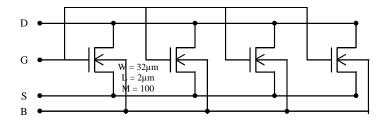

| 6.2  | Schematic of Transistor_4X block                                                        | 37             |

| 6.3  | Schematic of the clamped inductive circuit                                              | 38             |

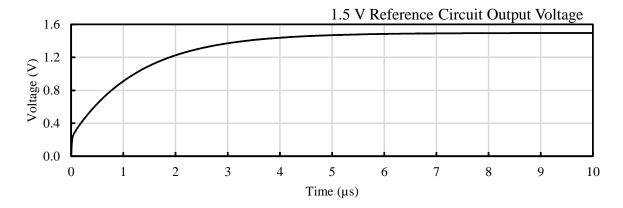

| 6.4  | Simulated output voltage of the 1.5 V reference circuit from turn-on to steady state 18 | 39             |

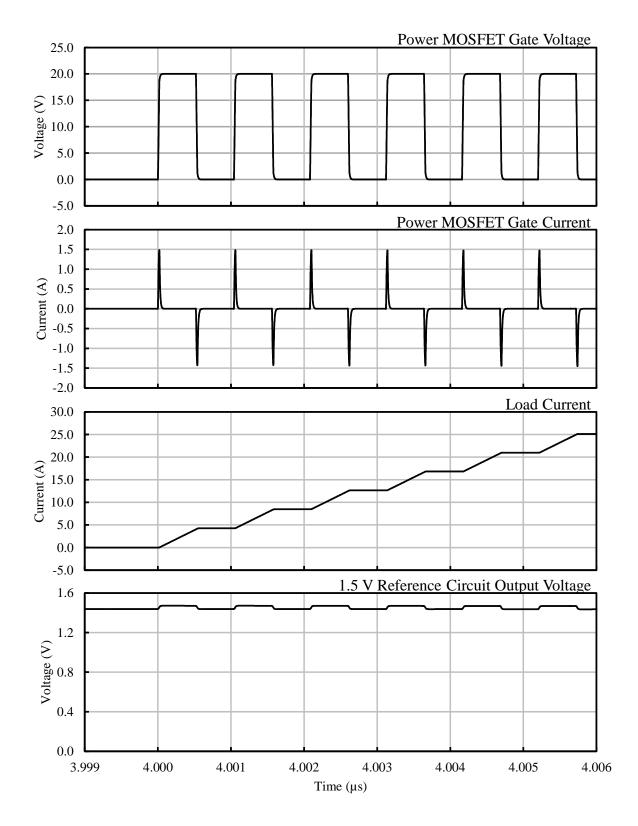

| 6.5  | Simulated waveforms of the clamped inductive circuit                                    | <del>)</del> 0 |

# **List of Tables**

| 2.1 | Electrical and thermal properties of Si and polytypes of SiC            |

|-----|-------------------------------------------------------------------------|

| 4.1 | Operating regions of the MOS-CAP                                        |

| 4.2 | AC parameter extraction                                                 |

| 4.3 | DC wide long channel parameter extraction                               |

| 4.4 | DC wide short channel parameter extraction                              |

| 4.5 | Temperature scaling parameters extracted using long-channel MOSFET 115  |

| 4.6 | Temperature scaling parameters extracted using short-channel MOSFET 116 |

| 4.7 | Extracted parameters of the PSP model                                   |

| 5.1 | Parameters in the Power MOSFET Model                                    |

# Chapter 1

#### Introduction

#### 1.1 Motivation

The fundamental requirements for all electrical systems is the supply of constant regulated power. Without the availability of good quality power, even the most sophisticated systems cannot function. The power supplied by the utility is in the form of Alternating Current (AC) supplied at a low frequency of 50/60 Hz. With the explosive growth in the popularity of digital integrated electronics, the demand for efficient and compact AC to DC converters has surged. Traditionally, power supplies consisted of linear power systems which consisted of a dissipative resistor with a transformer connected to the main power supply, often operating at 50/60 Hz. The low operating frequency meant most of the energy was stored in the reactive core of the transformer, which had to be extremely large and heavy to meet the power requirements. Moreover, due to higher losses in the core, linear power system efficiency was limited in the range of 30%. The large size and low efficiency of linear power systems were two major drawbacks of the linear power system.

With the rapid development of power semiconductor devices, a new breed of power supplies emerged which were known as Switch-Mode Power Supplies (SMPS) [2]. SMPS are typically used to supply a constant DC voltage output with an AC input, usually from the main power supply as shown in Fig. 1.1. The SMPS chops the AC signal coming in from the main power supply at a high frequency, which is then filtered easily into a regulated DC output. The higher frequency of operation enables a tremendous reduction in the size and weight of the power transformer as well as other filtering components. By switching at 100 kHz instead of 60 Hz, the overall system size

can be reduced by more than a factor of eight. This means that the power supply can be made very efficient as well as compact for any given power density. The development of SMPS represents a remarkable improvement over the traditional linear power systems. SMPS are now employed in almost every power system and are crucial to their operation.

Fig. 1.1: General schematic of a Switch-Mode Power Supply

At the heart of any SMPS is a high frequency inverter consisting mainly of power semiconductor devices like Bipolar Junction Transistors (BJTs), power Metal-Oxide Semiconductor Field Effect Transistors (MOSFETs), Junction Field Effect Transistors (JFETs), Insulated Gate Bipolar Transistors (IGBTs) etc. In addition to the power devices, the inverter also consists of rectifiers, inductors, capacitors and a transformer. The arrangement of all the components determines the topology of the inverter and determines the modes of operation, direction of power flow and other important characteristics of the SMPS. The selection of the type and material of the power semi-conductor device inside the inverter plays a pivotal role in the performance of the system.

Power transistors can be broadly classified as bipolar or unipolar devices. Power BJTs have excellent low on-state resistance but are slow at turning off due to their bipolar nature. IGBTs also suffer from the same problem, and have a 'tail-current' while turning off. This tail-effect is due to

the finite time required for the excess carriers in the base region of bipolar transistors to recombine before the transistor can start blocking again. As a result, BJTs and IGBTs are suitable for low frequency, high voltage blocking applications with low-on state conduction losses. Due to their higher turn-off time, their switching losses overtake the conduction losses and the bipolar devices become unsuitable at higher frequencies due to low efficiency.

On the other hand, unipolar devices like power MOSFETs have excellent switching characteristics as there is no recombination effect in these devices during switching. The switching of a power MOSFET involves only the charging and discharging of the internal capacitances. As a result, power MOSFETs are highly suitable for high frequency applications. However, since there is no conductivity modulation effect in the unipolar devices, their on-state resistance rises sharply with increasing blocking voltage. Thus, vertical silicon power MOSFETs are limited to applications requiring blocking voltages less than 200 V. At higher blocking voltages, the on-state resistance of silicon based unipolar devices becomes prohibitive from a conduction loss point of view and bipolar devices dominate due to their excellent on-state characteristics.

The lower voltage blocking limit of power MOSFETs holds true for silicon, which has been the staple material for fabricating power MOSFETs until recently. The rapid development of wide bandgap materials like silicon carbide is changing the playing field for unipolar devices. SiC power MOSFETs have shown excellent switching and conduction performance in the 1 kV to 10 kV blocking voltage applications, an application space traditionally dominated by Si IGBTs [3]. SiC power MOSFETs also offer very high switching frequencies without sacrificing power efficiency owing to their unipolar nature, something that IGBTs simply cannot offer due to their bipolar nature. SiC power MOSFETs are becoming very attractive for power applications for the following reasons:

- They are voltage-controlled devices, which require simple gate-drivers thus reducing the cost and complexity of gate-drivers.

- Being unipolar in nature, their on-state resistance increases with temperature which makes current sharing very straight-forward. As a result, power MOSFETs can be paralleled easily to meet any current ratings needed for the application.

- Their unipolar nature allows them to switch at very high frequencies with low switching losses. Operating at higher frequencies is very attractive from a system design point of view because the size and weight of the transformers and other passive components show a tremendous reduction with increasing frequency. Higher frequencies result in a much smaller overall system.

Despite the fact that SiC power MOSFETs are able to switch at higher frequencies, the overall system's operational frequency is still limited by the presence of parasitic inductances introduced by the long wires connecting the different discrete components in the system. In a multi-layered printed circuit board (PCB), several techniques are employed to minimize the inductances of the wire traces in order to be able to switch at higher frequencies. In order to capitalize on the ability of the SiC power MOSFETs to switch at high frequencies, there need to be ways to minimize external parasitic inductances. Since the interconnect wires contribute significantly to the system parasitic inductances, a novel approach to minimizing parasitic inductances is to integrate the gate-driver onto a single chip as shown in Fig. 1.2.

Integrated circuits shrink dimensions by orders of magnitude thereby reducing parasitic inductances to a minimum. In order to integrate the gate-control circuitry on the power MOSFET die or near it (e.g. a flip-chip approach with two separate dies), a low voltage process in SiC is required

Fig. 1.2: Integration of gate driver with the power MOSFET

to facilitate the development of the gate-driver chip. The low voltage process should be able to support active devices like MOSFETs or JFETs and passive devices like resistors and capacitors, to allow system-level design. Currently, there are no commercial low voltage SiC processes in the market. Thus, there is a strong need to develop such a process in SiC, and characterize it over temperature. In addition, necessary design tools like compact models for the various components in the process must also be developed to enable large-scale integrated circuit design on SiC. With such a process in place, fully integrated power system solutions can be developed which have the power-stage and control stage all on a single die.

Cree Semiconductor Research has developed a new low voltage process in 4H-SiC which can be integrated with their existing 4H-SiC power MOSFET process to build low voltage components on the SiC die. The process supports n-type enhancement and depletion mode MOSFETs as active devices, and resistors and capacitors for passives. Being a new process, it is not well characterized and there exist no compact models to support circuit design for it.

The ultimate objective of this work is to enable the design of a gate driver chip using the low voltage SiC process. The gate driver chip can be integrated with the commercially available SiC

power MOSFET on a single die, minimizing system size and enabling high frequency operation.

The gate driver chip will contain digital, analog and mixed-signal integrated circuits using the new SiC process. The objective can be broken down into the following key components:

- Develop a compact model for the commercially available 1200 V, 20 A SiC power MOSFET,

which is the key component of the power stage

- Design a test-chip to fully characterize the new low voltage SiC process over temperature

- Using the test-chip, identify the desirable substrate qualities like doping profile, growth type (epilayer vs. implant) to enable all n-MOS circuit design

- Characterize the low voltage n-type enhancement and depletion MOSFETs over temperature

- Develop geometry and temperature scaled compact models for the low voltage SiC MOS-FETs

- Validate the compact models by characterization data from devices, and system level simulations

## 1.2 SiC Power MOSFET Modeling

The key component of the power stage is the 1200 V, 20 A SiC power MOSFET. In order to select the best topology for the application, an accurate compact model of the power MOSFET is needed. With the help of the model, designers can simulate and analyze the performance of their designs for each topology. In addition, the model also provides detailed information about power loss estimates, switching speeds, etc. which help the designers in narrowing down their topology

choices. Designers also have the added advantage of being able to select passive component values and layouts prior to any prototype development of their final topologies. Without the aid of compact device models, designers would need to build prototypes for each topology which is a time-consuming and expensive affair. Thus accurate compact models are an indispensable tool for any development process.

The first part of work presented in the dissertation deals with the development of a compact model for SiC power MOSFETs. The requirements for the power MOSFET model are:

- It should have a good description of the underlying equations that govern device behavior

- It should be accurate and predict the device characteristics well against measured data

- It should converge well in large system level simulations

- It should be able to scale over temperature from 25 °C to 225 °C which is the intended application range

- It should have an efficient and clear way of extracting parameters.

In order for the model to be able to replicate and predict the characteristics of a real 1200 V, 20 A SiC power MOSFET from Cree, the devices are first characterized to extract their electrical characteristics for different test setups. The model's parameters are then extracted using the measured device characteristics. Finally, the model with the new extracted parameters is simulated in different configurations in a virtual test-bench and the results of the simulation are compared with measured results using real devices. This process is called parameter extraction and is vital to the adoption and popularity of any compact model. The power MOSFET model also has built-in

temperature scaling equations which scale its parameters to predict the device characteristics over a wide temperature range.

# 1.3 SiC Low Voltage MOSFET Modeling

The proposed methodology to reduce system parasitics to a minimum is by integrating the gatedriver circuitry on the power MOSFET wafer or on a separate die which is bonded very close to the power MOSFET. The gate driver will be developed entirely in SiC using depletion and enhancement type n-MOSFETs. In order to characterize the new 4H-SiC low voltage process from Cree, a test-chip has been developed in the first run with several test components on it to characterize the properties of the process. Like in the case of the power MOSFET model, circuit designers require high accuracy device models to enable the design of the gate-driver circuitry. Low voltage MOSFETs are available in several different geometries (different widths and lengths or W/L) which presents a new dimension of geometry scaling in the Low Voltage MOSFET model (LVMOS model) in addition to temperature scaling. Being a new process, there do not exist any models for low voltage SiC MOSFETs. The PSP low voltage MOSFET Model [1, 4] has been chosen as a starting point for developing LVMOS models for SiC MOSFETs as it has shown excellent performance for sub-micron MOSFET technologies down to 20 nm [5] for Si MOSFETs. The PSP model code has been modified to include material specific constants for SiC like bandgap, mobility and carrier concentrations. A big issue in the modification of an existing model is to ensure the continuity of the model across all regions of operations to avoid any convergence issues. The developed model has been shown to scale over geometry as well as temperature (25 °C to 225 °C) and has been used to simulate numerous circuits for the gate-driver chip.

#### 1.4 Dissertation Structure

The dissertation has been organized as follows:

- Chapter 2: Background The fundamental properties of SiC have been presented with focus

on the changes implemented to the Si PSP model. An introduction to the field of compact

modeling has also been provided

- Chapter 3: SiC Low Voltage Process The development of the test chip for characterizing the new low voltage SiC process has been presented. The results of wide temperature characterization of low voltage MOSFET device arrays have also been shown

- Chapter 4: SiC PSP Model The SiC PSP model has been presented with a brief background and modeling results for the n-MOSFETs in the low volage process

- Chapter 5: Power MOSFET Model The power MOSFET model along with a new datasheet driven parameter extraction strategy has been described

- Chapter 6: Model Simulation Verification Results of validation of the models in systemlevel simulations have been presented

- Chapter 7: Conclusion And Future Work A summary with key contributions of the work and future work has been presented

#### Chapter 2

## **Background**

#### 2.1 SiC Material Properties

Silicon carbide has emerged to be one of the most attractive materials for the development of cutting edge power devices which feature very low on-state losses combined with excellent switching performance. Unipolar devices made in SiC like Schottky diodes, Junction Field Effect Transistors and Metal Oxide Semiconductor FETs have demonstrated orders of magnitude improvement in performance from their Si counterparts, thus pushing unipolar devices into the envelope of medium power density, a regime once only possible to their bipolar counterparts. This chapter discusses some of the important properties of SiC that has enabled such drastic improvements in device performance from Si.

Unipolar devices operate on the principle of conduction of majority carriers between two terminals which is controlled by a signal on the third terminal. Being unipolar in nature, the conduction of current is strongly dependent on the fundamental properties of the semiconductor like mobility, intrinsic carrier concentration etc. SiC exists predominantly in 3 poly-types based on its crystal arrangement: 3C, 4H and 6H. Table 2.1 compares the important electrical and thermal properties between different poly-types of SiC and Si. 4H-SiC is preferred over the other poly-types because it has the highest mobility and bandgap among the three.

<u>Note</u>: For the sake of brevity, the term SiC refers to 4H-SiC in this document unless specified otherwise.

Table 2.1: Electrical and thermal properties of Si and polytypes of SiC

|                                                   | Si   | 3C-SiC | 6H-SiC | 4H-SiC |

|---------------------------------------------------|------|--------|--------|--------|

| Bandgap (eV)                                      | 1.1  | 2.39   | 2.86   | 3.26   |

| Intrinsic Electron Mobility (cm <sup>2</sup> /Vs) | 1400 | 1000   | 600    | 1070   |

| Critical breakdown Field (MV/cm)                  | 0.3  | 2      | 3      | 3      |

| Thermal Conductivity (W/K.cm)                     | 1.5  | 4.9    | 4.9    | 4.9    |

## 2.1.1 Band Gap

The biggest difference between SiC and Si is their bandgap which results in different electrical properties. Si has a bandgap of 1.1 eV whereas 4H-SiC has a bandgap of 3.26 eV. A larger bandgap results in a smaller thermal generation of carriers in the depletion region. Since thermally generated carriers constitute the leakage current in the off-state, SiC has considerably less leakage current for a given blocking voltage as compared to Si. The variation of bandgap of 4H-SiC with temperature is given as [6]

$$E_g = 3.26 - 6.5 \times 10^{-4} \frac{T^2}{(T + 1300)}$$

(2.1)

The intrinsic carrier concentration is determined by the concentration of thermally generated electron-hole pairs at any given temperature, which is a strong function of the bandgap. For example, the intrinsic carrier concentration of Si increases from  $1.01 \times 10^{10}$  cm<sup>-3</sup> at room temperature to  $3.90 \times 10^{15}$  cm<sup>-3</sup> at 600K as shown in Fig. 2.1 [7]. The background doping concentration of the lightly doped regions in the device is in the order of  $10^{15}$  cm<sup>-3</sup>. Thus it can be seen that for Si, the intrinsic carrier concentration overshadows the background doping concentration beyond 600 K, and the region no longer posses the doped properties making the device inoperable. SiC on the other hand has a very low intrinsic carrier concentration, in the order of  $10^{-11}$  cm<sup>-3</sup> at room

temperature, and increases to only about  $10^{11}\,\mathrm{cm}^{-3}$  at 1000 K. This low carrier concentration at elevated temperatures enables SiC devices to retain their doped region properties over a wide range of temperature.

The intrinsic carrier concentration of SiC as a function of temperature can be modeled as

$$n_i \approx 1.7 \times 10^{16} T^{3/2} e^{-(2.08 \times 10^4)/T}$$

(2.2)

Equations (2.1) and (2.2) have been implemented in the SiC PSP model.

Fig. 2.1: Intrinsic carrier concentration of Si and 4H-SiC over temperature

## 2.1.2 Critical Breakdown Electric Field

One of the main advantages offered by SiC is a high value of the critical breakdown electric field.

The breakdown of a material can be understood by the impact ionization process that takes place

in the presence of an electric field inside the material. A charged particle like an electron, under the influence of an electric field will accelerate in the direction opposite to the applied field. As it accelerates through the material, it will eventually collide with a lattice atom and impart some of its energy to the atom. If the imparted energy is higher than the bandgap of the material, an electron inside the atom absorbs the excess energy and jumps to the conduction band, thus creating an electron-hole pair. This electron-hole pair in turn accelerates in the presence of the external electric field, and in similar fashion have a chance to collide with other lattice atoms. The critical breakdown electric field is defined as the maximum electric field that can be sustained across the material before the generation of electron-hole pairs due to impact ionization becomes a destructive process and results in a sudden large increase in current through the material. The impact ionization process can be described by the Chynoweth Law [8, 9] as

$$\alpha = ae^{-b/E} \tag{2.3}$$

The extracted values of a and b as a function of electric field for Si [10, 11, 12] and SiC [13] are shown in Fig. 2.2. It can be seen that the SiC can support 10 times as much electric field as Si for the same ionization coefficient which directly relates to the critical breakdown voltage.

## 2.1.3 Bulk Mobility

The resistivity of the drift region is given by

$$\rho_N = \frac{1}{q\mu_N N_D} \tag{2.4}$$

Fig. 2.2: Impact ionization coefficients of Si and 4H-SiC at room temperature

where  $\mu_N$  is the mobility of electrons in the bulk material and is a function of temperature and doping concentration,  $N_D$ . Bulk electron mobility for SiC at room temperature as a function of doping density is modeled as [14]

$$\mu_{N0}(SiC) = \frac{4.05 \times 10^{13} + 20N_D^{0.61}}{3.55 \times 10^{10} + N_D^{0.61}}$$

(2.5)

As can be seen from (2.5), the bulk electron mobility for SiC decreases with increased doping concentration due to increased Coulombic scattering of electrons by the ionized impurities. The variation of bulk mobility with temperature is given as [14]

$$\mu_N(SiC) = \mu_{N0} \left(\frac{T}{300}\right)^{-2.7}$$

(2.6)

(2.5) and (2.6) can be combined to yield the mobility variation with temperature and doping density as

$$\mu_N(SiC) = \frac{4.05 \times 10^{13} + 20N_D^{0.61}}{3.55 \times 10^{10} + N_D^{0.61}} \left(\frac{T}{300}\right)^{-2.7}$$

(2.7)

The treatment of surface mobility is very important to the behavior of low voltage SiC MOSFETs, and will be treated in a separate section in Chapter 3.

#### 2.2 SiC Power MOSFET

While the concept of the Field Effect Transistor [15] has been around before the development of the Bipolar Junction Transistor [16], FETs could not be made physically before BJTs due to problems associated with making a good quality interface which is fundamental to their operation. The first power MOSFETs in Si was developed in 1976 after issues related to oxide reliability were resolved by the CMOS community [17]. The proposed power MOSFET was based on the double diffused structure also known as the DDMOSFET structure. It was a P-type Si MOSFET featuring a P-drift region and a P-channel. However, due to the low hole mobility in bulk and the inversion channel in both Si and SiC, power MOSFETs are preferred to be N-type featuring a N-drift region. For example, in SiC the bulk mobility of holes is 125 cm<sup>2</sup>/V.s while the bulk mobility of electrons is 950 cm<sup>2</sup>/V.s [18, 19] in the drift region.

The DDMOSFET structure is shown in Fig. 2.3(a). The N<sup>+</sup> source and P<sup>-</sup> base region are formed by implanting boron and phosphorus using the self-aligned gate poly-silicon edge as termination. Due to different diffusion rates for the boron and phosphorus in Si (boron having higher diffusivity), their lateral drive-in lengths varies with the drive-in time and temperature. The n-channel in the Si power MOSFET is defined by the lateral extension of the P<sup>-</sup> base region under

the gate oxide. By accurately controlling the drive-in time, precise sub-micron channel lengths can be obtained without the need for high resolution masks. The elimination of high resolution masks significantly reduces the production cost. The DDMOSFET process proved to be highly successful in the production of Si power MOSFETs with low costs.

However, due to the low diffusivity of dopants in SiC, a different method is used to fabricate SiC power MOSFETs with the same structure as the DDMOSFET. Instead of using the gate oxide termination edge to define the channel, separate implant edges must be use to define the channel length in a SiC power MOSFET. As a result, for sub-micron channel lengths, high resolution lithography is required which increases the cost of production. This type of process is called the double implant process and the structure is known as DiMOSFET or DMOSFET in short. Despite the differences in the fabrication steps, the final structure for the DDMOSFET and the DiMOSFET look similar (with differences in doping profiles), and the structure shown in Fig. 2.3(a) is valid to study the operation of SiC power MOSFETs. The term DMOSFET in this dissertation refers to the final structure, and it is implied that the DiMOSFET process is used to fabricate SiC power MOSFETs.

The on-state resistance of the DMOSFET structure is given as

$$R_{ON} = R_{Contacts} + R_{Channel} + R_{JFET} + R_{Drift}$$

(2.8)

The various regions contributing to the on-state resistances are shown in Fig. 2.4. Since the major limitation to the performance of the power MOSFET is the on-state resistance, different structures and processing methods have been proposed to reduce the on-state resistance for a given blocking voltage. One such novel approach, borrowed from the DRAM industry in the 90s was

Fig. 2.3: Power MOSFET structures

the UMOSFET structure, shown in Fig. 2.3(b). The UMOSFET structure features a trench-gate with a vertical channel formed in the P-region next to the gate oxide. The UMOSFET structure completely eliminates the JFET region present in the DMOSFET structure, and as a result reduces the effective on-state resistance for the same blocking voltage. In the UMOSFET structure, the sharp trench corners in the gate-oxide become a problem when the devices need to be designed to support higher blocking voltages. The electric field developed in the semiconductor material is also present in the gate oxide, and the relative values for the electric field between the semiconductor

and the oxide is given as

$$\frac{E_{Oxide}}{E_{Semi}} = \frac{\varepsilon_{Semi}}{\varepsilon_{Oxide}} \tag{2.9}$$

where  $E_{Oxide}$  is the electric field inside the oxide,  $E_{Semi}$  is the electric field inside the semiconductor,  $\epsilon_{Oxide}$  is the relative permittivity of the oxide and  $\epsilon_{Semi}$  is the relative permittivity of the semiconductor. Thus, (2.9) yields  $E_{Oxide} \approx 3E_{Si}$  for Si and  $E_{Oxide} \approx 2.5E_{SiC}$  for SiC. The critical breakdown electric field for Si is of the order of  $3 \times 10^5$  V/cm, which keeps the value of electric field in the oxide to below its critical breakdown value, which is in the order of  $3 \times 10^6$  V/cm [7]. However, the critical breakdown field for SiC is in the order of  $9 \times 10^6$  V/cm, which exceeds the critical breakdown limit of the gate-oxide causing reliability issues. Since SiC power MOSFETs are designed to support higher blocking voltages than Si, the UMOSFET structure is not a viable option for SiC MOSFETs without special shielding techniques for the gate oxide [20].

Fig. 2.4: Contributions to the on-state resistance in a DMOSFET structure

The first SiC power MOSFET was demonstrated in 1992 [21] which was based on the UMOS-FET structure. It suffered from oxide-breakdown in the trench corners and had low surface in-

version mobility. In order to improve upon the low surface inversion mobility, an accumulation FET (ACCUFET) was proposed in 1997 [22]. The ACCUFET was a vertical 6H-SiC MOSFET structure with a breakdown voltage of 350 V and specific on-state resistance of 18  $\Omega$ .cm<sup>2</sup>. In order to circumvent the problems of oxide breakdown in the UMOSFET structure, the SiC DMOSFET structure was developed and a SiC DMOSFET with breakdown voltage of 760 V was demonstrated [23]. In 2002, a 2.4 kV 4H-SiC DMOSFET was developed [24] which had a specific on-state resistance of 42 Ω.cm<sup>2</sup>. Later in 2002, 3 kV and 5 kV UMOSFETs were demonstrated, which had gate-oxide protection and junction termination extensions [20, 25]. In 2004, a 10 kV power MOSFET was reported in 4H-SiC [26]. Later in 2007, with improvements in SiC manufacturing technology, state-of-the-art 10 kV 4H-SiC DMOSFETs were demonstrated [27] with specific onstate resistance of 111 Ω.cm<sup>2</sup>. In 2009, 1200 V, 60A power MOSFETs were demonstrated with on-state specific on-state resistances as low as 9  $\Omega$ .cm<sup>2</sup> [28]. 1200 V, 20 A SiC power MOSFETs with current rating of 30 A have also been demonstrated with lower specific on-state resistance of 7.1 Ω.cm<sup>2</sup> [29]. However, due to issues with reliable and repeatable manufacturing of SiC power MOSFETs [30], their commercialization has been very slow. To date, only Cree Inc., offers a set of 1200 V SiC power MOSFETs commercially with different current ratings and on-state resistances [31]. The power MOSFET used for the development of the SiC power MOSFET model in this thesis is the commercially available 1200 V, 20 A SiC power MOSFET from Cree (CMF20120D) [32].

### 2.3 Development Challenges

While the merits of using SiC over Si in the design of power MOSFETs is great in theory, there are numerous challenges faced by the industry in the commercialization of SiC technology. One of the challenges is the low channel inversion mobility, which arises due to three main reasons: (a) the wide bandgap of SiC results in much higher electric fields at the surface which increase surface scattering, (b) the large density of interface states at the SiC/SiO<sub>2</sub> interface and (c) high degree of surface roughness due to ion implantation and high temperature activation [33, 34].

By definition, inversion occurs in a MOSFET when the bands at the semiconductor/insulator interface bend lower (in case of a P-substrate) by an amount equal to twice the bulk potential (the difference in the energy level of the Fermi level and intrinsic level in the bulk). As a result, due to the wide bandgap in SiC, the bands have to bend a lot more than in Si which implies much larger electric fields at the interface in SiC (due to increased depletion width). It has been shown that surface roughness mobility varies inversly with the square of electric field which leads to lower surface inversion mobility in SiC [35]. The doping density of the P-substrate also affects the surface mobility indirectly by controlling the electric field developed at the surface. As doping is increased, the electric field on the surface increases which adversly affects the surface mobility. Thus, in order to increase the surface mobility, the substrate doping must be reduced.

The requirement of the reduction of substrate doping to improve surface mobility contradicts the requirement of a larger substrate doping for obtaining a reasonable value of the threshold voltage over temperature. The threshold voltage of a MOSFET is given as

$$V_T = V_{FB} + \frac{\sqrt{2q\varepsilon_{SiC}N_A\Phi_s}}{C_0} + \Phi_s \tag{2.10}$$

$$V_{FB} = \Phi_{ms} - \frac{Q_i}{C_0} \tag{2.11}$$

$$C_0 = \frac{\varepsilon_{SiC}}{T_0} \tag{2.12}$$

where  $\Phi_{ms}$  is the work-function between the metal and semiconductor,  $Q_i$  is the trapped charge in the oxide,  $\Phi_s$  is the surface potential at inversion,  $N_A$  is the doping density of the substrate and  $T_0$  is the thickness of the oxide. The threshold voltage of the MOSFET is decreased due to the presence of a large number of trapped positive charges in the oxide (of the order of  $10^{12}$  cm<sup>-2</sup>, which contribute to the term  $Q_i$  in (2.11). As temperature increases, the threshold voltage decreases. In order to ensure reliable operation over high temperature, it is attractive to have a high enough value of threshold voltage so the the drain current stays below  $1\mu$ A in the off-state even at high temperatures. However, the threshold voltage should not be so large that it places a burden on the gate-driver to switch the device from fully-on to fully-off states at high frequencies. Increasing the doping of the substrate also allows reducing the thickness of the drift region, which reduces the on-state resistance of the power MOSFET. In SiC MOSFETs, it is desirable to reduce the number of positive fixed charges in the oxide so that the doping requirements of the substrate become more relaxed. Striking the balance in the substrate doping to achieve desirable surface mobility and threshold voltage is a challenging task.

Another challenge arises due to the the thinner drift regions in SiC DMOSFETs. In order to reduce the on-state resistances, the drift layer in SiC DMOSFETs is doped 100 times more than in Si, which allows the reduction of drift layer thickness by an factor of 10. The input capacitance of the DMOSFET consists of the overlap capacitance between the gate and the source-metallization  $C_{GS}$ , which can be treated as constant for the sake of argument and the capacitance between the gate

and the drain in the form of a series combination of the gate oxide capacitance  $C_{ox}$  and the depletion layer capacitance  $C_{GDj}$  as shown in Fig. 2.5. The depletion layer capacitance is simply calculated as the parallel plate capacitance between the interface and the edge of the depletion width which varies with the doping density. As the doping density increases, the depletion width reduces which in turn increases the value of the depletion capacitance. Since the depletion capacitance is much smaller than the oxide capacitance when the device is in the blocking state, the effective input capacitance is determined by the value of the depletion capacitance which increases sharply with increasing doping density. This places harsh dv/dt requirements on the DMOSFET as well as the gate driver to switch the device at higher frequencies.

Fig. 2.5: Internal capacitances in the power MOSFET

Finally, the SiC/SiO<sub>2</sub> interface also contains a large density of interface traps [36]. The presence of interface traps has a two-fold effect: (a) when gate voltage is applied, some of the electrons are trapped in the interface states which reduces the electrons available for conduction and (b) the trapped electrons act as scattering centers which increasing Coulumbic scattering effects on the surface. Several improvements for the oxidation of the SiC interface have been proposed which

include Metal Enhanced Oxidation (MEO) and annealing in the presence of NO [37] which aim at reducing the density of interface states at the SiC/SiO<sub>2</sub> interface. Capped activation of anneals with graphitized resists have shown improvement in the roughness of the interface, which would help in improving the overall surface inversion mobility [34]. Further improvements in the processing of the interface would help in the commercialization of a larger array of SiC power MOSFETs.

#### 2.4 Device Modeling

SiC power MOSFETs have seen rapid development in the last decade. While structurally similar to the Si power MOSFET, there are numerous differences in the material properties, device dimensions and the behavior of the internal regions of the device that warrant the development of models specifically for SiC power MOSFETs. Device models can be broadly classified as

- · Numerical models

- Compact models

- Table look-up models

## 2.4.1 Numerical Models

Numerical device models solve the fundamental drift-diffusion equations and current continuity equations in the various regions of the device to yield information about the device characteristics. The inputs to numerical models are device structure, mesh definition, doping profiles, material parameters and other processing information relevant to the device itself. There are several commercial device simulators available like TCAD Sentaurus and Medici from Synopsys [38] and Atlas from Silvaco [39] that provide various tools for each step in building a numerical model of

the device. For example, the TCAD Sentaurus Tool has various tools built in like Sentaurus Process to emulate processing steps, Sentaurus Mesh to create and refine meshes on any structure, Sentaurus Structure Editor that lets the user edit and create device structures using a GUI and Sentaurus Device that simulates the device structures built in the other tools.

There are numerous advantages of using numerical models. Firstly, once calibrated to a certain process, numerical models can reasonably predict device characteristics of structures that have not been characterized or are entirely different devices, as long as all the underlying physical phenomena have been captured and provided to the device simulator. For example, once the mobility of the material being simulated has been properly characterized under various conditions, the device simulator will be able to predict the current through the material of arbitrary geometry under the presence of an electric field. However, unobserved phenomena will not be captured by the numerical simulator and as a result, the quality of material characterization and device simulator equations heavily determines the outcome of numerical models. Since device simulators solve 2 dimensional differential equations at a large number of mesh points, the simulations are often very time consuming. The large number of mesh points also places the burden of properly defining the mesh density in the regions of interest in the device to ensure proper convergence, reasonable simulation time and high resolution of data in the regions of interest. While numerical models are extremely useful in understanding a process and designing and optimizing devices in it, they are computationally intensive. As a result, they are rarely used in circuit simulators to design circuits.

#### 2.4.2 Compact Models

While designing circuits, the circuit designers are not interested in obtaining information about the concentration of electrons and holes in the various regions of the device, nor are they interested

in the built-in electric fields and potential distribution inside the device. They are more interested in accurate prediction of device performance, proper convergence across various bias conditions and quick simulation times of their circuits. Compact models bridge the gap between the requirements of the circuit designer and the plethora of information provided by numerical models. Compact models are generally built for specific device families and are valid for a range of device sizes. Compact models are generally built in different Hardware Description Languages (HDL) like Verilog-A, VHDL and MAST. Different simulators support different HDLs. For example, the HSPICE simulator from Synopsys and the Spectre simulator from Cadence support Verilog-A, while MAST is a proprietary language supported by the Saber simulator from Synopsys. Verilog-A is generally supported by a large number of simulators, and as a result, the compact models developed in this dissertation have been developed in Verilog-A. There are various compact models available in the public domain for different devices like:

- MOSFET BSIM1-BSIM4 from University of California, Berkeley [40], PSP and MOS

Model 11 from NXP Semiconductor [1], HiSIM from Hiroshima University [41] and SPICE

Level 1-17 from different vendors

- **BJT** Mextram from NXP Semiconductor [42], VBIC [43] and Gummel Poon [44]

- Power MOSFET UA model [45], Saber model, McNutt model [46]

- **IGBT** Hefner's IGBT model [47]

In a compact model, the device structure is broken down into various nodes, some of which are external and others are internal. The external nodes are available to the circuit simulator where the various biases are applied to the device. For example, a MOSFET has gate, drain, source and

substrate nodes as external nodes. The internal nodes are defined in order to divide the device structure into different regions based on the physics of operation.

After the structure of the model is defined, equations are formulated for each branch of the device based on actual device physics. The detail in the description of the equations determines the complexity and number of factors accounted by the model. The equations inside a compact model have several model parameters in them, that allow the tailoring of the model to different device characteristics. For example, a simple resistor model has a parameter R, that determines the resistance of the resistor. More advanced models may also contain other parameters like the temperature co-efficient, stress inside the resistor etc. Compact models are often identified by levels. A level 1 model is a very simplified model of a device, and is useful to assist in rough calculations of a circuit. The advantages of a level 1 model are that they are very easy to tailor to a particular device (albeit the fitting of the model to the device may not be very accurate), are fast to simulate and thus are ideal to be used in logic circuits and in general provide a very quick estimate on the performance of a device in a circuit. However, in order to design detailed circuits, more complex models are used which account for several second order effects in the device. A good compact model generally possesses the following qualities:

• Level of detail – Since every compact model is designed for an intended application space, the needs of the application space should be sufficiently met by the compact model. For example, compact models for digital applications need to be very fast and may skim on the degree of effects modeled as long as some basic criteria of device characteristics are met. This is because the number of devices used in digital circuits is very large, and models need to be simple enough to simulate in reasonable time. On the other hand, analog applications require a lot more detail