# University of Arkansas, Fayetteville ScholarWorks@UARK

Theses and Dissertations

5-2012

# Silicon Germanium SRAM and ROM Designs for Wide Temperature Range Space Applications

Matthew Barlow University of Arkansas, Fayetteville

Follow this and additional works at: http://scholarworks.uark.edu/etd

Part of the VLSI and Circuits, Embedded and Hardware Systems Commons

#### Recommended Citation

Barlow, Matthew, "Silicon Germanium SRAM and ROM Designs for Wide Temperature Range Space Applications" (2012). Theses and Dissertations. 362.

http://scholarworks.uark.edu/etd/362

This Thesis is brought to you for free and open access by ScholarWorks@UARK. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of ScholarWorks@UARK. For more information, please contact scholar@uark.edu, ccmiddle@uark.edu.

| SILICON GERMANIUM SRAM AND ROM DESIGNS FOR WIDE TEMPERATURE RANGE SPACE APPLICATIONS                     |                        |                                           |                         |         |

|----------------------------------------------------------------------------------------------------------|------------------------|-------------------------------------------|-------------------------|---------|

| SILICON GERMANIUM SRAM AND ROM DESIGNS FOR WIDE TEMPERATURE RANGE SPACE APPLICATIONS                     |                        |                                           |                         |         |

| SILICON GERMANIUM SRAM AND ROM DESIGNS FOR WIDE TEMPERATURE RANGE SPACE APPLICATIONS                     |                        |                                           |                         |         |

| SILICON GERMANIUM SRAM AND ROM DESIGNS FOR WIDE TEMPERATURE RANGE SPACE APPLICATIONS  SPACE APPLICATIONS |                        |                                           |                         |         |

|                                                                                                          | SILICON GERMANIUM SRAM | AND ROM DESIGNS FOI<br>SPACE APPLICATIONS | R WIDE TEMPERATURI<br>S | E RANGE |

|                                                                                                          |                        |                                           |                         |         |

|                                                                                                          |                        |                                           |                         |         |

|                                                                                                          |                        |                                           |                         |         |

|                                                                                                          |                        |                                           |                         |         |

|                                                                                                          |                        |                                           |                         |         |

|                                                                                                          |                        |                                           |                         |         |

# SILICON GERMANIUM SRAM AND ROM DESIGNS FOR WIDE TEMPERATURE RANGE SPACE APPLICATIONS

A thesis submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

Ву

Matthew Barlow University of Arkansas Bachelor of Science in Electrical Engineering, 2007

> May 2012 University of Arkansas

#### **Abstract**

This thesis presents a design flow from specifications and feature requirements to embeddable blocks of SRAM and ROM designs from 64 bytes to 1 kilobyte that are suitable for lunar environments. The design uses the IBM SiGe 5AM BiCMOS 0.5 micron process for a synchronous memory system capable of operating at a clock frequency of 25 MHz. Radiation mitigation techniques are discussed and implemented to harden the design against total ionizing dose (TID), single-event upset (SEU), and single-event latch-up (SEL). The memory arrays are also designed to operate over the wide temperature range of -180 °C to 125 °C. Design, simulation, and physi cal layout are evaluated throughout the process. Modeling of the memory arrays for static timing analysis (STA) is done to allow easy integration of the design into a typical RTL design flow. System simulation data is incorporated into block-level simulations to validate the memory timing models. Hardware testing over five iterations of the memory array designs demonstrates the functionality of the design as well as validates the design specifications.

| Thesis Director:     |

|----------------------|

| Dr. H. Alan Mantooth |

| Thesis Committee:    |

| Dr. Jia Di           |

| Dr. Scott Smith      |

This thesis is approved for recommendation to the Graduate Council.

# **Thesis Duplication Release**

| I hereby authori research and/or | ze the University of Arkansas Libraries to duplicate this thesis when needed for scholarship. |

|----------------------------------|-----------------------------------------------------------------------------------------------|

| Agreed _                         | Matthew Barlow                                                                                |

| Refused _                        | Matthew Barlow                                                                                |

#### Acknowledgements

The author is grateful for the guidance, support, and dedication of the thesis committee, consisting of Dr. H. Alan Mantooth, Dr. Jia Di, and Dr. Scott Smith. The work described here is a part of the Silicon-Germanium Integrated Electronics for Extreme Environments project. The experience shared by Richard Berger, Adam Bumgarner, and Jason Ross of helped this work get started on the right track and maintain momentum. Additionally, the author would like to thank Guoyuan Fu, Brent Hollosi, Chris Lee, and Aaron Arthurs for their parts helping out with the design, simulation, and testing involved with the entire project

## **Dedication**

| I would like to d | ledicate this | thesis to | my | wife | Kathryn, | my | daughter | Abigail, | and | my | son | Ethan. |

|-------------------|---------------|-----------|----|------|----------|----|----------|----------|-----|----|-----|--------|

|-------------------|---------------|-----------|----|------|----------|----|----------|----------|-----|----|-----|--------|

# **Table of Contents**

| Chapter 1 – Introduction and Overview                                                    |      |

|------------------------------------------------------------------------------------------|------|

| 1.1 Digital Data Storage for Microcontroller Applications                                |      |

| 1.2 Project Overview                                                                     |      |

| 1.3 Silicon Germanium Process                                                            |      |

| Chapter 2 – Background on Memory Design                                                  |      |

| 2.1 Latch                                                                                |      |

| 2.2 Flip-Flops                                                                           |      |

| 2.3 Memory Arrays                                                                        |      |

| 2.3.1 Dynamic Random Access Memory                                                       |      |

| 2.3.2 Static Random Access Memory                                                        |      |

| 2.3.3 Read Only Memory                                                                   |      |

| Chapter 3 – Memory Array Design                                                          |      |

| 3.1 General Design Techniques                                                            |      |

| 3.2 Introduction to Simulations                                                          |      |

| 3.3 Bit-Cell Design                                                                      |      |

| 3.3.1 ROM Cell Design                                                                    |      |

| 3.4 Bit-Cell Simulations                                                                 |      |

| 3.5 SRAM Bit Layout                                                                      |      |

| 3.6 ROM Bit Layout                                                                       |      |

| 3.7 Array Layout                                                                         |      |

| 3.8 Row Select                                                                           |      |

| 3.8.1 Row Access Simulation                                                              |      |

| 3.8.2 Row Access Layout                                                                  | . 30 |

| 3.9 Column Access                                                                        |      |

| 3.9.1 Column Multiplexing                                                                |      |

| 3.9.2 Pre-charge                                                                         |      |

| 3.9.3 Write Drive                                                                        |      |

| 3.9.4 Sense Amplifier                                                                    |      |

| 3.9.5 Layout of BL Access                                                                |      |

| 3.10 Control Logic                                                                       |      |

| 3.10.1 Hamming ECC                                                                       |      |

| Chapter 4 – System Integration and Simulation                                            |      |

| 4.1 Memory Array Characterization                                                        | . 54 |

| 4.2 Simulating SRAM Using Vectors from ModelSim                                          |      |

| Chapter 5 – Hardware Testing                                                             |      |

| 5.1 CRYO3 Setup                                                                          |      |

| 5.1.1 Room Temperature Setup                                                             |      |

| 5.1.2 Cryogenic Setup                                                                    |      |

| 5.2 CRYO4 Testing                                                                        | .64  |

| 5.2.1 CRYO4 Logic Alteration through Focused Ion Beam Micromachining                     |      |

| 5.2.2 Brookhaven Radiation Latch-up Testing                                              |      |

| 5.3 CRYO5 and CRYO5A Testing                                                             |      |

| 5.4 RDC3 Testing                                                                         |      |

| Chapter 7 - Summary and Conclusion                                                       |      |

| Chapter 7 – Future Work                                                                  |      |

| 7.1 Layout Integration of ECC into Layout Macro                                          |      |

| 7.2 Explore Different Bit-Cell Transistor Sizes                                          |      |

|                                                                                          |      |

| 7.4 Improve Speed of Designs                                                             |      |

| Appendix B – Row Mask Generation Code  Appendix B – Memory Array Control Logic Equations |      |

| Appendix C – Error Correction Logic VHDL                                                 | 82   |

| Appendix D – Liberty Models                                                              |      |

| Appendix - Livery modele                                                                 |      |

# List of Figures

| Fig. | 2.1 - Latch with enable                                                                           | 5    |

|------|---------------------------------------------------------------------------------------------------|------|

|      | 2.2 - Master-slave flip-flop                                                                      |      |

|      | 2.3 - DRAM bit-cell                                                                               |      |

| Fig. | 2.4 - Six transistor CMOS SRAM cell (left) and four transistor resistive NMOS SRAM cell (right)   | 8    |

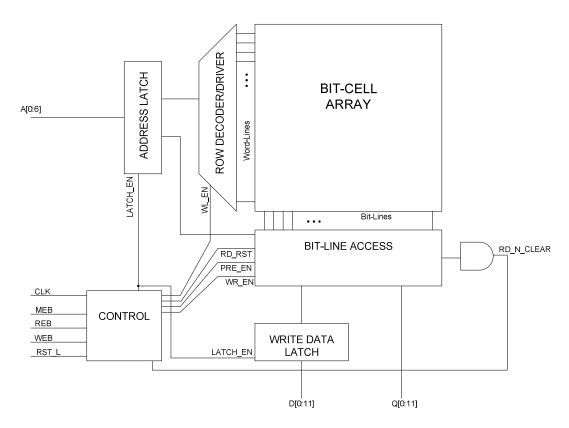

| Fig. | 3.1 Block diagram for a 128 Byte memory array                                                     | .11  |

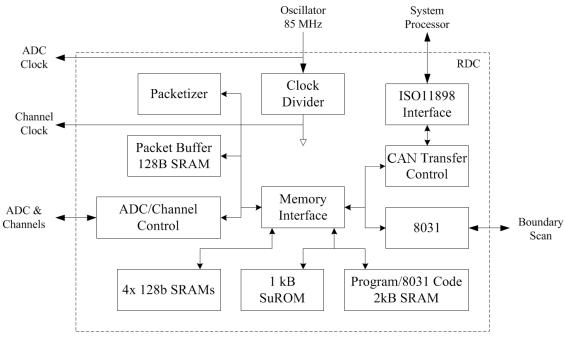

|      | 3.2 - Remote Digital Controller (RDC) system diagram                                              |      |

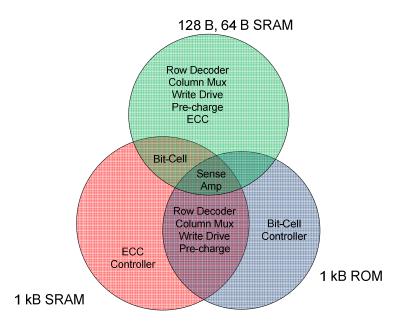

| Fig. | 3.3 - Venn diagram of design reuse across different SRAM models                                   | .14  |

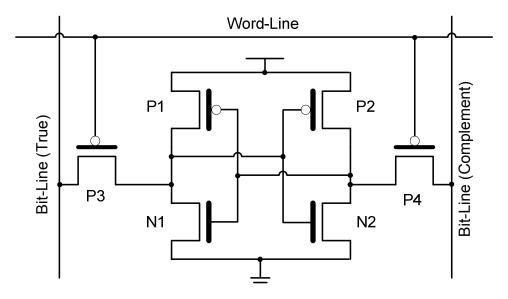

| Fig. | 3.4 - Bit-cell schematic                                                                          | .16  |

| Fig. | 3.5 - ROM bit-cell schematic (Storing '1')                                                        | 20   |

| Fig. | 3.6 - Bit-cell schematic modified for SNM measurement                                             | 21   |

|      | 3.7 - SNM simulation showing upset at 35 ns                                                       |      |

| Fig. | 3.8 - Simulated SNM over temperature and voltage                                                  | . 22 |

| Fig. | 3.9 - SRAM bit-cell layout                                                                        | 24   |

|      | 3.10 - ROM bit-cell layout                                                                        |      |

|      | 3.11 - Word-line drive schematic                                                                  |      |

|      | 3.12 - Word-line drive optimization schematic                                                     |      |

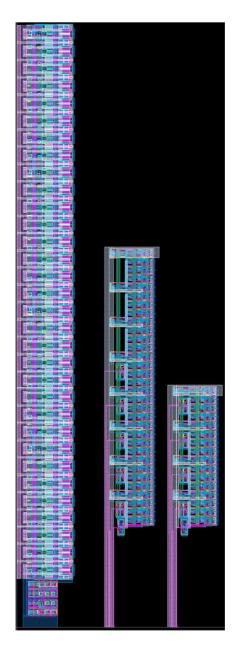

|      | 3.13 - Row decoder layouts for 64, 32, and 16 row arrays                                          |      |

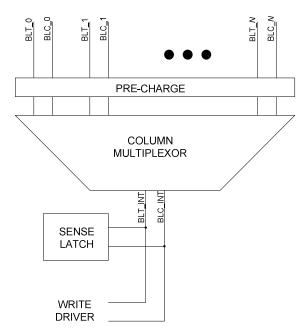

|      | 3.14 - Column access block diagram                                                                |      |

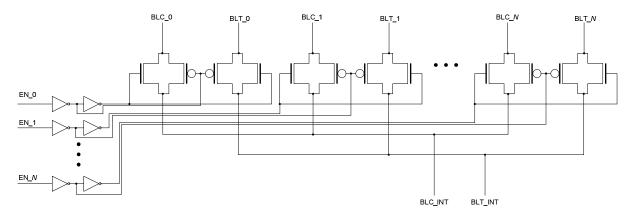

|      | 3.15 - Column multiplexer schematic                                                               |      |

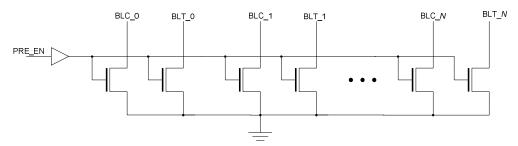

| Fig. | 3.16 - Pre-charge schematic                                                                       | .34  |

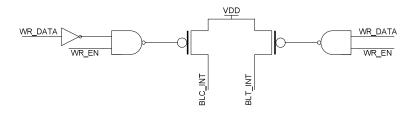

|      | 3.17 - Write drive schematic                                                                      |      |

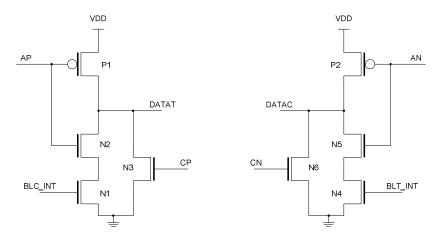

|      | 3.18 - Sense amplifier schematic                                                                  |      |

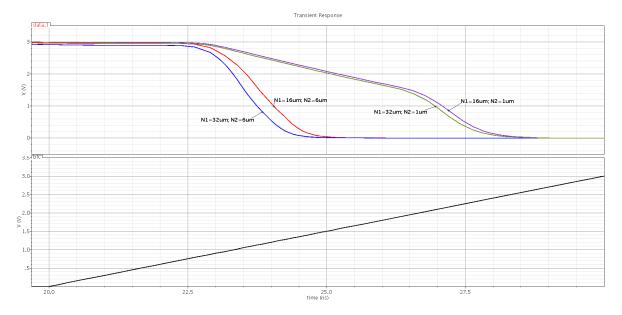

|      | 3.19 – Simulation results of transistor sizing on sense amplifier fall time                       |      |

|      | 3.20 - Column access layout - 4 columns                                                           |      |

|      | 3.21 - Column access layout - 16 columns                                                          |      |

|      | 3.22 - Control logic delayed clock generator                                                      |      |

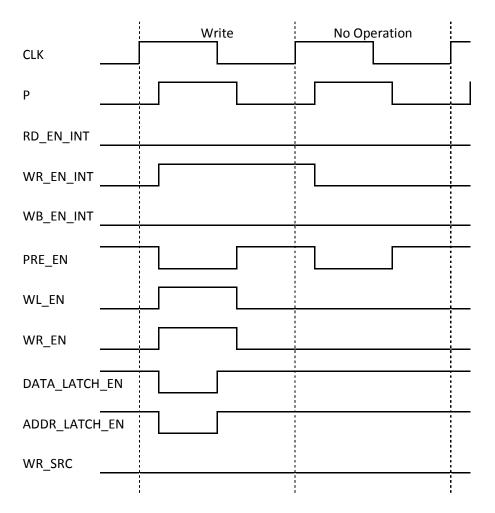

|      | 3.23 - 1 kB SRAM control signals - write                                                          |      |

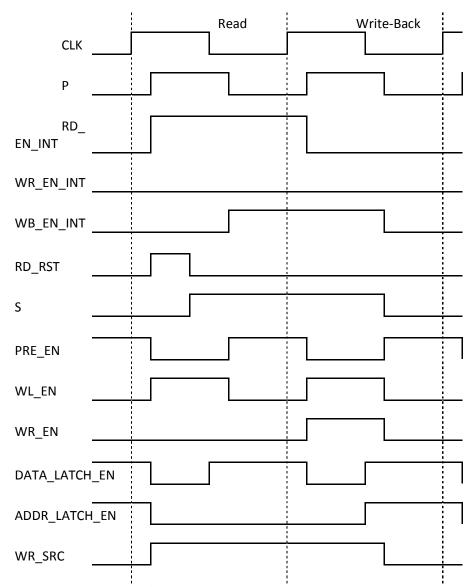

|      | 3.24 - 1 kB SRAM control signals - read with write-back                                           |      |

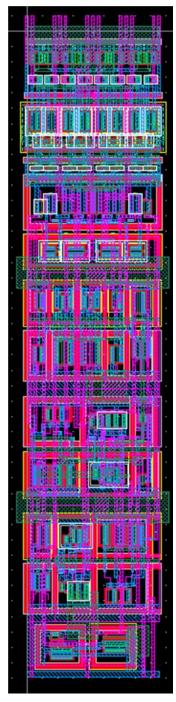

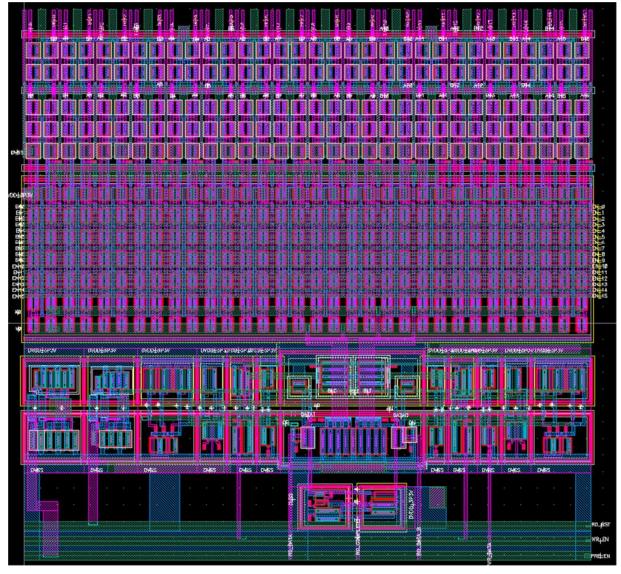

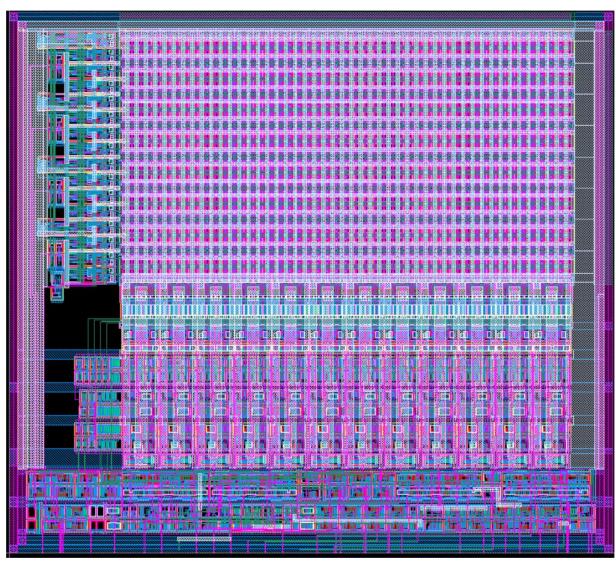

|      | 3.25 - UARK_SRAM_12X64 layout                                                                     |      |

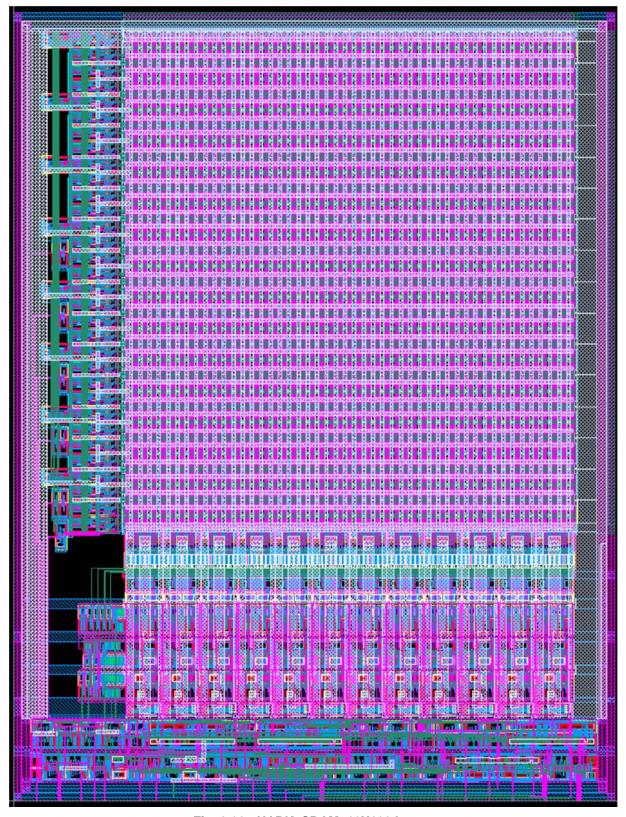

|      | 3.26 - UARK_SRAM_12X128 layout                                                                    |      |

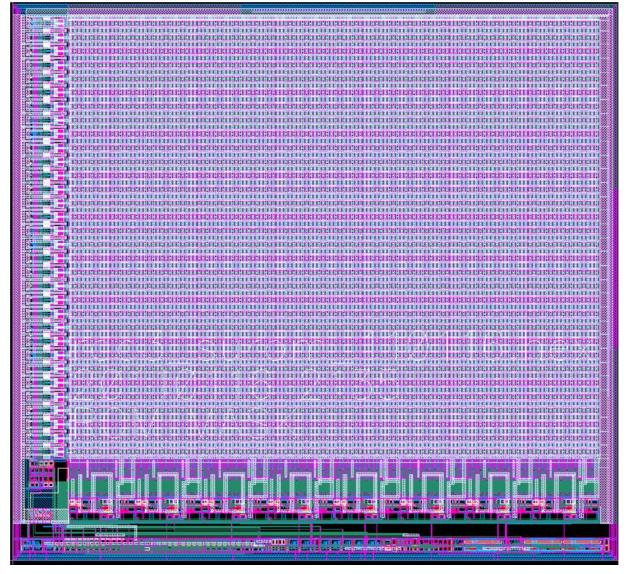

|      | 3.27 - UARK_SRAM_13X1024 layout                                                                   |      |

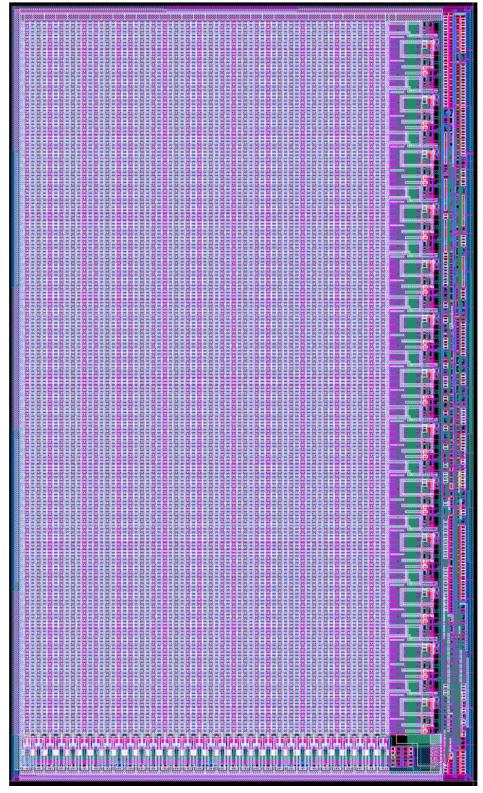

|      | 3.28 - UARK_ROM_8X1024 layout                                                                     |      |

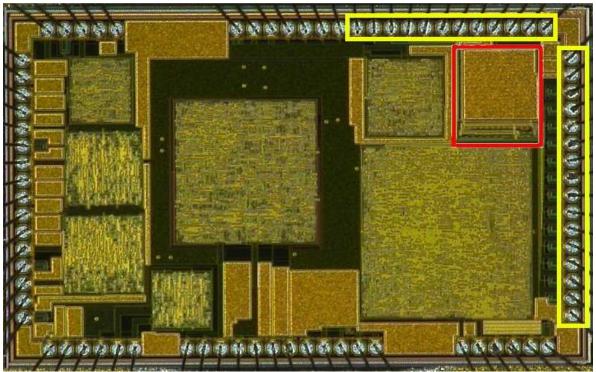

|      | 5.1 - CRYO 3A die micrograph with SRAM and SRAM pads highlighted                                  |      |

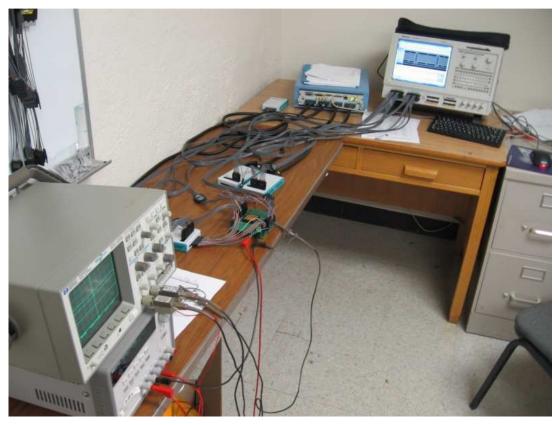

| Fig. | 5.2 - CRYO 3A testing boards                                                                      | 60   |

|      | 5.3 - CRYO 3A room temperature testing setup                                                      |      |

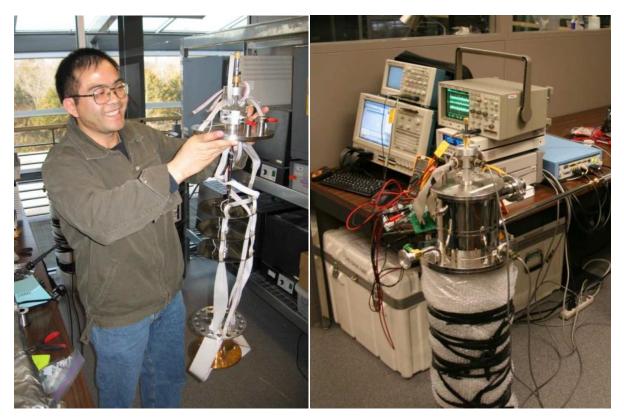

|      | 5.4 - CRYO 3A cold temperature setup                                                              |      |

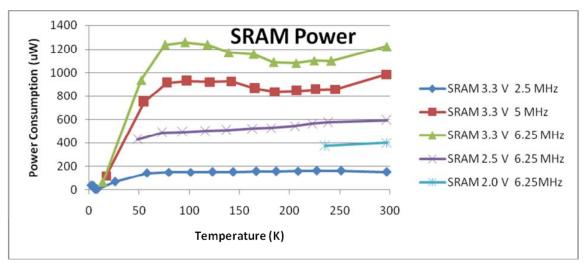

|      | 5.5 - Measured power consumption over temperature with varying V <sub>DD</sub> and execution rate |      |

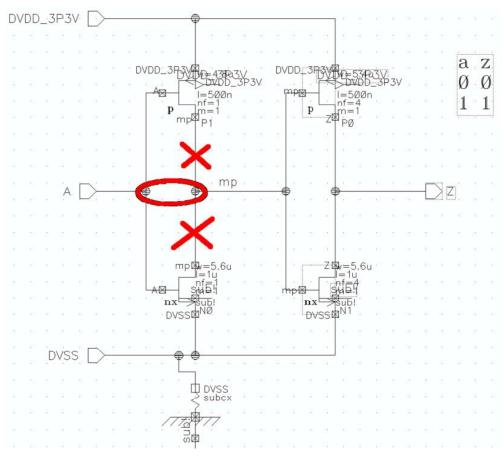

|      | 5.6 - CRYO 4 logic error. Highlighted buffer should be an inverter.                               |      |

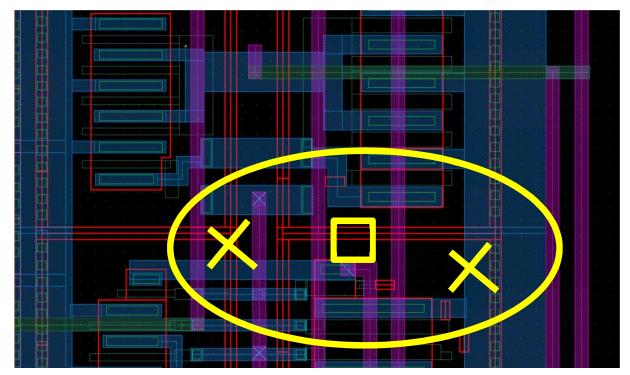

|      | 5.7 - CRYO 4 FIB layout: window (oval), bridging (square), and cuts (X)                           |      |

|      | 5.8 - CRYO 4 FIB schematic: Bridging (oval) and cuts (X)                                          |      |

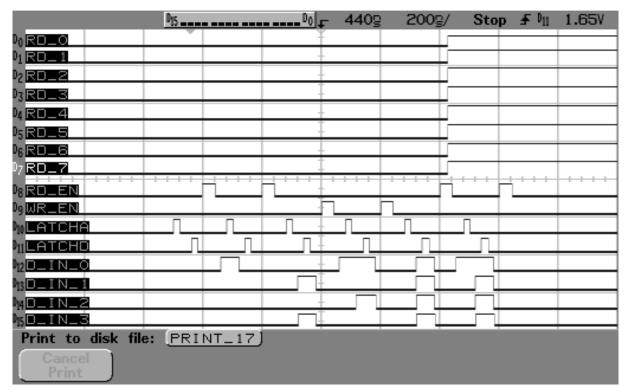

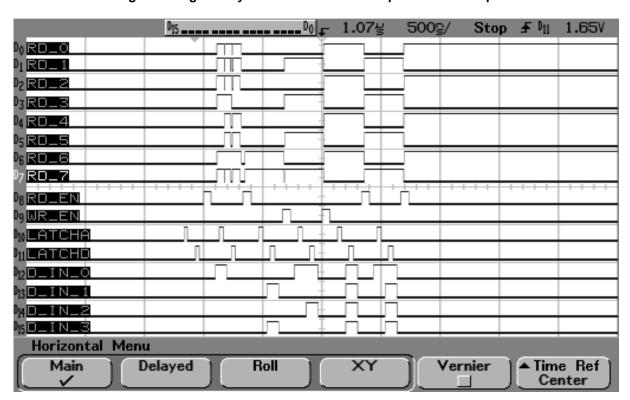

|      | 5.9 - Logic analyzer trace of CRYO 4 chip without FIB repair                                      |      |

| Fig. | 5.10 - Logic analyzer of CRYO 4 after FIB. Read data is the top eight rows                        | 69   |

## **List of Tables**

| Table 3.1 - General System Specifications                       | 10 |

|-----------------------------------------------------------------|----|

| Table 3.2 - Specific Feature Requirements For Each Memory Array | 12 |

| Table 3.3 - Calculated Values For Static Noise Margin           | 18 |

| Table 3.4 - SRAM Bit-cell Transistor Sizes                      | 19 |

| Table 3.5 - Memory Array Dimensions                             |    |

| Table 3.6 - Word-line Drive Transistor Sizes                    | 29 |

| Table 3.7 - Column Multiplexers Transistor Sizes                | 33 |

| Table 3.8 - Pre-charge Transistor Sizes                         | 35 |

| Table 3.9 - Write Drive Transistor Sizes                        | 36 |

| Table 3.10 - Sense Amplifier Transistor Sizes                   | 37 |

| Table 3.11 - List of Control Inputs and Outputs                 |    |

| Table 3.12 - Memory Array Operation Truth Table                 | 42 |

| Table 3.13 - Hamming ECC Encoding                               | 52 |

| Table 3.14 - Hamming ECC Single Error Decoding                  | 52 |

| Table 3.15 - Hamming ECC Single Error Syndrome Generation       |    |

| Table 4.1 - List of Liberty Model Characterization Points       | 55 |

| Table 4.2 - Memory Array Simulations Using ModelSim Vectors     |    |

| Table 5.1 - CRYO 4 Latch-up Test List                           | 71 |

#### Chapter 1 – Introduction and Overview

Data storage is a crucial part of almost all digital systems. Without some form of memory, circuits are limited in their responses to a set of input conditions. The design of reliable, compact, high-performance memories can present a significant design challenge. Memories designed for extreme environment applications, such as for operation in the rigors of space, present a wholly unique set of constraints and challenges that must be met. In this work the design of memory arrays for application to the lunar environment has been undertaken.

#### 1.1 Digital Data Storage for Microcontroller Applications

Digital data storage can be put into special arrays of optimized structures to improve the density and performance of a system. The traditional data storage elements such as the latch and flip-flop are simplified to store a voltage in an array. These simplifications either store a single voltage dynamically, or with feedback reinforcing the stored voltage.

Memory arrays can be used to store many different types of digital data. Microcontrollers and computers are primary users of memory arrays, although custom digital systems can also use memory. Typical microcontrollers such as the 8051 have program memory where in-order executable operation codes, or programs, are stored [1]. Depending on the architecture of the microcontroller core, the program memory may share address space with the scratchpad or data storage memory, which follows the Von Neumann architecture [2]. The other dominant processor architecture type is the Harvard architecture, which has separate address spaces for program memory and data memory, and is used by the 8051 microcontroller family [2].

The first few lines executed after the microcontroller powers on or resets are typically stored in a non-volatile memory array such as a ROM. In simple memory architectures, a single ROM bank is sufficient to store the instructions required to accomplish the intended task. Larger systems, such as a computer, or systems requiring greater flexibility may start with an initial ROM subroutine which then loads executable code into volatile RAM from a disk or remote host.

Data acquired from sensors or other measurements can be stored in memory arrays. Many operations benefit from large sets of measurements or periodic measurements. A simple use of such data is for playback or historical logging, such as with a digital storage oscilloscope, where a large memory array is filled with sequential digitized samples from an analog input that is displayed to a user afterwards. Other uses include temporary storage of measured data until the data can be transmitted to a master controller or a permanent storage device.

For any mathematical operation more complicated than a binary operation, most processors require an intermediate step. Typical microcontrollers, such as the 8051, require the calculation and storage of intermediate terms for calculations as simple as adding three numbers. Many simple microcontrollers lack complicated instructions found in computer processors such as floating point operations, multiplication, or division. These complicated instructions require multi-step algorithms with different state variables to complete. From a programming perspective, dynamic variables must be stored in RAM.

#### 1.2 Project Overview

The NASA Silicon Germanium Exploration Technology Development Program (ETDP) team was formed to do research on robust electronics for extreme environments such as space. During the first year of the project, the ETDP team embarked upon the challenge of creating an integrated replacement for a remote health node (RHN) design by BAE Systems as a demonstration of its capabilities. The RHN module was originally designed to be placed throughout the proposed X-33 space plane as a sensor data acquisition device [3]. This module contained a large number of parts within a warm box to maintain a suitable temperature during operation. The ETDP project aim is to develop a two-chip solution that essentially replicates the functionality of the original RHN. This new design consists of a mixed-signal

sensor interface chip, the Remote Sensing Interface (RSI), and a digital control chip, the Remote Digital Controller (RDC). These two chips, along with a voltage regulator and oscillator, replicate the functionality of the original RHN. The shielding and heating of the warm box are not necessary for the more robust proposed ICs, and thus even greater power, size, and weight savings over the original design are achieved. The proposed use of this device is to function over long-term lunar missions. The temperatures on the moon can reach values as low as -180 °C during a lunar night, and even down to -230 °C in permanently shadowed polar craters. Temperatures can reach up to +120 °C in direct lunar sunlight [4]. The elimination of environmental controls requires the electronics to function over this significantly wider temperature range.

#### 1.3 Silicon Germanium Process

The IBM SiGe5AM BiCMOS process has been used for the NASA ETDP project. This process combines a  $0.5~\mu m$  minimum gate length CMOS process with a silicon germanium hetero-junction bipolar transistor. A local interconnect layer is available in addition to 4 layers of metal. The top layer of metal is a thick analog metal layer [5].

Several challenges arise when dealing with an extreme temperature range. Validation of any design before manufacture is typically done through simulation. However, the models supplied with the process design kit only cover a subset of the required temperature range, from -55  $^{\circ}$ C to +125  $^{\circ}$ C. Transistor models for the extended temperature range of -180  $^{\circ}$ C to -55  $^{\circ}$ C were developed using measured data, allowing verification of designs through simulation over the desired temperature range of -180  $^{\circ}$ C to +125  $^{\circ}$ C [6].

Additional issues arise at low temperatures, where hot carrier injection can cause a gradual degradation of short channel transistors over time. As temperatures decrease, electrons are more likely to become trapped in the gate oxide [7]. This trapped charge decreases the effective  $V_t$  of the device, eventually making the device inoperable. Experimental data shows that this is primarily an issue for the NFET devices; PFET devices are largely unaffected. Two different techniques can be used to mitigate this effect at temperatures down to -180  $\circ$ C, and bo th aim to reduce the density of the electric field in the

transistor. The first method is to reduce the maximum voltage experienced by the transistor. In this application, the default process voltage of 3.3 V would need to be reduced to 2.5 V to provide adequate protection. The other method for mitigating the hot carrier injection effect is to maintain the process voltage of 3.3 V, and increase the channel length from the minimum of 0.5  $\mu$ m up to 1.0  $\mu$ m for all NFET devices [8]. To meet the project power supply requirement of 3.3 V, all NFETs in the RDC have gate lengths of 1.0  $\mu$ m or longer.

Radiation effects are also major concerns for a given design. On a transistor device level, the total ionizing dose received by a device can degrade the performance of the device. Experimental data shows that NFET devices are particularly vulnerable to a decrease in V<sub>t</sub> due to trapped charges in the shallow trench isolation around the transistor gate accumulated during exposure to radiation [4]. Other radiation effects are typically caused by a single heavy-ion strike on the circuit. When an ion strikes a transistor, the deposited charge may temporarily change the output of the circuit until the charge is dissipated. This effect may be a temporary glitch on a data signal, or it may change the stored value in a memory element. Depending on the nature of the single event upset, the result can cause a disruption in the circuit operation [9]. Mitigation of single event upsets has obvious implications in the design of memories, and requires both logical and physical design considerations.

Another single event effect which must be considered is latch-up. This is caused by the activation of the parasitic bipolar transistors inherent in the bulk CMOS process [10]. A heavy ion strike to the substrate can cause the activation of one of the many parasitic transistors formed by PNP/NPN junctions formed between substrate, wells and contacts. If one such transistor turns on, it can turn on another parasitic transistor, which then results in the latch-up chain reaction. Once activated, latch-up cannot be deactivated without removing the power supply from the circuit. Latch-up prevents the circuit from operating, and can cause excessive current draw resulting in device failure. In order to reduce the risk of latch-up in a CMOS process, the circuit designer must add guard rings, well contacts, and substrate contacts. These layout structures decrease the resistance between the base of the parasitic NPN/PNP and the power supply rails, making it harder for the pair to activate.

#### Chapter 2 – Background on Memory Design

Memory comes in all shapes and sizes. Depending on the intended use, there are several design parameters to emphasize. From simple one-bit designs to complex, high-density arrays, the tradeoffs focus on power, speed, and area.

#### 2.1 Latch

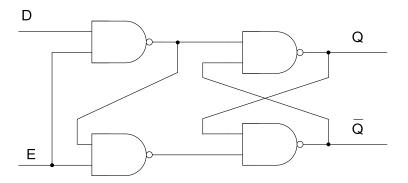

The latch is the simplest form of digital data storage [11]. A latch holds a single binary value or bit of data at a time. As shown in Fig. 2.1, a latch has two inputs and one output: a data input, an enable input, and a data output. The enable input determines the mode of operation of the latch, either transparent or latched. In the transparent mode, the data input is transferred to the output instantly. Changing the mode to the latched mode fixes the output data to the last input value while the latch was in the transparent mode. This data is now "latched" and all further inputs to the data input are ignored until the latch switches to the transparent mode.

Fig. 2.1 - Latch with enable

#### 2.2 Flip-Flops

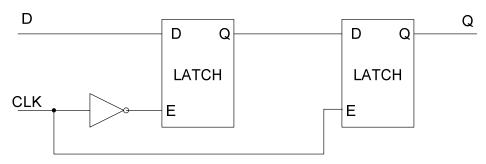

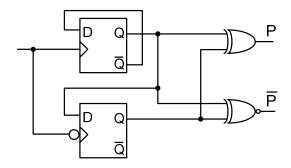

Flip-flops are more complicated data storage circuits. The primary difference between flip-flops and latches is that while latches pass data from the input to the output whenever the enable signal is asserted, flip-flops only pass data at the instant that the clock changes [11]. Typical flip-flops trigger on a single edge of the clock, either the rising or the falling edge. Dual edge triggered flip-flops exist as well, but these are less common. A simple way to create a flip-flop, shown in Fig. 2.2, is to chain two latches in series and invert the enable signal on one of the latches. With flip-flops, finite state machines are easily designed with a storage register and a logic function.

Fig. 2.2 - Master-slave flip-flop

#### 2.3 Memory Arrays

For large quantities of data storage, arrays are often used to provide density savings. The tradeoff between a memory array and a single memory element is density versus accessibility. Memory arrays are designed to access only a subset of their elements at a time through a port. Multiple-port memories allow reading and writing simultaneously to different addresses. Small arrays may use flip-flops or latches as the storage elements due to easy design and signaling requirements, but specialized memory arrays provide the best performance and storage density. Discrete flip-flops and latches have an advantage in that placing the single-bit storage gates is significantly easier in a design.

#### 2.3.1 Dynamic Random Access Memory

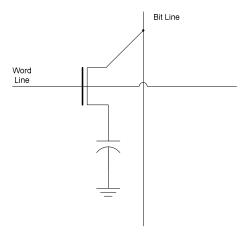

One form of memory array is the Dynamic Random Access Memory (DRAM). DRAM is dynamic due to the fact that there is no active restoring feedback. Typically, data is stored as a charge on a capacitor. A single transistor is used to regulate access to the capacitor [11]. This capacitor and transistor bit shown in Fig. 2.3 is arranged with other bits in a rectangular grid. Word lines run horizontally across

the array, connecting every gate of each transistor in a single row. Vertical bit-lines connect the drains of every transistor in a column, and the source of each transistor is connected to a capacitor. Each bit-line is connected to a sense amplifier, pre-charge, and write circuitry. Each word-line is connected to a driver that is connected to an address decoder.

Fig. 2.3 - DRAM bit-cell

At the beginning of a DRAM memory cycle, each bit-line is pre-charged to ½ V<sub>DD</sub>. The desired row is asserted and all bits in that row pull the bit-line towards either logic '1', or logic '0'. Because the bit-line capacitance is usually much larger than the capacitance of a single bit, the actual voltage change is small. This small change is amplified by a sense amplifier, which decreases the time required to detect the stored voltage. The process of reading data from a DRAM bit destroys the data contents of the entire row. This requires each row to be temporarily stored and written back. If data is to be written to an address, then this overrides the data stored by the sense amplifiers. The final stage of a DRAM cycle is to write the row data back into the capacitors. This is accomplished by driving each bit-line to either logic '1' or '0'. After the capacitors have been appropriately charged, the word-line is deactivated.

The charge on the capacitor degrades over time to a point when it is insufficient to register a large enough voltage difference on the bit-lines. This necessitates a periodic refreshing of each row in a DRAM array in addition to typical read and write operations. Due to this periodic refreshing, a DRAM module is constantly drawing power for the refresh read and write-back. In addition, if typical read and write operations do not service all addresses in a sufficiently timely manner; additional latency may be incurred

when a scheduled refresh of one row conflicts with a read or write on a different row.

#### 2.3.2 Static Random Access Memory

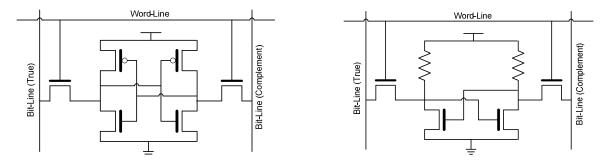

Static Random Access Memory (SRAM) differs conceptually from DRAM in one important feature: the data stored in a bit of SRAM will retain its value as long as power is applied to the circuit. This feature is obtained by a bi-stable circuit typically consisting of two cross-coupled inverters. Other topologies for bit-cells exist for special needs such as radiation hardness, separate read and write mechanisms, or low leakage in sub-90 nm processes. These inverters can be traditional CMOS inverters or even NMOS/PMOS with a resistive pull-up/down. Traditional SRAM bits are differential, storing a bit and its complement. Two additional access transistors are connected to each node to provide the ability to change the value of the bit-cell. SRAM arrays, as shown in Fig. 2.4, have two differential bit-lines that are connected to the drains of each access transistor, and a single word-line that connects to the gates of both access transistors. The peripheral circuitry is similar to DRAM in that there are address decoders driving the word-lines. Sense amplifiers, pre-charge circuits, and write drivers are also connected to both bit-lines.

Fig. 2.4 - Six transistor CMOS SRAM cell (left) and four transistor resistive NMOS SRAM cell (right)

A write cycle begins with pre-charging the bit-lines and applying the data pattern to the bit columns that will be written. The word line for the row is asserted, and the bit-line voltages will overpower the internal state of the bit-cell. For the circuits in Fig. 2.4, writing a logic '1' to the memory cell would begin by pre-charging both bit-lines to  $V_{DD}$ , and then grounding the bit-line compliment. The word-line is then switched from logic '0' to logic '1', and the voltage on the complementary bit-line overpowers the weak PFET or resistor pull-up.

A read cycle begins with the pre-charging of the bit-lines. The word line for the row is asserted

and the bit-cells begin to pull the bit-line voltages towards the internal voltages of the bit-cell. After sufficient time has elapsed to allow the bit-line voltages to change, the sense amplifier is activated, and it produces a logic-level output of the current bit-line state. The word-line is then de-asserted, and the memory array is ready for another cycle. The bit-cells in Fig. 2.4 could be read by pre-charging the bit-lines to VDD, and then switching the word-line from logic '0' to logic '1'. The relatively strong NFET on the node storing a logic '0' will pull the bit-line voltage towards ground, creating a voltage differential that can be read by a sense amplifier.

#### 2.3.3 Read Only Memory

Read Only Memory (ROM) is often used in digital circuits for the storage of fixed data. This data is stored in the array outside normal operating conditions, and is not changeable during normal circuit conditions. ROM arrays have several usages in digital circuits, such as look-up tables for mathematical operations, machine code program storage for central processing units, finite state machines, and complex logic operations.

A common design for a ROM array starts with an array of NFET devices with all sources grounded. All the gates in a row are tied together into word lines, and all the drains in a column are connected to bit lines. At the beginning of a read cycle from the ROM array, all the bit-lines are precharged to V<sub>DD</sub>. The desired word-line is then asserted, and the asserted transistors change the bit-line value from V<sub>DD</sub> towards ground. This results in every bit registering as a '0'. A bit can be programmed with '1's by disabling the transistor. This can be accomplished several ways and at many stages of the circuit's design life. The programming of the transistors can be accomplished very early in the design stage by removing the transistor in the layout. After the design has been fabricated, the transistors in the array can be programmed by ion bombardment to raise the threshold voltage, effectively removing the transistor from the circuit. Additional technologies allow programming through tunneling effects such as EPROM, EEPROM, and Flash [11].

#### Chapter 3 - Memory Array Design

Design of an SRAM block is a sequential process. A design begins with the core element, the bitcell, and the rest of the design is built around that single design. Each specification for subsequent blocks is dependent on earlier blocks. In order to preserve chronological design processes, each building block will be fully discussed before moving forward.

**Table 3.1 - General System Specifications**

| Supply Voltage          | 3.0 V – 3.6 V    |

|-------------------------|------------------|

| Operational Temperature | -180 ℃ to +125 ℃ |

| Operational Frequency   | 25 MHz           |

The array topology was chosen to provide flexibility with the error correction logic, as well as reduce timing dependencies. Fig. 3.1 Block diagram for a 128 Byte memory array the selected topology for the 128 byte SRAM. The bit-cells are arranged in a rectangular grid to form the bit-cell array. The word-lines from the array are driven by a row decoder with an included driver. Bit-lines are connected to the bit-line access block, where the bit-lines are manipulated for read, write, and pre-charge operations. The bit-line access also provides a completion signal for use with read timing. The address and write data are fed into latches and then drive the row decoder and bit-line access blocks. The control block interprets the clocked control signals coming into the array, and translates those signals into precise signals for controlling the input latches, row decoder, and bit-line access blocks. While the diagram is specifically for the 128 byte SRAM, the topology requires only minor modifications to fit all memory blocks.

Fig. 3.1 Block diagram for a 128 Byte memory array

General system requirements for memories are outlined in Table 3.1. The supply voltage range and operational temperature are functions of the total REU requirements, and the operational frequency is based on the 21 MHz RDC system clock. The frequency is higher to allow for additional logic in the data path. The RDC (Fig. 3.2) required four sizes and types of memory, as illustrated in Table 3.2. The CAN bus interface requires 2 blocks of 64 bytes for send/receive buffers, 128 byte blocks are used for sample averaging and packetization of data for the CAN bus, and 2 kilobytes of program memory are needed for the 8031 core. A 1 kilobyte ROM containing start-up code for the 8031 is required as well. The 2 kilobyte block is implemented as two 1 kilobyte arrays to allow further design sharing with the 1 kilobyte SRAM.

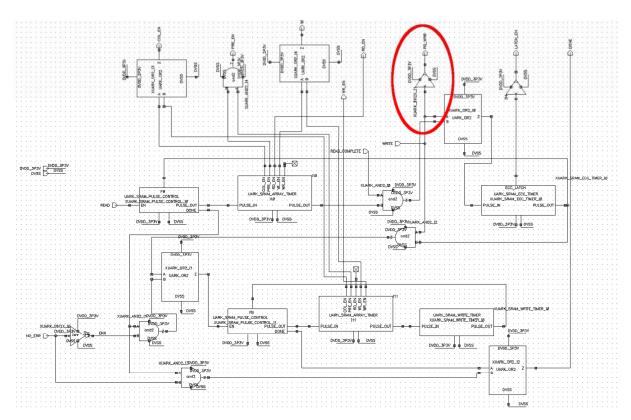

Fig. 3.2 - Remote Digital Controller (RDC) system diagram

Table 3.2 - Specific Feature Requirements For Each Memory Array

| 64 B SRAM  | Clocked inputs                                         |

|------------|--------------------------------------------------------|

| 128 B SRAM | Single Error Correction ECC                            |

|            | Single clock cycle operation                           |

| 1 kB SRAM  | Clocked inputs                                         |

|            | Single Error Correction, Double Error Detection ECC    |

|            | Automatic correction of stored data on error detection |

| 1 kB ROM   | Clocked inputs                                         |

|            | Single clock cycle operation                           |

#### 3.1 General Design Techniques

Several techniques were used throughout the design to meet the system requirements. The wide temperature range specified for the REU module required care for both the high and low temperature extremes. At the high end, the primary concern is electromigration. This is the erosion of metal wires due to high current. This effect is exasperated at higher temperatures, and by constant DC currents [5]. In order to mitigate the risks of electromigration, high current nets should have wider traces. At cold temperatures, hot electrons are an additional risk for degraded functionality over time. As discussed

previously, hot electron tunneling effects can be reduced at low temperature by decreasing the supply voltage or increasing the channel length of the NFET devices. Since the supply voltage is not a flexible constraint, all NFET transistors use a channel length of 1um or longer. Device characteristics vary greatly over the 305 °C temperature range. Both transistor threshold voltages as well as carrier mobility result in significant switching changes over the temperature ranges. As a result, great care was taken to understand the impact of temperature on circuit operation.

Radiation is also a major concern for the circuit, since the primary application is in space. There are two types of effects that were addressed at a system level. The first is Single-Event Latch-up (SEL), which is the activation of the parasitic bipolar transistors inherently present in a CMOS process. In order to minimize the SEL risk, all NFET and PFET transistors are enclosed in a guard ring [12]. This reduces the resistance in the parasitic bipolar latch to a point where the NPN and PNP transistors cannot turn on. The second type of radiation effect is Single-Event Upset, where a radiation event causes corruption in stored data. There are two storage elements that are considered for protection – the D flip-flops and the bit-cells. For the flip-flops, a dual interlocking cell topology prevents an ion strike on a single transistor from flipping the stored data value [13], [14]. To provide data protection for the SRAM arrays, Hamming error correction codes are applied to store redundant data. This redundant data provides the ability to correct a single bit of data. The algorithm and implementation will be addressed in greater detail in a following section.

With four similar arrays to design, a major focus is to minimize the amount of work that must be duplicated. Fig. 3.3 illustrates the extent of the design reuse throughout the project. When possible, blocks were designed to work in a broad range of operating configurations. A memory array is well suited to this task, as there is inherent modularity due to the array of bit-cells. In addition, a standard cell library is leveraged. The standard cell library, which is used for the entire RDC system design, meets all the base design requirements. All layouts are designed to easily tile for maximum compactness, and have been thoroughly simulated and characterized [14].

Fig. 3.3 - Venn diagram of design reuse across different SRAM models

#### 3.2 Introduction to Simulations

Simulation of any circuit provides valuable feedback at every stage of the design process. Poor design topologies can be vetted out, device size choices can be made, circuit interactions can be monitored, and whole design functionality can be verified through simulations.

Two simulation paths are used for design analysis and verification. The primary simulator is the Spectre simulator through the Cadence Analog Environment [15]. This SPICE-type simulator provides detailed model support and high accuracy for many levels of simulation. The primary limitation of the Spectre simulator is poor scaling to large device counts. This is particularly evident on large array simulations with over 100,000 transistors. For large arrays or long simulations, Spectre simulations take too long to provide useful information. These simulations require a simulator capable of using algorithms optimized for digital signals, such as Synopsys' HSIM [16]. Such "Fast SPICE" simulations can be completed in a fraction of the time required for a full Spectre simulation. These simulators potentially sacrifice some accuracy for speed, although the tradeoffs are minimized for digital CMOS circuits.

Models used for the simulations are a combination of the standard IBM design kit models and custom models for use over an extended temperature range. With design temperatures ranging from -180  $^{\circ}$ C to +125  $^{\circ}$ C, the importance of simulating the cir cuit over the entire temperature range cannot be overstated. The original IBM design kit models are valid over a temperature range of -55  $^{\circ}$ C to +125  $^{\circ}$ C, leaving the -180  $^{\circ}$ C to -55  $^{\circ}$ C range without models. Models were developed by ETDP team members for design validation at these lower temperatures. In addition to simulating over a wide temperature range, it is also important to simulate process variations. The models from the IBM design kit can be varied based on the measured statistical variation of properties such as gate oxide thickness, or doping concentrations. This can be used to verify functionality and performance of the circuit regardless of any manufacturing variability.

#### 3.3 Bit-Cell Design

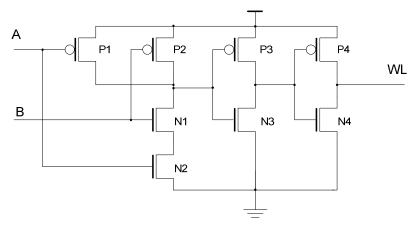

The bit-cell is the fundamental component of any memory array. Two basic topologies were considered for the bit-cell - a traditional NFET-based design using PFET pull-ups, and a PFET-based design using NFET pull-downs. The traditional NFET-based approach is usually preferred due to the increased frequency and drive strength of NFET devices. However, there are several disadvantages to the NFET devices when used over a wide temperature range and in high radiation environments. At extremely low temperatures, hot electron tunneling effects are more severe. For a temperature range extending to -180C, there are two primary techniques for mitigating these hot electron effects: reducing the supply voltage of the device, or increasing the channel length. In addition, the shallow trench isolation for the NFETs is susceptible to trapping charge, biasing the devices so that the off-state leakage increases as the total ionizing dose increases. These two effects significantly reduce the advantage NFET devices have over PFET devices for this particular application. For this reason, an alternative, PFET-based design shown in Fig. 3.4 was also considered.

Fig. 3.4 - Bit-cell schematic

Three transistor sizes are required for each of the three functions performed in a CMOS SRAM bit-cell. The two transistors in each cross-coupled inverter consist of a dominant driver transistor (P1 and P2), and a weak load transistor (N1 and N2). The transistors that perform the gating function to the bit are the access transistors (P3 and P4), and those are the same type as the driver transistor. The driver transistor is the strongest, followed by the access transistor, and the smallest transistor is the load transistor. If the transistor W/L ratios between the three devices are not carefully considered, the bit-cell may not be writable, or it may have such a low noise threshold that performing a read operation may upset the bit-cell.

One way of characterizing how easy it is for a bit-cell to change values is through calculation of the Static Noise Margin (SNM). The SNM quantifies the voltage that must be added between the cross-coupled inverters to induce a change in the stored value. A static noise margin of greater than 10% of VDD, or > 0.33V was suggested through industry consultations with BAE Systems [17], [18]. Following the design formulas (3.1)-(3.6)shown below [19], a set of transistor ratios were calculated to meet the SNM target and minimize transistor area. This design process only calculates the relative strengths of the transistors. The transistors are indicated as the driver  $\beta_d$  (P1 and P2), access  $\beta_a$  (P3 and P4), and load/pull-down  $\beta_p$  (N1 and N2).

$$SNM_{6T} = V_T - \left(\frac{1}{k+1}\right) \left\{ \frac{V_{DD} - \frac{2r+1}{r+1}V_T}{1 + \frac{r}{k(r+1)}} - \frac{V_{DD} - 2V_T}{1 + k\frac{r}{q} + \sqrt{\frac{r}{q}\left(1 + 2k + \frac{r}{q}k^2\right)}} \right\}$$

(3.1)

$$r = \frac{\beta_d}{\beta_a} \tag{3.2}$$

$$q = \frac{\beta_p}{\beta_a} \tag{3.3}$$

$$k = \left(\frac{r}{r+1}\right) \left\{ \sqrt{\frac{r+1}{r+1 - \frac{V_s^2}{V_r^2}}} - 1 \right\}$$

(3.4)

$$V_{s} = V_{DD} - V_{T} \tag{3.5}$$

$$V_r = V_s - \left(\frac{r}{r+1}\right)V_T \tag{3.6}$$

Using (3.1)-(3.6) to solve for SNM, it is apparent that there are an infinite number of solutions possible. Transistor sizes were chosen to minimize area by setting the weakest transistor, the load transistor, to a W/L ratio of 1um/1um. The difference in carrier mobility between PFETs and NFETs inherent in the CMOS process is multiplied by the W/L ratio, to give a  $\beta_p$  equal to 2.2. With this value fixed,  $\beta_a$  and  $\beta_d$  were swept to find the combination that matched the SNM requirement and minimized the sum of  $\beta_a$  and  $\beta_d$ , shown below in Table 3.3.

**Table 3.3 - Calculated Values For Static Noise Margin**

| Parameter                       | Value   |

|---------------------------------|---------|

| $\frac{I_{DSAT_N}}{I_{DSAT_P}}$ | 2.2 [5] |

| $V_{DD}$                        | 3.3 V   |

| $V_{T_P}$                       | 0.55 V  |

| $oldsymbol{eta}_a$              | 4       |

| $oldsymbol{eta}_d$              | 8       |

| $\beta_p$                       | 2.2     |

| R                               | 2       |

| Q                               | 0.275   |

| К                               | 0.227   |

| $V_s$                           | 2.75 V  |

| $V_r$                           | 2.38 V  |

| SNM <sub>6T</sub>               | 0.341 V |

The resulting transistor sizes shown in Table 3.4 were derived from the ratios and were then simulated to verify that the signal-to-noise margin was sufficient. Minimum gate lengths were used for the PFETs, and a 1.0 µm gate length was used for the NFETs. The calculated ratios were converted into transistor dimensions using (3.7)-(3.9), shown below.

$$\beta_d = \frac{W_d}{0.5\mu m} \tag{3.7}$$

$$\beta_a = \frac{W_a}{0.5\mu m} \tag{3.8}$$

$$\beta_p = \frac{W_p}{1.0\mu m} \times \frac{I_{DSAT_N}}{I_{DSAT_P}}$$

(3.9)

Table 3.4 - SRAM Bit-cell Transistor Sizes

| Transistor              | W/L Ratio       |

|-------------------------|-----------------|

| P1, P2 (drive)          | 4.0 μm / 0.5 μm |

| P3, P4 (access)         | 2.0 μm / 0.5 μm |

| N1, N2 (load/pull-down) | 1.0 μm / 1.0 μm |

Two initial versions of each topology were designed and physically implemented. In preliminary layouts, the NFET access bit-cell layout was 11.2% smaller than the PFET access design. However, the PFET access design has lower word-line capacitance due to the shorter channel length. In addition, NFET devices are much more susceptible to TID induced leakage. This could potentially reduce the isolation of a bit-cell from the bit-lines while not in use, causing data corruption. However, in the PFET access design, if the NFET load transistors developed large leakage currents, the bit-cell would shift to a complementary passive pull-down topology. This would make the bit-cells tolerant of a larger TID. The circuit benefits of the PFET access bit-cell were selected over the area savings of the NFET access design.

#### 3.3.1 ROM Cell Design

Traditional ROM designs use a single NFET transistor in an array, with a single bit-line for reading. This provides optimal layout density as well as a fast, low capacitance circuit. A primary design goal for the ROM was to maximize design reuse of the SRAM design at both the schematic and layout levels. This changes the design approach from minimizing area and transistor count to minimizing as many layout and interface changes as possible.

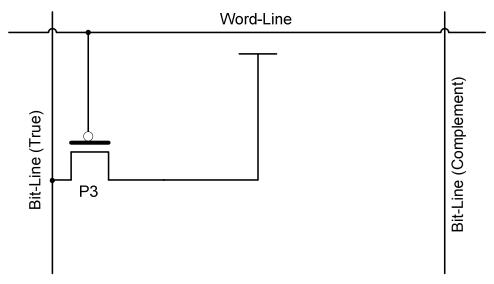

In order to make an SRAM bit-cell into a ROM bit-cell, modifications of the schematic were based on the assumptions of a fixed, pre-programmed value for each bit. This fixed the internal value of the cross-coupled inverter, with one node tied to ground, and one node tied to  $V_{DD}$ . Once these nodes are fixed, the driver and load transistors may be removed in favor of open circuits and shorts. This only leaves the two access transistors connected to both of the bit-lines. One of these access transistors will be connected to  $V_{DD}$ , and the other will be connected to ground. By analyzing the function of the access

transistors during a read operation, the access transistor connected to ground does not affect the bit-line voltage, only the access transistor connected to  $V_{DD}$ . Thus, the grounded access transistor is not necessary and can be removed, resulting in the schematic shown in Fig. 3.5. The circuitry interfacing the array is only changed to disable writing.

Fig. 3.5 - ROM bit-cell schematic (Storing '1')

#### 3.4 Bit-Cell Simulations

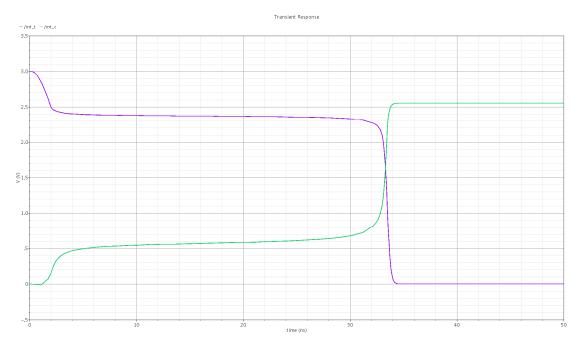

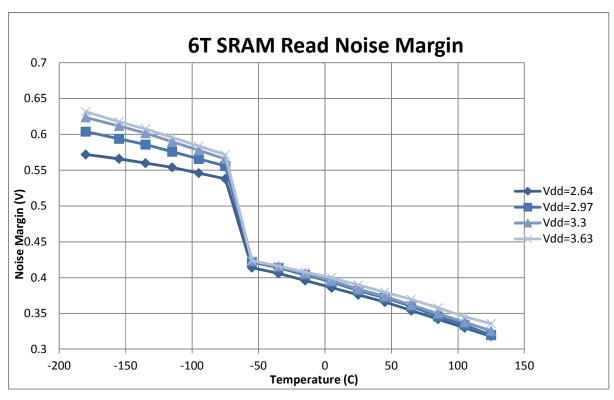

The primary stand-alone simulation with the bit-cells tests the Static Noise Margin (SNM). This test verifies the minimum amount of noise or mismatch required to upset the value of a memory cell during a read operation. Fig. 3.6 shows the simulation schematic, which is identical to the bit-cell except for the stimulus voltage sources. Ideal voltage sources are placed between the gates of each cross-coupled inverter and the drain of the opposite inverter. These voltage sources act as a worst-case noise source. The bit-lines are fixed to the worst case read conditions, and then the word-line is pulsed to simulate a read. The bit-cell is then monitored for an upset. A typical simulation is shown in Fig. 3.7. Both the true and compliment bit-lines are shown. If the voltages cross, such as at the 35 ns mark in Fig. 3.7, then an upset has occurred, and the applied offset voltage exceeds the SNM of the bit-cell. The simulation is repeated for increasing offset voltages until the highest offset voltage that does not result in an upset is found. The noise margin simulations show the simulated SNM of the bit-cell over all expected operating conditions in Fig. 3.8, excluding random process variation.

Fig. 3.6 - Bit-cell schematic modified for SNM measurement

Fig. 3.7 - SNM simulation showing upset at 35 ns

Fig. 3.8 - Simulated SNM over temperature and voltage

#### 3.5 SRAM Bit Layout

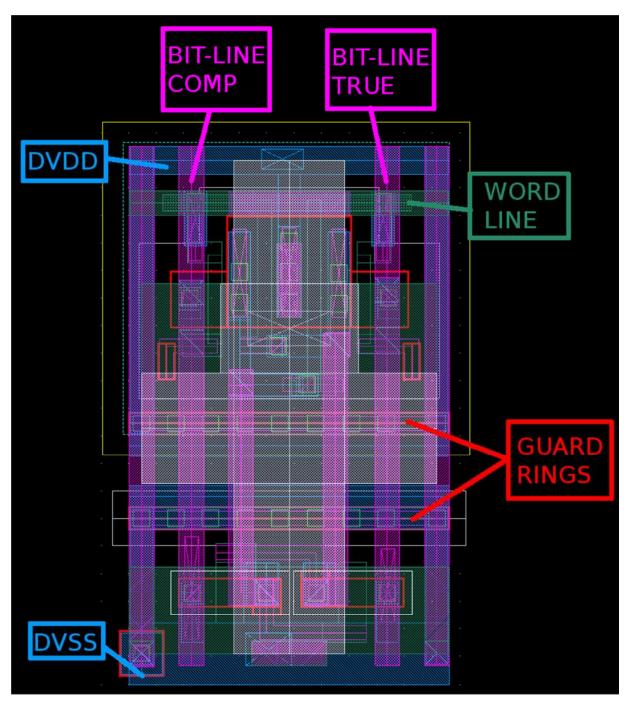

Careful design of the bit-cell layout is a high priority for any memory design, because any redesign in the bit-cell layout will most likely result in major layout modifications of any adjacent circuitry. The bit-cell is thus the cornerstone of the memory layout, and must be completed first. Optimization of the bit-cell layout is important to obtain maximum memory density and performance. An image of the bit-cell layout is shown in Fig. 3.9. Conversely, many radiation hardening layout techniques add significant area to the design. The main layout feature for radiation hardening is the n-well guard ring. The guard ring adds several microns of length to the n-well / p-substrate junction and prevents the routing of signals on any layer below the second metal layer. The downside to this is that four metal layers are required to provide full power and ground connectivity in addition to the bit-line and word-line signals. Without guard rings, a fully connected design is possible using only the first two metal layers; leaving top metal layers available for global routing. In this design, signals are routed on the first three metal layers, and power and ground connections are present on all four metal layers. This effectively prevents routing of any signals over the array.

Power and ground routing in the bit-cell uses both vertical and horizontal metal straps. This ensures a low resistance across the array and increases the number of suitable places for supplying power to the entire circuit. In order to reduce the number of n-well / p-substrate junctions, every other row is flipped vertically. This allows each row to have only one set of guard rings. The guard rings are a single ring for an N-well diffusion.

Fig. 3.9 - SRAM bit-cell layout

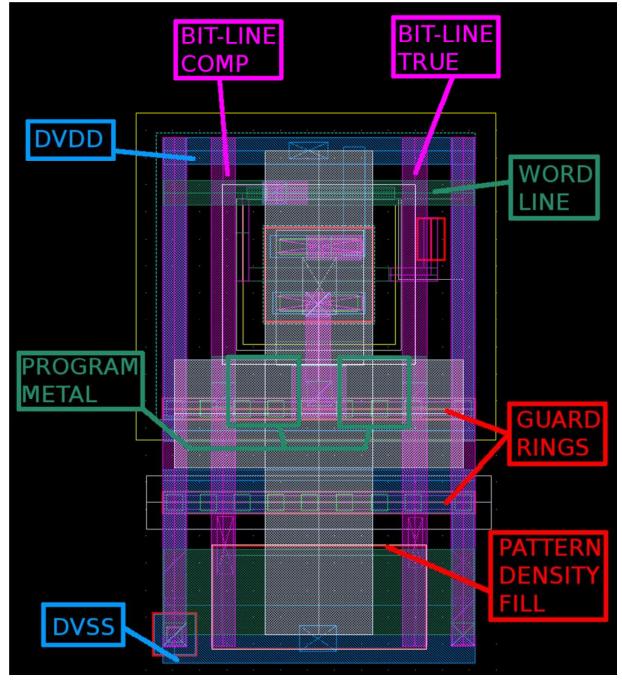

# 3.6 ROM Bit Layout

The ROM bit-cell was designed to act like an SRAM bit both electrically as well as physically. The bit-line and word-line wire locations were not moved in the ROM bit, creating a port layout similar to the RAM bit. The single transistor of the ROM bit is placed in the center of the n-well region. The drain of the PFET is connected up to the third layer of metal, through a metal bridge to either the complementary or true bit-line and down to one of the bit-lines on the second metal layer. This is done to reduce the shape changes to the bit-lines and word-lines and to facilitate efforts to change the ROM values. The third metal layer is the highest layer that could easily host the programming short. These shorting blocks are generated by a Python script from an Intel Hex file (Appendix A). This is shown below in Fig. 3.10 with the relevant areas highlighted.

Placing the programming layer as high on the metal stack as possible provides multiple benefits towards being able to reprogram the ROM array. Whole wafers can be preserved after processing all layers below the third metal layer, allowing a 'reprogramming' by changing only one processing mask. By placing the programming layer higher in the metal stack, the turn-around time of the redesign is shorter because fewer layers need to be added to finish the wafer. The other major advantage with a higher programming metal layer is that Focused Ion Beam (FIB) reprogramming is less costly due to the depth of the metal layer from the top of the wafer surface. A metal programming layer was chosen over using via programming for the relative ease of a FIB repair of a metal short programming over via programming.

Fig. 3.10 - ROM bit-cell layout

One of the design rules that is often only considered once a chip is nearing completion is design layer pattern density. Many design layers require that the layer usage be within a range specified in the design manual. Since the ROM bit-cell is a slimmed down version of the SRAM bit-cell, the area of certain layers used for transistors is below the minimum percentage. This deficiency can be a major issue when

an entire array is placed on a chip. Fill areas were added to supplement the active and polysilicon layers of the ROM bit-cell, thus avoiding a fill deficiency in the final memory array.

# 3.7 Array Layout

Once the bit-cell layout is ready for use, it must be combined into arrays to fit the size requirements for each block. Generally, the array aspect ratio determines the length of the bit-lines and word-lines. Square or wide rectangle arrays tend to balance the tradeoff between the word-line and bit-line capacitance, with a preference on longer word-lines. Table 3.5 below lists the array sizes that were chosen for the memory arrays.

**Table 3.5 - Memory Array Dimensions**

| Array Name | Array Size     | Array Grid | Physical<br>Dimensions |

|------------|----------------|------------|------------------------|

| SRAM 64    | 64 x 12 bits   | 16 x 48    | 286.4 x 604.8          |

| SRAM 128   | 128 x 12 bits  | 32 x 48    | 572.8 x 604.8          |

| SRAM 1024  | 1024 x 13 bits | 64 x 208   | 1145.6 x 2620.8        |

| ROM 1024   | 1024 x 8 bits  | 64 x 128   | 1145.6 x 1612.8        |

Once the array dimensions are selected, the array is constructed. Special layouts are used for the corner and edge bit-cells to properly contain the guard rings and power connections. After the layouts are finished, detailed parasitic extraction is performed to measure the estimated capacitance for the longest bit-lines and word-lines. These values are used in simplified test benches to ease the simulation load during the design of later blocks.

# 3.8 Row Select

The word-lines of a memory array determine if a row is connected to the bit-lines or not. During any single memory operation, only one word-line will be asserted. Many rows may be present in an array, requiring a method of ensuring that only one row is active at a time. In addition, reducing the number of control signals is a high priority for data busses inside a circuit. The optimal circuit for meeting both goals

simultaneously is a decoder. To understand decoder operation, consider that each memory array row is assigned a unique sequential number. A binary data bus carries a value equal to the row number that is to be accessed. Logic blocks then "decode" the binary signal to a single output, providing the minimal number of control lines for a given number of rows.

In addition to the decoding of address bits, additional buffering and control is required for driving the word-lines. During memory operations, the desired word-line is not continuously asserted. This permits time for presetting the bit-lines to voltages appropriate for the operation and data values desired. A simple decoder circuit does not have a way to de-assert a word-line signal, so a simple scheme is devised to add this function: increase the number of input control signals by one, and only implement one half of the decoder physically. In this design, this is accomplished by a logical AND with each output bit and an enable signal from the controller. Word-lines also have large capacitive loads on the circuits, requiring multiple stage buffering.

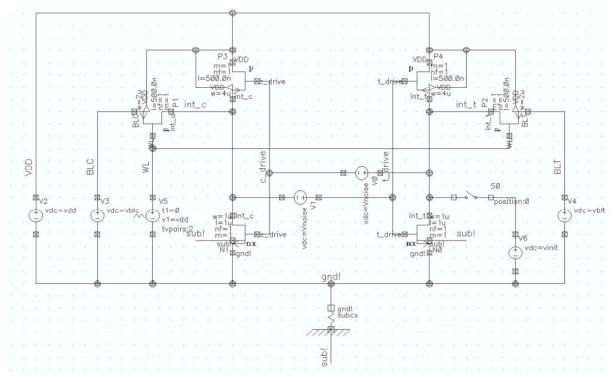

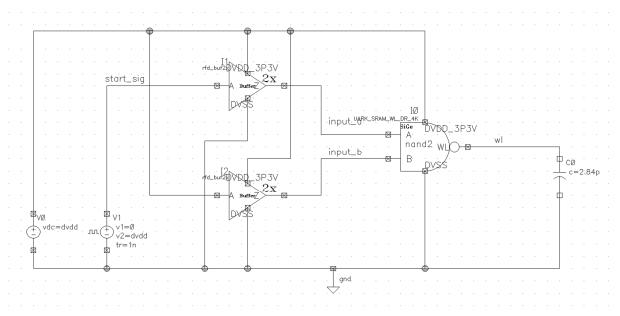

For the 1 kB arrays, the design is implemented as a set of four 4-to-16 decoders with multiple enable inputs that allow several decoders to be placed in the system with minimal additional circuitry. A NAND gate drives a buffer, shown in Fig. 3.11, which provides enough drive strength to switch the word-line. The word-line enable signal is fed to one of the inputs of the NAND gate to reduce the propagation delay of the enable signal. The smaller arrays use one decoder to fully access all rows, but share the NAND gate and buffer output. Both designs leverage the standard cell library for all gates except the final drive gates. These cells have special layouts to match the pitch of the array. The drive strength of the final buffer is adjusted for both sizes.

Fig. 3.11 - Word-line drive schematic

#### 3.8.1 Row Access Simulation

The row decoder consists of a decoder and a driver for the word-lines. Since the decoding portion consists of standard cells, the primary interest in simulation is the propagation delay and the rise and fall times of the word-line. The word-line driver is connected to an ideal capacitor that emulates the capacitive load of the word-line in the bit-cell array. The optimization function of Analog Environment is then used to iteratively determine optimal transistor sizes of the word-line driver to minimize delay, rise time, fall time, and power consumption. The resulting transistor sizes are shown below in Table 3.6. The simulation test bench is shown below in Fig. 3.12. Two versions of the memory arrays were optimized: the 48 column wide version, and the 208 column wide version. The ROM width of 128 columns was not optimized, and uses the 208 column driver.

Table 3.6 - Word-line Drive Transistor Sizes

| Device | SRAM_12X64, SRAM_12X128 | SRAM_13X1024, ROM_8X1024 |

|--------|-------------------------|--------------------------|

| P1, P2 | 1.5 µm / 0.5 µm         | 6.675 μm / 0.5 μm        |

| P3     | 1.5 μm / 0.5 μm         | 46.36 μm / 0.5 μm        |

| P4     | 6.0 μm / 0.5 μm         | 82.4 μm / 0.5 μm         |

| N1, N2 | 2.0 μm / 1.0 μm         | 15.875 μm / 1.0 μm       |

| N3     | 1.0 μm / 1.0 μm         | 11.16 µm / 1.0 µm        |

| N4     | 4.0 μm / 1.0 μm         | 25.55 μm / 1.0 μm        |

Fig. 3.12 - Word-line drive optimization schematic

# 3.8.2 Row Access Layout

The layout of the row decoder and drive circuit is heavily dependent on the height of the bit-cell. The final AND gate and buffer must exactly match the height of the bit-cell so that it can be flipped and abutted with it. The smallest module of the row decoder will be at least a multiple of the row height. Additional circuits with large fan-outs are placed below the row decoder in the rectangular space formed by the row decoder and the column circuitry. A sampling of all the final versions of the row decoders is shown in Fig. 3.13. The 16-row version is derived from the 32-row decoder.

Fig. 3.13 - Row decoder layouts for 64, 32, and 16 row arrays

# 3.9 Column Access

The analog circuitry that connects directly to the bit-lines is called the column access block. Each array has eight to thirteen access blocks, depending on the array size. The sub-blocks all need to be in close physical proximity, and the design is simplified by grouping these four sub-blocks together. The configuration of these blocks is shown below in Fig. 3.14.

Fig. 3.14 - Column access block diagram

#### 3.9.1 Column Multiplexing

To create large matrices that have more columns than the width of the data bus, some method of switching between the columns is required. Multiplexing the columns is a simple and effective method to interface multiple columns. Through multiplexing, a single set of columns in an array can be selected for read or write operations. Two choices exist on where to multiplex the columns. The first option is to include read and write circuitry for every column, and use digital multiplexers to select the desired column. This is a common approach for DRAM due to the need to read every bit in a row. One major downside to this method is the increased difficulty of laying out the read and write circuitry in the width of a bit-cell. The other approach is to use a transmission gate multiplexer to select a pair of bit-lines from all of the column

bit-line pairs in a group and use only one set of read and write circuitry for every column associated with a certain bit, shown in Fig. 3.15. This allows more optimal layout design due to the significantly less restrictive width requirements.

Fig. 3.15 - Column multiplexer schematic

A one-level multiplexer was used instead of a tree multiplexer to improve scalability as well as to minimize the number of transistors in series with the writing and pre-charging circuits. The original 128 byte SRAM uses four columns for every bit, requiring two 4-to-1 multiplexers to interface the array to the reading and writing circuitry. For the larger arrays, sixteen columns are used, so two 16-to-1 multiplexers are added. If the transistors are not large enough, there will not be enough drive strength to write to the array. Transistor sizing for the column multiplexers, shown in Table 3.7, was determined by analyzing simulations with the pre-charging and writing circuits to ensure that the drive strength is sufficient to function across all simulation corners.

**Table 3.7 - Column Multiplexers Transistor Sizes**

| Device | SRAM_12X64,<br>SRAM_12X128 | SRAM_13X1024,<br>ROM_8X1024 |

|--------|----------------------------|-----------------------------|

| PFET   | 9.0 μm / 0.5 μm            | 24.0 μm / 0.5 μm            |

| NFET   | 2.0 μm / 1.0 μm            | 8.0 μm / 1.0 μm             |

# 3.9.2 Pre-charge

At the beginning of a read or write operation, the bit-lines are at an unknown state. Either bit-line could be at a voltage between ground and V<sub>DD</sub> due to previous array activity. A preexisting state on the bit-lines can pre-bias the sense amplifiers to produce the opposite result, or even hinder the writing of data into a bit-cell. In order to counter this effect, a pre-charge circuit is used to set the bit-lines to a known voltage before reading or writing. There are two functions of a pre-charge circuit; to bring the bitline voltages towards a reference voltage and to reduce the voltage difference between the two complimentary bit-lines. The most convenient and stable reference available that allows the read operations to function properly is the negative supply rail, or ground. An alternative voltage reference used in other designs is  $\frac{1}{2}$   $V_{DD}$ . By using ground as the voltage reference for the pre-charge circuit, high current, temperature stable voltage references are not required, which saves area, reduces design complexity, and simplifies wire routing. The pre-charge driver circuit uses two NFET devices to pull both bit-lines to ground. Every column has a pair of NFET devices in order to ensure that the bit-lines will not inadvertently write data during a read operation, as illustrated in Fig. 3.16. The transistor sizes were determined by simulating the pre-charge cycle of a memory array and adjusting the size of the transistors to take a bit-line at 3.3 V down to 0 V in approximately 1/4 of the expected clock cycle, or 10 ns. The resulting transistor sizes are shown in Table 3.8.

Fig. 3.16 - Pre-charge schematic

Table 3.8 - Pre-charge Transistor Sizes

| Device | SRAM_12X64, SRAM_12X128 | SRAM_13X1024, ROM_8X1024 |  |  |  |

|--------|-------------------------|--------------------------|--|--|--|

| NFET   | 4.0 μm / 1.0 μm         | 8.0 μm / 1.0 μm          |  |  |  |

| Buffer | rfd_buf8x               | rfd_buf18x               |  |  |  |

#### 3.9.3 Write Drive

Writing to the bit-cells is accomplished after pre-charging the bit-lines to ground. Consider one of the bit-lines driven to  $V_{DD}$ . The appropriate word-line is then asserted, and the data value is written to the bit-cells in the row. Writing is then accomplished by two PFET devices controlled by a logic function of the write enable signal and the data to be written, shown in Fig. 3.17. When write enable is asserted, one of the PFET devices will activate, driving the connected bit-line to  $V_{DD}$ . This should be powerful enough to overcome the load transistor through the access transistor in the bit-cell, or else writing is not possible. Simulations across all corners were performed to ensure that the transistor sizes in Table 3.9 allowed reliable write performance. Asserting the write enable signal before asserting the appropriate word-line signal allows faster writing by allowing the bit-line voltage to rise to  $V_{DD}$  before the word-line is asserted. The result is the higher initial bit-line voltage switches the bit-cell faster than if the bit-line voltage is driven to  $V_{DD}$  after the word-line is asserted.

Fig. 3.17 - Write drive schematic

Table 3.9 - Write Drive Transistor Sizes

| Device   | SRAM_12X64, SRAM_12X128 | SRAM_13X1024, ROM_8X1024 |

|----------|-------------------------|--------------------------|

| PFET     | 9.0 μm / 0.5 μm         | 32.0 μm / 0.5 μm         |

| Inverter | rfd_inv2x               | rfd_inv4x                |

| NAND     | rfd_nand2i2x            | rfd_nand2i8x             |

#### 3.9.4 Sense Amplifier

The sense amplifier is a circuit used during a read operation that accelerates the resolution of the data value on the bit-lines. It provides isolation from extra capacitive loads and noise present in downstream circuits. It also provides a driving capability to the data outputs, and a fast transition time. When the word line in a row is asserted, the bits charge the bit-line voltages through the access transistors. For this design, the bit-lines are pre-charged to 0 Volts, and the bit-cells pull either the true or complement bit-line towards the supply voltage of 3.3 Volts. The bit-line voltage's rate of change depends largely on the number of bit-cells in a column of an array. For the relatively small 64 and 128 byte arrays, there are 16 and 32 rows, respectively. The larger memory designs such as the 1 kB ROM and the 1 kB SRAM have 64 rows, resulting in much higher resistive and capacitive loads on the bit-cells. In the initial design with 32 rows, the bit-line voltage rises to the full value on the order of a several nanoseconds.

While high performance RAM uses a type of clocked latched comparator, generating timing signals used for such a latch is difficult over wide temperature and voltage variations. A conservative design shown in Fig. 3.18 was chosen to ensure that unexpected bit-line conditions could not cause a fault. The sensing input is provided by two NFETs (N1 and N4) with each gate tied to one of the bit-lines. After a pre-charge, both bit-lines will be at 0 Volts, and the drain voltages of the sensing NFETs are at 3.3 Volts. When the word-line is asserted, one of the bit-line voltages will begin to rise. This turns on one of the sensing NFETs, which pulls the drain voltage towards ground. Once one of the outputs reaches 0 Volts, both sensing transistors are disconnected by a series NFET (N2 or N5), and an inverter drives the latched output for both bit-lines. Additional logic shown in (3.10)-(3.14) controls the unlatching (CP, CN, AP, BLT\_INT) and ensures that the four transistors on each leg cannot shunt current directly from the power supply to ground.

Fig. 3.18 - Sense amplifier schematic

$$CP = \overline{RD\_RST + \overline{DATAC} + DATAT}$$

(3.10)

$$CN = \overline{RD\_RST + \overline{DATAT} + DATAC}$$

(3.11)

$$AP = \overline{RD\_RST + \overline{DATAC}}$$

(3.12)

$$AN = \overline{RD\_RST + \overline{DATAT}}$$

(3.13)

$$RD\_COMPLETE = AP + AN$$

(3.14)

**Table 3.10 - Sense Amplifier Transistor Sizes**

| Device | W/L              |  |  |  |  |

|--------|------------------|--|--|--|--|

| P1, P2 | 4.0 μm / 0.5 μm  |  |  |  |  |

| N1, N4 | 32.0 μm / 1.0 μm |  |  |  |  |

| N2, N5 | 6.0 μm / 1.0 μm  |  |  |  |  |

| N3, N6 | 4.0 μm / 1.0 μm  |  |  |  |  |

The result is a robust circuit that is well behaved regardless of any potential startup or transient anomalies. Transistor sizing shown in Table 3.10 was determined by minimizing the transition time on the output node. The holding transistors do not have a time critical function, so the W/L ratio is relatively small. The sensing transistor and the series-pass transistor were optimized to result in minimal fall time during sensing. The effects of transistor sizing on the fall time is shown below in Fig. 3.19. The design performs well with both fast rise times from the small arrays as well as with the longer rise times from the 1 kB arrays. As a result, the sense amp was used on all arrays to reduce the total number of designs required.

Fig. 3.19 – Simulation results of transistor sizing on sense amplifier fall time 3.9.5 Layout of BL Access

There are two layout variants of the bit-line access circuitry, but the topology is essentially the same. At the top of the layout, nearest to the bit-cell array, are the pre-charge drivers. Positioning them here allows for an efficient layout of the drivers and minimizes the signals passing through to just the enable signal. Immediately below the pre-charge is the column multiplexer. The write drive transistors and the sense amplifier transistors are clustered together for a balanced layout. Balance is more important in this layout than transistor matching. Balance affects different wire resistances and capacitances, which can cause differences in performance from the intended design. At the bottom of the cell is all the standard cell logic used to drive the four blocks. The logic leverages the standard cell library for all gates. The final layouts of the 4 column (Fig. 3.20) and 16 column (Fig. 3.21) column access layouts are shown below.

Fig. 3.20 - Column access layout - 4 columns

Fig. 3.21 - Column access layout - 16 columns

# 3.10 Control Logic

Once the array has been built, additional control logic is necessary to convert the raw control signals needed to activate the array into inputs that are compatible with a synchronous system. The target system is a synchronous state machine, and the memory integrates into the state register portion of the state machine diagram. This translates into a system requirement that the memory array processes inputs based on a rising clock edge, and the output must be ready for the following stage by the next rising clock edge.

The control signals on the input of the memory array are active-low, and consist of a reset, block enable, read enable, and write enable. The reset signal is an asynchronous reset that places the array control logic in a known state. The reset will not affect any contents inside the memory array, but asserting the reset signal during a write may cause data corruption. The enable control signals are synchronous inputs that are latched on a rising clock edge. These inputs, along with the clock, must be converted into carefully timed signals for the array control signals. Any mistiming of the control signals has the potential of corrupting data or preventing the data from being read back. Table 3.11 lists the input and output signals of the control block, and Table 3.12 shows the expected functionality for a given set of control inputs.

Table 3.11 - List of Control Inputs and Outputs

| Pin Name | Туре       | Description                                                       |

|----------|------------|-------------------------------------------------------------------|

| CLK      | INPUT      | Input clock – maximum frequency 25 MHz                            |

| RST_L    | INPUT      | Asynchronous reset for all control logic                          |

| MEB      | INPUT      | Array enable ("Chip Select")                                      |

| REB      | INPUT      | Read Enable                                                       |

| WEB      | INPUT      | Write Enable (SRAM only)                                          |

| ADR      | INPUT BUS  | Active Address                                                    |

| D        | INPUT BUS  | Write Data                                                        |