# **PURDUE UNIVERSITY GRADUATE SCHOOL Thesis/Dissertation Acceptance**

This is to certify that the thesis/dissertation prepared

$_{Bv}\,$  Stephen W. Abell

#### Entitled

Parallel Acceleration of Deadlock Detection and Avoidance Algorithms on GPUs

Master of Science in Electrical and Computer Engineering For the degree of \_

Is approved by the final examining committee:

Dr. John Jaehwan Lee

Chair

Dr. Brian King

Dr. Stanley Chien

To the best of my knowledge and as understood by the student in the *Research Integrity and* Copyright Disclaimer (Graduate School Form 20), this thesis/dissertation adheres to the provisions of Purdue University's "Policy on Integrity in Research" and the use of copyrighted material.

Approved by Major Professor(s): Dr. John Jaehwan Lee

Approved by: Dr. Brian King

06/26/2013

Date

Head of the Graduate Program

# PARALLEL ACCELERATION OF DEADLOCK DETECTION AND AVOIDANCE ALGORITHMS ON GPUS

A Thesis

Submitted to the Faculty

of

Purdue University

by

Stephen W. Abell

In Partial Fulfillment of the

Requirements for the Degree

of

Master of Science in Electrical and Computer Engineering

August 2013

Purdue University

Indianapolis, Indiana

#### ACKNOWLEDGMENTS

First and foremost, I must thank my advisor Dr. John Lee. His dedication to innovative and thorough research is what led to the accomplishments in this thesis. I must thank him for our many meetings, technical discussions, and paper revisions. All of which have helped me grow into a more thorough engineer.

I must thank my family and girlfriend for their undying support and confidence in me. They have always stood beside me in my decision to seek higher education and believed in my abilities as an engineer.

Lastly, I would like to thank Sherrie Tucker. Sherrie has always been helpful when it comes to logistical aspects of my graduate career and has always kept me on track. Also, her seemingly endless supply of coffee and candy has been a huge aid in my success as a masters student.

# TABLE OF CONTENTS

iii

|    |      |        |                                             | Page |

|----|------|--------|---------------------------------------------|------|

| LI | ST O | F TAB  | LES                                         | vi   |

| LI | ST O | F FIGU | JRES                                        | vii  |

| A] | BSTR | ACT    |                                             | ix   |

| 1  | INT  | RODUC  | CTION                                       | 1    |

|    | 1.1  | Proble | m Statement                                 | 1    |

|    | 1.2  | Termir | nology                                      | 2    |

|    |      | 1.2.1  | Definitions in the CUDA Framework           | 2    |

|    |      | 1.2.2  | Definitions in the Deadlock Domain          | 3    |

|    |      | 1.2.3  | Definitions in the Graph Theory Domain      | 5    |

|    |      | 1.2.4  | Theorems for Deadlock Detection             | 10   |

|    | 1.3  | Relate | d Work                                      | 11   |

|    | 1.4  | Motiva | tion                                        | 13   |

|    | 1.5  | Thesis | Organization                                | 15   |

| 2  | PAR  | ALLEL  | COMPUTING AND THE CUDA FRAMEWORK            | 16   |

|    | 2.1  | Serial | vs. Parallel Computing and Flynn's Taxonomy | 16   |

|    |      | 2.1.1  | Single-Instruction Single-Data (SISD)       | 17   |

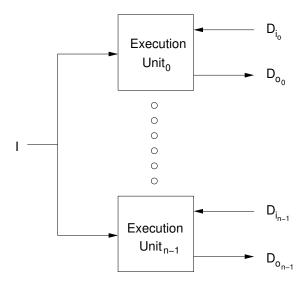

|    |      | 2.1.2  | Single-Instruction Multiple-Data (SIMD)     | 18   |

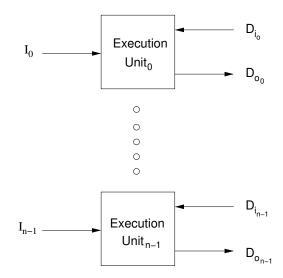

|    |      | 2.1.3  | Multiple-Instruction Single-Data (MISD)     | 19   |

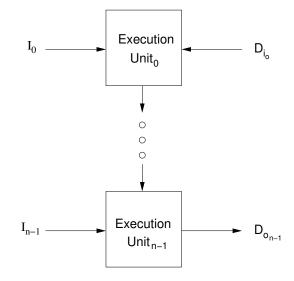

|    |      | 2.1.4  | Multiple-Instruction Multiple-Data (MIMD)   | 20   |

|    | 2.2  | CUDA   | Overview                                    | 21   |

|    | 2.3  | CUDA   | Hardware Architecture Details               | 21   |

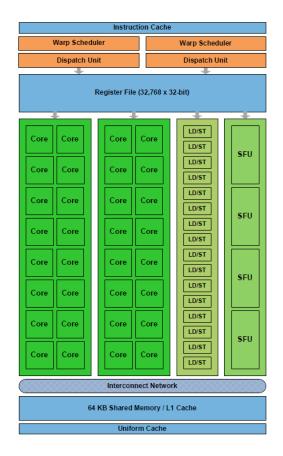

|    |      | 2.3.1  | Streaming Multiprocessors                   | 22   |

|    |      | 2.3.2  | CUDA Memories                               | 26   |

|    | 2.4  | CUDA   | Programming Model Details                   | 31   |

# Page

|   |     | 2.4.1  | Core Software Instrinsics                                                 | 31 |

|---|-----|--------|---------------------------------------------------------------------------|----|

|   |     | 2.4.2  | Occupancy                                                                 | 35 |

|   | 2.5 | Chapt  | er Summary                                                                | 36 |

| 3 |     |        | DA: A GPU-BASED DEADLOCK DETECTION<br>HM FOR SINGLE UNIT RESOURCE SYSTEMS | 37 |

|   | 3.1 | Introd | luction                                                                   | 37 |

|   | 3.2 | Backg  | round                                                                     | 37 |

|   |     | 3.2.1  | Assumptions and Terms                                                     | 37 |

|   |     | 3.2.2  | Underlying Theory of OSDDA                                                | 38 |

|   | 3.3 | GPU-   | OSDDA Design                                                              | 42 |

|   |     | 3.3.1  | Introduction                                                              | 42 |

|   |     | 3.3.2  | Bit-Vector Design                                                         | 42 |

|   |     | 3.3.3  | Handling a Resource Request Granted Event                                 | 46 |

|   |     | 3.3.4  | Handling a Resource Request Blocked Event                                 | 48 |

|   |     | 3.3.5  | Handling a Resource Release Event                                         | 52 |

|   |     | 3.3.6  | Supplementary Kernels                                                     | 56 |

|   | 3.4 | Exper  | imentation and Results                                                    | 58 |

|   | 3.5 | Conclu | usion                                                                     | 60 |

| 4 |     |        | DA: A GPU-BASED DEADLOCK DETECTION<br>HM FOR MULTI-UNIT RESOURCE SYSTEMS  | 61 |

|   | 4.1 | Introd | luction                                                                   | 61 |

|   | 4.2 | Backg  | round                                                                     | 61 |

|   |     | 4.2.1  | Assumptions and Terms                                                     | 61 |

|   |     | 4.2.2  | Underlying Theory of LMDDA                                                | 62 |

|   | 4.3 | GPU-   | LMDDA Design                                                              | 68 |

|   |     | 4.3.1  | Introduction                                                              | 68 |

|   |     | 4.3.2  | Bit-Vector Design                                                         | 69 |

|   |     | 4.3.3  | Handling a Resource Request Granted Event                                 | 74 |

|   |     | 4.3.4  | Handling a Resource Request Blocked Event                                 | 76 |

# Page

|    |      | 4.3.5  | Handling a Resource Release Event          | 83  |

|----|------|--------|--------------------------------------------|-----|

|    |      | 4.3.6  | Supplementary Kernels                      | 93  |

|    | 4.4  | Experi | imentation and Results                     | 94  |

|    | 4.5  | Conclu | asion                                      | 97  |

| 5  |      |        | A GPU-BASED DEADLOCK AVOIDANCE<br>IM       | 98  |

|    | 5.1  | Introd | uction                                     | 98  |

|    | 5.2  | Backg  | round                                      | 99  |

|    |      | 5.2.1  | Assumptions and Terms                      | 99  |

|    |      | 5.2.2  | Underlying Theory of PBA                   | 99  |

|    |      | 5.2.3  | Computations of PBA and the H-Safety Check | 100 |

|    | 5.3  | GPU-I  | PBA Design                                 | 103 |

|    |      | 5.3.1  | Introduction                               | 103 |

|    |      | 5.3.2  | Handling a Resource Request                | 103 |

|    |      | 5.3.3  | Handling a Resource Release                | 118 |

|    | 5.4  | Experi | imentation and Results                     | 120 |

|    | 5.5  | Conclu | asion                                      | 123 |

| 6  | SUM  | IMARY  | ,<br>                                      | 125 |

|    | 6.1  | Thesis | Conclusions                                | 125 |

|    | 6.2  | Future | e Work                                     | 126 |

| LI | ST O | F REF  | ERENCES                                    | 129 |

## LIST OF TABLES

| Tab | le                                                                         | Page |

|-----|----------------------------------------------------------------------------|------|

| 2.1 | Flynn's Taxonomy                                                           | 16   |

| 2.2 | CUDA Device Memory Features                                                | 26   |

| 2.3 | CUDA Memory Access Times                                                   | 26   |

| 3.1 | Common variables used throughout GPU-OSDDA                                 | 43   |

| 3.2 | Run-Time/Speedup of CPU-OSDDA and GPU-OSDDA (Initial)                      | 59   |

| 3.3 | Run-Time/Speedup of CPU-OSDDA and GPU-OSDDA (Bit-Packed) $% \mathcal{A}$ . | 59   |

| 4.1 | Common variables used throughout GPU-LMDDA                                 | 70   |

| 4.2 | Event structure in GPU-LMDDA                                               | 71   |

| 4.3 | Run-Time/Speedup of CPU-LMDDA and GPU-LMDDA (Initial) $\ . \ .$ .          | 96   |

| 4.4 | Run-Time/Speedup of CPU-LMDDA and GPU-LMDDA (Bit-Packed)                   | 96   |

| 5.1 | Data Structures for GPU-PBA                                                | 100  |

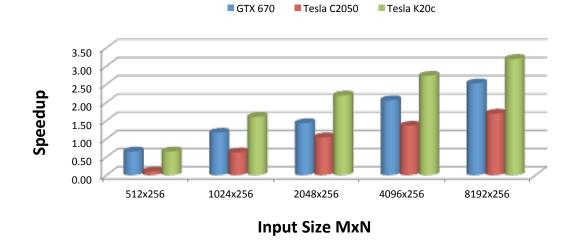

| 5.2 | Run-Time/Speedup of CPU-PBA and GPU-PBA (256 Resources)                    | 121  |

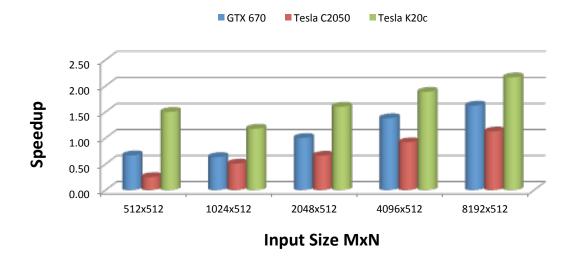

| 5.3 | Run-Time/Speedup of CPU-PBA and GPU-PBA (512 Resources)                    | 121  |

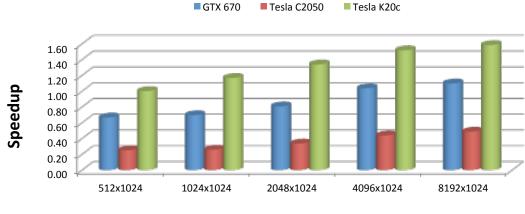

| 5.4 | Run-Time/Speedup of CPU-PBA and GPU-PBA (1024 Resources)                   | 122  |

## LIST OF FIGURES

| Figu | re                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Page |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

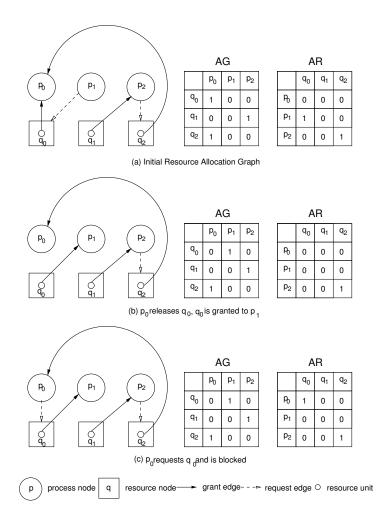

| 1.1  | A 3 $\times$ 3 RAG incurring resource events                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7    |

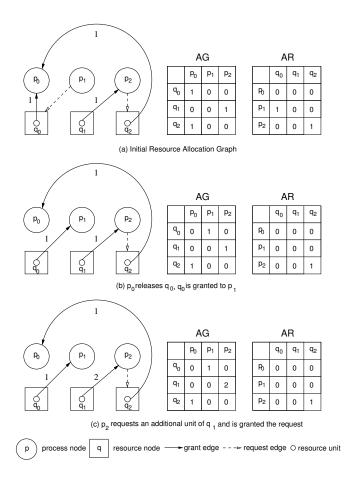

| 1.2  | A 3 $\times$ 3 Weighted RAG incurring resource events $\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hf$ | 8    |

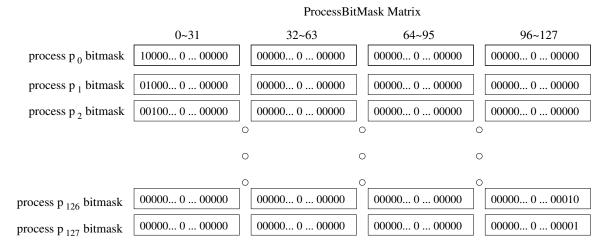

| 1.3  | The process bit-mask matrix represented with bit-vectors                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 10   |

| 2.1  | SISD Execution Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 17   |

| 2.2  | SIMD Execution Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 18   |

| 2.3  | MISD Execution Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 19   |

| 2.4  | MIMD Execution Model                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 20   |

| 2.5  | Fermi SM Block Diagram (Courtesy of Nvidia)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 22   |

| 2.6  | Kepler SMX Block Diagram (Courtesy of Nvidia)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 23   |

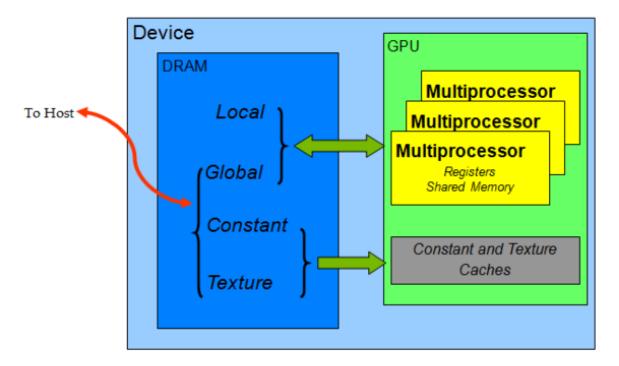

| 2.7  | CUDA Memory Spaces (Courtesy of Nvidia)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 27   |

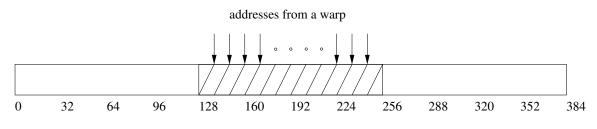

| 2.8  | Coalesced memory accesses in a single 128-byte L1-Cache line $\ . \ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 28   |

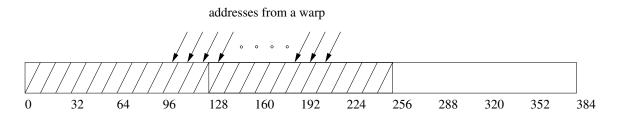

| 2.9  | Unaligned sequential addressing in two 128-byte L1-Cache lines $\ . \ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 29   |

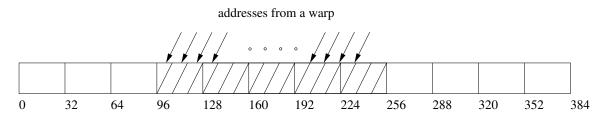

| 2.10 | Misaligned sequential addressing in five 32-byte L2-Cache lines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 29   |

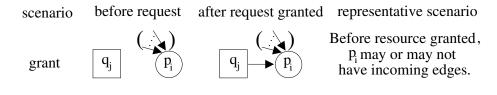

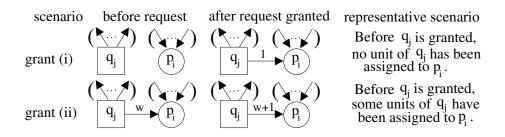

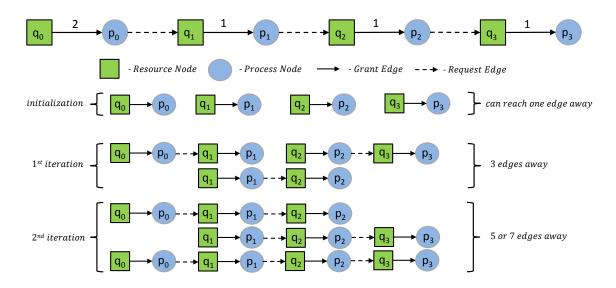

| 3.1  | Scenarios of resource request granted events (GPU-OSDDA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 39   |

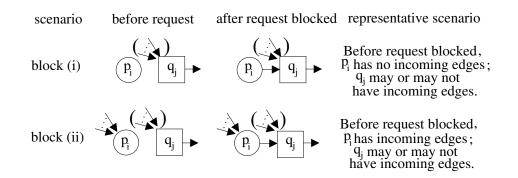

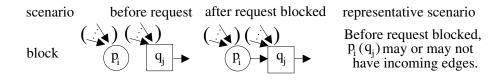

| 3.2  | Scenarios of <i>resource request blocked</i> events (GPU-OSDDA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 39   |

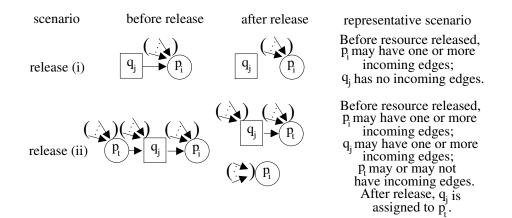

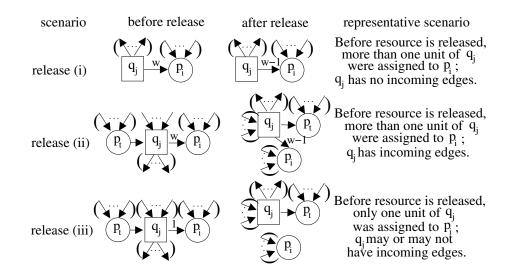

| 3.3  | Scenarios of <i>resource release</i> events (GPU-OSDDA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 40   |

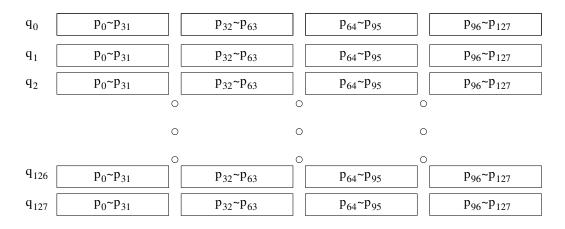

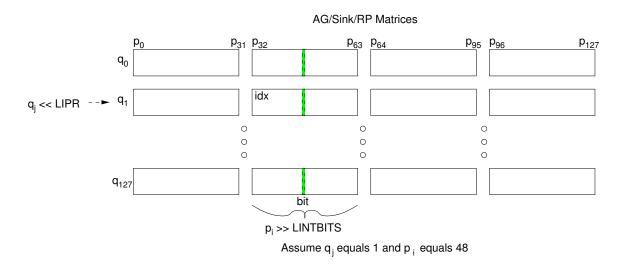

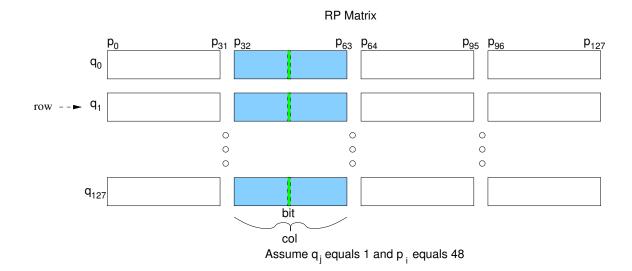

| 3.4  | A 128x128 Bit-Vector Adjacency Matrix (GPU-OSDDA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 43   |

| 3.5  | Computation to update AG/Sink/RP Matrix (Resource Granted) $\ . \ .$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 46   |

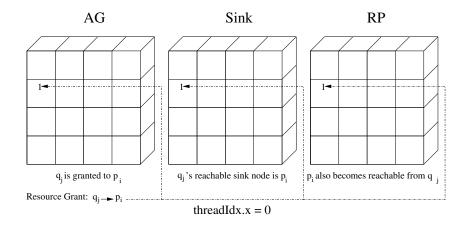

| 3.6  | Resource Request Granted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 47   |

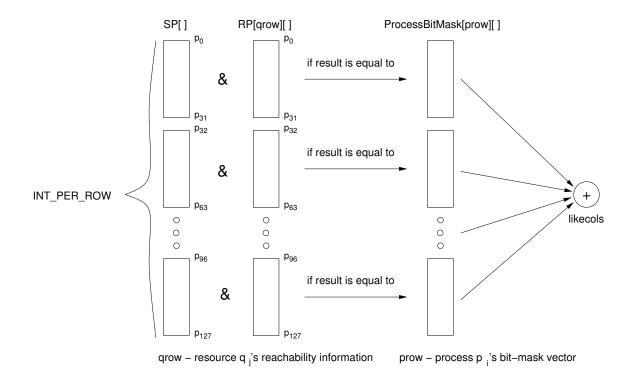

| 3.7  | Calculation to determine reachability in RAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 51   |

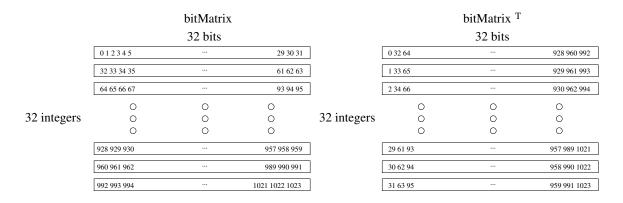

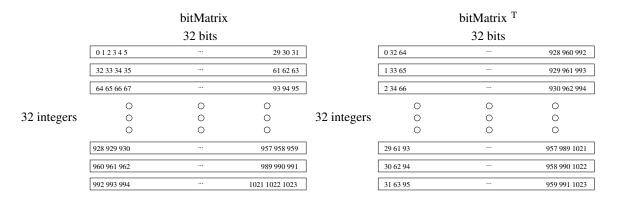

| 3.8  | Bit-Matrix Transpose in GPU-OSDDA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 56   |

| 3.9  | Transpose of bit-matrix tiles in GPU-OSDDA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 57   |

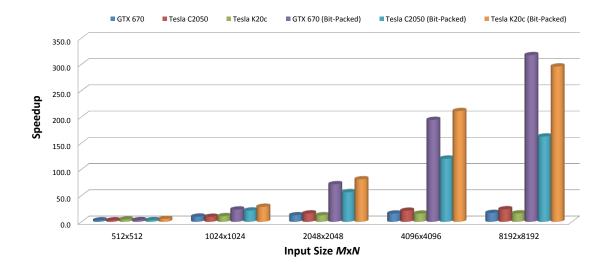

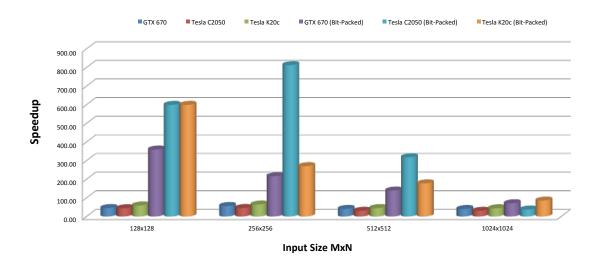

| 3.10 | GPU-OSDDA Speedup                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60   |

| 4.1  | Scenarios of <i>resource request granted</i> events (GPU-LMDDA)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 63   |

| Figu | re                                                                                   | Page |

|------|--------------------------------------------------------------------------------------|------|

| 4.2  | Scenarios of <i>resource request blocked</i> events (GPU-LMDDA)                      | 64   |

| 4.3  | Scenarios of <i>resource release</i> events (GPU-LMDDA)                              | 65   |

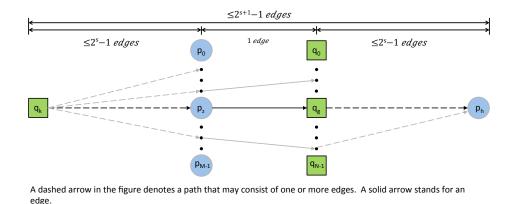

| 4.4  | Example of the node hopping mechanism finding reachable processes .                  | 66   |

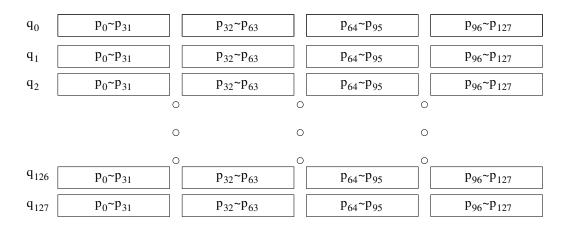

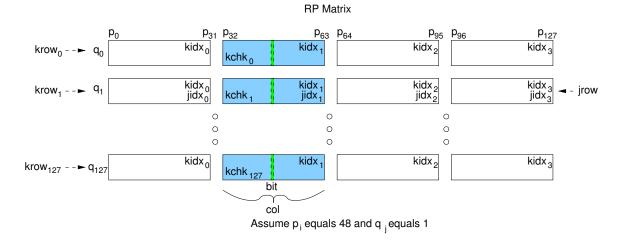

| 4.5  | A 128x128 Bit-Vector Adjacency Matrix (GPU-LMDDA)                                    | 70   |

| 4.6  | Illustration of computation to update RP Matrix (Resource Granted) .                 | 75   |

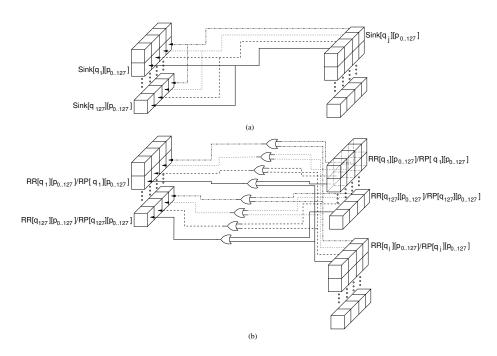

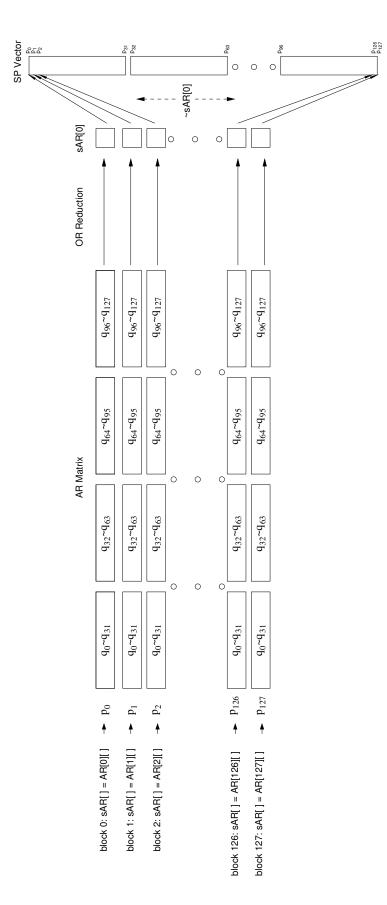

| 4.7  | Illustration of finding sink process nodes                                           | 77   |

| 4.8  | Illustration of computation to check for deadlock                                    | 80   |

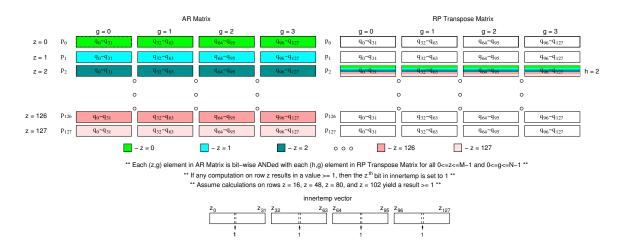

| 4.9  | Illustration of computation to update RP Matrix (Resource Blocked) .                 | 81   |

| 4.10 | Illustration of computation to find waiting processes                                | 85   |

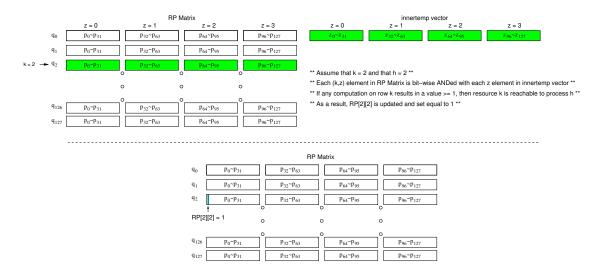

| 4.11 | Illustration of RC for $RP[k][h]$ for a single iteration                             | 88   |

| 4.12 | Illustration of connecting process $z$ to process $h$ (RC) $\hdots$                  | 91   |

| 4.13 | Illustration of connecting resource $k$ to process $h\ (RC)\ \ldots\ \ldots\ \ldots$ | 92   |

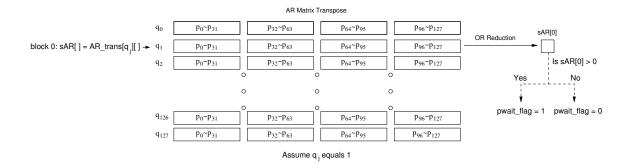

| 4.14 | Bit-Matrix Transpose in GPU-LMDDA                                                    | 93   |

| 4.15 | Transpose of bit-matrix tiles in GPU-LMDDA                                           | 94   |

| 4.16 | GPU-LMDDA Speedup                                                                    | 96   |

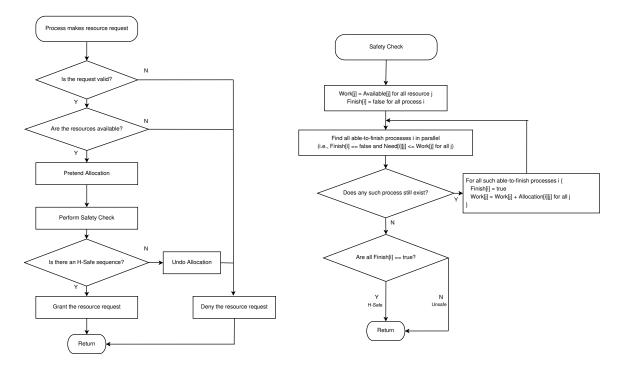

| 5.1  | PBA Process Flowchart                                                                | 101  |

| 5.2  | GPU-PBA Speedup w/ 256 Resources                                                     | 122  |

| 5.3  | GPU-PBA Speedup w/ 512 Resources                                                     | 123  |

| 5.4  | GPU-PBA Speedup w/ 1024 Resources                                                    | 123  |

viii

#### ABSTRACT

Abell, Stephen W. MSECE, Purdue University, August 2013. Parallel Acceleration of Deadlock Detection and Avoidance Algorithms on GPUs. Major Professor: Dr. John Jaehwan Lee.

Current mainstream computing systems have become increasingly complex. Most of which have Central Processing Units (CPUs) that invoke multiple threads for their computing tasks. The growing issue with these systems is resource contention and with resource contention comes the risk of encountering a deadlock status in the system. Various software and hardware approaches exist that implement deadlock detection/avoidance techniques; however, they lack either the speed or problem size capability needed for real-time systems.

The research conducted for this thesis aims to resolve issues present in past approaches by converging the two platforms (software and hardware) by means of the Graphics Processing Unit (GPU). Presented in this thesis are two GPU-based dead-lock detection algorithms and one GPU-based deadlock avoidance algorithm. These GPU-based algorithms are: (i) GPU-OSDDA: A GPU-based Single Unit Resource Deadlock Detection Algorithm, (ii) GPU-LMDDA: A GPU-based Multi-Unit Resource Deadlock Detection Algorithm, and (iii) GPU-PBA: A GPU-based Deadlock Avoidance Algorithm.

Both GPU-OSDDA and GPU-LMDDA utilize the Resource Allocation Graph (RAG) to represent resource allocation status in the system. However, the RAG is represented using integer-length bit-vectors. The advantages brought forth by this approach are plenty: (i) less memory required for algorithm matrices, (ii) 32 computations performed per instruction (in most cases), and (iii) allows our algorithms to handle large numbers of processes and resources. The deadlock detection algorithms

also require minimal interaction with the CPU by implementing matrix storage and algorithm computations on the GPU, thus providing an interactive service type of behavior. As a result of this approach, both algorithms were able to achieve speedups over two orders of magnitude higher than their serial CPU implementations (3.17-317.42x for GPU-OSDDA and 37.17-812.50x for GPU-LMDDA). Lastly, GPU-PBA is the first parallel deadlock avoidance algorithm implemented on the GPU. While it does not achieve two orders of magnitude speedup over its CPU implementation, it does provide a platform for future deadlock avoidance research for the GPU.

## **1 INTRODUCTION**

#### 1.1 Problem Statement

Modern computing platforms have grown increasingly complex over the past decade. The advent of multi-cored and multi-threaded Central Processing Units (CPUs) have reintroduced a common problem regarding resource contention, deadlock. In the past, many software-based deadlock detection/avoidance approaches were devised that handled both single-unit and multi-unit request systems. The issue with these deadlock detection solutions was that they were not capable of determining events that led to deadlock in a deterministic and expedited manner. These solutions typically had poor run-time complexities on the order of  $\mathcal{O}(M \times N)$ ,  $\mathcal{O}(N^2)$ , or  $\mathcal{O}(N^3)$ , where M and N are process and resource counts, respectively.

As a result, researchers began developing hardware solutions to the deadlock detection problem. The key advantage to these hardware techniques was their ability to exploit parallelism in the Resource Allocation Graph (RAG) while performing deadlock detection computations. Since these parallel computations took place in hardware, the algorithms devised had low run-time complexities, i.e.,  $\mathcal{O}(log_2(min(M,N)))$ and  $\mathcal{O}(1)$ . The only issue with applying these hardware solutions to real world systems was the inability to handle increasingly large numbers of processes and resources. By increasing the number of processes and resources, the size of the hardware solutions would grow polynomially, as would their cost.

Furthermore, in the past 7 years their has been a paradigm shift in the way researchers, scientists, and software engineers handle parallel computations. Graphics card manufacturers (Nvidia and ATI) realized, with the help of the hardware and software communities, that their massively parallel hardware platforms, or Graphics Processing Units (GPUs), could be used as a large vector processor. Nvidia then created their Compute Unified Device Architecture (CUDA) framework. This development has given researchers the capabilities of massively parallel processors in a discrete package that fits into most common personal computers (PC). This leads to the research conducted for this thesis. By thinking about the previously developed hardware algorithms in terms of software, it was hypothesized that those same algorithms could be developed for the modern GPU. As a result, several deadlock detection/avoidance algorithms could be utilized for real world systems that would yield large speedups with respect to a CPU implementation. Since the GPU is a secondary device to the CPU, limited interaction with the CPU would be required so that it may continue performing its normal tasking.

#### 1.2 Terminology

This section defines terms and theorems in the CUDA framework, deadlock detection and graph theory domains that are applicable to this thesis.

### 1.2.1 Definitions in the CUDA Framework

**Definition 1.2.1** API is the acronym for an Application Programming Interface.

**Definition 1.2.2** CUDA is the acronym for Nvidia's Compute Unified Device Architecture. The CUDA framework consists of both the hardware architecture and the parallel programming model provided by Nvidia.

**Definition 1.2.3** GPU is the acronym for a Graphics Processing Unit.

**Definition 1.2.4** A Streaming Multiprocessor (SM) is a multi-cored processing unit on the GPU.

**Definition 1.2.5** A Stream Processor (SP) is one of many execution units on the SM of a GPU.

**Definition 1.2.6** A thread is a single path of execution that takes place on an SP inside of an SM.

**Definition 1.2.7** A block is a grouping of threads that are scheduled on multiple SP's inside of a single SM.

**Definition 1.2.8** A grid consists of many groupings of thread blocks that can be distributed across many SP's of many SM's.

**Definition 1.2.9** A warp is the lowest level grouping of threads that are scheduled on the GPU. The warp consists of 32 threads.

**Definition 1.2.10** A kernel is the programmer derived software function to be launched on the GPU.

### 1.2.2 Definitions in the Deadlock Domain

**Definition 1.2.11** Deadlock is a situation in which a set of processes are permanently blocked for competing for system resources or communicating with each other. The following are necessary and sufficient conditions for deadlock to occur:

- **Condition 1** Mutual exclusion condition: a resource (unit) is either assigned to one process or it is available.

- Condition 2 Hold and wait condition: processes already holding resources may request additional resources.

- **Condition 3** No preemption condition: only a process holding a resource can release it.

- **Condition 4** Circular wait condition: two or more processes form a circular chain where each process waits for a resource that the next process in the chain holds.

**Definition 1.2.12** Deadlock detection is a way of dealing with deadlock that tracks resource allocation and process states to find deadlock, and rolls back and restarts one or more of the processes in order to remove the deadlock.

**Definition 1.2.13** A single-unit resource is a resource that serves at most one process at a time. This means while a single-unit resource is serving a process, all other processes requesting this resource must wait.

**Definition 1.2.14** A multi-unit resource is a resource that can serve one or more processes at the same time. All processes are served with the same or similar functionality.

**Definition 1.2.15** An active process is a process which has no outgoing edge (no pending resource request) but may have incoming edges (granted resources).

**Definition 1.2.16** A system is in an expedient state if any request for available units is granted immediately.

**Definition 1.2.17** A single-unit request system is a system in which a process may request only one unit at a time, and thus has at most one outstanding request for a single unit of some resource.

**Definition 1.2.18** An H-Safe sequence is an enumeration  $p_1, p_2, \ldots, p_N$  of all processes in the system, such that for each  $i=1, 2, \ldots, N$ , the resources that  $p_i$  may request are a subset of the union of resources that are currently available and resources currently held by  $p_1, p_2, \ldots, p_{i-1}$  [1] [2].

**Definition 1.2.19** An H-Safe state exists if and only if there exists an H-Safe sequence  $p_1, p_2, \ldots, p_N$ . If there is no H-Safe sequence, the system is in an H-Unsafe state [2].

#### 1.2.3 Definitions in the Graph Theory Domain

In this section, we first describe the Resource Allocation Graph (RAG), followed by definitions from graph theory that are used throughout the algorithms in this thesis.

**Definition 1.2.20** Let  $P = \{p_1, p_2, \ldots, p_M\}$  be a set of M requestors or processes that may request and/or hold a number of resources at any given time.

**Definition 1.2.21** Let  $Q = \{q_1, q_2, \ldots, q_N\}$  be a set of N resources that provide specific functions usable by processes. Each resource consists of a fixed number (one or more) of units to supply.

**Definition 1.2.22** Let the set of nodes V be  $P \cup Q$ , which is divided into two disjoint subsets P and Q such that  $P \cap Q = \emptyset$ . Another notation for the set of nodes is,  $V = \{v_1, v_2, \ldots, v_l\}.$

**Definition 1.2.23** Let G be a set of grant edges. Let an ordered pair  $(q_j, p_i)$  be a grant edge where the first node is a resource  $q_j \in Q$ , the second node is a process  $p_i \in P$ , and  $q_j$  has been granted to  $p_i$ . Thus, a set of grant edges G can be written as  $G = \{(q_j, p_i) | j \in \{1, 2, ..., n\}, i \in \{1, 2, ..., m\}$ , and resource  $q_j$  has been granted to process  $p_i\}$ . An ordered pair  $(q_j, p_i)$  can also be represented by  $q_j \to p_i$ .

**Definition 1.2.24** Let R be the set of request edges. Let an ordered pair  $(p_i, q_j)$  be a request edge where the first node is a process  $p_i \in P$ , the second node is a resource  $q_j \in Q$ , and  $p_i$  has requested  $q_j$  but has not yet acquired it. Thus, a set of request edges R can be written as  $R = \{(p_i, q_j) | i \in \{1, 2, ..., m\}, j \in \{1, 2, ..., n\}$ , and process  $p_i$  is blocked for requesting resource  $q_j\}$ . An ordered pair  $(p_i, q_j)$  can also be represented by  $p_i \to q_j$ .

**Definition 1.2.25** Let the set of edges E be  $R \cup G$ . Another notation used is,  $E = \{e_1, e_2, \ldots, e_h\}.$  **Definition 1.2.26** A particular resource allocation situation in a given system with processes and resources can be abstracted by a Resource Allocation Graph (RAG). A RAG is a directed graph  $\theta = \{V, E\}$ , such that V is a non-empty set of nodes defined in Definition 1.2.22, and E is a set of edges defined in Definition 1.2.25. The RAG is also split into two separate adjacency matrices: Adjacency Request (AR) and Adjacency Grant (AG), which hold the resource request and grant information, respectively. In this thesis we assume a RAG handles single-unit resources (see Definition 1.2.13).

**Definition 1.2.27** The Adjacency Request matrix is a component of the RAG. It contains request edges (see Definition 1.2.24) that denote that a process  $p_i$  has requested a resource  $q_j$ .

**Definition 1.2.28** The Adjacency Grant matrix is the second component of the RAG. It contains grant edges (see Definition 1.2.23) that denote that a resource  $q_j$  has been granted to process  $p_i$ .

Summary of AG/AR for RAG Handling Single-Unit Resources

$$AG[j][i] = \begin{cases} 1 & \text{if } \exists q_j \to p_i, \\ 0 & \text{otherwise.} \end{cases} \qquad AR[i][j] = \begin{cases} 1 & \text{if } \exists p_i \to q_j, \\ 0 & \text{otherwise.} \end{cases}$$

RAG Example

Figure 1.1(a) shows an example RAG of a  $3 \times 3$  system consisting of three processes  $(p_0, p_1, p_2)$  and three resources  $(q_0, q_1, q_2)$ . Since we assume a RAG handles a singleunit system, each resource has one unit and grant edge weights do not exceed 1. Accompanying the RAG in Figure 1.1 are the associated adjacency matrices AG and AR to reflect resource allocation status in the system.