# PURDUE UNIVERSITY GRADUATE SCHOOL

### **Thesis/Dissertation Acceptance**

| This is to certify that the thesis/dissertation prepared                                                                                                                                        |                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|

| By Nathaniel William Bruce                                                                                                                                                                      |                                         |

| Entitled AUTOMATIC MODELING AND SIMULATION OF NETWORKED                                                                                                                                         | D COMPONENTS                            |

| For the degree of Master of Science in Electrical and Compute                                                                                                                                   | er Engineering                          |

| Is approved by the final examining committee:                                                                                                                                                   |                                         |

| Sarah Koskie                                                                                                                                                                                    |                                         |

| Chair                                                                                                                                                                                           |                                         |

| Yaobin Chen                                                                                                                                                                                     |                                         |

| Lingxi Li                                                                                                                                                                                       |                                         |

| To the best of my knowledge and as understood by the student in Copyright Disclaimer (Graduate School Form 20), this thesis/di Purdue University's "Policy on Integrity in Research" and the us | ssertation adheres to the provisions of |

| Approved by Major Professor(s): Sarah Koskie                                                                                                                                                    |                                         |

| Approved by: Yaobin Chen                                                                                                                                                                        | 04/13/2011                              |

| Head of the Graduate Program                                                                                                                                                                    | Date                                    |

## PURDUE UNIVERSITY GRADUATE SCHOOL

## **Research Integrity and Copyright Disclaimer**

| Title of Thesis/Disser                          | rtation:                                                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AUTOMATIC MODE                                  | LING AND SIMULATION OF NETWORKED COMPONENTS                                                                                                                                                                                                                                                                                          |

|                                                 |                                                                                                                                                                                                                                                                                                                                      |

| For the degree of                               | Master of Science in Electrical and Computer Engineering                                                                                                                                                                                                                                                                             |

|                                                 | reparation of this thesis, I have observed the provisions of <i>Purdue University Jum No. C-22</i> , September 6, 1991, <i>Policy on Integrity in Research.</i> *                                                                                                                                                                    |

|                                                 | this work is free of plagiarism and all materials appearing in this we been properly quoted and attributed.                                                                                                                                                                                                                          |

| United States' copyrig<br>my use of their work, | righted material incorporated into this thesis/dissertation is in compliance with the ght law and that I have received written permission from the copyright owners for which is beyond the scope of the law. I agree to indemnify and save harmless om any and all claims that may be asserted or that may arise from any copyright |

| Nathaniel William Bru                           | uce                                                                                                                                                                                                                                                                                                                                  |

| Printed Name and Signatu                        | re of Candidate                                                                                                                                                                                                                                                                                                                      |

| 04/13/2011                                      |                                                                                                                                                                                                                                                                                                                                      |

| Date (month/day/year)                           |                                                                                                                                                                                                                                                                                                                                      |

|                                                 |                                                                                                                                                                                                                                                                                                                                      |

<sup>\*</sup>Located at http://www.purdue.edu/policies/pages/teach\_res\_outreach/c\_22.html

# AUTOMATIC MODELING AND SIMULATION OF NETWORKED COMPONENTS

A Thesis

Submitted to the Faculty

of

Purdue University

by

Nathaniel William Bruce

In Partial Fulfillment of the

Requirements for the Degree

of

Master of Science in Electrical and Computer Engineering

May 2011

Purdue University

Indianapolis, Indiana

#### **ACKNOWLEDGMENTS**

I would like to acknowledge all of the many people who helped make this work possible. In particular, special recognition is given to my advisor, Dr. Sarah Koskie, who has helped greatly in project work and thesis preparation.

Acknowledgment should also be given to my committee members, Dr. Lingxi Li and Dr. Yaobin Chen who provided advice and suggestions throughout the development of this thesis.

Thank you to my co-workers Dr. Robert DuFour, Ray Prieto, Heather Wisdom, Hari Krishna, and Kreg Sweeney for their support and thank you to my family and friends.

Thanks, also, to the graduate coordinator, Valerie Lim Diemer, department secretary, Sherrie Tucker, and other administrative staff who helped along the way.

#### TABLE OF CONTENTS

|    |                                               |                                                                                            |                                                                                                                                                                                                          | Page                                                           |

|----|-----------------------------------------------|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| LI | ST O                                          | F TAB                                                                                      | LES                                                                                                                                                                                                      | v                                                              |

| LI | ST O                                          | F FIGU                                                                                     | JRES                                                                                                                                                                                                     | vi                                                             |

| Al | BBRE                                          | EVIATI                                                                                     | ONS                                                                                                                                                                                                      | viii                                                           |

| Al | BSTR                                          | ACT                                                                                        |                                                                                                                                                                                                          | ix                                                             |

| 1  | INT:<br>1.1<br>1.2<br>1.3<br>1.4              | Proble<br>Previo<br>Innova                                                                 | CTION                                                                                                                                                                                                    | 1<br>3<br>5<br>6                                               |

| 2  | BAC<br>2.1<br>2.2<br>2.3                      | Comm                                                                                       | PUND                                                                                                                                                                                                     | 7<br>7<br>8<br>11                                              |

| 3  | IMP<br>3.1<br>3.2<br>3.3<br>3.4<br>3.5<br>3.6 | Oververstep 1 Step 2 Step 3 Step 4                                                         | NTATION  iew  : Record Communications Trace  : Identify Relevant Signals  : Synthesize FSM  : Manually Modify FSM  : Simulate FSM In Real-Time                                                           | 18<br>18<br>21<br>23<br>26<br>37<br>39                         |

| 4  | RES<br>4.1<br>4.2<br>4.3<br>4.4<br>4.5        | Practi<br>Synthe<br>4.2.1<br>4.2.2<br>4.2.3<br>4.2.4<br>Simula<br>Model<br>Discus<br>4.5.1 | cal Evaluation of Finite State Machines esis Results  A Controller And Its Supervisor Controller with Increased Complexity Cruise Control Other Applications ation Results ing Time Synthesis Variations | 48<br>48<br>52<br>52<br>57<br>63<br>68<br>70<br>72<br>74<br>76 |

|    |                                               | 4.5.1 $4.5.2$                                                                              | Simulation Variations                                                                                                                                                                                    |                                                                |

|                                              | Page |

|----------------------------------------------|------|

| 5 CONCLUSION                                 | 78   |

| LIST OF REFERENCES                           | 79   |

| APPENDIX: SOURCE CODE (in supplemental file) |      |

#### LIST OF TABLES

| Tab | le                                                                     | Page |

|-----|------------------------------------------------------------------------|------|

| 3.1 | Recorded Messages                                                      | 23   |

| 3.2 | Recorded Messages with Signal Values                                   | 25   |

| 4.1 | Event Sets for Example Automata                                        | 50   |

| 4.2 | Minimal Event Sets for Example Automata                                | 51   |

| 4.3 | Deviation Quantification Steps for $A_{few}$ Compared with $A_{ideal}$ | 56   |

| 4.4 | Comparison of Modeling Times                                           | 73   |

| 4.5 | Evaluation Results                                                     | 74   |

#### LIST OF FIGURES

| Figu | re                                                                             | Page |

|------|--------------------------------------------------------------------------------|------|

| 3.1  | Vehicle's CAN network structure and modules                                    | 19   |

| 3.2  | Interface used to identify relevant signals                                    | 24   |

| 3.3  | Class diagram showing relations between data structures used in the algorithms | 28   |

| 3.4  | Steps 1-6 for construction of the FSM example                                  | 35   |

| 3.5  | Step 7 for construction of the FSM example                                     | 36   |

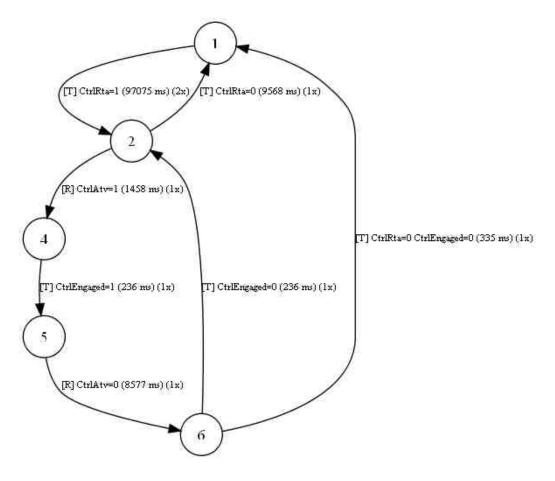

| 3.6  | Final result of the FSM synthesis (before reduction)                           | 37   |

| 3.7  | FSM after equivalency reduction                                                | 38   |

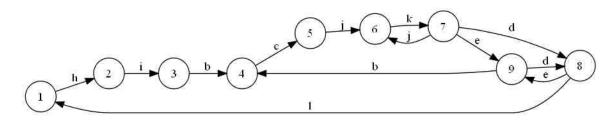

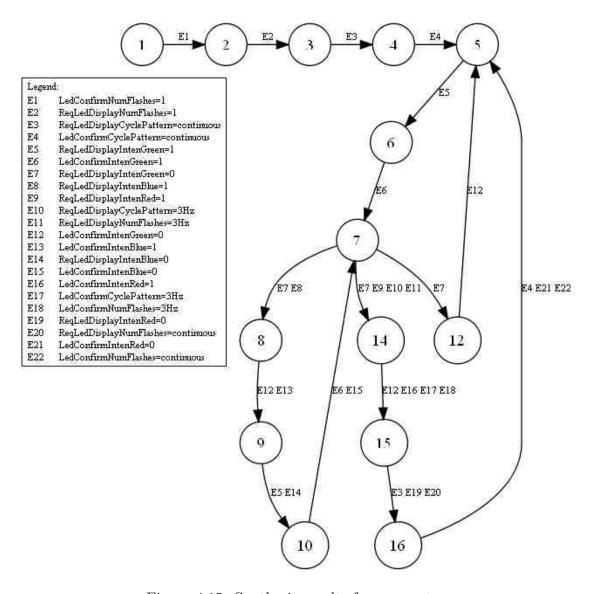

| 3.8  | Completely synthesized finite state machine                                    | 39   |

| 3.9  | FSM after manual modifications                                                 | 40   |

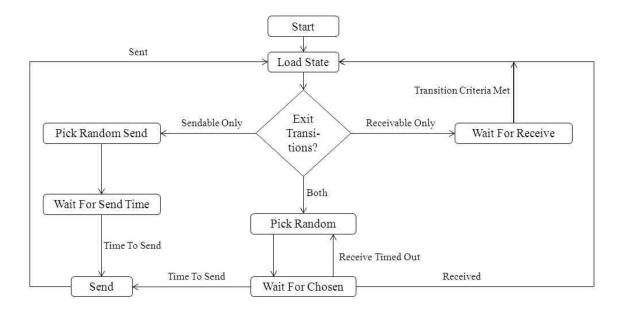

| 3.10 | Flowchart showing the modes of simulator operation                             | 41   |

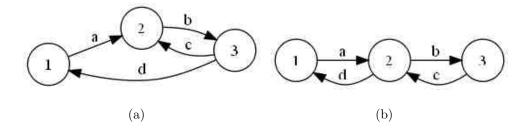

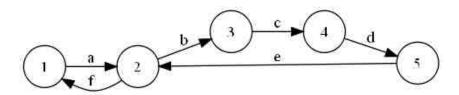

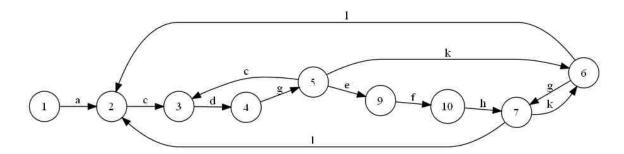

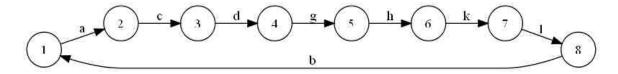

| 4.1  | Two example state diagrams for automata $G_1$ and $G_2$                        | 49   |

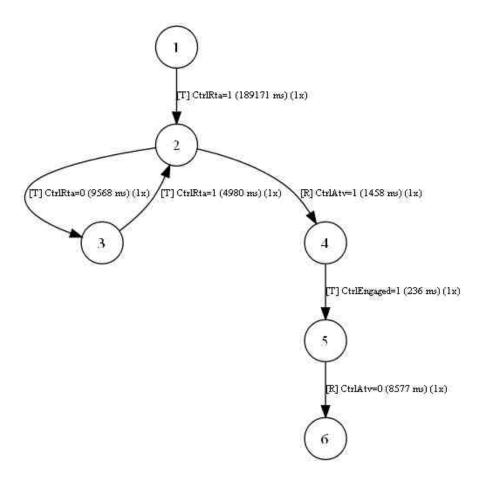

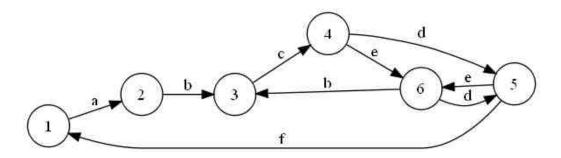

| 4.2  | Controller synthesis by hand $(A_{ideal})$                                     | 53   |

| 4.3  | Controller synthesis from data with few events $(A_{few})$                     | 53   |

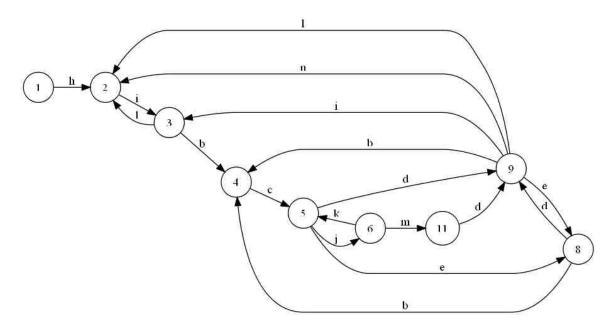

| 4.4  | Controller synthesis from data with many events $(A_{many})$                   | 54   |

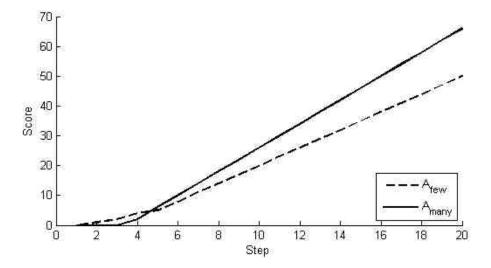

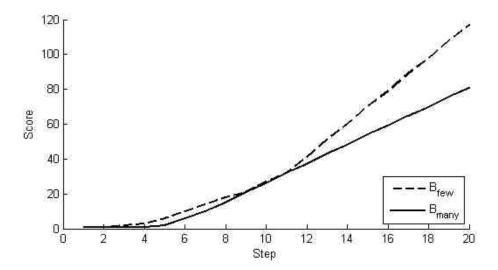

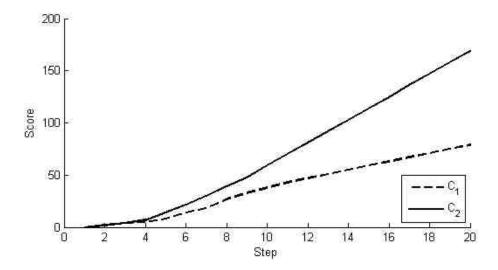

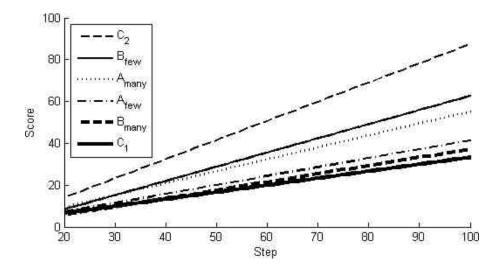

| 4.5  | Scores for $A_{ideal}$ compared with $A_{many}$ and $A_{few}$                  | 58   |

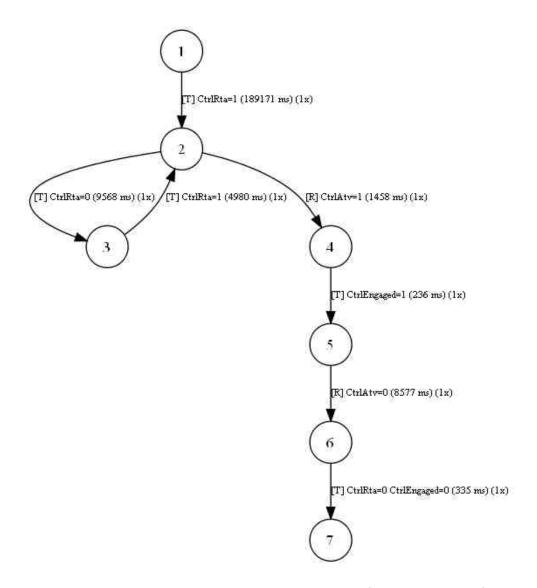

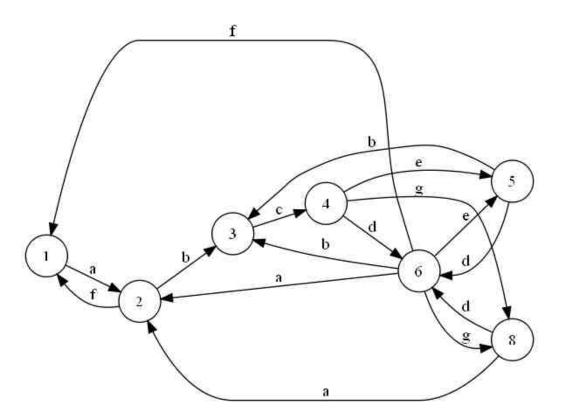

| 4.6  | Controller synthesis by hand $(B_{ideal})$                                     | 59   |

| 4.7  | Controller synthesis from data with few events $(B_{few})$                     | 59   |

| 4.8  | Controller synthesis from data with many events $(B_{many})$                   | 60   |

| 4.9  | Scores for $B_{ideal}$ compared with $B_{many}$ and $B_{few}$                  | 63   |

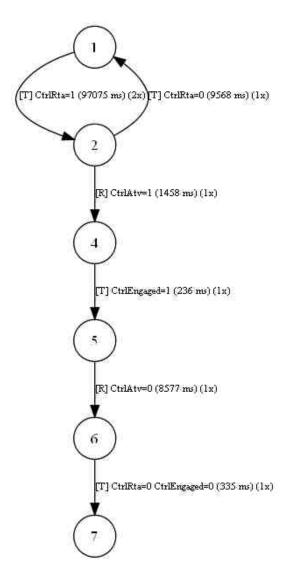

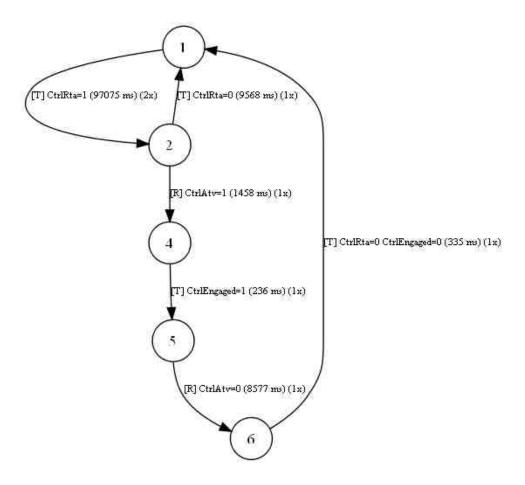

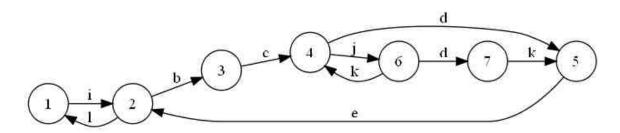

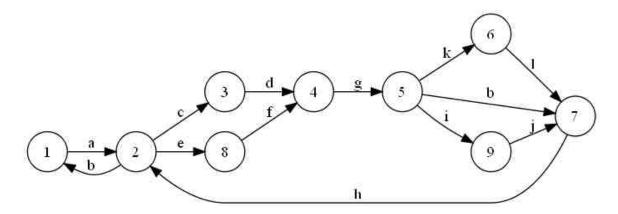

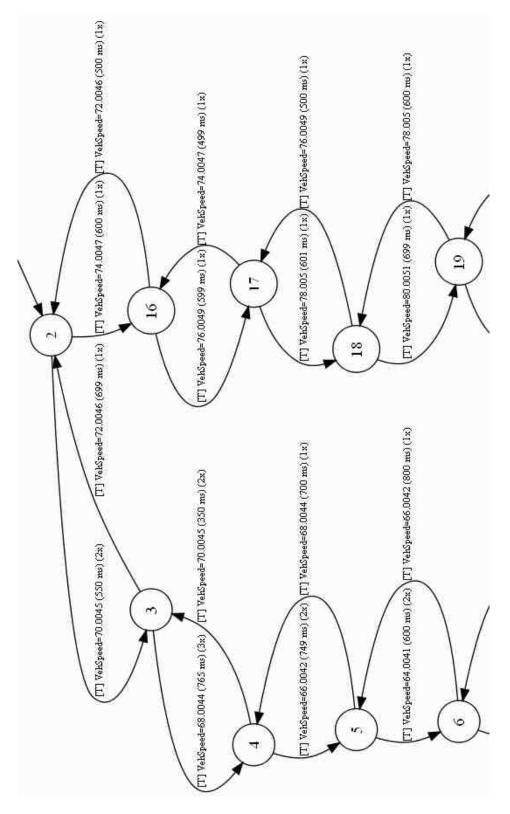

| 4.10 | Cruise control synthesis by hand $(C_{ideal})$                                 | 65   |

| 4.11 | Cruise control synthesis from first data set $(C_1)$                           | 65   |

| 4.12 | Cruise control synthesis from second data set $(C_2)$                          | 66   |

| 4.13 | Scores for $C_{ideal}$ compared with $C_1$ and $C_2$                           | 68   |

| Figure                                                               |  |   | Page |

|----------------------------------------------------------------------|--|---|------|

| 4.14 Synthesis results for vehicle speed (excerpt)                   |  | • | 69   |

| 4.15 Synthesis results for a repeater                                |  |   | 71   |

| 4.16 Comparison of all evaluated results (scaled by language size) . |  |   | 75   |

viii

#### ABBREVIATIONS

CAN Controller Area Network

CFSM Communicating Finite State Machine

CRC Cyclic Redundancy Check

DES Discrete Event System

FSM Finite State Machine

HIL Hardware-in-the-Loop

SIL Software-in-the-Loop

USAP Upper Service Access Point

#### ABSTRACT

Bruce, Nathaniel William. M.S.E.C.E., Purdue University, May 2011. Automatic Modeling and Simulation of Networked Components. Major Professor: Sarah Koskie.

Testing and verification are essential to safe and consistent products. Simulation is a widely accepted method used for verification and testing of distributed components. Generally, one of the major hurdles in using simulation is the development of detailed and accurate models. Since there are time constraints on projects, fast and effective methods of simulation model creation emerge as essential for testing.

This thesis proposes to solve these issues by presenting a method to automatically generate a simulation model and run a random walk simulation using that model. The method is automated so that a modeler spends as little time as possible creating a simulation model and the errors normally associated with manual modeling are eliminated. The simulation is automated to allow a human to focus attention on the device that should be tested.

The communications transactions between two nodes on a network are recorded as a trace file. This trace file is used to automatically generate a finite state machine model. The model can be adjusted by a designer to add missing information and then simulated in real-time using a software-in-the-loop approach.

The innovations in this thesis include adaptation of a synthesis method for use in simulation, introduction of a random simulation method, and introduction of a practical evaluation method for two finite state machines.

Test results indicate that nodes can be adequately replaced by models generated automatically by these methods. In addition, model construction time is reduced when comparing to the from scratch model creation method.

#### 1. INTRODUCTION

This chapter introduces the problem that this thesis addresses and the motivating reasons why this work is needed. Previous work in the field of automatic model generation and software- and hardware-in-the-loop simulation is reviewed. The contributions and innovations introduced in this thesis are described and the layout of the thesis is outlined.

#### 1.1 Problem and Motivation

Often in the development of complex systems, testing and validation are left out of a project plan. A working product is usually the final deliverable of a large project, so fewer resources are devoted to the verification stages. With little time spent on testing, the quality of the final product is often compromised. In all cases this is unacceptable because it can pose a risk to human safety.

Even with adequate time allocated to testing, there may arise the need for obscure equipment or a different working environment. Most products must be tested in the target environment that they will eventually be deployed in. This requires all interfacing devices to be present so that full testing can be completed. The availability of these external devices can be limited by geographical constraints and cost constraints. Despite these factors, products still need to be tested in order to verify that they are safe, reliable, and meet their design requirements.

Simulation is often a way of coping with these concerns. It is a means of replacing some of the interfacing devices in a system so that the other devices can perform without modification. By using a simulation, many of the previous concerns can be completely eliminated. The real-time hardware-in-the-loop style of simulation has the added benefit of finding flaws due to factors that may arise only in the implementation

of a design. Simulation is a popular approach to verifying a design or product by attempting to find flaws in large state spaces either with random or directed test patterns. Simulation is intuitive, easy to use, and adequate to detect early-stage errors [1]. Simulation can also be used in real-time in the target environment.

Although simulation does solve many problems associated with testing and verification, there are also disadvantages that can hinder the process. The first is that a simulation is only as good as the model. The more detailed the model, the more successfully it can replicate a device in a simulation setting. Of course, in order to add as much detail as possible to the model, more development time is required. An accurate model is key to successful simulation, but since few resources may be allocated to the testing phase of development, this severely restricts the viability of simulation for use in testing.

This thesis proposes to solve these issues by presenting a method to automatically generate a simulation model and run a simulation using that model. In order to generate a model, the presented method will use recorded data in order to inform the construction process so that an operator (*i.e.* human user of the system) can spend as little time as possible constructing a simulation model by hand. This minimization reduces the resources required for the testing phase and can also improve the simulation model by eliminating the error associated with manual construction of a model. This method is also generic and flexible enough that it can be applied in many different architectures and environments.

Some of the reasons automatic model generation methods are preferred to manual generation methods include [2]:

- 1. A simulation model typically must be continuously adapted to the current state of the project and will need to be recreated several times

- 2. Manual modeling can result in errors and cause misleading simulation results; the quality of a simulation model should not be in question

- 3. Engineering resources are often not available

4. Domain specialists for simulation and modeling are sometimes necessary for development of suitable models

The method in this thesis will use a recovery approach to model generation. In the recovery approach, the transactions between modules on a network are recorded as a communications trace, and using this trace the communications protocol can be recreated. Once this protocol is known, the information about what is received and sent by an individual node on the network can be used to construct a simulation model of that node. This model can then be improved manually and simulated in real-time using a software-in-the-loop (SIL) approach. The SIL approach is preferred to traditional simulation methods because of the trade-offs between fidelity and speed, model validation, and code reusability [3].

Some of the desirable features of a model development environment include [4]:

- 1. Modeling flexibility

- 2. Ease of model development

- 3. Fast model execution speed

- 4. Animation

- 5. Automatic model replications (multiple runs)

These features were addressed when the proposed methods were created. The synthesis methods make model development easier. The simulation methods execute models quickly. Automatic model replications can be done easily. The other two features, modeling flexibility, and animation are considered as well.

#### 1.2 Previous Work

The idea of automatic model generation is not new. Previously, artificial intelligence techniques such as automatic programming have been used to help modelers generate the code needed for simulation models, such as in [5] and [6]. Automatic

programming was used in [7] as well to help modelers write programs in higher levels of abstraction and to create a model library. The automatic programming techniques are among the most promising methods of automatic model generation, but require complete source code in order to generate models. On older projects, this is often not available.

In [8], air conditioning systems were used as a case study in automatic model generation. Models were created manually first, and then were modified and updated automatically based on behaviors of the modeled system as they were measured. This method saves some time since the models are updated automatically, but the initial time spent in creating the model is still significant.

Stochastic simulation model generation has also been suggested. In [9], the authors argue that by using stochastic generation, large quantities of models, each with slight variations, can aid in automatic model abstraction and simulation verification. Constraints are provided by a user to inform the process and several random models are generated. The drawback is that all of the models must be simulated or chosen between by a human, and despite these improvements, it is still accepted that modeling and simulation take too much time.

In [10], the authors state that creating models manually, rather than automatically, has the most benefit, but suggest that using hardware-in-the-loop (HIL) simulation will speed up the process. Adding a manual modeling step has also been used in [2], where a human provides some information in an object-oriented file which is later used to automatically generate a simulation model. A similar approach has been taken in [11] where a Petri net data structure is formed and a simulation model is created by populating the data structure.

The idea of using both hardware and software components as in HIL or SIL simulation has been widely used to accelerate the testing process. For example, real-time HIL simulation is used in [12] in order to rapidly develop digital controllers for power electronics. Maximum code reuse and minimal cost are some of the improvements that SIL methods have been shown to produce. The work in [3] proposes that the

main benefit of SIL is the combination of flexibility and low cost of a simulator with the fidelity of a hardware emulator.

Similar to the method presented in this thesis, automatic unit test generation has been done in [13]. In this method the user's operating steps are recorded, and data from the system test script is used in conjunction to generate a unit test script. This requires a system test script, something that is not necessarily readily available when the testing phase begins.

Simulation has also been done without first generating models. Given the design to test and the desired simulation coverage, the method in [1] generates a few key constraints to achieve high simulation coverage. A small number of executions are run to collect coverage holes, then analysis of control-data flow graphs is conducted to automatically extract constraints. Another approach is seen in [14] where an adaptive Markov Model is used to guide the design under test into a state where further testing can be performed. This method is a semi-formal approach, but is efficient in covering corner cases with hard-to-reach states.

Another approach has been used for automatic test generation. In [15], the state space of the design is explored by automatically generating test vectors using a divide and conquer approach. Typically state exploration is not possible because of the state explosion problem, but divide and conquer is a viable option. However, it does not reach corner cases easily and will spend valuable time unsuccessfully attempting to navigate to unreachable states.

#### 1.3 Innovations

Although there has been some significant work in the field of automatic model development and simulation, none met the criteria that this thesis addresses. The major contributions and innovations in this thesis include:

- Adaptation of the synthesis method proposed in [19], including addition of simulation data such as weighted transitions and timings, removal of a cyclical protocol requirement, and removal of potential simulation deadlock

- Introduction of a random walk simulation method

- Introduction of a practical evaluation of finite state machines to compare results

#### 1.4 Thesis Layout

Following this introduction, the rest of the chapters explain the methods of this thesis and are organized as follows.

Chapter 2 provides background on topics necessary to the implemented methods. An overview of digital communications and the controller area network are given, discrete event systems and regular expressions are introduced, and the work that the synthesis method of this thesis is based on is summarized.

Chapter 3 proposes the innovative methods of this thesis and how they are implemented. The process is outlined, then each step is discussed in the general case and specific examples are given.

Chapter 4 describes the results from applying the methods in Chapter 3. An evaluation method is given in order to evaluate two similar finite state machines. Then, five examples are shown and analyzed using the proposed methods. Qualitative results are explained for the real-time simulation method. Finally, the results and possible method variations are discussed.

Finally, Chapter 5 contains the conclusion of the thesis and describes future directions.

#### 2. BACKGROUND

This chapter serves as a primer on topics that are necessary to the proposed methods of this thesis. First, an introduction to digital communications with the Controller Area Network is presented. Then, background on discrete event systems is given, including formal languages and regular expressions for automata. Finally, work on the recovery of a communications protocol using a dynamic reverse engineering approach is discussed.

#### 2.1 Communications with the Controller Area Network

Digital communications provide a foundation for the implementation of the methods in this thesis. Although application to other platforms is possible, a communication network is the intended environment. The methods in this thesis were realized using a Controller Area Network (CAN). The following information is summarized from [16].

The CAN network is a multi-master serial bus using broadcast to transmit to all nodes. The CAN protocol allows up to 1 Mbit/s speeds and can be used in real-time systems. The data is reliable and error detection is robust. CAN is also very flexible because nodes can be added and taken away without reconfiguration.

CAN was originally developed for the automotive industry, but is now popular in many industries including marine, medical, manufacturing, and aerospace. The CAN protocol describes how information is passed between nodes or devices on a network and how the software and hardware layers are defined.

CAN is a carrier-sense multiple-access protocol meaning that each node on the bus must wait a specified period of time before attempting to send a message. CAN also supports collision detection and message priority arbitration, meaning that collisions are resolved through bitwise arbitration based on a predetermined identifier field of each message. A higher priority identifier always wins bus access. Associating message priority with the identifier is a feature that makes CAN useful in a real-time environment.

In the protocol, there are four message types that can be transmitted. The data frame is the most common. It contains an 11-bit identifier, 8 bytes of data, a cyclic redundancy check (CRC) field with checksum for error detection, and an acknowledgment field.

It is often inefficient to use all 8 bytes of data for a single piece of information from a source. Instead, the bytes are packed with several pieces of information in groupings of bits called signals. These signals are predefined with bit numbers and lengths, numeric types, and resolutions in order to compactly represent the contained information. In the implementation of this thesis, a database file containing these definitions is used to standardize the signals between executions.

Also in the implementation, error frames and communication failures are assumed to be nonexistent and the communications network is treated as a working "black box" model. Naturally, if failures and errors are present in the data or at simulation time, the resulting quality of the simulation and modeling process will deteriorate accordingly.

#### 2.2 Discrete Event Systems

A discrete event system (DES) is a discrete-state, event-driven system. In other words, a DES's state evolution depends only on the occurrence of asynchronous discrete events over time. A DES is a formal language structure that will aid in the understanding of finite state machine comparison and evaluation later. The concepts in this section are summarized from [17].

In a DES, the state space is a discrete set X, as opposed to a continuous time or discrete time systems. A DES behaves in a way described in terms of event

sequences specifying the order in which various events occur over time. The actual times associated with the occurrence of these events are not part of the structure, however.

An event set E of a DES is used as an alphabet. Sequences of events from the alphabet can be formed into strings. A string can contain no events and is then called the empty string, denoted  $\epsilon$ . The length of a string s (denoted as |s|) is the number of events contained in it, including duplicates.

A language can be defined over the event set E, and represents a set of finite-length strings formed from events in E. Language is a formal structure and by itself is not easy to work with, so the automata modeling formalism is used to represent and manipulate DES languages.

A deterministic automaton, denoted G, is a six-tuple

$$G = (X, E, f, \Gamma, x_0, X_m)$$

where:

- X is the set of states

- E is the finite set of events associated with G

- $f: X \times E \to X$  is the transition function: f(x, e) = y means that there is a transition labeled by event e from state x to state y

- $\Gamma: X \to 2^E$  is the active event function (or feasible event function).  $\Gamma(x)$  is called the active (or feasible) event set and contains all events e for which f(x, e) is defined

- $x_0$  is the initial state

- $X_m \subseteq X$  is a set of marked states.

An automaton G begins operation in an initial state  $x_0$ . When an event  $e \in \Gamma(x_0) \subseteq E$  occurs, the automaton will make a transition to the state  $f(x_0, e) \in X$ .

Here, it will wait until another event occurs that takes the automaton to a new state. This process continues indefinitely until a deadlock state is reached where f(x, e) is not defined for any event e.

For convenience, f is usually extended from the domain  $X \times E$  to the domain  $X \times E^*$  in the following way:

$$f(x,\epsilon) := x$$

$$f(x,se) := f(f(x,s),e) \text{ for } s \in E^* \text{ and } e \in E$$

Languages and automata are, of course, connected. This connection can be seen by inspecting the state transition diagram of an automaton. Starting in the initial state, consider all directed paths that can be followed in the state transition diagram. This leads to the notion of the language generated by an automaton. The language generated by  $G = (X, E, f, \Gamma, x_0, X_m)$  is

$$\mathcal{L}(G) := \{ s \in E^* : f(x_0, s) \text{ is defined} \}$$

$$(2.1)$$

Starting at the initial state, the language  $\mathcal{L}(G)$  is used to represent all directed paths that can be followed in the state transition diagram, where a path is a string concatenating the event labels of transitions that make up the path. Thus, a string s is in  $\mathcal{L}(G)$  only if it corresponds directly to a possible path in the state transition diagram. This also means s is in  $\mathcal{L}(G)$  only if f is defined at  $(x_0, x)$ . Any event in E that appears in a string in  $\mathcal{L}(G)$  is called an active event. Not all events that are in E are necessarily active.

If a language can be marked by a finite-state automaton, it is said to be regular. Using the automaton structure, regular languages can be manipulated in a practical manner for use in analysis or control synthesis problems.

Since languages tend to be infinite (or at least quite large), it is necessary to describe them in a compact form. Regular expressions are typically used to compactly represent a regular language. A regular expression is defined as follows:

1.  $\emptyset$  is a regular expression denoting the empty set;  $\epsilon$  is a regular expression denoting the set  $\{\epsilon\}$ ; e is a regular expression denoting the set  $\{e\}$ , for all  $e \in E$ .

- 2. If r and s are regular expressions, then rs, (r+s),  $r^*$ ,  $s^*$  are regular expressions.

- 3. There are no regular expressions other than those constructed by applying rules 1 and 2 above a finite number of times.

The symbol "+" is used as a logical OR meaning that either event will be accepted. The \* indicates Kleene-closure of an event. The Kleene-closure of u is  $\{u\}^* = \{\epsilon, u, uu, uuu, ...\}$  and is usually written simply as  $u^*$ . When the sets  $\{u\}$  and  $\{v\}$  are concatenated into  $\{uv\}$ , it is written as uv. Expressions like  $(u+v)^*$  are used to represent sets that are too complex to write through individual element enumeration. Regular expressions provide a compact finite representation for potentially cumbersome languages with an infinite number of strings.

#### 2.3 Recovery of Communication Protocol

Previously, Saleh, Probert and Manonmani presented work on how communications protocol could be recovered through reverse engineering [19]. It is upon this foundation that the work of this thesis is built. The following section summarizes that work.

A protocol is a set of rules designed to govern how messages are exchanged in order to provide a desired service. Designing and developing communications protocols can be complex because of the varied nature of the communicating elements. Because of this, correctly recovering protocol designs is necessary to the maintenance and improvement of communication systems.

A communication system can be viewed as a "black box" providing services to a number of users. The users can access the system through distributed upper service access points (USAPs). To create the service, the communication system is separated into protocol entities which can exchange private messages that are not observable to users at the USAPs. A communication protocol describes the behavior of the entities which each service a particular access point.

In the past, formal methods have not always been used when designing protocols, and there is a significant amount of existing software that has been developed using informal approaches to protocol engineering. Typically this software does not have formally documented service definitions and its design documents are lacking information or are not updated to match the latest implementation.

Using reverse engineering is a suitable approach to the problem of recovering a communication protocol. Reverse protocol engineering can be used to analyze an existing implementation, identify its basic components and their relationships, and create system models.

A design recovery approach is typically either static or dynamic. In the static method, protocol designs are taken from software code and require a thorough understanding of the details of the code. Full automation of this method is usually not possible since a lot of information is needed from the user or designer. In the dynamic method, recovery data is collected during actual system execution, ensuring that no false information is used. The information is taken as a trace recording of observable events which are analyzed to recover the design. In this work, the dynamic approach is used because of the benefits described above.

A recovered design is described using the communicating finite state machine (CFSM) model. Communications traces are collected at run-time at various observation points of the system. The traces are then merged and rearranged so that the events' recorded times are in increasing order. The traces then consist of a sequence of zero or more trace records, where each record corresponds to an event observed and recorded at an observation point. Using the ordered traces, a synthesis algorithm is applied that produces the protocol design.

Each element of the trace TR has a record structure with the components:

#### • TR.op

This field enumerates the observation point where events are observed and recorded.

#### • TR.type

The type indicates whether the event was received or transmitted.

#### • TR.ev

This field contains the name of the event.

#### • TR.V

The vector clock value yields the order of the event relative to the whole system.

Operations on the traces are necessary when describing the procedure of this method. Two traces a and b can be concatenated:

$$a.b = a_1...a_n b_1...b_m \tag{2.2}$$

where  $a = a_1...a_n$  and  $b = b_1...b_m$ .

Two or more traces  $t_1, ..., t_n$  collected at various observation points can also be serialized:

$$T = t_1 \otimes t_2 \otimes \dots \otimes t_n \tag{2.3}$$

so that T includes the events in  $t_1, ..., t_n$  which are sorted and concatenated. This merging process is similar to merging two sorted lists of integers.

A trace t can be projected over a set of observation points, denoted  $\Pi_{sops}(t)$ . This projection is a subtrace of t, which contains only the events that were observed at the specific observation point and preserves the order of occurrence.

The traces collected at different observation points of the system are used to construct the CFSM. The communication protocol is assumed to have only one initial state. Most protocols are cyclic, where the initial and final states are the same. Trace collections start with the occurrence of an initial event. The collected traces will contain random occurrences of initial events, and thus are collected over a long time period in order to capture as many different representative sequences as possible. The recording is stopped when a final event is received, and the partial state machine is synthesized. The resulting CFSM is partial because the collected traces may not cover all possible transitions and behaviors.

14

To construct a CFSM from a collected trace, let  $t_{i1}, t_{i2}..., t_{ik}$  be the traces collected

at the different observation points of a protocol entity  $PE_i$ , and perform the following:

1. Serialize the traces  $t_{i1}...t_{ik}$  to form  $ST_i = t_{i1} \otimes t_{i2} \otimes ... \otimes t_{ik}$ .

2. Extract the event names TR.en in order from  $ST_i$  to form the trace T. TR.en

is preceded by "-" ("+") sign if it is a transmission (reception) event. Then

T contains the events corresponding to the protocol messages recorded at the

observation points of  $PE_i$  in order of occurrence. Let  $T = (te_1, te_2, ... te_n)$  where

each event  $te_k$  is made up of the pair (TR.type, TR.en) of the kth trace record

in  $ST_i$  and the function  $TR.en(te_i)$  will return the value of TR.en of the ith

event of T.

3. Produce the CFSM using Algorithm 3.

#### Algorithm 1 Create-State

Input: nStates

Output: nStates

1:  $nStates \leftarrow nStates + 1$

2: return nStates

The Create-State procedure in Algorithm 1 is used to create a new state. It is

called by the MAIN procedure when a transition does not already exist in the set.

#### Algorithm 2 Equivalence-Reduction

Input: Q, E, nextState

Output: Q, nextState

- 1: repeat

- 2: **if**  $\exists event \in E, \forall x, y \in Q : nextState[x, event] = nextState[y, event]$  **then**

- 3: for all  $z \in Q$  do

- 4: for all  $event \in E$ : nextState[z, event] = y do

- 5:  $\operatorname{nextState}[z, event] \leftarrow x$

- 6:  $Q \leftarrow Q \{y\}$

- 7: **until** no state y was removed from Q

- 8:  $\mathbf{return}$  Q, nextState

The Equivalence-Reduction procedure in Algorithm 2 is used by Main after one communication's full start to finish cycle has been processed from the trace. It then removes the redundant states.

#### Algorithm 3 MAIN

```

Input: Initial event \overline{\text{list, Trace }T}

Output: CFSM G = \{Q, q_0, E, TF\}

1: INITIALSTATE \leftarrow 1; EMPTY \leftarrow 0

2: Declare int array nextState[*,*] indexed by state number and event enumeration

3: nStates \leftarrow 0; Q = \{1\}; E = \emptyset

4: currentState \leftarrow INITIALSTATE

5: Read(event);

6: while event != EOF do

7:

Read(nextEvent)

8:

if \exists x, y \in Q : \text{nextState}[x, event] = y then

9:

currentState \leftarrow \text{nextState}[currentState, event] \leftarrow y

if nextEvent \in initalEvents then

10:

11:

EQUIVALENCE-REDUCTION()

else

12:

if nextEvent \in initialEvents then

13:

currentState \leftarrow nextState[currentState, event] \leftarrow INITIALSTATE

14:

EQUIVALENCE-REDUCTION()

15:

if TR.en(event) \notin E then

16:

E \leftarrow E \cup \{TR.en(event)\}

17:

else

18:

nextState[currentState, event] \leftarrow newState \leftarrow Create-State()

19:

Q \leftarrow Q \cup \{newState\}

20:

if TR.en(event) \notin E then

21:

E \leftarrow E \cup \{TR.en(event)\}

22:

currentState \leftarrow newState

23:

24:

event \leftarrow nextEvent

```

Algorithm 3 shows the Main procedure. Starting in initial state 1, the events are processed sequentially and the next state is determined. This determination is done by checking if a similar transition already exists in the partially constructed CFSM. If one does exist, then the next state becomes the state corresponding to that event transition. If a similar transition does not exist, a new state is created and added to the CFSM, with a new transition pointing to it. If the next event in the trace is one of the initial events, the cycle is over and equivalence reduction is performed. Following this procedure, the protocol can be recovered as a finite state machine model showing which message events were seen to occur after each other. The intended purpose of this is for design recovery in the form of documentation, but this method will be adapted for model generation.

#### 3. IMPLEMENTATION

This chapter describes the methods that this thesis proposes for automatic model generation and random simulation. First, an overview is given describing the process. Following this, the five main steps of the synthesis and simulation methods are discussed in detail.

#### 3.1 Overview

As previously stated, the method proposed by this thesis generates and runs a simulation model automatically. It uses information from a recorded communications trace to inform the construction process. The method requires at least two networked modules. Each of these modules on the network can be a controller or some type of data processor. The modules should communicate at regular intervals without errors in the communication protocol. Additionally, at least one of these modules (or another in the network) should be able to record every communication transaction that occurs on the network. Given this setup, a module can be removed for servicing or use in another location and the method is used to automatically generate a model simulating its communication transactions. This method will look to replace only the communications of a device will be replaced and not the function of the device, such as controlling a plant. Often, this is quite acceptable, since testing a device on a network does not require the other devices to perform their functions; it only requires that they communicate.

The proposed method could be realized on various setups. Here, it was accomplished using a Windows PC, but could be adapted for use in an embedded environment as well. It was set up in an automobile with multiple modules on a CAN communication network. A PC was introduced into the vehicle's network in order to

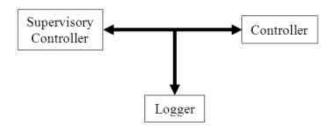

record transactions and later to simulate a removed module. Focus was placed on simulating the transactions of a controller in the vehicle. This controller would perform some digital control of a plant, communicate its status, and receive commands from a supervisory controller. See Figure 3.1 for a diagram of the vehicle's network structure.

Figure 3.1. Vehicle's CAN network structure and modules

When designing this method of automatic simulation, it was important to consider what outcome was desirable. The following are goals of the method, stated with most desired first:

#### 1. Provide an accurate model

The accuracy of the model is the most important consideration. If a model is inaccurate, simulation will not provide a good test environment since it will be difficult to tell what piece of the system is malfunctioning. An accurate model that is generated automatically will also reduce the workload of the operator since there will be less to correct.

#### 2. Reduce the time necessary to create a simulation model

Currently, creating a simulation model from scratch requires an operator to spend time designing a separate test bench or constructing a simulation model from nothing. Often, doing this by hand can take more time than it took to design the product that needs to be tested.

#### 3. Require minimal operator interaction

This goal of minimal operation interaction follows from the previous one. By

minimizing operator interaction, the operator's time can be spent doing other tasks.

#### 4. Produce repeatable and predictable results

Repeatable and predictable results provide more structure so that test plans can be repeated exactly each time without variation, reducing or eliminating operator error.

#### 5. Require minimal change to the environment's current architecture

This is also a goal that will save time. It is desirable that no change should happen to the environment that the simulator will be run on. Reconfigurations can introduce new errors and will take time that possibly was not allocated initially.

#### 6. Offer adaptability to other architectures

This goal offers versatility so that the methods proposed here can be used in other environments not envisioned by the original specifications. The goal is that the methods here could be used on other networks.

These goals led to the development of a five step procedure for generating a simulation model. In the first step, a communications trace is recorded which describes the transactions in and out of the module that will be simulated. In the second step, an operator specifies which signals within the messages are relevant to the logical operation and behavior of the module. In the third step, the information from the previous two steps is used to automatically synthesize a finite state machine (FSM). In the fourth step, the operator is given the option to adjust the FSM model to correct inconsistencies. In the final step, the FSM is simulated in real-time over the network, effectively replacing the communications transactions of the module.

By using the information found in a communications trace, the operator is saved the tedious process of entering each detail into the simulation model, effectively achieving Goal 2. Two of the five steps in the procedure require operator interaction. Thus, three of the five steps are automated, reducing operator interaction and achieving Goal 3. Also, Step 4 is optional, which can further reduce operator interaction in some cases. The synthesis step is deterministic, and the results are repeatable and predictable, but because of the nature of the simulation model, the simulation step is stochastic and therefore not predictable, so Goal 4 is achieved in some cases. The implementation of these steps was accomplished in a vehicle's CAN network with no modifications, achieving Goal 5. This procedure is adaptable to other architectures as well, achieving Goal 6. The accurate outcome of the model in Goal 1 will be discussed later.

#### 3.2 Step 1: Record Communications Trace

The first step in the procedure is the successful recording of a communications trace. In this implementation, the recording was accomplished by listening to all transactions on the CAN network and logging them sequentially into a file. Each transaction is considered a Message (id, data, time), where id is the identifier of the message, data is the group of data bits of the message, and time is the received time of the message. These messages are recorded sequentially and placed in a file for use in Step 2.

As stated, the result of this step is a file containing sequentially recorded messages. Ideally, the recording should be of as much data as possible to cover all permutations of possible transactions and module behaviors. It is also important that modules being recorded are functioning properly so that the recorded information is as accurate as possible. This will save the operator from making a lot of corrections by hand later.

This approach to trace recording works well because it is simple. In fact, it is common for existing data loggers to already perform this function. This means data could exist already and this step, then, is unnecessary. The recording approach also allows for an operator to record data in a geographically separate location and transfer the file to another location for simulation use. The other benefit is that one recorded

trace file can be used to synthesize several completely separate finite state machines, each with different target modules.

In the setup of Figure 3.1, the CAN protocol is used. The *id* field is an 11-bit identifier number which identifies the transmitter, receiver, and data format of the message. The *data* is 8 bytes of data, formatted according to the *id*. The *id* can be used to look up how the data chunk is formatted and separated into bit groupings, called signals. The *time* field is the number of milliseconds since the trace began until the transaction occurred.

For example, the trace might have data similar to that shown in Table 3.1. In this example, a controller and its supervisor communicate over a CAN network. The first column of the table shows the id of the recorded message. The id 849 is sent by the controller and the id 914 is sent by the supervisory controller. These messages are the primary means of communication between the two modules. The second column in the table shows the 64 bits of data in hexadecimal. The meaning of this data will be clarified later. The third column contains the time. For illustration, this table shows only part of the full recording.

This data was recorded by a computer listening to the network and saving the transactions in real-time as they occurred. Although this was implemented using a CAN network, this type of logging format is general enough that it could be used with other types of networks.

There are few constraints limiting how this could be applied to other networks. As long as a node can record all of the transactions to and from that node, a model can be synthesized to replace the node. Some adaptation would be necessary to apply the methods to a network with multiple channels. Redundant information received over multiple channels would need to be eliminated or merged and separating transmissions by channel would have to be considered.

As discussed in Section 4.4, the results indicate that the most improvement in model quality comes from a data set with the right number events in the correct order. In this initial step, it is important for the operator to force (if possible) the

Table 3.1 Recorded Messages

| ID  | Data (hex)              | Time   |

|-----|-------------------------|--------|

| 914 | 00 00 00 00 00 00 03 00 | 185685 |

| 849 | 00 00 00 00 80 00 F8 00 | 185930 |

| 849 | 00 00 00 00 40 00 00 20 | 189171 |

| 849 | 00 00 00 00 80 00 F8 00 | 198739 |

| 849 | 00 00 00 00 40 00 00 20 | 203719 |

| 914 | 00 00 00 00 00 00 13 00 | 205177 |

| 849 | 00 00 00 00 40 00 00 30 | 205413 |

| 914 | 00 00 00 00 00 00 03 00 | 213990 |

| 849 | 00 00 00 00 80 00 F8 00 | 214325 |

modeled device to demonstrate all transactions that are necessary to a successful model, and to do so in the correct order. This may seem obvious, but should be mentioned due to its importance.

#### 3.3 Step 2: Identify Relevant Signals

The second step of this procedure is for the operator to specify which signals are relevant to the the logic of the model to be created. Signals are (name, value) pairs that are used as criteria for a transition (defined later). Informed by a database file that specifies the signals' formats and bit numbers, the operator is presented with a list of all signals that were detected in the execution trace. Based on what signals are key to the logical operation and behavior of the created model, the operator specifies whether each signal should be received by the model, sent by the model, or ignored.

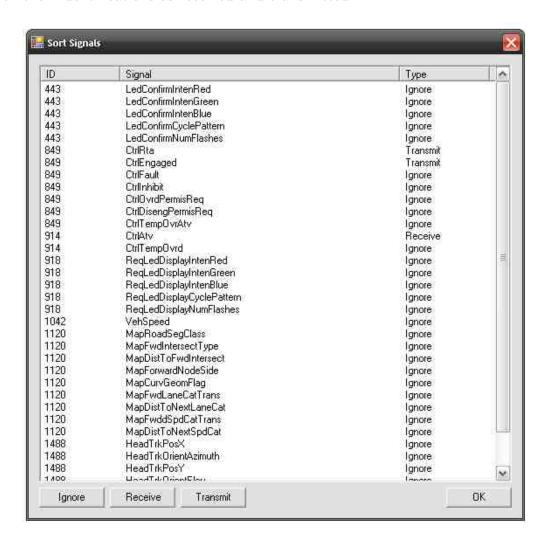

In the implementation, the controller will be simulated and the supervisory controller will operate as normal. Based on knowledge of the controller's operation, the operator would identify that the controller model should send two signals saying when it is ready and when it is engaged. The controller will also receive the signal from the supervisory controller commanding it to engage or disengage. The interface for sorting signals is shown in Figure 3.2, showing the ready, engaged, and engage signals with their identifications as received and transmitted.

Figure 3.2. Interface used to identify relevant signals

Continuing the example from Section 3.2, the operator must now identify which groups of bits correspond to relevant data. In the implementation, the organization of the data chunk was well defined in the database file. The 8 bytes of data for each message are separated into groups of at least one bit in size, or signals. This is a

common practice in digital networks. In the example of Table 3.1, the most significant bit is on the left (numbered as bit 63) and the least significant bit is on the right (numbered as bit 0). In the definition for message 849, bit four corresponds to the controller indicating engaged (1 is engaged, 0 is disengaged), and bit five corresponds to the controller indicating ready (1 is ready, 0 is not ready). In the definition for message 914, bit 12 corresponds to the supervisory controller commanding the controller to engage (a value of 1) or disengage (a value of 0). So, the controller indicates when it is ready to be engaged, then the supervisory controller can engage it, and the controller will indicate engaged. Since the operator wishes to simulate the communications behavior of the controller, ready and engaged should be identified as transmitted signals, and engage should be identified as a received signal.

Table 3.2 below extends Table 3.1 by showing the values of the relevant signals for each message that were identified in this step.

Table 3.2 Recorded Messages with Signal Values

| ID  | Data (hex)              | Time   | Relevant Signal Values       |

|-----|-------------------------|--------|------------------------------|

| 914 | 00 00 00 00 00 00 03 00 | 185685 | CtrlAtv = 0                  |

| 849 | 00 00 00 00 80 00 F8 00 | 185930 | CtrlRta = 0, CtrlEngaged = 0 |

| 849 | 00 00 00 00 40 00 00 20 | 189171 | CtrlRta = 1, CtrlEngaged = 0 |

| 849 | 00 00 00 00 80 00 F8 00 | 198739 | CtrlRta = 0, CtrlEngaged = 0 |

| 849 | 00 00 00 00 40 00 00 20 | 203719 | CtrlRta = 1, CtrlEngaged = 0 |

| 914 | 00 00 00 00 00 00 13 00 | 205177 | CtrlAtv = 1                  |

| 849 | 00 00 00 00 40 00 00 30 | 205413 | CtrlRta = 1, CtrlEngaged = 1 |

| 914 | 00 00 00 00 00 00 03 00 | 213990 | CtrlAtv = 0                  |

| 849 | 00 00 00 00 80 00 F8 00 | 214325 | CtrlRta = 0, CtrlEngaged = 0 |

### 3.4 Step 3: Synthesize FSM

Once information has been gathered in the previous two steps, a finite state machine can be synthesized. This step is completely automated. In fact, the first step could be skipped if the synthesis is done in real-time, as discussed later.

The recorded communications trace will be processed one message at a time. As the messages are processed, they are formed into a finite state machine. This step is based largely on the work of [19]. That work recovered the protocol for documentation purposes, but the method will be adapted for model generation. The improvements and changes include:

1. Adding simulation data such as count and average time to transitions

This added information will be useful in the simulation stage described in Section 3.6.

### 2. Moving equivalency reduction to the end

This is due to the non-cyclical nature of some of the communication traces that the proposed methods were executed on. The original method called for a starting event after reception of which equivalent states would be merged. Since it is anticipated that no cyclical pattern will exist, this part is removed and equivalency reduction is performed at the end. Also, equivalency reduction is a computationally intensive procedure. The cyclical protocol requirement is effectively removed.

### 3. Addition of end state recycling

This is another addition to help with simulation. This further automates the FSM simulation by removing the requirement for the operator to reset the simulation when it reaches a deadlock state. The final state is the only possible state where deadlock could occur, and this addition removes the possibility of deadlock.

With these modifications, the algorithm generates a simulation FSM model based on the recorded communications trace and identified signals.

```

Algorithm 4 Synthesize

```

Input: Set of Messages T

Output: FSM f

- 1:  $f \leftarrow \text{new FSM}$

- 2:  $f.states \leftarrow \{1\}$

- $3: f.currentState \leftarrow 1$

- 4: for each  $m \in T$  do

- 5: PROCESS-MESSAGE(f, m)

- 6: Reduce-Equivalency (f)

- 7: RECYCLE-END-STATE(f)

- 8: **return** *f*

In Algorithm 4, the FSM f is created. Input T is the ordered set of messages that were recorded in the communications trace. The initial state, 1, is added to f's set of states and the currentState is set to 1 as well. Then, each message is processed using the Process-Message routine in Algorithm 5. Once all of the messages have been processed, equivalency reduction (Algorithm 6) is performed on f to merge any states that are equivalent. Then, the final state is recycled (Algorithm 8) if it has no outgoing transitions, completing the synthesis step.

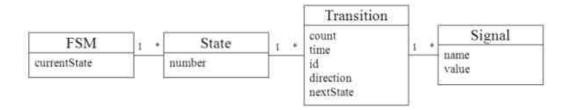

Algorithm 4 introduces several data structures. The first is T which is a set of messages. The structure of each message is a tuple as described in Section 3.2. The next data structure presented is f which is of type FSM, a tuple (states, currentState), where states is a set of all the reachable states and currentState is the state the FSM is currently operating in. The State data structure is a tuple (transitions, number) where transitions is a set of Transitions and number is the state's identifying number. A Transition is a tuple (signals, id, direction, time, count, nextState), where signals is a set of the (signal, value) pairs that are the criteria for the transition to occur, id is

the message identifier number that the criteria signals arrive in, direction represents the directional flow of the transition (as a transmission or reception), time is the average time spent in the state before the transition occurs, count is the number of times the transition occurred in the recorded communications trace, and nextState is the state that the FSM will operate in if the transition occurs. These data structures are summarized in the class relation diagram shown in Figure 3.3.

Figure 3.3. Class diagram showing relations between data structures used in the algorithms

### Algorithm 5 Process-Message

```

Input: FSM f, Message m

1: t \leftarrow \text{new Transition}

2: Add all relevant signals that changed with the new message to t.siqnals

3: if size(t.signals) > 0 then

t.count \leftarrow 1

4:

t.time \leftarrow m.time - f.lastEventTime

5:

f.lastEventTime \leftarrow m.time

6:

7:

t.id \leftarrow m.id

if \exists t_1 \in f.transitions \mid t_1.signals = t.signals then

8:

t.nextState = t_1.nextState

9:

else

10:

s \leftarrow \text{new State}

11:

12:

t.nextState \leftarrow s

f.states \leftarrow f.states \cup s

13:

f.currentState.transitions \leftarrow f.currentState.transitions \cup t

14:

f.currentState \leftarrow t.nextState

15:

```

Algorithm 5 describes the routine to process an individual message found in a communications trace. The input is the partially constructed FSM f and a Message m to be processed. It takes the information found in m and adds a transition to the finite state machine from the current state. If a transition in the FSM with the same criteria signal and value pairs exists, then the new transition directed to its nextState is added. If no transition with the same criteria exists, then a new state is created and the transition is directed to the new state.

First, a new transition is created. Then m is analyzed to determine which signals' values have changed since the last time a message with this identifier was seen in the trace. The changed signals are added to the new transition's set of signals along with their new values. If no signals changed since the last time this message was

seen, the routine is complete. Otherwise, the new transition's count is set to 1 and the difference in time is calculated from the last event. Then, if a transition exists with the same signals set as the new transition, the new transition's nextState is set to the matched transition's nextState. Otherwise, a new state is created and the new transition is directed to it. The transition is added to the current state and the current state is updated.

# Algorithm 6 REDUCE-EQUIVALENCY

Input: FSM f

- 1: for each  $s_1 \in f.states$  do

- 2: **for** each  $s_2 \in f.states$  **do**

- 3: if  $s_2.number > s_1.number$  and  $s_1.transitions = s_2.transitions$  then

- 4: Merge-States $(f, s_1, s_2)$

Reduce-Equivalency (Algorithm 6) works on the simple principal that two states are equivalent if all of their outgoing transitions and next states are equivalent. So, the procedure takes f and iterates over all permutations of states to see if they are equivalent. If the transition sets for two states are equivalent, then the states are considered equivalent and are merged together using the Merge-States routine (Algorithm 7).

# Algorithm 7 Merge-States

```

Input: f, s_1, s_2

1: for each t \in s_2.transitions do

2:

Find a transition \{t_f \in s_1.transitions : t_f.transitions = t.transitions\}

t_f.time \leftarrow \frac{t_f.time \cdot t_f.count + t.time \cdot t.count}{t_f.count + t.count}

3:

t_f.count \leftarrow t_f.count + t.count

4:

5: for each s \in f.states do

6:

for each t \in s.transitions do

7:

if t.nextState = s_2.number then

t.nextState \leftarrow s_1.number

8:

9: f.states \leftarrow f.states - \{s_2\}

```

Algorithm 7 shows the MERGE-STATES procedure. It takes as input FSM f and two states that are identified as equivalent,  $s_1$  and  $s_2$ . In the merger, it is desired that transition properties such as count and average time be combined so that the information is not lost. Since the states are known to be equivalent, their transition sets are the same. So, the algorithm can iterate through the transition set of one state and match each transition in the other set in order to merge their properties. The algorithm finds a transition  $t_f$  in  $s_1$ .transitions that is equivalent to t in  $s_2$ .transitions. Then,  $t_f$ 's time average is updated using the time average of t, and the two counts are summed. The algorithm then iterates through all transitions in all states and redirects any transitions directed at  $s_2$  to  $s_1$  instead. Finally,  $s_2$  is removed from the state set.

# Algorithm 8 Recycle-End-State

```

Input: FSM f

1: q \leftarrow \text{last state} \in f.states

2: if \text{size}(q.transitions) > 0 then

3: for each s \in f.states do

4: for each t \in s.transitions do

5: if t.nextState = q then

6: t.nextState \leftarrow 1

7: f.states \leftarrow f.states - \{q\}

```

The Recycle-End-State procedure is shown in Algorithm 8. This procedure checks the final state in the FSM f. If the final state has no outgoing transitions, then all transitions directed to the final state are redirected to the initial state. This serves the purpose of eliminating the only possible deadlock state. When simulating, it is likely that upon reaching this final state the operator will desire to restart the simulation. This recycling procedure eliminates that need.

This procedural step is accomplished using SYNTHESIZE in Algorithm 4. The information gathered in Steps 1 and 2 is used to inform this step. A finite state machine can be generated that is modeled from data found in the recorded communications trace. The larger the data set is, the more detailed the finite state machine will become.

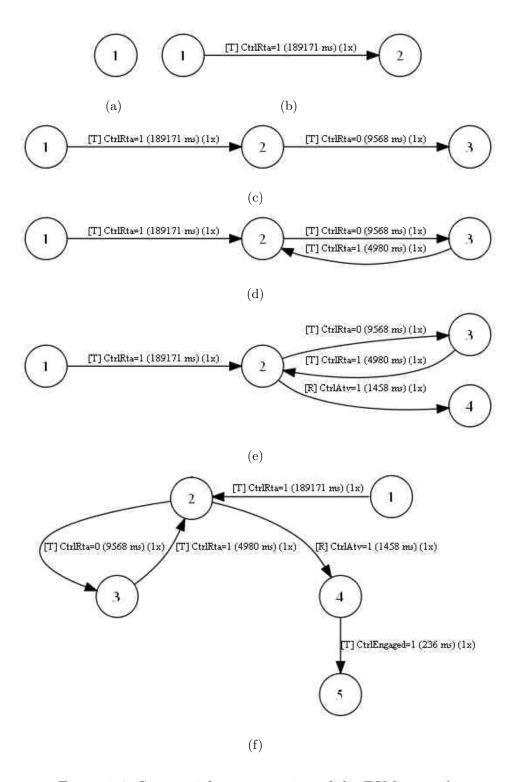

The example from the previous sections will be used to walk through the algorithms shown in this section. The recorded communications trace shown in Table 3.1 is formed into a set T. Then Synthesize is used to generate the corresponding FSM. Per Algorithm 4, each message in the set is added to the FSM through Process-Message. The FSM is set up so that the current state is set to the newly created state 1. The FSM is shown in Figure 3.4(a).

From the first entry in Table 3.2, the relevant signal is CtrlAtv. Since this is the first message of id 914, the value of CtrlAtv will be compared with 0 to deter-

mine change. This means that CtrlAtv has not changed with the arrival of this new message. Thus, t.signals is empty and the routine completes.

From the next entry in the table, the message is (849, 00 00 00 00 80 00 F8 00, 185930). Since this is the first message of id 849, its signals will be compared with 0 to determine which relevant signals changed. From the new message, the value of the relevant signals CtrlRta and CtrlEngaged is 0. Therefore no relevant signals were changed with the new message, t.signals is empty, and the routine completes.

The next message entry in the table is (849, 00 00 00 00 40 00 00 20, 189171). Since a message of id 849 has already been processed, the new values are compared to the previous signal values. The old values of CtrlEngaged and CtrlRta were both 0, and the new value of CtrlRta is 1, while CtrlEngaged remains 0. Since CtrlRta changed, it is added to t.signals as a signal (CtrlRta, 1). The new transition's properties are updated, setting count to 1, time to 189171 - 0 = 189171, and id to 849. Then, the FSM's transitions are checked to see if the new transition is the same as any transition already part of the FSM. In this case none match, so a new state s is created and the new transition's nextState is pointed to s. The new transition is added to the current state, and the current state is set to the new transition's nextState. This step is shown in Figure 3.4(b).

The fourth message in Table 3.2 shows CtrlRta and CtrlEngaged both 0. CtrlRta's previous value was 1, so a change occurred. This signal is added to t.signals. The new transition's properties are updated as before, with time = 198739 - 189171 = 9568. The FSM's transitions are checked to see if a transition matches the new one. None match, so the transition is pointed to a new state, and currentState is updated to match. Figure 3.4(c) shows the update.

The fifth message in the table shows that CtrlRta has changed from its previous value of 0 to a new value of 1. This is added to t.signals, the transition's properties are updated with time = 203719 - 198739 = 4980. Now, the FSM's transitions are checked to see if a match exists. In this case, the transition from state 1 to 2 has the same criteria as this new transition. Following Algorithm 5 the new transition.

sition is pointed to that transition's state, which is 2. The transition is added and *currentState* is updated. The change is shown is Figure 3.4(d).

The next table entry shows that CtrlAtv has changed from its previous value of 0 and is now 1. This transition is not matched in the FSM, so it is pointed to a new state. The result is shown in Figure 3.4(e).

The next entry in the table shows that CtrlEngaged has changed to 1. This transition does not already exist, so it is pointed to a new state. Figure 3.4(f) shows the update.

The eighth entry in the table shows CtrlAtv has changed to 0. This transition does not exist in the FSM already, so it is added and pointed to a new state. The addition is shown in Figure 3.5.

The final entry in the table shows that both CtrlRta and CtrlEngaged have changed to a new value of 0. A transition with this criteria does not exist, so it is added and pointed to a new state. The resulting FSM is shown in Figure 3.6.

Once all of the messages have been processed, Algorithm 4 calls the procedure Reduce-Equivalency (Algorithm 6). This serves to reduce the number of states by merging those that are equivalent. Two states are equivalent if their exit transition sets are equivalent (same number and equivalent transition criteria). Pairs of states are tested to see if their transition sets are equal. In the example, it can be seen immediately that state 3 is equivalent to state 1. Both have the exit transition CtrlRta = 1 which point to state 2. The Reduce-Equivalency will check each pair of states sequentially as (1, 1), (1, 2), (1, 3), and find that (1, 3) is an equivalent pair. Merge-States is called on the pair (1, 3). In this routine, the exit transition from state 3 is matched to the exit transition of state 1. State 1's transition's time is updated with the average of the two times:  $\frac{189171\cdot1+4980\cdot1}{1+1} = 97075$ , and it's count is updated as well: 1+1=2. Then, every transition in the FSM is checked. If a transition is pointed to state 3 (which will be removed), it is instead pointed to state 1. This applies to the transition from state 2 to 3 with CtrlRta = 0. State 3 is removed from the set. The resulting FSM is shown in Figure 3.7.

Figure 3.4. Steps 1-6 for construction of the FSM example

Figure 3.5. Step 7 for construction of the FSM example

Once equivalency reduction has completed, Algorithm 4 then calls RECYCLE-END-STATE (Algorithm 8). The algorithm checks the last state to see if any exit transitions exist. In the example, state 7 has no exit transitions, so it will be recycled. All transitions in the FSM are inspected to see if they point to the final state. If so, they are redirected to state 1, and then the final state is removed. During inspection, it is found that the transition between states 6 and 7 is the only transition pointing to 7, and it will be redirected to state 1. The result is shown in Figure 3.8.

Figure 3.6. Final result of the FSM synthesis (before reduction)

## 3.5 Step 4: Manually Modify FSM

At this point, the FSM created by Steps 1-3 is completely ready for simulation. However, a human operator may desire to change or add to the model that is created automatically. Since this method does not produce perfect results (e.g. in the case where too few events have been captured in the communications trace) it is likely that the operator will want to make some changes. In this implementation, the operator can adjust the transitions between states and can also add or remove states

Figure 3.7. FSM after equivalency reduction