### University of New Mexico UNM Digital Repository

**Computer Science ETDs**

**Engineering ETDs**

Fall 12-1-2018

# Adaptive Parallelism for Coupled, Multithreaded Message-Passing Programs

Samuel K. Gutiérrez

Follow this and additional works at: https://digitalrepository.unm.edu/cs\_etds Part of the <u>Numerical Analysis and Scientific Computing Commons</u>, <u>OS and Networks</u> <u>Commons</u>, <u>Software Engineering Commons</u>, and the <u>Systems Architecture Commons</u>

#### **Recommended** Citation

Gutiérrez, Samuel K.. "Adaptive Parallelism for Coupled, Multithreaded Message-Passing Programs." (2018). https://digitalrepository.unm.edu/cs\_etds/95

This Dissertation is brought to you for free and open access by the Engineering ETDs at UNM Digital Repository. It has been accepted for inclusion in Computer Science ETDs by an authorized administrator of UNM Digital Repository. For more information, please contact disc@unm.edu.

Samuel Keith Gutiérrez

Candidate

Computer Science

Department

This dissertation is approved, and it is acceptable in quality and form for publication:

Approved by the Dissertation Committee:

Professor Dorian C. Arnold, Chair

Professor Patrick G. Bridges

Professor Darko Stefanovic

Professor Alexander S. Aiken

Patrick S. McCormick

## Adaptive Parallelism for Coupled, Multithreaded Message-Passing Programs

by

### Samuel Keith Gutiérrez

B.S., Computer Science, New Mexico Highlands University, 2006M.S., Computer Science, University of New Mexico, 2009

#### DISSERTATION

Submitted in Partial Fulfillment of the Requirements for the Degree of

> Doctor of Philosophy Computer Science

The University of New Mexico

Albuquerque, New Mexico

December 2018

©2018, Samuel Keith Gutiérrez

# Dedication

To my beloved family

"A Dios rogando y con el martillo dando."

Unknown

## Acknowledgments

Words cannot adequately express my feelings of gratitude for the people that made this possible. Please know that this accomplishment is as much yours as it is mine. We made it—persevered. With all my being, thank you.

I was incredibly fortunate to have a dedicated academic advisor who was demanding, yet patient—making me a better writer and researcher along the way. Dorian, thank you for your friendship and mentorship throughout these years. I owe a thankyou to the members of my committee, Alex Aiken, Dorian Arnold, Patrick Bridges, Patrick McCormick, and Darko Stefanovic, for their helpful comments. To the members of the Scalable Systems Lab at UNM, thank you for your honest feedback and encouragement, but more importantly your fellowship. Special thanks to David DeBonis, Matthew Dosanjh, Noah Evans, Kurt Ferreira, Aaron Gonzales, Taylor Groves, Nathan Hjelm, Dewan Ibtesham, Edgar León, Scott Levy, Whit Schonbein, and Patrick Widener.

Many supportive and understanding individuals undoubtedly enabled my going back to school while also working full-time at LANL. To my management, both past and present, John Cerutti, Linn Collins, David Daniel, Ed Dendy, Gary Grider, Jeff Johnson, Christoph Junghans, Mike Lang, Patrick McCormick, David Montoya, Randal Rheinheimer, and Galen Shipman, thank you for allowing my research at work to align nicely with my academic endeavors. To my colleagues, thank you for being my extended academic family. Special thanks to Randy Baker, Zach Baker, Ben Bergen, Bob Bird, Jon Dahl, Kei Davis, Daniel Holladay, Erika Maestas, Patrick McCormick, Scott Pakin, Robert Robey, Ben Santos, Justin Tripp, and Joe Zerr. To all my friends, thank you for reminding me that the world is full of fun, exciting people. To my uncles, aunts, and cousins, thank you for letting a curly haired kid be a part of such a loving and supportive group. I thank especially my uncle Frank, aunt Isabel, Krystal, and Brittany. To Max, Beth, Christina, Gerald, and Max, thank you for accepting me so completely into your family and letting me be a part of your lives.

I was blessed to have an upbringing full of love, encouragement, support, happiness, hard work, and discipline. Mom, thank you. You worked so very hard, often taking on multiple jobs so that I could have and do things that I found interesting. You always put me first and made sure your *hito* was loved and cared for no matter what. Grandma and grandpo, thank you for raising me as one of your own. Some of my most cherished childhood memories are of us at the ranch.

To Jess—my love, my rock, my friend and confidant, the mother of our son. Thank you for being there, through thick and thin. I know I'm not the easiest person to get along with when I'm stressed, so thank you for your steadfast love and support. It is because of your commitment that I saw this thing through—we did it. To Andres—my son, my pride and joy. Thank you for bringing us so much happiness. I look forward to our adventures together.

# Sponsorship

Work supported by the Advanced Simulation and Computing program of the U.S. Department of Energy's NNSA and by the Exascale Computing Project (17-SC-20-SC), a collaborative effort of the U.S. Department of Energy Office of Science and the National Nuclear Security Administration. Los Alamos National Laboratory is managed and operated by Los Alamos National Security, LLC (LANS), under contract number DE-AC52–06NA25396 for the Department of Energy's National Nuclear Security Administration (NNSA).

## Adaptive Parallelism for Coupled, Multithreaded Message-Passing Programs

by

#### Samuel Keith Gutiérrez

B.S., Computer Science, New Mexico Highlands University, 2006M.S., Computer Science, University of New Mexico, 2009Ph.D., Computer Science, University of New Mexico, 2018

#### Abstract

Hybrid parallel programming models that combine message passing (MP) and sharedmemory multithreading (MT) are becoming more popular, especially with applications requiring higher degrees of parallelism and scalability. Consequently, *coupled* parallel programs, those built via the integration of independently developed and optimized software libraries linked into a single application, increasingly comprise message-passing libraries with differing preferred degrees of threading, resulting in *thread-level heterogeneity*. Retroactively matching threading levels between independently developed and maintained libraries is difficult, and the challenge is exacerbated because contemporary middleware services provide only static scheduling policies over entire program executions, necessitating suboptimal, *over-subscribed* or *under-subscribed*, configurations. In coupled applications, a poorly configured component can lead to overall poor application performance, suboptimal resource utilization, and increased time-to-solution. So it is critical that each library executes in a manner consistent with its design and tuning for a particular system architecture and workload. Therefore, there is a need for techniques that address dynamic, conflicting configurations in coupled multithreaded message-passing (MT-MP) programs. Our thesis is that we can achieve significant performance improvements over static under-subscribed approaches through reconfigurable execution environments that consider compute phase parallelization strategies along with both hardware and software characteristics.

In this work, we present new ways to structure, execute, and analyze coupled MT-MP programs. Our study begins with an examination of contemporary approaches used to accommodate thread-level heterogeneity in coupled MT-MP programs. Here we identify potential inefficiencies in how these programs are structured and executed in the high-performance computing domain. We then present and evaluate a novel approach for accommodating thread-level heterogeneity. Our approach enables full utilization of all available compute resources throughout an application's execution by providing programmable facilities with modest overheads to dynamically reconfigure runtime environments for compute phases with differing threading factors and affinities. Our performance results show that for a majority of the tested scientific workloads our approach and corresponding open-source reference implementation render speedups greater than 50 % over the static under-subscribed baseline.

Motivated by our examination of reconfigurable execution environments and their memory overhead, we also study *the memory attribution problem*: the inability to predict or evaluate during runtime where the available memory is used across the software stack comprising the application, reusable software libraries, and supporting runtime infrastructure. Specifically, dynamic adaptation requires runtime intervention, which by its nature introduces additional runtime and memory overhead. To better understand the latter, we propose and evaluate a new way to quantify component-level memory usage from unmodified binaries dynamically linked to a message-passing communication library. Our experimental results show that our approach and corresponding implementation accurately measure memory resource usage as a function of time, scale, communication workload, and software or hardware system architecture, clearly distinguishing between application and communication library usage at a per-process level.

| Li            | List of Figures xv: |                                         |    |  |  |

|---------------|---------------------|-----------------------------------------|----|--|--|

| $\mathbf{Li}$ | ist of              | Tables x                                | х  |  |  |

| $\mathbf{G}$  | lossa               | ry xx                                   | ii |  |  |

| 1             | Intr                | roduction                               | 1  |  |  |

|               | 1.1                 | Motivation                              | 1  |  |  |

|               | 1.2                 | Thesis Statement                        | 2  |  |  |

|               | 1.3                 | Contributions and Organization          | 2  |  |  |

| <b>2</b>      | Bac                 | kground                                 | 8  |  |  |

|               | 2.1                 | Parallel Computers and Execution Models | 8  |  |  |

|               | 2.2                 | High-Performance Computing Platforms 1  | .0 |  |  |

|               | 2.3                 | Parallel Programming Environments       | 2  |  |  |

|               |                     | 2.3.1 Message Passing                   | .3 |  |  |

|   |     | 2.3.2  | Shared-Memory Multithreading             | 14 |

|---|-----|--------|------------------------------------------|----|

|   | 2.4 | Parall | el Speedup                               | 14 |

|   | 2.5 | Summ   | nary                                     | 15 |

| 3 | Acc | commo  | dating Thread-Level Heterogeneity        | 16 |

|   | 3.1 | Coupl  | ed Applications and Their Challenges     | 18 |

|   |     | 3.1.1  | Parallelism                              | 19 |

|   |     | 3.1.2  | Conflicting Configuration Requirements   | 20 |

|   | 3.2 | Backg  | ground and Related Work                  | 24 |

|   |     | 3.2.1  | Portable Hardware Locality               | 24 |

|   |     | 3.2.2  | Abstract Hardware Representation         | 24 |

|   |     | 3.2.3  | Multiprocessor Scheduling                | 25 |

|   |     | 3.2.4  | Current Approaches in HPC                | 28 |

|   | 3.3 | Adapt  | tive Parallelism for Coupled MPI+X       | 29 |

|   |     | 3.3.1  | Adaptive Execution Environments with QUO | 30 |

|   |     | 3.3.2  | Quo Contexts                             | 31 |

|   |     | 3.3.3  | Hardware/Software Environment Queries    | 31 |

|   |     | 3.3.4  | Programmable Dynamic Process Affinities  | 32 |

|   |     | 3.3.5  | Data Dependencies                        | 35 |

|   |     | 3.3.6  | Parallel Task Distribution               | 36 |

|   |     | 3.3.7  | Node-Level Process Quiescence            | 37 |

|   |     | 3.3.8 Policy Management                                     | 37 |

|---|-----|-------------------------------------------------------------|----|

|   | 3.4 | Quo Performance and Effectiveness                           | 38 |

|   |     | 3.4.1 Experimental Setup                                    | 38 |

|   |     | 3.4.2 Application Results: Evaluating Quo's Effectiveness 4 | 40 |

|   | 3.5 | Practical Considerations                                    | 44 |

|   | 3.6 | Summary                                                     | 45 |

| 4 | Ado | lressing The Memory Attribution Problem 4                   | 17 |

|   | 4.1 | Background                                                  | 49 |

|   |     | 4.1.1 Parallel Application Memory Utilization               | 50 |

|   |     | 4.1.2 Parallel Application Analysis                         | 50 |

|   |     | 4.1.3 Intercepting Application Behavior                     | 51 |

|   |     | 4.1.4 Collecting Process/System Information                 | 52 |

|   | 4.2 | Methods in Memory Utilization Analysis                      | 53 |

|   |     | 4.2.1 Heap Profiling and Memory Map Analysis                | 54 |

|   |     | 4.2.2 Middleware Attribution of Memory Usage                | 55 |

|   |     | 4.2.3 Our Approach                                          | 56 |

|   | 4.3 | Micro-Benchmarks and Proxy Applications                     | 60 |

|   |     | 4.3.1 Application Drivers: Proxy Applications               | 61 |

|   | 4.4 | Results                                                     | 64 |

|   |     | 4.4.1 Experimental Setup                                    | 64 |

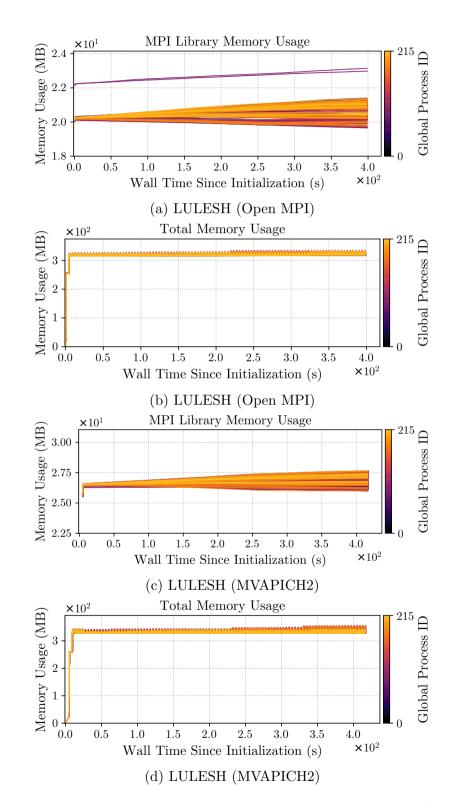

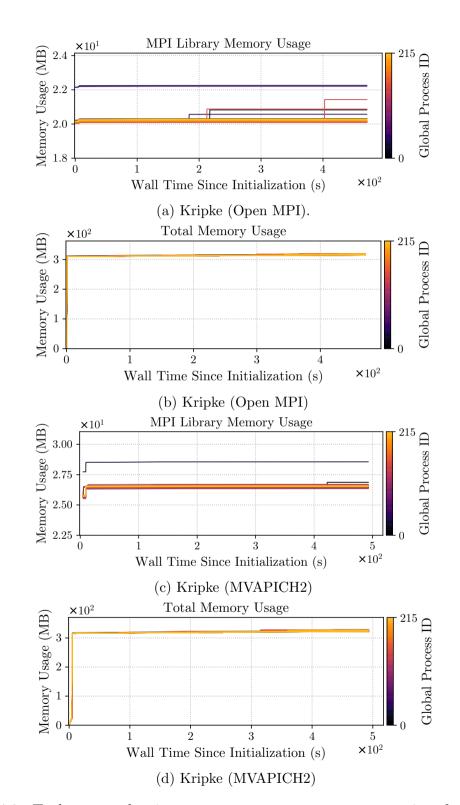

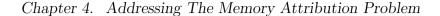

|   |     | 4.4.2   | Memory Usage Timelines                          | 64 |

|---|-----|---------|-------------------------------------------------|----|

|   |     | 4.4.3   | Peak Memory Usage                               | 68 |

|   |     | 4.4.4   | Tool-Induced Application Overhead               | 69 |

|   | 4.5 | Discus  | ssion and Summary                               | 74 |

| 5 | Ove | erhead  | of Adaptive Parallelism: A Case Study with Quo  | 76 |

|   | 5.1 | Runti   | me Overhead                                     | 76 |

|   |     | 5.1.1   | Micro-Benchmark Results: Cost of Quo Operations | 77 |

|   |     | 5.1.2   | Application Overhead from Process Quiescence    | 78 |

|   |     | 5.1.3   | Application Overhead from Data Remapping        | 79 |

|   | 5.2 | Memo    | ry Overhead                                     | 82 |

|   |     | 5.2.1   | Cost of Quo Runtime State                       | 83 |

|   |     | 5.2.2   | Cost of Quiesced Processes                      | 84 |

|   | 5.3 | Summ    | nary                                            | 87 |

| 6 | Cor | nclusio | n                                               | 88 |

|   | 6.1 | Summ    | nary of Contributions                           | 88 |

|   | 6.2 | Open    | Related Studies                                 | 89 |

|   |     | 6.2.1   | Transparent Data Dependency Satisfaction        | 89 |

|   |     | 6.2.2   | Examination of Other Dynamic Configurations     | 90 |

|   | 6.3 | Conch   | uding Remarks                                   | 91 |

|   | 6.3 | 6.2.2   |                                                 | 9( |

| Appendices                                    | 92 |

|-----------------------------------------------|----|

| A Example Quo Policies                        | 93 |

| A.1 Pseudocode for a Caller-Driven Quo Policy | 94 |

| A.2 Pseudocode for a Callee-Driven Quo Policy | 95 |

# List of Figures

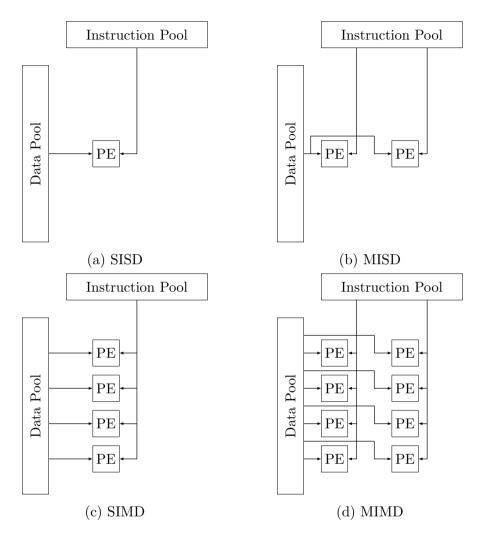

| 2.1 | Flynn's computer taxonomy.                                                                                                            | 9  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------|----|

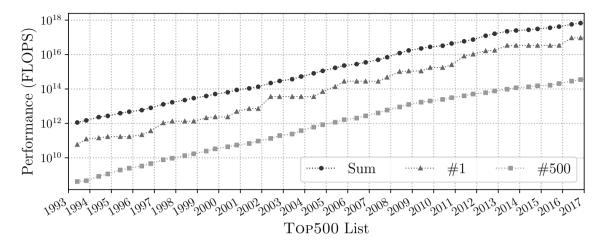

| 2.2 | Performance development of HPC systems as recorded by the TOP500.                                                                     | 11 |

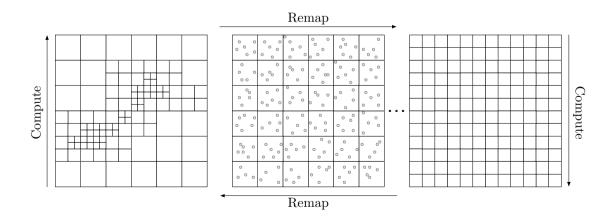

| 3.1 | Notional illustration of computational phases interleaved with data structure remapping phases across library domains                 | 18 |

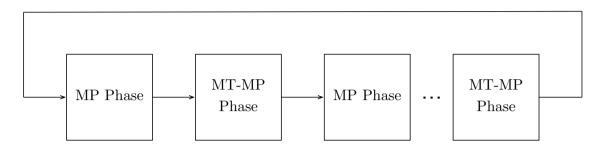

| 3.2 | Interleaved phases of a coupled thread-heterogeneous message-passing application with non-uniform runtime configuration requirements. | 20 |

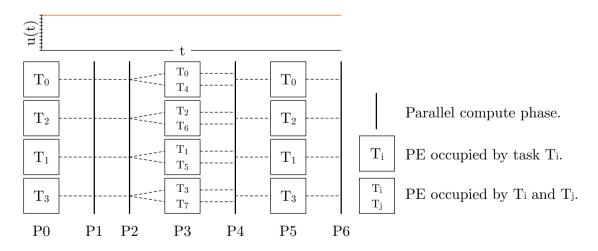

| 3.3 | Compute resource utilization $u(t)$ by tasks (processes and threads)<br>over time of a static over-subscribed MPI+X configuration     | 21 |

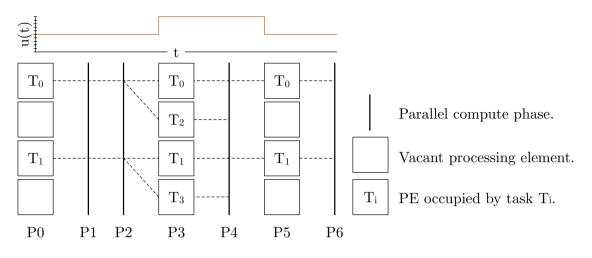

| 3.4 | Compute resource utilization $u(t)$ by tasks (processes and threads)<br>over time of a static under-subscribed MPI+X configuration    | 22 |

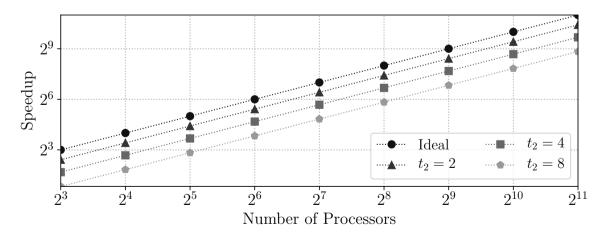

| 3.5 | Log-log plot of modeled speedups showing the potential losses in parallelism resulting from under-subscription as a function of scale | 23 |

| 3.6 | Schematic of a machine with two quad-core sockets                                                                                     | 25 |

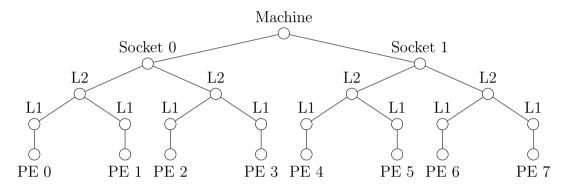

| 3.7 | Hardware topology of the machine diagrammed in Figure 3.6                                                                             | 25 |

| 3.8 | Example task to affinity mask relations.                                                                                              | 27 |

| 3.9  | Quo architecture diagram.                                                                                                                                                                                                                                              | 30 |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.10 | Compute resource utilization by tasks over time $u(t)$ for a Quo-<br>enabled MPI+X configuration. Consult Table 3.1 for a description<br>of the phases.                                                                                                                | 32 |

| 3.11 | Control flow of a Quo-enabled application.                                                                                                                                                                                                                             | 35 |

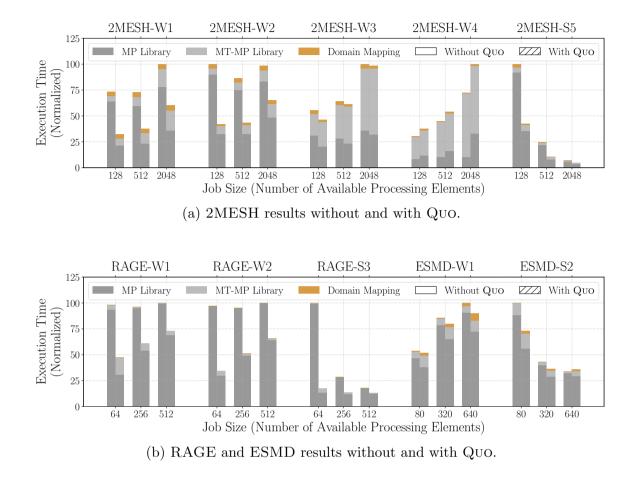

| 3.12 | Application results without and with QUO.                                                                                                                                                                                                                              | 43 |

| 4.1  | MPI profiling interface example.                                                                                                                                                                                                                                       | 52 |

| 4.2  | Code snippet showing memnesia instrumentation of ${\tt MPI\_Barrier()}$ .                                                                                                                                                                                              | 57 |

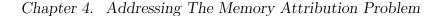

| 4.3  | A typical offline tool architecture where analysis probes start with the application and remain in place for the entirety of the application's execution. After all analysis data are written, they are then read, aggregated, and finally analyzed by a separate tool | 58 |

| 4.4  | The tool architecture we adopted, which bears many similarities to<br>its counterpart shown in Figure 4.3. The key difference is that tool<br>data aggregation is parallelized using the job's resources with MPI.                                                     | 59 |

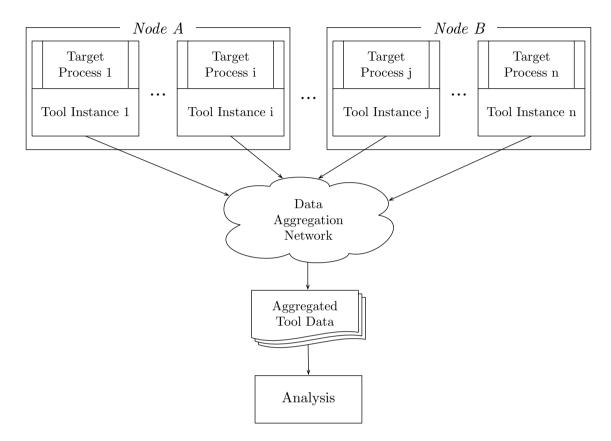

| 4.5  | Single-process memory usage and data collection points                                                                                                                                                                                                                 | 60 |

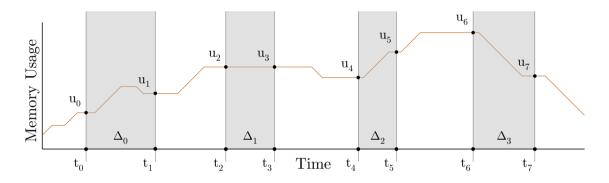

| 4.6  | Point-to-point communication structure formed by each proxy appli-<br>cation used in this study. Colors are mapped to data transfer to-<br>tals between MPI processes (send/receive pairs) using point-to-point<br>communication operations                            | 63 |

| 4.7  | Tool output showing per-process memory usage over time for LULESH.<br>Colors are mapped to a process's MPI_COMM_WORLD rank.                                                                                                                                            | 65 |

### List of Figures

| 4.8  | Tool output showing per-process memory usage over time for Kripke.                                                                                                                                                                                                                                      |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | Colors are mapped to a process's $\texttt{MPI_COMM_WORLD}$ rank. $\hfill \ldots$ .                                                                                                                                                                                                                      | 66 |

| 4.9  | memnesia timelines showing aggregate total (i.e., MPI library and application) memory usage over time from 216-process (six-node) runs on Trinitite.                                                                                                                                                    | 67 |

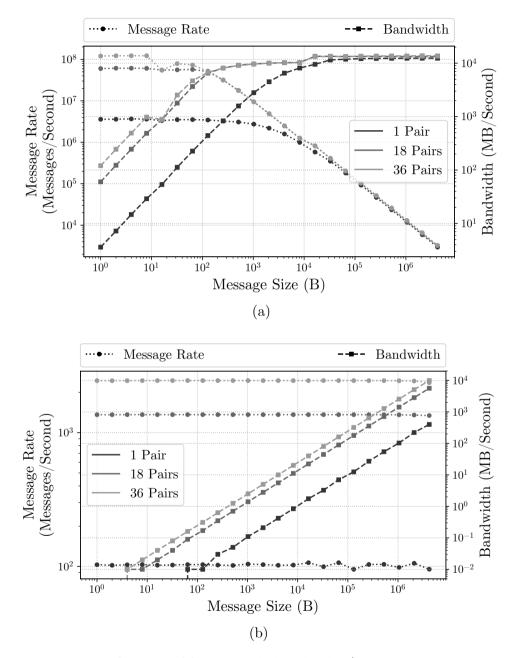

| 4.10 | Results from the OSU multiple bandwidth/multiple message rate<br>micro-benchmark, where the number of send/receive pairs vary. Fig-<br>ure a shows our performance baseline, while Figure b shows perfor-<br>mance results with memnesia instrumentation enabled, both plotted<br>using a log-log scale | 73 |

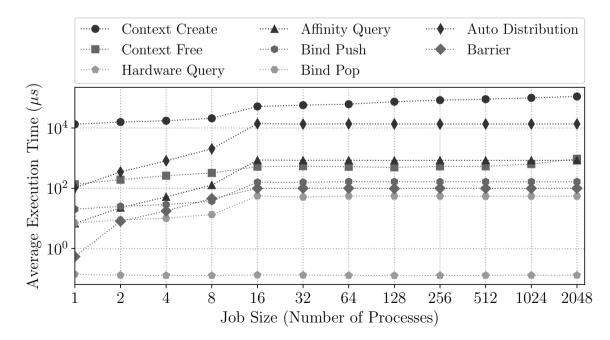

| 5.1  | Log-log plot of average execution times of QUO operations on Cielo.                                                                                                                                                                                                                                     | 77 |

# List of Tables

| 2.1 | Node and network architectures of contemporary HPC platforms                                        | 11 |

|-----|-----------------------------------------------------------------------------------------------------|----|

| 2.2 | The scales at which contemporary supercomputers operate                                             | 12 |

| 3.1 | Explanation of Quo-enabled MPI+X phases in Figure 3.10                                              | 33 |

| 3.2 | An overview of compute node architectures used for this study                                       | 39 |

| 3.3 | Application identifiers and descriptions of the applications they represent.                        | 40 |

| 3.4 | Target applications and their environments used for this study                                      | 41 |

| 3.5 | Application configurations used in this study                                                       | 41 |

| 4.1 | Hardware statistics of the last 10 number one computer systems ac-                                  |    |

|     | cording to the TOP500 by earliest date of first-place ranking                                       | 48 |

| 4.2 | Tools and their respective attributes.                                                              | 56 |

| 4.3 | An overview of hardware and software used for this study                                            | 68 |

| 4.4 | Average reported peak memory consumption (in MB) on Trinitite                                       | 70 |

| 4.5 | Average peak memory consumption (in MB) on Trinitite (tt) and<br>Snow (sn) as reported by memnesia. | 71 |

### List of Tables

| 5.1 | Average quiescence-induced overhead by mechanism                       | 79 |

|-----|------------------------------------------------------------------------|----|

| 5.2 | Application results: average data remapping costs without and with QUO | 81 |

| 5.3 | Average per-process cost of Quo runtime state.                         | 84 |

| 5.4 | MPI library memory footprint of fully subscribed node configurations.  | 85 |

| 5.5 | Resource-subscription-induced memory overhead                          | 86 |

# Glossary

| ANSI    | American National Standards Institute                          |

|---------|----------------------------------------------------------------|

| API     | Application Programming Interface                              |

| ASIC    | Application-Specific Integrated Circuit                        |

| CPU     | Central Processing Unit                                        |

| DRAM    | Dynamic Random-Access Memory                                   |

| ECC     | Error-Correcting Code                                          |

| FLOPS   | Floating point operations per second                           |

| GPU     | Graphics Processing Unit                                       |

| HPC     | High-Performance Computing                                     |

| HPL     | High-Performance LINPACK: a parallel version of LINPACK.       |

| I/O     | Input/Output                                                   |

| ISO     | International Organization for Standardization                 |

| LINPACK | A performance benchmark for computers that analyzes and solves |

dense systems of linear equations [35].

### Glossary

| LSB-0           | Least significant bit zero                                               |

|-----------------|--------------------------------------------------------------------------|

| MP              | Message Passing                                                          |

| MPS             | Messages Per Second                                                      |

| MT-MP           | Multithreaded Message Passing                                            |

| NIC             | Network Interface Controller                                             |

| Node            | A component in a system of networked machines—a computer.                |

| NUMA            | Non-Uniform Memory Access                                                |

| OS              | Operating System                                                         |

| PE              | Processing Element: a core or hardware thread.                           |

| POSIX           | Portable Operating System Interface                                      |

| PPN             | Processes Per Node                                                       |

| RMA             | Remote Memory Access                                                     |

| Rmax            | An HPL performance metric.                                               |

| Task            | A thread of execution associated with either an OS process or thread.    |

| TFLOPS          | $10^{12}$ FLOPS                                                          |

| $T_i/C_j$       | Task $T_i$ has affinity to (can be scheduled to execute on) core $C_j$ . |

| $T_i/C_j   C_k$ | Task $T_i$ has affinity to cores $C_j$ and $C_k$ .                       |

| TX/RX           | Send/Receive                                                             |

| UMA             | Uniform Memory Access                                                    |

# Chapter 1

# Introduction

Parallel computer simulation has been used as a tool to further scientific understanding for decades, as it provides a way to conduct experiments that would otherwise be too costly, dangerous, or impractical [7, 52, 58, 75, 76, 87]. Consequently, parallel programming systems and applications have evolved to improve their performance and scalability as computer systems have grown to higher degrees of parallelism. This, in turn, has led to a field of study concerning how best to structure, execute, and analyze massively parallel and distributed applications. In this work, we study all three of these aspects in the context of coupled message-passing programs used predominantly in the high-performance computing (HPC) domain.

### 1.1 Motivation

Hybrid parallel programming models that combine message passing (MP) and sharedmemory multithreading (MT) are becoming more popular, especially with applications requiring higher degrees of parallelism and scalability. Consequently, *coupled* parallel programs, those built via the integration of independently developed and

#### Chapter 1. Introduction

optimized software libraries linked into a single application, increasingly comprise message-passing libraries with differing preferred degrees of threading, resulting in *thread-level heterogeneity*. Retroactively matching threading levels between independently developed and maintained libraries is difficult, and the challenge is exacerbated because contemporary middleware services provide only static scheduling policies over entire program executions, necessitating suboptimal *over-subscribed* or *undersubscribed* configurations. In coupled applications, a poorly configured component can lead to overall poor application performance, suboptimal resource utilization, and increased time-to-solution. So it is critical that each library executes in a manner consistent with its design and tuning for a particular system architecture and workload. Therefore, there is a need for techniques that address dynamic, conflicting configurations in coupled multithreaded message-passing (MT-MP) programs.

### **1.2** Thesis Statement

Our thesis is that we can achieve significant performance improvements over today's static under-subscribed approach through reconfigurable execution environments that consider compute phase parallelization strategies along with both hardware and software characteristics.

### **1.3** Contributions and Organization

This dissertation presents new ways to structure, execute, and analyze coupled MT-MP programs. For the remainder of this section, we outline this document's structure, summarizing significant contributions along the way. Please note that a substantial amount of material in this dissertation has been presented or published in other venues:

#### Chapter 1. Introduction

Samuel K. Gutiérrez, Kei Davis, Dorian C. Arnold, Randal S. Baker, Robert W. Robey, Patrick McCormick, Daniel Holladay, Jon A. Dahl, R. Joe Zerr, Florian Weik, and Christoph Junghans. Accommodating Thread-Level Heterogeneity in Coupled Parallel Applications. In 2017 IEEE International Parallel & Distributed Processing Symposium (IPDPS), Orlando, Florida, 2017.

Samuel K. Gutiérrez, Dorian C. Arnold, Kei Davis, and Patrick McCormick. On the Memory Attribution Problem: A Solution and Case Study Using MPI. *Journal* on Concurrency and Computation: Practice and Experience (ExaMPI Special Issue Paper). To Appear.

**Chapter 2: Background:** We present an overview of core topics in parallel and distributed computation with a focus on concepts and techniques typical to HPC and their application to modeling and simulation. Related work and supplemental background material on specific topics are not presented here but instead located within relevant chapters that follow.

**Chapter 3:** Accommodating Thread-Level Heterogeneity: In this chapter, we study coupled MT-MP applications with dynamic, phased configuration conflicts. Focusing on applications based on the Message Passing Interface (MPI), we address the practical challenges of thread-level heterogeneity. We present a general methodology and corresponding implementation for dynamically (at runtime) accommodating coupled application configuration conflicts in a way that is composable, hardware topology aware, MPI implementation agnostic, works with a variety of unmodified Pthread-based parallel programming systems, increases overall system resource utilization, reintroduces lost parallelism, and is straightforward to incorporate into existing parallel applications. To the best of our knowledge, this is the first work to satisfy all of these criteria. Significant contributions of this work are summarized as follows:

- We examine contemporary approaches used to accommodate thread-level heterogeneity in coupled MT-MP programs. Here, we identify potential inefficiencies in how these coupled programs are currently structured and executed in the HPC domain.

- We present a novel approach for accommodating thread-level heterogeneity. Our approach enables full utilization of all available compute resources throughout an application's execution by providing programmable facilities to dynamically reconfigure runtime environments for compute phases with differing threading factors and affinities.

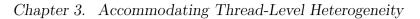

- We evaluate our methodology by applying it to three production-quality simulation codes employing a variety of parallelization strategies. Our performance results show that for a majority of the 30 tested scientific workloads our approach and corresponding open-source reference implementation, QUO, render speedups greater than 50% over the static under-subscribed baseline.

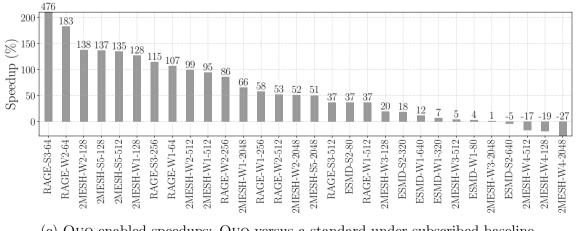

Chapter 4: Addressing The Memory Attribution Problem: We present the design and implementation of memnesia, a novel memory usage profiler for parallel and distributed message-passing applications. Our approach captures component-level memory usage statistics from unmodified binaries dynamically linked to a message-passing communication library. This work is motivated principally by the lack of parallel tools capable of extracting metrics relevant to our study in Chapter 5 concerning Quo-induced memory overhead. Significant contributions of this work are summarized as follows:

• We examine contemporary approaches in memory profiling and discuss their limitations as pertaining to what we call *the memory attribution problem*: the inability to predict or evaluate during runtime where the available memory is used across the software stack comprising the application, reusable software

libraries, and supporting runtime infrastructure needed to enable the application at a given scale, under a given workload, and in a time- and space-sharing scheduled environment.

- We propose an approach for accurate, per-process quantification of memory resource usage over time that is able to distinguish between application and MPI library usage clearly. With this new capability, we show that job size, communication workload, and hardware/software architecture can influence peak runtime memory usage.

- We develop a corresponding open-source profiling library named memnesia for applications using any implementation of the Message Passing Interface. We develop this software with a specific goal in mind: once memory attribution is better understood, applications will potentially be able to improve or maintain their memory utilization as they are developed, maintained, and deployed.

- We evaluate our memory profiler's runtime overhead and behavior using microbenchmarks. Here, we show that memnesia overheads are most apparent at small-message sizes, where its effect on operational latencies dominates messaging rates. Large-message bandwidth is least affected by the presence of memnesia instrumentation, as increased operational latencies are amortized over the transfer of larger payloads. That is, once a transfer is initiated, memnesia instrumentation has no appreciable effect on transfer rate.

- We discuss memnesia's memory overhead and application perturbation. For the former, we show that total memory overhead is proportional to  $2s \sum_{i=0}^{m-1} n_i$ , where the size of a single trace record s = 25 B, m is the total number of processes under memnesia supervision, and  $n_p$  is the total number of trace events triggered by process  $p \in \{0, 1, 2, ..., m-1\}$ . For the latter, we show that for a single process the amount of tool-induced application perturbation

is proportional to s times the number of trace records already collected by our event-driven profiler.

Chapter 5: Overhead of Adaptive Parallelism: A Case Study with Quo: Focusing on runtime and memory costs brought on by the use of our dynamic approach, we examine Quo's overhead using proxy and full applications. We show that Quo's overhead is modest, imposing small runtime and memory usage penalties over the static baseline. Our results are summarized as follows:

- We quantify the individual overhead costs for a representative set of Quo operations, showing that runtime operational latencies average  $\sim 2 \text{ ms}$  at 16 processes per node (PPN) across 128 nodes.

- We evaluate the overhead of QUO process quiescence by comparing two approaches, namely MPI\_Barrier() and QUO\_barrier(). Our results show that QUO\_barrier() significantly outperforms MPI\_Barrier() and is close to the ideal case where quiescence is not necessary. In particular, our approach introduces approximately an 8% overhead, while the naive approach using MPI\_Barrier() introduces approximately 116% overhead.

- We quantify data remapping overhead at different scales and input configurations using three scientific applications. Because of our approach's quiescing and later resumption of tasks (i.e., MPI processes), application data remappings across library domains may increase and are dependent on job scale and inter-domain data movement requirements. So we study those overheads as a function of job size and application workload in two distinct regimes. Our results show that in the worst case data remapping consumes approximately 15% of overall optimized application runtime—on average consuming about 4% across the 30 workloads tested.

#### Chapter 1. Introduction

• We study Quo-induced memory overhead, focusing on two sources: Quo runtime state and increased hardware subscription levels often required by our approach. For the former, our experiments show that Quo's memory footprint is influenced primarily by hardware/software architecture, job scale, and process distribution—averaging across the 18 experiments ~1.4 MB of additional memory per process. For the latter, we show that the cost of maintaining additional MPI processes is hardware-subscription-, platform- and implementationdependent, averaging across the 18 configurations tested ~14 MB per process.

Chapter 6: Conclusion: We conclude with a summary of our results and discuss opportunities for future work.

## Chapter 2

# Background

In this chapter, we present an overview of core topics in parallel and distributed computation with a focus on concepts and techniques typical to HPC and their application to modeling and simulation. We begin with a discussion of parallel computer architectures and programming models, focusing on Flynn's taxonomy and execution models that are of particular interest to this work. We then discuss HPC platforms and describe how they are commonly programmed. Finally, we conclude with a short description of parallel speedup.

## 2.1 Parallel Computers and Execution Models

A parallel computer comprises a potentially distributed collection of connected components (processors and memories) that work cooperatively to solve a computational problem. A standard way to classify these machines is Flynn's taxonomy, which categorizes computers according to the number of data streams and instruction (or control) streams they have [39]. In total there are four possibilities: SISD, MISD, SIMD, and MIMD.

Chapter 2. Background

Figure 2.1: Flynn's computer taxonomy.

Single Instruction Stream, Single Data Stream (SISD): A sequential computer architecture exploiting neither instruction stream nor data stream parallelism as shown in Figure 2.1a.

Multiple Instruction Streams, Single Data Stream (MISD): An uncommon parallel computer architecture exploiting instruction stream parallelism on a single stream of data as shown in Figure 2.1b.

Single Instruction Stream, Multiple Data Streams (SIMD): A parallel com-

#### Chapter 2. Background

puter architecture exploiting data stream parallelism, where a single operation, such as a multiply, is applied to multiple data simultaneously as shown in Figure 2.1c.

Multiple Instruction Streams, Multiple Data Streams (MIMD): A parallel computer exploiting both instruction stream and data stream parallelism wherein multiple autonomous processors execute different operations on different data as shown in Figure 2.1d. The MIMD classification can be divided into two parallel execution models: SPMD and MPMD.

Single Program, Multiple Data Streams (SPMD): The most common parallelization strategy used in the high-performance computing domain. Developed by Darema et al. [34], SPMD is characterized by a set of cooperating tasks executing the same program while operating on multiple pieces of data.

Multiple Programs, Multiple Data Streams (MPMD): A parallel execution model that extends the SPMD model to multiple programs.

### 2.2 High-Performance Computing Platforms

HPC platforms are built for executing parallel numerical calculations of modeled systems. These parallel computer simulations are used across a broad range of scientific disciplines because they provide a way to conduct experiments that would otherwise be too costly, dangerous, or impractical. As a consequence, the compute capability of high-performance computing systems has grown exponentially over the last two decades (Figure 2.2) to keep pace with increasingly ambitious goals such as modeling complex physical phenomena through coupled multi-physics simulation [42].

Large-scale parallel computer simulations require an enormous amount of parallelism and memory capacity, so they must execute on parallel computers based on a distributed memory architecture in which compute nodes with local processors

Chapter 2. Background

Figure 2.2: Performance development of HPC systems as recorded by the TOP500.

and memories are networked to create a larger system—a *supercomputer*. Below we present architectural details of the top 10 supercomputers according to the November 2017 TOP500 list (Table 2.1) and show the scales at which they operate (Table 2.2).

| System     | Node Architecture                             | Network                 |  |

|------------|-----------------------------------------------|-------------------------|--|

| TaihuLight | Sunway SW26010 260C                           | Sunway                  |  |

| Tianhe-2   | Xeon E5–2692v2 12C, Xeon Phi $31\mathrm{S1P}$ | Express-2 Fat-Tree [74] |  |

| Piz Daint  | Xeon E5–2690v3 12C, Tesla P100                | Aries Dragonfly [8]     |  |

| Gyoukou    | Xeon D-1571 16C, PEZY-SC2                     | Infiniband EDR          |  |

| Titan      | Opteron 6274 16C, Tesla K20x                  | Gemini 3D Torus [9]     |  |

| Sequoia    | IBM Power BQC 16C                             | BG/Q 5D Torus [29]      |  |

| Trinity    | Xeon E5–2698v3 32C, Xeon Phi $7250\ 68C$      | Aries Dragonfly         |  |

| Cori       | Xeon E5–2698v3 32C, Xeon Phi $7250\ 68C$      | Aries Dragonfly         |  |

| Oakforest  | Xeon Phi 7250 68C                             | Omni-Path Fat-Tree [72] |  |

| K Computer | SPARC64 VIIIfx 8C                             | Tofu 6D Torus [6]       |  |

Table 2.1: Node and network architectures of contemporary HPC platforms.

Chapter 2. Background

| System                                                                               | Node Count  | Core Count | Memory Capacity      | Rmax          |  |

|--------------------------------------------------------------------------------------|-------------|------------|----------------------|---------------|--|

| TaihuLight                                                                           | 40,960      | 10,649,600 | $1,\!311\mathrm{TB}$ | 93,015 TFLOPS |  |

| Tianhe-2                                                                             | 16,000      | 3,120,000  | $1,\!375\mathrm{TB}$ | 33,863 TFLOPS |  |

| Piz Daint                                                                            | 5,320       | 361,760    | $438\mathrm{TB}$     | 19,590 TFLOPS |  |

| Gyoukou                                                                              | $1,250^{1}$ | 19,860,000 | $576\mathrm{TB}$     | 19,136 TFLOPS |  |

| Titan                                                                                | 18,688      | 560,640    | 710 TB               | 17,590 TFLOPS |  |

| Sequoia                                                                              | 98,304      | 1,572,864  | $1,536\mathrm{TB}$   | 17,173 TFLOPS |  |

| Trinity                                                                              | 19,392      | 979,968    | $2,163\mathrm{TB}$   | 14,137 TFLOPS |  |

| Cori                                                                                 | 12,076      | 735,200    | $1,469\mathrm{TB}$   | 14,015 TFLOPS |  |

| Oakforest                                                                            | 8,208       | 558,144    | 919 TB               | 13,555 TFLOPS |  |

| K Computer                                                                           | 88,128      | 705,024    | $1,410\mathrm{TB}$   | 10,510 TFLOPS |  |

| $^{-1}$ A node is defined here as eight SC2 chips connected to a single Xeon D-1571. |             |            |                      |               |  |

Table 2.2: The scales at which contemporary supercomputers operate.

## 2.3 Parallel Programming Environments

Most parallel and distributed scientific applications (or software libraries) are programmed using general-purpose languages parallelized via optimizing compiler techniques (e.g., automatic vectorization), language features or extensions (e.g., parallel loop constructs), or runtime/middleware system services (e.g., collective inter-process communication). Supercomputers offer a hierarchy of exploitable concurrency, so parallelism in scientific programs is achieved by combining approaches that best suit each level of an architecture-defined hierarchy. An example is the use of messagepassing SPMD for coarse-grained parallelism in which distributed tasks also exploit loop- and instruction-level parallelism from within a node. Below we describe popular approaches used in contemporary scientific software engineering.

#### Chapter 2. Background

## 2.3.1 Message Passing

In the context of parallel programming models, message passing is a way of structuring cooperation between a collection of tasks executing concurrently on a parallel computer. In this model, tasks cooperate by sending messages to one another; so the sharing of data by other means, for example, shared memory, is prohibited. Data may be exchanged between cooperating tasks using *synchronous* or *asynchronous* messages, or a combination thereof. The former requires synchronization between a sender and receiver such that the receiver is *ready* for receipt of a message before the sender initiates transmission, whereas asynchronous messaging is less restrictive in that a message may be sent to a task before it is ready (or able) to receive data. The exchange of data between a single sender and a single receiver is called *point-to-point communication*. The generalization of this concept, which allows for the transfer of data between multiple senders and receivers, is called *collective communication*. For more information about message passing models, consult the seminal works by Hewitt et al. [54], Baker and Hewitt [16], Hoare [55], Valiant [99], and Milner [79].

Now that we have a general understanding of the message passing model let us now focus on a particular message passing specification: MPI, the Message Passing Interface [78]. MPI is a portable application programming interface (API) specification for point-to-point communication with extensions to the canonical message passing model that includes collective communication, remote memory access (RMA) operations, dynamic process creation, and parallel file input/output (I/O). Function calls defined by the standard's C and Fortran language bindings express these operations, though other language bindings exist outside the standard's purview. For over twenty years, MPI has served as the de facto message passing standard for parallel and distributed scientific applications. Thus, a tremendous amount of software infrastructure has been designed and built around its specification, which has undergone two major revisions since its official debut in 1994. Chapter 2. Background

## 2.3.2 Shared-Memory Multithreading

In the shared-memory model, a collection of tasks share a common address space, and any data that are not explicitly designated as *task-local*, accessible only to a single task, are shared. Tasks are allowed to read and write shared data structures asynchronously, so multithreaded programs are carefully structured to avoid *race conditions*, undesirable non-determinism that can affect program correctness. Because scientific applications require large amounts of memory, shared-memory parallelization strategies cannot be used without a distributed-memory component. Consequently, hybrid approaches combining shared-memory multithreading and message passing are becoming commonplace in scientific software (details in Chapter 3).

## 2.4 Parallel Speedup

Speedup is a standard metric used to assess the scalability of parallel programs. For a fixed problem size, x, speedup is defined as follows:

$$S(p,x) = \frac{T(1,x)}{T(p,x)},$$

(2.1)

where T(1, x) is the time taken by an optimized sequential program to perform a given computation on a single processor and T(p, x) is the time taken to perform the same calculation in parallel using p processors. Measuring speedups in this way quantifies a parallel program's *strong scaling* characteristics for a given workload at increasing processor counts. By contrast, *weak scaling* measures speedups as a function of both problem size and processor count and assumes a fixed problem size per processor, so speedup in this regime is defined as

$$S(p, x \cdot p) = \frac{T(1, x)}{T(p, x \cdot p)}.$$

(2.2)

Demonstrating strong scaling requires solving a fixed problem size faster as p increases, while demonstrating weak scaling requires solving increasing larger problems within a fixed amount of time.

Chapter 2. Background

## 2.5 Summary

In summary, supercomputers can be structured and programmed in different ways. Some are built entirely from commodity components, a classic example is a Beowulf cluster [20], while others opt for custom hardware altogether—the approach used for TaihuLight. More commonly, though, a graded approach is taken where both custom and commodity technologies are integrated into a single distributed memory machine. As an example let us consider the architectural features of the computers listed in Table 2.1. Here we will notice that the majority (9/10) are built using commodity technologies interconnected by specialized high-speed networks. With this diversity, achieving program and performance portability is challenging, so parallelism is achieved and expressed in different ways.

## Chapter 3

# Accommodating Thread-Level Heterogeneity

Parallel and distributed software such as multi-physics applications play crucial roles in science and engineering. Because of their interdisciplinary nature, these applications are often coupled, that is, built via the integration (or coupling) of independently developed and optimized software libraries linked into a single application. As previously described, in such coupled applications, a poorly performing library can lead to overall poor application performance, suboptimal resource utilization, and increased time-to-solution, so it is critical that each library executes in a manner consistent with its design and tuning for a particular system architecture and workload. Generally, each library (*input/compute phase pair*) has its optimal *runtime configuration*, for example, number and placement of processes or threads. In coupled applications, effective configuration parameters are determined (most often heuristically, manually, and offline) for all performance-critical computational phases.

*Configuration conflicts* arise when an optimal configuration for one phase is suboptimal for another, and there are a variety of approaches for resolving configuration

conflicts. At one extreme lie applications written to parallel and distributed programming systems such as Legion [18] and Charm++ [62], which by design resolve such conflicts at runtime. At the other extreme lie MT-MP applications that use message passing for inter- and intra-node parallelism and multithreading for additional intra-node parallelism, where the common approach is to allocate resources to satisfy the most demanding compute phase. The library with the highest degree of threading per process has one processing element per thread, and libraries with fewer threads per process run under-subscribed, using only a fraction of the available compute resources when running.

In this chapter, we study coupled MT-MP applications with dynamic, phased configuration conflicts. Focusing on applications based on the Message Passing Interface, we address the practical challenges of thread-level heterogeneity, where a coupled application comprises MPI libraries requiring different degrees of thread-level parallelism. We present a general methodology and corresponding implementation for dynamically (at runtime) accommodating coupled program configuration conflicts in a way that is composable, hardware topology aware, MPI implementation agnostic<sup>1</sup>, works with a variety of unmodified Pthread-based parallel programming systems, increases overall system resource utilization, reintroduces lost parallelism, and is straightforward to incorporate into existing applications. To the best of our knowledge, this is the first work to satisfy all of these criteria. Finally, we evaluate our methodology by applying it to three production-quality simulation programs that employ a variety of parallelization strategies. Our results show that significant performance improvements are achievable when used in environments positioned to make effective use of the additional levels of parallelism our approach enables.

<sup>&</sup>lt;sup>1</sup>So long as the underlying representation of an MPI process is a system process. This is true for most MPI implementations with one notable exception: MPC-MPI [81, 82].

## 3.1 Coupled Applications and Their Challenges

As previously described, parallel applications are often built by coupling independently developed and optimized software libraries. For example, coupled physics applications are often implemented in a fashion where each physics library, in turn, updates common application state data. Such scientific libraries tend to have their preferred data discretization scheme, for example, unstructured meshes, regular meshes, or particles, so they manage their distributed state and parallelization strategies with little or no coordination across library boundaries. More generally, libraries interact by exchanging data through APIs that remap data from one library domain to another, for example, from a field defined on a computational mesh to a system of linear equations, or from one mesh to another as illustrated in Figure 3.1. Quite often, such data structure remappings suggest complementary remappings of tasks to hardware. Inter-library interactions can take place many times during the lifespan of an application. Furthermore, at a given program point these interactions may change during a simulation to accommodate new requirements, for example, particular physics appropriate for a specific spatial scale and resolution.

Figure 3.1: Notional illustration of computational phases interleaved with data structure remapping phases across library domains.

## 3.1.1 Parallelism

Parallel scientific application executions exploit data parallelism, where many instances of the same computation execute in parallel on different data and on different computational resources. In the canonical MP model, message passing is used for both inter- and intra-node parallelism (other than SIMD vectorization). For MPI applications this is called *MPI-everywhere*. In this model, computational resources are usually *fully subscribed*, that is, the program's set of single-threaded processes is in one-to-one correspondence with processing elements (i.e., cores or hardware threads) and parallelism is realized via either SPMD or MPMD schemes. Alternatively, a scientific application can employ a hybrid model using multithreaded message passing (MT-MP) for inter- and intra-node parallelism. For MPI applications, MT-MP is an instance of the more general MPI+X model in which applications employ additional on-node parallelization strategies. This approach is increasingly popular as core (or hardware thread) counts increase in shared-memory nodes, and because of the flexibility and performance potential of a hierarchical approach [26, 53, 73].

While MPI+X is gaining popularity, it is not ubiquitous. Restructuring large, mature code bases to exploit new parallel programming systems effectively is challenging and generally requires a significant amount of effort that is often unjustifiable because of cost or priority. Furthermore, it is not uncommon that an MPI-everywhere version of a scientific code performs as well as or better than its MPI+X instantiation [15, 69], which discourages speculative hybridizing of existing programs. Finally, while an MPI+X library may be written such that its runtime configuration is settable within some range at startup, the particular runtime parameters that give the best performance may depend on static or dynamic variables such as input and problem scaling factors. For all of these reasons, coupled scientific codes will for the foreseeable future continue to be built from libraries that use a mix of non-uniform runtime configurations as illustrated in Figure 3.2. A runtime configuration may

Figure 3.2: Interleaved phases of a coupled thread-heterogeneous message-passing application with non-uniform runtime configuration requirements.

include the total number of processes to use for SPMD or MPMD parallelism, a process threading degree for shared-memory multithreading, and a mapping of tasks (processes and threads) to compute resources, for example, PEs and memories.

## 3.1.2 Conflicting Configuration Requirements

For decades coupled applications had relatively uniform library configuration requirements because they were built from single-threaded message-passing libraries, so static configurations set at application launch were sufficient. Today, however, configuration conflicts are common in coupled applications because they comprise independently developed and maintained scientific libraries that have been written or ported to hybrid MT-MP programming models.

#### Static Configurations

In today's static computing environments, dynamically accommodating inter-library configuration conflicts is difficult. While it is well understood that binding tasks to hardware resources can improve the performance of an MPI application [25, 43], parallel application launchers such as orterun [27], srun [103], aprun [66], and Hydra [71] allow only static allocations and static binding capabilities: launch-time configura-

tions persist for the entire parallel application's execution. Most single-threaded applications are launched by binding a single PE dedicatedly to each process. This approach mitigates ill effects of task migration in multiprocessor architectures, for example, cache invalidation that occurs when a thread moves from one PE to another.

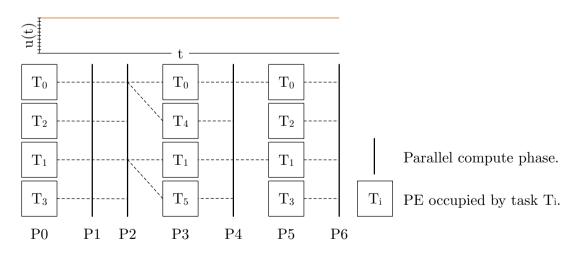

Given a static configuration for coupled MT-MP applications with conflicting configurations, the two primary configuration options are *over-subscription* and *undersubscription*. In over-subscribed configurations, all allocated resources are always in use, that is, the number of PEs equals the number of threads in the computational phase with the lowest degree of threading per process. In phases that require more threads, resources are over-subscribed with multiple threads per PE. Figure 3.3 illustrates the evolution of an over-subscribed MPI+X configuration where hardware utilization u(t) remains constant at 100%. In this example, MPI-everywhere phases fully subscribe hardware resources (phases P0-P2, P5-P6), while multithreaded regions over-subscribe them (phases P3-P4). In practice, over-subscription is generally avoided because increased resource contention in the threaded regions tends to affect overall application performance and scalability negatively [101].

Figure 3.3: Compute resource utilization u(t) by tasks (processes and threads) over time of a static over-subscribed MPI+X configuration.

Chapter 3. Accommodating Thread-Level Heterogeneity

Figure 3.4: Compute resource utilization u(t) by tasks (processes and threads) over time of a static under-subscribed MPI+X configuration.

The standard approach for accommodating thread-level heterogeneity in coupled MPI applications is to statically (at application launch time) under-subscribe compute resources such that the computational phase with the highest degree of threading per MPI process has one PE per software thread. As a consequence, phases with fewer threads per process use only a fraction of the available compute resources, thus leading to poor system resource utilization. Figure 3.4 illustrates the evolution of compute hardware resource utilization over time for a typical MPI+X configuration. Over time, hardware utilization fluctuates between 50 % and 100 % as the application moves in and out of regions with differing degrees of multithreading.

#### Lost Parallelism Through Resource Under-Subscription

Given an application that strong-scales perfectly (the theoretical upper bound), we can calculate the theoretical slowdown of static under-subscription approaches using Amdahl's law [11],

$$S = \left(\sum_{i=1}^{m} \frac{p_i}{s_i}\right)^{-1},\tag{3.1}$$

where n is the total number of available processors; m is the total number of phases;  $t_i$  is the optimal threading degree for a phase i;  $t_{max} = \max(t_1, \ldots, t_m)$ ;  $u_i = t_i/t_{max}$ is a phase's processor under-subscription factor; and  $s_i = n \cdot u_i$  is the speedup factor for a given phase. Consider two serial phases L1 and L2 whose percentages of execution time are equal:  $p_1 = 0.5$  and  $p_2 = 0.5$ . Assuming L1 runs optimally with an MPI-everywhere parallelization strategy and L2 optimally with an MPI+X strategy, Figure 3.5 plots the theoretical speedups of three under-subscribed runtime configurations where L1's threading degree is fixed at  $t_1 = 1$  and L2's varies. We compare those to an idealized configuration (Ideal) where each phase of the parallel computation is exposed to all available PEs. This simple model illustrates the potential losses in parallelism resulting from today's static under-subscription approach.

In summary, coupled scientific applications based on the MT-MP model can comprise libraries with conflicting configuration requirements. For such applications, today's static computational environments necessitate suboptimal over-subscribed or under-subscribed configurations. Therefore, there is a need for techniques that address dynamic, conflicting configurations in coupled MT-MP applications.

Figure 3.5: Log-log plot of modeled speedups showing the potential losses in parallelism resulting from under-subscription as a function of scale.

## **3.2** Background and Related Work

In this section, we begin with a discussion of portable hardware locality and abstract hardware representation, focusing exclusively on techniques and software systems used in this work. We then discuss related topics in multiprocessor scheduling, affinity scheduling, and runtime configuration conflict resolution.

### 3.2.1 Portable Hardware Locality

Contemporary HPC node architectures are complex and diverse, demanding careful consideration of their processor and memory configurations. To effectively guide the dynamic (runtime) mapping of application-specific software (logical) affinities to hardware resources, one must be able to obtain both the underlying platform's resource information and the application's current usage of those resources. To that end, we use hwloc [25, 44], an open-source software library that provides services to gather such information at runtime from the most popular and widely used operating systems in HPC. Operating system and hardware portability are achieved by the library's use of Standard C (ANSI/ISO C), a common, widely supported C standard, and a plugin architecture that allows for back-end component specialization.

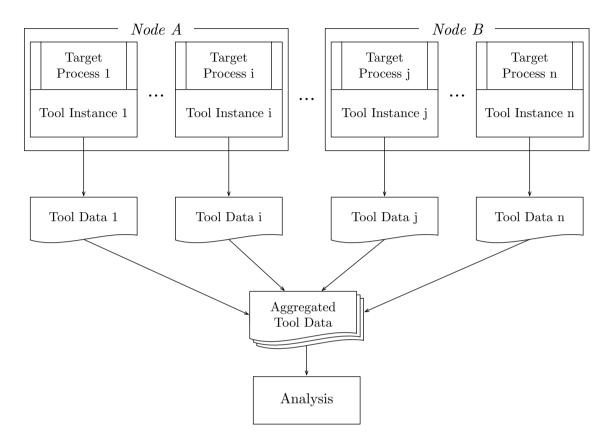

#### 3.2.2 Abstract Hardware Representation

hwloc represents hardware information as a k-ary tree of typed hardware objects that carry additional information through type-appropriate attributes, for example, cache level and size. The topology formed by these objects represents memory and processor relationships existing in hardware, including cache, NUMA, and other general hardware affinities such as those existing when processing elements are packaged together within a socket. Further, abstract hardware topologies need not be *full* (for

|          |          |          | 32 G     | B ] | RAM      |          |          |          |

|----------|----------|----------|----------|-----|----------|----------|----------|----------|

| Socket 0 | Socket 0 |          |          |     |          |          |          | Socket 1 |

| 4 M      | B L2     | 4 M      | B L2     |     | 4 M      | B L2     | 4 M      | B L2     |

| 32 kB L1 | 32 kB L1 | 32 kB L1 | 32 kB L1 |     | 32 kB L1 | 32 kB L1 | 32 kB L1 | 32 kB L1 |

| PE 0     | PE 1     | PE 2     | PE 3     |     | PE 4     | PE 5     | PE 6     | PE 7     |

Figure 3.6: Schematic of a machine with two quad-core sockets.

Figure 3.7: Hardware topology of the machine diagrammed in Figure 3.6.

all levels each node has exactly 0 or k children), symmetric (being a mirror image of itself), or homogeneous (built from exactly one type of memory or processor), and so can represent complex hardware configurations. The binary tree shown in Figure 3.7 depicts the compute node architecture diagrammed in Figure 3.6, namely a uniform memory access (UMA) machine built from two quad-core sockets, where each core has a dedicated level one cache (L1) and a shared level two (L2).

## 3.2.3 Multiprocessor Scheduling

MULTIPROCESSOR SCHEDULING (MSP) is a well-known optimization problem that can be stated as follows: given q processors and n tasks of varying lengths, find a *schedule*—an assignment of n tasks to q processors—with minimal total length. Because of the problem's considerable importance and due to its computational intractability (MSP is known to be NP-hard [19, 41]), many efficient heuristics have been proposed and studied [12, 31, 57, 67, 77, 91, 100]. Here, we focus on a few that align with our primary interests.

#### Affinity Scheduling

Markatos and LeBlanc studied *affinity scheduling* in their work concerning loop scheduling algorithms for shared-memory multiprocessors [77]. Their results show that parallel workloads on such systems can benefit from scheduling policies that exploit data locality in caches and local memories during parallel loop iteration assignment to processors. Their work builds on that of Squillante and Lazowska, which shows that locality-indifferent scheduling increases the *cache-reload transient penalty*—the cache misses caused by bringing a task's working set from main memory into cache as it is reinitiated after being suspended temporarily [96]—thus negatively affecting both individual task and overall system performance [91].

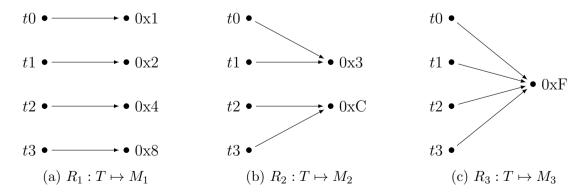

An affinity schedule is given by a potentially dynamic specification that exploits application-specific features (e.g., adjacency graphs, parallelization strategies) to improve upon application-oblivious schedules. The problem can be stated as follows: given q processors and a set of cooperating tasks T, find a set of task scheduling directives M and a binary relation  $R : T \mapsto M$  that minimizes T's makespan. Most often the derivation of M and R involves offline manual experimentation, but automated techniques have been proposed and studied in the literature [5, 21, 22, 23, 60, 61, 88, 89]. A task's *CPU affinity mask* determines the set of processors  $\hat{P}$  on which it is eligible to run and is defined as follows: given q linearly ordered processors  $P = \{p_0, p_1, p_i, \ldots, p_{q-1}\}$ , let m be a least significant bit zero (LSB-0) string defined by  $m_i \leftarrow 1$  if use of  $p_i$  is permitted and  $m_i \leftarrow 0$  otherwise,

so  $\hat{P} = \{p_i \mid 0 \leq i < n, m_i = 1\}$ . To better understand what we mean, consider the following scenarios given four processors  $P = \{p0, p1, p2, p3\}$  and as many cooperating tasks  $T = \{t0, t1, t2, t3\}$ . Relation  $R_1$ , diagrammed in Figure 3.8a, represents a configuration commonly used for single-threaded data-parallel workloads: a processor is dedicated to a single thread of execution to minimize task migration costs. If we let  $T_l = \{0, 1\}$  and  $T_u = \{2, 3\}$  be two multithreaded processes taken from T, then Figure 3.8b represents a typical configuration used to influence the schedule of multithreaded data-parallel workloads: each multithreaded process is given a set of dedicated processing elements so that threaded regions can execute in parallel while maintaining some memory locality—an especially important point on NUMA architectures. Finally, the relation shown in Figure 3.8c represents a completely permissive scheduling policy. That is, each task is runnable (can be scheduled) on any available processor. In practical terms this means that the operating system's scheduler can assign tasks to resources in any way it sees fit, most likely using completely fair scheduling.

$$M_{1} = \{0001_{2} \ (0x1), 0010_{2} \ (0x2), 0100_{2} \ (0x4), 1000_{2} \ (0x8)\} \}$$

$$M_{2} = \{0011_{2} \ (0x03), 1100_{2} \ (0xC)\},$$

$$M_{3} = \{1111_{2} \ (0xF)\}$$

Figure 3.8: Example task to affinity mask relations.

## 3.2.4 Current Approaches in HPC

Affinity scheduling has proven useful for improving HPC workload performance [25, 43, 60, 90], so much that, in one form or another, it is regularly used in practice. Today, the majority of parallel applications use static affinity (or *binding*) policies characterized by their use of a single, persistent configuration set during parallel application startup. Most single-threaded applications are launched by binding a single processing element dedicatedly to each process to mitigate the ill effects of task migration, for example, cache invalidation occurring when a task moves from one processing element to another. In contrast, multithreaded applications tend to favor less restrictive process binding policies that allow for maximal hardware-level parallelism during the execution of threaded regions, meaning in practical terms that a CPU affinity mask is chosen so a process's threads are eligible for execution on an appropriate number of processing elements.

Hybridizing MPI applications has been studied extensively [30, 36, 84, 85]. These works suggest that choosing between MPI-everywhere and MPI+OpenMP is a nontrivial task involving careful consideration regarding, but not limited to, algorithmic choices in the application and the characteristics of the target architecture. These works evaluate MPI+OpenMP schemes that use a static under-subscription approach, whereas we present a general methodology to dynamically accommodate a broader set of Pthread-based MPI+X schemes that additionally consider both data and hardware localities at runtime.

The study of dynamic process and memory binding methodologies that consider application, data, and hardware localities is not new. Broquedis et al. present and evaluate hwloc by incorporating it into MPI and OpenMP runtimes to dynamically guide task affinities at runtime [25]. While similar in many respects, our work differs from theirs in that we present a general methodology for programmatically resolving

configuration conflicts in dynamic, phased Pthread-based MPI+X programs—a use case not considered in their work.

For HPC applications there are a variety of published approaches for efficiently resolving runtime configuration conflicts that arise in thread-heterogeneous environments. Carribault et al. present a unified runtime for both distributed- and shared-memory MPI+X codes [81, 82]. Unlike other MPI implementations, theirs implements MPI processes as user-level threads (instead of processes), so their scheduler can efficiently accommodate both single- and multi-threaded regions during the execution of an MPI+X application. In contrast, our approach is MPI implementation agnostic and exposes an API to programmatically influence task placement and scheduling at runtime. Huang et al. present another MPI implementation that uses processor virtualization to facilitate application adaptation, including thread-level heterogeneity [59]. Their approach, however, requires the use of their runtime and modified versions of others, for example, GNU OpenMP, whereas ours works with unmodified MPI and OpenMP runtimes. Other parallel and distributed programming systems such as Legion [18] and Charm++ [62] are designed to dynamically resolve runtime configuration conflicts, but once again require that applications be rewritten to their respective paradigms.

## 3.3 Adaptive Parallelism for Coupled MPI+X

Next we present a general, composable runtime approach for programmatically accommodating library configuration conflicts that arise in dynamic, coupled, threadheterogeneous MPI+X applications. Our design is influenced by requirements for generality, composability, efficiency, and pragmatism in the face of production HPC software realities, that is, easily fitting into large, established code bases that are still be under active development.

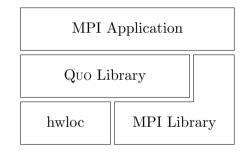

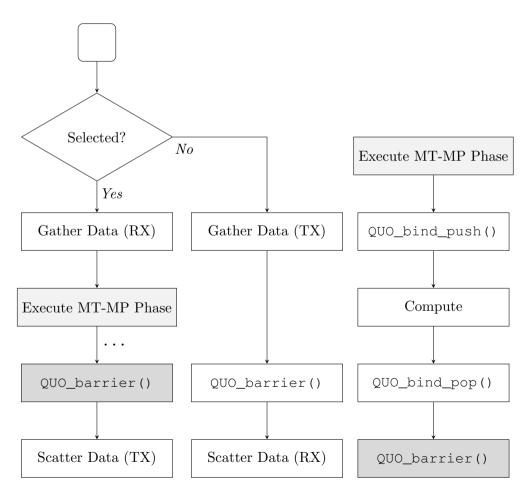

## 3.3.1 Adaptive Execution Environments with Quo

Quo (as in "status quo") is both a model and a corresponding implementation that facilitates the dynamically varying requirements of computational phases in coupled MT-MP applications. Specifically, Quo allows an application to dynamically query and reconfigure its process bindings. While the model is general, the current implementation focuses on Pthread-based MPI+X applications [49]. Fundamentally, Quo uses hwloc [25] and MPI, interfacing with those libraries and the application as shown in Figure 3.9. The hwloc library is used to gather system hardware topology information and to control process binding policy changes during the target application's lifetime. MPI is used primarily for exchanging setup information during Quo *context* (QC) setup, which is discussed in a later section.

Figure 3.9: QUO architecture diagram.

The portable, production-quality, open-source runtime library is written in C, but also provides C++ and Fortran language bindings. The Quo API operates on QC pointers. This design allows for the creation and manipulation of multiple QCs within a single application that are either encapsulated within a library or passed from one library to another—a key for composability. The remainder of this section presents the principle concepts and mechanisms that underlie our design and approach.

## 3.3.2 Quo Contexts

QUO contexts, which encapsulate state data gathered and manipulated by QUO, are created via a collective call to QUO\_create() in which all members of the initializing communicator must participate. QCs may be created at any time after the underlying MPI library has been initialized and remain valid until freed via QUO\_free(), which must occur before the MPI library has been *finalized*. QUO can maintain multiple independent, coexisting QCs within a single application.

## 3.3.3 Hardware/Software Environment Queries

As previously described in Section 3.2.1, contemporary HPC node architectures are complex and diverse, demanding careful consideration of their resource (PE and memory) configurations. To effectively guide the dynamic (runtime) mapping of application-specific software (logical) affinities to hardware resources, one must be able to obtain both the underlying platform's resource information and the application's current usage of those resources. In this regard, QUO's approach is straightforward: its API provides thin convenience wrappers around commonly-used hwloc hardware query routines for hardware information. Relevant hardware information includes memory localities relative to PEs in non-uniform memory access (NUMA) architectures and hierarchical hardware relationships (e.g., determining how many cores are contained in a particular socket).