## University of New Mexico UNM Digital Repository

**Computer Science ETDs**

**Engineering ETDs**

Fall 10-19-2017

# Improving HPC Communication Library Performance on Modern Architectures

Matthew G. F. Dosanjh University of New Mexico

Follow this and additional works at: https://digitalrepository.unm.edu/cs\_etds Part of the <u>Digital Communications and Networking Commons</u>, and the <u>OS and Networks</u> <u>Commons</u>

#### **Recommended** Citation

Dosanjh, Matthew G. F.. "Improving HPC Communication Library Performance on Modern Architectures." (2017). https://digitalrepository.unm.edu/cs\_etds/88

This Dissertation is brought to you for free and open access by the Engineering ETDs at UNM Digital Repository. It has been accepted for inclusion in Computer Science ETDs by an authorized administrator of UNM Digital Repository. For more information, please contact disc@unm.edu.

Matthew G. F. Dosanjh

Candidate

Computer Science

This dissertation is approved, and it is acceptable in quality and form for publication:

Approved by the Dissertation Committee:

Patrick G. Bridges , Chairperson

Ryan E. Grant

Anthony Skjellum

Dorian C. Arnold

## Improving HPC Communication Library Performance on Modern Architectures

by

## Matthew G. F. Dosanjh

B.S., Computer Science, University of New Mexico, 2010 M.S., Computer Science, University of New Mexico, 2013

## DISSERTATION

Submitted in Partial Fulfillment of the Requirements for the Degree of

> Doctor of Philosophy Computer Science

The University of New Mexico

Albuquerque, New Mexico

December, 2017

©2017, Matthew G. F. Dosanjh

# Dedication

To my friends and family for helping me through this... uhh... grad school thing.

"Everything is perfect, but there is a lot of room for improvement."

Shunryu Suzuki

# Acknowledgments

There are a number of people without whom this document would not exist. First I'd like to acknowledge my advisor, Patrick Bridges. His guidance has proved essential in my development as a researcher and in the development of this dissertation. Through working with him, I've learned how to develop research ideas, test and explore these ideas, and communicate results to the scientific community. The opportunities I have now can be traced back seven years to when I first had the opportunity to work with Patrick, and I am forever grateful.

During the last four years of my PhD, I have been extremely fortunate to hold an internship at Sandia National Laboratories<sup>1</sup>. During the majority of that time, Ryan Grant has served as a mentor and de facto second advisor. The skills and knowledge I gained from working with him have been invaluable. The time and effort he contributed to help increase my understanding of the field and discuss and evaluate research ideas has impacted every part of this dissertation.

I would also like to acknowledge the other two members of my committee. Dorian Arnold has always been willing provide in-depth constructive criticism which proved extremely useful to create the best and most polished work of my career. Tony Skjellum has provided useful feedback through his experience and unique area knowledge that helped me contextualize my work. Their contributions have greatly helped in the work and writing of this dissertation.

I would like to thank all my fellow students and friends at the Scaleable Systems Laboratory. David DeBonis, Noah Evans, Taylor Groves, Aaron Gonzales, Dewan Ibtesham, Scott Levy, Oscar Mondragon, Whit Schonbein, Philip Soltero, and Hans Weeks have all helped by providing feedback, advice, and a platform for discussing ideas. I'd also like to thank some of my other peers from other research groups and institutions: Sridutt Bhalachandra, Jeffery Bowels, Carl Evans, and George Stelle.

There were a number of people that helped guide me before I got to the path that led to this dissertation. Joel Castelanos gave me a chance to become a teaching assistant, for a class I was clearly unprepared to teach, and helped solidify my path to grad school. Andree Jacobson, through the Cluster and Network Management Institute, taught me the basics of cluster computing which ultimately led me to HPC as a research path. Suzanne M. Kelly, my first mentor at Sandia, gave me an opportunity to work on my first HPC research project and introduced me to the research group I continue to work with.

<sup>&</sup>lt;sup>1</sup>Parts of this research were supported by the Exascale Computing Project (ECP 17-SC-20-SC), a collaborative effort of the U.S. Department of Energy Office of Science and the National Nuclear Security Administration. Additionally, this research was performed in part at Sandia National Laboratories, supported by the U.S. Department of Energy contractcontract DE-NA0003525

Finally, I would like to thank my family for all the love and support I needed over the years. My wife, Marie, has always been there for me and pushed me forward through the rough times where I wanted to give up. My daughter, Athena, has given me a reason to wake up at 5:30 in the morning, whether I want to or not. My parents have always been there for advice and support over the years and are directly responsible for getting me hooked on math at an early age.

## Improving HPC Communication Library Performance on Modern Architectures

by

Matthew G. F. Dosanjh

B.S., Computer Science, University of New Mexico, 2010

M.S., Computer Science, University of New Mexico, 2013

Ph.D., Computer Science, University of New Mexico, 2017

### Abstract

As high-performance computing (HPC) systems advance towards exascale (10<sup>18</sup> operations per second), they must leverage increasing levels of parallelism to achieve their performance goals. In addition to increased parallelism, machines of that scale will have strict power limitations placed on them. One direction currently being explored to alleviate those issues are many-core processors such as Intel's Xeon Phi line. Many-core processors sacrifice clock speed and core complexity, such as out of order pipelining, to increase the number of cores on a die. While this increases floating point throughput, it can reduce the performance of serialized, synchronized, and latency sensitive code paths, such as traditional communication libraries.

In this thesis, I examine the impact of many-core processors on large-scale scientific applications and explore ways to improve performance for both future and legacy applications. I examine the effect by characterizing the performance and power tradeoffs for different core frequencies and network hardware. Then, I explore the viability of next-generation programming models by benchmarking the performance of communication libraries utilizing multi-threaded one-sided communication. Next, I improve communication library performance for legacy applications for many-core systems through optimizing the matching algorithm to leverage single instruction multiple data vectors and caching behavior. Finally, I explore two other matching algorithm optimizations targeted at next-generation processors and applications.

List of Tables

| List of Figures |  |  |

|-----------------|--|--|

|                 |  |  |

| 1 | Intr | oduction                                                           | 1 |

|---|------|--------------------------------------------------------------------|---|

|   | 1.1  | Modern HPC hardware                                                | 2 |

|   |      | 1.1.1 Many Lightweight Cores                                       | 2 |

|   |      | 1.1.2 Network Offload                                              | 3 |

|   |      | 1.1.3 High Bandwidth Memory                                        | 3 |

|   | 1.2  | The Message Passing Interface                                      | 4 |

|   |      | 1.2.1 Message Passing and Remote Memory Access                     | 4 |

|   |      | 1.2.2 Message Matching                                             | 4 |

|   |      | 1.2.3 Thread Modes                                                 | 5 |

|   | 1.3  | Design Challenges for Communication Libraries on Many-Core Systems | 6 |

|   |      | 1.3.1 Power                                                        | 6 |

|   |      | 1.3.2 Memory                                                       | 6 |

|   |      | 1.3.3 Parallelism                                                  | 7 |

|   | 1.4  | Contributions                                                      | 8 |

|   | 1.5  | Dissertation Outline                                               | 8 |

|   |      |                                                                    |   |

## 2 Related Work

xiv

xviii

|   | 2.1 | Introd | uction                                                                                              | 10 |

|---|-----|--------|-----------------------------------------------------------------------------------------------------|----|

|   | 2.2 | Messa  | ge Passing Interface (MPI)                                                                          | 10 |

|   |     | 2.2.1  | Matching                                                                                            | 11 |

|   |     | 2.2.2  | Threading $\ldots$ | 14 |

|   |     | 2.2.3  | One-Sided Communication                                                                             | 15 |

|   | 2.3 | MPI N  | Matching                                                                                            | 16 |

|   |     | 2.3.1  | Performance Studies                                                                                 | 16 |

|   |     | 2.3.2  | Data Structures                                                                                     | 17 |

|   |     | 2.3.3  | Matching Hardware                                                                                   | 18 |

|   | 2.4 | MPI f  | or Modern Architectures                                                                             | 20 |

|   |     | 2.4.1  | Multi-threading                                                                                     | 20 |

|   |     | 2.4.2  | Power and Energy                                                                                    | 21 |

|   | 2.5 | Other  | HPC Programming Models                                                                              | 22 |

|   |     | 2.5.1  | One-Sided Programming                                                                               | 22 |

|   |     | 2.5.2  | Many Task Programming                                                                               | 24 |

|   | 2.6 | Chapt  | er Summary                                                                                          | 24 |

| 3 | The | Powe   | r and Performance Effects of Many Core Processors                                                   | 25 |

|   | 3.1 | Introd | uction                                                                                              | 25 |

|   | 3.2 | Exper  | imental Methodology and Setup                                                                       | 26 |

|   |     | 3.2.1  | Hardware and Data Collection Setup                                                                  | 27 |

|   |     | 3.2.2  | Benchmarks and Applications                                                                         | 27 |

|   | 3.3 | Exper  | imental Results                                                                                     | 29 |

|   |     | 3.3.1  | Microbenchmark Evaluation                                                                           | 29 |

|   |     | 3.3.2  | Application Benchmark Evaluation                                                                    | 33 |

|   | 3.4 | Analy  | sis                                                                                                 | 38 |

|   | 3.5 | Conclu | usions                                                                                              | 41 |

| 4 | Nex | t Gen  | eration Parallel Programming Models                                                                 | 43 |

|   | 4.1                 | Introduction                                                                                                | 43         |

|---|---------------------|-------------------------------------------------------------------------------------------------------------|------------|

|   | 4.2                 | Benchmarks and Mini-applications                                                                            | 44         |

|   |                     | 4.2.1 Benchmarks                                                                                            | 44         |

|   |                     | 4.2.2 Miniapps                                                                                              | 48         |

|   | 4.3                 | Experimental Methodology                                                                                    | 49         |

|   | 4.4                 | Single Threaded Results                                                                                     | 50         |

|   | 4.5                 | Multi-Threaded Benchmarks                                                                                   | 53         |

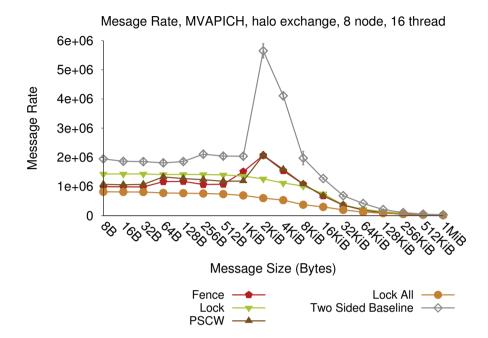

|   |                     | 4.5.1 MVAPICH Release                                                                                       | 54         |

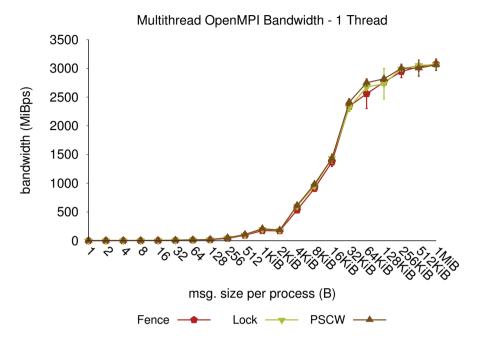

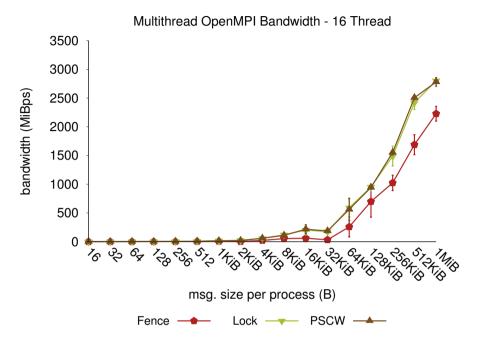

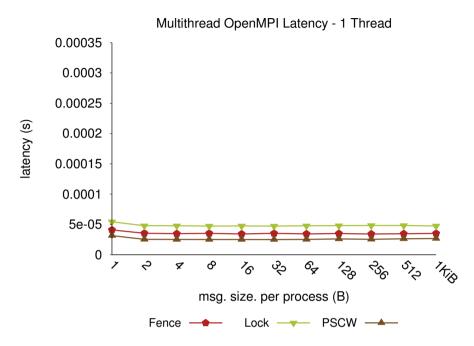

|   |                     | 4.5.2 Open MPI development branch                                                                           | 58         |

|   |                     | 4.5.3 Discussion                                                                                            | 63         |

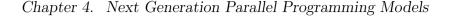

|   | 4.6                 | MiniApp Results                                                                                             | 64         |

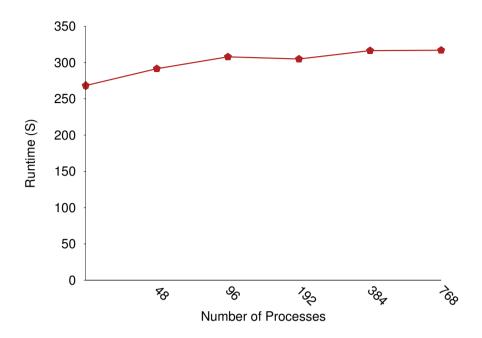

|   |                     | 4.6.1 HPCCG                                                                                                 | 65         |

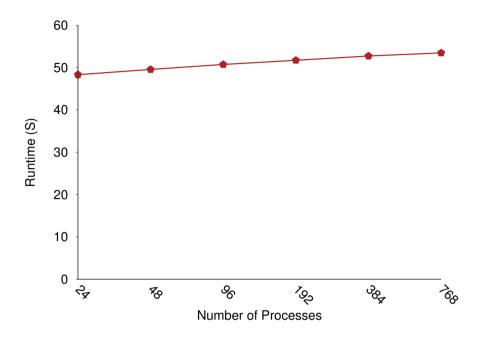

|   |                     | 4.6.2 MiniMD                                                                                                | 66         |

|   |                     | 4.6.3 MiniFE                                                                                                | 67         |

|   | 4.7                 | SHMEM Results                                                                                               | 68         |

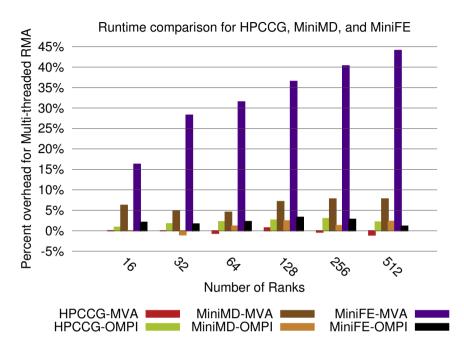

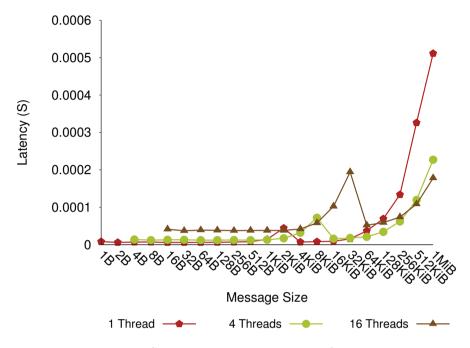

|   |                     | 4.7.1 Latency                                                                                               | 69         |

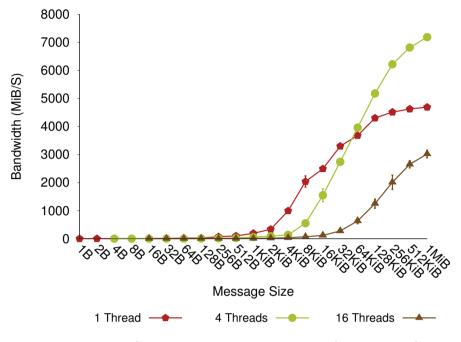

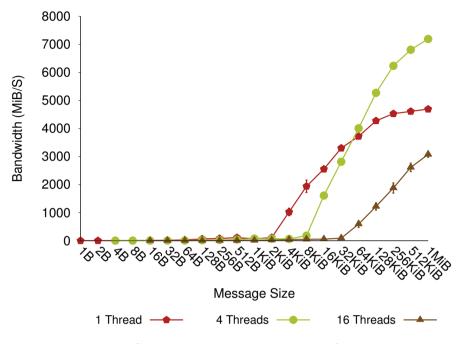

|   |                     | 4.7.2 Bandwidth                                                                                             | 70         |

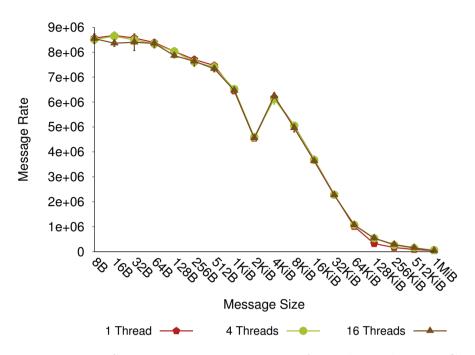

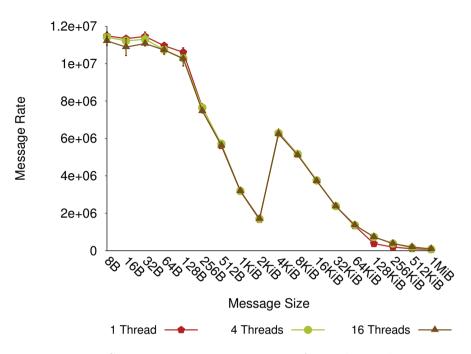

|   |                     | 4.7.3 Message Rate                                                                                          | 71         |

|   |                     | 4.7.4 MiniApp Results                                                                                       | 73         |

|   | 4.8                 | Analysis                                                                                                    | 74         |

|   | 4.9                 | Conclusions                                                                                                 | 77         |

| - | <b>N</b> <i>T</i> 4 |                                                                                                             | <b>7</b> 0 |

| 5 |                     |                                                                                                             | <b>78</b>  |

|   | 5.1                 | Introduction                                                                                                | 78<br>70   |

|   | 5.2                 | Background and Motivation                                                                                   | 79         |

|   | 5.3                 | MPI Matching Improvements                                                                                   | 81         |

|   |                     | 5.3.1 Linked List of Arrays                                                                                 | 83         |

|   |                     | 5.3.2 Intrinsics for AVX Vectors                                                                            | 84         |

|   |                     | 5.3.3 Hot Caching $\ldots$ | 86         |

| 5.4        | Experimental Results                                                                                                                                    | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | 5.4.1 Experimental Setup                                                                                                                                | 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | 5.4.2 Optimizations on Xeon Sandy Bridge                                                                                                                | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | 5.4.3 Optimizations on Xeon Broadwell                                                                                                                   | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | 5.4.4 Optimizations on Xeon Phi                                                                                                                         | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | 5.4.5 Application Study 9                                                                                                                               | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | 5.4.6 Full Application Study                                                                                                                            | )5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | 5.4.7 Discussion $\ldots \ldots \ldots$ | )9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 5.5        | Conclusions and Future Work                                                                                                                             | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Opt        | imizations For Future Matching Engine Architectures 11                                                                                                  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| -          |                                                                                                                                                         | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0.2        |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <b>C</b> D |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0.3        |                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|            | 6.3.1 Approach                                                                                                                                          | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | 6.3.2 New Vector Instructions                                                                                                                           | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | 6.3.3 Application Tag and Rank Characteristics                                                                                                          | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 6.4        | Experimental Results                                                                                                                                    | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | 6.4.1 Tail Queues Results                                                                                                                               | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | 6.4.2 Fuzzy Matching Results                                                                                                                            | 28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Con        | clusions and Future Work 14                                                                                                                             | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7.1        | Summary                                                                                                                                                 | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 7.2        | Future Work                                                                                                                                             | 12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| efere      | nces 14                                                                                                                                                 | 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | <ul> <li>5.5</li> <li><b>Opt</b>:</li> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li><b>Con</b></li> <li>7.1</li> <li>7.2</li> </ul>          | 5.4.1       Experimental Setup       8         5.4.2       Optimizations on Xeon Sandy Bridge       9         5.4.3       Optimizations on Xeon Broadwell       9         5.4.4       Optimizations on Xeon Phi       9         5.4.5       Application Study       9         5.4.6       Full Application Study       9         5.4.7       Discussion       10         5.5       Conclusions and Future Work       11         6.1       Introduction       11         6.2       Tail Queues       11         6.2       Tail Queues Architecture       11         6.3       Fuzzy Matching       11         6.3.1       Approach       11         6.3.2       New Vector Instructions       11         6.3.3       Application Tag and Rank Characteristics       11         6.4.1       Tail Queues Results       12         6.4.2       Fuzzy Matching Results       12 |

# List of Figures

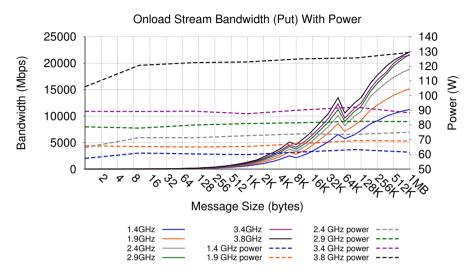

| 3.1  | Onload stream with varying CPU frequencies                                              | 30 |

|------|-----------------------------------------------------------------------------------------|----|

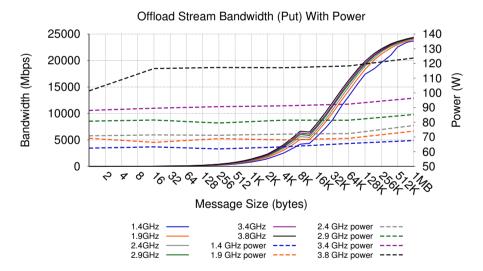

| 3.2  | Offload stream with varying CPU frequencies                                             | 30 |

| 3.3  | Onload stream with varying CPU frequencies without cache effects                        | 31 |

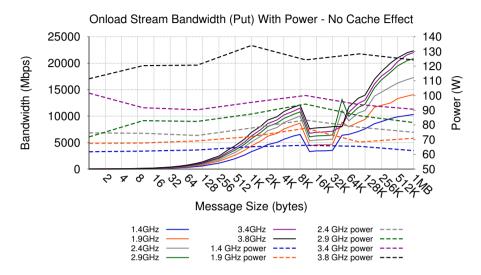

| 3.4  | Offload stream with varying CPU frequencies without cache effects                       | 31 |

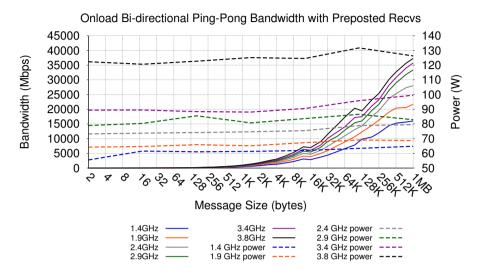

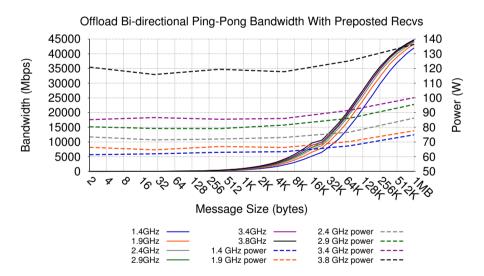

| 3.5  | Onload bi-directional ping-pong with send-recv and preposted recvs $\ldots$ .           | 32 |

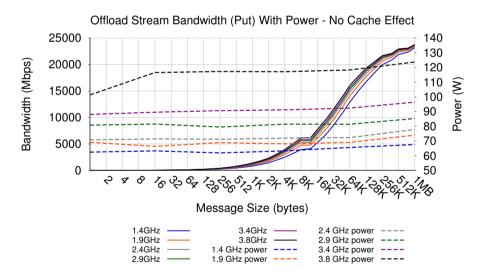

| 3.6  | Offload bi-directional ping-pong with send-recv and preposted recvs $\ldots$ .          | 32 |

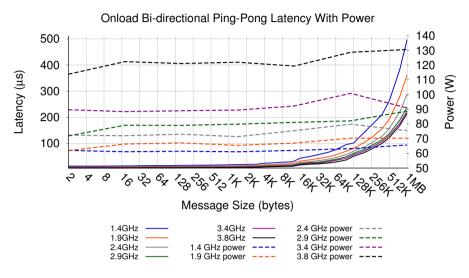

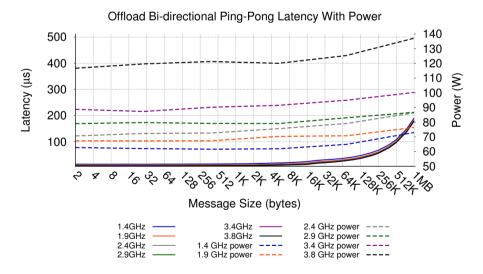

| 3.7  | Onload bi-directional ping-pong latency                                                 | 34 |

| 3.8  | Offload bi-directional ping-pong latency                                                | 34 |

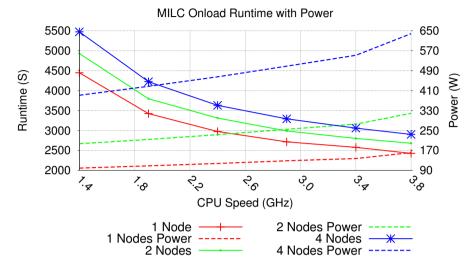

| 3.9  | Onload runs of the MILC application                                                     | 38 |

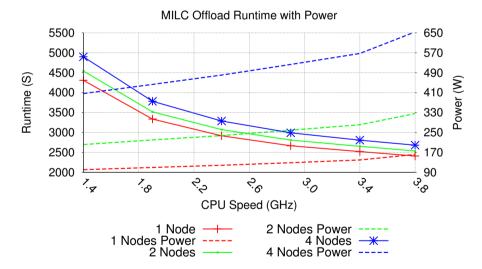

| 3.10 | Offload runs of the MILC application                                                    | 38 |

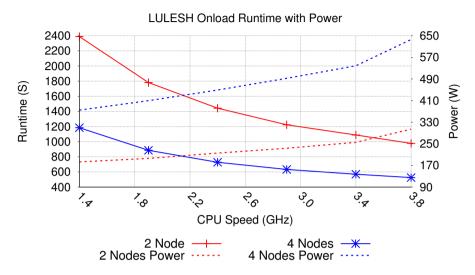

| 3.11 | Onload runs of the LULESH application                                                   | 39 |

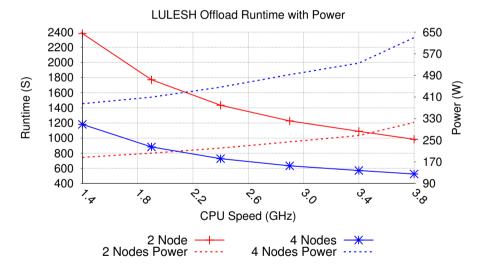

| 3.12 | Offload runs of the LULESH application                                                  | 39 |

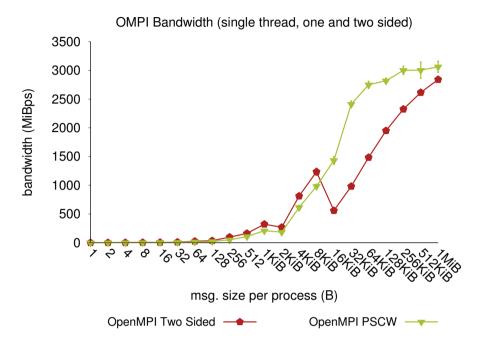

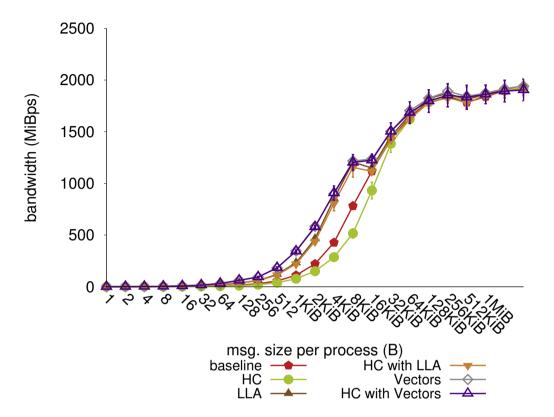

| 4.1  | Single threaded one-sided and two sided bandwidth Open MPI $\ . \ . \ . \ .$            | 51 |

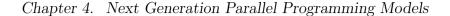

| 4.2  | Single threaded one-sided and two sided latency of Open MPI                             | 52 |

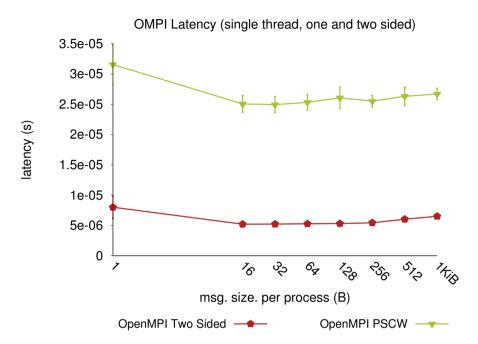

| 4.3  | Single threaded one-sided and two sided message rate of Open MPI                        | 53 |

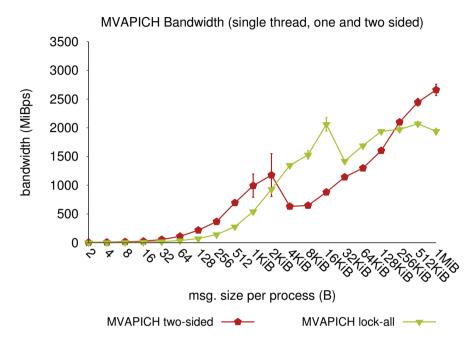

| 4.4  | Single threaded one-sided and two sided bandwidth of MVAPICH $\ \ . \ . \ .$            | 54 |

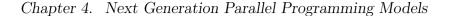

| 4.5  | Single threaded one-sided and two sided latency of MVAPICH $\ \ldots \ \ldots \ \ldots$ | 55 |

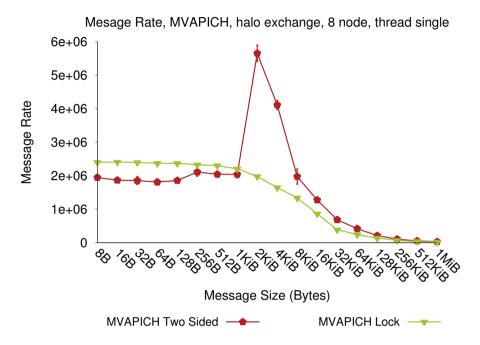

| 4.6  | Single threaded one-sided and two sided message rate of MVAPICH $\ . \ . \ .$           | 56 |

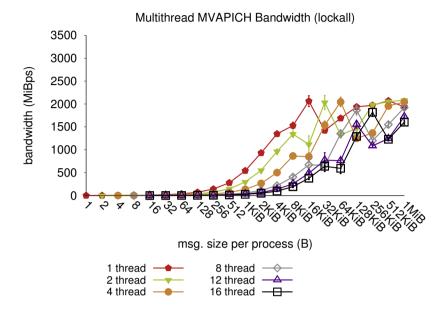

| 4.7  | MVAPICH bandwidth results for one-sided (lockall) communication $\ . \ . \ .$           | 57 |

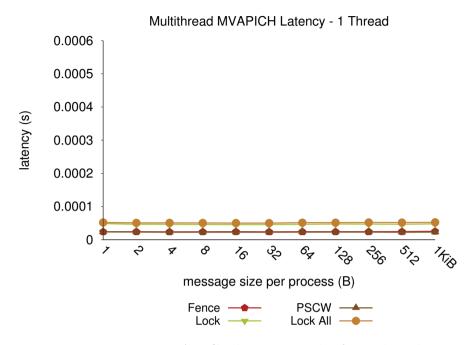

| 4.8  | MVAPICH latency results for 1 thread                                                    | 58 |

## List of Figures

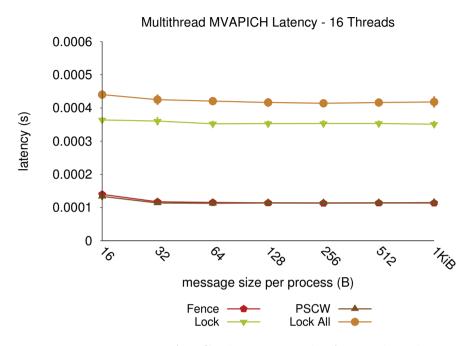

| 4.9  | MVAPICH latency results for 16 threads                                 | 59 |

|------|------------------------------------------------------------------------|----|

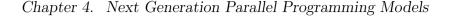

| 4.10 | MVAPICH message rate results for 1 thread                              | 60 |

| 4.11 | MVAPICH message rate results for 16 threads                            | 61 |

| 4.12 | Open MPI bandwidth results for 1 thread                                | 62 |

| 4.13 | Open MPI bandwidth results for 16 threads                              | 63 |

| 4.14 | Open MPI latency results for 1 thread                                  | 64 |

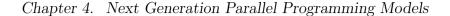

| 4.15 | Open MPI latency results for 16 threads                                | 65 |

| 4.16 | Open MPI message rate results for 1 thread                             | 66 |

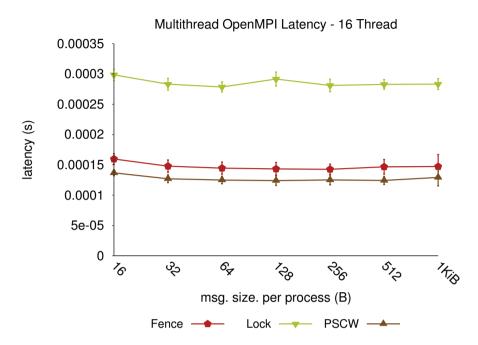

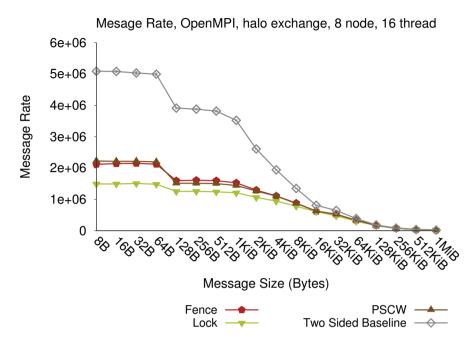

| 4.17 | Open MPI message rate results for 16 threads                           | 67 |

| 4.18 | RMA-MT mini-app run time overhead compared to the regular version $~$  | 68 |

| 4.19 | SHMEM-MT Latency Performance - Get                                     | 69 |

| 4.20 | SHMEM-MT Latency Performance - Put                                     | 70 |

| 4.21 | SHMEM-MT Bandwidth Performance - Get                                   | 71 |

| 4.22 | SHMEM-MT Bandwidth Performance - Put                                   | 72 |

| 4.23 | SHMEM-MT Message Rate for Halo Exchange - Get                          | 73 |

| 4.24 | SHMEM-MT Message Rate for Halo Exchange - Put                          | 74 |

| 4.25 | SHMEM-MT Mini-application Weak-scaling Runtime - HPCCG                 | 75 |

| 4.26 | SHMEM-MT Mini-application Weak-scaling Runtime - MiniFE                | 76 |

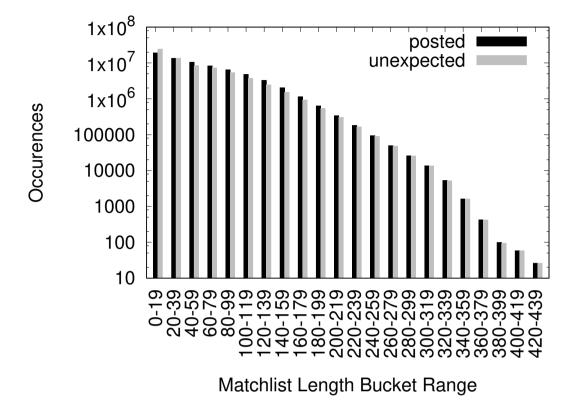

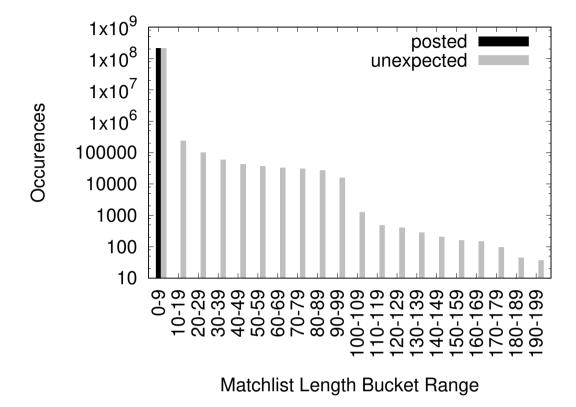

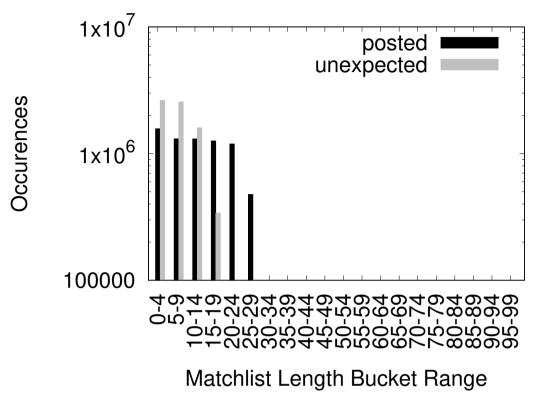

| 5.1  | AMR match list sizes - 64K                                             | 80 |

| 5.2  | Sweep3D match list sizes - 128K                                        | 81 |

| 5.3  | Halo3D match list sizes - 256K                                         | 82 |

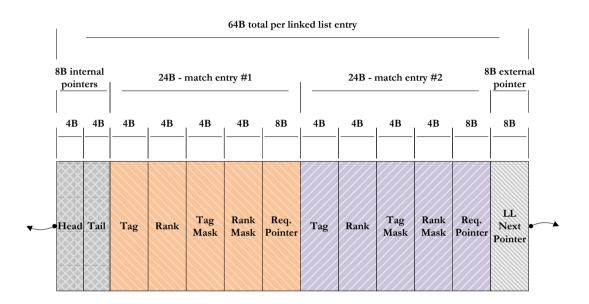

| 5.4  | Packing data structures into 64 byte cache lines                       | 83 |

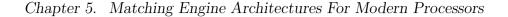

| 5.5  | Vector matching logic                                                  | 85 |

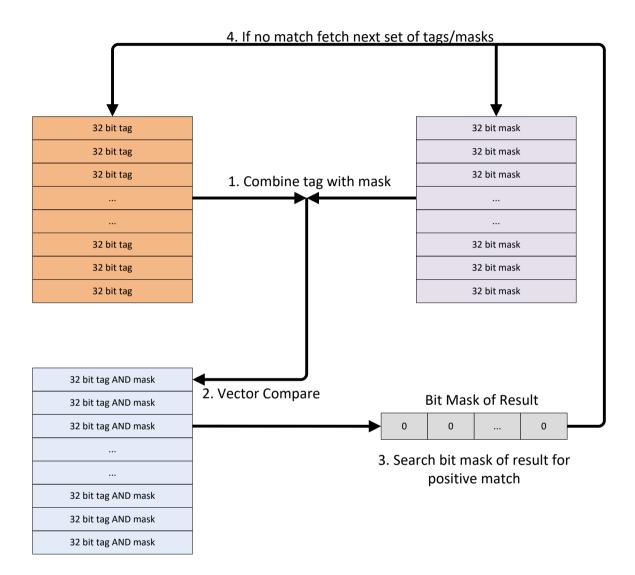

| 5.6  | Hot Caching                                                            | 86 |

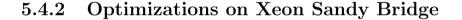

| 5.7  | Sandy Bridge Latency                                                   | 90 |

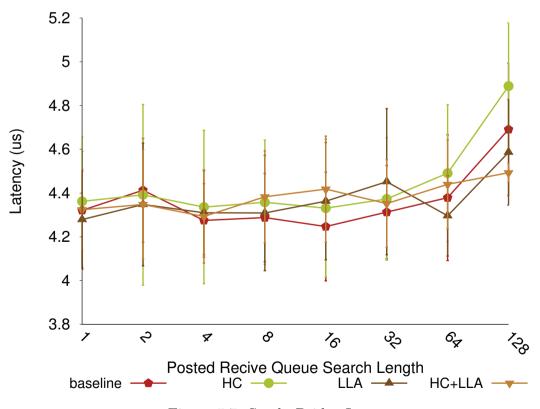

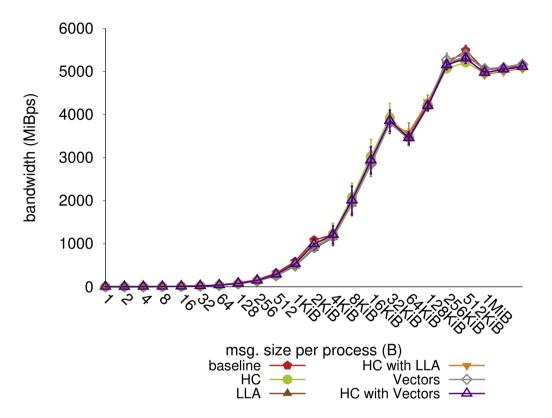

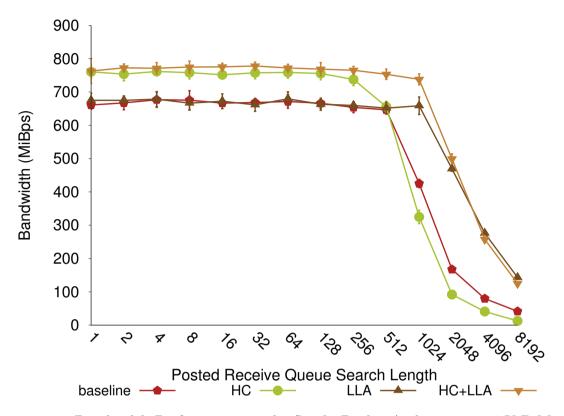

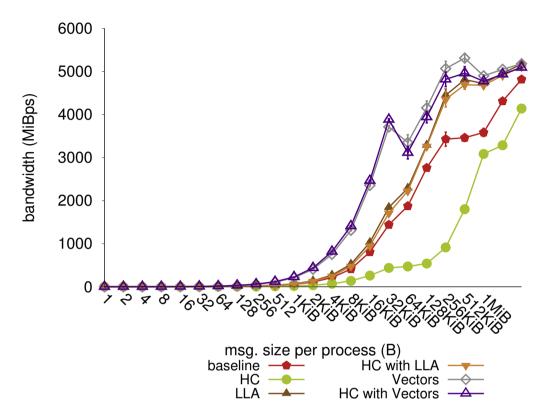

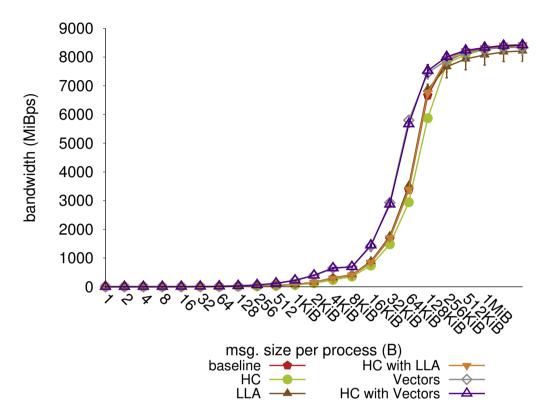

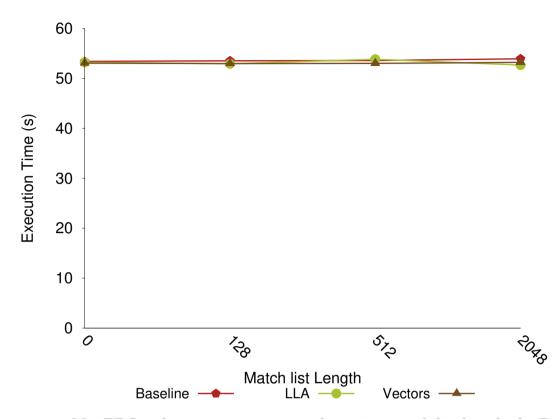

| 5.8  | Bandwidth Performance With an Empty Matching Engine - Sandy Bridge .   | 91 |

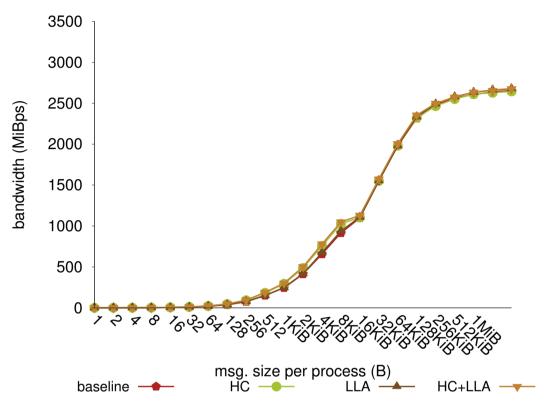

| 5.9  | Bandwidth Performance With an Empty Matching Engine - Broadwell        | 92 |

| 5.10 | Bandwidth Performance With an Empty Matching Engine - Knight's Landing | 93 |

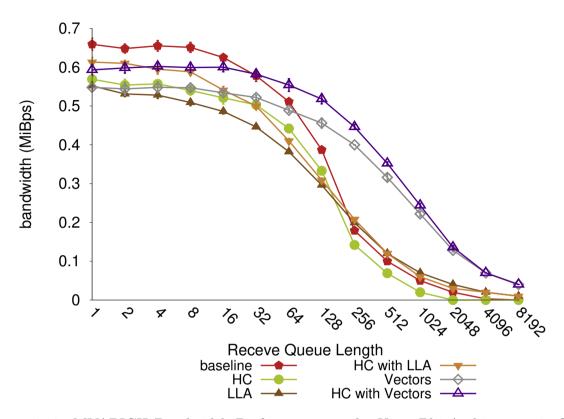

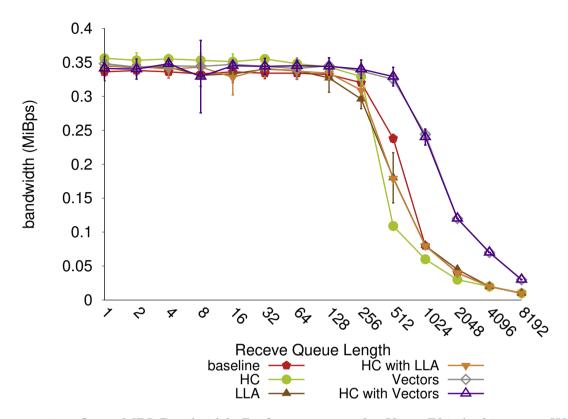

| 5.11                                      | Bandwidth Performance on the Sandy Bridge Architecture - Queue Depth                    |            |

|-------------------------------------------|-----------------------------------------------------------------------------------------|------------|

|                                           | 1024                                                                                    | 94         |

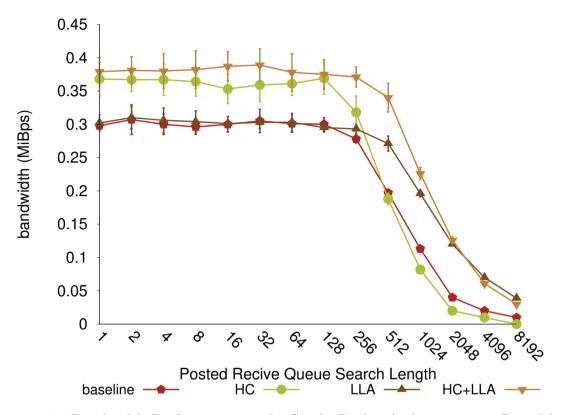

| 5.12                                      | Bandwidth Performance on the Sandy Bridge Architecture - 1 Byte Messages                | 95         |

| 5.13                                      | Bandwidth Performance on the Sandy Bridge Architecture - 4 KiB Messages                 | 96         |

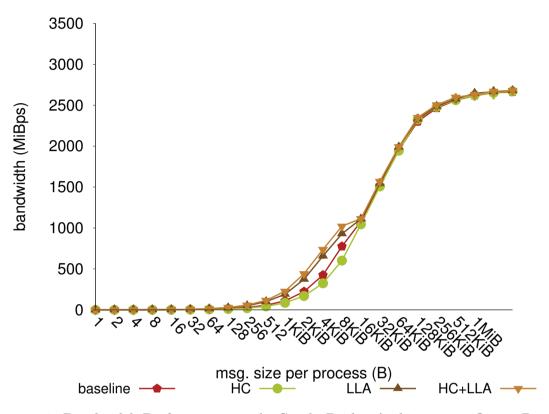

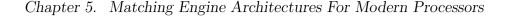

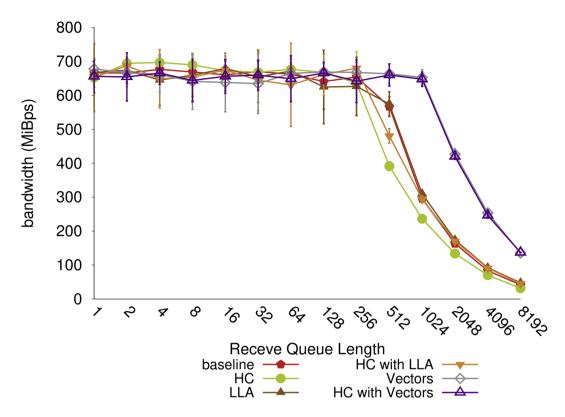

| 5.14                                      | Bandwidth Performance on the Broadwell Architecture - Queue Depth $1024$                | 97         |

| 5.15                                      | Bandwidth Performance on the Broadwell Architecture - $1\ {\rm Byte}\ {\rm Messages}$ . | 98         |

| 5.16                                      | Bandwidth Performance on the Broadwell Architecture - $4~{\rm KiB}$ Messages $~$ .      | 99         |

| 5.17                                      | MVAPICH Bandwidth Performance on the Xeon Phi Architecture in Shared                    |            |

|                                           | Memory - Queue Depth 1024                                                               | 100        |

| 5.18                                      | MVAPICH Bandwidth Performance on the Xeon Phi Architecture in Shared                    |            |

|                                           | Memory - 1 Byte Messages                                                                | 101        |

| 5.19                                      | MVAPICH Bandwidth Performance on the Xeon Phi Architecture in Shared                    |            |

|                                           | Memory - 4 KiB Messages                                                                 | 102        |

| 5.20                                      | Open MPI Bandwidth Performance on the Xeon Phi Architecture With an                     |            |

|                                           | Aries Network - Queue Depth 1024                                                        | 103        |

| 5.21                                      | Open MPI Bandwidth Performance on the Xeon Phi Architecture With an                     |            |

|                                           | Aries Network - 1 Byte Messages                                                         | 104        |

| 5.22                                      | Open MPI Bandwidth Performance on the Xeon Phi Architecture With an                     |            |

|                                           | Aries Network - 4 KiB Messages                                                          | 105        |

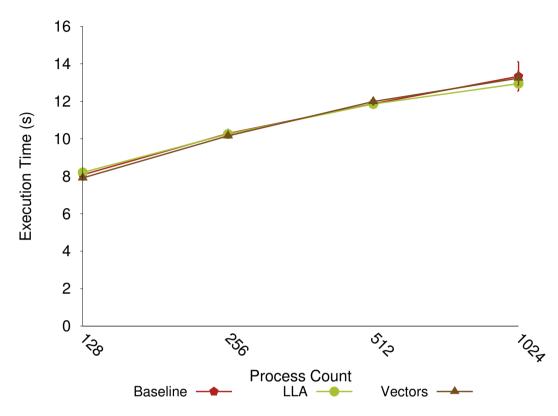

| 5.23                                      | AMG2013 Scaling Results for Broadwell                                                   | 106        |

| 5.24                                      | MiniFE Results at 512 processes with varying match list lengths for Broadwell           | 107        |

| 5.25                                      | Fire Dynamics Simulator Scaling Results For Three Experiments on Xeon $\ .$             | 108        |

| 5.26                                      | Fire Dynamics Simulator Scaling Results For Xeon Phi                                    | 109        |

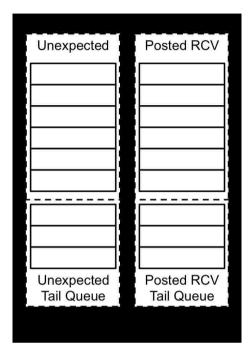

| 6.1                                       | Tail Queues Locking                                                                     | 114        |

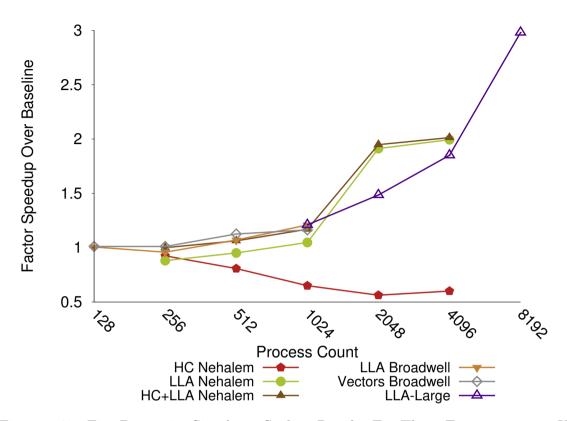

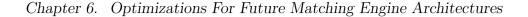

| 6.2                                       |                                                                                         | 123        |

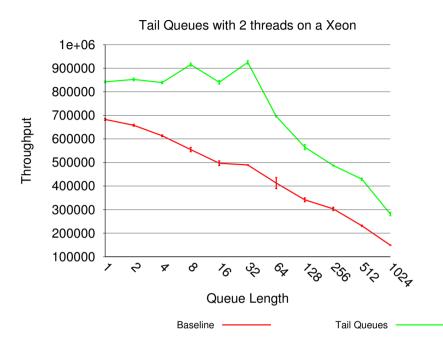

| 6.3                                       |                                                                                         | 123 $124$  |

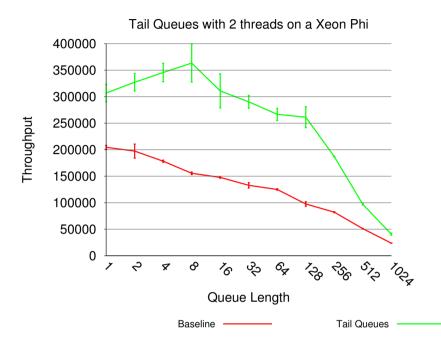

| 6.4                                       |                                                                                         |            |

| $\begin{array}{c} 0.4 \\ 6.5 \end{array}$ |                                                                                         | 125<br>126 |

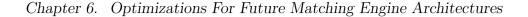

| 0.0                                       | Tail Queues Prototype Using 8 Threads on a KNC                                          | 126        |

## List of Figures

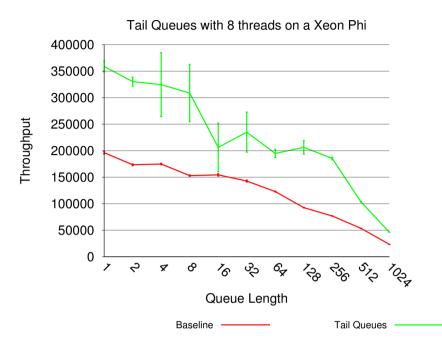

| 6.6  | Tail Queues Prototype Using 2 Threads on a KNC - No UMQ Entries | 127 |

|------|-----------------------------------------------------------------|-----|

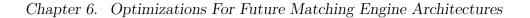

| 6.7  | Tail Queues MPICH Implementation                                | 127 |

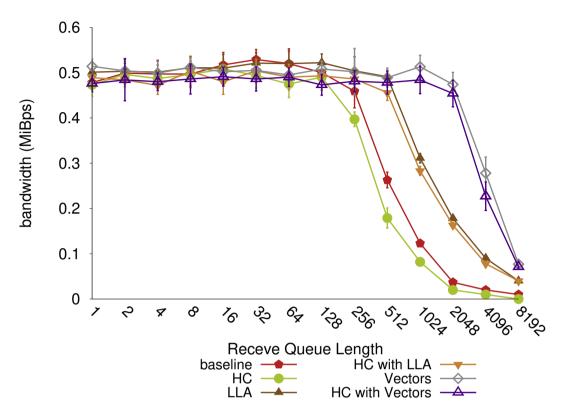

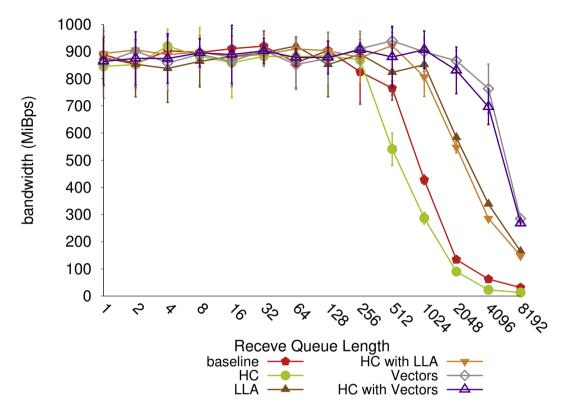

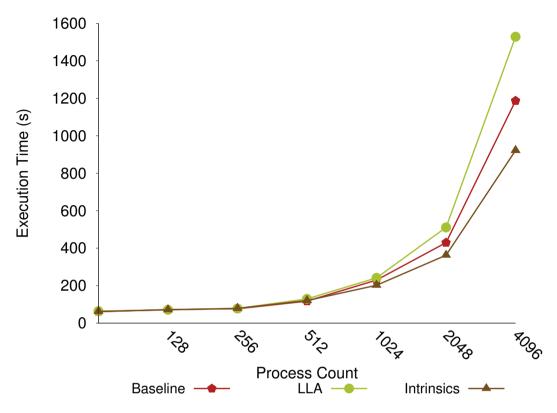

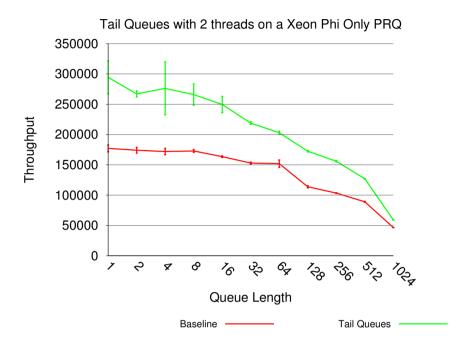

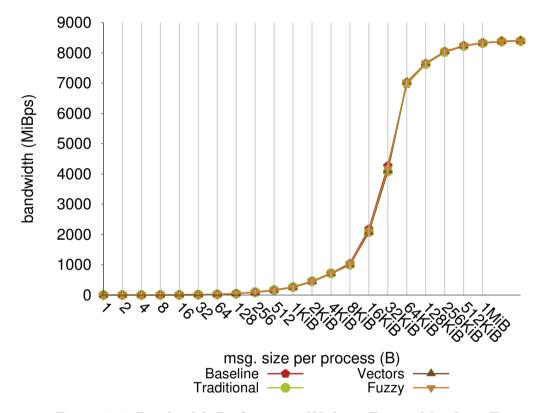

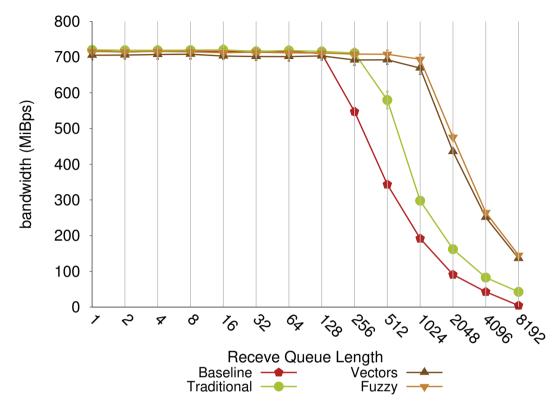

| 6.8  | Bandwidth Performance With an Empty Matching Engine             | 130 |

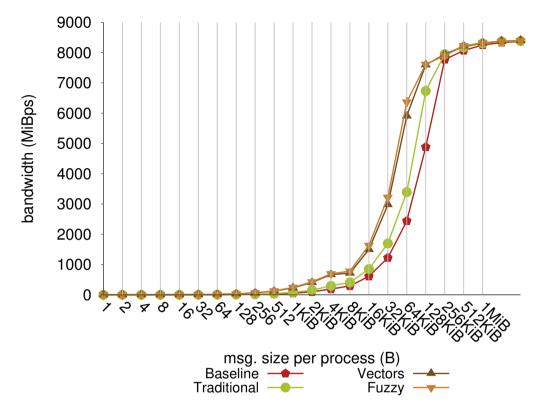

| 6.9  | Bandwidth Performance at Queue Depth 1024                       | 131 |

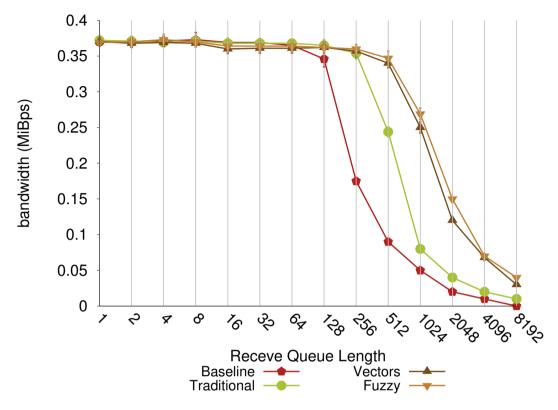

| 6.10 | Bandwidth Performance at 1 byte Messages                        | 132 |

| 6.11 | Bandwidth Performance at 4 KiB Messages                         | 133 |

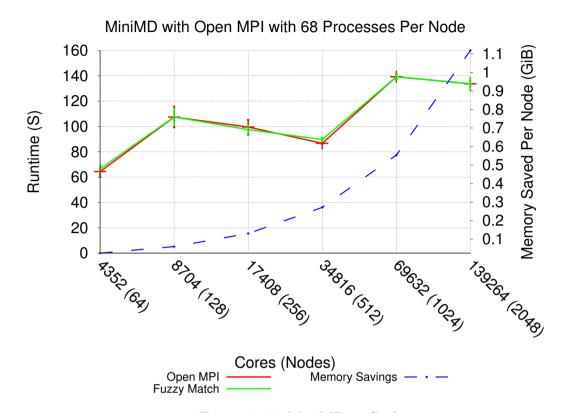

| 6.12 | MiniMD at Scale                                                 | 134 |

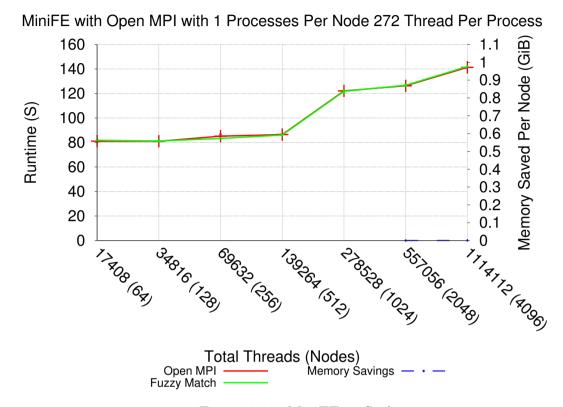

| 6.13 | MiniFE at Scale                                                 | 135 |

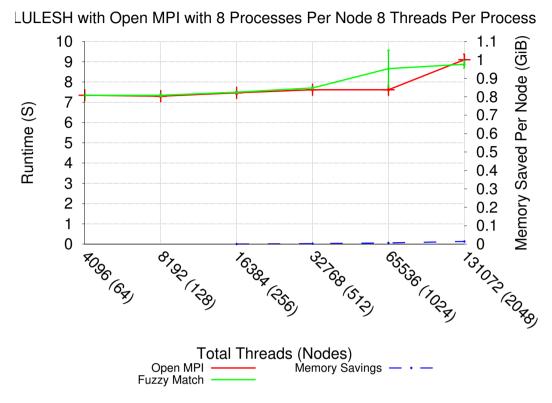

| 6.14 | LULESH at Scale                                                 | 136 |

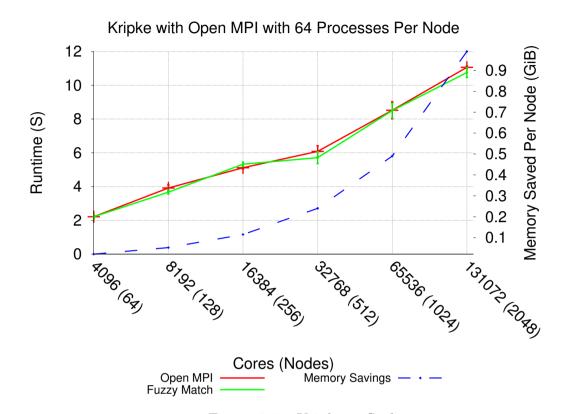

| 6.15 | Kripke at Scale                                                 | 137 |

# List of Tables

| 3.1 | Distribution of MPI Calls                                                                                                                | 37  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.2 | Distribution of Time Within MPI on a Standard Run                                                                                        | 37  |

| 5.1 | Maximum Time, in Seconds, Spent Searching The Matching Queues on<br>Knight's Landing Averaged Across Three Runs (Posted Receives — Unex- |     |

|     | pected Messages)                                                                                                                         | 100 |

| 6.1 | Algorithm Terminology                                                                                                                    | 113 |

| 6.2 | Open MPI Memory Overhead for different Run Scenarios for Trinity's KNL                                                                   |     |

|     | Partition                                                                                                                                | 139 |

# Chapter 1

# Introduction

The drive to improve performance and capability in modern scientific computing has caused computational scientists to leverage increasing levels of parallelism in their applications. Traditional high performance computing (HPC) has focused on providing communication and data movement between computers (nodes) with fast, complex processors with limited parallelism on the chip. However, as clock speeds approach their theoretical and practical limits, new generations of processors are focusing on improving performance through parallelism and new hardware features. New processor architectures, such as the many-core Intel Xeon Phi, have opted to reduce core speed and complexity to enable even greater parallelism.

This poses a challenge to HPC middleware and communication libraries which have been designed and optimized for fast complex cores and limited parallelism. Expensive data structures in critical sections can decrease performance for latency sensitive regions of the code, keeping them from utilizing increased parallelism. In addition, proposed programing models have the potential to exacerbate the problem by redistributing work into smaller pieces, increasing synchronization and middleware overhead.

This chapter introduces the broader HPC concepts and research challenges for the use of communication libraries on many-core architectures. Section 1.1 presents advances in mod-

ern HPC hardware including many-core processors, network offload, and high bandwidth memory. Section 1.2 presents the current state of the art in HPC communication libraries, focusing on the most prevalent interface, MPI. Section 1.3 discusses the design challenges and constraints facing next generation HPC systems: power, memory performance, and increased parallelism. Section 1.4 presents the technical contributions of this dissertation. Finally, Section 1.5 presents an outline for the remaining chapters of this dissertation.

## 1.1 Modern HPC hardware

Current trends in HPC architectures have eschewed traditional processor clock speed for improving performance through other hardware optimizations. Many-core architectures, network offload, and high bandwidth memory are three advances proposed to improve performance for current and future HPC architectures. The rest of this section will discuss these hardware advancements in detail; 1.1.1 will discuss many-core architectures, 1.1.2 will discuss network offload, and 1.1.3 will discuss high bandwidth memory.

## 1.1.1 Many Lightweight Cores

Many-core systems sacrifice core complexity and speed to provide a large increase in the number of cores. For example, the Xeon Phi Knight's Landing (KNL) architecture has up to 72 cores on a chip compared to 22 in the Intel Xeon Broadwell. This comes at the cost of low clock speeds, maxing out at 1.5 GHz rather than the 3.7 GHz<sup>1</sup> on Broadwell, and decreased complexity, with a 3 step out-of-order pipeline compared to the 20 step out-of-order pipeline per-thread on Broadwell. This allows highly parallel codes to achieve higher computational throughput by leveraging all of the cores. It also has limitations for serial segments of code and hiding latency of operations such as memory lookups.

<sup>&</sup>lt;sup>1</sup>This clock speed is based on a different model of Broadwell, the frequency for the 22 core model is 2.2 GHz.

### 1.1.2 Network Offload

Network offload is a hardware technique that utilizes a dedicated network protocol processor to reduce interference with application processes. This approach avoids costly context switches, system noise, and memory contention [49]. This approach can vary in the amount of a network processing operation done on the added hardware. This amount varies from Intel's Infinipath network, which offloads a subset of low level network operations, to Atos' BXI interconnect [28] which fully offloads network and HPC communication library processing. While this approach is becoming increasingly available and can become a solution for HPC communication libraries in the future, it presents an interesting challenge to HPC communication libraries as different networks diverge in utilized code-path and optimizations on one platform will not have the same impact on another.

### 1.1.3 High Bandwidth Memory

As processors continue to increase parallelism to increase throughput, performance bottlenecks have shifted to other parts of the system. Memory bandwidth is one of the more prominent limiting factors for many-core systems. To address this constraint, the Knight's Landing processor has introduced high bandwidth memory in the form of Multi-Channel DRAM (MCDRAM). MCDRAM is structurally different than standard memory, being stacked on top of the processor die. MCDRAM increases memory bandwidth to the processor but has limited capacity. While the MCDRAM can act as a cache, many applications see better performance when running exclusively out of MCDRAM [97]. This places a memory limitation on HPC communication libraries which need to maintain state for each process in the job. The memory constraint is expected to further reduce the amount of available memory per core in next generation systems.

## 1.2 The Message Passing Interface

The Message Passing Interface (MPI) is a network communication interface defined by the community. It has a number of widely-used implementations including Open MPI and MPICH. MPI is the most common communication library for HPC workloads and is utilized in parallel scientific applications. While alternatives like OpenSHMEM and Unified Parallel C exist, they do not see the same community adoption as MPI. Due to the ubiquity of MPI, this dissertation focuses on it as the primary HPC communication library. Subsection 1.2.1 describes the traditional two-sided and newer one-sided user interfaces. Subsection 1.2.2 presents some of the implementation details of message matching, a required component for MPI's two-sided interface. Finally, Subsection 1.2.3 presents the details of MPI's thread support.

### **1.2.1** Message Passing and Remote Memory Access

Traditional message passing has been one of the main focuses of MPI requiring both sides to interact with the library to manage data placement. The receiver of a message must provide an inbox buffer and identification data. The sender of a message must provide data and routing information to ensure that the data gets place properly. To properly place the data, the receiving process does message matching which is described in detail in section 1.2.2. RMA is another form of communication in MPI that attempts to avoid library processing steps like matching. It does this by placing data in a sender specified region and does not require interaction from the receiver. Section 2.2 has more details on MPI and RMA.

### 1.2.2 Message Matching

The message matching engine is one of the major internal computations in MPI. It matches incoming message data to a buffer specified in a receive function call. This matching uses

two identifiers, a tag and the sender's rank. The matching engine is constrained by behavior guarantees in the MPI specification. First, the matching engine must ensure order. If a receive request matches two pending messages, it must match the first to enter the match list. Second, receives must support wild card identifiers. This allows for unexpected communication between two nodes. For example, AMG2013 [7] uses this to establish communication outside of its regular halo exchange.

Standard matching implementations utilize a pair of linked lists: a posted receive queue and an unexpected message queue. To post a receive, the library searches through the unexpected queue and, if no match is found, appends a new element to the posted receive queue. An incoming message must do the same for the other list. Due to the complexity of guaranteeing order and wild card usage, most multithreaded implementations treat the matching engine as a singe large critical section. This significantly limits MPI performance on many-core systems.

## 1.2.3 Thread Modes

The MPI specification defines four thread modes that provide optimizations based on userguaranteed behavior. The most general is *MPI\_THREAD\_MULTIPLE*, which provides a thread-safe MPI interface. This mode has traditionally been implemented using coarse grained synchronization methods that attempt to acquire a lock upon entry to MPI. More recent implementations have been exploring fine grained synchronization to minimize the performance impact of critical sections. Unfortunately, the lack of a performant thread safe MPI limits the performance of programs that use multithreaded communications, like those expected to be needed to take advantage of an exascale many-core system. This is discussed in more depth in Section 2.2.2.

# 1.3 Design Challenges for Communication Libraries on Many-Core Systems

As most communication libraries are optimized for traditional systems, there are a few major challenges that arise for large scale HPC system with many-core processors. Three of the major challenges are power usage, memory bottlenecks, and parallelism.

### 1.3.1 Power

While systems have been increasing their computation capability, the power required per operation has been decreasing slowly. This has led to two major concerns among current high performance clusters: power caps and energy budgets. Power caps are a limit to the instantaneous wattage a cluster can draw from the power grid. This is primarily a concern for capability class supercomputers, where the expected increase to power requirements gets close and potentially exceeds the amount of power available. Another concern is energy budgets. With systems requiring more power, the expenses required to run machines have been steadily increasing. This has led to a desire to explore potential power saving techniques for network technologies such as offload network cards and network routers.

This is discussed in more detail in Section 2.4.2

## 1.3.2 Memory

One of the major sacrifices that many-core processors make is a reduced out-of-order pipeline which reduces the processor's ability to handle memory look-ups and prefetch data. The lack of deep out-of-order processing reduces the processor's ability to hide the latency of cache misses. This particularly impacts the use of data structures that are non-contiguous in memory, such as linked lists. For instance, the KNL architecture only supports 3 step out

of order processing to hide the latency of memory lookups compared to the 20 step out of order pipeline of traditional cores. This can be even more problematic because of small cache sizes. The KNL's biggest level of cache is the 2 MiB L2 that is shared between two cores with a total of eight hyper-threads.

Memory latency has the potential for large impacts on the performance of non-contiguous data structures in HPC communication libraries, such as the matching engine. The lack of complexity causes a larger latency when fetching an entry from memory and the limited cache size causes these data structures to be evicted from cache between uses. This is particularly relevant to HPC communication libraries, as applications often process large amounts of data between communication phases.

### 1.3.3 Parallelism

One of the biggest challenges in many-core architectures is in fully utilizing the parallelism provided by the architecture. As the current generation of Xeon Phi can have 72 cores with a total of 288 hardware thread contexts, an application must utilize a large number of threads per node to fully utilize the available hardware resources. This is a constraint for MPI-everywhere legacy applications, because increasing the number of ranks causes MPI to require more time and resources to operate. It also creates an additional trade-off for hybrid applications, as users will have to determine how many processes per node and how many threads per processes are optimal on each new architecture.

HPC communication libraries must support application models that leverage this increasing parallelism. MPI+X is an attempt to couple two different parallelism models together. It usually consists of MPI to handle inter-node parallelism and a threading library, such as OpenMP, to handle the intra-node parallelism. The combination of MPI+X programing models and fine grained messaging techniques, such as communication and computation overlap, has driven the desire to have performant, multithreaded communication libraries.

## 1.4 Contributions

The goal of this dissertation is to demonstrate that successfully leveraging parallelism, offload, and caching behaviors will improve the performance of HPC communication libraries on modern hardware architectures.

The major contributions of this work are:

- An evaluation of the impact of many-core processors on modern communication systems including onload and offload network architectures

- A suite of benchmarks, RMA-MT, to explore the performance of next generation communication systems

- Studies using these benchmarks of the performance of both MPI RMA and shmem in hybrid programing contexts

- A vector matching architecture optimized for many-core processors that improves MPI performance by reducing cache cache misses and leveraging modern vector operations

- A multi-threaded matching architecture that reduces lock contention in current HPC communication systems

- An optimistic matching approach to reduce memory overheads in modern MPI implementations by utilizing lossy compression

- A software based explicit cache management technique that improves HPC communication performance on many-core and traditional processor architectures

## 1.5 Dissertation Outline

The rest of this dissertation is structured as follows: Chapter 2 presents an overview of the related work. Chapter 3 presents a exploratory study of how modern many-core architectures

impact communication processing on onload and offload networks. Chapter 4 presents novel benchmarks and performance studies that explore the new parallelism model of one-sided communication in multi-threaded contexts. Chapter 5 presents techniques that leverage current state of the art hardware to improve MPI matching for traditional applications. Chapter 6 presents preliminary results for novel techniques for optimizing MPI matching for next generation hardware and applications. Finally, Chapter 7 summarizes the contributions of this dissertation and presents future directions in this work.

# Chapter 2

# **Related Work**

## 2.1 Introduction

This dissertation builds on three key research areas of improvements to HPC communication libraries: software techniques, hardware techniques, and alternative programing models. Section 2.2 presents background on MPI including message matching, threading, and RMA. Section 2.3 presents the state of the art in MPI matching research, including studies of matching performance and behavior, software techniques to improve message matching, and hardware techniques to offload message matching. Section 2.4 discusses the impact of modern architectures on MPI, specifically discussing multi-threaded MPI and power concerns. Section 2.5 presents background on other programing models for HPC systems, including one-sided communication and task based parallelism.

## 2.2 Message Passing Interface (MPI)

MPI [81] is an HPC communication library specification, the first version of which was published in November 1992. It is the most common HPC communication library on systems

today. MPI's goal is to provide a performant and portable interface for tightly coupled scientific simulations. To accomplish this, the standard has defined interfaces for a number of different communication types, including point-to-point, collective, and one-sided communication. This communication diversity allows scientific applications to utilize cluster computation for different communication needs, such as mesh problem decomposition, global all-to-all communications, and scatter and reduce data dissemination.

Traditional MPI point-to-point communication is built on the concept of receiver-specified data placement. Each communication consists of two parts: a send and a receive. Messages are delivered based on two identifiers: tag and rank. Tag is a user-defined value that must match on both sides of the communication to identify the message. Rank is the MPI address assigned to each process, and each side of a communication must specify the other to properly route the message from sender to receiver. A send is given a buffer of data to transfer, an identifying tag, and a destination rank, while the receive takes a buffer in which to place the data, an identifying tag, and a source rank. This design imposes significant implementation requirements on the library but provides convenient communication semantics to users.

Since its inception, there have been many implementations, including MPICH [102], MVA-PICH [103], Open MPI [104], FT-MPI [37], LA-MPI [6], LAM/MPI, Platform MPI, MPI Pro [30], ChaMPIon [29], and PACX-MPI [41]. There have been vendor-tuned implementations, such as Cray MPI, BG-MPI, and Intel MPI. Also, there have been implementations that have extended the standard to change functionality, such as MPI/RT [64] for realtime computation and FG-MPI [63] for task based programing models.

## 2.2.1 Matching

MPI matching works on three key elements: a source address, a matching tag, and a communicator. An MPI communicator is a special isolation mechanism that allows processes that belong to that communicator to send messages to each other. Each process in a commu-