# University of New Mexico UNM Digital Repository

Computer Science ETDs

**Engineering ETDs**

5-1-2009

# Improving the performance of parallel scientific applications using cache injection

Edgar Leon Borja

Follow this and additional works at: https://digitalrepository.unm.edu/cs etds

#### Recommended Citation

$Leon\ Borja,\ Edgar.\ "Improving\ the\ performance\ of\ parallel\ scientific\ applications\ using\ cache\ injection."\ (2009).\ https://digitalrepository.unm.edu/cs_etds/4$

This Dissertation is brought to you for free and open access by the Engineering ETDs at UNM Digital Repository. It has been accepted for inclusion in Computer Science ETDs by an authorized administrator of UNM Digital Repository. For more information, please contact disc@unm.edu.

| dgar A. Leon Borja                                                                      |               |

|-----------------------------------------------------------------------------------------|---------------|

| ndidate                                                                                 |               |

| omputer Science                                                                         |               |

| partment                                                                                |               |

|                                                                                         |               |

| his dissertation is approved, and it is acceptable in quality and form for publication: |               |

| oproved by the Dissertation Committee:                                                  |               |

|                                                                                         |               |

| C Sail                                                                                  | , Chairperson |

| Munuf flin                                                                              |               |

|                                                                                         |               |

| de de                                                                                   |               |

| Pairica Ruer                                                                            |               |

| Leigne 1862                                                                             |               |

|                                                                                         |               |

|                                                                                         |               |

|                                                                                         |               |

|                                                                                         |               |

|                                                                                         |               |

|                                                                                         |               |

| *                                                                                       |               |

# **Improving the Performance of Parallel Scientific Applications Using Cache Injection**

by

### Edgar A. León Borja

B.S., Computer Science, Universidad Nacional Autónoma de México, 2001 M.S., Computer Science, University of New Mexico, 2003

#### DISSERTATION

Submitted in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy Computer Science

The University of New Mexico

Albuquerque, New Mexico

May, 2009

©2009, Edgar A. León Borja

To my parents, for their endless efforts in looking out for my happiness.

# **Acknowledgments**

Foremost, I would like to thank my adviser, Barney Maccabe, for his mentoring, advise, guidance, encouragement, friendship, and for his key role in my development as a scientist. I would also like to thank Rolf Riesen for his contributions to the scalable cluster simulator, for setting it up at Sandia, and for executing many experiments there; Ron Brightwell for allowing me to use his MIAMI API and his MPICH device layer; Kurt Ferreira for his feedback during our many technical discussions and for his friendship; Michal Ostrowski for his contributions to the shim layer; Orran Krieger and Hazim Shafi for their feedback and for introducing me to cache injection; Lixin Zhang and Jim Peterson for their support in using Mambo; Amos Waterland and Jimi Xenidis for their feedback, support and friendship; Dilma da Silva for being part of my dissertation committee and for her feedback and friendship; Patricia Teller for being part of my dissertation committee and for her feedback; Linda Maccabe for her friendship and moral support in my education; the Brantley family and the Calderon family for their love and friendship; Katie Edwards for her editorial comments to this document; the members of the Scalable Systems Laboratory for their support; and finally, the Department of Energy, Office of Science, IBM and Intel for their generous support in this research.

# Improving the Performance of Parallel Scientific Applications Using Cache Injection

by

## Edgar A. León Borja

#### ABSTRACT OF DISSERTATION

Submitted in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy Computer Science

The University of New Mexico

Albuquerque, New Mexico

May, 2009

# **Improving the Performance of Parallel Scientific Applications Using Cache Injection**

by

#### Edgar A. León Borja

B.S., Computer Science,

Universidad Nacional Autónoma de México, 2001 M.S., Computer Science, University of New Mexico, 2003

Ph.D., Computer Science, University of New Mexico, 2009

#### **Abstract**

Cache injection is a viable technique to improve the performance of data-intensive parallel applications. This dissertation characterizes cache injection of incoming network data in terms of parallel application performance. My results show that the benefit of this technique is dependent on: the ratio of processor speed to memory speed, the cache injection policy, and the application's communication characteristics.

Cache injection addresses the memory wall for I/O by writing data into a processor's cache directly from the I/O bus. This technique, unlike data prefetching, reduces the number of reads served by the memory unit. This reduction is significant for data-intensive applications whose performance is dominated by compulsory cache misses and cannot be alleviated by traditional caching systems.

Unlike previous work on cache injection which focused on reducing host network stack overhead incurred by memory copies, I show that applications can directly benefit from this technique based on their temporal and spatial locality in accessing incoming network data. I also show that the performance of cache injection is directly proportional to the ratio of processor speed to memory speed. In other words, systems with a memory wall can provide significantly better performance with cache injection and an appropriate injection policy. This result implies that multi-core and many-core architectures would benefit from this technique. Finally, my results show that the application's communication characteristics are key to cache injection performance. For example, cache injection can improve the performance of certain collective communication operations by up to 20% as a function of message size.

# **Contents**

| Li | st of l | Figures                                         | Xii |

|----|---------|-------------------------------------------------|-----|

| Li | st of ' | <b>Fables</b>                                   | xiv |

| 1  | Intr    | oduction                                        | 1   |

|    | 1.1     | Thesis statement and contributions of this work | 3   |

|    | 1.2     | Research approach                               | 4   |

|    | 1.3     | Thesis outline                                  | 6   |

| 2  | Cac     | he injection                                    | 7   |

|    | 2.1     | What is cache injection?                        | 8   |

|    | 2.2     | Cost considerations                             | 10  |

|    | 2.3     | Comparing cache injection and data prefetching  | 12  |

|    |         | 2.3.1 Experimental framework                    | 14  |

|    |         | 2.3.2 Experimental evaluation                   | 15  |

|    | 2.4     | Limitations of cache injection                  | 18  |

## Contents

|   |      | 2.4.1 The Jacobi method                              | 19 |

|---|------|------------------------------------------------------|----|

|   |      | 2.4.2 Performance using blind injection              | 20 |

|   | 2.5  | Injection policies                                   | 22 |

| 3 | Exp  | erimental infrastructure                             | 25 |

|   | 3.1  | Cluster simulator                                    | 27 |

|   | 3.2  | Validation                                           | 32 |

| 4 | Test | environment                                          | 37 |

|   | 4.1  | Platform and simulated system configuration          | 37 |

|   | 4.2  | Injection policies                                   | 38 |

|   | 4.3  | Parallel applications and performance analysis tools | 40 |

|   |      | 4.3.1 AMG from the Sequoia acceptance suite          | 40 |

|   |      | 4.3.2 FFT from the HPC Challenge benchmark suite     | 41 |

|   |      | 4.3.3 mpiP: an MPI profiling library                 | 42 |

|   |      | 4.3.4 IMB: Intel MPI benchmarks                      | 42 |

| 5 | Resi | ults and analysis                                    | 43 |

|   | 5.1  | Memory and processor speed                           | 44 |

|   | 5.2  | Cache injection policy                               | 46 |

|   | 5.3  | Application's communication characteristics          | 51 |

|   |      | 5.3.1 Collective operations                          | 55 |

## Contents

|            | 5.4   | Putting it all together: cache injection and the LogGP model | 58 |

|------------|-------|--------------------------------------------------------------|----|

| 6          | Rela  | ated work                                                    | 62 |

|            | 6.1   | Consumer-driven techniques for the memory wall               | 63 |

|            | 6.2   | Producer-driven techniques for intra-processor communication | 64 |

|            | 6.3   | Producer-driven techniques for inter-processor communication | 65 |

|            | 6.4   | Past architectures for direct data transfer                  | 67 |

| 7          | Con   | clusions and future work                                     | 69 |

|            | 7.1   | Conclusions                                                  | 69 |

|            | 7.2   | Future Work                                                  | 70 |

| <b>D</b> a | foron | ras                                                          | 72 |

# **List of Figures**

| 2.1 | Memory write operation initiated by the NIC                                                                                  | 9  |

|-----|------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Cache injection operation initiated by the NIC                                                                               | 10 |

| 2.3 | Base architecture for cache injection (based on IBM's Power5)                                                                | 11 |

| 2.4 | Memory bandwidth utilization                                                                                                 | 16 |

| 2.5 | Execution time                                                                                                               | 17 |

| 2.6 | Jacobi problem domain for process $k$                                                                                        | 20 |

| 3.1 | The shim layer                                                                                                               | 29 |

| 3.2 | The implementation of MPI on a single simulated machine                                                                      | 31 |

| 3.3 | The parallel cluster simulator                                                                                               | 32 |

| 3.4 | NAS IS benchmark on four nodes.                                                                                              | 34 |

| 3.5 | NAS IS benchmark on 16 nodes                                                                                                 | 35 |

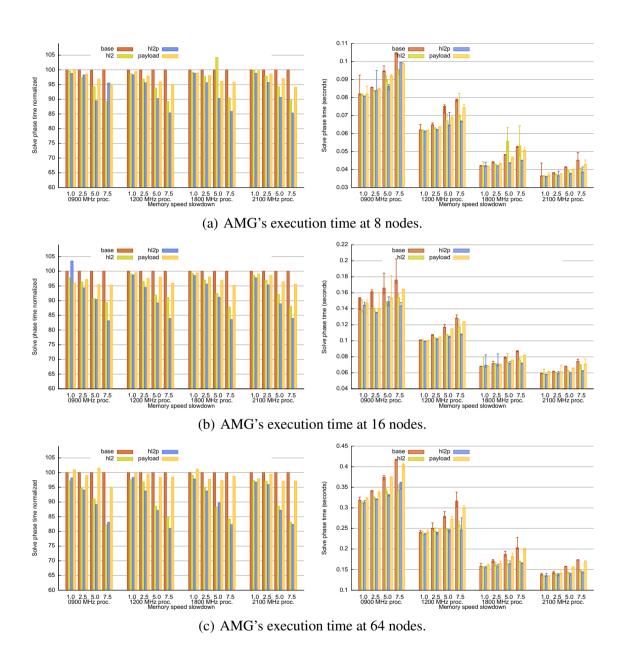

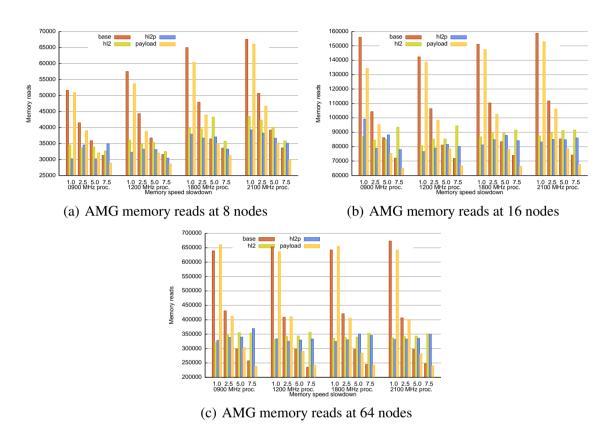

| 5.1 | Performance of AMG solve phase as a function of memory and processor speed, cache injection policy, and number of processors | 45 |

## List of Figures

| 5.2 | AMG's number of memory reads carried out by the memory unit as a    |    |

|-----|---------------------------------------------------------------------|----|

|     | function of memory and processor speed, cache injection policy, and |    |

|     | number of processors                                                | 48 |

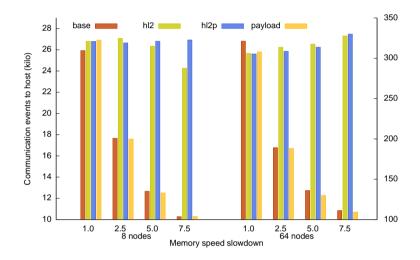

| 5.3 | AMG's number of NIC to host communication events for a 2.1GHz pro-  |    |

|     | cessor as a function of memory speed and number of MPI processes    | 49 |

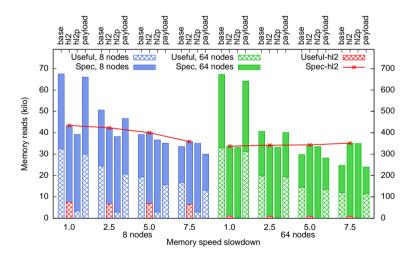

| 5.4 | AMG's number of memory reads carried out by the memory unit for a   |    |

|     | 2.1GHz processor                                                    | 50 |

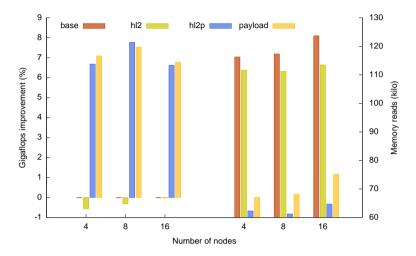

| 5.5 | Impact of cache injection policies on the performance of HPCC's FFT | 52 |

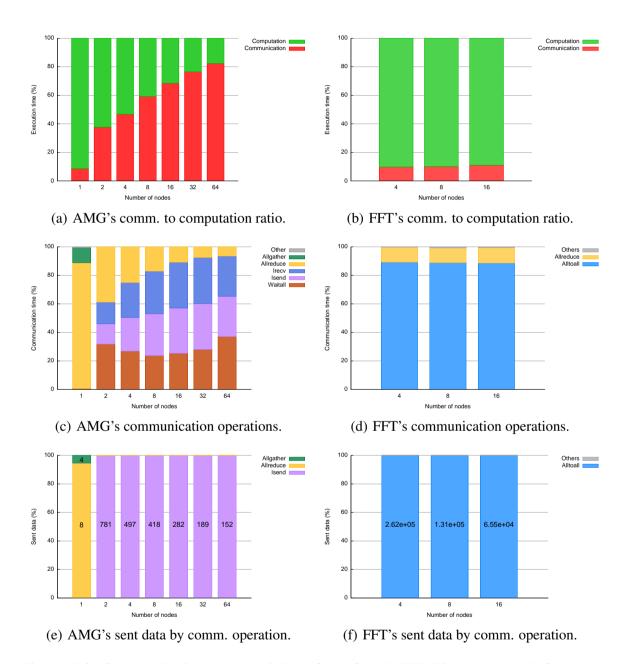

| 5.6 | Communication characteristics of AMG and FFT                        | 53 |

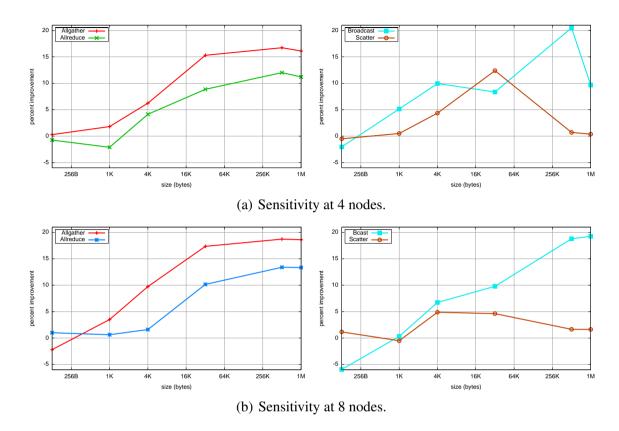

| 5.7 | Sensitivity of certain MPI collective operations to cache injection | 56 |

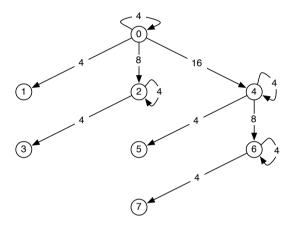

| 5.8 | MPICH's scatter algorithm for 32KB and $n = 8$                      | 57 |

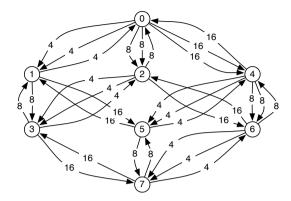

| 5.9 | MPICH's broadcast algorithm for 32KB and $n=8$                      | 58 |

# **List of Tables**

| 2.1 | Prefetching vs. cache injection                 | 13 |

|-----|-------------------------------------------------|----|

| 2.2 | System configuration parameters                 | 16 |

| 3.1 | A shim interface                                | 29 |

| 3.2 | MIAMI API                                       | 31 |

| 3.3 | Simulated system configuration                  | 33 |

| 5.1 | Memory speeds as a function of processor speed. | 44 |

# Chapter 1

## Introduction

For almost two decades, the growing disparity of processor to memory speed has affected applications with poor temporal locality in their ability to benefit from improvements in processor speed. This disparity known as the memory wall [58], makes memory speed the limiting factor in the performance of a system. Even in systems with perfect caches, the memory wall affects application performance due to compulsory cache misses on data with poor locality. Data prefetching may not alleviate this problem in applications where the memory bus is already saturated, or those with not enough computation in between memory accesses to mask memory latency.

Examples of applications affected by the memory wall include scientific, cryptographic, signal processing, string processing, image processing, and some graphics computations [42]. More recently, many high-end, real-world scientific applications showed a strong dependence on the memory characteristics of a system [48, 47]. These applications show poor locality by accessing large amounts of unique data (data-intensive applications). This data generates compulsory cache misses resulting in an increased dependency on memory speed.

Cache injection alleviates the memory wall by placing data from an I/O device directly

into the cache [6, 28, 12]. The benefits of this technique are reducing memory access latency and reducing memory pressure (the number of requests issued to the memory controller per unit of time). In current architectures, I/O data is transferred to main memory, and cached copies of old values are invalidated. Accessing I/O data results in compulsory cache misses and, thereby, accesses to main memory. To hide memory latency, prefetching can overlap memory accesses with computation [4, 44]. Prefetching anticipates memory accesses based on usage patterns or specific instructions issued by the compiler, the OS or the application. Prefetching can hide memory latency, but unlike cache injection, it does not reduce and may increase traffic over the already saturated memory bus, a precious resource for memory-bound applications. Prefetching is more widely applicable than cache injection, but the latter provides better performance for I/O. Recent Intel architectures provide a similar mechanism to cache injection called Prefetch Hint [51]. This mechanism allows early prefetching of I/O data initiated by the NIC. Like prefetching, this technique does not reduce memory bandwidth utilization.

The impact of cache injection on application performance is dependent on several factors including timely use of data, the amount of data, the type and frequency of communication primitives, the application's data usage patterns, and the underlying architecture. For example, injecting data into a cache may evict the application's working set, and in a multiprocessor system, an incorrect choice of processor/cache may increase overhead (local memory may be closer than another processor's cache).

Appropriate injection policies must be made to account for these factors. Injection policies answer the questions of *what*, *when*, and *where* to inject. The impact of cache injection on application performance is dependent on the policies that determine the consumer processor/core and the appropriate level in the memory hierarchy. The information needed by these policies is distributed throughout the system, in the application, the OS, the communication library, the compiler and the caches. For example, the mapping of processes to processors/cores is held by the OS; the application and/or the compiler can

provide hints of data usage; information about the implementation of collective communication operations may reside in the communication library and/or the NIC.

In this work, I show how cache injection can improve the performance of parallel applications as a function of processor to memory speed ratio, injection policy, and communication characteristics of applications. This characterization of cache injection provides a framework to identify applications which may benefit from this technique.

In the next section, I present my thesis statement and contributions of this work, followed by a description of my research approach. An outline of the overall thesis is presented in Section 1.3.

#### 1.1 Thesis statement and contributions of this work

Cache injection can improve the performance of parallel scientific applications as a function of the ratio of processor to memory speed, the injection policy, and the application's communication characteristics.

The major contribution of this work is to show that cache injection can improve the performance of parallel scientific applications. This improvement is dependent on: (1) the processor to memory speed ratio; (2) the injection policy; and (3) the communication characteristics of applications. Cache injection addresses the memory wall for data intensive applications with a significant amount of communication.

To adequately build the foundations of this work, I developed micro-benchmarks to investigate the benefits and limitations of cache injection and created a scalable infrastructure to analyze the impact of this technique on application performance. I compared and contrasted the benefits of cache injection and data prefetching. I showed that, unlike data prefetching, cache injection can reduce memory bandwidth utilization. To illustrate the

main limitation of cache injection, I showed an example where this technique may create cache pollution. To address this limitation, I proposed cache injection policies based on OS, application and compiler information. I implemented a subset of these policies tailored for MPI and analyzed their impact on application performance using an infrastructure to study the impact of cache injection and other novel architectural features on application performance at scale.

A more detailed list of the contributions of this work follow:

- The performance of cache injection is directly proportional to the processor to memory speed ratio. The higher the memory wall, the greater the benefit.

- Injecting communication meta-data improves the performance of latency-sensitive applications.

- Injecting application data improves the performance of bandwidth-sensitive applications that show temporal and spatial locality in using incoming network data.

- Cache injection can improve the performance of applications using a significant number of collective operations. Cache injection can improve the performance of MPI\_Allgather, MPI\_Alltoall, MPI\_Allreduce, and MPI\_Bcast operations.

This work is unique in relating cache injection of application data to application performance. Previous work focused on using cache injection to reduce the overhead of memory copies incurred by the network stack. High-performance communication systems typically use zero-copy implementations which do not benefit from this.

## 1.2 Research approach

Using simulation, I characterize the impact of several injection policies on the performance of two applications. The following steps summarize my research approach.

- 1. Characterize the benefits of cache injection. I developed a micro-benchmark to show, experimentally, the benefits of cache injection compared to data prefetching. These experiments measured execution time and memory pressure incurred by the micro-benchmark. Unlike data prefetching, cache injection reduces memory bandwidth utilization [13, 14].

- 2. Characterize the limitations of cache injection. Using the Jacobi iteration, I demonstrated, analytically, that cache injection can pollute the cache and decrease application performance [12]. In this case, the NIC and the application compete for the cache. The working set of the application may be evicted by incoming network data written by the NIC.

- 3. Design injection policies to address the limitations of cache injection. I proposed a set of policies to minimize the amount of pollution introduced into the cache. These policies answer the questions of what, when, and where to inject. Using simulation, I implemented a subset of policies tailored for MPI.

- 4. Design and implement a scalable infrastructure to execute parallel scientific applications on a cluster of cache injection nodes. I coupled hundreds of instances of an existing cycle-accurate, full-system simulator with cache injection using a model of a high-performance network [18]. I showed that the resulting distributed infrastructure can accurately simulate application performance on a parallel, high-performance machine [19].

- 5. Characterize the impact of cache injection on parallel application performance. Using the cluster simulator mentioned above, I measured the performance of selected applications using a set of injection policies tailored for MPI. The results showed that cache injection is particularly effective on machines with a memory wall. Furthermore, the performance of cache injection is dependent on the application's communication characteristics and the injection policy.

### 1.3 Thesis outline

The rest of this document is organized as follows. Chapter 2 presents a detailed study of cache injection. This study includes a demonstration of an upper bound on the performance benefits of this technique; a comparison with data prefetching; an example where cache injection without an appropriate policy can be decremental to application performance; and a description of policies based on OS, compiler, communication library, and application information to improve the performance of applications. Chapter 3 describes the experimental infrastructure developed to execute parallel applications using MPI with and without cache injection. This infrastructure is based on simulation and leverages current cycle-accurate simulators into a distributed and scalable cluster simulator. Even though the simulated system cannot be validated against a real machine (because it does not exist), I developed a set of experiments using unmodified parallel applications that show the cluster simulator is accurate. Chapter 4 describes the test environment including the platform used for running the cluster simulator, the simulated system configuration, the injection policies implemented, and the applications and analysis tools used in this study. Chapter 5 illustrates the impact of different injection policies on application performance. It also analyzes the relationship between cache injection performance and the ratio of processor to memory speed and the application's communication characteristics. Chapter 6 describes related work. Finally, Chapter 7 summarizes the results and contributions of this work, as well as a discussion of possible directions for future research.

# Chapter 2

# **Cache injection**

Cache injection [6, 28] is one of several techniques to mitigate the imbalance between processor and memory speeds [44, 46, 42]. This technique reduces memory access latency and memory pressure by placing data from I/O devices directly into the cache.

In current architectures, data from I/O devices is written to the system's main memory. When an application requests this data, the processor fetches it into a local cache. Fetching data can be done ahead of time by a prefetch engine which may anticipate accesses to blocks of memory based on usage patterns. With prefetching [44], data latency is reduced by overlapping memory reads with computation. Unlike prefetching, cache injection reduces memory pressure by reducing the number of accesses to main memory.

The performance of cache injection is dependent on several factors including timely usage of data, the amount of data, and the application's data usage patterns. In a multi-processor system, the consumer processor has to be identified so that data is written into the appropriate cache. If the application does not use the injected data promptly, cache injection may result in cache pollution, evicting the application's working set from the cache. This motivates the need for injection policies that determine the consumer processor and the appropriate level of the memory hierarchy where data may be written (L2)

cache, L3 cache or main memory). The information needed for such policies may come from different sources including the OS, the compiler, the application, and the communication library. For example, the OS is responsible for assigning software threads/processes to cores/processors and maintaining this information.

In this chapter, I provide: (1) experimental results showing that cache injection can reduce memory bandwidth utilization as compared to data prefetching; (2) an example where cache injection without an appropriate policy can be harmful to application performance; and (3) injection policies based on OS, compiler, and application information that can overcome the limitations of this technique.

## 2.1 What is cache injection?

In current architectures, data from I/O devices is written to main memory. Before the processor can use this data, it is fetched to the cache by the processor or by a prefetch engine. With cache injection, data from I/O devices is placed directly from the I/O bus into a processor's cache. Cache injection reduces memory latency by satisfying memory requests from cache, and it reduces memory pressure by reducing the number of requests to the memory controller.

Cache injection is a producer-driven and non-binding technique. It is producer-driven because the data transfer is initiated by the producer of data, in this case an I/O device. When a block of data is written or injected into the cache, it follows the cache's replacement and coherency protocol. This operation is non-binding because data is not bound to a particular block in the cache.

Producer-driven mechanisms can be classified as implicit or explicit [10] depending on whether the producer knows the identity of the consumer. Cache injection is an explicit method, the consumer or target of data must be identified before the injection operation

takes place. The target can be an L2 cache, L3 cache, or main memory. Also, the consumer processor must be identified to determine the appropriate cache or memory. In the remainder of this document, I use cache injection of incoming network messages to provide a specific example of this technique, even though cache injection can be used with other DMA devices.

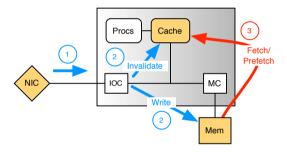

Figure 2.1 depicts the steps a traditional cache-coherent architecture follows when receiving data from the network. For each cache block, a write-invalidate operation is performed, i.e., write to memory and invalidate the appropriate cache block. This operation results in compulsory cache misses, thereby incurring memory latency for incoming network data. Although prefetching can overlap memory latency with computation, memory bandwidth is still used.

Figure 2.1: Memory write operation initiated by the NIC. In step 1, incoming network data arrives at the NIC which in turn initiates the transfer to memory through the IO controller (IOC); in step 2, cached copies are invalidated and data is written to main memory through the memory controller (MC); in step 3, the processor or the prefetch engine fetches data from main memory into the cache.

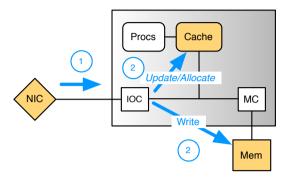

Figure 2.2 depicts the steps to move data from the network to a processor using cache injection. Cache injection transfers incoming network data directly from the NIC to a processor's cache. When this data is used promptly by the processor, memory latency and memory pressure are significantly reduced. Fetching incoming network data from memory is no longer necessary and, thus, requests issued to the memory controller are decreased. Reducing memory traffic may translate into performance improvements for

memory-bound applications.

Figure 2.2: Cache injection operation initiated by the NIC. Unlike the memory write operation, step 2 allocates/updates incoming network data into the cache. If the processor uses this data promptly, there is no need to fetch it from main memory.

#### 2.2 Cost considerations

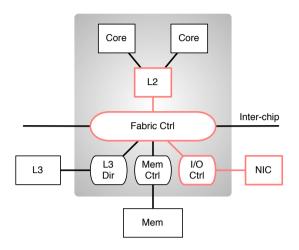

The benefits of cache injection on application performance stem from reducing memory latency and memory pressure. Cache injection, however, presents costs that have to be considered. In this section, I analyze these costs. The base architecture in consideration is based on a Power5 architecture [54]. This system represents a modern multi-core system with an integrated, on-chip memory controller (see Figure 2.3).

Modern systems provide a hierarchy of caches, some local to a particular core, and others shared by a number of cores. One of these caches must be selected when using cache injection. Selecting a local cache provides lower latency at the expense of lower capacity. Targeting a local cache may require information from the OS about the location of the consumer of data. A simpler implementation of cache injection may target a shared cache. A shared cache provides greater capacity at the expense of higher latency. This greater capacity reduces the probability of evicting the application's working set.

Figure 2.3: Base architecture for cache injection (based on IBM's Power5).

Major architectural modifications to the individual caches are not needed to implement cache injection. The caches in the base architecture are snooping associative caches and implement an extension of the MESI coherency protocol. When cache injection is enabled, data is written to main memory and allocated into the cache. The state of the appropriate cache block is set to clean-exclusive. If cache injection only writes to the cache, the state of the block can be set to modified-exclusive. Thus, when it is evicted from the cache, it will be written back to main memory. Both of these states are part of the existing coherency protocol. Cache replacement policies remain the same (pseudo LRU). Also, caches are expected to be at least 8-way associative [28] to reduce evictions of recently injected data. The base architecture implements a 10-way L2 cache and a 12-way set associative L3 cache.

As shown in Figure 2.3, the base architecture already provides data and control paths to the cache through the fabric controller. In the base architecture, the NIC issues invalidation requests to the cache and data requests to main memory when moving incoming network data to the host. The fabric controller forwards the invalidation requests to the cache and the data requests to the memory controller. Cache injection replaces invalidation requests

with allocate requests. Thus, cache injection does not need any additional control or data paths.

The major modifications when enabling cache injection are implemented on the NIC. Each transaction issued by the NIC adds an identifier of the target device. In other words, the NIC determines the data's destination (L2, L3 or main memory) using this identifier. The chipset should be able to route transactions from the NIC to the specified device. Also, the NIC's firmware has to be modified to implement a particular injection policy. An injection policy determines when and what to inject into the cache. These policies, as shown later in this chapter, may require information from the OS, the application, and the compiler. The communication library will also require modifications to communicate this information to the NIC. The operating system and applications, however, can run unmodified.

In summary, minor architectural changes are necessary to enable cache injection in modern architectures. The NIC, however, requires sufficient resources to implement the injection policy of interest and may also need information from the host that can be provided by the communication library. The OS and applications can run unmodified.

## 2.3 Comparing cache injection and data prefetching

In the previous section, I analyzed the architectural and system costs of implementing cache injection. In this section, I provide the context for this technique by comparing it with data prefetching. Prefetching is a well-know, widely implemented technique to hide memory latency. Using simulation and a micro-benchmark, I show that cache injection, unlike prefetching, can reduce memory traffic due to network data. This reduction in memory bandwidth usage is significant for applications whose memory bus is already saturated.

Cache injection and data prefetching strive to reduce data latency by moving data into the cache before it is needed. Unlike prefetching, which provides a general technique to reduce memory latency, cache injection can only be applied to data from I/O devices. Prefetching is a consumer-driven technique—initiated by the application, the OS, or the compiler, while cache injection is producer-driven—initiated by an I/O device, e.g., a NIC.

Many studies have shown that prefetching can be an effective technique to reduce data latency. However, prefetching has a significant disadvantage when compared to cache injection. Prefetching data from I/O devices consumes memory bandwidth due to two transactions: (1) transfer of data from the I/O producer to memory (while invalidating cached copies); and (2) fetching data from memory when demanded by the consumer. With cache injection, the second transaction is not necessary (assuming that the data is used promptly), decreasing the amount of data that has to go over the memory bus.

Both techniques may not perform optimally. Certain applications may not use sufficient computation instructions in between memory accesses to allow prefetching to hide memory latency. Both techniques are prone to cache pollution if data brought to the cache is not used promptly (see Section 2.4). Table 2.1 summarizes the differences between prefetching and cache injection.

Table 2.1: Prefetching vs. cache injection.

Prefetching Cache injection

| Prefetching               | Cache injection                                                                             |

|---------------------------|---------------------------------------------------------------------------------------------|

| 1) write to memory        | 1) write to                                                                                 |

| 2) fetch to cache         | cache                                                                                       |

| use memory bw             | reduce bw usage                                                                             |

| reduce da                 | ta latency                                                                                  |

| data is not used promptly |                                                                                             |

| general-purpose           | limited to I/O                                                                              |

| consumer-driven           | producer-driven                                                                             |

|                           | 1) write to memory 2) fetch to cache use memory bw reduce da data is not us general-purpose |

In the next two sections, I provide experimental results comparing cache injection and data prefetching. Section 2.3.1 describes the testing environment, while Section 2.3.2 describes the methodology and results.

#### 2.3.1 Experimental framework

In this section, I describe the infrastructure to compare, experimentally, cache injection and data prefetching. Since no architecture exists that implements cache injection, I use simulation.

The experimental infrastructure is based on simulation and consists of two components: the base architecture and a high-performance communication system. The base architecture is based on IBM's Mambo full-system simulator [7]. Mambo has been extended with an implementation of cache injection to the L3 cache [6]. The simulated machine is based on a cache-coherent, distributed shared memory architecture.

The high-performance communication system consists of a simulated high-performance NIC that attaches to Mambo and an OS-bypass zero-copy network stack [18]. The NIC is capable of running arbitrary functionality. It interacts with the host system through conventional write-invalidate memory operations and through non-binding write-allocate/update cache injection operations.

The network stack provides an unreliable datagram connectionless service with a UDP-like interface. I implemented this interface using an OS-bypass, zero-copy design which is common in high-performance networks. This implementation, Fast UDP [17], consists of code running on the host and code running on the NIC. The code running on the host is a user-level library that virtualizes NIC resources to applications. The code running on the NIC implements message matching and checksum processing.

In commodity UDP implementations, when a packet arrives from the network, the NIC copies the message to a kernel buffer and raises an interrupt to notify the kernel about its arrival. The OS processes the packet through the UDP/IP stack and then copies the payload to user space. In Fast UDP, the NIC has been instrumented to partially process UDP packets so that the payload is transferred directly from the NIC to user space, while the header (control information) is copied to a kernel buffer. Thus, the kernel remains aware

of incoming network packets, but does not incur overhead of processing application's data (including an extra copy to user space).

Like UDP, message matching semantics of Fast UDP are based on an IP address and a port. Unlike conventional UDP implementations, this operation in Fast UDP is performed on the NIC. The information about receive UDP buffers is shared by the OS with the NIC when a user posts a UDP receive. When a UDP packet arrives from the network, the NIC matches the packet using its destination port, and if a user has posted a receive for that port, the payload will be delivered to the user buffer. UDP checksum on the packet is performed on the NIC to avoid the transfer of erroneous data to the user.

#### 2.3.2 Experimental evaluation

Using the infrastructure described in the previous section, I compare quantitatively cache injection and data prefetching by measuring memory bandwidth and execution time of a micro-benchmark in three configurations: (1) base case with no optimizations; (2) base configuration with prefetching; and (3) base configuration with cache injection. The micro-benchmark performs a linear traversal of incoming network data in calculating a reduction operation. This micro-benchmark represents a stage of computation that is limited by memory bandwidth and provides an optimal case for prefetching (linear traversal of data).

The machine configuration for these experiments is shown in Table 2.2. The simulated machine is based on a Power5 architecture [54] with a non-binding cache injection implementation to the L3 cache. The processor chip includes an L2 cache, a memory controller, and an I/O controller. The L3 cache is a victim cache [24] and is implemented off-chip. Data prefetching is implemented in hardware by the architecture. Data is prefetched into the L1 data cache by first fetching it into the L2 cache and then from the L2 to the L1 cache. The operating system is IBM's K42 research kernel [3].

Table 2.2: System configuration parameters.

| <u>, , , , , , , , , , , , , , , , , , , </u> |

|-----------------------------------------------|

| Mambo PowerPC full-system simulator           |

| K42                                           |

| Fast UDP                                      |

| Power5 with cache injection to L3             |

| 1.65GHz frequency                             |

| 64KB/32KB 2-way/4-way                         |

| 1.875MB 3-slice 10-way 10 cycle latency       |

| 36MB 3-slice 12-way 80 cycle latency          |

| 128B                                          |

| 512MB 230 cycle latency                       |

|                                               |

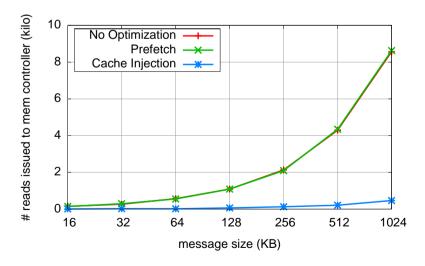

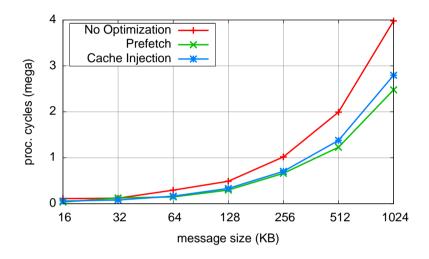

First, I measure the memory bandwidth used by the micro-benchmark in terms of the number of memory reads issued to the memory controller. As shown in Figure 2.4, the base case and the prefetching configuration perform equally as prefetching has to fetch incoming network data from memory. Prefetching anticipates data accesses correctly due to the sequential access pattern used by the application. Cache injection reduces the number of memory reads by up to 96% as all application accesses to incoming network data hit the L3 cache.

Figure 2.4: Memory bandwidth utilization.

Second, I measure the execution time of the application in processor cycles. As shown

in Figure 2.5, cache injection and prefetching outperform the base case as they both reduce the number of cache misses on network data. Prefetching reduces execution time by up to 37% while cache injection by up to 30%. Prefetching performs better because it fetches blocks to the L2 cache, while the cache injection implementation targets the L3 cache [13, 14, 12].

Figure 2.5: Execution time.

Since cache injection reduces memory pressure for incoming network data, its benefits are dependent on the ratio of incoming network data and local data used by the application. The communication traffic and granularity of communication vary from application to application and, thus, the improvements on performance will vary. Several high-performance computing applications will likely benefit from cache injection as they exchange a significant amount of network messages. For example, SMG2000 [9], a memory intensive application, at 384 tasks spends almost 75% of the overall application aggregate time in communication operations [57].

In summary, cache injection reduces memory bandwidth utilization compared to data prefetching. The results presented in this section represent an upper bound on the benefits provided by cache injection.

## 2.4 Limitations of cache injection

In the previous section, I showed that cache injection can reduce memory pressure significantly. Also, previous work [6, 28] showed that cache injection can provide significant performance improvements for a particular type of application, namely TCP/IP protocol processing. In this case, the kernel consumes the injected data right after it is written, signaled by an interrupt to the processor.

Cache injection, however, presents challenges intrinsic to the explicit and producerdriven nature of this technique, namely timely transfer and identifying the consumer of data. For example, data may be transferred too early before the consumer can fetch it from cache, or data may be written to the cache of a processor which is not executing the consumer thread. In the former, cache pollution may occur, and in the latter, depending on the architecture, transfer from one cache to another may incur higher overhead than writing to main memory.

Cache injection requires explicit knowledge about the identity of the consumer. The NIC, the producer of data, has to choose quickly between a set of potential consumers. Even in a uni-processor system, the choice between an L2 cache, L3 cache or main memory has to be made. In a multiprocessor system, a core/processor has to be chosen. An incorrect choice of the target may result in higher delays than a conventional system without cache injection.

I refer to the process of transferring data from the NIC to a processor's cache directly without any knowledge of the application's usage patterns nor the state of the system as blind cache injection. In the remaining of this section, I show an application based on the Jacobi method in which cache injection without an appropriate injection policy (i.e., blind injection) suggests loss of performance. This motivates the study of injection policies, which are directly related to the effectiveness of this technique.

#### 2.4.1 The Jacobi method

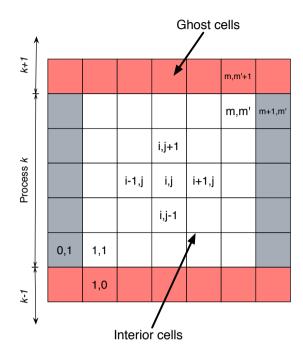

The Jacobi method [23] is an iterative algorithm used to solve a partial differential equation called the Laplace equation. This method can be used, for example, in calculating the temperature of a body represented by a multidimensional grid. At each time step, the Jacobi method computes the temperature of all interior points or cells based on their neighbors' values. The algorithm continues to refine the temperature values until a specific threshold is reached. The boundary points are fixed and set by boundary conditions.

A simple parallel implementation of this algorithm on a two-dimensional grid (n,n), may partition the problem domain into sub-domains that can be assigned to individual processes. Figure 2.6 shows the problem domain for a specific process. Given p processes, the grid is decomposed into sets of n/p rows. Every process is in charge of computing  $n^2/p$  points. To compute the values in the first and last rows for a particular process, the values of the boundary rows from its preceding and following neighbors' processes are needed. This requires data exchange between processes. At each time step, each process sends the values of its first and last rows (2N values) to its neighboring processes accordingly. In a message-passing communication paradigm such as MPI [21], an algorithm (per process per iteration) that overlaps computation and communication can be outlined as follows:

- 1. MPI\_Isend row boundary interior cells

- 2. MPI\_Irecv ghost cells

- 3. Calculate interior cell values

- 4. MPI Wait for ghost cells to arrive

- 5. Calculate boundary interior cell values

The steps of this algorithm can be classified into communication and computation stages. Steps 1, 2 and 4 are communication steps, and steps 3 and 5 are computation steps.

Figure 2.6: Jacobi problem domain for process k.

## 2.4.2 Performance using blind injection

Assume that the algorithm outlined above is running in a cluster of nodes, where one process runs in one node and each node is connected through a NIC to the cluster's network. At the beginning of execution, each process executes communication steps 1 and 2. Since the communication operations are non-blocking, each process continues executing step 3 even if the previous operations have not been completed. Also, assume that while executing step 3, ghost cells arrive to the NIC and are written to main memory (overlap of computation and communication). If step 3 is long enough for the communication stage to complete, then step 4 completes immediately, and the system continues to execute the last step. Otherwise, the process waits for the requested data to arrive and at that point moves to the last step.

In a system with blind cache injection, i.e., data is moved directly from the NIC to

a processor's cache as soon as it arrives, the overlap of communication and computation steps may be problematic. While the processor is working on local data, the NIC cache injection operation may be taking the application's working set out of the cache. Thus, the application has to fetch its working set again possibly replacing those blocks written by the NIC. After completion of step 3 and if the network data has arrived, the processor has to fetch the network data back to the cache to execute the last step. The effects of blind injection in this case result in the overhead of unnecessarily evicting the application's working set from the cache and then fetching this data back to the cache. This overhead increases memory bandwidth traffic as well as data latency. The conventional system without cache injection performs better.

The performance penalty incurred by blind injection is due to the producer-driven nature of this technique. In other words, data is written to the cache as soon as it is produced (when it arrives from the network), which happens to be too early for the application to take advantage of it. To leverage the data latency and memory bandwidth benefits of this technique, injection policies to make informed decisions about when to inject data to the cache are necessary.

Two simple policies can overcome this problem: (1) for incoming network data whose size exceeds a specific threshold, write data to the L3 cache, otherwise write data to the L2 cache; and (2) if the consumer thread or process is blocked waiting for data, write into the L2, otherwise write to main memory. The first policy is appealing considering the growing size of L3 caches, e.g., a Power5 machine contains a 36MB cache. The second policy requires OS information and may improve performance by speeding up the completion of step 4 (wait step).

Thus, if the consumer thread does not use the injected data promptly, blind cache injection may create cache pollution resulting in loss of performance. The performance benefits of this technique rely on informed injection policies. This information is based on the usage pattern of applications, the OS, the compiler and the communication library.

## 2.5 Injection policies

To leverage the performance improvements that can be provided by cache injection, adequate policies are needed. The goal of these policies is twofold: (1) to determine the appropriate place in the memory hierarchy for incoming network data; and (2) to identify the appropriate processor that will consume this data. In this section, I present a set of policies based on information from the OS, the compiler, and the application to make adequate decisions about what, when, and where to inject incoming network data.

**Processor-direction** Inject to the processor/cache where the consumer thread is executed.

This information is provided by the OS and can be included in the memory descriptors that the NIC will use to match incoming messages. When a buffer is registered (pinned in memory) for communication, the OS adds the identifier of the consumer processor to the memory descriptor. MPI processes on a node are not expected to migrate. However, if they do, the OS can update the NIC with this information so that messages can be routed to the appropriate processor. This policy depends on the specific architecture where cache injection is implemented and it should take into consideration the latency for cache-to-cache transfers inside and outside a chip, and between chips as well as memory-to-cache latencies between chips and within a chip. Based on these parameters, the NIC can make a better decision to place incoming network data into the appropriate target to reduce memory bandwidth usage and data latency.

Application/Compiler-driven Inject to the target cache when the application, communication library and/or compiler explicitly solicits the data. This policy uses software injection which is analogous to software prefetching. With software injection, hints are passed to the NIC to indicate that specific messages should be injected into the cache. These hints can be automatically generated from the compiler using existing prefetching techniques, or they can be specifically indicated by the application

#### Chapter 2. Cache injection

and/or communication library.

On-wait Inject to the target cache when the consumer thread is blocked waiting for incoming network data. The communication library may notify the NIC when the application is about to block waiting for network data. The notification may include a token identifying a particular memory descriptor on the NIC. When a matching message arrives from the network, the NIC writes to the cache if the receiving memory descriptor indicates that the application is waiting. Otherwise, data is written to main memory.

In-cache Inject to the target cache if the line is present. This policy requires querying the cache for a particular line or set of lines. Searches in a cache can be an expensive operation since the whole cache may be traversed. Smart searches [33] can be employed to determine rapidly if a line is not in the cache. However, the search algorithm is prone to false-hits. In other words, the search may indicate a hit when the line is not cached. Smart searches use an array located in the cache controller to store partial tag bits. Depending on the number of bits, false-hits are less probable to occur at the cost of extra space in the smart search array. The cost of this policy is directly related to the overhead of a cache search and is dependent on the architecture.

**Meta-data** Inject to the target cache the header or information about the payload of a message. In MPI, for example, the header is represented by the message envelope and may be used by the communication library shortly after written to the cache. The library may be polling a message notification queue, or it may be scheduled to run explicitly after a network interrupt issued by the NIC.

**Size-dependent** Inject to the L2 cache, L3 cache, or main memory depending on the size of the caches and the size of the incoming message. For medium or large messages, this policy may inject to the target cache the first part of a message and write the

#### Chapter 2. Cache injection

rest to main memory. The idea is to let the prefetch engine fetch the rest of the message to the cache as it is needed. This policy reduces data latency by potentially overlapping computation on the first part of the message with memory latency for the rest of the message. In this case, there are no savings on memory bandwidth for the second part of the message.

The performance of these policies on application performance is dependent on several factors including the size and frequency of messages, the type of communication operations, and the ratio of communication to computation.

# Chapter 3

# **Experimental infrastructure**

In Chapter 2, I described the benefits and limitations of cache injection from first principles. I analyzed the architectural and system costs of implementing this technique; showed that cache injection reduces memory bandwidth utilization compared to prefetching using a micro-benchmark; demonstrated that cache injection can decrease application performance without an appropriate policy; and proposed policies to address the limitations of cache injection.

In this chapter, I describe the experimental infrastructure to demonstrate the effect of cache injection on application performance. The requirements of this infrastructure include cycle-accurate simulation of nodes (including cache injection), execution of unmodified message-passing applications at scale (hundreds of nodes), and functional and time-accurate simulation of the network. The resulting infrastructure is a distributed, cache injection cluster simulator that allows the execution of unmodified MPI applications at scale.

The study of cache injection at scale is part of a broader problem to simulate novel architectural features on many computational nodes. Researchers are exploring potential architectural changes for clusters, including a wide range of techniques such as hard-

ware matching support for scalable communication libraries [8] and radical architectural changes like processor-in-memory [53]. Unfortunately, the impact of such changes are difficult to predict analytically due to complex interactions between the architecture, operating system, system libraries, and applications.

Architectural simulators that examine the impact of system changes on application performance have not historically scaled well. For example, coarse-grained simulators skew dramatically when these changes are scaled up over tens or hundreds of systems. Similarly, cycle-accurate simulators, which can model each event to nanosecond accuracy in a single system, scale up poorly. Their running time increases dramatically even for a small number of processors. This limits designers in their ability to study how architectural changes affect scientific application performance as a cluster grows in scale.

To address this problem, I present an MPI-based cluster simulator designed to enable studies of architecture/operating system/application interactions on current and future architectures. Unlike previous work, my cluster simulator architecture uses existing clusters to simulate future clusters by coupling a cycle-accurate full-system node simulator<sup>1</sup> with an MPI-based high-performance network model. The resulting MPI-based cluster simulation system can be used to predict the impact of architectural changes such as cache injection.

In the following section, I describe the cluster simulator in detail followed by validation results showing that this simulator is accurate.

<sup>&</sup>lt;sup>1</sup>A *full system* in this context means all the components that make up the compute engine of a cluster node: CPUs, caches, main memory, and the components that connect these parts.

### 3.1 Cluster simulator

To study the impact of cache injection on scientific applications at scale, I built an apparatus to simulate a cluster of machines based on a cycle-accurate simulator which leverages the parallel computation capabilities of current clusters. The simulated cluster is simulated on an actual cluster. A number of simulated nodes are run per physical node depending on the node's available resources. Communication between simulated nodes entails communication between physical nodes. By decoupling the simulation of individual nodes and the simulated interactions between them, a true parallel implementation can be achieved. The NIC and network model are distributed among the simulated nodes, resulting in a scalable simulator.

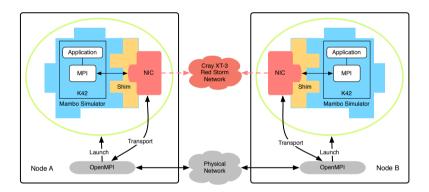

This apparatus consists of the following components: (1) a multiprocessor, multicore full-system simulator that simulates one computational node; (2) an OS, communication libraries and MPI applications for the simulated node; (3) a shim layer to bridge between a simulated node and a physical node; (4) a modeled NIC to communicate between simulated nodes; (5) a modeled network that models the network between simulated nodes; and (6) a message-passing communication system on the physical cluster that allows the launching and communication capabilities of the simulated cluster. I use the following terms for the rest of this chapter: a node refers to a physical host within the physical cluster; a machine refers to a full-system simulator (simulated node) running on a node; and a NIC refers to a modeled NIC that connects machines within the simulated cluster.

The simulated cluster is launched on a physical cluster by executing one instance of the full-system simulator per node. The machines communicate with each other over a modeled network through a modeled NIC. The NIC serves as a bridge between a (simulated) machine and a (physical) node. The NIC uses the existing messaging system (MPI) on the physical cluster to communicate with NICs running on other machines.

The full-system simulator provides a cycle-accurate simulation of a single-node, mul-

tiprocessor system. This machine provides a platform to study architectural features and configurations not yet available in current hardware. My goal in developing a cluster apparatus is not to create such single-node simulators, but to leverage their capabilities in a cluster setting. Communication between machines is achieved through a modeled NIC that can be loaded dynamically into the simulator and communicates with other machines through their associated NICs.

The specific simulator I use for this infrastructure is an augmented version of IBM's Mambo full-system simulator [7] with cache injection of incoming network messages [6]. The simulated machine is based on a Power5 architecture [54]. This architecture provides three levels of cache. The L1 and L2 caches are on board the processor chip, while the L3 cache is off-chip. The memory controller and L3 directory are also on board. The L2 is inclusive of the L1 cache, and the L3 is a victim cache (cache blocks evicted from the L2 are allocated in the L3 cache). Every machine runs the K42 research OS [3].

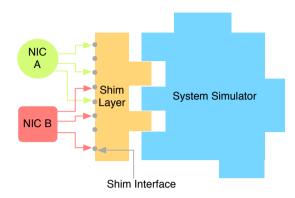

A simulated machine and its modeled NIC interact through a shim layer [18]. This layer provides a bidirectional path between the simulated machine and the NIC (see Figure 3.1). On one side, a machine communicates with its NIC through memory mapped registers. Using this mechanism, a user process can interact with the NIC directly, bypassing the OS and/or Hypervisor if needed. Access to these registers is controlled by the OS and/or Hypervisor. On the other side, a NIC communicates with its machine through a well-defined interface called the shim interface (see Table 3.1). This interface allows the NIC to write to the host's main memory and caches, to perform computation using the host's timing model, and to provide the appropriate functions to execute on accesses to memory mapped registers. In addition, the shim interface provides functions to load and unload network interface controllers and other devices at run time.

A modeled NIC connects its associated machine with the rest of the simulated machines running on the cluster. In addition, it functions as a bridge between its machine and the physical node it is running on. A NIC communicates with its associated machine

Chapter 3. Experimental infrastructure

Figure 3.1: The shim layer provides the glue between the system simulator and the modeled NIC.

Table 3.1: A shim interface

| Function                     | Description                  |

|------------------------------|------------------------------|

| memory_read/write            | read/write to host memory    |

| cache_write                  | write to L2/L3 cache         |

| schedule_job                 | launch async task            |

| delay_cycles                 | time delay on host           |

| raise_interrupt              | I/O interrupt                |

| <pre>memory_mapped_I/O</pre> | functions to trigger on regs |

through the shim layer and to other machines (running on other nodes) using the physical node's transport layer.

The NIC is capable of reading and writing to host memory and writing to the L2 and L3 caches. Writing to memory is performed by issuing write-invalidate bus transactions. Writing to a cache is performed in chunks of one cache block, and the state of the resulting block is set to clean exclusive [55]. Writes of less than one block are handled by a write with flush operation (flush the cache line first and then write the data into memory). Writes to a cache require the physical address of the destination to be block-aligned. Thus, writing incoming network data to a cache may involve writing the first few words using write with flush until the destination address is cache aligned, then writing full blocks to the cache.

Currently, all writes to the cache also update main memory under the assumption that most accesses to network data are read operations (no write-back operations are necessary). A different approach could be used for applications that frequently update incoming network data. Cache injection would only write to the cache, setting the state of incoming cache blocks to modified exclusive (dirty). When the values of these blocks are evicted, they are written back to memory.

The NIC uses the same timing model used by the machine simulator through the shim interface. For example, to perform a specific checksum on a particular packet, the NIC launches an asynchronous job (running in parallel with the simulated host) and assigns a particular delay (in terms of host processor cycles) to this task. Since every simulated machine runs asynchronously of each other, it is possible for one machine to move forward faster than others depending on the resources available for the simulator provided by its physical node. To set an upper bound on the time difference between any two simulated machines, the NIC synchronizes all simulated clocks every few tens of thousands of simulated cycles. The exact number is set based on the model of the network.

Each message sent between simulated machines is augmented by the NIC with a timestamp and delay information about the modeled network. The NIC then sends that information together with the machine's payload using the transport layer provided by the physical node. The receiving NIC waits to deliver the message to its simulated machine until its clock reaches the message's timestamp plus the modeled network delay [36]. This is possible because the network of the physical cluster appears lightning fast in comparison to the very slowly running simulated machines (in real time). The modeled NIC can deliver messages at any specified latency and bandwidth in simulated time, allowing the simulated cluster to use any type of network (physically possible or not). In this work, I use a Cray XT-3 network model based on Seshat [52], an execution-driven discrete event simulator to study application behavior under varying network characteristics.

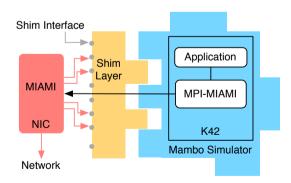

The simulated cluster uses MPI to communicate between simulated machines. My

MPI implementation is based on MPICH [26] and MIAMI (Minimal Interface for An MPI Implementation). As shown in Table 3.2, the MIAMI API abstracts message-passing functionality into a small number of operations that can be implemented by the NIC. MPI operations are translated into MIAMI operations at the host communication library (see Figure 3.2). The library invokes MIAMI operations implemented by the NIC. The modeled NIC supports OS-bypass and allows for zero-copy MPI transfers.

Table 3.2: MIAMI API

| Function  | Description                |

|-----------|----------------------------|

| init      | initialize                 |

| finalize  | clean up                   |

| size      | number of processes in job |

| rank      | my rank in job             |

| clock     | time in seconds            |

| tx_start  | start a send               |

| stx_start | synchronous send           |

| tx_done   | check send completion      |

| rx_start  | post a receive             |

| rx_done   | check receive completion   |

| rx_probe  | probe for message arrival  |

Figure 3.2: The implementation of MPI on a single simulated machine.

The communication between the simulated machine and its NIC through the MIAMI API is implemented with a user-level event queue. Each call to the MIAMI user library

generates an entry into this queue with the appropriate parameters. Once the event is written, a write to memory-mapped registers is performed to signal the NIC about this new event. The user queue is pinned in memory, cache block-aligned and each entry is one cache block in size.

To launch the simulated machines into the physical cluster and to communicate between nodes, I use the physical cluster's MPI library. The resulting MPI-based cluster simulation system is depicted in Figure 3.3 and its parameters shown in Table 3.3.

Figure 3.3: The parallel cluster simulator is simply an MPI job running on a physical cluster.

## 3.2 Validation

My cluster simulation system is based on a validated host simulator [7] and an accurate network model [52]. Even though I cannot validate this infrastructure against a real architecture, because such architecture does not exist, I provide evidence that this infrastructure is accurate.

I examine how the simulator could be used to study the effect of a simple architectural change (throttled network bandwidth) on cluster application performance and compare it

Table 3.3: Simulated system configuration

| Feature      | Configuration                           |

|--------------|-----------------------------------------|

| Simulator    | Mambo PowerPC full-system simulator     |

| Architecture | Power5 with cache injection             |

| Processor    | 1.65GHz frequency                       |

| Memory       | 825MHz on-chip controller, 275MHz DDR2  |

| L1 I/D cache | 64KB/32KB 2-way/4-way                   |

| L2 cache     | 1.875MB 3-slice 10-way 10 cycle latency |

| L3 cache     | 36MB 3-slice 12-way 80 cycle latency    |

| Cache line   | 128B                                    |

| Main memory  | 512MB 230 cycle latency                 |

| OS           | K42                                     |

| Comm. Lib.   | MPICH-MIAMI w/OS-bypass & 0-copy        |

| Network      | Cray XT-3 Red Storm                     |

against previous work [41, 16]. Because my system configuration is not identical to that of previous work, however, I cannot formally validate this result.

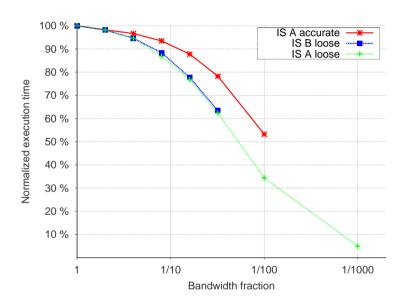

Network throttling is achieved by changing the parameters of the underlying modeled network. I also use these results to study how various simulation modes affect simulation times and how to verify that simulator behavior was consistent across different underlying execution platforms. I use two simulation modes: loose and accurate. In loose mode, the Mambo PowerPC simulator does not simulate the contents of the cache nor the behavior of the system using those caches which saves a lot of simulation time. In accurate mode, all the components of the system are simulated and, thereby, simulation time is slow.

In the following experiments, I use IS from the NAS parallel benchmark suite version 2.4 [5]. This code is a well-known integer sort benchmark. I chose IS because it was used in the previous work that I include for comparison. The runtime of IS is small, making it suitable for cycle-accurate simulations which take many thousand times longer to finish than the native execution time of the tested benchmark. In addition, I chose (small) NAS class A and B data sets for testing IS as opposed to the larger class C and D data sets for

the same reason.

Figure 3.4 is a comparison of IS on four nodes. I compare the results from running IS class A in loose and accurate modes and the class B results. I use the result of the unmodified bandwidth run as the 100% marker. I then plot the runs with fractions of that bandwidth and show the execution time IS reports as a percentage of the execution time when it is run at 100% bandwidth.

Figure 3.4: NAS IS benchmark on four nodes.

The plot lines in Figure 3.4 show very similar trends. The class A and class B runs show almost perfect overlap. The class A run in accurate mode is shifted to the right but shows a similar trend. I believe this shift is due to the changed CPU floating point performance to network bandwidth ratio when running in loose mode which alters the simulated processor performance.

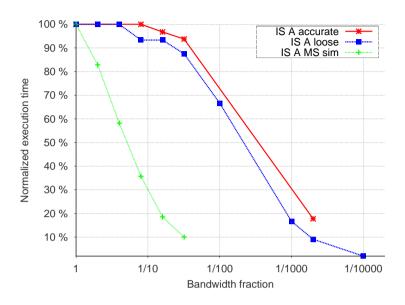

In Figure 3.5, I repeat these IS simulations on sixteen nodes. I see a similar shift to the right of the accurate run versus the loose run as shown in Figure 3.4 for four nodes.

Figure 3.5 also includes the results from [15, 16]. In that work, the authors ran IS on

Figure 3.5: NAS IS benchmark on 16 nodes.

sixteen nodes and artificially slowed down the bandwidth of the network on a real system. This was done by introducing delays in the firmware of the Myrinet network cards in the cluster used for those experiments. I used the numbers obtained in those experiments and normalized them. The resulting line in Figure 3.5 does show a general similarity to the simulations ran on my simulator. Due to a different compute power to network bandwidth ratio, that line is much farther to the left. However, it does show about the same rate of decline in IS performance as the network bandwidth decreases.

These results combined with past work validating Mambo and Seshat show that the simulation infrastructure described in Section 3.1 can be used to predict how system changes would affect the performance of cluster applications. Also, I have shown elsewhere [19] that my simulator can accurately simulate a scalable machine by looking at a scalable application, and I show that it continues to scale when run inside my environment. My simulator has been able to scale to hundreds of nodes. In that work, I also demonstrated that the application's execution time starts to diverge as I increase the synchronization interval. As long as the synchronization interval does not exceed a specific

threshold (application dependent), applications perform deterministically. This behavior was also observed by previous work [20]. These, and other experiments, indicate that my simulator is accurate. Nonetheless, until I can simulate an existing system, direct validation cannot be done.

# Chapter 4

# **Test environment**

My evaluation of cache injection consists of executing MPI applications on a cache injection cluster simulator (see Section 3.1) over a variety of simulated system configurations. In this section, I describe the hardware and software environment used for this evaluation. This includes a description of the platform used for executing the cluster simulator, the simulated system base configuration, the cache injection policies implemented on the modeled NIC, the two parallel applications I ran on the cluster simulator, and the analysis tools used to gather application performance data and MPI collectives performance data.

## 4.1 Platform and simulated system configuration

I ran the cluster simulator on two cluster systems: Phoenix, a 16-node cluster at the University of New Mexico and Thunderbird, a much larger machine at Sandia National Laboratories. Phoenix is comprised of 16 compute nodes. Each node has two 2.20 GHz Intel Xeon processors and 1 GB of memory. A Gigabit Ethernet serves as the interconnect fabric. Phoenix uses the OpenMPI library [25] version 1.2.4 to transmit messages between nodes. The nodes run the Ubuntu Linux distribution using a 2.6.20 kernel. Thunderbird

is comprised of 4,480 compute nodes. They are dual 3.6GHz Intel EM64T processors with 6 GB of RAM. Thunderbird's network is an Infiniband fabric with a two level Clos topology. The nodes run Red Hat Enterprise Linux with a 2.6.9 kernel and use Lustre as the parallel file system. I used OpenMPI version 1.2.7 and OFED version 1.3.1 to connect to the Infiniband fabric.

The experimental results are gathered from a simulated cluster with very different characteristics than those systems on which the cluster simulator is executed. The simulated system configuration is shown in Table 3.3. This cluster is based on IBM eServer p550 nodes with cache injection running the K42 operating system. The nodes are interconnected with a Cray XT-3 Red Storm network.

## 4.2 Injection policies

In this section, I describe a subset of the policies from Section 2.5 that I implemented on the simulated system to evaluate cache injection. These policies are implemented on the NIC and place incoming network data and associated communication events into the appropriate level of the memory hierarchy (L2, L3 or main memory). The following policies are tailored for MPI and use the techniques outlined more generally in Section 2.5.

The first policy called **header** or **hl2** writes message headers (communication events) to the L2 cache. This policy is an instance of the meta-data and size-dependent policies, and is based on the interaction between the communication library (MIAMI) and the NIC. The host library and the NIC communicate through a queue of communication events residing on the host and pinned in memory. An event in the queue is used by the library to invoke a particular communication operation on the NIC. The library writes the operation's parameters to an event and signals the NIC about this operation using memory mapped registers. The NIC pulls the event from host memory, initiates the requested operation,