## University of New Mexico UNM Digital Repository

Electrical and Computer Engineering ETDs

**Engineering ETDs**

6-9-2016

# FPGA IMPLEMENTATION OF A REALTIME CYCLOSTATIONARY FEATURE DETECTOR FOR OFDM SIGNALS

Sean Hamlin

Follow this and additional works at: https://digitalrepository.unm.edu/ece etds

#### **Recommended** Citation

Hamlin, Sean. "FPGA IMPLEMENTATION OF A REALTIME CYCLOSTATIONARY FEATURE DETECTOR FOR OFDM SIGNALS." (2016). https://digitalrepository.unm.edu/ece\_etds/112

This Thesis is brought to you for free and open access by the Engineering ETDs at UNM Digital Repository. It has been accepted for inclusion in Electrical and Computer Engineering ETDs by an authorized administrator of UNM Digital Repository. For more information, please contact disc@unm.edu.

Sean Hamlin

Candidate

Electrical and Computer Engineering Department

This thesis is approved, and it is acceptable in quality and form for publication:

Approved by the Thesis Committee:

Dr. Christos Christodoulou, Chairperson

Dr. Sudharman Jayaweera

Dr. Manel Martinez-Ramon

### FPGA IMPLEMENTATION OF A REALTIME CYCLOSTATIONARY FEATURE DETECTOR FOR OFDM SIGNALS

by

## SEAN HAMLIN

### BACHELOR OF SCIENCE-ELECTRICAL ENGINEERING WICHITA STATE UNIVERSITY, 2010

THESIS

Submitted in Partial Fulfillment of the Requirements for the Degree of

Master of Science Electrical Engineering

The University of New Mexico Albuquerque, New Mexico

May, 2016

## FPGA IMPLEMENTATION OF A REALTIME CYCLOSTATIONARY FEATURE DETECTOR FOR OFDM SIGNALS

by

Sean Hamlin

B.S. Electrical Engineering, Wichita State University, 2010 M.S. Electrical Engineering, University of New Mexico, 2016 ABSTRACT

The demand for wireless connectivity has prompted regulatory authorities in the United States to investigate spectrum sharing of the DSRC band with U-NII operators. However, DSRC operation has public safety implications, and moreover, time-critical requirements due to the vehicular nature of its application. The field of cognitive radio has identified several sensing techniques for the identification of licensed operators in a given band. This thesis explores cyclostationary detection techniques for primary users. A method will be identified for the detection of the 802.11p OFDM modulation used for DSRC communications. A test statistic will be given that is invariant to the signal noise covariance to allow simple and robust operation. Finally, the detection algorithm will be implemented in FPGA digital logic in order to demonstrate the methods ability to be employed in a commercial radio chipset with minimum resource requirements, yet still provide real-time detection.

iii

## TABLE OF CONTENTS

| LIST OF FIGURES                                                                                      | v   |

|------------------------------------------------------------------------------------------------------|-----|

| LIST OF TABLES                                                                                       | vii |

| CHAPTER 1 INTRODUCTION TO COGNITIVE RADIO                                                            |     |

| 1.1 Overview of Cognitive Radio                                                                      |     |

| 1.2 DSRC Spectrum Sharing                                                                            |     |

| 1.3 Overview of Feature Detection Techniques                                                         |     |

| 1.3.1 Energy Detectors                                                                               |     |

| 1.3.2 Matched Filters                                                                                |     |

| 1.3.3 Cyclostationary Detection                                                                      | 7   |

| CHAPTER 2 CYCLOSTATIONARY SIGNAL ANALYSIS                                                            |     |

| 2.1 Introduction                                                                                     |     |

| 2.2 Cyclic Autocorrelation Function                                                                  |     |

| 2.3 Spectral Correlation Function                                                                    | 13  |

| 2.4 Spectral Coherence Function                                                                      | 19  |

| CHAPTER 3 OFDM FEATURE DETECTION                                                                     |     |

| 3.1 OFDM Overview                                                                                    |     |

| 3.2 DSRC Modulation                                                                                  | 22  |

| 3.3 802.11p Simulation Model                                                                         | 27  |

| 3.4 OFDM Features for Cyclostationary Detection                                                      |     |

| 3.4.1 Preamble                                                                                       |     |

| 3.4.2 Pilots                                                                                         |     |

| <ul><li>3.4.3 Cyclic Prefix</li><li>3.5 Detection of Cyclic Prefix with CAF</li></ul>                |     |

| -                                                                                                    |     |

| CHAPTER 4 DSRC DETECTION WITH CAF                                                                    |     |

| 4.1 Spatial Sign Cyclic Correlation Estimator                                                        |     |

| <ul> <li>4.2 Dual-Lag SSCCE with Cyclic Phase Compensation</li> <li>4.3 MATLAB Simulation</li> </ul> |     |

| 4.5 INATLAD Simulation                                                                               |     |

| 4.3.2 ROC at Fixed SNR                                                                               |     |

| 4.3.3 Histogram at Fixed SNR                                                                         |     |

| CHAPTER 5 FPGA IMPLEMENTATION                                                                        |     |

| 5.1 FPGA Overview                                                                                    |     |

| 5.2 SSCCE Algorithm Implementation                                                                   | 53  |

| 5.2.1 Spatial Sign Function                                                                          |     |

| 5.2.2 Lead/Lag Shift Register                                                                        |     |

| 5.2.3 Multipliers                                                                                    |     |

| <ul><li>5.2.4 Numerically Controlled Oscillator</li><li>5.2.5 Moving Average Filter</li></ul>        |     |

| 5.3 SSCCE Behavioral Simulation                                                                      |     |

| 5.4 SSCCE Resource Utilization                                                                       |     |

| 5.5 Conclusion.                                                                                      |     |

| APPENDIX A MATLAB CODE                                                                               |     |

|                                                                                                      |     |

| APPENDIX B HDL CODE                                                                                  |     |

| REFERENCES                                                                                           | 100 |

## LIST OF FIGURES

| Figure 1.1  | DSRC channel plan in the ITS band (from [5])                                                                                                                                                                                    |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2  | Proposed new UNII-4 band (from [5])                                                                                                                                                                                             |

| Figure 1.3  | Example of a receiver operating characteristic (ROC) curve                                                                                                                                                                      |

| AM s        | <ul><li>(a) Power spectral density of lowpass signal.</li><li>(b) Power spectral density of signal.</li><li>(c) Power spectral density of squared lowpass signal.</li><li>(d) Power ral density of squared AM signal.</li></ul> |

|             | Simplified block diagram of a spectrum analyzer for measuring the power ral density at center frequency $f$ (from [12])                                                                                                         |

| U           | Block diagram of a spectral correlation analyzer for center frequency $f$ and frequency $\alpha$ (from [12])                                                                                                                    |

| 0           | Estimated spectral correlation density of an AM modulated signal with: (top) ditive noise, (middle) 5dB SNR, (bottom) -5dB SNR                                                                                                  |

| -           | Contour of the estimated spectral correlation density of an AM modulated                                                                                                                                                        |

| Figure 3.1  | Simplified block diagram of an OFDM modulator and demodulator                                                                                                                                                                   |

| Figure 3.2  | DSRC channel plan (from [18])                                                                                                                                                                                                   |

| Figure 3.3  | PPDU frame format (from [21])                                                                                                                                                                                                   |

|             | Time-domain plot an 802.11p PPDU frame of 10 symbols encoded with 64-<br>                                                                                                                                                       |

| -           | Power spectral density of an 802.11p PPDU frame of 100 symbols encoded 54-QAM                                                                                                                                                   |

| Figure 3.6  | Estimated spectral correlation density of an 802.11p PPDU frame                                                                                                                                                                 |

| U           | Contour of the estimated spectral correlation density of an 802.11p PPDU                                                                                                                                                        |

| 0           | Contour of the estimated spectral correlation density of an 802.11p PPDU modified by replacing the pilot subcarriers with nulls                                                                                                 |

| U           | Contour of the estimated spectral correlation density of an 802.11p PPDU modified by randomizing the pilot subcarriers                                                                                                          |

| Figure 3.10 | D Estimated cyclic correlation density of an 802.11p PPDU frame                                                                                                                                                                 |

| Figure 3.1  | Autocorrelation function of an 802.11p PPDU frame                                                                                                                                                                               |

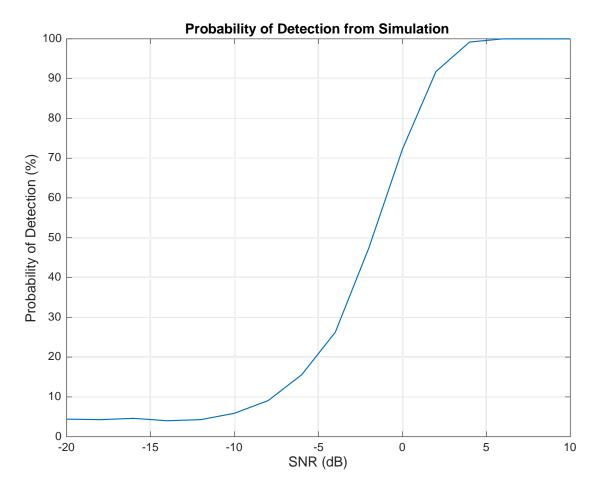

| 0           | Probability of detection vs. SNR of an 802.11p signal corrupted by an AWGN g channel using SSCCE method with sample size of 1000                                                                                                |

| -           | Probability of detection vs. SNR of an 802.11p signal without additional rments using SSCCE method with sample size of 1000                                                                                                     |

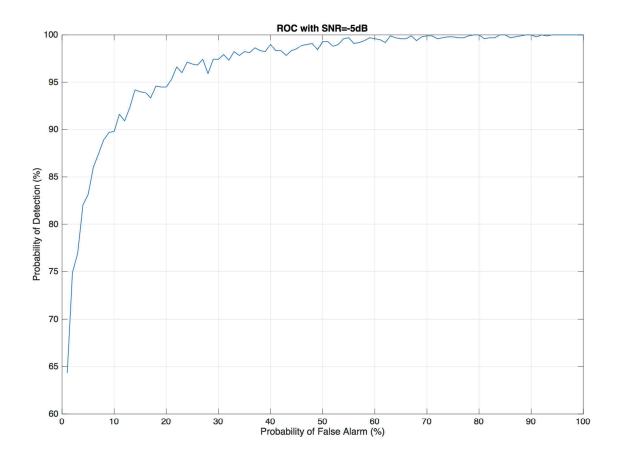

| -          | Receiver operating characteristic curve of the SSCCE method for an 802.11p<br>            |

|------------|-------------------------------------------------------------------------------------------|

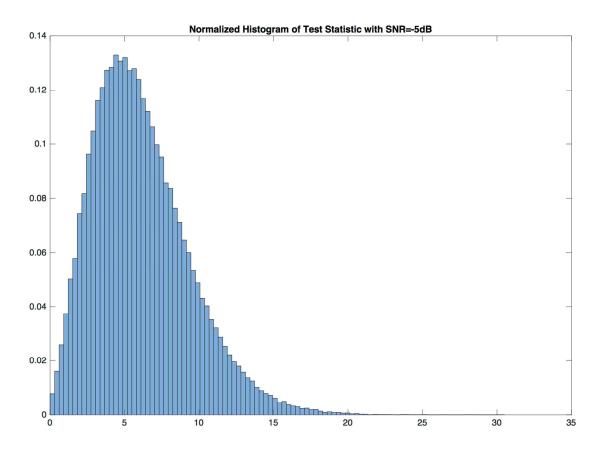

| Figure 4.4 | Histogram of SSCCE test statistic for an 802.11p signal with -5dB SNR 50                  |

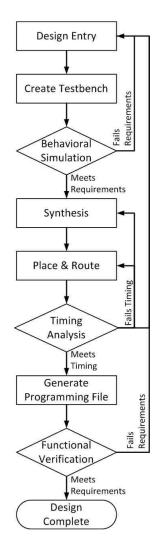

| Figure 5.1 | Flowchart of a typical FPGA design flow                                                   |

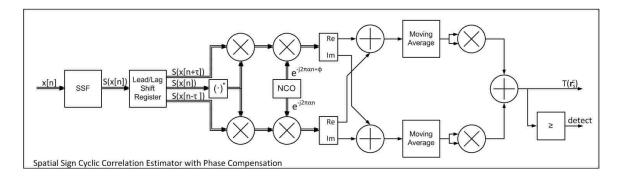

| Figure 5.2 | Block diagram of the FPGA implementation of the SSCCE algorithm 53                        |

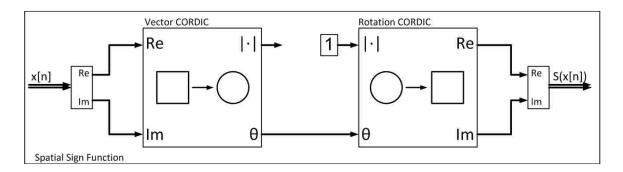

| U          | Block diagram showing the implementation of the SSF using CORDIC es                       |

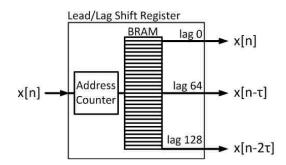

| Figure 5.4 | Block diagram showing the implementation of the lead/lag shift register 56                |

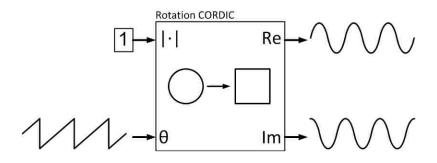

| Figure 5.5 | Block diagram showing the implementation of a NCO using CORDIC 59                         |

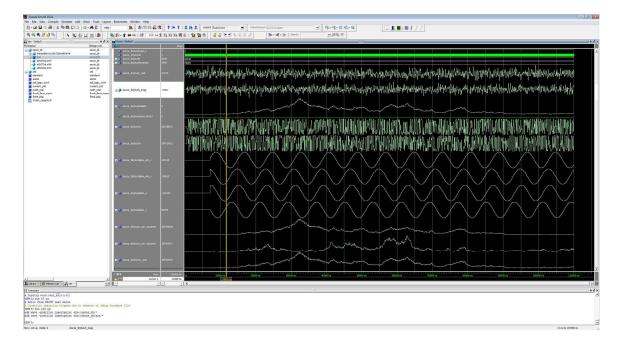

| Figure 5.6 | Screenshot of design simulation using Questa Sim                                          |

| -          | SSCCE algorithm probability of detection vs. SNR results from MATLAB ation                |

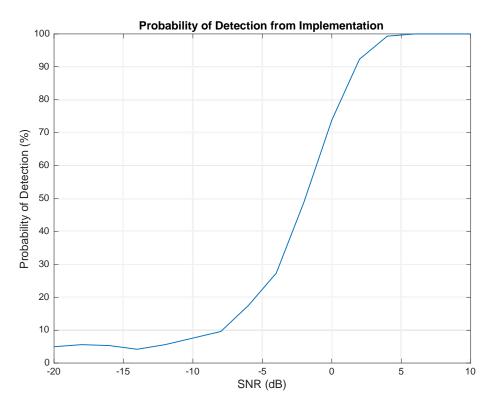

| -          | SSCCE algorithm probability of detection vs. SNR from HDL mentation behavioral simulation |

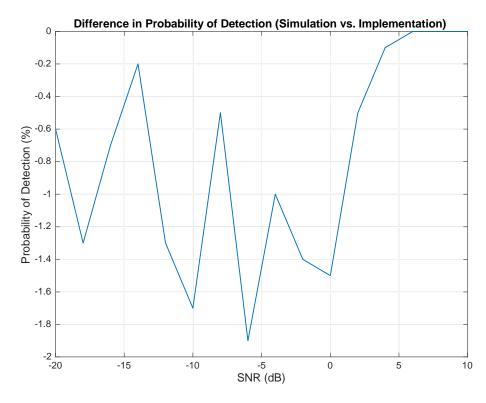

| -          | Difference in probability of detection between MATLAB simulation and implementation       |

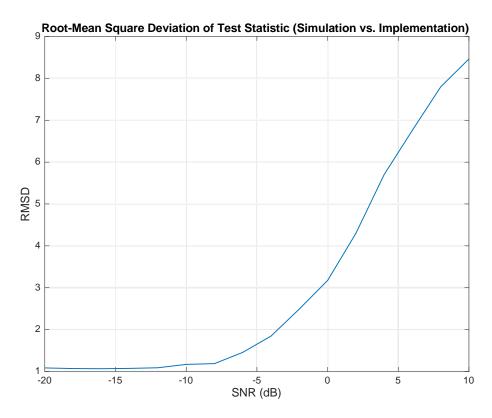

| -          | ) RMSD of the SSCCE test statistic between MATLAB simulation and HDL mentation            |

| U          | Histogram of the first test statistic value to exceed the threshold for 5% $P_{fa}$ .     |

## LIST OF TABLES

| Table 1 | OFDM PHY Modulation Parameters of 802.11p   | 24 |

|---------|---------------------------------------------|----|

| Table 2 | Subcarrier Modulation Parameters of 802.11p | 26 |

| Table 3 | SSCCE Implementation Resource Utilization   | 66 |

#### **CHAPTER 1**

#### **INTRODUCTION TO COGNITIVE RADIO**

#### 1.1 Overview of Cognitive Radio

The demand on spectrum access has exploded within the past decade. Wireless connectivity has seen rapid growth through 4G LTE, the ubiquity of Wi-Fi connection hotspots, and the advent of LTE-A. Along with the incumbent spectrum users for LMR, TV, radio, avionics and military communications, the ability to service all users will become increasingly difficult with the current allocation schema. With this growing strain on the wireless spectrum, interest in cognitive radio has transitioned from its inception in the late 1990's as a means to enhance the radio operator experience [1], to legislative mandate by which the growing spectrum crisis can be mitigated [2].

Several definitions exist for the term cognitive radio. However, when discussed in the context of spectrum sharing, perhaps the most germane description is that provided by a spectrum regulating authority. According to the Federal Communications Commission (FCC), cognitive radio is defined as an emerging technology of software defined radios that monitor, sense, detect, and autonomously adapt their channel access to suit the RF environment in which they are operating [**3**].

#### **1.2 DSRC Spectrum Sharing**

In 1999, the FCC licensed the 5.9 GHz band (5850-5925 MHz) for the purposes of Dedicated Short Range Communications (DSRC) as an Intelligent Transportation

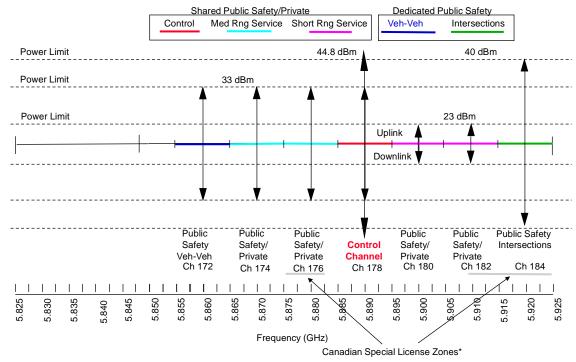

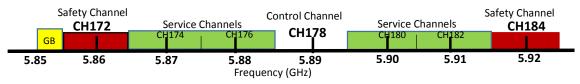

Systems radio service [4]. The intended purpose of this licensed spectrum is enhanced transportation safety via Vehicle-to-Vehicle (V2V) and Vehicle-to-Infrastructure (V2I) communications. Potential uses of DSRC are to alert drivers of approaching emergency vehicles, blind spot, sudden braking, collision avoidance, adverse road conditions, as well as traffic condition updates. Figure 1.1 shows the approved DSRC channel frequency and power limit plan.

Figure 1.1 DSRC channel plan in the ITS band (from [5]).

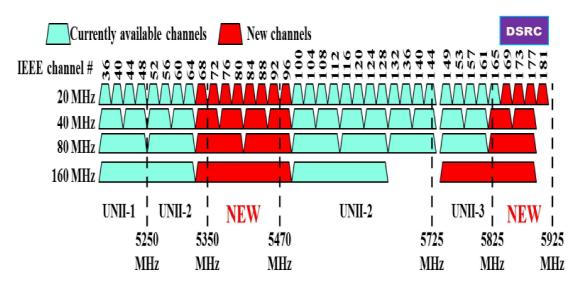

Recently, the FCC and NTIA have been legislatively tasked with opening the 5850-5925 MHz frequency band to U-NII devices [6] as shown in Figure 1.2. Due to the public safety aspect of DSRC, any spectral reuse in this band by secondary users must be subject to the principal constraint of robust detection. Furthermore, due to the potentially high vehicular speed (and thus rapidly changing) mobile environment in which DSRC

transceivers operate, secondary users must quickly detect primary users and relinquish the spectrum. Additionally, given the nature of the currently identified secondary user devices (802.11ac devices) the spectral detection mechanism must be power efficient and consume minimum device resources in order to be commercially viable. Given these constraints, the spectral detection and classification engine will likely reside in the radio chipset of the secondary user device. This thesis will explore a new feature detection technique, focused on the application of spectral reuse in the dedicated DSRC band for 802.11p primary users.

Figure 1.2 Proposed new UNII-4 band (from [5]).

#### **1.3** Overview of Feature Detection Techniques

The scope of the term cognitive radio can include receiver side technologies for detecting spectrum holes, channel estimation, and capacity prediction as well as transmitter side technologies for transmitter power control and dynamic spectrum management [7]. Arguably the main focus of cognitive radio is to enable the sharing of

spectrum between licensed primary users and unlicensed secondary users. Towards this end, spectrum sensing and signal detection techniques comprise a large portion of the research in the field of cognitive radio [8].

In the field of cognitive radio, three primary signal detection techniques are prominent, each with performance and design tradeoffs. These are energy based detection, matched filter based detection, and cyclostationary based detection [8], [9].

#### **1.3.1 Energy Detectors**

Energy based detection is the simplest spectrum sensing technique. This approach does not require knowledge of the primary signal and has a low implementation complexity and computational cost. Energy based detectors simply compare the energy of a receiver output against a threshold value. The threshold value is calculated according to the level of noise in the received signal. In their simplest form, energy detectors calculate a test statistic from *N* received samples as follows:

$$T(y) = \frac{1}{N} \sum_{n=0}^{N-1} |y[n]|^2$$

(1)

where the received signal is assumed to have the form:

$$y[n] = s[n] + w[n] \tag{2}$$

with s[n] being the primary signal to be detected and w[n] is additive white Guassian noise. The goal of spectrum sensing algorithms is to form a decision as to the presence of the primary signal. Therefore, the null hypothesis, that the primary signal is not present, and its alternative are formulated as:

$$\begin{aligned} \mathcal{H}_{o} &: \quad y[n] = w[n], \\ \mathcal{H}_{1} &: \quad y[n] = s[n] + w[n]. \end{aligned} \tag{3}$$

A threshold value,  $\lambda$ , is determined for the test statistic, above which the null hypothesis is rejected. The performance of the energy detector to correctly detect the presence of the primary signal (i.e. its sensitivity) is given as:

$$P_D = Prob\{T(y) > \lambda | \mathcal{H}_1\}$$

(4)

Similarly, the performance of the detectors false alarm rate, that is the probability of asserting the presence of a primary signal when it is not present (i.e. its specificity), is given as:

$$P_{FA} = Prob\{T(y) > \lambda | \mathcal{H}_0\}$$

(5)

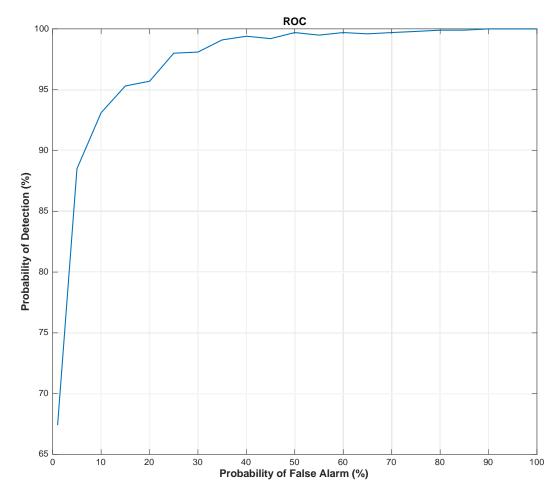

A receiver operating characteristic (ROC) curve is obtained by plotting the probability of detection versus the probability of false alarm, an example of which is shown in Figure 1.3. Naturally it is desired to maximize the probability of detection while minimizing the probability of false alarm. The desired balance between probability of detection and probability of false alarm is controlled by the threshold value  $\lambda$ . In order to determine the value of  $\lambda$ , it is observed that the noise component w[n] is assumed to be normally distributed with zero-mean and variance  $\sigma_w^2$ . The distribution of the test statistic (1) is then given as:

$$T(y)|\mathcal{H}_0 \sim \mathcal{N}\left(\sigma_w^2, \frac{2}{N}\sigma_w^4\right) \tag{6}$$

Using (6), (5) can then be rewritten as

$$P_{FA} = Q\left(\frac{\lambda - \sigma_w^2}{\sqrt{\frac{2}{N}\sigma_w^2}}\right) \tag{7}$$

where  $Q(\cdot)$  is the Guassian complementary cumulative density function [10]. For a given false alarm rate, the threshold value  $\lambda$  can be determined from (7). Typical values for  $P_{FA}$  are 1% and 5%.

Figure 1.3 Example of a receiver operating characteristic (ROC) curve.

As can be seen from the above derivation, the presence of a signal is determined by the energy detector with no apriori information about the primary signal. However, there is also no distinction between a primary signal and interference or other secondary signals. Furthermore, as can be seen from (7), knowledge of the noise power is required to determine the optimal threshold value. It may also be observed that by averaging more samples, an arbitrarily low signal-to-noise ratio could still allow for positive signal detection. However, as shown in [**10**] any slight uncertainty in the knowledge of the noise variance drastically affects the performance of the detection scheme below a certain SNR, regardless of the number of samples averaged.

#### **1.3.2 Matched Filters**

Matched filters provide the optimal detection method for a known signal type. These filters are created by correlating a known signal with the received signal, and are optimal in the sense that they maximize the signal to noise ratio of the filter output. Unfortunately, this method requires complete knowledge of the primary signal, and demodulation of the same, in order to implement. For all but the most simple of modulation types, this method entails a high-computational complexity.

#### **1.3.3** Cyclostationary Detection

Cyclostationary processes are those whose statistical parameters vary periodically as a function of time [**11**]. A common example is meteorological data, which has strong periodicities according to the season. Many communications modulation and coding schemes exhibit cyclostationarity as well.

7

Periodicity in signals can typically be found by visual inspection of either their time series data or through spectral analysis. For example, a signal corrupted by noise,  $x(t) = A \cos(2\pi\alpha t + \theta) + w(t)$ , when subject to the linear transformation with the Fourier kernel will produce spectral lines at  $f = \pm \alpha$ . In such case, regardless of the noise component, the signal is said to contain first-order periodicity in frequency  $\alpha$  [12]. However, a time-series may contain other types of periodicities that do not produce spectral lines. These signals are said to posses wide-sense cyclostationarity of order-*n* if and only if there exists a non-linear time-invariant transformation of the time-series such that the transformed time-series produces spectral lines [12]. Therefore, a signal contains second-order periodicity (i.e. *n*=2) if its time-series undergoes a quadratic time-invariant transformation

$$y(t) = \int_{-\infty}^{\infty} \int_{-\infty}^{\infty} k(u,v) x(t-u) x(t-v) \, du \, dv \tag{8}$$

such that y(t) exhibits first-order periodicity in frequency  $\alpha$  [13]. Some possible quadratic nonlinear time invariant transformation functions could be the squaring operation on the time-series or the multiplication of the time-series with a time lagged version of itself.

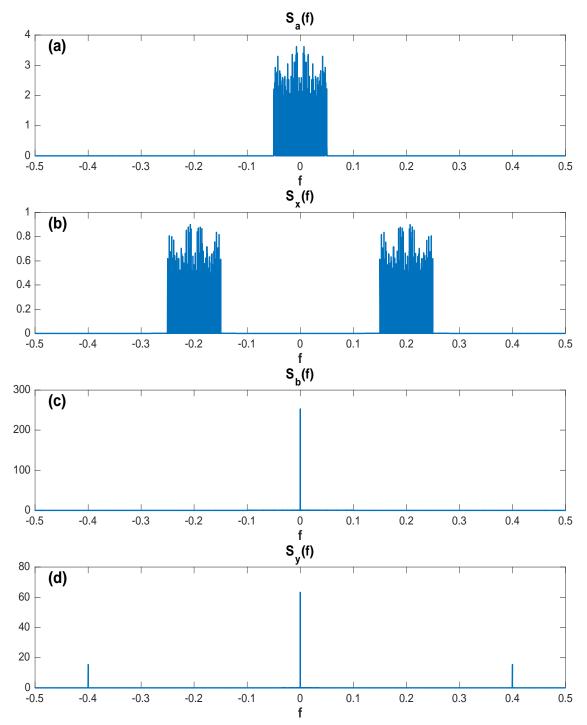

The following example adapted from [12] illustrates the above discussion. Consider a random bit sequence lowpass signal, a(t), with bandwidth B = 0.1, that does not produce spectral lines as illustrated by the estimated power spectral density  $S_a(f)$ shown in Figure 1.4(a). Next, assume a(t) is modulated with a carrier at frequency  $f_c = 0.2$  to produce the AM signal

$$x(t) = a(t)\cos(2\pi f_c t). \tag{9}$$

The resulting power spectral density  $S_x(f)$  of the modulated signal is then

$$S_x(f) = \frac{1}{4} [S_a(f+f_c) + S_a(f-f_c)], \qquad (10)$$

whose estimate is shown in Figure 1.4(b). Observe that the power spectral density of the modulated signal still does not contain any spectral lines. In order to test the modulated signal for second-order periodicity, we use a squaring function as a quadratic time-invariant transformation:

$$y(t) = x^{2}(t) = a^{2}(t) + \cos^{2}(2\pi f_{c}t)$$

$$= \frac{1}{2}[b(t) + b(t)\cos(4\pi f_{c}t)]$$

(11)

where

$$b(t) = a^2(t) \tag{12}$$

The squaring operation forces b(t) to be completely non-negative, boosting the DC component, doubling the bandwidth of a(t) and leading to the spectral line at f = 0 shown Figure 1.4(c). The power spectral density of (11) is

$$S_{y}(t) = \frac{1}{4} \left[ S_{b}(f) + \frac{1}{4} S_{b}(f + 2f_{c}) + \frac{1}{4} S_{a}(f - 2f_{c}) \right],$$

(13)

which is estimated in Figure 1.4(d). The quadratic transformation has therefore produced first-order periodicity by revealing spectral lines at f = 0 and  $f = \pm 2f_c$ . The next chapter will explore cyclostationary methods in more depth.

Figure 1.4 (a) Power spectral density of lowpass signal. (b) Power spectral density of AM signal. (c) Power spectral density of squared lowpass signal. (d) Power spectral density of squared AM signal.

#### **CHAPTER 2**

### CYCLOSTATIONARY SIGNAL ANALYSIS

#### 2.1 Introduction

The previous chapter introduced the concept of cyclostationary time-series. For signals of second-order periodicity, it was shown that a quadratic time-invariant transformation could be used to create a time-series that exhibited first-order periodicity. A simple example of such a transformation was given as the squaring operation. However, the squaring operation is really an example of a more generalized quadratic transformation as shown examination of (8). Specifically, any operation that measures second-order moment (variance) is required. Two second-order measures are the autocorrelation function in the time domain and the power spectrum transform in the frequency domain. Therefore, the definition of wide-sense cyclostationary time-series can be restated as one whose first-order measure (expectation value) and second-order measure (autocorrelation function) are periodic with some period  $T_0$  [11].

#### 2.2 Cyclic Autocorrelation Function

From the definition of wide-sense cyclostationary time-series it is implied that for all  $t, \tau$ :

$$E[x(t + T_0)] = E[x(t)]$$

(14)

$$R_{x}(t+T_{0},\tau) = R_{x}(t,\tau)$$

(15)

where the autocorrelation function is defined as

$$R_x(t,\tau) \triangleq \mathbf{E}[x^*(t+\tau)x(t)]. \tag{16}$$

Because the autocorrelation function (16) is wide-sense stationary, (15) can be simplified to only be a function of  $\tau$ :

$$R_{\chi}(t,\tau) = R_{\chi}(\tau). \tag{17}$$

In order to show if a time-series exhibits second-order periodicity, it is then necessary to see if the time-series that has undergone transformation via the autocorrelation function generates spectral lines. The most intuitive test of first-order periodicity at a frequency  $\alpha$  would be to determine the Fourier coefficient of the autocorrelation function at that frequency [13]:

$$R_x^{\alpha}(\tau) \triangleq \lim_{T \to \infty} \frac{1}{T} \int_{-T/2}^{T/2} x\left(t + \frac{\tau}{2}\right) x^*\left(t - \frac{\tau}{2}\right) e^{-j2\pi\alpha t} dt.$$

(18)

The above expression is referred to as the Cyclic Autocorrelation Function (CAF). Using the CAF, x(t) can be said to exhibit second-order cyclostationarity if and only if for some nonzero value of  $\alpha$ ,  $R_x^{\alpha}(\tau) \neq 0$ , i.e. it contains a sine-wave component. The frequency parameter  $\alpha$  is referred to as the cycle or cyclic frequency and implies that a time-series with cyclostationary periodicity of  $T_0$  has a nonzero CAF at cyclic frequency  $\alpha = 1/T_0$ . Note, that for  $\alpha = 0$  the CAF is the usual continuous-time autocorrelation function.

#### 2.3 Spectral Correlation Function

As in any signal analysis, transformation into the frequency domain can reveal details about the signal of interest that might be obscured or not easily detected by time-domain examination. Cyclostationary signal analysis is no exception. If the CAF is considered a time-domain transform of the time-series, then the question naturally arises as to determining the frequency domain equivalent. Not surprisingly, the answer appears by simply taking the Fourier transform of (18), yielding

$$S_{x}^{\alpha}(f) \triangleq \int_{-\infty}^{\infty} R_{x}^{\alpha}(\tau) e^{-j2\pi f\tau} d\tau, \qquad (19)$$

which is referred to as the Spectral Correlation Function (SCF). The autocorrelation function and the power spectral density are related from the Wiener-Khinchin theorem, a relationship that also applies between the CAF and the SCF as

$$S_x^{\alpha}(f) = \mathcal{F}\{R_x^{\alpha}(\tau)\}.$$

(20)

For this reason, (20) is sometimes referred to as the cyclic Wiener relation [12], [13].

As a consequence of the Wiener-Khinchin theorem, for wide sense stationary signals the power spectral density function can be obtained without explicitly calculating the autocorrelation function:

$$S_{x}(f) = \int_{-\infty}^{\infty} R_{x}(\tau) e^{-j2\pi f\tau} d\tau = \mathbb{E}[|X(f)|^{2}].$$

(21)

The power spectrum density can then be estimated from time-smoothing of the finitetime signal  $x_T(t)$  as follows

$$S_{x}(f) = \lim_{T \to \infty} S_{x_{T}}(f) = \lim_{T \to \infty} \mathbb{E}[|X_{T}(f)|^{2}].$$

(22)

$X_T(f)$  can be estimated from the short-time Fourier transform

$$X_T(t,f) = \frac{1}{\sqrt{T}} \int_{t-T/2}^{t+T/2} x(u) e^{-j2\pi f u} du.$$

(23)

The finite-time estimate of the power spectrum density is then

$$S_{x_T}(t,f)_{\Delta t} = \frac{1}{\Delta t} \int_{-\Delta t/2}^{\Delta t/2} \frac{1}{T} X_T(t+u,f) X_T^*(t+u,f) du, \qquad (24)$$

from which the power spectrum density is calculated according to the limits

$$S_{x}(f) = \lim_{T \to \infty} \lim_{\Delta t \to \infty} S_{x_{T}}(t, f)_{\Delta t}.$$

(25)

Graphically, (24) can be realized as the familiar spectrum analyzer, shown in Figure 2.1, whose output yields the power spectrum density as the filter bandwidth  $B = 1/T \rightarrow 0$  and the observation time  $\Delta t \rightarrow \infty$

$$S_{x}(f) = \lim_{B \to 0} \frac{1}{B} \left\langle \left| h_{BPF}(t) * x(t) \right|^{2} \right\rangle.$$

(26)

$$\begin{array}{c|c} x(t) & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & &$$

Figure 2.1 Simplified block diagram of a spectrum analyzer for measuring the power spectral density at center frequency f (from [12]).

Likewise, the spectral correlation function can be estimated from frequencyshifting and time-smoothing the finite-time signal [13]. First, the complex exponential term in (18) can be factored into the time-series as a frequency shift operation, represented as

$$u(t) = x(t)e^{-j\pi\alpha t},$$

$$v(t) = x(t)e^{j\pi\alpha t},$$

(27)

and having corresponding short-time Fourier transforms

$$\frac{1}{\sqrt{T}}U_T(t,f) = \frac{1}{\sqrt{T}}X_T\left(t,f + \frac{\alpha}{2}\right),$$

$$\frac{1}{\sqrt{T}}V_T(t,f) = \frac{1}{\sqrt{T}}X_T\left(t,f - \frac{\alpha}{2}\right).$$

(28)

Then, analogous to (22)

$$S_x^{\alpha}(f) = \lim_{T \to \infty} S_{uv_T}^{\alpha}(f) = \lim_{T \to \infty} \mathbb{E}\left[U_T(f)V_T^{*}(f)\right].$$

(29)

From which the finite-time estimate of the spectral correlation function is calculated

$$S_{x_T}^{\alpha}(t,f)_{\Delta t} = \frac{1}{\Delta t} \int_{-\Delta t/2}^{\Delta t/2} \frac{1}{T} U_T(t+u,f) V_T^*(t+u,f) du.$$

(30)

And finally yielding the spectral correlation function in the limits

$$S_x^{\alpha}(f) = \lim_{T \to \infty} \lim_{\Delta t \to \infty} S_{x_T}^{\alpha}(t, f)_{\Delta t}.$$

(31)

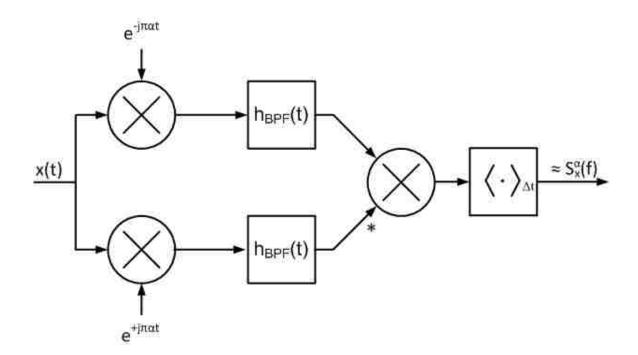

Similar to the spectrum analyzer, a spectral correlation analyzer, illustrated in

Figure 2.2, provides the spectral correlation function output as the filter bandwidth  $B = 1/T \rightarrow 0$  and the observation time  $\Delta t \rightarrow \infty$  [12]

$$S_x^{\alpha}(f) = \lim_{B \to 0} \frac{1}{B} \left\langle \left[ h_{BPF}(t) * u(t) \right] \left[ h_{BPF}(t) * v(t) \right]^* \right\rangle.$$

(32)

Figure 2.2 Block diagram of a spectral correlation analyzer for center frequency f and cyclic frequency  $\alpha$  (from [12]).

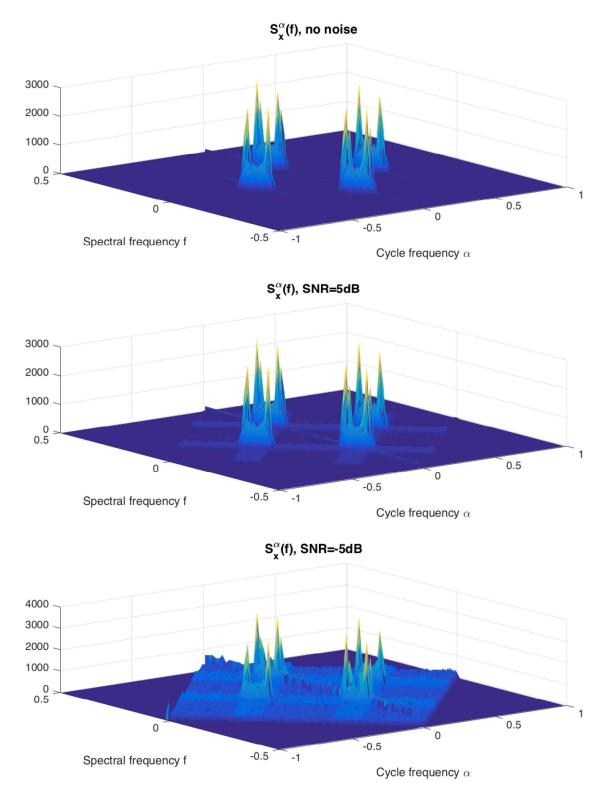

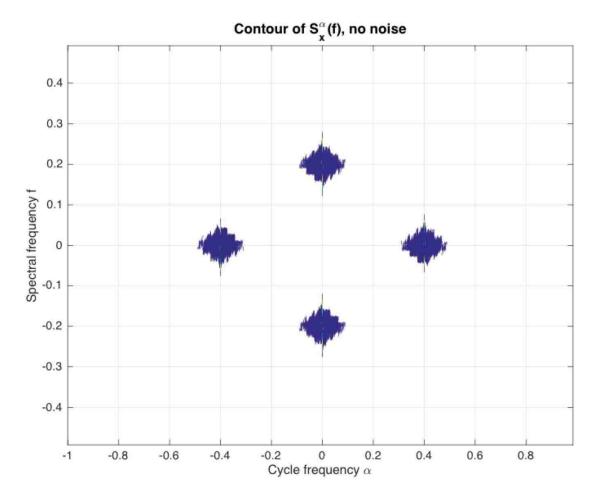

Because the SCF allows visualization of a time-series in the bi-frequency plane (cyclic frequency vs. spectral frequency), the cyclostationary parameters of multiple incident signals can be examined simultaneously. Communications signals exhibit cyclostationarity due to symbol rate, sampling rate, multiplexing, modulation, and coding operations [11]. These cyclostationary effects manifest themselves in the SCF such that many modulation types will present unique signatures in the bi-frequency plane, which can aid in their identification. Additionally, because the SCF is a correlation of the spectral components of the time-series, and white noise is uncorrelated, the SCF is insensitive to the effects of additive white noise for cyclic frequencies other than zero [14]. Figure 2.3 shows an estimated spectral correlation density of the AM signal (9) examined previously in Section 1.3.3 along with the same signal corrupted by various amounts of noise. Note, in the bottom plot, even though the signal is buried in the noise floor, the cyclic peaks are still clearly visible. The contour plot of the estimated spectral correlation density for the no additive noise case is shown in Figure 2.4. Observe using Figure 2.3 and Figure 2.4 that for cyclic frequency  $\alpha = 0$  the SCF matches the PSD shown in Figure 1.4(b) and that cyclic frequency peaks match those shown in Figure 1.4(d).

One of the drawbacks of the SCF is its computational complexity, which is significantly higher than ordinary spectral analysis. It is the large number of correlation factors that must be computed that drives the computational expense [15]. Several methods have been developed to approximate the SCF via averaging in time or frequency, but even these methods require the parallel computation of several FFTs and complex multiplications.

17

Figure 2.3 Estimated spectral correlation density of an AM modulated signal with: (top) no additive noise, (middle) 5dB SNR, (bottom) -5dB SNR.

## 2.4 Spectral Coherence Function

Lastly, the SCF can be normalized to produce a proper coherence value, referred to as the spectral coherence function (abbreviated SOF) with a magnitude in the range [0,1], given as [14]

$$C_{x}^{\alpha}(f) = \frac{S_{x}^{\alpha}(f)}{\left[S_{x}^{0}\left(f + \frac{\alpha}{2}\right)S_{x}^{\alpha}\left(f - \frac{\alpha}{2}\right)^{*}\right]^{1/2}}.$$

(33)

Figure 2.4 Contour of the estimated spectral correlation density of an AM modulated signal.

#### **CHAPTER 3**

#### **OFDM FEATURE DETECTION**

#### 3.1 **OFDM Overview**

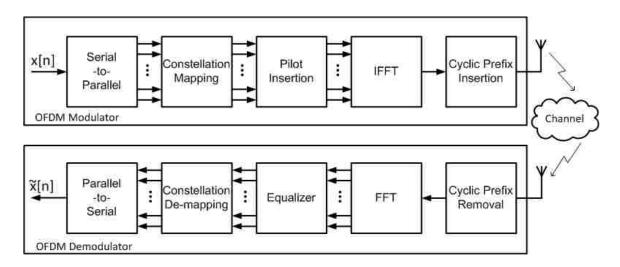

Orthogonal frequency-division multiplexing (OFDM) is a digital modulation scheme that is ideally suited for the transmission of data in multipath fading environments. As data rates continue to increase, the symbol time of single-carrier modulation methods becomes less than the channel impulse response time and which can result in severe intersymbol interference (ISI) from multipath propagation. OFDM instead utilizes multiple carriers to transmit the same aggregate data rate but at a lower per carrier symbol rate, conceptually analogous to parallelizing a data bus to achieve the same bandwidth as a much faster serial bus. The subcarriers are spaced orthogonally in frequency according to the inverse of the data symbol time  $T_{FFT}$

$$\Delta f = \frac{1}{T_{FFT}}.$$

(34)

In this way, OFDM can achieve high-spectral efficiency by maintaining optimal spacing between subcarriers. The subcarriers themselves can be modulated with any suitable quadrature amplitude modulation encoding scheme.

The longer symbol times in OFDM modulation techniques make mitigation of multipath propagation easier by the insertion of a sub-symbol time guard interval. This guard interval is referred to as a cyclic prefix and consists of a portion of the end of the OFDM symbol appended to the front of the symbol, the duration of which is chosen to be longer than the channel impulse response. Typical lengths for the guard interval are <sup>1</sup>/<sub>8</sub> to

<sup>1</sup>/<sub>4</sub> of the symbol time. By copying the end of the symbol to its beginning and assuming the channel impulse response is shorter than or equal to the length of the guard interval, the linear convolution of the transmitted symbol with the channel response can be modeled as a circular convolution. By assuming a flat fading model per subcarrier, receiver equalization is then simplified to a one-tap equalizer for each subcarrier.

The concept of OFDM modulation has been known for some time, but only recently has been exploited on a commercial basis with the advent of low-cost, highperformance digital signal processors and application specific integrated circuits. OFDM modulators and demodulators are efficiently implemented with the use of the Fast Fourier Transform (FFT). In the case of the modulator, the inverse-FFT converts the parallel set of mapped complex baseband data, which are conceptually in the frequency domain and separated by the bin spacing of the IFFT, into a serial stream of time domain data. This transformation of the baseband data from frequency domain to time domain has the effect of modulating the baseband samples by their respective subcarriers. Not all of the subcarriers may necessarily be used for modulating data. Depending on the modulation type, some subcarriers may be assigned a pilot signal to assist the receiver in equalization and other subcarriers may be null. Afterwards the cyclic prefix is appended to the symbol before transmission. Note, due to the optimal spacing of the subcarriers, the bandwidth of the OFDM transmission is related to the number of subcarriers,  $N_{FFT}$  and the subcarrier spacing:

$$BW = N_{FFT} \cdot \Delta f \tag{35}$$

An OFDM demodulator operates in reverse to the modulator. First, the cyclic prefix is removed to obtain a symbol frame corresponding to the expected number of subcarriers, which is then fed to an FFT. The FFT output bins represent the demodulated data of each of the subcarriers. The output bins are equalized, de-mapped, and serialized to provide the output data. Figure 3.1 presents a simplified block diagram of an OFDM modulator and demodulator.

Figure 3.1 Simplified block diagram of an OFDM modulator and demodulator.

#### **3.2 DSRC Modulation**

Dedicated Short Range Communications (DSRC) is properly defined by ASTM Standard E2213-03 and is identified as the 5.9 GHz band allocated for Intelligent Transportation Systems (ITS) communications. The DSRC band consists of seven 10 MHz-wide channels starting at 5.855 GHz, shown in Figure 3.2 (a 5 MHz guard band separates DSRC from the lower adjacent band) [16]. ASTM E2213-03 utilizes IEEE-802.11p amendment (referred to as Wireless Access in Vehicular EnvironmentsWAVE) for the definition of the medium access control (MAC) and physical layer (PHY) aspects of DSRC [17]. Likewise, IEEE amendment 802.11p derives from 802.11a, which is commonly known as the Wireless LAN standard employing OFDM modulation in the 5 GHz band.

The spectral efficiency, high-bandwidth, and resilience to multipath fading make OFDM a well-suited modulation for use in the highly mobile wireless vehicular environment. WAVE defines several enhancements to the MAC and PHY aspects of 802.11a in order to increase its suitability for vehicle-to-vehicle and vehicle-toinfrastructure communications. The PHY modifications entail increasing the OFDM symbol duration by a factor of two. This reduces the subcarrier spacing by half, resulting in an occupied bandwidth of 10 MHz vs. 20 MHz for 802.11a. Table 1 lists the OFDM PHY modulation parameters for 802.11p [**18**].

Figure 3.2 DSRC channel plan (from [18]).

The PHY layer in 802.11p is responsible for the movement of data between the MAC layer and the physical transmission medium. This is done in two sub layers. The first sub layer is the Physical Layer Convergence Protocol (PLCP), which communicates with the MAC by organizing the MAC Packet Data Units (MPDU) into the necessary OFDM frame format known as the PPDU (Protocol Packet Data Unit) [18], [19]. The

second sub layer is the Physical Medium Dependent (PMD). The PMD places the PPDUs on the physical medium (RF in the case of DSRC applications).

| Parameters                       | Notation                    | 802.11p                                        |  |                                  |  |

|----------------------------------|-----------------------------|------------------------------------------------|--|----------------------------------|--|

| Total number of subcarriers      | N <sub>FFT</sub>            | 64                                             |  |                                  |  |

| Total number of used subcarriers | $N_{ST}$                    | 52                                             |  | 52                               |  |

| Data subcarriers                 | N <sub>SD</sub>             | 48                                             |  | 48                               |  |

| Pilot subcarriers                | N <sub>SP</sub>             | 4 (subcarriers $\pm 7, \pm 21$ )               |  | 4 (subcarriers $\pm 7, \pm 21$ ) |  |

| Null subcarriers                 | Null                        | 12 (IFFT bins 0, [27:37])                      |  |                                  |  |

| Subcarrier frequency spacing     | $\Delta f$                  | 0.15625 MHz (1/T <sub>FFT</sub> )              |  |                                  |  |

| Symbol duration                  | T <sub>SYM</sub>            | 8 $\mu$ s (T <sub>GI</sub> +T <sub>FFT</sub> ) |  |                                  |  |

| Guard interval duration          | $T_{GI}$                    | 1.6 $\mu$ s (1/4 T <sub>FFT)</sub>             |  |                                  |  |

| FFT duration                     | $\mathrm{T}_{\mathrm{FFT}}$ | 6.4 µs                                         |  |                                  |  |

| Chip duration                    | T <sub>c</sub>              | 100 ns                                         |  |                                  |  |

| Preamble duration                | $T_{PREM}$                  | 32 $\mu s (10T_{STS} + 2T_{GI} + 2T_{LTS})$    |  |                                  |  |

| Short training symbol duration   | T <sub>STS</sub>            | 1.6 μs                                         |  |                                  |  |

| Long training symbol duration    | $T_{LTS}$                   | 6.4 µs                                         |  |                                  |  |

Table 1 OFDM PHY Modulation Parameters of 802.11p

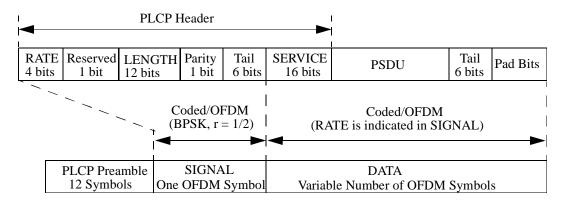

A PPDU frame consists of three main elements. The first element in the frame is the preamble, which also marks the frame's beginning. The preamble is comprised of ten short training sequences (STS) and two long training sequences (LTS) separated by a double length guard interval. The STS consists of 12 subcarriers (subcarriers  $\pm 4$ ,  $\pm 8$ ,  $\pm 12$ ,  $\pm 16$ ,  $\pm 20$ , and  $\pm 24$ ), which are used by the receiver for signal detection, automatic gain control, diversity detection, and coarse frequency offset using the known pattern

$$STS = [1 + j, -1 - j, 1 + j, -1 - j, -1 + j, -1 - j, -1 + j, -1 - j, -1 - j, -1 - j, 1 + j, 1 + j, 1 + j, 1 + j].$$

(36)

The STS symbols have a shorter duration of  $1.6 \,\mu$ s, resulting in total short training sequence duration of  $16 \,\mu$ s. Afterwards, the LTS is transmitted, consisting of two long

training symbols. Each long training symbol consists of all  $\pm 26$  used subcarriers, which allow for channel estimation and fine frequency offset correction using the known pattern

The LTS symbols have a duration of 6.4  $\mu$ s, which when combined with the double length guard interval results in a total long training sequence length of 16  $\mu$ s and a total preamble length of 32  $\mu$ s.

The second field element in a PPDU frame is the signal field (SIG) consisting of a single OFDM symbol. The SIG field consists of header information that details the coding rate, modulation scheme, and packet length of the following data field in the PPDU. The SIG field is always encoded at <sup>1</sup>/<sub>2</sub> rate with BPSK modulation, resulting in 24 bits. The first four bits encode the modulation rate and scheme and are referred to as the RATE subfield. The next bits are a null bit followed by twelve bits referred to as the LENGTH subfield, which describes the number of bytes in the PPDU data field. The remaining bits in the SIG field are parity and null [**18**], [**20**], [**21**].

Figure 3.3 PPDU frame format (from [21]).

The final element in the PPDU frame is the data field. The data field uses a convolutional code for forward error correction at either  $\frac{1}{2}$  or  $\frac{3}{4}$  coding rate [18]. Additionally, the modulation scheme can be either BPSK, QPSK, 16-QAM, or 64-QAM. The coding rate and modulation scheme are chosen by the higher-level protocol according to the error rate of the transmission channel [21]. The parameters and data rates for the various modulation schemes are listed in Table 2. The rate and modulation scheme are hoped in Table 2. The rate and modulation scheme apply to all bytes of the data field in the PPDU frame, which may contain a maximum of 4096 bytes. The four pilot subcarriers ( $\pm 7$  and  $\pm 21$ ) in each OFDM symbol are always encoded as BPSK and are modulated with a pseudo-random binary sequence to prevent the generation of spectral lines [20], [21]. The PPDU frame format is illustrated in Figure 3.3

| Modulation Type | Coding rate | Coded bits per<br>subcarrier | Data bits per<br>symbol (N <sub>DBPS</sub> ) | Data rate (Mbps) |

|-----------------|-------------|------------------------------|----------------------------------------------|------------------|

| BPSK            | 1/2         | 1                            | 24                                           | 3                |

| BPSK            | 3/4         | 1                            | 36                                           | 4.5              |

| QPSK            | 1/2         | 2                            | 48                                           | 6                |

| QPSK            | 3/4         | 2                            | 72                                           | 9                |

| 16-QAM          | 1/2         | 4                            | 96                                           | 12               |

| 16-QAM          | 3/4         | 4                            | 144                                          | 18               |

| 64-QAM          | 1/2         | 6                            | 192                                          | 24               |

| 64-QAM          | 3/4         | 6                            | 216                                          | 27               |

Table 2 Subcarrier Modulation Parameters of 802.11p

#### 3.3 802.11p Simulation Model

In order to test the cyclostationary features of an 802.11p signal, a simulation model that generates the complex baseband modulation was developed. The physical layer of 802.11p is identical to that of 802.11a, but with the timing parameters doubled. Therefore, the MATLAB model developed for 802.11a in [**19**] was modified and reused to produce 802.11p compliant waveforms.

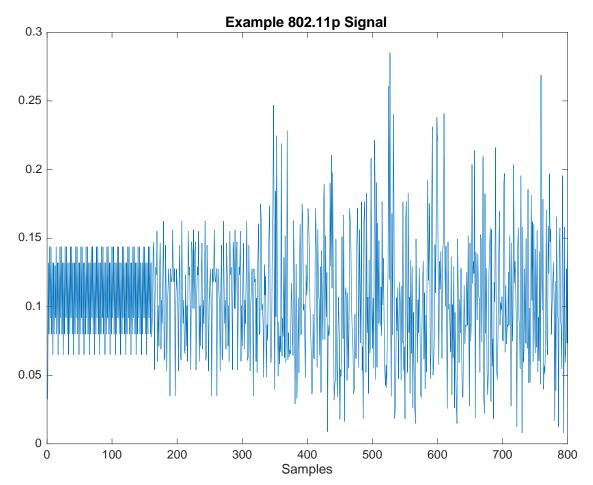

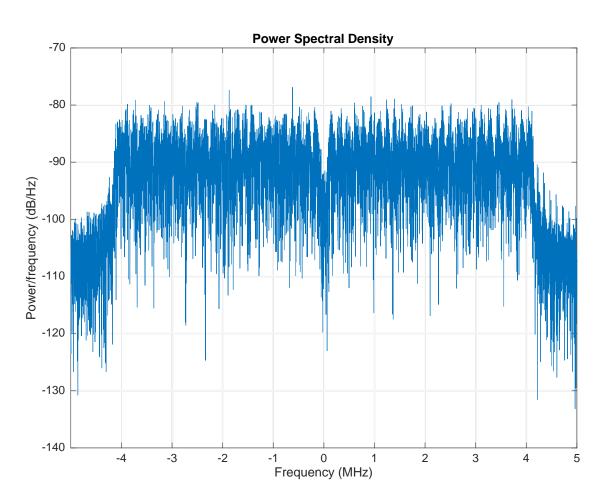

The baseband data is generated with the function WiFi\_BasebandMod.m, which is included in Appendix A. The function is parameterized by Q the number of symbols to generate (variable), m the number of bits per chip (1, 2, 4, or 6), bk the actual binary packet data (a sequence of random integers in the set [0 1] of length  $m^*Q^{*48}$ ), and Frame the number of OFDM symbols per PPDU frame (variable up to the maximum depending on bits per symbol). With the supplied parameters, the baseband simulation model first modulates the data according to the appropriate M-ary QAM object, then the preamble sequence consisting of 10 STS and 2 LTS symbols with guard intervals is created. Afterwards, the SIG symbol is generated, indicating the number of symbols and their encoding rate. The pseudo-random pilot subcarrier vector is created, and along with the data, guard bands, and DC null, the time-domain vector is generated with an inverse FFT. The cyclic prefix is created from the output of the inverse FFT for every symbol and the combined samples are then serialized to provide the baseband signal output. An example time-domain plot of a signal with 10 symbols encoded with m=6 is shown in Figure 3.4. An example power spectral density of a signal with 100 symbols encoded with m=6 is shown in Figure 3.5.

27

Figure 3.4 Time-domain plot an 802.11p PPDU frame of 10 symbols encoded with 64-QAM.

#### 3.4 OFDM Features for Cyclostationary Detection

In Section 1.3 various signal detection methods were reviewed. Cyclostationary signal analysis was revealed to provide several benefits over alternative techniques such as energy detection and matched filtering approaches. Specifically, cyclostationary analysis provides reduced sensitivity to noise and the ability to obtain signal parametric signatures related to modulation type and carrier frequencies. Additionally, cyclostationary techniques do not require frequency or phase synchronization with the

signal of interest, unlike coherent approaches such as matched filtering [22]. The main drawback of cyclostationary techniques that rely upon the calculation of the SCF is the computational expense. The algorithms developed in [15] for the estimation of (30) relate the cyclic frequency resolution to be inversely proportional to the observation time

$$\Delta \alpha = 1/\Delta t. \tag{38}$$

Figure 3.5 Power spectral density of an 802.11p PPDU frame of 100 symbols encoded with 64-QAM.

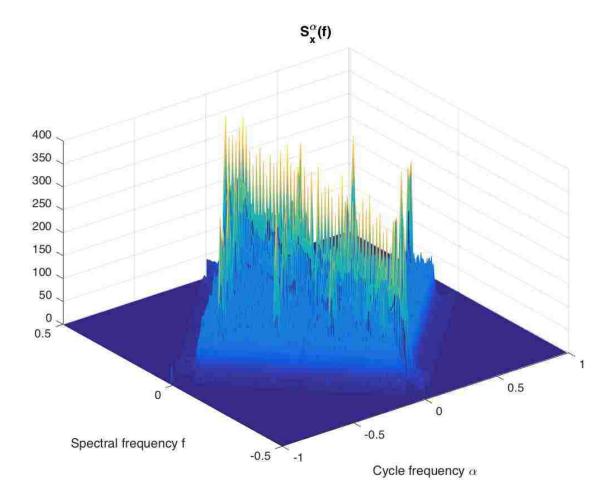

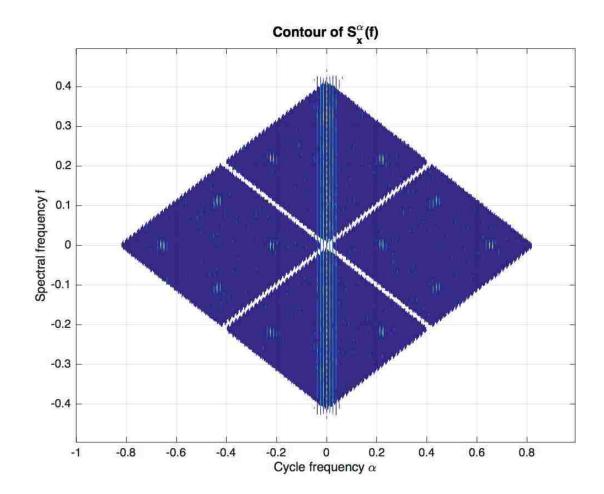

The reliability of the SCF approximations to adequately resolve spectral and cyclic frequency elements of the signal of interest can thus impose a heavy computational burden as well as slow down the detection time by requiring longer observation periods. However, if the signal of interest is known apriori, then the SCF can reveal cyclic signatures that could be utilized in the detection of the signal. Consequently, provided the cyclic signatures are unique, the computation of the SCF may be avoided in favor of the computationally inexpensive calculation of the CAF that corresponds to specific lag values and cyclic frequencies of the related signatures. Therefore, using the model described in the previous section, the SCF is generated for an example 802.11p frame, shown in Figure 3.6. The related contour is shown in Figure 3.7.

### 3.4.1 Preamble

Perhaps the most obvious signal signature of an 802.11p frame that is useful for detection is the PPDU preamble consisting of short and long training sequences. These sequences are located at known subcarriers with known amplitude and phase, as given in (36) and (37). In fact, one of the intended functions of the preamble sequences is identification by a corresponding 802.11p device for clear channel assessment prior to transmission as well as incoming signal detection. However, the main drawback of the preamble sequence is its relatively infrequent occurrence. The preamble sequence occurs only at the beginning of a PPDU frame transmission. The number of symbols,  $N_{SYM}$ , in a PPDU frame is given by [**21**]

$$N_{SYM} = [(16 + 8 \cdot LENGTH + 6) / N_{DBPS}].$$

(39)

Figure 3.6 Estimated spectral correlation density of an 802.11p PPDU frame.

Because the byte length of a PPDU frame may be up to 4095 bytes according to the 12bit LENGTH subfield, the probability of detection of an 802.11p transmitter using only the 12 symbols of the preamble sequence is less than 1% in the worst case scenario where the modulation type is  $\frac{1}{2}$  rate BPSK with a data bits per symbol,  $N_{DBPS}$ , of 24. Such a detection mechanism by a secondary user would be susceptible to assuming an unoccupied channel when in fact a primary user may indeed be transmitting. Extended sensing time prior to transmission would be required in order to mitigate the possibility of interfering with an 802.11p frame in progress. However, this leads to an inefficient reuse of the spectral resource by the secondary user. As a result, this method is not considered as a reliable mechanism for the detection of highly mobile and time critical 802.11p transmissions.

Figure 3.7 Contour of the estimated spectral correlation density of an 802.11p PPDU frame.

### 3.4.2 Pilots

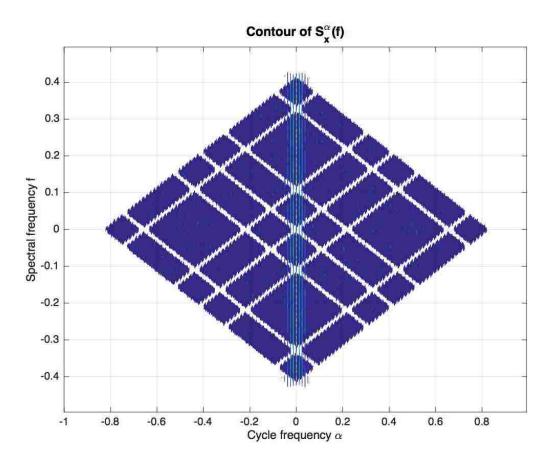

Each OFDM symbol dedicates four subcarriers for use as pilot signals. These signals are utilized by an 802.11p receiver in order to provide robustness against frequency offsets and phase noise [21]. They are received coherently with the rest of the symbol and used by the receiver for frequency correction and equalization. The pilot subcarriers are modulated by a pseudo-random binary sequence to prevent the generation of spectral lines. However, each subcarrier is modulated by the same value in the pseudo-random binary sequence, creating the opportunity for cyclic detection. Moreover, the pseudo-random sequence is only 127 elements long, after which the sequence repeats [21]. For PPDU frames that exceed 127 OFDM symbols, this repetition should also provide a means for cyclic detection. Indeed, careful examination of Figure 3.7 reveals the presence of cyclic features that correspond to the pilot symbols located at subcarriers  $\pm 7, \pm 21$ . These cyclic features can be more clearly revealed by modifying the model to replace the pilot subcarriers with null subcarriers. This exposes the pilot subcarriers in a similar pattern to the null subcarrier located at DC and is shown in Figure 3.8. Between Figure 3.7 and Figure 3.8, it can be observed that spectral lines are produced at the cyclic intersections of the pilot subcarriers, which are given by the coordinates

$$\alpha = \pm (SC_x - SC_y) \cdot \Delta f$$

$$f = \pm (SC_x + SC_y) \cdot \Delta f/2'$$

(40)

where

$$SC_x, SC_y = \{\pm 7, \pm 21 | SC_x \neq SC_y\}.$$

(41)

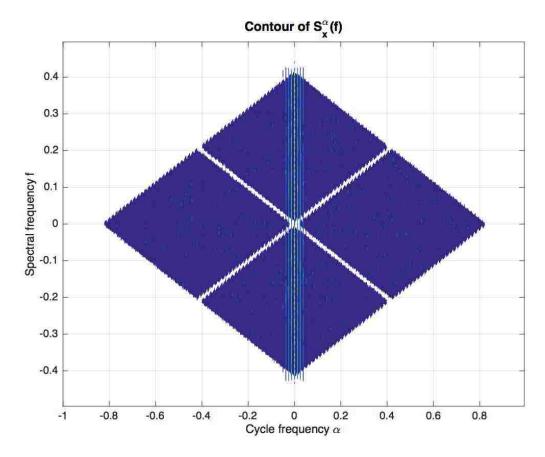

These intersections represent the correlation of the identical pilot subcarriers in a symbol at the various cyclic and spectral frequencies listed in (40), as well as the correlation from the contribution of the pilot subcarriers to the symbol's cyclic prefix. To illustrate this point, the simulation model is modified again to provide random modulation values for each pilot subcarrier, which eliminates their cyclic features in the SCD as shown in Figure 3.9.

Figure 3.8 Contour of the estimated spectral correlation density of an 802.11p PPDU frame modified by replacing the pilot subcarriers with nulls.

Clearly the pilot subcarriers could be utilized as a means of detection of a primary 802.11p signal due to their cyclostationary signature. However, the pilots are spread over a relatively wide bandwidth, which is subject to dispersion. In fact, the pilots are intended to be used by an 802.11p receiver in order to provide channel estimation and frequency equalization. In poor channel conditions the pilots will begin to become uncorrelated, thus weakening their cyclic features. Additionally, the cyclic features produced by the pilots exist at relatively narrow spectral frequencies and occur at multiple cyclic frequencies, which complicates their detection. Therefore, the pilot subcarriers are deemed as a possible, but not desired, element to use for primary signal detection.

Figure 3.9 Contour of the estimated spectral correlation density of an 802.11p PPDU frame modified by randomizing the pilot subcarriers.

# 3.4.3 Cyclic Prefix

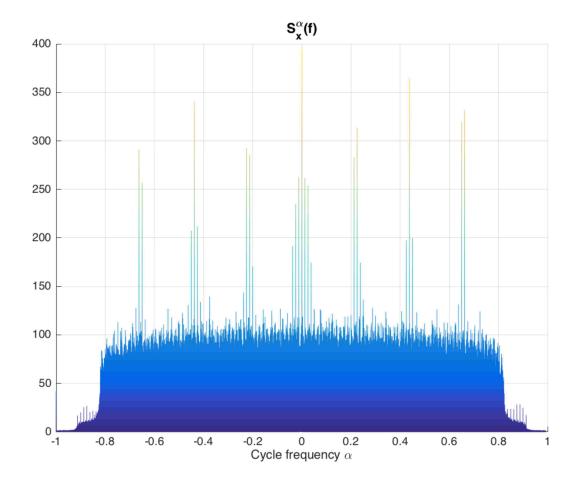

A cyclic prefix is utilized in OFDM systems, including 802.11p, in order to combat the effects of multipath fading. In 802.11p the cyclic prefix consists of the last 16 samples of the time-domain symbol being replicated at the front of the symbol. This predictable repetition should generate spectral lines in a cyclostationary analysis, and in fact they are revealed in the contour shown in Figure 3.7 as the multiple spectral lines close to  $\alpha = 0$ . Figure 3.10 shows the cycle frequency cross-section of Figure 3.6 to more clearly display these spectral lines.

The source of these spectral lines can be determined analytically. Consider that the complex envelop of an OFDM symbol with subcarriers modulated with QAM sequences can be represented by [23]

$$x(t) = \sum_{k} \sum_{n=0}^{N_{FFT}-1} \gamma_{n,l} e^{j2\pi nt/T_{FFT}} q(t - kT_{SYM})$$

(42)

where  $\gamma_{n,l}$  is an independent and identically distributed message sequence representing the symbol QAM data, q(t) is a square shaping pulse with duration  $T_{SYM} = T_{FFT} + T_{GI}$ , and  $N_{FFT}$  is the number of subcarriers. The spectral correlation function of the complex envelope of x(t) is then given as [23]

$$S_x^{\alpha}(f) = \begin{cases} \frac{\delta_{\gamma}^2}{T_{SYM}} \sum_{n=0}^{N_{FFT}-1} Q\left(f - \frac{n}{T_{FFT}} + \frac{\alpha}{2}\right) \cdot Q^*\left(f - \frac{n}{T_{FFT}} - \frac{\alpha}{2}\right), & \alpha = \frac{l}{T_{SYM}} \\ 0, & \alpha \neq \frac{l}{T_{SYM}} \end{cases}$$

(43)

where

$$Q(f) = \frac{\sin(\pi f T_{SYM})}{\pi f}.$$

(44)

It can be seen that the SCF exhibits periodicity with cyclic frequencies at multiples of the symbol rate. In the case of 802.11p,  $T_{SYM} = 80 \cdot T_c$ , and from Figure 3.10 periodicity from the cyclic prefix is easily discernable up to values of l = 3. Additionally, correlation from the cyclic prefix can be observed at the pilot subcarriers, but due to the limited spectral bandwidth of these correlations, periodicity can only be observed for l = 1.

Figure 3.10 Estimated cyclic correlation density of an 802.11p PPDU frame.

# 3.5 Detection of Cyclic Prefix with CAF

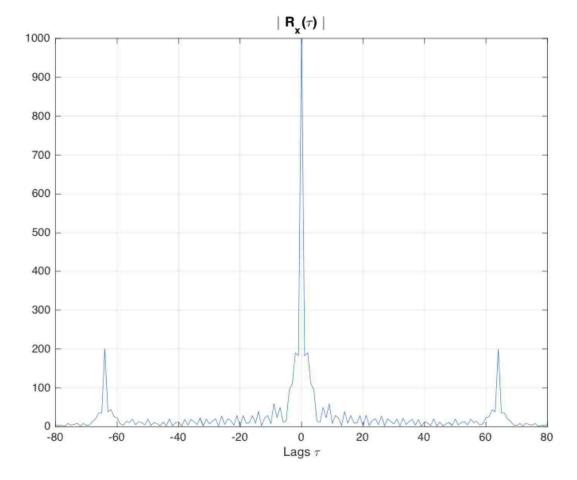

Correlation due to the cyclic prefix provides an excellent means of detection of an 802.11p signal. The cyclostationary signature only exists for an OFDM signal possessing the same number of subcarriers, bandwidth, symbol rate, and cyclic prefix length. Additionally, because the spectral bandwidth of the correlation from the cyclic prefix spans the entire bandwidth of the signal, implementation of a detection mechanism can be easily accomplished with an autocorrelation function. By computing the autocorrelation function with lags equal to  $\pm N_{FFT}$ , the repetition in the OFDM symbol caused by the cyclic prefix can easily be seen as shown in Figure 3.11.

Figure 3.11 Autocorrelation function of an 802.11p PPDU frame.

The cyclic autocorrelation function (CAF) described by (18) can then be applied, assuming a signal at the baseband sampling rate, for fixed lag values  $\tau = \pm N_{FFT}$  at cyclic frequencies corresponding to the total symbol sample length  $\alpha = 1/(N_{FFT} + N_{GI})$ , where  $N_{GI}$  indicates the number of baseband samples in the guard interval. The discrete estimation of the CAF over N samples is given by

$$\hat{R}_{x}^{\alpha}(\tau) = \sum_{n=0}^{N-1} x[n] x^{*}[n+\tau] e^{-j2\pi\alpha n}$$

(45)

which is the sum of the CAF and an error term  $\varepsilon_x^{\alpha}(\tau)$

$$\hat{R}_{x}^{\alpha}(\tau) = R_{x}^{\alpha}(\tau) + \varepsilon_{x}^{\alpha}(\tau).$$

(46)

It is desired to form a test to determine the presence of the primary signal based on the computation of the CAF, therefore a test hypothesis is formulated similar to (3)

$$\begin{aligned} \mathcal{H}_o &: \quad \boldsymbol{r}_x = \boldsymbol{\varepsilon}_x \\ \mathcal{H}_1 &: \quad \boldsymbol{r}_x = \hat{\boldsymbol{r}}_x + \boldsymbol{\varepsilon}_x, \end{aligned} \tag{47}$$

where

$$\hat{\boldsymbol{r}}_{x} = \frac{\left[\operatorname{Re}\left\{\hat{R}_{x}^{\alpha}(\tau_{1})\right\}, \dots, \operatorname{Re}\left\{\hat{R}_{x}^{\alpha}(\tau_{k})\right\},}{\operatorname{Im}\left\{\hat{R}_{x}^{\alpha}(\tau_{1})\right\}, \dots, \operatorname{Im}\left\{\hat{R}_{x}^{\alpha}(\tau_{k})\right\}\right]}$$

(48)

and

$$\boldsymbol{\varepsilon}_{x} = \frac{[\operatorname{Re}\{\varepsilon_{x}^{\alpha}(\tau_{1})\}, \dots, \operatorname{Re}\{\varepsilon_{x}^{\alpha}(\tau_{k})\},}{\operatorname{Im}\{\varepsilon_{x}^{\alpha}(\tau_{1})\}, \dots, \operatorname{Im}\{\varepsilon_{x}^{\alpha}(\tau_{k})\}].}$$

(49)

For the scenario where k = 2, if the samples x[n] that are well separated in time are approximately independent [24], then it can be shown that the error vector has a multivariate normal distribution with zero mean and noise covariance matrix  $\Sigma$ , i.e.

$$\lim_{N \to \infty} \sqrt{N} \boldsymbol{\varepsilon}_{\chi} \sim \mathcal{N}(\mathbf{0}, \boldsymbol{\Sigma}).$$

(50)

The test statistic is then defined as

$$T(\hat{\boldsymbol{r}}_{\boldsymbol{\chi}}) = N \cdot \boldsymbol{r}_{\boldsymbol{\chi}} \boldsymbol{\Sigma}^{-1} \boldsymbol{r}_{\boldsymbol{\chi}}^{\mathsf{T}},\tag{51}$$

which under the null hypothesis is chi-square distributed with 2k degrees of freedom

$$T(\hat{\boldsymbol{r}}_{x})|\mathcal{H}_{o} \sim \chi_{2k}^{2}.$$

(52)

A threshold value can be set in order to provide a constant false alarm rate

$$P_{FA} = Prob\{T(\hat{r}_x) > \lambda | \mathcal{H}_0\}, \tag{53}$$

which the distribution given by (52) allows to be calculated as

$$\lambda = F_{\chi_{2k}^{2}}^{-1} (1 - P_{FA}), \tag{54}$$

where  $F_{\chi^2_{2k}}^{-1}$  is the inverse cumulative distribution function of  $\chi^2_{2k}$  [24].

Similar to the example energy based detector example given in Section 1.3.1, in order to implement a test for cyclostationarity using the CAF the covariance matrix must be estimated from the received signal and its inversion calculated [25]. In Chapter 4, a technique that eliminates the need to estimate and invert the covariance matrix will be introduced.

## **CHAPTER 4**

# **DSRC DETECTION WITH CAF**

## 4.1 Spatial Sign Cyclic Correlation Estimator

The previous chapter reviewed various OFDM signal features for potential use in a cyclostationary detection scheme. The cyclic prefix was found to introduce strong cyclostationary effects making it an ideal candidate for the detection of 802.11p primary users. Moreover, the CAF provides a computationally efficient means by which to calculate the cyclostationary properties of the cyclic prefix. Unfortunately, the detection method requires estimation and inversion of the signal noise covariance matrix. In real applications the noise statistics may not be known completely, in which case an SNR wall develops in the detection scheme as discussed in Section 1.3.1. Additionally, any statistics estimation is subject to frequent change due to the mobile environment in which 802.11p exists. It is therefore desired to develop a detection mechanism that does not require computation of the noise statistics.

One such method proposed in [26] utilizes the spatial sign function (SSF) in order to avoid estimation of the noise probability density function. The SSF for a complex input signal x[n] is given as

$$S(x[n]) = \begin{cases} \frac{x[n]}{|x[n]|} & x[n] \neq 0\\ 0 & x[n] = 0 \end{cases}$$

(55)

The SSF is a nonlinear operation that normalizes the input signal to exist on the unit circle in the complex plane, with the key assumption that the data possesses zero mean.

If the mean is not zero, it should be estimated and removed. The spatial sign cyclic correlation estimator (SSCCE) is then given as

$$\hat{R}_{s}^{\alpha}(\tau) = \frac{1}{N} \sum_{n=0}^{N-1} S(x[n]) S(x^{*}[n+\tau]) e^{-j2\pi\alpha n}, \quad \forall \tau \neq 0$$

(56)

In [**26**] it is shown that the nonlinearity of the SSF does not affect the periodicity of the autocorrelation function for circularly symmetric complex Gaussian processes (an accurate model for OFDM systems).

As before, a test statistic is defined to reject the null hypothesis that the received signal does not contain the primary signals. In order to compute the test statistic, it is first necessary to determine the distribution of the SSCCE for an i.i.d. circular noise process with zero mean, w[n]. The mean of the SSCCE for w[n] is thus [26]

$$E[\hat{R}_{S}^{\alpha}(\tau)] = \frac{1}{N} \sum_{n=0}^{N-1} E[S(w[n])S(w^{*}[n+\tau])]e^{-j2\pi\alpha n}$$

$$= \frac{1}{N} \sum_{n=0}^{N-1} E[S(w[n])]E[S(w^{*}[n+\tau])]e^{-j2\pi\alpha n} = 0, \quad \forall \alpha$$

(57)

The covariance of the SSCCE for w[n] is given by

$$\begin{split} \boldsymbol{\Sigma}_{\hat{R}_{s}^{\alpha}(\tau)} &= \mathrm{E}\big[\hat{R}_{s}^{\alpha}(\tau)\hat{R}_{s}^{\alpha^{*}}(\tau)\big] \\ &= \mathrm{E}\Big[\bigg(\frac{1}{N}\sum_{n=0}^{N-1}S(w[n])S(w^{*}[n+\tau])e^{-j2\pi\alpha n}\bigg) \cdot \\ & \left(\frac{1}{N}\sum_{n=0}^{N-1}S(w[n])S(w^{*}[n+\tau])e^{-j2\pi\alpha n}\bigg)^{*}\bigg] \\ &= \frac{1}{N^{2}}\sum_{n=0}^{N-1}\mathrm{E}[|S(w[n])|^{2}|S(w[n+\tau])|^{2}] \,. \end{split}$$

(58)

The normalization property of the SSF ensures that

$$E[|S(w[n])|^2|S(w[n+\tau])|^2] = 1$$

(59)

Therefore the covariance of the noise process after normalization from the SSF is

$$\Sigma_{\hat{R}_{\mathcal{S}}^{\alpha}(\tau)} = \frac{1}{N} \mathbf{I}.$$

(60)

A test hypothesis is again formulated

$$\begin{aligned} \mathcal{H}_{o} &: \quad x[n] = w[n] \\ \mathcal{H}_{1} &: \quad x[n] = s[n] + w[n], \end{aligned} \tag{61}$$

where s[n] is the primary signal of interest. A vector of the calculated SSCCE functions for various lag values is given as

$$\hat{\boldsymbol{r}}_{s} = \left[\hat{R}_{s}^{\alpha}(\tau_{1}), \dots, \hat{R}_{s}^{\alpha}(\tau_{k})\right].$$

(62)

From ( 60 ) it follows that  $\hat{\boldsymbol{r}}_s$  is complex normal distributed

$$\lim_{N \to \infty} \hat{\boldsymbol{r}}_{s} | \mathcal{H}_{o} \sim \mathcal{CN}\left(\boldsymbol{0}, \frac{1}{N}\mathbf{I}\right).$$

(63)

Then the test statistic can be given as [26]

$$T(\hat{\boldsymbol{r}}_s) = N \cdot \|\hat{\boldsymbol{r}}_s\|^2, \tag{64}$$

which under the null hypothesis is chi-square distributed with k complex degrees of freedom

$$T(\hat{\boldsymbol{r}}_s) | \mathcal{H}_o \sim \chi_k^2. \tag{65}$$

The threshold is then calculated according to the desired false alarm rate

$$\lambda = F_{\gamma}^{-1} (1 - P_{FA}), \tag{66}$$

where  $F_{\gamma}^{-1}$  is the inverse gamma cumulative distribution function with scale factor of one and shape factor *k* [25].

## 4.2 Dual-Lag SSCCE with Cyclic Phase Compensation

As discussed in Section 3.4.3, the cyclic prefix induces strong cyclostationary features that can be detected with the CAF. As illustrated in Figure 3.11, correlation occurs at lags  $\pm N_{FFT}$ , which is 64 in the case of 802.11p and clearly visible in Figure 3.10 for cyclic frequencies  $\alpha = l/(N_{FFT} + N_{GI})$ ,  $l = 0, \pm 1, \pm 2, \pm 3$ . The detection scheme proposed is to calculate the SSCCE at dual lags  $\tau = \pm 64$  and  $\alpha = 1/80$ . The test statistic from ( 64 ) is then

$$T(\hat{\boldsymbol{r}}_{s}) = N \cdot \left| \hat{R}_{s}^{\alpha}(\tau_{1}) \right|^{2} + N \cdot \left| \hat{R}_{s}^{\alpha}(\tau_{2}) \right|^{2}.$$

(67)

In [27] it is shown that for a dual-lag (k = 2) with cyclic frequency  $\alpha = 1/(N_{FFT} + N_{GI})$ , a cyclic phase compensation can be introduced in order to align the

SSCCE values of the two lags in time. The two SSCCE computations are complex valued and have an instantaneous phase difference

$$\emptyset = \arg(\hat{R}_s^{\alpha}(\tau_1)) + \arg(\hat{R}_s^{\alpha}(\tau_2)).$$

(68)

For an 802.11p primary signal that exhibits correlation at the lag values from the cyclic prefix, the phase difference  $\emptyset$  is a constant value based on  $\tau$  and  $\alpha$  [27]

$$\emptyset = 2\pi\tau_1 \alpha. \tag{69}$$

The constant phase difference correction is applied to the second SSCCE calculation

$$\hat{R}_{s}^{\alpha^{\emptyset}}(\tau_{2}) = \frac{1}{N} \sum_{n=0}^{N-1} S(x[n]) S(x^{*}[n+\tau_{2}]) e^{-j2\pi\alpha n + \emptyset}.$$

(70)

Because the two SSCCEs are now coherent the test statistic can be summed simply as

$$T(\hat{\boldsymbol{r}}_{s}^{c}) = \frac{N}{2} \cdot \left| \hat{R}_{s}^{\alpha}(\tau_{1}) + \hat{R}_{s}^{\alpha^{\emptyset}}(\tau_{2}) \right|^{2}, \qquad (71)$$

which lowers the degrees of freedom to k = 1 as well as reduces the implementation complexity. The threshold value is computed the same as (66) but with scale and shape factors of one.

### 4.3 MATLAB Simulation

The previous section detailed a cyclostationary detection method based on the CAF that avoids the necessity of estimating the noise covariance by normalizing the

signal via the SSF. In order to test the performance and suitability of this method for hardware implementation, a MATLAB simulation was developed. The 802.11p baseband simulation model described in Section 3.3 was used to generate various size PPDU frames. The baseband data was subjected to several impairments to simulate real world channel effects. First, multipath fading was simulated via a Rayleigh model with Doppler shift corresponding to a mobile unit velocity of 130kph. Additionally, the baseband data was shifted 30kHz in order to model a local oscillator offset of 5ppm, which is representative of the maximum typical offset error [28]. Finally, measured additive white Gaussian noise was added to the baseband signal to further simulate the channel. The SSCCE algorithm with cyclic phase compensation, (70), was coded as a MATLAB function, sscce\_pc.m, and is included in Appendix A. The function is parameterized by x the baseband input signal, *alpha* the cyclic frequency, *phi* the cyclic phase compensation (vector valued), and *lag* the desired lags for the autocorrelation (also vector valued). The signal test statistic is calculated from the SSCCE function for  $\tau = \pm 64$  and  $\alpha = 1/80$ , which is returned along with the calculated SSCCE values. The threshold value is set according to (66) for a standard false alarm probability of 5%.

#### 4.3.1 Probability of Detection vs. SNR

Because the detection scheme operates by correlating *N* samples, the probability of detection will increase with larger input signal length. However, to simulate realistic scenarios, typical message lengths should be used. The DSRC describes over 150 data elements that can be included in a DSRC message [**29**]. The data elements describe such information as vehicle acceleration, speed, heading, anti-lock brake status, wiper status,

46

etc. From these elements, eight high-priority safety messages have been defined. Since these messages are the ones for which detection is paramount, the simulated 802.11p frame should be representative of a typical safety message length. After encoding and protocol encapsulation of the per message data elements, a high-priority safety message may be comprised of approximately 856 to 1408 bits at the PHY PSDU [**29**]. Depending on the subcarrier modulation scheme, according to (39) the corresponding number of symbols for the smallest safety message encoded at the highest data rate of 27 Mbps is 33 symbols, which represents the worst case signal detection scenario.

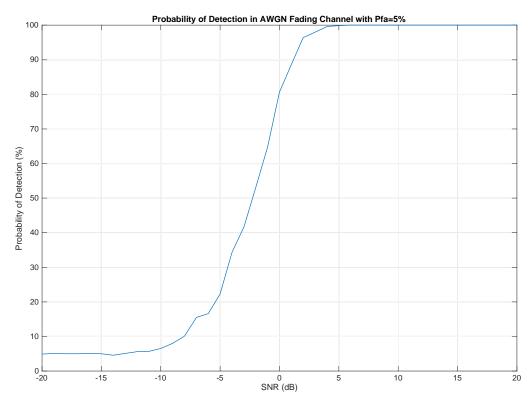

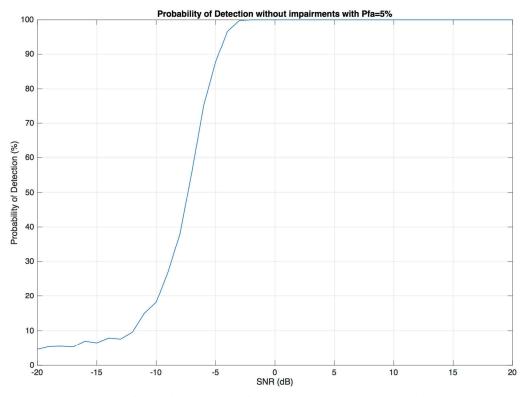

Simulations were performed in order to test reliability and performance of the SSCCE detector in varied noise environments. A baseband 802.11p signal 33 symbols in length was generated with the impairments described in the previous section along with measured amounts of AWGN. The SSCCE output test statistic was compared against the threshold value computed for 5% false alarm rate and plotted versus signal SNR, as shown in Figure 4.1. The test was run with a sample size of 1000. As expected, the detection rate trends towards 5% as the noise level increases. Also, observe that despite the relatively few samples used for the correlation (2640 baseband samples), the probability of detection is effectively 100% for any SNR greater than 5dB. The same simulation repeated but without multipath fading or LO offset impairments is shown in Figure 4.2, which indicates approximately 5dB improvement over the previous scenario.

Figure 4.1 Probability of detection vs. SNR of an 802.11p signal corrupted by an AWGN fading channel using SSCCE method with sample size of 1000.

Figure 4.2 Probability of detection vs. SNR of an 802.11p signal without additional impairments using SSCCE method with sample size of 1000.

# 4.3.2 ROC at Fixed SNR

The receiver operating characteristic curve was evaluated using the same signal length as the previous section and without fading or LO impairments. The specificity vs. sensitivity is shown in Figure 4.3 when the signal is corrupted by AWGN such that the SNR is -5dB.

Figure 4.3 Receiver operating characteristic curve of the SSCCE method for an 802.11p signal.

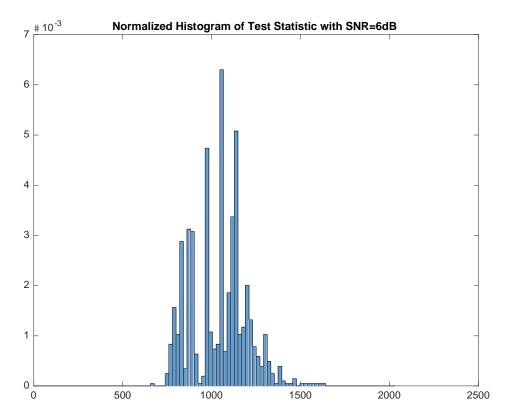

# 4.3.3 Histogram at Fixed SNR

Finally, the histogram of the test statistic at SNR of -5dB is shown in Figure 4.4 for a sample size of 1000, indicating the test statistic is well modeled by the chi-squared probability density function.

Figure 4.4 Histogram of SSCCE test statistic for an 802.11p signal with -5dB SNR.

## **CHAPTER 5**

# **FPGA IMPLEMENTATION**

## 5.1 FPGA Overview

As discussed in Section 1.2, spectrum sharing in the DSRC band has several unique challenges. First, the detection methodology must be robust. Several detection schemes have been discussed in the previous chapters. Of those discussed, a cyclostationary method for the detection of the OFDM symbol's cyclic prefix appears to be the most promising for robustness against noise and probability of detection. Secondly, the detection method must provide rapid discovery of primary users. The SSCCE approach reviewed in Chapter 4 was shown to provide detection of 802.11p signals within a fixed number of baseband samples corresponding to a shortest case DSRC safety message. Furthermore, the SSCCE method is not computationally taxing, which addresses the final constraints for a DSRC spectrum-sharing device, namely that it be power and resource efficient. It is expected that a detection engine for 802.11p signals would be implemented in a radio chipset to achieve real-time and power efficient operation. This chapter will review a field programmable gate array (FPGA) implementation of the SSCCE algorithm discussed in Chapter 4.