#### University of New Mexico UNM Digital Repository

**Electrical and Computer Engineering ETDs**

**Engineering ETDs**

7-1-2016

# Avalanche ISFET Sensing Chip for DNA Sequencing

Mohammad Uzzal

Follow this and additional works at: https://digitalrepository.unm.edu/ece\_etds Part of the <u>Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

Uzzal, Mohammad. "Avalanche ISFET Sensing Chip for DNA Sequencing." (2016). https://digitalrepository.unm.edu/ece\_etds/263

This Dissertation is brought to you for free and open access by the Engineering ETDs at UNM Digital Repository. It has been accepted for inclusion in Electrical and Computer Engineering ETDs by an authorized administrator of UNM Digital Repository. For more information, please contact disc@unm.edu.

Mohammad Mohiuddin Uzzal Candidate

Electrical and Computer Engineering *Department*

This dissertation is approved, and it is acceptable in quality and form for publication:

Approved by the Dissertation Committee:

Dr. Payman Zarkesh-Ha , Chairperson

Dr. Vince Calhoun

Dr. Jeremy S. Edwards

Dr. Ashwani K. Sharma

Dr. Paul Szauter

# Avalanche ISFET Sensing Chip for DNA Sequencing

By

#### Mohammad Mohiuddin Uzzal

B.Sc. in EEE, Bangladesh Uni. of Engg. and Tech. (BUET), Bangladesh, 2002

M.S.E in EE, Arizona State University (ASU), AZ, USA, 2006

M.B.A in Finance/Management, IBA, University of Dhaka, Bangladesh, 2008

DISSERTATION

Submitted in Partial Fulfillment of the Requirements for the Degree of

> Doctor of Philosophy Engineering

The University of New Mexico Albuquerque, New Mexico

#### **July 2016**

@2016, Mohammad Mohiuddin Uzzal

### **DEDICATION**

To my family and friends

### ACKNOWLEDGMENT

My graduate student life in University of New Mexico was one of the most exciting, joyful and rewarding experience in my life. Hereby, I would like to show my best gratitude and appreciation to the people who helped me to have this great time and make a lasting impression in my life.

First, I want to thank my advisor Dr. Payman Zarkesh-Ha for his continuous advice, suggestions and support throughout this amazing journey of knowledge. It was a great exciting and pleasant opportunity to be a member of his group, to learn from him and to do research on very interesting topics. Dr. Payman provided me with every bit of guidance, assistance, and expertise that I needed during this journey. I quite simply cannot imagine a better adviser.

I would like to thank the theory faculty at the University of New Mexico, specially Dr. Payman Zarkesh-Ha, Dr. Luke Lester, Dr. Ashwani Kumar Sharma, Dr. Christos Christodoulou, and Dr. Ralph Dawson for the substantial influence that their courses have on my research. I would also like to thank my committee members for their time and valuable input, discussions and accessibility.

I am deeply thankful to my family, my parents, my brother, and my sister for their love, support, and sacrifices. They were always on my side in my good and bad times. Their encouragement is always my greatest motivation on study.

In the end, I would like to thank my friends in the Electrical and Computer Engineering department at UNM for all the great times that we have shared. I would also like to thank to my group mates. Their abundant knowledge and experience always helped me when I met any difficulty in my study and research. I owe them so much.

# Avalanche ISFET Sensing Chip for DNA Sequencing

By

Mohammad Mohiuddin Uzzal

B.Sc. in EEE, Bangladesh Uni. of Engg. and Tech. (BUET), Bangladesh, 2002

M.S.E in EE, Arizona State University (ASU), AZ, USA, 2006

M.B.A in Finance/Management, IBA, University of Dhaka, Bangladesh, 2008

Ph.D., Engineering, University of New Mexico, New Mexico, USA, 2016

#### ABSTRACT

DNA sequencing is a fundamental tool for biological science, aimed primarily at uncovering the genetic contributions to diseases. The first Human DNA sequence, which employed conventional fluorescent-based Sanger Sequencing method, took many years to complete at a cost of over three billion dollars. In one survey, it shows that Human Genome Project (HGP) had generated more than \$67 billion in U.S. economic output, \$20 billion in personal income for Americans and 310 thousand jobs in USA, only during year 2010. The HGP has increased the need for highthroughput, low cost, fast, accurate and inexpensive DNA sequence technique. This demand has forced a fundamental shift away from the conventional Sanger sequencing technique to Next Generation Sequencing (NGS) technique for genome analysis. NGS techniques provide high-throughput; low cost, user-friendly DNA sequencing and they are opening fascinating new opportunities in biomedicine. In near future, as the price of complete DNA sequencing goes further down to a few hundred dollars, we will then have DNA sequence data of millions of people. The enormous DNA sequencing data and corresponding correlation will allow us to figure out which sequences are responsible for which traits. As we relate the sequences of all of these people to their traits, we will be able to connect the dots and learn the genetic equations that define health, longevity, and behavior.

In this dissertation, we propose a new avalanche ion-sensitive field effect transistor (A-ISFET) capable of sensing very weak pH changes during DNA synthesis. This is the first attempt to operate ISFET in avalanche mode. A-ISFET is the core of our proposed highly dense, low-cost and high-throughput DNA sequencing technique. To validate our proposed concept, we have designed, laid-out, fabricated, and successfully tested a test chip with arrays of A-ISFET using TSMC 0.25um CMOS process. Our research also includes the development of data processing circuits and system architectures for fast and efficient data processing. The test chip is used as the verification of this new DNA sequencing concept and the validation of the interfacial circuitry for the synchronization of sensing system. Each of the unit cells in the test chip is accessed through column-select and row-select signals during readout process. We design a test environment and test setup for correct readout of the sensing data from the chip through proper synchronizing signal. A specially milled and shaped structure is used to inlet and outlet the bio-chemical on the gate surface of the A-ISFET arrays. The inlet and outlet is attached to a timecontrolled valve to control the flow of liquids on the surface of A-ISFET chip for test and verification of this novel DNA sensing concept. The test chip has been tested both at normal mode and at avalanche mode. Test results show that the sensitivity at avalanche mode is 6 times more than the normal mode of operation.

We have developed a model to determine the signal-to-noise ratio (SNR) of A-ISFET. The model identifies that there is an optimum bias point of A-ISFET to have maximum SNR sensitivity from the sensor. Every electronic device generates its own intrinsic noise, in addition to other induced noise from associated nearby components. We have identified different noise components of A-ISFET and have modeled their respective characteristics with bias change. Different noise components that we find in A-ISFET are thermal noise, flicker noise, shot noise, and dark current noise. This noise modeling of A-ISFET sensor will help us to understand noise sources better and to predict the sensor behavior with change of bias. Using the noise model, we can select a bias point to minimize the noise impact of A-ISFET sensor and maximize its SNR. We also have developed a physical operation-based drain current model for A-ISFET during avalanche operation. Since A-ISFET operates in avalanche region, an accurate model for the breakdown behavior is therefore very important from both circuit design and circuit reliability point of view. The avalanche breakdown can result from impact ionization, a parasitic bipolar transistor, or the punch-through effect. Our developed model of A-ISFET drain current at avalanche region is due to impact ionization. We have validated the drain current model at avalanche through a correlation study among analytical model results, SPICE simulation results, and experimental measured results.

### **TABLE OF CONTENTS**

| ABSTRA    | CT                                                        | vi   |

|-----------|-----------------------------------------------------------|------|

| TABLE O   | F CONTENTS                                                | ix   |

| LIST OF H | FIGURES                                                   | xiii |

| LIST OF T | TABLES                                                    | xvii |

|           |                                                           |      |

| СНАРТЕ    | R 1: INTRODUCTION                                         | 1    |

| 1.1       | Background                                                | 1    |

|           | 1.1.1 Human Genome Project : Importance of DNA sequencing | 2    |

|           | 1.1.2 DNA sequencing and ISFET                            | 4    |

| 1.2       | Dissertation contents                                     | 6    |

| 1.3       | Innovative aspects and Unique Contributions               | 9    |

| 1.4       | Organization of the Dissertation                          | 9    |

| 1.5       | Discussions                                               | 10   |

|           |                                                           |      |

| СНАРТЕ    | R 2: THEORY ON ISFET AND SENSITIVITY                      | 11   |

| 2.1       | Introduction to Sensor                                    | 11   |

|           | 2.1.1 Bio-Sensor: Chemical Sensors and their features     | 13   |

|           | 2.1.2 Amperometric Chemical Sensor                        | 14   |

| 2.2       | Ion Sensitive Field Effect Transistor (ISFET)             | 15   |

|           | 2.2.1 Fundamentals of semiconductor                       | 16   |

|           | 2.2.2 MOSFET structure and Field Effect                   | 17   |

|           | 2.2.3 MOSFET to ISFET                                     | 19   |

|           | 2.2.4 Sensing approaches of ISFET                         | 21   |

|           | 2.2.5 CMOS compatibility of ISFET                         | 22   |

|           | 2.2.6 ESD Protection of ISFET                             | 23   |

|           | 2.2.7 Non-idealities of ISFET                             | 24   |

| 2.3       | Avalanche ISFET (A-ISFET)                                 | 25   |

|           | 2.3.1 Structure and Bias of A-ISFET                       | 26   |

|        | 2.3.2 Physics of Avalanche operation         | 26 |

|--------|----------------------------------------------|----|

|        | 2.3.3 Failure of A-ISFET                     | 27 |

| 2.4    | ISFET sensor: Sensitivity                    | 28 |

|        | 2.4.1 Normal Operation Mode                  | 29 |

|        | 2.4.2 Sensitivity of ISFET at Avalanche Mode | 33 |

| 2.5    | Discussions                                  | 35 |

| CHAPTI | ER 3: NOISE ANALYSIS OF A-ISFET              | 36 |

| 3.1    | Introduction to Noise                        | 36 |

| 3.2    | Noise in ISFET                               | 37 |

|        | 3.2.1 Thermal Noise                          | 38 |

|        | 3.2.2 Flicker Noise                          | 40 |

|        | 3.2.3 Shot Noise                             | 41 |

|        | 3.2.4 Dark Current Noise                     | 42 |

|        | 3.2.5 Avalanche Noise                        | 42 |

| 3.3    | Signal-to-Noise ratio (SNR) of A-ISFET       | 43 |

|        | 3.3.1 Multiplication Factor, M               | 43 |

|        | 3.3.2 Excess Noise Factor, F                 | 43 |

|        | 3.3.3 Model Formulation for SNR of A-ISFET   | 46 |

| 3.4    | Simulation Results                           | 50 |

| 3.5    | Design Suggestion to Reduce Noise: A-ISFET   | 52 |

| 3.6    | Discussions                                  | 52 |

| CHAPTI | ER 4: DRAIN CURRENT MODEL OF A-ISFET         | 53 |

| 4.1    | Introduction                                 | 53 |

| 4.2    | Model Formation Process                      | 53 |

|        | 4.2.1 Mobility Degradation Effects           | 54 |

|        | 4.2.2 Avalanche Breakdown Mechanism          | 56 |

| 4.3    | Simulation Results                           | 60 |

| 4.4    | Verification and Correlation                 | 62 |

|     | R 5: AN OVERVIEW ON TEST CHIP                          |

|-----|--------------------------------------------------------|

| 5.1 | Introduction                                           |

| 5.2 | Literature Review                                      |

|     | 5.2.1 ISFET Sensor                                     |

|     | 5.2.2 DNA sequencing                                   |

| 5.3 | Design Overview of Test Chip                           |

|     | 5.3.1 Unit Cell                                        |

|     | 5.3.2 Peripheral Circuit: Column Select and Row Select |

|     | 5.3.3 Chip Architecture                                |

|     | 5.3.4 Layout of the Chip                               |

|     | 5.3.5 EDA tools                                        |

|     | 5.3.6 ESD Protection                                   |

|     | 5.3.7 PAD                                              |

|     | 5.3.8 Well Creation                                    |

| 5.4 | Design Consideration for Full Scale Genome Sequencing  |

| 5.5 | Discussions                                            |

| PTE | R 6: TEST SETUP AND EXPERIMENTAL RESULT                |

| 6.1 | Introduction                                           |

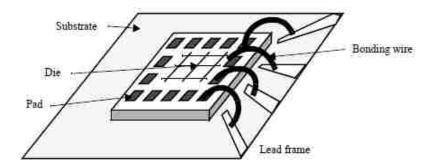

|     | 6.1.1 Wire-bonding                                     |

| 6.2 | Readout mechanism and Synchronization Process          |

| 6.3 | Noise Cancellation Principles                          |

| 6.4 | Test Setup and Hardware                                |

| 6.5 | Experimental results                                   |

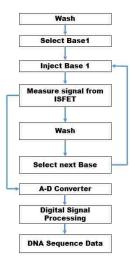

| 6.6 | Proposed DNA Sequencing Procedure                      |

|     |                                                        |

| <b>CHAPTER 7:</b> | CONCLUSIONS |  | 93 |

|-------------------|-------------|--|----|

|-------------------|-------------|--|----|

| REFERENCES | •                                       | 95  |

|------------|-----------------------------------------|-----|

| APPENDIX A | MATLAB: NOISE MODEL FOR SNR SENSITIVITY |     |

|            | OF A-ISFET                              | 103 |

| APPENDIX B | DRAIN CURRENT MODEL OF A-ISFET AT       |     |

|            | AVALANCHE                               | 106 |

### **LIST OF FIGURES**

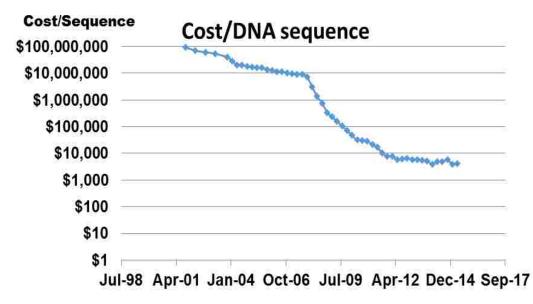

| Figure 1.1:  | DNA sequencing cost per person: NHGRI [7]                    | 2  |

|--------------|--------------------------------------------------------------|----|

| Figure 1.2:  | Functional impacts associated with DNA sequencing [4]        | 3  |

| Figure 1.3:  | Typical ISFET sensor and its output signal                   | 5  |

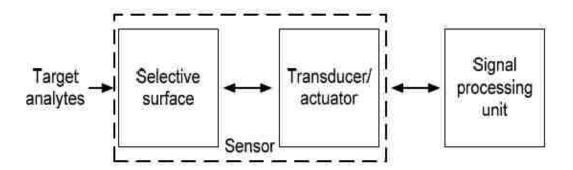

| Figure 2.1:  | Typical elements of Electric Bio-sensor [21]                 | 12 |

| Figure 2.2:  | General features of a chemical sensor [20, 24]               | 13 |

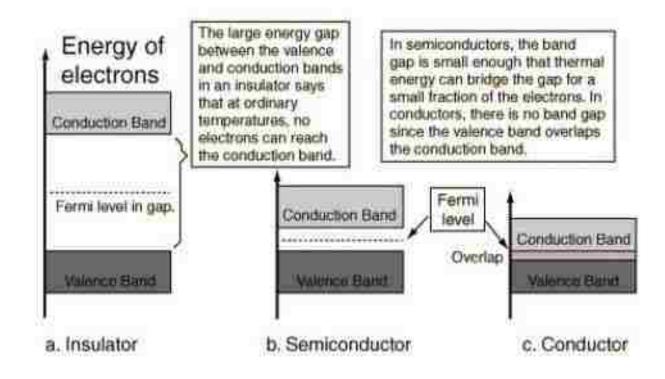

| Figure 2.3:  | Energy band diagram of materials [31]                        | 15 |

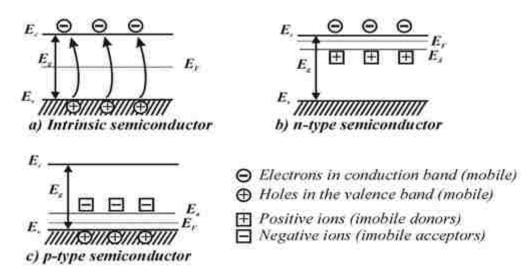

| Figure 2.4:  | Three types of semiconductors: a) intrinsic semiconductors   |    |

|              | B) n-type semiconductors c) p-type semiconductors [31]       | 16 |

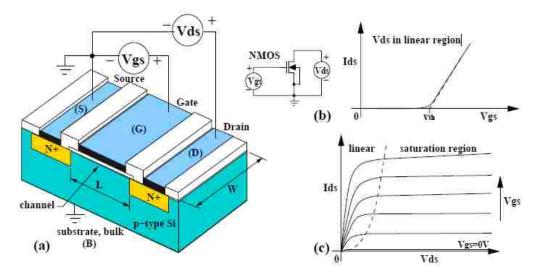

| Figure 2.5:  | NMOS transistor and its operation with characteristics curve |    |

|              | [32]                                                         | 18 |

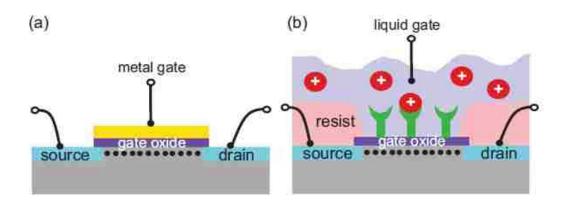

| Figure 2.6:  | Structure of MOSFET and ISFET: compare and contrast [33]     | 19 |

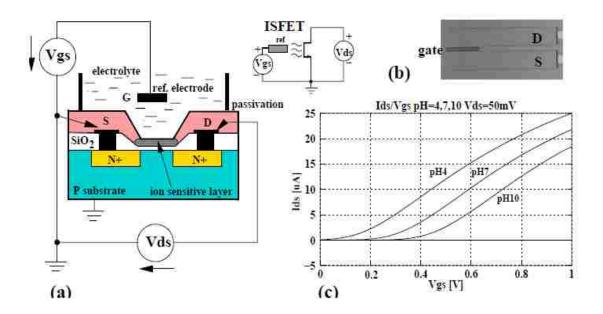

| Figure 2.7:  | ISFET operation with transfer curve [32]                     | 20 |

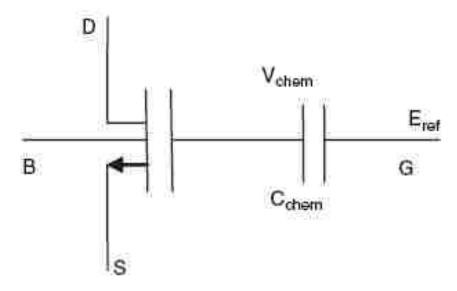

| Figure 2.8:  | ISFET model with respect to MOSFET [35]                      | 21 |

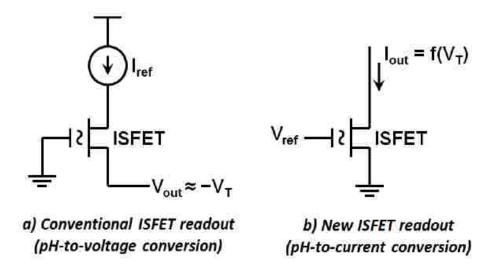

| Figure 2.9:  | Sensing and readout principles of ISFET [18]                 | 22 |

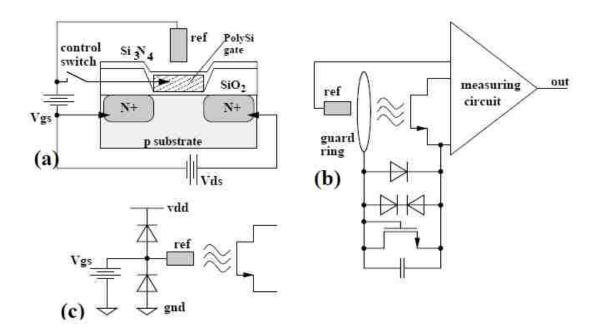

| Figure 2.10: | ESD protections of ISFET (a) Poly Si gate switching (b)      |    |

|              | Guard ring around ISFET gate with diode (c) Diode            |    |

|              | protection of reference                                      | 24 |

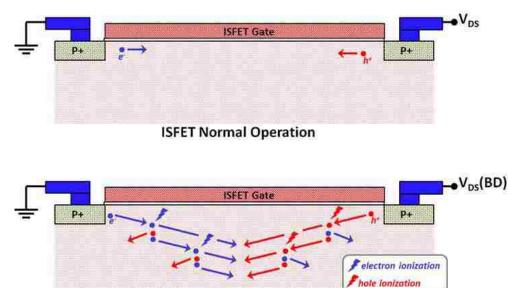

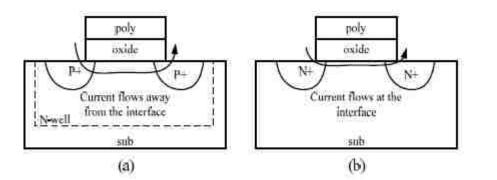

| Figure 2.11: | (a) An ISFET under nominal voltage (b) An ISFET under        |    |

|              | avalanche breakdown showing impact ionization. [18]          | 26 |

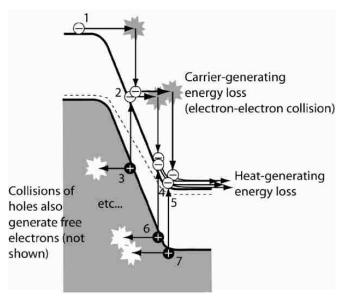

| Figure 2.12: | Avalanche multiplication process in semiconductor [47]       | 27 |

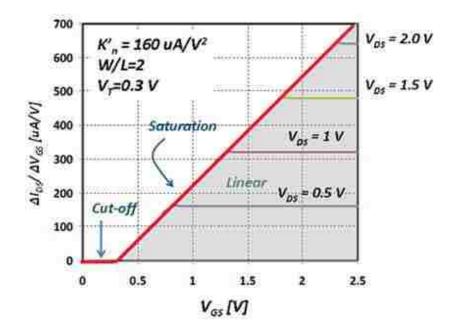

| Figure 2.13: | Voltage-to-current sensitivity of an ideal ISFET [13]        | 29 |

| Figure 2.14: | pH-to-current sensitivity of an ideal ISFET [13]             | 30 |

| Figure 2.15: | Sensitivity of a short channel ISFET with W/L=2 [13]         | 31 |

| Figure 2.16: | Sensitivity of a long channel ISFET with W/L=2 [13]          | 32 |

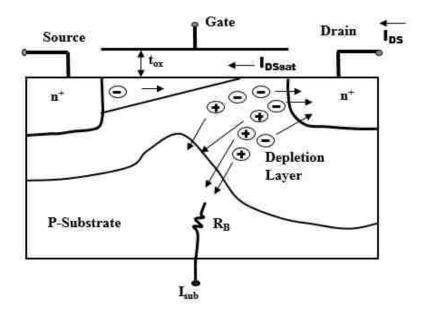

| Figure 2.17: | Current flow in n-channel MOSFET at avalanche [48]           | 33 |

| Figure 2.18: | SPICE simulation showing (~10 times) higher sensitivity      |    |

|              | from ISFET device [18]                                       | 34 |

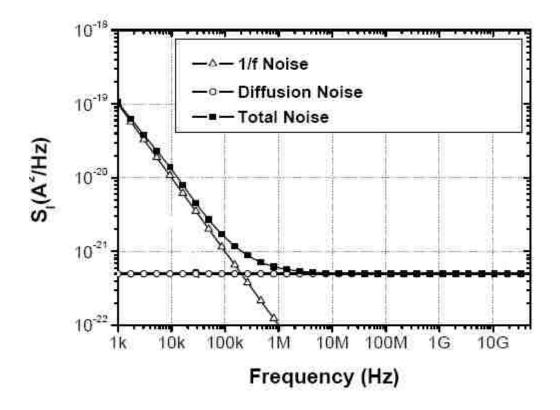

| Figure 3.1:  | Different noise sources and their effect on signal [51]      | 36 |

| Figure 3.2:  | Noise spectrum of MOSFET/ISFET [51]                          | 38 |

|              |                                                              |    |

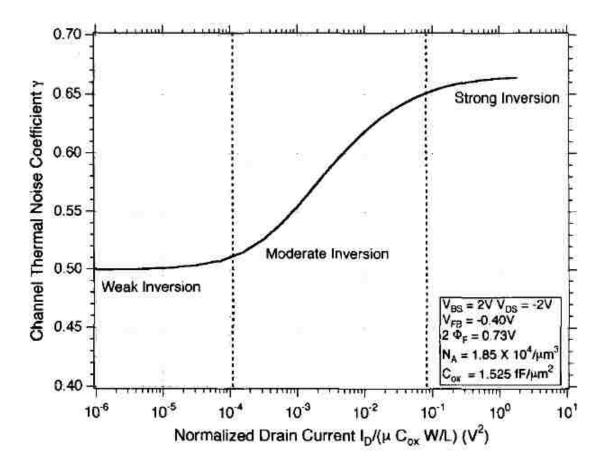

| Figure 3.3:  | Noise coefficient $\gamma$ in saturation as a function of normalized |    |

|--------------|----------------------------------------------------------------------|----|

|              | drain current. Regions of weak, moderate and strong                  |    |

|              | inversion are indicated [55]                                         | 39 |

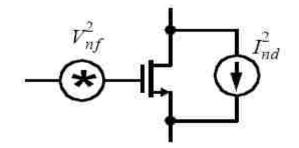

| Figure 3.4:  | Buried channel and flicker noise: manufacturing technique to         |    |

|              | reduce flicker noise. a) Buried channel: low Flicker noise b)        |    |

|              | Standard process: high flicker noise [51]                            | 40 |

| Figure 3.5:  | Thermal noise and Flicker noise of MOSFET [50]                       | 41 |

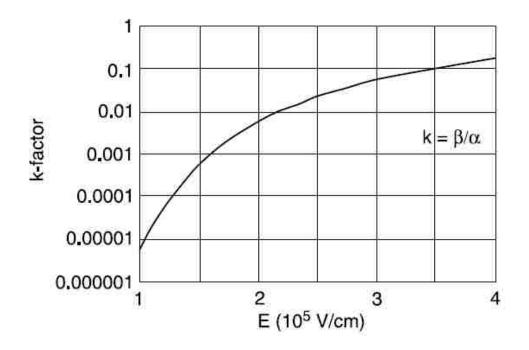

| Figure 3.6:  | Ionization factor, k as function of electric field, during           |    |

|              | avalanche [60]                                                       | 44 |

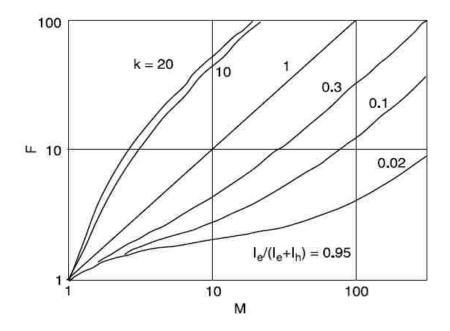

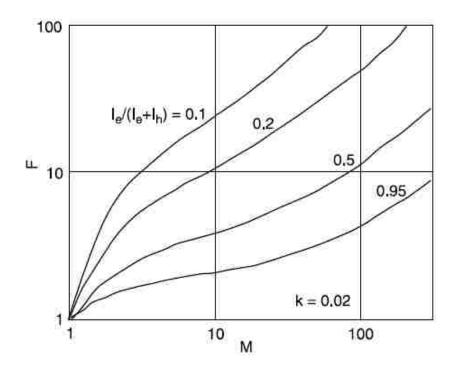

| Figure 3.7:  | Excess noise factor as function of k and M with given                |    |

|              | electron injection ratio of Ie/ (Ie+Ih) = 0.95 [60]                  | 44 |

| Figure 3.8:  | Dependence of noise factor, multiplication factor and                |    |

|              | electron injection ratio, when k=0.02 [60]                           | 45 |

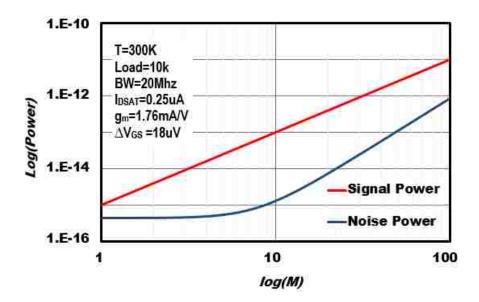

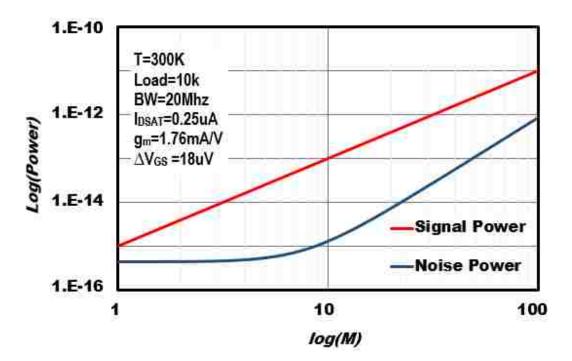

| Figure 3.9:  | Signal power and noise power of A-ISFET as M increases               | 48 |

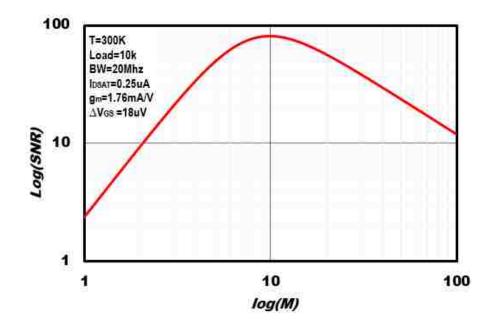

| Figure 3.10: | Signal-to-Noise ratio (SNR) of A-ISFET with Avalanche                |    |

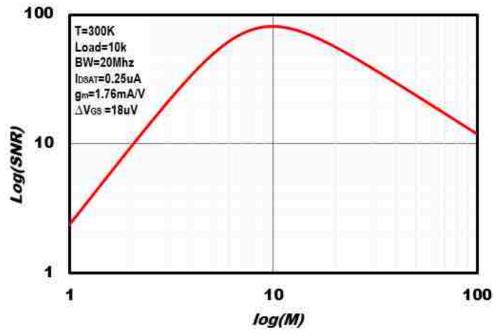

|              | multiplication factor                                                | 49 |

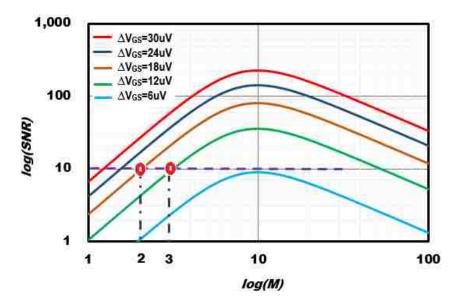

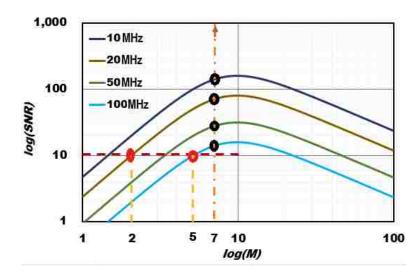

| Figure 3.11: | log(SNR) Vs log(M) for different amount of pH change                 | 50 |

| Figure 3.12: | log(SNR) Vs log(M) for different bandwidth of operation              | 51 |

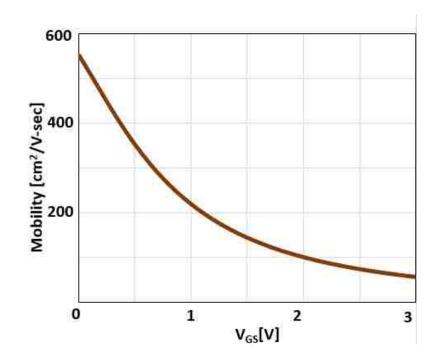

| Figure 4.1:  | Mobility Degradation of carrier in ISFET as $V_{GS}$ voltage         |    |

|              | changes                                                              | 55 |

| Figure 4.2:  | Typical Current flow in a n-channel MOSFET during                    |    |

|              | avalanche [48]                                                       | 55 |

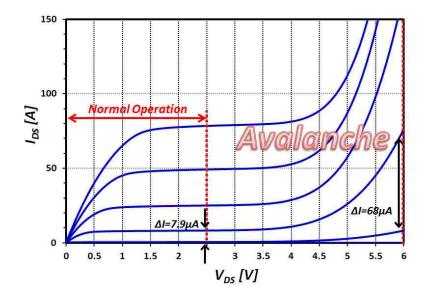

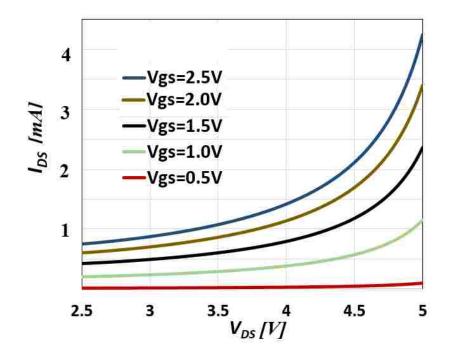

| Figure 4.3:  | Analytical model of output Characteristics curve of A-ISFET          |    |

|              | at Avalanche region                                                  | 57 |

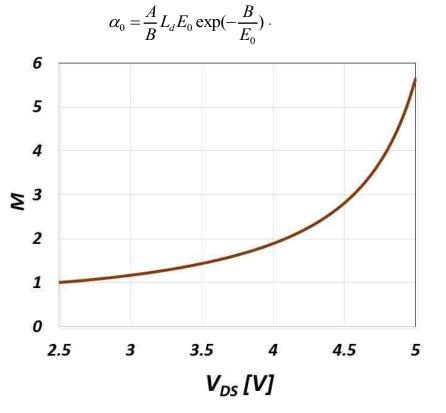

| Figure 4.4:  | Avalanche Multiplication Factor, M when $V_{DS}$ voltage             |    |

|              | across channel is changed                                            | 58 |

| Figure 4.5:  | Signal power and noise power of A-ISFET as M increases               | 59 |

| Figure 4.6:  | Signal-to-noise ratio of A-ISFET as M increases                      | 60 |

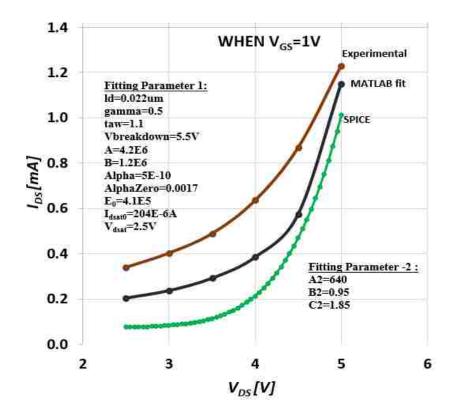

| Figure 4.7:  | Correlation among Drain-Source Current of A-ISFET:                   |    |

|              | SPICE simulation, Experimental measured, and MATLAB                  |    |

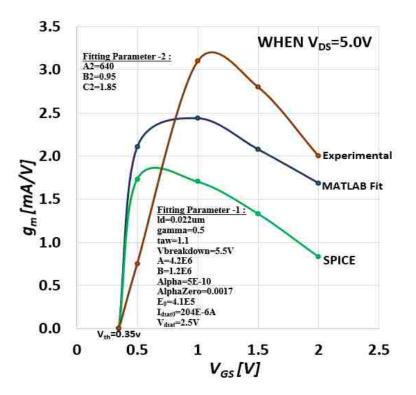

|              | model                                                                | 61 |

| Figure 4.8:  | re 4.8: Correlation among Trans-conductance of A-ISFET at       |    |  |

|--------------|-----------------------------------------------------------------|----|--|

|              | avalanche region: SPICE simulation, Experimental                |    |  |

|              | measured, and MATLAB model                                      | 6  |  |

| Figure 5.1:  | Drift in A1 <sub>2</sub> O <sub>3</sub> membrane at pH=7.0 [70] | 6  |  |

| Figure 5.2:  | ISFET sensor for very small amount of dopamine detection        |    |  |

|              | [79]                                                            | 60 |  |

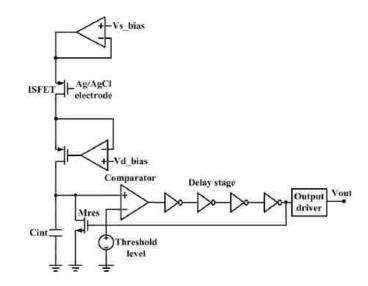

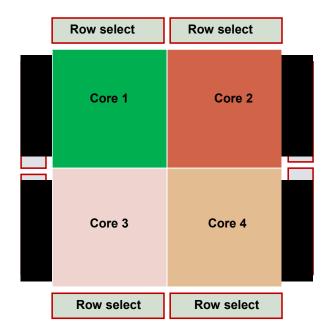

| Figure 5.3:  | Typical system on Chip unit cell and top-level architecture     |    |  |

|              | [82]                                                            | 6  |  |

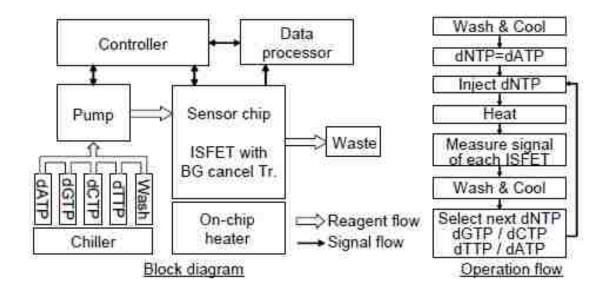

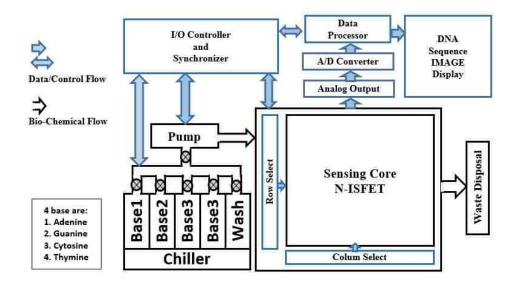

| Figure 5.4:  | Typical ISFET based DNA sequencing system [83]                  | 68 |  |

| Figure 5.5:  | Genome mapping cost per person survey conducted by              |    |  |

|              | NHGRI [7]                                                       | 69 |  |

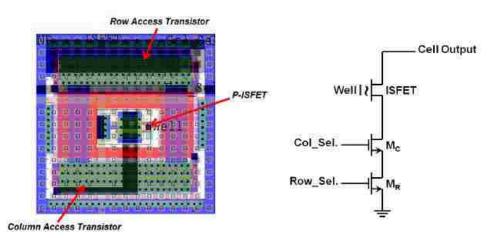

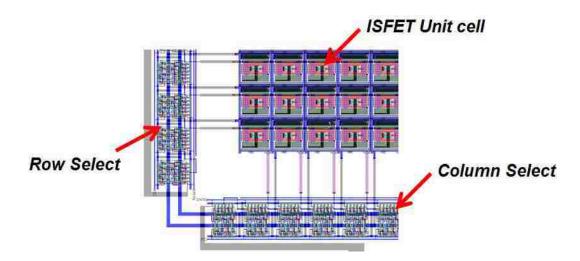

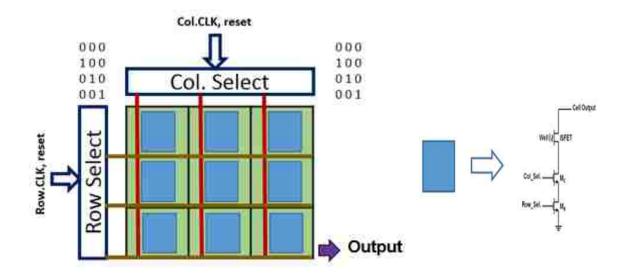

| Figure 5.6:  | A) The layout of the unit-sensing cell - different component    |    |  |

|              | is outlined. B) Unit cell structure of the ISFET sensing chip   |    |  |

|              | with supporting column selector and row selector to access      |    |  |

|              | the sensing data from the cell/ well                            | 70 |  |

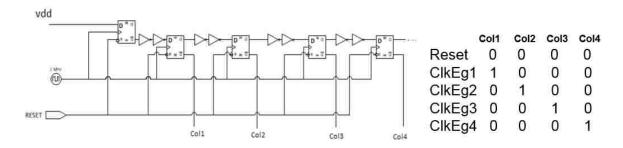

| Figure 5.7:  | The shift register used for row and column select circuits      | 70 |  |

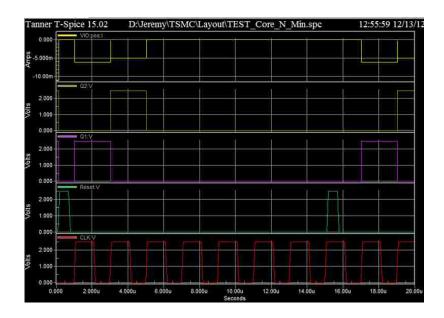

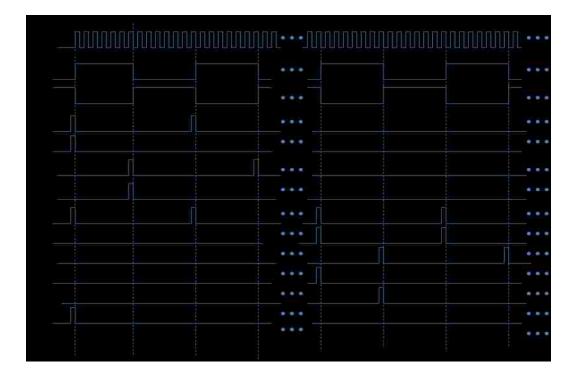

| Figure 5.8:  | The SPICE simulation results showing the clock, reset,          |    |  |

|              | column select pulses and the unit cell output current           | 7  |  |

| Figure 5.9:  | The layout of the row/column select and other supporting        |    |  |

|              | circuits                                                        | 72 |  |

| Figure 5.10: | A typical architecture of a $3 \times 3$ unit sensing chip and  |    |  |

|              | structure of unit cell                                          | 72 |  |

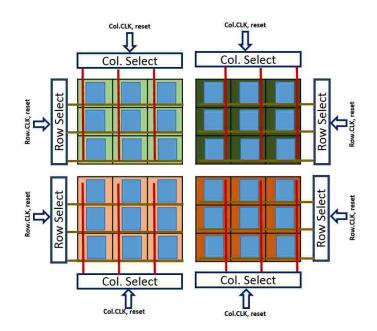

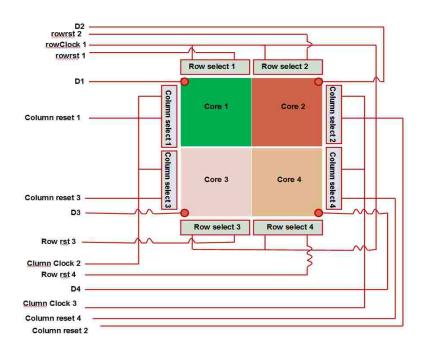

| Figure 5.11: | A typical 4 core sensing chip with respective column select     |    |  |

|              | and row select registers                                        | 73 |  |

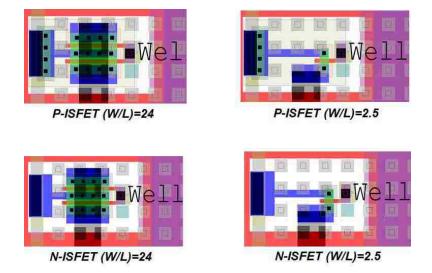

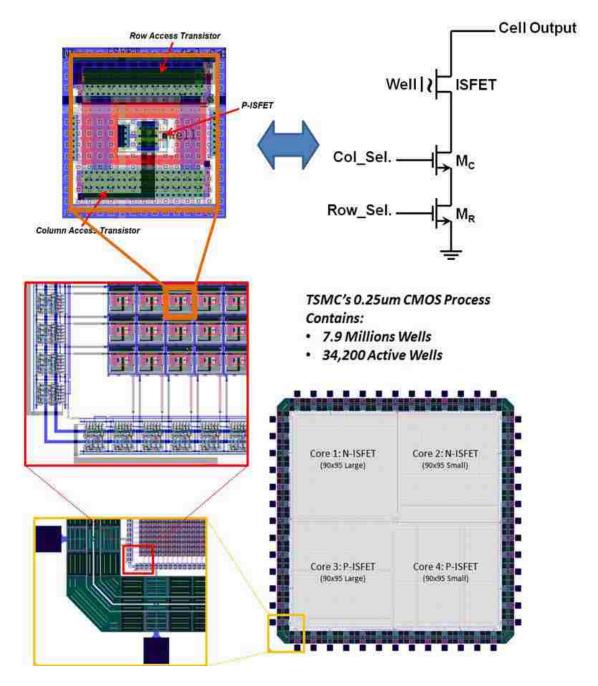

| Figure 5.12: | Top Level architecture and block diagram of ISFET chip          | 74 |  |

| Figure 5.13: | The layout of four types of ISFETs designed in the test chip    | 74 |  |

| Figure 5.14: | The layout of the test chip with ~35,000 arrays of A-ISFETs,    |    |  |

|              | including row select and column select [18]                     | 7  |  |

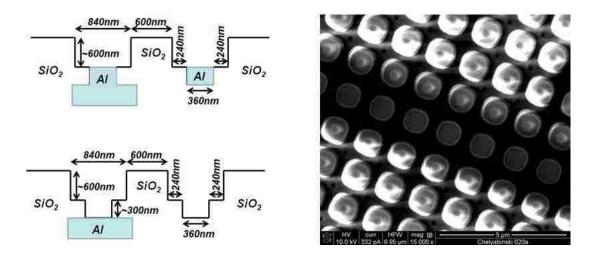

| Figure 5.15: | The cross section diagram of the wells structures (left) and    |    |  |

|              | the SEM photograph of the wells (right) [18]                    | 77 |  |

| Figure 6.1:  | Typical wire bonding and packaging of a chip [94]               | 79 |  |

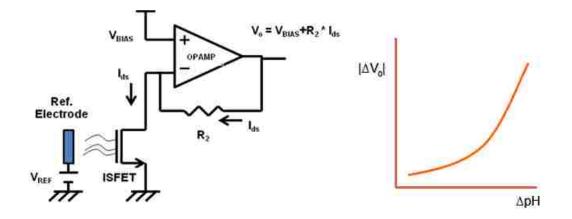

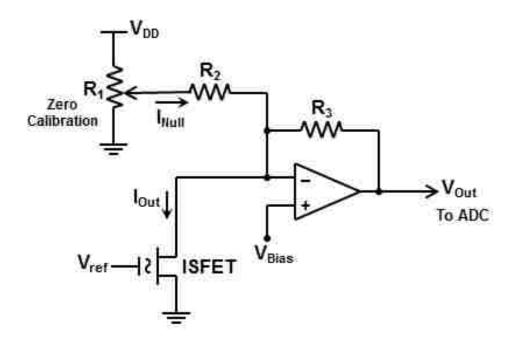

| Figure 6.2:  | A) Circuit diagram showing the new pH to current readout        |    |  |

|              | concept [1] B) Shows the change in output of the readout        |    |  |

|              |                                                                 |    |  |

|              | circuit as the pH is changed                                         | 81 |  |

|--------------|----------------------------------------------------------------------|----|--|

| Figure 6.3:  | Top-level architectural diagram of the ISFET sensing chip            |    |  |

|              | with I/O connections [13]                                            | 81 |  |

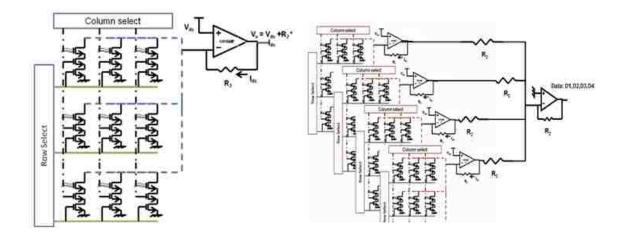

| Figure 6.4:  | A) structure of a $3 \times 3$ single core sensing chip with readout |    |  |

|              | circuit B) Integration of data from a typical 4 core ISFET           |    |  |

|              | chip in Analog domain                                                | 82 |  |

| Figure 6.5:  | Timing diagram of the readout circuit of A-ISFET chip [13].          | 83 |  |

| Figure 6.6:  | DC offset Cancellation in ISFET chip by forcing null current         |    |  |

|              | [18]                                                                 | 84 |  |

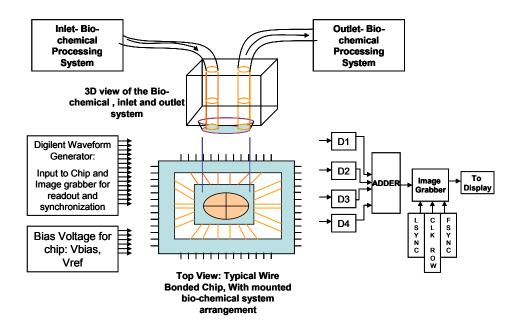

| Figure 6.7:  | Different block for test Setup of A-ISFET sensing wire               |    |  |

|              | bonded chip: top mounted bio-chemical processing system,             |    |  |

|              | waveform generator, bias voltage generator and data                  |    |  |

|              | processing system with image grabber [13]                            | 85 |  |

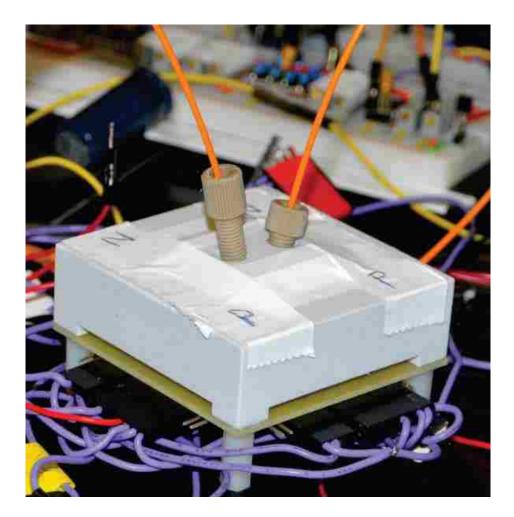

| Figure 6.8:  | Actual lab setup for the testing of the ISFET sensing chip           |    |  |

|              | [13]                                                                 | 86 |  |

| Figure 6.9:  | Actual test setup and wiring - implemented in lab with               |    |  |

|              | biochemical system's inlet and outlet [13]                           | 87 |  |

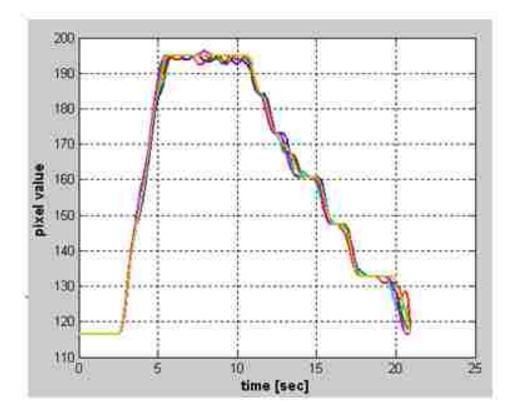

| Figure 6.10: | Transient response of a unit cell of the ISFET chip                  | 88 |  |

| Figure 6.11: | The test chip in the package and with fluidics caps. A typical       |    |  |

|              | extracted image by A-ISFET chip [18]                                 | 89 |  |

| Figure 6.12: | The digital output of an ISFET as a function of pH during            |    |  |

|              | normal operation and avalanche mode of operation [18]                | 89 |  |

| Figure 6.13: | The measured ISFET trans-conductance under nominal                   |    |  |

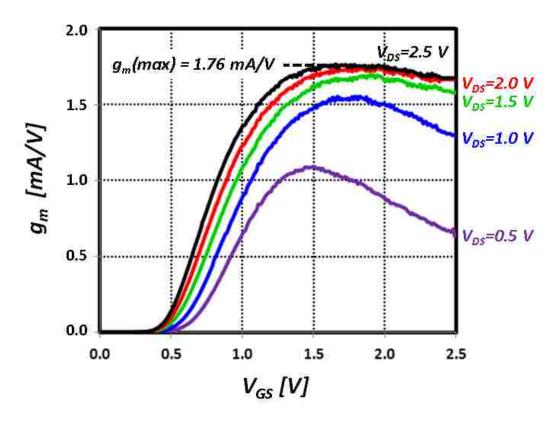

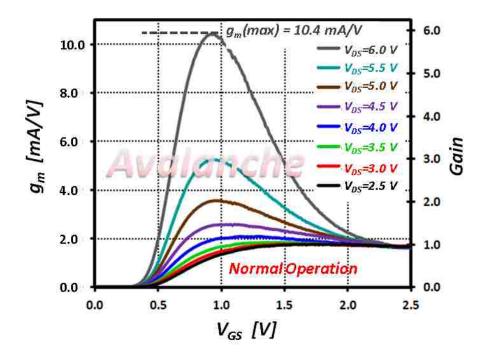

|              | voltages showing the maximum g <sub>m</sub> of 1.76mA/V [18]         | 90 |  |

| Figure 6.14: | The measured ISFET trans-conductance of the same device,             |    |  |

|              | but under avalanche voltages, showing the maximum gm of              |    |  |

|              | 10.4 mA/V [18]                                                       | 91 |  |

| Figure 6.15: | Proposed DNA sequencing system using A-ISFET chip                    | 91 |  |

| Figure 6.16: | Bio-chemical process Flow Diagram for DNA sequencing                 | 92 |  |

### **LIST OF TABLES**

Table 2.1:Electrochemical Sensor Transduction Mechanisms [24].....14

## CHAPTER 1 INTRODUCTION

#### 1.1 Background

DNA stands for Deoxyribonucleic Acid. It is found inside a special area of cell called the nucleus. In 1953, Watson and Crick determined the structure of DNA. Scientists before Watson and Crick had determined the chemical composition of DNA, and that it was the hereditary material, while scientists after Watson and Crick broke the genetic code, and determined how the sequence of bases in DNA specified the sequence of amino acids in proteins. Since then, developing technology for reading this sequence was a fundamental problem in molecular and biological sensing [1]. Techniques that first enabled us to read DNA sequence was invented by Sanger in 1978. They were very costly, slow, and tedious [2]. International Human Genome Project (IHGP) did the first human DNA sequence in 2003, to improve our biological understanding, our health, and wellbeing. IHGP had used conventional Sanger sequencing method for DNA sequencing and it took around 13 years to complete the whole sequencing at a cost of over three billion dollars [3-4].

Reductions in the cost, complexity and time required to sequence large amounts of DNA have significant scientific, economic, and cultural impact [2, 5]. Attempts were made for fast DNA sequencing through conventional Sanger method with massively parallel architecture by Rothberg et.al. in 2005, however the cost remained tremendous [1, 6]. The completion of first human DNA sequencing by HGP in 2003, initiated the need for high-throughput, low cost, fast, accurate, and inexpensive DNA sequencing technologies, Next Generation Sequencing (NGS). NGS is aimed to provide low cost, fast, accurate, user friendly, point-of-care DNA sequencing to uncover details of the genetic contributions to diseases [1-2]. DNA sequencing is a fundamental tool for biological science, which determines the precise order of four bases - adenine, guanine, cytosine, and thymine within a DNA molecule [6].

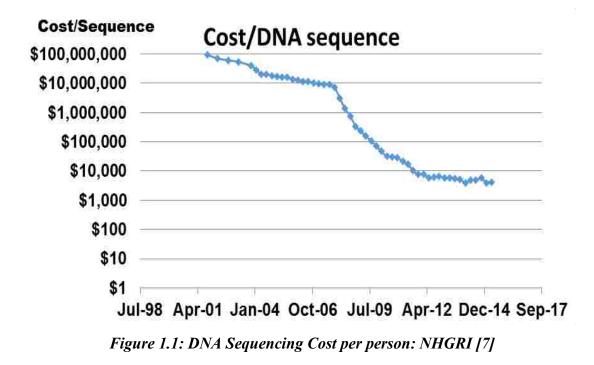

In 2001, the US National Human Genome Research Institute (NHGRI) put forth a goal of achieving a "\$1000 human genome", i.e. the full cost of identifying human genome sequence for less than USD\$1000, as a performance milestone in low cost human genome sequencing. Figure 1.1, shows the trend in human DNA sequencing cost at sequencing centers that are funded by NHGRI [7]. We can see a huge reduction in cost per DNA sequence that results from the development and advancement of next-generation sequencing (NGS) technologies. Low cost human genome sequence will provide us easy access to genomic information to prescribe genomic personalized medicine [1].

#### 1.1.1 Human Genome Project (HGP) : Importance of DNA sequencing

The sequencing of the human genome by HGP was the largest single undertaking in the history of biological science. It was a huge milestone in scientific achievement [4] and was coordinated by the National Institutes of Health and the U.S. Department of Energy. This massive project was carried out in 13 long years i.e. starts in 1990 and was completed in 2003. The primary objective of HGP was to determine the sequence of the human genome and to identify different genes that it contained. The HGP has discovered that there are  $\sim 20,500$  human genes. It has also detailed out

the location, structure, organization, and function of those human genes. The tools and techniques that were developed and used by HGP, helped a great deal to characterize the genomes of several other important organisms used in biological research, such as mice, fruit flies, and flatworms [8].

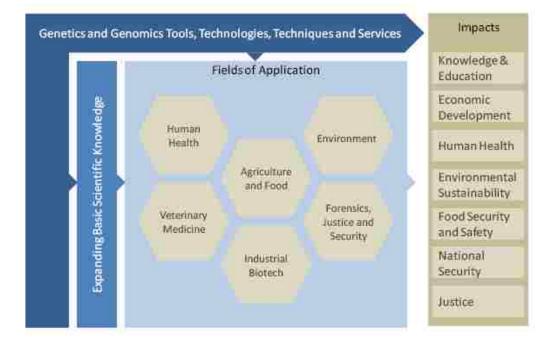

Since the completion of HGP at 2003, there has been a significant development of genomic tools, technologies and techniques to fuel the DNA sequencing efforts forward. These developments, in many cases, are commercialized and form the foundation for a highly active and growing commercial genomics-based industry [4]. One survey shows that federal investment of \$3.8 billion throughout 13 long years in HGP project had generated more than \$67 billion in U.S. economic output, \$20 billion in personal income for Americans and 310 thousand jobs in USA in fiscal year 2010. Literally, the HGP had initiated a "genomic revolution" by influencing renewable energy development, industrial biotechnology, agricultural biosciences, veterinary sciences, environmental science, forensic science, homeland security, and advanced studies in zoology, ecology, anthropology, and other disciplines [4]. Figure 1.2, shows the detailed structure of the functional impacts that had resulted from the sequencing of the human genome by HGP in 2003.

Figure 1.2: Functional Impacts Associated with DNA sequencing [4]

The development and advancement of many NGS techniques provide us fast and low cost DNA sequencing. It is now possible to complete the DNA sequence of a human for a cost of only a few thousand dollars [7] and in couple of days. In the near future, as the price of complete DNA sequencing goes further down to few hundred dollars, we may have the complete DNA sequence data for millions of people. The DNA sequencing data and corresponding correlation may allow us to figure out which sequence is responsible for which traits. As we relate the sequences of all of these people to their traits, we can connect the dots, and have an understanding of the genetic information that defines health, longevity, and behavior.

#### 1.1.2 DNA sequencing and ISFET

IHGP had used conventional Sanger sequencing method for DNA sequencing. This conventional sequencing technique requires expensive laser to detect fluorescent tags or labels. It also needs highly precise and expensive instrumentation, specialized personnel, and very sophisticated numerical algorithms to interpret the generated data. These requirements make this sequencing process very time consuming and costly. Therefore, it is not suitable for use in mass portable point-of-care medical systems [9]. Researchers are exploring various NGS techniques that are cost efficient, fast and easy to use for DNA sequencing. These novel NGS techniques are targeted to on-site and point-of-care medical diagnostics to prescribe genomic personalized medicine. Numerous research and development on NGS has forced a fundamental shift away from the Sanger sequencing for genome analysis to different label-free, user friendly, non-optical, fast, and easy techniques [5].

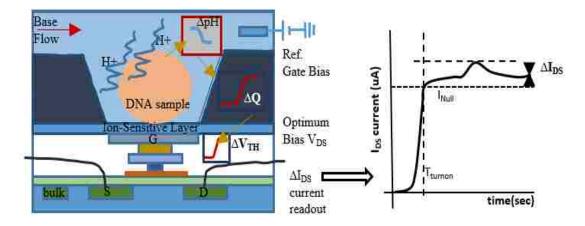

Figure 1.3: Typical ISFET sensor and its output signal

Semiconductor based, non-optical DNA sequencers are suitable for low cost and high throughput sequencing because they read a DNA sequence electronically. Moreover, they can be manufactured in high volumes at very low cost by standard complementary metal oxide semiconductor (CMOS) fabrication process [10]. Ion sensitive filed effect transistor (ISFET) [11] based electro-chemical sensor is one of the most suitable candidate for DNA sequencing in non-optical, semiconductor based techniques [12]. In addition, ISFET biosensors are also CMOS compatible, portable and label-free [12-14].

The ion sensitive gate insulator of the ISFET senses specific ion concentration and generates an interface potential at the gate ( $\Delta V_{th}$ ). This interface potential is proportional to pH change ( $\Delta pH$ ). The change in interface potential at gate, due to pH change results in a change of drain-source current, based upon the bias of ISFET [10, 13]. Figure 1.3, shows the structure of a typical ISFET sensor and the generated output signal of the sensor [10]. The gate of ISFET can be made of different ionsensitive materials, which includes Al<sub>2</sub>O<sub>3</sub>, Si<sub>3</sub>N<sub>4</sub>, Ta<sub>2</sub>O<sub>5</sub>, SnO<sub>2</sub>, and SiO<sub>2</sub>. Our selection of gate material is based on stability, sensitivity, selectivity, long-term drift, temperature dependency, and responses time of the gate material.

#### **1.2 Dissertation contents**

This dissertation mainly focuses on the design, test and analysis of an ISFET sensing chip, which is fabricated to verify a highly sensitive NGS technique for DNA sequencing. As we are dealing with a very weak sensing signal, the ISFET chip is designed to operate in avalanche mode of operation to derive higher sensitivity from the ISFET sensor. The avalanche phenomenon is an established idea for photodetectors (APD) and is extensively used in optical communication. However, the concept of avalanche ISFET (A-ISFET) is very new and was never used for ISFET sensor. Our motivation behind this unique A-ISFET concept is to reduce DNA sequencing cost further and to increase the sensor sensitivity further. Avalanche operation of ISFET provides us enough sensitivity from a smaller sensing device and it makes the overall chip size smaller, which results further reduction in DNA sequencing cost.

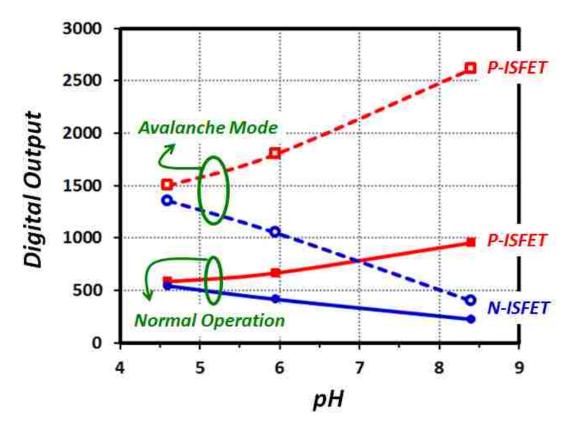

We also propose a new readout technique for A-ISFET sensor, which is based on pH-to-Current conversion [13]. The conventional readout technique for ISFET is pHto-Voltage [10, 14-17]. In pH-to-Voltage readout technique, we force a small reference current into the drain of ISFET and measure the V<sub>GS</sub> voltage as the output of ISFET sensor. The proposed pH-to-Current readout technique for A-ISFET, on the other hand, forces a drain-source voltage that is close to breakdown voltage and reads the current I<sub>DS</sub>, which results from the small change of interface potential at the gate  $(\Delta V_{th})$ . The change in interface potential at gate  $(\Delta V_{th})$  is proportional to pH change  $(\Delta pH)$ . The unique circuit that we designed for pH-to-Current readout ensures the operation of ISFET in avalanche through forcing a drain to source bias voltage that is near breakdown region of the p-n junction. A-ISFET, which is designed for pH-to-Current readout, is the sensing component of our DNA sequencing chip [18]. However, the output response from A-ISFET is non-linear with pH change. This nonlinear response of A-ISFET can be taken care by proper calibration and lookup table as well as through post processing of the bulk data by digital signal processing algorithm. The operation of ISFET in avalanche region gives us a very high output signal in response to a very weak signal at sensor input. This high output signal results from the multiplication of carriers due to impact ionization in depletion region of reverse bias p-n junction. A very strong reverse bias voltage in p-n junction at drain

side of A-ISFET creates a long depletion region and most of the carrier multiplication takes place there.

The completion of HGP in 2003, had initiated a strong drive for NGS techniques that are of low cost, fast, and user-friendly. Among NGS techniques, ISFET based very large scale DNA sensor-array chip is getting huge attention [10, 12, 18] for direct human genome sequencing because of, their low cost, non-optical, semi-conductor based sensing. We need to minimize the size of ISFET sensor further so that very large-scale DNA sensor-array integration is possible with lower cost. This dissertation proposes a very unique unit sensing cell with only three scalable FET transistor i.e. one is used for sensing (A-ISFET) and the rest two (MOS-FET) are for switching and synchronization. This unique and compact structure of the unit cell greatly reduces the size and fabrication cost of the sequencing chip.

We have found through mathematical analysis that the sensitivity of the ISFET is greatly dependent on the operational region, which is set by DC bias of the device. During ISFET operation with nominal voltages, we can get maximum sensitivity from the device by operating it in saturation region. SPICE simulation confirms that if we operate ISFET in avalanche region, we can achieve even more sensitivity from a tiny device i.e.  $\sim$ 10X more sensitivity from maximum sensitivity at normal mode of operation.

Noise is a disturbance that obscures or reduces the clarity of a signal. Every electronic device generates its own intrinsic noise, in addition to other induced noise from associated nearby components. We have identified different noise components of A-ISFET and have modeled their respective characteristics with bias change. Different noise components that we find in A-ISFET are thermal noise, flicker noise, shot noise, and dark current noise. We have developed a model to determine the signal-to-noise (SNR) ratio of A-ISFET. The model identified that there is an optimum bias point of A-ISFET to have maximum SNR sensitivity from the sensor. This noise modeling of A-ISFET sensor will help us to understand the associated noise sources better and it will provide us options to optimize the design. Using the

noise model, we can minimize the noise impact of A-ISFET sensor and maximize its Signal-to-Noise (SNR).

We have developed a physical operation-based drain current model for novel avalanche ISFET (A-ISFET). Since the A-ISFET operates in avalanche region, an accurate model for the breakdown behavior is therefore very important for both circuit design and circuit reliability point of view. The drain breakdown can result from impact ionization, a parasitic bipolar transistor, or the punch-through effect. Our model of A-ISFET drain current at avalanche region is due to impact ionization. To validate our drain current model of A-ISFET we perform a correlation study of the analytical data with SPICE simulation results, and experimental measured results.

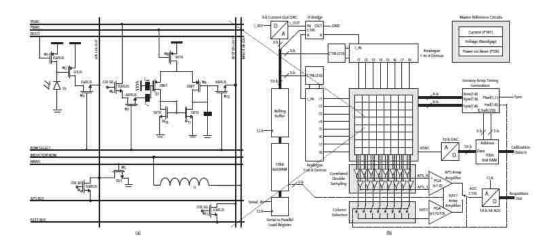

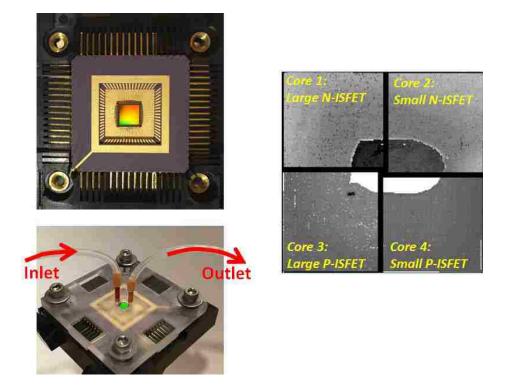

We have designed a test chip by the TSMC's 0.25um CMOS process and laid out the chip to fabricate using the same process. Our test chip contains four different cores where each core is made of different unit cells with different dimensions and type. The available ISFET devices are of p-type and n-type with small (with W/L=2.5) and large (with W/L=24) dimensions. Each core is made of 90x95 arrays of specific type of ISFET device. The chip pad ring contains electrostatic discharge (ESD) devices to protect the transistors in the core against electrostatic charge injection during chip handling. There are total of 52 pins in the chip including four  $V_{DD}$ , four GND and several input/output signals. In this dissertation, we also designed the readout interfaces, data processing circuits and integrated the whole system for fast and efficient data processing. The test chip is used as the verification of this A-ISFET based new DNA sequencing concept and the validation of the integration and synchronization of the whole sensing system.

The fabricated chip from TSMC is found to be functional. We have created a test environment and test setup for correct readout of the sensing data from the chip through proper synchronizing signal. During test, we have accessed each of the unit cells in the test chip through column select and row select signal during readout process. A specially milled and shaped structure is used to inlet and outlet the biochemical on the surface of A-ISFET arrays. The inlet and outlet of the bio-chemical system is controlled by time-controlled valve, to control the flow of liquids on the surface of A-ISFET chip for test and verification of this unique DNA sensing concept. We test the chip both at normal mode and at avalanche mode. We find that it works perfectly as a sensor both in normal mode and in avalanche mode. Test results show that the sensitivity at avalanche mode is much higher than (~6 times) the sensitivity at normal mode of operation.

#### 1.3 Innovative aspects and Unique Contributions

This dissertation contains some novel aspects that are listed below:

- First ever operation of an ISFET in the avalanche region to derive high sensitivity from a very weak input signal and/or tiny sensing device.

- A unique pH-to-Current readout process is proposed and demonstrated to operate the sensing device in avalanche mode.

- Noise analysis of ISFET in avalanche mode is carried out to ensure optimum bias for maximum Signal-to-Noise ratio (SNR) during operation.

- A very unique, compact and tiny unit cell is designed to minimize the chip size, and cost.

- A physical operation based drain current model for ISFET at avalanche mode of operation is developed and a correlation study is performed to validate the model.

- A functional test chip is designed, laid out and tested to validate the concept of A-ISFET.

#### **1.4 Organization of the Dissertation**

In this dissertation, we are mainly concerned with analysis, design, modeling, and testing of a very new sensing device; avalanche ISFET (A- ISFET) for low cost Next Generation DNA sequencing.

Chapter 1 starts with a discussion on background and motivation toward DNA sequencing and low cost NGS techniques. It is followed by a discussion on the innovative aspects of this dissertation and the contents of the dissertation.

Chapter 2 gives us an introduction with ISFET sensor and sensitivity. It also presents a mathematical analysis on the sensitivity of ISFET based sensor. The analysis was done in SPICE and MATLAB, for both normal modes of operation and avalanche mode of operation.

Chapter 3 identifies different noise components in A-ISFET and model their behavior with change of bias. Here, we developed a model to find an optimum bias point for A-ISFET sensor that give us maximum Signal-to-Noise ratio (SNR).

Chapter 4 models the drain current behavior of ISFET while it operates in avalanche region. We also verified the model through a correlation study with simulation, and measurement data.

Chapter 5 discusses on the design, architecture, and layout of the ISFET test chip. It also discusses on the different building blocks of the test chip and their operation. Here, we also present the findings of our literature review on state of the art ISFET sensor and DNA sequencing technique.

Chapter 6 presents the test procedure, and results of the ISFET chip. It also discusses on wire bonding, signal setup, synchronization, hardware, and other details.

Finally, in Chapter 7 we concluded the dissertation with discussions.

#### 1.5 Discussions

In this chapter, we give a brief introduction on the dissertation, its contents and organization. It also gives us an indication on the motivation behind the research and the economic impact of the research.

## CHAPTER 2 THEORY ON ISFET AND SENSITIVITY

#### 2.1 Introduction to Sensor

A sensor is a device that is used to translate information, such as amount of ion concentration into an analytical signal, whereas, a biosensor is generally defined as an analytical device that is designed to detect or quantify a biochemical molecule such as a particular DNA sequence, pH or particular protein [19]. A successful biosensor has a high sensitive detector element that can detect very small changes in the bio-sensitive element without cross sensitivity to other irrelevant parameters, such as temperature or pressure. An ideal biosensor should neither be harmful nor deteriorate in the presence of biological substances. Ideal biosensors are fully reversible, highly reliable, highly selective, small, portable, have high signal-to-noise ratio, be immune to environmental conditions, and easy to calibrate. An actuator, on the other hand, can be defined as a transducer that converts an electrical signal or energy into a signal of another form for motors and switches [20].

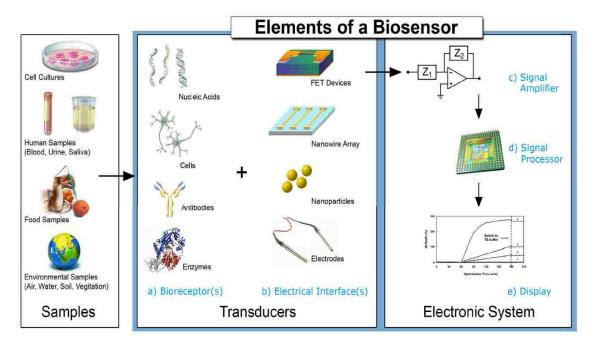

Quantification of biological or biochemical processes is of the utmost importance for medical, biological and biotechnological applications. However, converting the biological information to an easily processed electronic signal is challenging due to the complexity of connecting an electronic device directly to a biological environment. Electrochemical biosensors provide us with an attractive way to analyze the content of a biological sample due to the direct conversion of a biological event to an electronic signal [21]. Figure 2.1, shows typical elements and components of electrical biosensors.

Figure 2.1: Typical elements of Electric Biosensor [21]

For a sensor, one of the most important figures of merit is the limit of detection, defined by the smallest concentration or amount of target that can be reliably sensed. Its internal noise, its drift, and its temperature [19] determine the limit of detection of sensor. However, we can improve overall sensing from a sensor through differential measurements in which a reference and a sensing element are used. Ideally, the reference element is insensitive to the analyte, but otherwise it has similar properties to the sensing element. The output signal that results from the difference between the signal of reference element and the sensing element is very robust from noise and influences [22].

This research work limits us to the electronic ion sensitive field-effect sensor, which is the basis of our A-ISFET based DNA sequencing chip. Electronic biosensors rely solely on the measurement of currents and/or voltages to detect the contents in a bio-chemical [19]. Due to their low cost, low power, and ease of miniaturization, electrical biosensors have great potential for applications, where minimizing size and cost is crucial, such as point of care diagnostics and bio-warfare agent detection.

#### 2.1.1 Bio-Sensor: Chemical Sensors and their features

A chemical sensor is a device that transforms chemical information into an analytically useful signal. Biosensors are chemical sensors in which the recognition system uses a biochemical mechanism [23]. A biosensor needs to have three general features, which are a selective surface, a transducer, and a processor [20] as shown in Figure 2.2. The selective surface allows for a specific interaction with the target analyte, which is a compound whose composition or presence is being sought. A common method to achieve selectivity is to modify the sensor surface with immobilized receptors that bind selectively to the wanted target.

The main limitations of many chemical sensors are associated with the selectivity of the response to the target analyte compared with the response seen from potential background or contaminating compounds [25]. In a constant background, there is little need for selectivity. Generally, for a chemical sensor the background concentration changes in unknown ways due to the presence of similar chemical components or active species, temperature and pressure fluctuations.

The main types of chemical sensors developed to date rely on electrical or optical transduction technologies [25]. In this dissertation, we are mainly concerned with electrical transduction, which can be divide into amperometric type, potentiometric type or conductimetric type, depending on whether the measured signal is the current, voltage or conductance, respectively [19,25].

Figure 2.2: General features of a chemical sensor [20, 24]

| Transducer     | Mechanism                                               | Signal                                                                      | Example Sensor                                                                     |  |

|----------------|---------------------------------------------------------|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|

| Amperometric   | Electron charge<br>transfer reaction<br>(Faraday's law) | Current: due to<br>production or<br>consumption of<br>electroactive species | Oxygen, some<br>hydrocarbons,<br>hydrogen peroxide,<br>fuel cells                  |  |

| Potentiometric | Multiphase<br>equilibrium<br>(Nernst Equation)          | Potential: due to<br>distribution of ionic<br>species                       | Glass pH electrode,<br>ion selective electrode                                     |  |

| Conductomeric  | Variation of<br>resistance with<br>composition          | Conductance or<br>resistance: due to<br>change in resistive<br>elements     | Metal-oxide-<br>semiconductor gas and<br>humidity sensor, the<br>oxide gas sensors |  |

Table 2.1: Electrochemical Sensor Transduction Mechanisms [24]

#### 2.1.2 Amperometric Chemical Sensor

The diagnostic analyses that are widely available are based on optical measurements. However, complicated readout instrumentation, long duration for sample pre-processing and labeling makes optical diagnostic methods expensive, time-consuming and non-portable. Electrical detection methods, on the other hand, rely on much simpler instrumentation that ensures lower cost, and easy and faster operation. Electrical detection methods also ensure label-free detection, avoidance of the influence of the label on the binding properties, and the possibility of real-time monitoring of binding interactions. In addition, micro fabrication based mass production provides the possibility of miniaturization and multiplex sensing through electrical transducers. The sensing method of our proposed DNA sequencing is based on electrical transduction in which amperometric chemical sensing is used.

An amperometric chemical sensor measures the current that results from change in electro-active species in a bio-chemical solution [21]. The sensor is made of two metal electrodes maintained at a constant potential or voltage difference. The current flow through the sensor circuit is established and is monitored by suitable electronics and techniques. The presence of electro-active species is sensed through the variation of measured current between the electrodes.

#### 2.2 Ion Sensitive Field Effect Transistor (ISFET)

ISFET is an electronic device that is used as an electro-chemical sensor and it works on the field effect principle, similar to that of MOSFET. ISFET was proposed and invented by Piet Bergveld over 40 years ago [26]. Since then, the original ISFET had been used in various devices including digital pH meters [27], urea detection devices [28], glucose sensors [29], and DNA image Sensors [30]. Recently, massive arrays of ISFETs are reported to use in CMOS compatible integrated circuit, to directly perform DNA sequencing of genomes [12]. This dissertation is mainly concerned with A-ISFET based DNA sequence chip where ISFET is the building block of the sensor. Many ISFET's characteristics are related to the FET behavior. Therefore, in this section fundamentals of semiconductors and FET physics will be discussed.

Figure 2.3: Energy band diagram of materials [31]

#### 2.2.1 Fundamentals of Semiconductor

Materials such as metals, insulators or semiconductors have different electrical properties due to their electronic band structure. In semiconductors, there are forbidden energy states within an energy band gap  $E_g$ . Allowed energy levels form bands below and above the band gap  $E_g$  are called valence and conduction band, respectively. Typically, in a semiconductor, the energy of the band gap  $E_g$  is smaller than 2 eV and the thermal energy at room temperature can give electrons enough energy to move from the valence band to the conduction band. Insulators have a wider band gap (e.g. 9 eV for SiO<sub>2</sub>). Therefore, in insulator electrons cannot cross the band gap at room temperature. Whereas in metals/conductors the valence band and conduction band overlaps. Figure 2.3, shows the relation of valence band and conduction band with bandgap for metal, semiconductor and insulator [31].

Based on doping, semiconductors can be classified into two types, which are intrinsic semiconductor and extrinsic semiconductor. In intrinsic semiconductors, there are no impurity atoms and electron-hole pairs are generated and destroyed by thermal generation-recombination processes. In thermal equilibrium, each electron in the conduction band forms a hole in the valence band and thus the concentration of electrons equals the concentration of holes, in intrinsic semiconductors. This is the reason for Fermi level being in middle of the band gap in intrinsic semiconductor.

Figure 2.4: Three types of semiconductors: a) intrinsic semiconductors. B) n-type semiconductors [31]

A semiconductor material that has implanted impurities is called extrinsic semiconductors. Implanted impurities form energy states within the band gap of semiconductor, which are very close to the valence or the conduction band, depending on the type of doping atoms. Doping atoms can have either three or five valence electrons. As an example, Boron has only three valence electrons and when it substitutes a silicon atom in the crystal lattice; it accepts an additional electron and becomes ionized. Therefore, boron is known as an acceptor. When boron is ionized, a positively charged hole is generated in the valence band that begins to participate in ptype conductance, whereas the boron ion stays fixed in the silicon crystal. For n-type conductance, the silicon is doped with doping atoms having five valence electrons, such as phosphorus or arsenic. The extra valence electron is donated to the lattice and a free electron is generated in the conduction band. In extrinsic semiconductor, the Fermi level is not in the middle of the band gap and it moves with variation of doping concentration in the material. In Figure 2.4, we can see the relation among valence band, conduction band, Fermi level and doping concentrations [31] of semiconductor materials.

#### 2.2.2 MOSFET structure and Field Effect

Transistors are the semiconductor device that is extensively fabricated to make different electronic equipment. There are two types of transistors, one is current controlled bipolar junction transistor (BJT) and the other is voltage-controlled field-effect transistor (FET). In 1925, Julius E. Lilienfeld patents the basic principle of FET operation. However, in 1959 Atalla and Kahng from the Bell Labs first fabricated a metal oxide field-effect transistor (MOSFET) that works on the same principles as of FET.

The structure of an enhancement n-channel MOSFET, which has four different terminals, is shown in Figure 2.5. The terminals are drain (D), source (S), gate (G) and substrate (B). There is no conducting channel between source and drain, when the applied voltage in gate is zero. However, as we apply a positive voltage on the gate, charge carriers accumulate under the gate oxide through inversion process and conduction between drain and source begins. We can control the conductance and the amount of charge in MOSFET channel by changing the gate voltage V<sub>gs</sub>[31].

Figure 2.5: NMOS transistor and its operation with characteristics curve [32]

The type of charge carriers responsible for the conduction of the channel is opposite to the substrate. The p-type substrate inverts into n-type and an inversion layer is formed. The transfer curve and output characteristics curve of an n-channel MOSFET is also shown in Figure 2.5 [32].

One of the most important parameter of MOSFET is the threshold voltage (V<sub>th</sub>), which is the minimum gate voltage required to form inversion channel under gate oxide for conduction, as shown in Figure 2.5. MOSFET has two regions of operation, the triode region and the saturation region at each fixed gate voltage. When  $V_{ds} < V_{gs} - V_{th}$  and  $V_{gs} > V_{th}$ , MOSFET operates in triode or linear region of operation. In triode region, the channel current is linear function of drain-source voltage V<sub>ds</sub>, which can be modeled as:

$$I_{ds} = \mu_n C_{ox} \frac{W}{L} \left[ (V_{gs} - V_{th}) V_{ds} - \frac{1}{2} V_{ds}^2 \right] = K_{n'} \frac{W}{L} \left[ (V_{gs} - V_{th}) V_{ds} - \frac{1}{2} V_{ds}^2 \right] \quad , \qquad (2.1)$$

when  $V_{ds} = V_{gs} - V_{th}$  and  $V_{gs} > V_{th}$ , MOSFET operates in saturation region. In saturation region, the current is independent of drain-source voltage,  $V_{ds}$  and it can be modeled by:

$$I_{ds} = \mu_n C_{ox} \frac{W}{2L} [ (V_{gs} - V_{th}) ]^2 = K_{n'} \frac{W}{2L} [ (V_{gs} - V_{th}) ]^2 .$$

(2.2)

Figure 2.6: Structure of MOSFET and ISFET : Compare and Contrast [33]

# 2.2.3 MOSFET to ISFET

If we compare the structure and operation of ISFET with MOSFET, we find that they are very similar. ISFET is a MOSFET whose metal gate is replaced by a liquid gate, which is typically an electrode immersed in an electrolyte solution as shown in Figure 2.6. When ISFET is used as a sensor, the electrolyte is the solution under test that contains charged particles such as charged bio-molecules or protons. The gate oxide of ISFET is directly exposed to the electrolyte solution and is usually modified due to specific bindings of target species with receptors [33].

In case of MOSFET the threshold, voltage is assumed constant whereas, the threshold voltage for ISFET is dependent upon the ion concentration in electrolyte solution on the oxide layer. The threshold voltage of ISFET can be modeled as in [26]-

$$V_{th} = E_{ref} - \psi_0 + \chi_{solution} - \frac{\phi_{Si}}{q} - \frac{Q_{ox} + Q_{ss} + Q_B}{C_{ox}} + 2\phi_j \quad , \tag{2.3}$$

where,  $E_{ref}$  is the constant potential of reference electrode,  $\psi_o$  is the interface potential at solution/oxide interface,  $\chi_{solution}$  is the surface dipole potential of the solvent,  $\phi_{s_i}$  is the work function of the silicon,  $Q_{ox}, Q_{ss}$  and  $Q_B$  are the oxide charge, oxide interface charge and bulk charge respectively,  $2\phi_j$  is the potential for inversion of channel, and  $C_{ox}$  is the oxide capacitance /unit area. It can be simplified as in [34] to be-

$$V_{th} = V_{th(MOS)} + V_{chem} \quad , \tag{2.4}$$

where  $V_{chem} = \gamma + 2.303 \alpha U_T pH$  and  $\gamma$  is a group of pH independent chemical potential,  $\alpha$  is a dimensionless sensitivity parameter, and  $U_T = kT/q$  is the thermal voltage.

In an ideal case, where the highest sensitive interface material Ta<sub>2</sub>O<sub>5</sub> is used on the gate,  $\alpha$  is approximately equal to 1 and  $U_T$  at room temperature is about 26mV; we can achieve about 60mV of change in threshold voltage for every unit of pH change. Therefore, as the pH of gate liquid increase, threshold voltage of ISFET increases too. This increment of threshold voltage in ISFET causes reduced drainsource current  $I_{ds}$  for a given bias condition, shown in Figure 2.7.

We can model ISFET by combining a chemical part and a MOS transistor together, as shown in Figure 2.8. The capacitor in the chemical part is consists of two serially connected capacitors, which are Gouy-Chapman and Helmholtz capacitors [35]. This model concludes ISFET to be a standard MOS transistor with a pH sensitive oxide surface (SiO<sub>2</sub>) that can be modeled as a capacitor.

Figure 2.7: ISFET operation with transfer curve [32]

### 2.2.4 Sensing approaches of ISFET

ISFET can be used as an electro-chemical sensor that can directly produce electrical signal at sensor output. The electrical detection method of ISFET provides much simpler instrumentation, lower setup cost, easier and faster operation. This unique property of ISFET is the main reason for its huge popularity among researchers. Electrical detection method also ensures label-free detection approaches, avoidance of the influence of the label on the binding properties, and possibility of real-time monitoring of binding interactions. Moreover, semiconductor based ISFET sensors are compatible to standard scalable CMOS micro-fabrication. Therefore, ISFET sensors can be produced in large scale. They are also suitable for integration, and multiplex sensing.

The readout signal from ISFET sensor can be either the voltage or the current. The conventional approach is to read the voltage at the output of ISFET through pH-to-voltage conversion process as shown in Figure 2.9. In pH-to-Voltage conversion process, we force a small reference current through the channel and measure the voltage change at gate, due to ion-concentration change or chemical activity. As shown in [34], the threshold voltage of ISFET is linearly proportional to the pH of its sensing port. Therefore, ISFET sensor shows a linear response with pH change, when we use pH-to-Voltage conversion readout technique. However, it is desirable to measure and readout the threshold voltage of an ISFET at the weak inversion.

Figure 2.8 : ISFET model with respect to MOSFET [35]

Figure 2.9: Sensing and readout principles of ISFET [18]

Our new proposed approach is to read current through a pH-to-current readout scheme shown in Figure 2.9. In this technique, we force a constant  $V_{ds}$  and measure the I<sub>ds</sub> current for pH change at the gate. Although this new scheme does not provide a linear response to the pH, it allows the ISFET to operate in avalanche mode, which provides us with more sensitivity when gate signal is very weak [18]. High sensitivity of A-ISFET results from the avalanche multiplication arising from impact ionization of carries in depletion region of p-n junction when high reverse bias voltage is applied. We can address the non-linear response issue of A-ISFET through the proper calibration and lookup table as well as through post processing of the bulk data from DNA sequencing chip by complex digital signal processing algorithm.

## 2.2.5 CMOS compatibility of ISFET

The structure of ISFET is similar to that of MOSFET. Therefore, the fabrication of ISFET is compatible to standard CMOS process and it can be manufactured through economical scalable standard CMOS process. The gate of ISFET is made from chemical sensitive dielectric materials, which are SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, Al<sub>2</sub>O<sub>3</sub> or Ta<sub>2</sub>O<sub>5</sub> etc. We generally select them based on their sensitivity, selectivity and long-term stability [26, 36, 37]. The standard CMOS process uses poly-silicon gate to define source and drain. Therefore, for fabricating ISFET many modified standard CMOS process is proposed [38, 39] with additional process steps. The extra

steps define the ISFET gate oxide region, formation of the gate oxide and pH sensitive insulator layers, and the formation of a window in the passivation layer to expose the ISFET sensor. When low cost fabrication is the focus, use of standard unmodified CMOS process for ISFET fabrication is the most desirable as they are the most economical option.

If an unmodified CMOS process is used to fabricate an ISFET, the polysilicon layer must be left in the gate area for good source and drain definitions. This does not counteract the ISFET operation if an insulating pH-sensitive layer is used on top of the poly-silicon gate of standard CMOS process. Several pH-sensitive ISFET structures reported in literature [40, 41] use commercial CMOS process without any modification or post processing. In this research, our avalanche ISFET DNA sequencing chip went through standard CMOS process at TSMC and then was postprocessed for well creation at MTTC of UNM.

## **2.2.6 ESD protection of ISFET**

ISFET has very high input impedance, which makes it very sensitive to electrostatic discharge damage (ESD), similar to MOSFET. Diode networks that provide a lower impedance path between susceptible gates and the substrate can protect standard MOS devices. However, these protective networks are not available with normal ISFETs, since there is no gate conductive electrode in ISFET. There are two kind of electrostatic charge based damage in ISFET. The first type of ESD damage is destructive in nature and it damages the gate insulator. This damage of gate insulator is due to high electric field and it makes the ISFET inoperable.

The second type of ESD damage is non-destructive and it leads to a large change in threshold voltage of the device. This ESD problem of ISFET is highly reduced once the device is immersed in a solution; the conducting liquid takes away any static charge on the ISFET gate. Several ISFET electrostatic protection circuits can be found in literature consisting additional poly gate switch [42], using guard ring close to ISFET with diodes, a MOS transistor and a capacitor [43], or an ESD diode protection with the reference electrode [44] as shown in Figure 2.10.

Figure 2.10: ESD protections of ISFET (a) Poly Si gate switching (b) Guard ring around ISFET gate with diode (c) Diode protection of reference electrode

## 2.2.7 Non-idealities of ISFET

The concept of ISFET is around 40 years old but practical applications are still emerging slowly, due to limiting factors arising from non-idealities associated with ISFET fabrication and operation. The non-idealities of ISFET can be divided into several categories, which are temperature dependence, light sensitivity and drift.

The temperature dependency of ISFET arises from the dependence of drain current on  $\beta$  and  $V_{th}$ . The term  $\beta$  is proportional to mobility of carriers in the channel whereas the mobility is an inverse function of the absolute temperature in Kelvin scale *T*. Therefore, ISFET has a negative temperature co-efficient from temperature dependency of  $\beta$ . Threshold voltage is another temperature dependent parameter of ISFET. Previously, we had seen that the threshold voltage of ISFET can be written as [26]-

$$V_{th} = V_{th(MOS)} + V_{chem} \quad , \tag{2.5}$$

where  $V_{chem} = \gamma + 2.303 \alpha U_T pH$ ,  $\gamma$  is a group of pH independent chemical potential,  $\alpha$  is a dimensionless sensitivity parameter and  $U_T = kT/q$  is the thermal voltage i.e. linear function of temperature. Therefore, we can see the threshold voltage of ISFET has positive temperature co-efficient. However, the temperature co-efficient of threshold voltage of MOSFET is negative. Therefore, this two forces work against each other and minimize the impact of temperature variation on threshold voltage of ISFET.

The light sensitivity of ISFET can be explained with that of MOSFET. Similar to MOSFET, there are two photosensitive regions in ISFET which are: reverse biased source and drain p-n junctions and ISFET channel from threshold voltage variation. Simulation results presented in [44] show that light has very minimal influence on ISFET channel and threshold voltage but parasitics reverse saturation current arising from drain-bulk and source-bulk, increases with optical radiation.

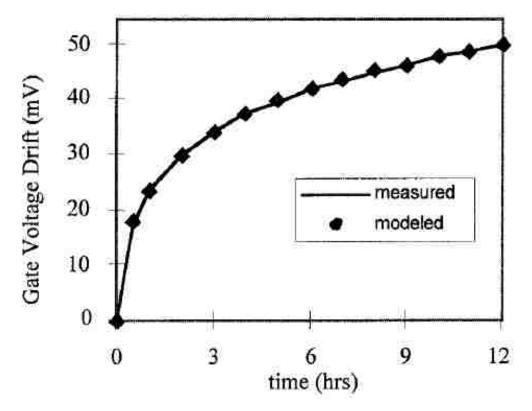

ISFET sensors are prone to drift, which is a temporal shift of the output voltage under constant conditions of temperature, pH value and buffer concentration [45]. Through drift, a sensor can show different behavior at different time and the output of sensor becomes unreliable. This drift effect of ISFET restrict its use in medical field as the accuracy required in biomedical pH sensor is very high i.e. at least 0.03pH within a measuring period of a number of hours. Reference [46] shows that an ISFET with Al<sub>2</sub>O<sub>3</sub> membrane shows a drift of 0.06pH unit during first 4.5 hours and a maximum drift of 0.15pH in 24 hours.

#### 2.3 Avalanche ISFET (A-ISFET)

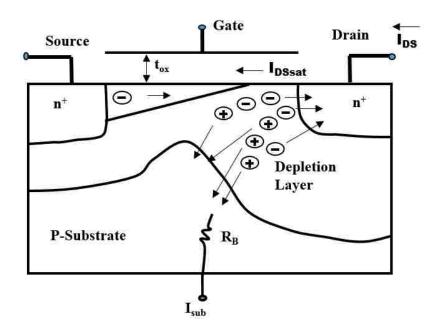

The least explored region of operation for ISFET is the avalanche region. In this region, high velocity carriers are injected in the substrate of the ISFET where they are multiplied by impact ionization. This multiplication of carriers makes the device highly conductive and in a fraction of a nanosecond, a very high current start to flow. The large voltage drops across junction along with large current flow during avalanche can generate enough heat to make the ISFET device dysfunctional. However, an avalanche tolerant device can indefinitely sustain a moderate level of current while on the edge of breakdown. Generally, avalanche operation occurs when the reverse bias voltage of p-n junction approaches the breakdown voltage.

ISFET Operation during Avalanche

Figure 2.11: (a) An ISFET under nominal voltage (b) An ISFET under avalanche breakdown showing impact ionization. [18]

## 2.3.1 Structure and Bias of A-ISFET

The structure of an A-ISFET and the required bias for its avalanche operation is shown in Figure 2.11. A weak chemical signal in a normal ISFET can generate only few electrons or holes. On the other hand, in an avalanche ISFET (A-ISFET) the same weak signal results in a very large current due to carrier multiplication. The detailed phenomenon of avalanche is discussed in following section.

# 2.3.2 Physics of Avalanche operation

The conduction in any electronic materials results from the mobile charge carriers, which are free electrons and free holes. A fixed electron in a reverse-biased junction may break free due to its thermal energy, creating an electron-hole pair. If there is a voltage gradient in the semiconductor, the electron will move towards the positive voltage while the hole will move towards the negative voltage. However, when there is very high voltage gradient in p-n junction the free electrons move fast enough to knock a bound electron and make it free. Through this process, new electron-hole pairs are generated. Similarly, fast moving holes can also create electron-hole pairs as shown in Figure 2.12 [47]. This secondary electron-hole pair may have high energy and can lead to collisions that can generate more electron-hole pair. This carrier creation through impact is known as carrier multiplication. Due to multiplication effect during avalanche, the current through junction increase abruptly. This abrupt increase of current through junction during avalanche might lead to device breakdown. In ISFET devices, the peak of carrier generation is commonly observed in channel near the drain area, as the depletion region width is highest there. Normally, avalanche breakdown is not desirable for electronic devices and must be avoided in order to prevent reliability issues. However, if it occurs under a controlled environment, avalanche multiplication can be extremely useful in achieving large internal gain [18].

## 2.3.3 Failure of A-ISFET

The main reason of A-ISFET failure is the thermal properties of silicon. If not controlled properly, during avalanche operation the junction temperature of ISFET may raise to a point, which may cause failure in metal contacts. This high operating temperature can lead to thermal destruction of the device. From reliability point of view, the operation of A-ISFET beyond rated junction temperature is not recommended.

Figure 2.12: Avalanche Multiplication Process in Semiconductor [47]

27

Failure of A-ISFET from breakdown of the gate oxide can also be a concern as the gate-oxide is scaled down with the scaling of the CMOS process. Higher fields in the oxide increase the tunneling of carriers from the channel into the oxide. These carriers slowly degrade the quality of the oxide and lead them to failure over time. Use of high-k dielectric materials, allow us to have thicker oxide layer and to avoid oxide degradation from tunneling of carriers.

### 2.4 ISFET Sensor: Sensitivity

From earlier discussion, we can say that the current through drain-source of ISFET can be modeled with that of MOSFET. Similar to MOSFET, the drain-source current of ISFET strongly depends on the  $V_{GS}$  and  $V_{DS}$  bias voltages. The operating region of ISFET, based on the magnitude of bias voltages, can be differentiated into three regions, which are: i) Cut-off ii) Linear and iii) Saturation.

The following section will discuss on the ISFET operation and sensitivity at different operating region. We can define the sensitivity of an ISFET ( $S_{ISFET}$ ) as the change of ISFET current due to the change of gate liquid pH i.e. ISFET ability to detect pH change [13]. It can be quantified as below -

$$S_{ISFET} = \frac{\Delta I_{DS}}{\Delta pH} = \frac{\Delta V_{GS}}{\Delta pH} \cdot \frac{\Delta I_{DS}}{\Delta V_{GS}} = \left(\frac{\Delta V_{GS}}{\Delta pH}\right) g_m.$$

(2.6)

Figure 2.13: Voltage-to-current sensitivity of an ideal ISFET [13]

# 2.4.1 Normal Operation Mode

An ISFET operates in cutoff region when  $V_{GS} < V_T$ . At cutoff region of operation, both the current and change of current for ISFET is zero. Hence, this region is not suitable for operation of ISFET as sensor.

On the other hand, linear operating region of ISFET is dictated by the bias conditions  $V_{DS} < V_{GS}-V_T$  and  $V_{GS}>V_T$ . At linear operating region, the current and change of ISFET current ( $\Delta I_{DS}/\Delta V_{GS}$ ) can then be modeled as-

$$I_{DS} = \mu_n C_{ox} \frac{W}{L} \left[ (V_{GS} - V_T) V_{DS} - \frac{1}{2} V_{DS}^2 \right] = K_{n'} \frac{W}{L} \left[ (V_{GS} - V_T) V_{DS} - \frac{1}{2} V_{DS}^2 \right],$$

(2.7)

and

$$\left|\frac{dI_{DS}}{dV_{GS}}\right| = \left|\frac{dI_{DS}}{dV_T}\right| = \mu_n C_{ox} \frac{W}{L} V_{DS} = K_{n'} \frac{W}{L} V_{DS} \quad , \qquad (2.8)$$

where  $\mu_n$  is the mobility of electron,  $C_{ox}$  is the capacitance per unit area of the gate insulator,  $V_{DS}$  is drain to source bias voltage of ISFET, W is the channel width, L is the channel length and  $K_{n'}$  is the current driving capacity of an ISFET.

Based on (2.8), we can say that the change of ISFET current at linear region is a linear function of the voltage of  $V_{DS}$  but it is independent of  $V_{GS}$  and  $V_T$  voltages.

However, at saturation region, dictated by bias conditions  $V_{DS} => V_{GS}$ - $V_T$  and  $V_{GS} > V_T$ , ISFET current and change of ISFET current ( $\Delta I_{DS} / \Delta V_{GS}$ ) can be modeled by:

$$I_{DS} = \mu_n C_{ox} \frac{W}{2L} [(V_{GS} - V_T)]^2 = K_n \frac{W}{2L} [(V_{GS} - V_T)]^2, \qquad (2.9)$$

and

$$\left|\frac{dI_{DS}}{dV_{GS}}\right| = \left|\frac{dI_{DS}}{dV_T}\right| = \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_T) = K_n \frac{W}{L} (V_{GS} - V_T)$$

(2.10)

Equation (2.10) shows that at saturation region the change of ISFET current is independent of the voltage of  $V_{GS}$  but it is linearly dependent on  $V_{GS}$  and  $V_T$  voltages. We can also see from (2.8) and (2.10) that the effect of threshold voltage change (i.e. pH change) on ISFET current is same as of  $V_{GS}$  voltage change.

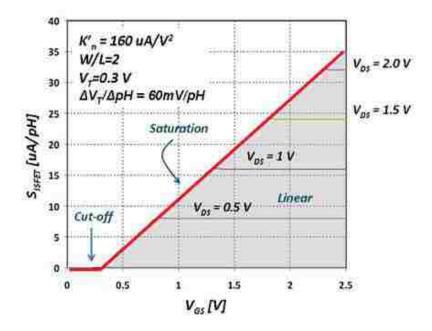

If we use  $Ta_2O_5$  as interface material in ISFET gate, we can achieve a threshold voltage change of around 60mV for every unit of pH change [34]. Therefore, the sensitivity variation of ideal ISFET with pH change will become as shown in Figure 2.14. We can achieve a sensitivity of around 35uA/pH for this ideal ISFET with W/L=2, V<sub>T</sub>=0.3 V and K<sub>n</sub>:=160uA/V<sup>2</sup>. However, the sensitivity from a non-ideal, real ISFET is normally lower than that is shown in Figure 2.14.

Figure 2.14: pH-to-current sensitivity of an ideal ISFET [13]

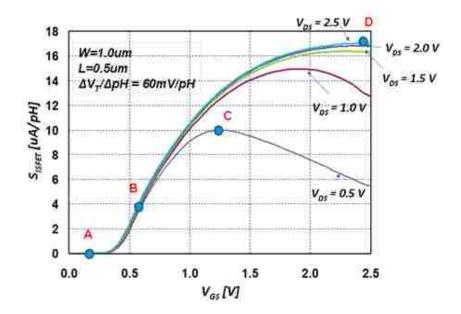

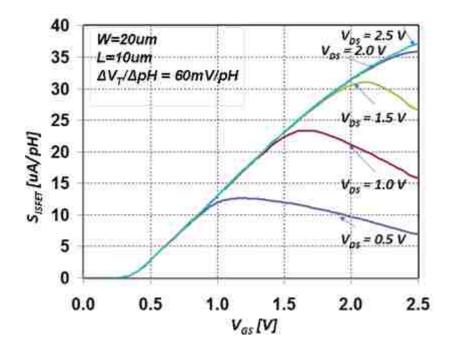

We have simulated an N-ISFET device with W/L=2 in SPICE to see its sensitivity variation with bias using TSMC's 0.25um technology model files. The sensitivity response of the short and long channel ISFETs are shown in Figure 2.15 and Figure 2.16 respectively. The sensitivity variation of long channel ISFET at saturation region follows the ideal ISFET sensitivity variation in Figure 2.14. However, the sensitivity of short channel ISFET degrades with the increase of V<sub>DS</sub> voltage and it becomes saturated due drain-induced barrier lowering (DIBL) and channel length modulation effects. At high V<sub>GS</sub> voltage, the sensitivity goes down due to mobility degradation of carrier in channel from carrier crowding.