### University of New Mexico UNM Digital Repository

Electrical and Computer Engineering ETDs

**Engineering ETDs**

6-26-2015

# Variation Tolerant Energy Efficient Design For Ultra Low Voltage Digital Circuits

Preyom Dey

Follow this and additional works at: https://digitalrepository.unm.edu/ece\_etds Part of the <u>Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

Dey, Preyom. "Variation Tolerant Energy Efficient Design For Ultra Low Voltage Digital Circuits." (2015). https://digitalrepository.unm.edu/ece\_etds/70

This Thesis is brought to you for free and open access by the Engineering ETDs at UNM Digital Repository. It has been accepted for inclusion in Electrical and Computer Engineering ETDs by an authorized administrator of UNM Digital Repository. For more information, please contact disc@unm.edu.

Preyom Kanti Dey

Candidate

Electrical and Computer Engineering

Department

This thesis is approved, and it is acceptable in quality and form for publication:

Approved by the Thesis Committee

Dr. Payman Zarkesh-Ha, Chairperson

Dr. Ganesh Balakrishnan

Dr. Ashwani K. Sharma

# VARIATION TOLERANT ENERGY EFFICIENT DESIGN FOR ULTRA LOW VOLTAGE DIGITAL CIRCUITS

by

#### PREYOM KANTI DEY

#### B.S., ELECTRONICS AND TELECOMMUNICATION ENGINEERING, NORTH SOUTH UNIVERSITY, 2009

THESIS Submitted in Partial Fulfillment of the Requirements for the Degree of

#### **Master of Science**

**Electrical Engineering**

The University of New Mexico Albuquerque, New Mexico

May, 2015

# Dedication

To my Parents.....

For their support and sacrifices

# Acknowledgement

First of all, I would like to express my special gratitude to my honorable advisor Professor Dr. Payman Zarkesh-Ha, for his endless hours of help, suggestions, ideas, advice and proper guidance throughout the whole time of my thesis. Working with Dr. Payman Zarkesh-Ha, has been a true privilege for me. His exceptional knowledge in electrical engineering area and extraordinary capability to explain difficult concepts clearly and simply has benefited me tremendously during my graduate study. He is a role model that I can always look up to. I am really thankful to him for teaching me the art of research.

My wholehearted thanks to Dr. Ganesh Balakrishnan and Dr. Ashwani K. Sharma for their time and accepting to be the member of my defense committee. Their valuable advice and suggestions on my research work has helped me a lot to improve the quality of my research work.

Most importantly, my deepest thank to my family members and friends. It would have not been possible for me to complete my thesis without their endless support and motivation. Their constant encouragement helped me to find ways even out of seeming dead-ends. My special thanks to Mr. Saadat Md. Mishkat-Ul Masabih and Mr. Pankaz Das.

Lastly, I like to express my sincerest gratitude to Almighty God for bestowing blessings upon me.

# Variation Tolerant Energy Efficient Design For Ultra Low

**Voltage Digital Circuits**

by

Preyom K. Dey

B.S., Electronics and Telecommunication Engineering, North South University,2009 M.S., Electrical Engineering, University of New Mexico, 2015

# Abstract

The demand of extremely long battery life for electronic devices is the driving force for modern semiconductor industry in recent years. Supply voltage scaling offers a promising solution for this matter. To control the energy consumption and limit the power dissipation of a circuit, supply voltage should be scaled continually. Threshold voltage should also be reduced to sustain performance and reliability. This scaling of supply and threshold voltage imposes several bottlenecks in ultra-low voltage circuit design.

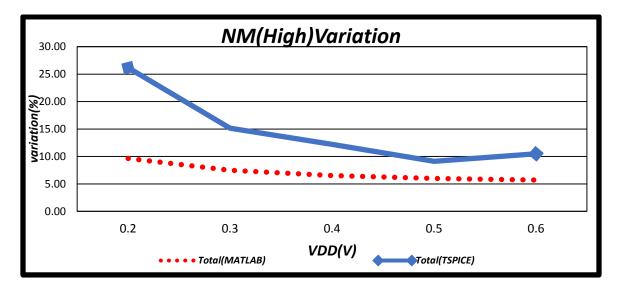

One of the major barriers for ultra-low voltage design is the performance deviation of digital circuit due to supply voltage variation. As technology scales, channel length, width and threshold voltage variation of the device during processing, also effect the digital circuit's characteristics. In this thesis, analytical models are derived to study the impact of process parameters and supply voltage variations on digital circuit. Based on these models, a projected 22nm process technology is used to examine the effects of device parameter variation on ultra-low voltage digital circuit's dynamic and static behaviors. High to low propagation delay variation and noise margin (high and low) variation of an inverter are investigated. Analytical simulation results are compared with T-Spice simulation as well to verify the accuracy of the analytical models. Monte Carlo method is used on a set of 1000 samples for T-Spice simulation. Results obtained by implementing our analytical models in MATLAB are similar to the T-Spice simulation results. Both simulation results confirm that the reduction of supply voltage increases the delay and noise margin variations in an inverter circuit. Noise margin (high) variation in an inverter is more sensitive to the process related issues than noise margin (low) variation.

Another most important challenge for ultra-low voltage circuit design is to reduce the sub-threshold leakage power. A new circuit level design technique is presented in this thesis to tackle this issue. This technique allows bulk CMOS circuits to work in the sub-0.6V supply territory. The new design technique is compared with two existing leakage power reduction techniques. T-Spice simulation results suggest that, our new design can reduce the leakage power without compromising the delay of the circuit significantly. Also, our new proposed energy efficient design is more tolerant to process parameters and supply voltage variation effects. In the case of noise margin (high and low) of an inverter circuit, this new design technique is more beneficial to use than the conventional design.

# **Table of Contents**

| Dedicationiii                                        |

|------------------------------------------------------|

| Acknowledgement iv                                   |

| Abstractv                                            |

| List of Figures x                                    |

| List of Tables xiii                                  |

| Chapter 1 1                                          |

| Introduction1                                        |

| 1.1 Background1                                      |

| 1.2 Motivation                                       |

| 1.3 Our Goal                                         |

| 1.4 Thesis Outline7                                  |

| Chapter 2 8                                          |

| Ultra Low Voltage Circuit Design 8                   |

| 2.1 Introduction                                     |

| 2.2 Device and Circuit Characteristics               |

| 2.3 Power Consumption 12                             |

| 2.4 Leakage Components 14                            |

| Chapter 3 18                                         |

| Process Parameter Variation on Mixed Signal Circuits |

| 3.1 Introduction                                     |

| 3.2 Variation Categories                             |

| 3.3 Sources of variation                                 |    |

|----------------------------------------------------------|----|

| 3.3.1 Random Dopant Fluctuation                          |    |

| 3.3.2 Critical Dimension Variation                       | 24 |

| 3.3.3 Line Edge Roughness                                |    |

| 3.3.4 Oxide Thickness variation                          |    |

| 3.3.5 Mobility Variation                                 |    |

| 3.3.6 Supply Voltage Variation                           |    |

| Chapter 4                                                |    |

| Analytical Models                                        |    |

| 4.1 Introduction                                         |    |

| 4.2 Device Variation Map                                 |    |

| 4.2.1 Assumptions                                        |    |

| 4.2.2 Derivations                                        |    |

| 4.3 Low Voltage digital circuits under device variations |    |

| 4.3.1 Propagation Delay                                  |    |

| 4.3.1.1 Ideal Square Wave (rise time=0)                  |    |

| 4.3.1.2 Non-ideal Square Wave (rise time≠0)              |    |

| 4.3.1.3 Effect of input rise time in delay variation     |    |

| 4.3.2. Nosie Margin:                                     | 53 |

| 4.3.2.1 Noise Margin(Low State) variation                | 54 |

| 4.3.2.2. Noise Margin(High State) variation              | 63 |

| Chapter 5                                                | 73 |

| Ultra Low Voltage Circuit Design Technique               | 73 |

| 5.1 Introduction                                         | 73 |

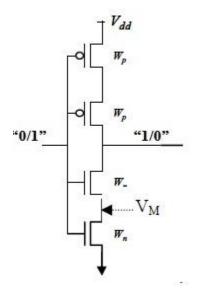

| 5.2 Dynamic Threshold CMOS(DTCMOS)                       | 74 |

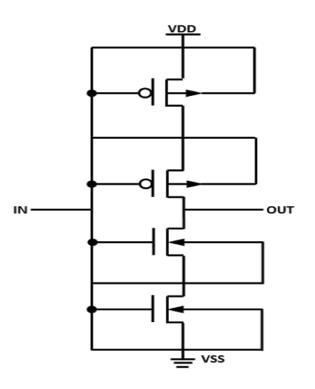

| 5.3 Transistor Stacking:                             | 75 |

|------------------------------------------------------|----|

| 5.4 Transistor Stacking with DTCMOS(New Design)      | 77 |

| 5.5 Simulation Results                               | 78 |

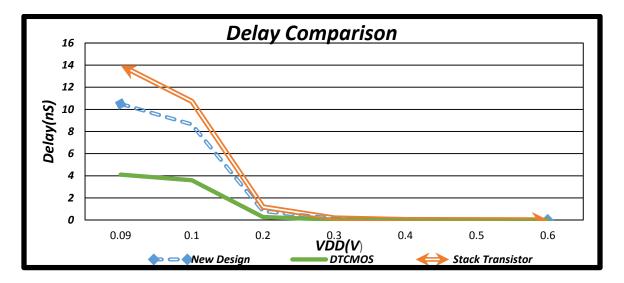

| 5.5.1 Delay Comparison (t <sub>pHL</sub> )           | 79 |

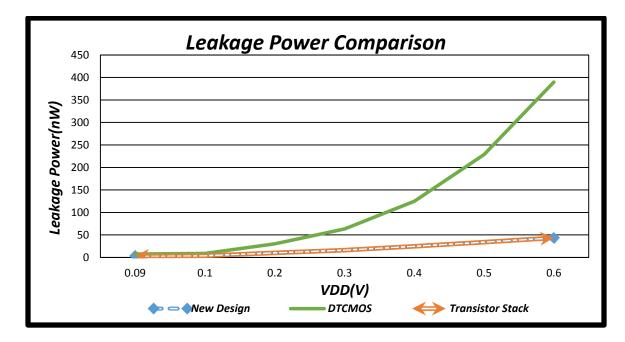

| 5.5.2 Leakage Power and Energy Comparison            | 80 |

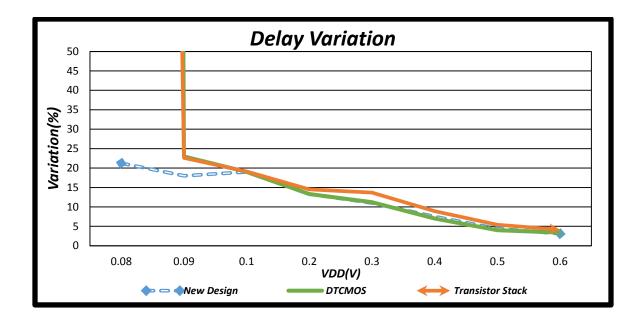

| 5.5.3 Delay (t <sub>pHL</sub> ) variation comparison | 82 |

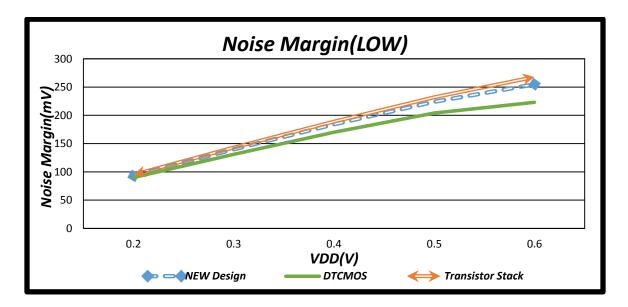

| 5.5.4 Noise Margin (Low state) comparison            | 84 |

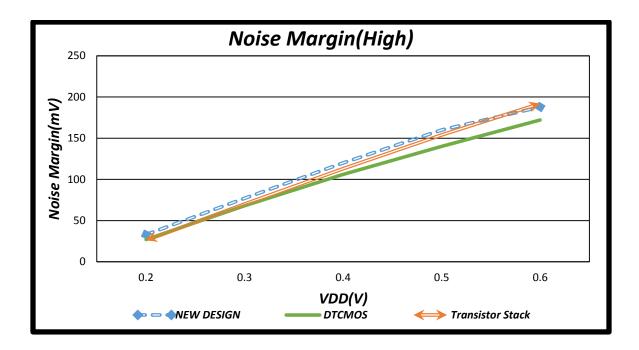

| 5.5.5 Noise Margin (High state) comparison           | 85 |

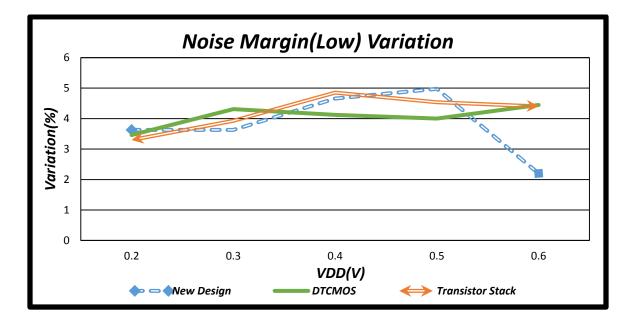

| 5.5.6 Noise Margin (Low State) variation comparison  | 87 |

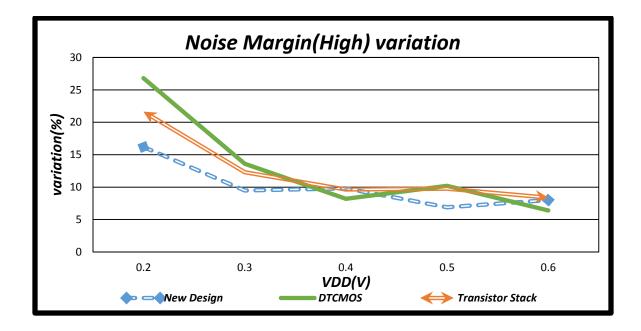

| 5.5.7 Noise Margin (High State) variation comparison | 88 |

| Chapter 6                                            | 91 |

| Conclusion and Future Work                           | 91 |

| 6.1 Conclusion                                       | 91 |

| 6.2 Future Work                                      | 93 |

| References                                           | 94 |

# List of Figures

| 1.1 Measured $I_{on}$ versus $I_{off}$ scatter plot showing large spread in $I_{off}$ for a 0.15 $\mu$ m                            |

|-------------------------------------------------------------------------------------------------------------------------------------|

| technology4                                                                                                                         |

| 2.1 Power Consumption in an inverter                                                                                                |

| 2.2 Leakage Components in a Transistor                                                                                              |

| 3.1 Variation categories of a circuit                                                                                               |

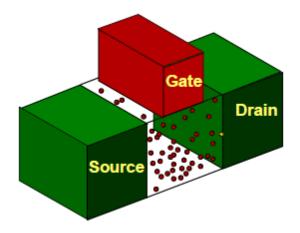

| 3.2 Three-dimensional bird's-eye view of planar bulk MOSFET with randomly distributed dopants in the channel region                 |

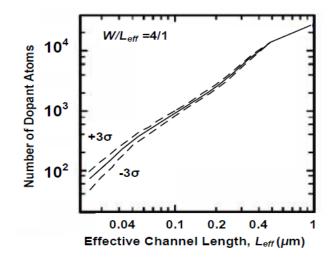

| 3.3 Number of dopant atoms in a depletion layer of a MOSFET vs. effective channel length                                            |

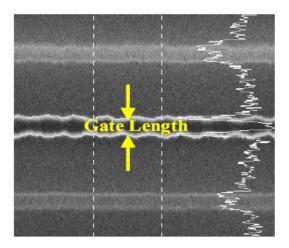

| 3.4 Line edge rougness due to lithography variation                                                                                 |

| 4.1 Device variation map on a 65nm NMOS I-V characteristics using experimental                                                      |

| data                                                                                                                                |

| 4.2 Projected Device Variation map for PTM's 22nm NMOS Device                                                                       |

| 4.3 The I-V trajectory of an NMOS in an inverter under different supply voltages using                                              |

| PTM's 22nm device parameters                                                                                                        |

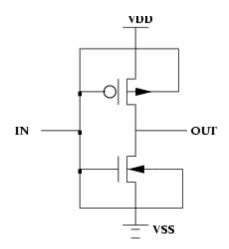

| 4.4 An Inverter circuit                                                                                                             |

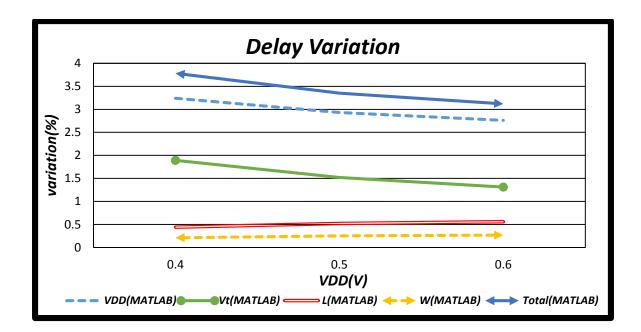

| <ul><li>4.5 Delay variation versus supply voltage for an inverter in PTM's 22nm technology node(Velocity Saturation)</li></ul>      |

| <ul><li>4.6 Delay variation versus supply voltage for an inverter in PTM's 22nm technology node (Saturation)</li></ul>              |

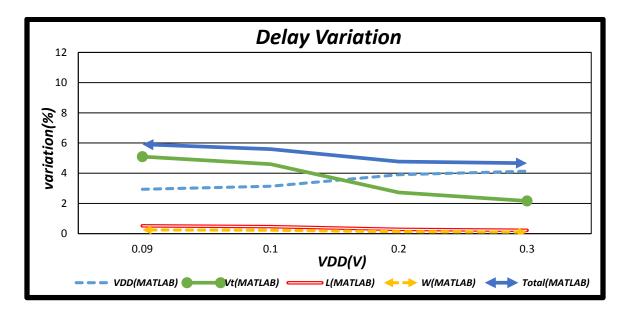

| <ul><li>4.7 Delay variation versus supply voltage for an inverter in PTM's 22nm technology node (Sub-threshold operation)</li></ul> |

| <ul><li>4.8 Delay variation versus supply voltage for an inverter in PTM's 22nm technology node. (Velocity saturation)</li></ul> |

|----------------------------------------------------------------------------------------------------------------------------------|

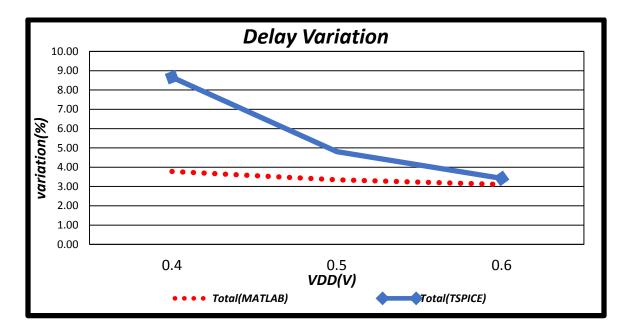

| 4.9 Delay variation comparison for an inverter (Velocity Saturation)                                                             |

| 4.10 Delay variation versus supply voltafe for an inverter in PTM's 22nm technology                                              |

| node. (Saturation)                                                                                                               |

| 4.11 Delay variation comparison for an inverter (Saturation)                                                                     |

| 4.12 Delay variation verusus supply voltage for an inverter in PTM's 22nm technology                                             |

| node. (Sub-threshold)                                                                                                            |

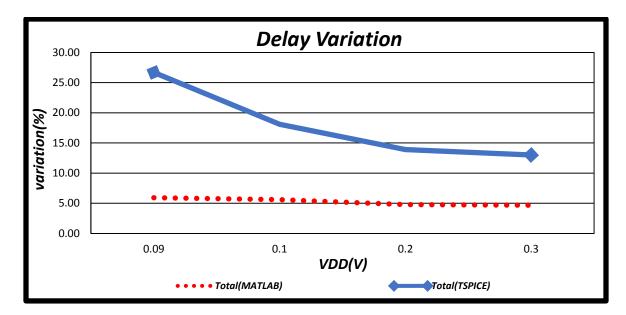

| 4.13 Delay variation comparison for an inverter (Sub-threshold)                                                                  |

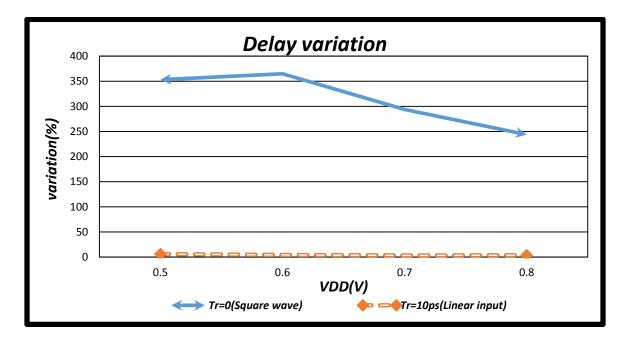

| 4.14 Effects of input rise time on delay $(t_{pHL})$ variation                                                                   |

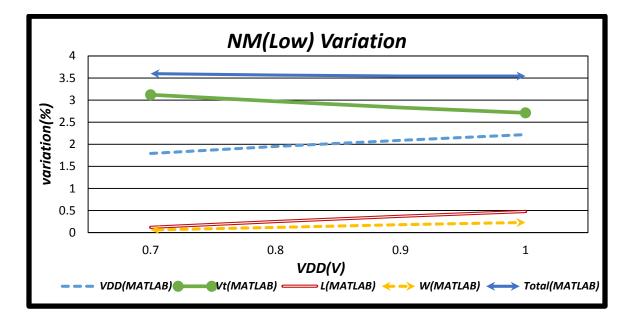

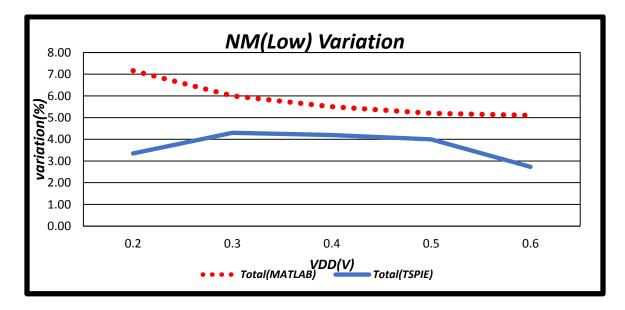

| 4.15 Noise Margin (Low state) versus supply voltage for an inverter in PTM's 22nm node (Super-threshold)                         |

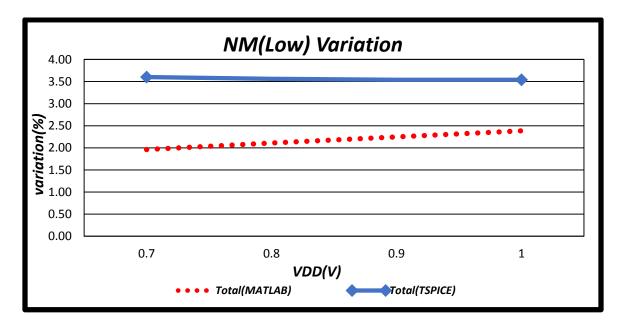

| 4.16 Noise Margin (Low State) variation comparison for an inverter (Super-threshold)                                             |

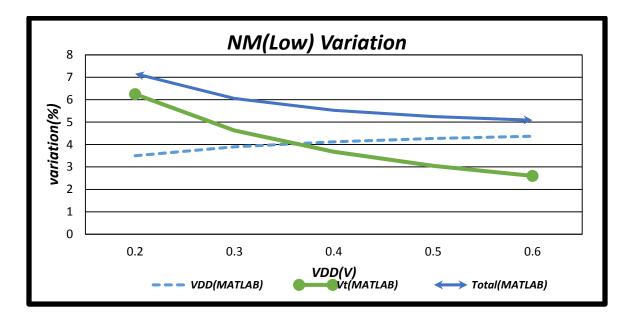

| 4.17 Noise Margin (Low state) versus supply voltage for an inverter in PTM's 22nm technology node (Sub-threshold)                |

| 4.18 Noise Margin(Low State)variation comparison for an inverter (Sub-threshold)                                                 |

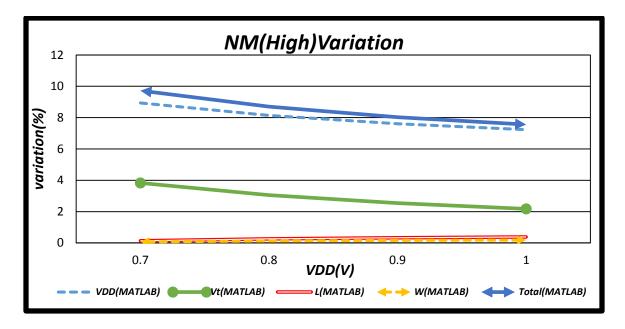

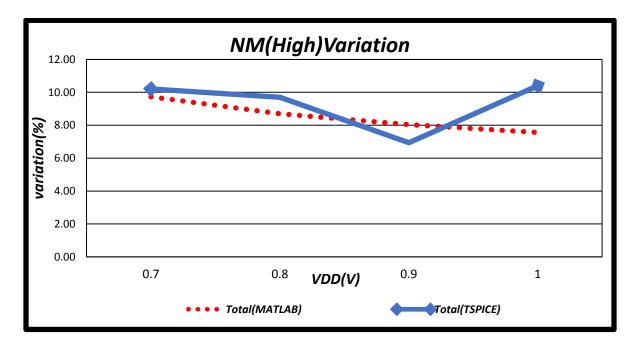

| 4.19 Noise Margin (High State) variation comparison for an inverter (Super-threshold)<br>                                        |

| 4.20 Noise Margin(High State) variation comparisonof an inverter (Super-threshold).                                              |

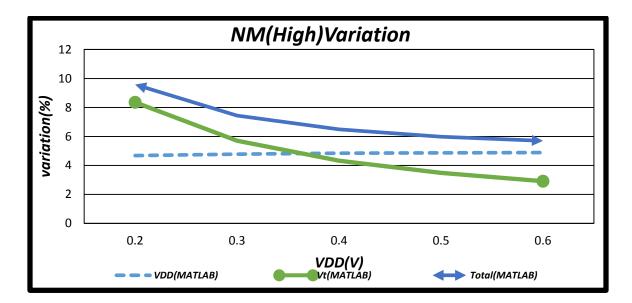

| 4.21 Noise Margin (High State) versus supply voltage for an inverter in PTM's 22nm technology node. (Sub-threshold)              |

| 4.22 Noise Margin (High State) variation comparison for (Sub-threshold)71                                                        |

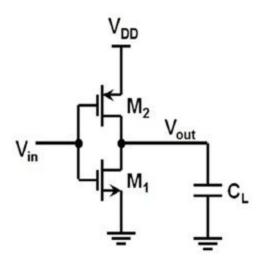

| 5.1 Schematic of DTCMOS inverter                                                                                                 |

| 5.2 Schematic of inverter with transistor stack                                                                                  |

| 5.3 Schematic of an inverter with DTCMOS transistor stack                                 |

|-------------------------------------------------------------------------------------------|

| 5.4 Delay $(t_{pHL})$ comparison for different leakage reduction techniques               |

| 5.5 Leakage Power comparison for different leakage reduction techniques                   |

| 5.6 Delay ( $t_{pHL}$ ) variation comparison for different leakage reduction techniques83 |

| 5.7 Noise Margin(Low State)comparison for different leakage reduction techniques.84       |

| 5.8 Noise Margin(High State)comparison for different leakage reduction techniques.86      |

| 5.9 Noise Margin (Low State) variation comparison for different techniques                |

| 5.10 Noise Margin (High State) variation comparison for different techniques89            |

# List of Tables

| 4.1 The PTM's 22nm CMOS Device Parameters                                                             |

|-------------------------------------------------------------------------------------------------------|

| 4.2 Comparison of T-Spice and MATLAB simulation results for delay variation.<br>(Velocity saturation) |

| (Velocity saturation)                                                                                 |

| 4.3 Comparison of T-Spice and MATLAB simulation results for delay variation.                          |

| (Saturation)                                                                                          |

| 4.4 Comparison of T-Spice and MATLAB simulation results for delay variation.                          |

| (Sub-threshold)                                                                                       |

| 4.5 Operational region of transistors in an inverter ( $V_{DD} \ge V_t$ )                             |

| 4.6 V <sub>iL</sub> values of an inverter (Super-threshold)                                           |

| 4.7 Comparison of T-Spice and MATLAB simulation results for noise margin                              |

| (Low state) variation. (Super-threshold)                                                              |

| 4.8 Comparison of T-Spice and MATLAB simulation results for noise margin                              |

| (Low state) variation. (Sub-threshold)                                                                |

| 4.9 <i>V<sub>iH</sub></i> values of an inverter (Super-threshold)                                     |

| 4.10 Comparison of T-Spice and MATLAB simulation results for noise margin (High                       |

| State) variation (Super-threshold)67                                                                  |

| 4.11 Comparison of T-Spice and MATLAB simulation results for noise margin (High                       |

| State) variation. (Subthreshold)71                                                                    |

| 5.1 Delay ( $t_{pHL}$ ) values of an inverter for different circuit techniques                        |

| 5.2 Leakage power of an inverter for different circuit techniques                                     |

| 5.3 Delay ( $t_{pHL}$ ) variation comparison for different leakage reduction techniques83             |

| 5.4 Noise margin (Low State) comparison for different leakage reduction techniques  |

|-------------------------------------------------------------------------------------|

|                                                                                     |

| 5.5 Noise margin (High State) comparison for different leakage reduction techniques |

|                                                                                     |

| 5.6 Noise margin (Low State) variation comparison for different leakage reduction   |

| techniques                                                                          |

| 5.7 Noise margin (High State) variation comparison for different leakage reduction  |

| techniques                                                                          |

# Chapter 1

#### Introduction

#### **1.1 Background**

As technology advances, our daily lifestyle becomes significantly dependent on the success of semiconductor industry. Computer, cell phone and other home appliances, all have complicated integrated circuits. Some of our regular use electronic devices such as modern cellular phones have functionality even more than the early decade's computers, even though their supplies comes from a battery. This passage was started in 1958, when first integrated circuit was invented. From then number of transistors on a single chip is doubled in every two or three years. In 1965, Gordon Moore showed that for any MOS transistor technology there exists a minimum cost that maximizes the number of components per integrated circuit [1]. He also predicted that as transistor dimensions are shrunk from one technology generation to the next, the minimal cost point allows doubling the number of transistors every two to three years [1]. Historically, technology scaling resulted in scaling of vertical and lateral dimensions by 0.7x each generation resulting in delay of the logic gates to be scaled by 0.7x and the integration density of logic gates to be increased by 2x [2]. Tremendous shift in the integrated circuits occurred in 1970's and 1980's, like the transitions from bipolar to PMOS, NMOS and CMOS technologies. In recent years, the number of transistors on microprocessor chips has grown at a faster rate with increasing use of on-chip cache memory, which is rising above billion-transistor

level. Ultra-modern embedded devices have continuously overcome postulated limits to technological progress. Therefore, transistors are now being manufactured with gate dimensions well below 100nm [3]. Electronic market predicts that this incredible success of the VLSI industry will be more rapid in near future.

This continuous progress of modern technologies has directed us to an era of mobile battery powered portable devices. As the success of semiconductor industry continues, extensive battery life of such popular mobile battery powered devices starts to demand more attention. The ultimate goal in design is close to having battery-less systems, because the battery contributes greatly to volume and weight. Solar power, fuel cells, and RF power are the most viable alternatives [4].One of the major challenges that circuit designers are facing in recent time is to design today's mobile battery powered electronic circuits with limited energy. And this stringent energy budget will be the major driving force for upcoming CMOS technologies. This fastest growing popularity of battery powered devices has forced the academic and industrial researchers to focus more deeply, not only just on low energy operation but also on performance and size of such devices, at the same time.

As research in ultra-low power circuit design proceeds further, supply voltage scaling becomes a more promising solution to this above mentioned power management problem. This technique gives a quadratic reduction of dynamic power. One field that is gaining interest and attraction among both corporate and scientific institutions is the concept of ultra-low power (ULP) or ultra-low energy design, which is equivalent to ultra-low voltage (ULV) design because of the relationship between power consumption or energy and voltage. This design methodology is also known as sub-threshold or near-

threshold design because the supply voltage is often lowered to values below or near the absolute value of the transistor's threshold voltage [5].

#### **1.2 Motivation**

Low power dissipation is attractive, and perhaps even essential in portable applications to have reasonable battery life and weight [4].Aggressive supply voltage scaling is the pioneer solution for soaring amount of power dissipation of an integrated circuit. However, this reduced power consumption is achieved at the expense of decreased performance. For many applications this performance reduction penalty is tolerable. For instance a significant performance penalty can be tolerated in sensor devices, energy harvesting imaging systems, and medical devices without compromising the usefulness of such devices [6]. However, for some applications performance is a critical issue. To improve performance, threshold voltage of the transistor is reduced too.

On the other hand, threshold voltage scaling results in substantial increase in the sub-threshold leakage current. As the threshold voltage decreases, sub-threshold leakage current exponentially increases [1]. Due to the substantial increase in the leakage current, the static power consumption is expected to exceed the switching component of the power consumption unless effective measures are taken to reduce the leakage power [7]. Since threshold voltage and supply voltage of a transistor are expected to be scaled regularly from one technology to another, the situation will become more deteriorated as CMOS technology proceeds further.

As number of transistors are doubled in each generation, not only billions of parasitic capacitances are charging and discharging at a high rate, but also leakage power density is becoming extreme. Heat dissipation of modern processors is reaching the level of a hot plate. Chip temperature has reached unprecedented levels requiring expensive packaging and heat dissipation technique. Serious reliability issues arise when working at such high temperatures [1].

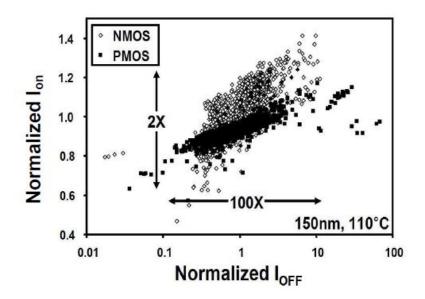

Another major bottleneck for ultra-low voltage operation is imposed by the process–related variation. This is mainly because leakage current strongly depends on process–related variations. For example, a slight change in sub-threshold voltage due to process variations can make severe spread in leakage current, since sub-threshold leakage current relies exponentially on threshold voltage. Fig. 1.1 shows measured I<sub>on</sub> and I<sub>off</sub> scatter plot for a 150nm technology [8].Even in that mature technology, there is an excessively large spread in I<sub>off</sub> (100x) as compared to the 2x spread in I<sub>on</sub> [9].

Figure 1.1: Measured I<sub>on</sub> versus I<sub>off</sub> scatter plot showing large spread in I<sub>off</sub> for a 0.15µm technology [8]

This process related variation is predicted to increase with technology scaling. One of the main reasons of this process related variation is subwavelength lithography [9]. Extreme sensitivity to device variations in low voltage electronics has made design of such systems extremely complicated [6]. Presently used nanometer scaled circuits are fundamentally different from their predecessor technologies in that they are subject to a wide range of new effects that induce on-chip variations. The effects of variability in nanometer-scale integrated circuits cause significant deviations from the prescribed specifications for a chip. The magnitudes of these deviations, together with tight performance specifications, imply that variability is an increasingly vexing problem as technologies continue to scale [10].

Analog design was suffering from this variation issue for some time, and now it is not alone anymore; digital design is also impacted significantly in nanometer technology nodes. Process variations strongly impact different aspects of digital circuit operation. For example, in random logic, the overdrive voltage ( $V_{DD}-V_{th}$ ) becomes unpredictable even for neighboring identically-sized transistors. As a result, the gate delay becomes a stochastic random variable, which complicates timing closure techniques [11-13]. Functional reliability is a major concern for circuits operating in ultra-low voltage. Yield loss probability increases and manufacturing cost due to low yield increases as a consequence. That is why it is very important to design circuit efficiently.

Another motivation for variation tolerant energy efficient design is that, the information technology industry council estimated that electricity consumption of computers in the U.S. was about 13% of the total power in 1998 with an annual growth of 2-3% [1,14].

Due to all these concerns, designing a variation tolerant, energy efficient, ultra-low voltage circuit with high yield, is the most challenging task for semiconductor industry in recent time. An ultra-low voltage circuit with lesser sub-threshold leakage current and more tolerable to process related variation facilitates competitive cost-to-performance ratio for electronic equipment.

#### 1.3 Our Goal

- Neither the ultra-low voltage operation nor the process related variation is a new concept for CMOS logic study. Both of these topics have been addressed in several studies with high importance. But the effect of process related variability on ultra-low voltage circuit is not fully analyzed. Our primary goal is to derive analytical model to study the impact of device parameter variations on low-voltage digital circuits. A projected 22nm process technology is used to serve our purpose. For digital circuit, delay (t<sub>PHL</sub>) variation and noise margin (NM<sub>H</sub> and NM<sub>L</sub>) variation of an inverter are considered. To analyze the effects of parameter variation, we have focused mainly on length, width, threshold voltage and supply voltage variations of a circuit.

- Our second goal is to design a more energy efficient digital logic circuit. This technique which is examined on an inverter, will not only be benefited in terms of reduced leakage power but also will be more resistant to the effects of process related variations.

#### **1.4 Thesis Outline**

This thesis is organized as follows:

- Chapter 2, presents a brief description about device and circuit characteristics at ultra-low voltage operations. Different sources of leakage current are discussed in this chapter.

- Various types of process related variability and their sources are explained in-Chapter 3.

- Then in Chapter 4, analytical models to study the effects of process parameters and supply voltage variations on digital circuit are derived. Results obtained from analytical models are compared with the T-Spice simulations in this chapter.

- We present our new design technique to reduce leakage power and parameter variation effect for digital circuit in Chapter 5. Some existing leakage power reduction techniques for digital circuits are also discussed in this chapter. Comparison results between new design and existing design techniques are presented in the latter half of Chapter 5.

- Finally, conclusions and future research directions are highlighted in Chapter 6.

### Chapter 2

### Ultra Low Voltage Circuit Design

#### **2.1 Introduction**

In order to increase the performance and density of transistors in an integrated circuit, CMOS devices have been scaled for more than 30 years by following Gordon More's Law. As a result, performance of microprocessors has been doubling in every two years. It is expected that for each technology generation, the delay time of a transistor will be reduced by more than 30% from its previous one. As the number of transistors on the chip becomes double, power dissipation per area increases. It is projected that by 2020, we will have one trillion transistors on a single chip [1]. Energy consumption becomes a major issue for nanometer CMOS circuits as technology progresses. To control energy consumption, supply voltage ( $V_{DD}$ ) has been scaled down too in every new technologies.

The terms *low power-* and *low energy-* serves to reach the same goal, although their definitions are different. An energy efficient circuit means a low power consuming circuit also. In this paper, our main emphasis will be to reduce the power consumption of the circuit, which will in turns fulfill one of our primary goals of designing an energy efficient digital circuit.

#### 2.2 Device and Circuit Characteristics

To minimize energy per operation and to achieve low power consumption for digital circuits  $V_{DD}$  is reduced. MOFETs then switch their operations from super-threshold  $(V_{DD} > V_t)$  operation in strong inversion with large gate overdrives, to near-threshold  $(V_{DD} \approx V_t)$  operation in weak inversion with very small overdrives, and finally into subthreshold  $(V_{DD} < V_t)$  operation. Primary difference between super-threshold and subthreshold operation is 'on' current  $(I_{on})$ . In sub-threshold region 'on' current  $(I_{on-sub})$ depends exponentially on threshold voltage  $(V_t)$  and power supply voltage  $(V_{DD})$ .On the other hand, super-threshold operation 'on' current  $(I_{on-super})$  is dependent on  $V_{th}$  and  $V_{DD}$ linearly (approximately).On current for super-threshold  $(I_{on-super})$  in general (not considering short channel effect and channel length modulation effect) is as follows [6] :

$$I_{On-super} = \mu C_{OX} \left(\frac{W}{L}\right) \left\{ (V_{GS} - V_t) V_{min} - \frac{V_{min}^2}{2} \right\}$$

(2.1)

Where  $V_{min}=min \{(V_{GS}-V_t), V_{DS}, V_{DSAT}\}, V_{DSAT}$  is the drain-source voltage under velocity saturation. Now, on current for sub-threshold  $(I_{on-sub})$  in general (not considering short channel effect and channel length modulation effect) is as follows [7]:

$$I_{On-sub} = \mu C_{OX} \left(\frac{W}{L}\right) (m-1) V_{TH}^{2} \exp\left(\frac{V_{GS}-V_{t}}{mV_{TH}}\right) \left\{1 - \exp\left(\frac{-V_{DS}}{V_{TH}}\right)\right\}$$

(2.2)

$$m = 1 + \frac{c_{dm}}{c_{ox}} = 1 + \frac{\frac{\varepsilon_{si}}{w_{dm}}}{\frac{\varepsilon_{ox}}{t_{ox}}} = 1 + \frac{3t_{ox}}{w_{dm}}$$

(2.3)

Here,  $V_t$  is the threshold voltage, and  $V_{TH} = KT/q$  is the thermal voltage. T is temperature, K is Boltzmann's constant, q is the charge of an electron.  $C_{ox}$  is the gate oxide capacitance,  $\mu$  is the zero bias mobility, and m is the sub-threshold swing coefficient.  $W_{dm}$ is the maximum depletion layer width, and  $t_{ox}$  is the gate oxide thickness.  $C_{dm}$  is the capacitance of the depletion layer, and  $C_{ox}$  is the capacitance of the insulator layer, L is the effective gate length. In long channel devices, the sub-threshold current is independent of the drain voltage for  $V_{DS}$  larger than few  $V_{TH}$  [7].

It is important to highlight the implicit  $V_t$  dependence on L in Equation (2.2) because  $I_{on-sub}$  becomes very sensitive to L due to the Vt term. Vt is also dependent on  $V_{DS}$ via drain-induced barrier lowering (DIBL), which plays a role in determining the effect  $V_{DD}$  has on  $I_{on-sub}$  [15].

The exponential sub-threshold  $I_{on-sub}$  sensitivity to  $V_t$  drastically affects circuit behavior. First, the circuit delay and now power also depend exponentially on  $V_t$  and  $V_{DD}$ . More significantly, current matching between two FETs is exponentially dependent on any difference in  $V_t$ . For example, while a reasonable  $6\sigma$  100-mV  $V_t$  mismatch disturbs the FET current ratios by only approximately 1.17x in super-threshold operation, a similar 100-mV  $V_t$  mismatch upsets the current matching by greater than 10x in sub-threshold operation [15]. This extreme sensitivity to  $V_{DD}$  and  $V_t$  presents the most significant challenge to subthreshold and near-threshold circuit functionality [15].

Channel length has a vital impact on sub-threshold current  $I_{on-sub}$ . Threshold voltage of NMOS and PMOS depends on channel length. Therefore, a minor change in gate length value due to process or temperature variation can drastically affect sub-threshold current. For short channel devices, the impact is substantial. In addition, channel length line-width variation leads to a significant disturbance in FETs drive strength matching. This creates a considerable challenge for ultra-low voltage circuit design. This problem is not so severe in the case of super-threshold operation, since current is dependent on threshold voltage either linearly or quadratically. This drive strength mismatch effect can be reduced by increasing the gate length L. However, increased gate length degrades super-threshold performance, whereas subthreshold performance is not affected as severely as super-threshold performance. This is because current can be regained with a small reduction of threshold, with no impact on the  $I_{on}/I_{off}$  ratio. More significantly, the additional capacitive loading associated with increasing gate length is significantly smaller for sub-threshold than it is for superthreshold. Sub-threshold operation at longer L values gives the added advantage of a steeper sub-threshold slope. Similar tradeoffs must also be considered with respect to narrow FET channel widths, W. However, the choice of L and W are greatly affected by the circuit application requirements [15]. Gate oxide thickness plays a key role for subthreshold current. Reducing gate oxide thickness improves sub-threshold slope and increases sub-threshold current noticeably [15].

At the circuit level, lowering of supply voltage below sub-threshold leads to concern about noise margins, and sensitivity to process related variations. For digital CMOS logic circuits, reduction of supply voltage reduces the noise margin significantly. Minor change in process parameters makes significant variations in delay and noise margins, which causes yield loss. In analog circuits, static noise margin (SNR), circuit performance, bandwidth, and voltage swing are also degrades by supply voltage scaling. Although scaling down the threshold voltage of MOSFETs can compensate for this performance loss to some degree, the  $V_t$  scaling will results in increased power dissipation again [16]. This is one of the main bottlenecks in ultra-low voltage design. Following section gives a brief description about power consumption in a sub-threshold circuit and its sources.

#### **2.3 Power Consumption**

Today's design strategies are directed toward achieving higher speed and lower energy consumption. One of the factors which affect these parameters is power dissipation in the circuit. Due to the substantial increase in the leakage current, the static power consumption is expected to exceed the switching component of the power consumption unless effective measures are taken to reduce the leakage power [7]. Reducing power dissipation is a design goal even for non-portable devices since excessive power dissipation results in increased packaging and cooling costs as well as potential reliability problems [17]. Total power consumption in active mode for any circuit is the sum of dynamic and static power consumption. Dynamic power consumption consists of switching power and short circuit power. Therefore, the total power during active mode can be described as follows:

$$P_{Total} = P_{Dynamic} + P_{static}$$

$$= P_{Switching} + P_{Short-Circuit} + P_{static}$$

(2.4)

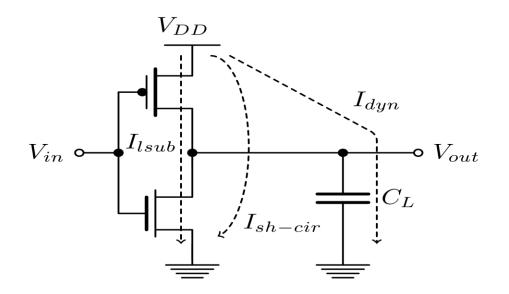

Figure 2.1: Power Consumption in an inverter [5]

Dynamic power occurs from charging and discharging of load and other parasitic capacitances of the circuit. Dynamic power can be estimated by following equation:

$$P_{Dvnamic} = \alpha f C_L V_{DD}^2 \tag{2.5}$$

Where, *f* is the switching frequency,  $C_L$  is the capacitive load,  $V_{DD}$  is the supply voltage and  $\alpha$  is the switching activity factor. Reducing any of these factors will lower the total power consumption of the circuit. Short circuit power occurs because input and output waveforms are not ideally square in real circuits; they have non-zero rise and fall time. Static power is due to non-zero current of NMOS and PMOS in off state in digital circuits or biasing current in analog circuits.  $P_{Short-Circuit}$  is much smaller comparing to the other terms. Therefore, ignoring the short circuit power, the total power for active mode can be approximated as:

$$P_{Total} = \alpha f C V_{DD}^{2} + I_{leak} * V_{DD}$$

(2.6)

and,

$$P_{leak} = I_{leak} * V_{DD} \tag{2.7}$$

Here,  $I_{leak}$  is the summation of all the components of the leakage currents. In the standby mode, the power dissipation is due to the standby leakage current. Different leakage mechanisms contribute to the total leakage in a device. A short description of major leakage mechanisms are described in the next section.

Leakage current (power) increases dramatically in the scaled devices. Particularly, with reduction of threshold voltage (to achieve high performance), leakage power becomes a dominant component of the total power consumption in both active and standby modes of operation. Hence, in order to suppress the power consumption in low-voltage circuits, it is necessary to reduce the leakage power in both the active and standby modes of operation. The reduction in leakage current has to be achieved using both process and circuit-level

techniques. At the process-level, the leakage current reduction can be achieved by controlling the dimensions (length, oxide thickness, junction depth, etc) and doping profile in transistors. At the circuit level, threshold voltage and leakage current of transistors can be effectively controlled by controlling the voltages of different device terminals (drain, source, gate, and body) [7].

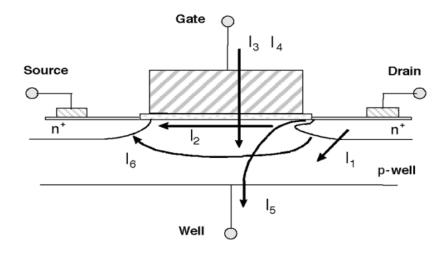

#### 2.4 Leakage Components

Six short-channel leakage mechanisms are illustrated in Fig. 2.2.  $I_1$  is the reverse-bias pn junction leakage;  $I_2$  is the sub-threshold leakage;  $I_3$  is the oxide tunneling current;  $I_4$  is the gate current due to hot-carrier injection;  $I_5$  is the GIDL; and  $I_6$  is the channel punch through current. Currents  $I_2$ ,  $I_5$  and  $I_6$  are off-state leakage mechanisms, while  $I_1$  and  $I_3$  occur in both ON and OFF states.  $I_4$  can occur in the off state, but typically it occurs during the transistor bias states in transition [18].

Figure 2.2 : Leakage Components in a Transistor [18]

- Minority carrier diffusion or drift near the depletion region edge and generation of electron and hole pair in the depletion region of the reversed biased junction together forms the pn junction reverse bias leakage current (*I*<sub>1</sub>) in a MOSFET. *I*<sub>1</sub> is dependent on junction area and doping concentration. Band-to-Band (BTBT) tunneling dominates pn reverse junction leakage current, when heavily doped channels are used.

- Out of these six sources of leakage components, sub-threshold leakage  $(I_2)$  dominates due to the low threshold voltage. It occurs during the off sate of a MOSFET when gate-source voltage  $(V_{GS})$  is less than threshold voltage (Vt) of the MOSFET. Sub-threshold current or the weak inversion current will be the same as of (2.2). In a short channel device, drain bias controls the threshold voltage via band bending over a significant portion of the device. As a consequence, sub-threshold current is a function of drain bias too. This effect is known as Drain Induced Barrier Lowering(DIBL).

- To get control over the gate, gate oxide thickness is reduced. This reduction of gate oxide thickness generates a high electric field across the oxide. Electrons then start to tunnel from substrate to gate and from gate to substrate. This process of tunneling through gate oxide gives rise to a leakage current known as gate oxide tunneling current ( $I_3$ ).

- Due to high electric field near Si/SiO<sub>2</sub> interface of a short channel device, electron and holes gain sufficient energy to cross the interface potential barrier. These carriers then trapped into the oxide layer of the gate. This process is referred as hot carrier injection. The trapped hot electrons

increases the threshold voltage of a short channel device. This phenomenon is more likely for electron than hole. The current associated for this process is called the gate leakage current due to hot carrier injection ( $I_4$ ).

- High field effect in the drain junction of a MOS transistor gives rise to another leakage current phenomena called Gate Induced Drain Leakage (GIDL) current ( $I_5$ ). Silicon surface under the gate reaches almost same potential of p-type substrate, when the gate is biased to form an accumulation layer. Surface behaves like a p-region more heavily doped than the substrate. Depletion layer at the surface become much narrower than elsewhere, because accumulated holes are present at the surface. When the negative gate bias is large, the n+ drain region under the gate can be depleted and even inverted. This causes a dramatic increase of high field effects such as avalanche multiplication and band-to-band tunneling. As a result of all these effects, minority carriers are emitted in the drain region underneath the gate. Since the substrate is at a lower potential for minority carriers, the minority carriers that have been accumulated or formed at the drain depletion region underneath the gate are swept laterally to the substrate, completing a path for the GIDL [7].

- The depletion regions at the drain-substrate and source-substrate junctions extend into the channel in the short channel devices. The reason behind this extension is the proximity of the source and drain. The separation between the depletion boundaries decreases with the channel length as the doping is kept constant. The junctions also become closer as the reverse bias across

the junctions increases. When the combination of channel length and reverse bias leads to the merging of the depletion regions, punch through will occurred. This reduces the potential barrier for majority carrier at the source, as drain voltage increases beyond the punch through voltage ( $V_{PT}$ ). More of the carriers cross the energy barrier and enter into the substrate, and the drain collects some of them. The net effect is an increase in the leakage current [7].

Sub-threshold leakage current is the largest leakage current component. It increases exponentially as a result of threshold voltage reduction. It is very important to find out an effective technique to reduce sub-threshold current. This is one of the primary concerns for ultra-low voltage design. Other than this, second most crucial concern is the variation in ultra-low voltage circuits imposed by process related issues. Next chapter will provide a details overview about effects process parameter variation in super-threshold and subthreshold circuit design.

# Chapter 3

#### **Process Parameter Variation on Mixed Signal Circuits**

#### **3.1 Introduction**

One of the effective ways of reducing both dynamic and leakage power is reducing supply voltage. However, supply voltage scaling can be achieved by sacrificing performance and efficiency of the device. The main overhead is an increased delay, as compared to circuits with nominal  $V_{DD}$ . Another vital issue for low voltage circuits is the process variability in integrated circuits, which has been previously demonstrated in several work on low voltage circuits [19-21]. Variability has been shown to be a severe limitation for sub-threshold circuits [22].

The effect of variability in nanometer-scaled circuits causes significant deviation from the prescribed specification for a chip. The magnitude of the deviations together with tight performance specifications, imply that variability is an increasingly vexing problem as technologies continue to scale. Process related variations are one-time variations that occur when a circuit is manufactured and cause process parameters to drift from their design values. These variations can impact key circuit performance characteristics: including delay, noise margin and logic threshold of digital circuits [10].

It is becoming evident that designing circuit at the nominal point, or using simple corner based approaches, are no longer viable [10]. Process variation not only effects

circuit performance but also disturbs the accuracy of leakage power estimation. Since leakage power will take significant portion of overall power consumption in the future technologies, it is important to estimate leakage power correctly. In a leakage dominant CMOS system to achieve high yields, it also becomes inevitable to identify techniques to reduce this variation and leakage power [2].

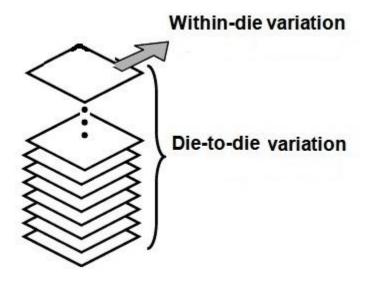

#### **3.2 Variation Categories**

Sources of variations in a circuit can be broadly categorized in to two divisions: Die-to-die (D2D) variations and Within-die (WID) variations. Figure 3.1 presents the sources of variation in a comprehensive way.

Figure 3.1: Variation categories of a circuit [2]

• **Die-to-die** variation is also known as inter-die variation or global variation. Integrated circuits are always vulnerable to this type of parameter fluctuations. Inter-die variation results from lot-to-lot, wafer-to-wafer, and within-wafer variations. This type of variation affects every element of a chip in the same pattern. For example, die-to-die variation may cause all the transistors' gate length of a particular die to be higher than the nominal value [9]. Processing environment mainly temperature, equipment properties, wafer polishing and wafer placement are responsible for lot-to-lot and wafer-to-wafer variations. Within-wafer variation contributes to both die-to-die and within-die fluctuations. An example of within-wafer variation that can affect the die-to-die variation is the resist thickness across the wafer [23].

• Within-die variation is also called local or intra-die variation. Variation that occurs between two devices of the same chip is known as within-die variation. This variation creates a non-uniformity of electrical characteristics across the chip. Those parameters that vary rapidly over distances, smaller than the dimension of a die, results in within-die variations. Within-die variation may effects different devices of the same chip differently. For example, some transistors in a chip may have higher threshold voltage than others [2,23].

Within-die variation can be divided into two sub categories; random and systematic.

• **Systematic** variations are in general spatially correlated and show specific trends across the chip. Deterministic shifts of process parameters in space and time creates systematic variations on a chip. Deviations of a stepper lens is an example of such variations. It is important to note that, some of

the systematic variations on a chip are considered as random variation because of their complexity in modeling [9,24].

Random variation differs randomly and independently from device to device. It is hard to model these types of variations, since sources are unknown. This type of variation changes the device behavior of a chip in a very unpredictable manner. No spatial or temporal correlation is available. One of the examples of such variation is the number of dopant atoms and their positions in a MOSFET. This effect is intrinsic and cannot be controlled externally by the manufacturing process [9,24].

Die-to-die (D2D) variations have been the prime concerns for a long time and within-die (WID) variation was neglected deliberately. However, as we entered the deep sub-micron arena, polysilicon gate length has been reduced below the wavelength of light used in optical lithography process. As a result of this complex lithography process, withindie (WID) variation has increased significantly and it is an ultimate threat for the performance of future integrated circuits. Process corners based design methodologies are no longer an effective solution for designing circuit with high accuracy [9]. In this thesis, we have given emphasis on within-die variation issue.

#### 3.3 Sources of variation

There are several sources of variation that can deviate the performance and electrical properties of a digital circuit. In this thesis we will concentrate on variation of some of the important parameters only. We will describe primary sources of variation briefly in following subsections:

## **3.3.1 Random Dopant Fluctuation**

The average number of dopants and their positions in a device is a random process. Still now, there is no such way to get control over the dopant atoms placement through the manufacturing process. Number of dopant atoms in a depletion region of a device is decreasing as CMOS devices are scaled down. Average number of dopant atoms in a 22nm MOSFET channel is only few tens of impurities with relatively large standard deviation. This significant amount of change in the average number of atoms varies the threshold voltages of MOSFETs in a chip enormously. Threshold voltage ( $V_i$ ) of a NMOS or a PMOS depends on the number of ionized atoms in the depletion region. This fluctuation issue was anticipated long ago [9]. In earlier technologies, number of dopant atoms in a MOSFET was sufficiently large enough so that their standard deviation was not disturbing the threshold voltage deviation very much. Hence, it was not creating much problem for digital circuits but they have always been important for analog circuits [9, 24].

A pioneer work of [26-28] showed that the statistical distribution of threshold voltage variation due to random dopant fluctuation is Gaussian and its standard deviation is as follows [9]:

$$\sigma_{V_t} = \left(\sqrt[4]{2q^3 \mathcal{E}_{si} N_a \phi_B}\right) \cdot \frac{t_{ox}}{\varepsilon_{ox}} \cdot \frac{1}{\sqrt{3WL}}$$

(3.1)

Figure 3.2 : Three-dimensional bird's-eye view of planar bulk MOSFET with randomly distributed dopants in the channel region [25]

Here *q* is the electron charge,  $\mathcal{E}_{St}$  and  $\mathcal{E}_{ox}$  are the permittivity of the silicon and gate oxide, respectively, *Na* is the channel dopant concentration,  $\mathcal{O}_B$  is the difference between Fermi level and intrinsic level,  $t_{ox}$  is the gate oxide thickness, and *W* and *L* are the channel width and channel length for the transistor, respectively. Equation (3.1) implies that the threshold voltage variation is inversely proportional to the square root of effective area of the device [9]. Although it is expected from (3.1) that increasing the effective area will reduce the threshold voltage variation significantly, in practice the scenario will not be same as expected. Position of the dopant atoms will vary the threshold voltage significantly [25]. Therefore, there will be a large spread in performance and power of a device.

Figure 3.3 shows the decrease in number of dopant atoms as the channel length decreases. This decrease has been roughly proportional to  $L^{1.5}$ . Now a days, FETs threshold voltage variation is determined by even less than 1000 dopant atoms. Thus, it has become very tough to restrict the  $\pm 3\sigma_N$  showed in figure 3.3 within a small range. That is why

random dopant fluctuation in a short channel device is getting so much attention to the designers now [9]. This variation effect is also known as "discrete dopant effect" [29].

Figure 3.3: Number of dopant atoms in a depletion layer of a MOSFET vs. effective channel length [9]

## **3.3.2 Critical Dimension Variation**

Another important process parameter that affects digital circuits is critical dimension of a device. A small variation in the device channel length or width can make a large spread in the performance and delay of a circuit. It is impossible to control this critical dimension's variation until there is any radical change in lithography technology (e.g. Extreme Ultraviolet Lithography). Today's technologies use feature sizes that are much smaller than the wavelength of light used in optical lithography. This results in diffraction of light, which is known as optical proximity effect (OPE). OPE is layout dependent and hence result in different critical dimension (CD) variations depending on neighboring lines as well as orientation. This makes the lithography process even more

challenging [9]. Manufacturing industries are using Optical proximity correction (OPC) and phase shift masks (PSM) to reduce this proximity effect, but still relative variation of critical dimensions are increasing [30].

Since these variations are layout dependent, they are considered as systematic intra-die variation. They have a spatial correlation across the die. The variation in transistor's channel length has direct impact on transistor's threshold voltage. The variation in threshold voltage arises due to the exponential dependence of  $V_t$  on channel length L for short channel devices, mainly due to drain induced barrier lowering (DIBL) [9]. Variations of the transistor's width (W) and length (L) directly affect its drive current, which is proportional to W/L [30]. Variation in the channel width (W) affects the threshold voltage ( $V_t$ ), due to narrow channel effect. However, this effect is negligible compare to the effect of channel length variation on threshold voltage, because channel width is normally much larger than the channel length of a transistor.

## 3.3.3 Line Edge Roughness

Line width roughness occurs in a transistor when the width of the resist feature varies quickly over the length of the feature. When examining these variations along just one edge it is called line edge roughness (LER). LER is caused by a number of statistically fluctuating effects at these small dimensions such as shot noise (photon flux variations), statistical distributions of chemical species in the resist such as photo acid generators, the random walk nature of acid diffusion during chemical amplification, and the nonzero size of resist polymers being dissolved during development [31]. It has a direct impact on threshold voltage and channel length variation of a transistor. *Ioff /Ion* current ratio for

short channel devices also increases due to line edge roughness. It is expected to have a high threshold voltage variation due to line edge roughness in 22nm technology [9,30].

Figure 3.4 : Line edge rougness due to lithography variation [32]

## **3.3.4 Oxide Thickness variation**

Gate oxide thickness variation during manufacturing can affect the performance and electrical properties of a circuit. However, this parameter is controlled consciously during processing. Therefore, the variation of gate oxide thickness is normally small.

## **3.3.5** Mobility Variation

Any variation in the mobility of hole or electron can affect the electrical properties of a transistor. Threshold voltage can be affected marginally by the mobility fluctuation. This variation can arise from several complex physical mechanisms.

## 3.3.6 Supply Voltage Variation

Supply voltage fluctuations are mainly caused by *IR* drop and di/dt noise. *IR* drop is caused by the current flow over the parasitic resistance of the power grid, whereas di/dt

noise is due to the parasitic inductance in combination with capacitance and resistance of the power grid and package. The superposition of both effects can not only lead to voltage drops, but also voltage overshoots. Besides fast changing power noise effects, also offsets in the voltage regulator can lead to deviations from the nominal supply voltage [30].

These are the primary sources that are responsible for performance and power variation of a mixed signal circuit. There are other sources of variations (such as temperature and interconnect) but their contributions are often negligible. Random dopant fluctuation and line edge roughness are random processes and they both have a significant effect on threshold voltage variation. For our analysis in this thesis, we will mainly focus on the impacts of threshold voltage variation, channel length and width variations and power supply voltage variation on digital circuits.

It is very important to estimate the effect of parameter variation accurately. Estimation accuracy is directly related to a company's overall revenue. Design complexity and manufacturing cost increases due to overestimation. Conversely, an underestimation can compromise the product's performance and overall yield [23]. To estimate the effect of variations, analytical models for digital circuit are discussed in Chapter 4.

# Chapter 4

## **Analytical Models**

## 4.1 Introduction

An important issue for low voltage circuits is the process variability in integrated circuits, which has been previously demonstrated in several works on low-voltage circuits. These variations can impact many key circuit performance characteristics. For digital circuits, affected parameters include: delay, noise margin and logic switching threshold of the circuit. As a result, properly analyzing the effect of process related variations on digital circuit has become the most demanding concern. To do so, an analytical model is required and a closed-form model for device variability is derived in this chapter to enable first order estimation of some fundamental circuit parameters. This analysis can be extended to develop models for the impact of variations on any circuit's parameters. To estimate the variation of device parameters, we will start with a device variation map to understand the effects properly.

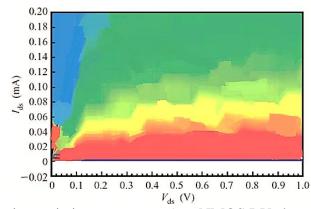

## **4.2 Device Variation Map**

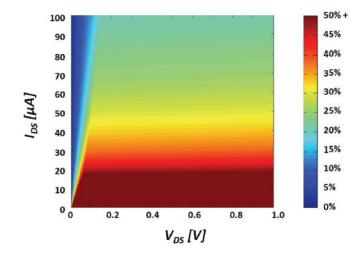

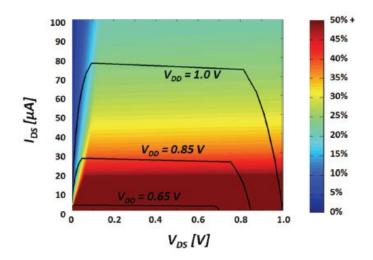

For the first time, Bernstein *et al.* used experimental and measured data to illustrate a color map of device variations on I-V characteristics plot in a 65nm CMOS device as shown in Figure 4.1 [6]. The background color in the figure is indexed to the magnitude of device current variation actually observed in DC hardware characterization of the device, operated at the specific drain-source voltage ( $V_{DS}$ ), drain-source currents ( $I_{DS}$ ) and implied gate-source voltage ( $V_{GS}$ ) point on the plot. The red shading indicates regions of the highest device current variation, and blue shading shows areas of the lowest device current variations. The device variation map shown in Figure 4.1, is a very useful tool in understanding the impact of device variations on various circuit topologies. In this section, we develop analytical models to construct such a device variation map for any given technology node [6].

#### 4.2.1 Assumptions

In the IC fabrication process, all device parameters are subject to deviations from their nominal values. Statistical models have been developed for transistor parameters, such as threshold voltage ( $\Delta V_t$ ), effective channel length ( $\Delta L_{eff}$ ) and device width ( $\Delta W$ ).In this study, we only considered these parameters as variables, but methods can be extended to any additional variables as well [6].

### 4.2.2 Derivations

In general the drain-source current,  $I_{DS}$  of a transistor is represented by:

$$I_{DS} = f(V_t, L, W) \tag{4.1}$$

Where  $V_t$  is the threshold voltage, L is the device length and W is the device width. Function f can be any analytical model that describes the device characteristics, such as alpha-power law model, unified model, or MOSFET transregional model, where it covers all regions of operations including the sub-threshold region [6].

Figure 4.1. Device variation map on a 65nm NMOS I-V characteristics using

experimental data [6]

Assuming that device variations are small compared to their nominal values and that they can be approximated by Gaussian distribution, the device current variation can be derived by taking partial derivative as shown below:

$$\Delta I_{DS} = \sqrt{\left(\frac{\partial f}{\partial v_t}\right)^2 \Delta V_t^2 + \left(\frac{\partial f}{\partial L}\right)^2 \Delta L^2 + \left(\frac{\partial f}{\partial W}\right)^2 \Delta W^2}$$

(4.2)

where each term represents the contribution of variation to the associated device parameter. To simplify the derivation, the unified model is used here to represent the transistor drain-source current,  $I_{DS}$ :

$$I_{DS} = K'_{n} \left(\frac{W}{L}\right) \left( (V_{GS} - V_{t}) V_{min} - \frac{V_{min}^{2}}{2} \right) (1 + \lambda V_{DS})$$

$$(4.3)$$

where  $V_{min}=min\{(V_{GS}-V_t), V_{DS}, V_{DSAT}\}$ ,  $V_{DSAT}$  is the drain-source voltage under velocity saturation,  $K_n'$  is the device trans conductance,  $\lambda$  is the channel length modulation factor and (W/L) is the device aspect ratio. From partial derivative equation in (4.2) the device current variation can be derived and simplified as [6]:

$$\frac{\Delta I_{\rm DS}}{I_{\rm DS}} = \sqrt{\left(\frac{2\Delta V_{\rm t}}{2(V_{\rm GS} - V_{\rm t})V_{\rm min}}\right)^2 + \left(\frac{\Delta L}{L}\right)^2 + \left(\frac{\Delta W}{W}\right)^2} \tag{4.4}$$

The analytical model represented in (4.4) is the key element in generating the device

variation map shown in Figure 4.1. An example of the device variation map for a projected 22nm CMOS is shown in Figure 4.2, where it clearly agrees with the device variation map shown in Figure 4.1 [2].

Figure 4.2. Projected Device Variation map for PTM's 22nm NMOS Device [6]

## 4.3 Low Voltage digital circuits under device variations

The analytical model for the device variation map derived and demonstrated in Section 4.1 is one of the main components for analyzing the impact of device variations for electronic circuits. By examining the I-V trajectory space for an NMOS circuit in electronic circuit over the device variation map, one can predict the impact of device variations under different conditions [6].

Figure 4.3. The I-V trajectory of an NMOS in an inverter under different supply voltages using PTM's 22nm device parameters [6]

For example, Figure 4.3 illustrates the I-V trajectory of a NMOS in an inverter under different supply voltages for the PTM's 22nm CMOS technology, as described in Table 4.1. Clearly, the impact of device variations is more severe in inverters with lower supply voltages, because the device spent a larger portion of the trajectory in the high (red) variation region [6].

| D | evice |             | Vt   |                        | K'   | v   | DSAT                |    | λ                  | (W/] | L) |

|---|-------|-------------|------|------------------------|------|-----|---------------------|----|--------------------|------|----|

| N | MOS   | 0.          | 37 V | 97.5 μA/V <sup>2</sup> |      | 0.  | .24 V 0.0           |    | 6 V <sup>-1</sup>  | 100  |    |

| Р | MOS   | 0.          | 25 V | 12.0 µA/V <sup>2</sup> |      | 0.  | 75 V 0.1            |    | V <sup>-1</sup>    | 200  | C  |

|   | Devic | e           | %Δ   | $V_t$ % $\Delta W$     |      |     | $\% \Delta L_{eff}$ |    | $\% \Delta V_{DD}$ |      |    |

|   | NMO   | S           | 4%   |                        | 1.2% |     | 2.5%                |    | 5%                 |      |    |

|   | PMO   | IOS 4% 1.2% |      | 1.2%                   |      | 2.5 | %                   | 5% | 6                  |      |    |

Table 4.1 : The PTM'S 22nm CMOS Device Parameters [6]

### 4.3.1 Propagation Delay

### 4.3.1.1 Ideal Square Wave (rise time=0)

To quantify the impact of parameter variations on digital circuit, we start with the high-to-low propagation delay of an inverter. All parameter values of the inverter are based on table 4.1. We will analyze both the super-threshold and sub-threshold region of operations of the inverter. It is important to note that, our main interest in this thesis project is to model a simple and accurate delay variation model that can help us to discover different design compromises, rather than modeling the propagation delay accurately. Therefore, our models will be simplified but not too precise. To simplify the analysis we use unified model for current equation. Similar analysis can be done for low-to-high propagation delay of the inverter also. In the following sections operating region of NMOS is determined based on the PTM's 22nm CMOS technology parameters but the derived equations for different operating regions of NMOS are universal and can be used for other technologies as well by identifying the proper region of operation.

### A. Super-threshold circuit ( $V_{DD} \ge V_t$ )

Considering a perfect square wave as an input signal in the gate ( $V_G = V_{DD}$ ), the propagation delay ( $t_{pHL}$ ) of an inverter can be expressed by the following equation:

$$t_{pHL} = \frac{C_L V_{DD}}{2I_{ON}} \tag{4.5}$$

where,

$$I_{on} = k_n' \left(\frac{W}{L}\right)_n \{ \left(V_{GS} - V_{t,n}\right) V_{min} - \frac{V_{min}^2}{2} \}$$

(4.6)

and

$$V_{min} = min\{(V_{GS}-V_{t,n}), V_{DS}, V_{DSAT}\}$$

Figure 4.4. An Inverter circuit [6]

## (i) **For** $V_{DD} = 0.62$ V to 1V

NMOS will be in velocity saturation region, because  $V_{DSAT}$ ,  $n < V_{GS}$ - $V_{t,n} < V_{DS}$ . So,  $t_{pHL}$  will be –

$$t_{pHL} = \frac{C_L V_{DD}}{2k_n' {\binom{W}{L}}_n \{ (V_{GS} - V_{t,n}) V_{DSAT,n} - \frac{(V_{DSAT,n})^2}{2} \}}$$

$$= \frac{C_L V_{DD}}{2k_n' {\binom{W}{L}}_n \{ (V_{DD} - V_{t,n}) V_{DSAT,n} - \frac{(V_{DSAT,n})^2}{2} \}}$$

(4.7)

Now by taking partial derivatives of equation (4.7) with respect to  $V_{DD}$ ,  $V_{t,n}$ , L and W, we can find the effect of each parameters individually:

(a)

$$\frac{\partial t_{pHL}}{\partial V_{DD}} = \frac{-C_L (V_{DSAT,n} V_{t,n} + \frac{(V_{DSAT,n})^2}{2})}{2k_n' (\frac{W}{L})_n \left( V_{DD} V_{DSAT,n} - V_{DSAT,n} V_{t,n} - \frac{(V_{DSAT,n})^2}{2} \right)^2}$$

(b)

$$\frac{\partial t_{pHL}}{\partial V_{t,n}} = \frac{C_L V_{DD} V_{DSAT,n}}{2k_n' (\frac{W}{L})_n \left( V_{DD} V_{DSAT,n} - V_{DSAT,n} V_{t,n} - \frac{(V_{DSAT,n})^2}{2} \right)^2}$$

(c)

$$\frac{\partial t_{pHL}}{\partial L} = \frac{C_L V_{DD}}{2k_n'(W)_n \left( V_{DD} V_{DSAT,n} - V_{DSAT,n} V_{t,n} - \frac{(V_{DSAT,n})^2}{2} \right)}$$

(d)

$$\frac{\partial t_{pHL}}{\partial W} = \frac{-C_L V_{DDL}}{2k_n'(W^2)_n \left( V_{DD} V_{DSAT,n} - V_{DSAT,n} V_{t,n} - \frac{(V_{DSAT,n})^2}{2} \right)}$$

Assuming that the variations of device parameters are small compared to their nominal values and they can be approximated by the Gaussian distribution, the inverter delay variation can be derived by as shown below:

$$\Delta t_{pHL} = \sqrt{\left(\frac{\partial t_{pHL}}{\partial V_{\text{DD}}}\right)^2 \Delta V_{\text{DD}}^2 + \left(\frac{\partial t_{pHL}}{\partial V_{\text{t}}}\right)^2 \Delta V_{\text{t,n}}^2 + \left(\frac{\partial t_{pHL}}{\partial L}\right)^2 \Delta L^2 + \left(\frac{\partial t_{pHL}}{\partial W}\right)^2 \Delta W^2}$$

(4.8)

From partial derivative equation in (4.8) the inverter delay variation can be derived and simplified as :

$$\frac{\Delta t_{pHL}}{t_{pHL}} = \sqrt{\left(\frac{V_{\text{DSAT,n}} + 2V_{\text{t,n}}}{2V_{\text{DD}} - 2V_{\text{t,n}} - V_{\text{DSAT,n}}}, \frac{\Delta V_{\text{DD}}}{V_{\text{DD}}}\right)^2 + \left(\frac{2\Delta V_{\text{tn}}}{2V_{\text{DD}} - 2V_{\text{t,n}} - V_{\text{DSAT,n}}}\right)^2 + \left(\frac{\Delta L}{L}\right)^2 + \left(\frac{\Delta W}{W}\right)^2}$$

(4.9)

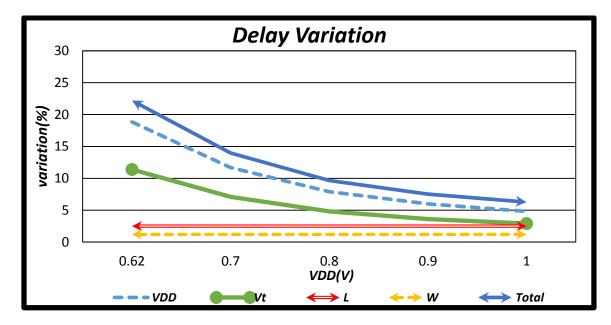

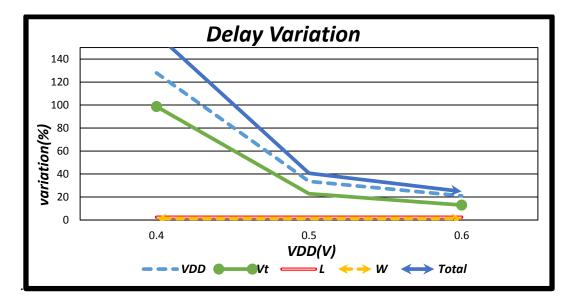

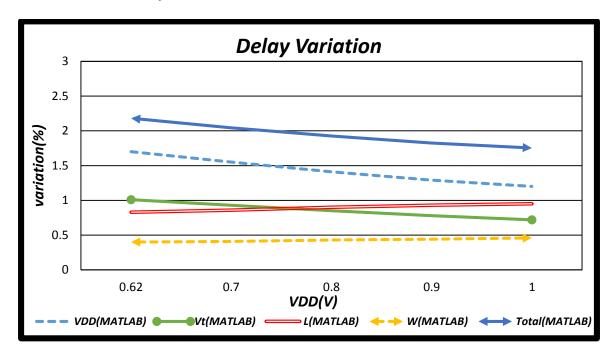

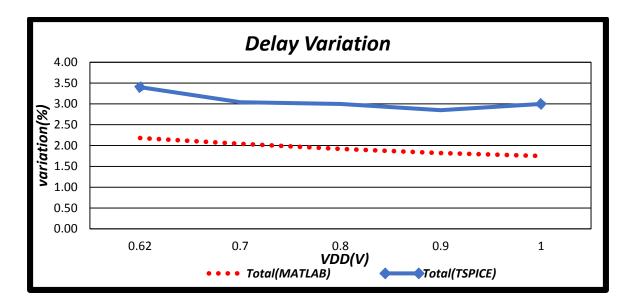

In addition, the variation of low-to-high propagation delay can be modeled by an equation analogous to (4.9). Using the device parameters for 22nm technology node given in Table 4.1 and the analytical model in (4.9), the plot of delay variation components versus supply voltage is illustrated in Figure 4.5. As expected, reducing supply voltage results in a very large delay variation. However, the analytical model shown in (4.9) provides the contribution of each variability component, separately. Figure 4.5 shows that, for analytical model presented in (4.9),  $V_{DD}$  and  $V_t$  are dominant source of uncertainty, especially when supply voltage is reduced below 0.8V. According to Figure 4.5, the impacts of channel length and device width variations on delay of digital circuits are negligible. For  $V_{DD} = 0.62V$ , total variation is around 25%, where  $V_{DD}$  variation contributes mostly by 22%. *L* and *W* variations contributes only 2.5% and 1.2%, respectively. 4%  $V_t$  variation

can make around 15% delay variation for an inverter circuit.

Figure 4.5. Delay variation versus supply voltage for an inverter in PTM's 22nm technology node. (Velocity saturation)

## (ii) For $V_{DD} = 0.37$ V to 0.61 V

NMOS will be in saturation region, because  $V_{GS}$ - $V_{t,n} < V_{DSAT,n} < V_{DS}$ . Therefore,  $t_{pHL}$  will be:

$$t_{pHL} = \frac{C_L V_{DD}}{k_n' (\frac{W}{L})_n (V_{GS} - V_{t,n})^2} = \frac{C_L V_{DD}}{k_n' (\frac{W}{L})_n (V_{DD} - V_{t,n})^2}$$

(4.10)

Now by taking partial derivatives of equation (4.10) with respect to  $V_{DD}$ ,  $V_{t,n}$ , L and W we can find out the effect of each parameters individually:

(a)

$$\frac{\partial t_{pHL}}{\partial V_{DD}} = \frac{-C_L(V_{DD} + V_{t,n})}{k_n' \left(\frac{W}{L}\right)_n \left(V_{DD} - V_{t,n}\right)^3}$$

$$(b) \frac{\partial t_{pHL}}{\partial V_{t,n}} = \frac{2C_L V_{DD}}{k_n' \left(\frac{W}{L}\right)_n \left(V_{DD} - V_{t,n}\right)^3}$$

$$(c) \frac{\partial t_{pHL}}{\partial L} = \frac{C_L V_{DD}}{k_n' (W)_n \left(V_{DD} - V_{t,n}\right)^2}$$

$$(d) \frac{\partial t_{pHL}}{\partial W} = \frac{-C_L V_{DD} L}{k_n' (W^2)_n \left(V_{DD} - V_{t,n}\right)^2}$$

Like previous case, assuming that the variation of device parameters are small compared to their nominal values and they can be approximated by the Gaussian distribution, the inverter delay variation can be derived by as shown below:

$$\Delta t_{pHL} = \sqrt{\left(\frac{\partial t_{pHL}}{\partial V_{\text{DD}}}\right)^2 \Delta V_{\text{DD}}^2 + \left(\frac{\partial t_{pHL}}{\partial V_{\text{t}}}\right)^2 \Delta V_{\text{t,n}}^2 + \left(\frac{\partial t_{pHL}}{\partial L}\right)^2 \Delta L^2 + \left(\frac{\partial t_{pHL}}{\partial W}\right)^2 \Delta W^2} \quad (4.11)$$

From partial derivative equation in (4.11) the inverter delay variation can be derived and simplified as:

$$\frac{\Delta t_{pHL}}{t_{pHL}} = \sqrt{\left(\frac{V_{DD} + V_{t,n}}{V_{DD} - V_{t,n}}, \frac{\Delta V_{DD}}{V_{DD}}\right)^2 + \left(\frac{2\Delta V_{tn}}{V_{DD} - V_{t,n}}\right)^2 + \left(\frac{\Delta L}{L}\right)^2 + \left(\frac{\Delta W}{W}\right)^2}$$

(4.12)

Plot of delay variation components versus supply voltage is illustrated in Figure 4.6. Like the model of (4.9), reducing supply voltage results in a very large delay variation. Figure 4.6 show that from analytical model presented in (4.12),  $V_{DD}$  and  $V_t$  are dominant source of uncertainty, again. According to figure 4.6, the impacts of channel length and device width variations are negligible on delay variation in this case too. For  $V_{DD} < 0.5V$ , total variation is no more tolerable; because the overall variation becomes more than 50%. Near threshold voltage overall variation is even more than 100%. For  $V_{DD}$ =0.4V total variation is 161%, where  $V_{DD}$  variation contributes mostly by 128%. *L* and *W* variations

contributes only 2.5% and 1.2% respectively.  $V_t$  variation can effect as much as around 100% delay variation for an inverter circuit.

Figure 4.6. Delay variation versus supply voltage for an inverter in PTM's 22nm technology node. (Saturation)

## **B.** Sub-threshold circuit ( $V_{DD} < V_t$ )

When the supply voltage is less than the threshold voltage, transistor operates in subthreshold region and current that passes through the transistor is called 'off current' or 'leakage current'. This off current is also known as sub-threshold conduction current. In a sub-threshold circuit, this leakage current is the driving force of logic circuit functionality. Considering a perfect square wave as an input signal in the gate, propagation delay ( $t_{pHL}$ ) of an inverter operating in the sub-threshold region can be expressed by the following equation:

$$t_{pHL} = \frac{C_L V_{DD}}{2I_{ON}} \tag{4.13}$$

where,

$$I_{ON} = k_n' \left(\frac{W}{L}\right) (m-1) V_{TH}^2 \exp\left(\frac{V_{GS} - V_{t,n}}{m V_{TH}}\right) \{1 - \exp\left(\frac{-V_{DS}}{V_{TH}}\right)\}$$

(4.14)

Since,  $V_{DS} \gg V_{TH}$ ,  $\exp\left(\frac{-V_{DS}}{V_{TH}}\right) \approx 0$ . Therefore,

$$t_{pHL} \approx \frac{C_L V_{DD}}{2k_n' \left(\frac{W}{L}\right)_n (m-1) V_{TH}^2 \exp\left(\frac{V_{DD} - V_{t,n}}{m V_{TH}}\right)}$$

(4.15)

Now taking partial derivatives of equation (4.15) with respect to the process parameters, we can find the followings:

$$(a) \frac{\partial t_{pHL}}{\partial V_{DD}} = \frac{C_L (1 - \frac{V_{DD}}{mV_{TH}})}{2k_n' \left(\frac{W}{L}\right)_n (m - 1)V_{TH}^2 \exp\left(\frac{V_{DD} - V_{t,n}}{mV_{TH}}\right)}$$

$$(b) \frac{\partial t_{pHL}}{\partial V_{t,n}} = \frac{-C_L V_{DD} (\frac{1}{mV_{TH}})}{2k_n' \left(\frac{W}{L}\right)_n (m - 1)V_{TH}^2 \exp\left(\frac{V_{DD} - V_{t,n}}{mV_{TH}}\right)}$$

$$(c) \frac{\partial t_{pHL}}{\partial L} = \frac{C_L V_{DD}}{2k_n' (W)_n (m - 1)V_{TH}^2 \exp\left(\frac{V_{DD} - V_{t,n}}{mV_{TH}}\right)}$$

$$(d) \frac{\partial t_{pHL}}{\partial W} = \frac{-C_L V_{DD} L}{2k_n' (W^2)_n (m - 1)V_{TH}^2 \exp\left(\frac{V_{DD} - V_{t,n}}{mV_{TH}}\right)}$$

Assuming like the other cases, that the variation of device parameters are small compared to their nominal values and they can be approximated by the Gaussian distribution, the inverter delay variation can be derived and simplified as:

$$\frac{\Delta t_{pHL}}{t_{pHL}} = \sqrt{\{(1 - \frac{V_{\text{DD}}}{mV_{TH}}), \frac{\Delta V_{\text{DD}}}{V_{\text{DD}}}\}^2 + (\frac{\Delta V_{\text{t,n}}}{mV_{TH}})^2 + (\frac{\Delta L}{L})^2 + (\frac{\Delta W}{W})^2}$$

(4.16)

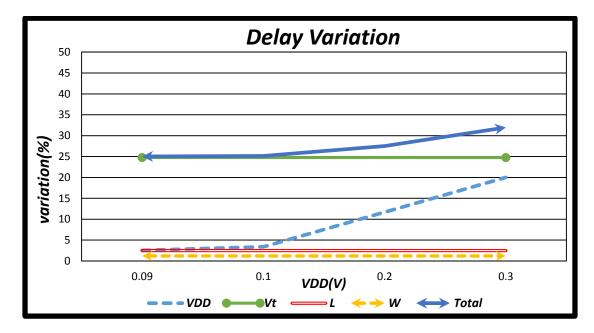

Plot of delay variation components versus supply voltage in the sub-threshold circuit is illustrated in Figure 4.7. Unlike the models of (4.9) and (4.12), reducing supply

voltage results in a reduction of overall delay variation. Figure 4.7 shows that, for analytical model presented in (4.16),  $V_t$  is the dominant source of delay variation. From Figure 4.7, the impacts of channel length and device width variations are negligible for delay variation and their contributions do not change with the supply voltage. For  $V_{DD}$ =0.3V, total delay variation is 31%, whereas for  $V_{DD}$ =0.09V variation is 25%. Delay variation in an inverter due to threshold voltage ( $V_t$ ) variation is constant for the sub-threshold operation and it is fixed at 25%. However, delay variation due to  $V_{DD}$  variation changes; 5% of  $V_{DD}$  variation can create 20% delay variation for an inverter when supply voltage is 0.3V and 2.5% when supply voltage is 0.1V.

Figure 4.7. Delay variation versus supply voltage for an inverter in PTM's 22nm

technology node. (Sub-threshold)

### **4.3.1.2** Non-ideal Square Wave (rise time≠0)

In last section, we have considered a step input signal in the gate of an inverter. However, in real circuit this assumption is not exactly correct. The dynamics of switching in a practical circuit is much more complicated and the input has a finite rise or fall times. Therefore, it is important to consider the impact of input slope on delay variation. Delay of an inverter is significantly disturbed by the finite input slew.

Since we are considering a finite input slope at the gate of an inverter, the gate voltage can be modeled as [9]:

$$V_G = \frac{t}{T_r} V_{DD} \tag{4.17}$$