# University of New Mexico UNM Digital Repository

Computer Science ETDs

**Engineering ETDs**

7-1-2016

## Logic Circuits Based on Extended Molecular Spider Systems

Dandan Mo

Follow this and additional works at: https://digitalrepository.unm.edu/cs\_etds

#### Recommended Citation

Mo, Dandan. "Logic Circuits Based on Extended Molecular Spider Systems." (2016). https://digitalrepository.unm.edu/cs\_etds/77

This Dissertation is brought to you for free and open access by the Engineering ETDs at UNM Digital Repository. It has been accepted for inclusion in Computer Science ETDs by an authorized administrator of UNM Digital Repository. For more information, please contact disc@unm.edu.

## Logic Circuits Based on Extended Molecular Spider Systems

by

### Dandan Mo

B.E., Shanghai Jiao Tong University, 2010

### DISSERTATION

Submitted in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy Computer Science

The University of New Mexico

Albuquerque, New Mexico

July, 2016

## **Dedication**

To my parents, Chengxiong Mo and Aixiang Wang, for their support and understanding. To my husband, Bo Li, for his company and encouragement.

"The Tao in its regular course does nothing (for the sake of doing it), and so there is nothing which it does not do." - Laozi

## Acknowledgments

I would like to thank my advisor, Professor Darko Stefanovic, for his support in my research and guiding me into the field of molecular computing. I would also like to thank Professor Matthew R. Lakin who gave me many important suggestions when I developed my research ideas and polished my work. I would like to thank my lab-mate Alireza Goudarzi, for his attendance at all my rehearsal talks, and his useful tips on improving presentation skills. I am grateful for the feedback of my dissertation committee: Shuang Luan, Milan Stojanovic, Matthew R. Lakin and Darko Stefanovic.

My work at the University of New Mexico was supported by the National Science Foundation under grants CCF-1318833, CCF-1422840, and CCF-1518861. I am grateful for this financial support.

## Logic Circuits Based on Extended Molecular Spider Systems

by

#### Dandan Mo

B.E., Shanghai Jiao Tong University, 2010Ph.D., Computer Science, University of New Mexico, 2016

#### Abstract

Spatial locality brings the advantages of computation speed-up and sequence reuse to molecular computing. In particular, molecular walkers that undergo localized reactions are of interest for implementing logic computations at the nanoscale. We use molecular spider walkers to implement logic circuits. We develop an extended multispider model with a dynamic environment wherein signal transmission is triggered via localized reactions, and use this model to implement three basic gates (AND, OR, and NOT) and a cascading mechanism. We develop an algorithm to automatically generate the layout of the circuit. We use a kinetic Monte Carlo algorithm to simulate circuit computations, and we analyze circuit complexity: our design scales linearly with formula size and has a logarithmic time complexity.

## Contents

| 1        | Intr | $\operatorname{roduction}$        | 1  |

|----------|------|-----------------------------------|----|

| <b>2</b> | Mo   | del Description                   | 5  |

| 3        | Des  | ign                               | 7  |

|          | 3.1  | Normal Sites and Functional Sites | 7  |

|          | 3.2  | Designs of the AND and OR Gates   | 9  |

|          | 3.3  | Design of the NOT gate            | 10 |

|          | 3.4  | Gate Cascades                     | 12 |

|          | 3.5  | Simulation Results                | 13 |

| 4        | Mo   | del Definition                    | 17 |

|          | 4.1  | Site types and transition rules   | 17 |

|          | 4.2  | Model definition.                 | 20 |

| 5        | Ver  | ification                         | 22 |

### Contents

|   | 5.1  | Geometric Layout Generation                   | 22 |  |  |

|---|------|-----------------------------------------------|----|--|--|

|   | 5.2  | Redesign of the Gates                         | 24 |  |  |

|   | 5.3  | Circuit Tree Construction                     | 25 |  |  |

|   |      | 5.3.1 Case 1: the root node is a NOT gate     | 26 |  |  |

|   |      | 5.3.2 Case 2: the root node is an AND/OR gate | 27 |  |  |

| 6 | Per  | rformance 2                                   |    |  |  |

|   | 6.1  | Complexity Analysis                           | 29 |  |  |

|   | 6.2  | Simulation Results                            | 30 |  |  |

| 7 | Circ | cuit Predictability                           | 35 |  |  |

|   | 7.1  | Improving Circuit Predictability              | 36 |  |  |

|   | 7.2  | Method 1: Height Reduction                    | 37 |  |  |

|   |      | 7.2.1 Analysis                                | 39 |  |  |

|   | 7.3  | Method 2: One-Directional Movements           | 42 |  |  |

|   |      | 7.3.1 Analysis                                | 42 |  |  |

| 8 | Pos  | sible Implementations                         | 59 |  |  |

|   | 8.1  | Possible Implementation I                     | 59 |  |  |

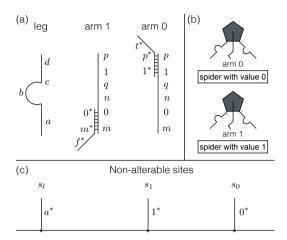

|   |      | 8.1.1 Spiders and non-alterable sites         | 60 |  |  |

|   |      | 8.1.2 Alterable sites and mechanisms          | 60 |  |  |

|   | 8.9  | Possible Implementation II                    | 62 |  |  |

### Contents

| 9 Discussion and Conclusion | 71 |

|-----------------------------|----|

| 10 Future Work              | 74 |

| References                  | 77 |

## Chapter 1

## Introduction

Modern computers use silicon-based chips to conduct computation, but the principles of computation can be embodied in various other kinds of physical and biological material. For example, quantum computing uses quantum mechanics to represent data and operations, neural computation uses neurons to process and propagate data, and molecular computing uses DNA and small molecules to construct computation units. The use of novel materials requires new types of computation models. These models differ from standard models such as the *Turing Machine* and the *Von Neumann architecture*. They provide new abstractions for computation, and reformulate original concepts in computer science such as "programming" and "algorithm". This thesis investigates the computation potential of a complex molecular system by using it to implement a logic circuit.

Molecular walkers are synthetic molecular machines inspired by natural biological motors. Previous studies [5, 8, 13, 14, 19, 21, 24, 28, 29, 35] have shown that walkers can move directionally and autonomously on a pre-programmed track via localized reactions. In molecular computing where all the reactants diffuse freely in a well-mixed solution, a computation unit needs to search the entire space to find another

#### Chapter 1. Introduction

computation unit that is designed to be reacted with, which makes computation slow. In the real implementation in lab, slow computation means to a long wait for the experimental result. Since all reactants can reach each other in a well-mixed solution, any two computation units that are not expected to react with each other should have different sequences, which makes the sequence design difficult if the computation is complicated. Spatial locality can meet the challenges of computation speed-up and sequence reuse that are faced in molecular computing when all the reactants diffuse freely in a well-mixed solution [3,11]. Hence, a walker system with inherent spatial locality has potential to perform more complex computational tasks. We investigate the computational power of a walker system by using it to implement scalable logic circuits.

We consider a molecular *spider* system, where a spider is a type of multi-legged molecular walker. A molecular spider [17], with a rigid body and several flexible legs, moves stochastically on a surface formed by sites containing DNA segments, and can exhibit biased behavior owing to different reactions with fresh sites (catalytic cleavage) and visited sites (dissociation). We extend previous models [1, 12, 23–26] to implement three basic logic gates (AND, OR, NOT), and cascade the gates to construct logic circuits. Unlike previous models where molecular spiders exhibit biased behaviors, our model uses multiple spiders that are assumed to behave in an unbiased manner with equal transition rates to all reachable sites. Sites are divided into *normal sites*, which are immutable, and *functional sites*, which can be altered via catalytic cleavage and/or strand displacement. We can encode signals into functional sites. Signal transmission [11, 15] is triggered locally when a spider interacts with a signal-carrying site, which dynamically changes the state of the spider or of the environment. We call this extended system an *active* molecular spider system.

In our design, each variable is represented by a moving spider with two legs and one arm. The arm has two possible states, 0 or 1, representing the Boolean value

#### Chapter 1. Introduction

of the signal the spider carries. Each gate is represented by a layout of different sites on a 2D lattice. In a single gate, spiders with different values will take different paths from their input locations. We arrange different functional sites along different paths, such that only a spider with the correct computation result will be directed to the output location via interactions between spiders and functional sites. On reaching the output location, a spider reports the computation result, and we call it the reporting spider. We cascade logic gates by connecting them such that only the reporting spider leaves the upstream gate and enters the downstream gate. We design a mechanism for exit from gates to implement gate cascades that allow parallel evaluation. As an example, Figure 3.4 will show a logic circuit where input spiders X and Y are initially placed at the input locations of two NOT gates, and the NOT gates are connected to the same AND gate via exit mechanisms. Spiders move within the circuit, and the spider reaching the final output location reports the computation result.

There has been much previous work on molecular logic circuits using different implementations. Molecular circuits using *DNA Strand Displacement* (DSD) [6,18,22] in a well-mixed solution use a high and a low relative concentration of a species to represent Boolean values 1 and 0, or they use two separate species in a dual-rail encoding. In deoxyribozyme-based circuits [2,7,16,32–34], substrates are cleaved by active DNA enzymes if they bind together. Catalytic cleavage between a modified substrate and a DNA enzyme releases a sequence with fluorescence, which leads to a fluorescence increase in the environment. Detection of a fluorescence change represents Boolean value 1. Here, we use spiders with arm state 1 or 0 to represent Boolean values, which removes potential ambiguity from result reporting because we do not need to decide whether a concentration is high or low, or whether there indeed exists a fluorescence change.

Using an extended active multi-spider system, while keeping the advantages re-

#### Chapter 1. Introduction

lated to spatial locality, our design ensures modularity, unambiguity, and scalability. We will describe the model in Chapter 2, and show how to construct logic circuits in Chapter 3, along with simulation results to assess circuit computation times. A formal definition of the model is given in Chapter 4. We discuss the verification of larger circuits in Chapter 5, where we give an algorithm that automatically generates the circuit layout. We present simulation results of circuit computations in Chapter 6, discuss circuit predictability in Chapter 7, and offer possible implementations in Chapter 8. We give conclusions and discuss current challenges in Chapter 9. In Chapter 10 we discuss directions for future work.

This dissertation contains material from a conference publication and one journal article. Chapters 2 and 3 use material from IPCAT 2015 paper [9]. Chapters 4 to 6 and 8 use material from a published article in journal *BioSystems* [10].

## Chapter 2

## **Model Description**

Our long-term goal is to realize the circuits we describe here with a physical implementation based on molecular spiders [8, 17]. Therefore, our model draws from the existing models of molecular spiders [21,24] and extends them to describe the richer functionalities of the walkers we hope to build. In spite of these extensions, we will use the evocative term "spider" throughout.

A molecular spider has a body and three limbs, two legs and an "arm", which it can use to attach to chemical sites on a surface. There is exclusion: at most one limb can be attached to a given site at a time. Different types of sites are laid out on a square lattice,  $\mathbb{Z}^2$ . A set of contiguous sites can form a *track* on which the spiders can move.

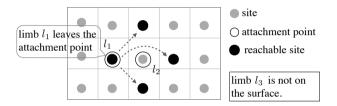

We model a spider's body as a single point, and the limbs as having equal length. This leads to the following postulated "hand-over-hand" gait [21]: at any given time, exactly two limbs are attached to the surface, and they are attached to nearest-neighbor sites. We call the sites a limb has bound to the attachment points. When a spider limb leaves a site, we assume it can quickly reattach to the surface, so there are always two attachment points for each spider, and they are adjacent to each other.

#### Chapter 2. Model Description

A transition step occurs when a spider detaches one of its limbs from an attachment point  $p \in \mathbb{Z}^2$ , and attaches to a site  $p' \in \mathbb{Z}^2$ . Figure 2.1 shows a transition step of a spider where there are four *reachable* sites that the limb can potentially transit to. However, a limb might not attach to a reachable site because whether a reachable site is *available* depends on the state of the site and of the limb, which will be discussed in Chapter 3 and Chapter 4. When multiple spiders are moving on the track, one spider cannot attach to a site occupied by another spider.

Figure 2.1: A spider has limb  $l_1$  and limb  $l_2$  attached to the surface. When limb  $l_1$  detaches from the left attachment point, four sites represented by the black dots are reachable for limbs  $l_1$  and  $l_3$ . The arrows show the transitions of a spider to other sites via hand-over-hand movement.

Spiders move stochastically on the track, interacting with the normal sites. If they attach to functional sites, signal transmission is triggered locally between two adjacent sites, or between a site and the spider attached to it. Changes to the sites and spiders may happen during a step, which is crucial in the operation of a logic circuit. In the next chapter, we will explain how to use different sites to construct three basic logic gates (AND, OR and NOT, thus complete for Boolean logic), and to cascade them to construct a logic circuit.

## Chapter 3

## Design

Each spider represents a Boolean variable. The value of the spider is indicated by its arm state, which is either 0 or 1. A logic circuit is formed by cascades comprising the basic logic gates. A logic gate is implemented as an arrangement of different sites on a square lattice, including an output location and input locations. When spiders begin moving from the input locations, their interactions with the sites lead to changes to the sites and the spider values, which ends with one spider reaching the output location. The value of that spider represents the computation result of the logic circuit.

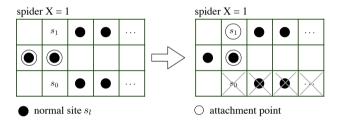

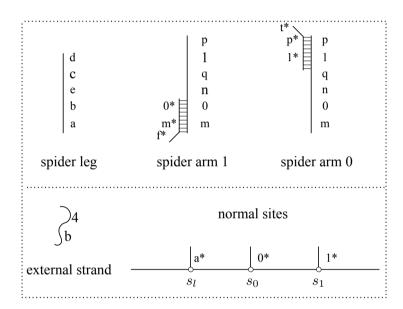

### 3.1 Normal Sites and Functional Sites

We define the set of site types as  $S = S_{norm} \cup S_{fun}$ , where the *normal* sites  $S_{norm} = \{s_l, s_1, s_0\}$  are non-alterable and the *functional* sites in  $S_{fun}$  are alterable. A normal site of type  $s_l$  binds to a spider's leg, and is used for the "wires" of a logic circuit. Sites of type  $s_0$  and  $s_1$  bind to the spider's arm if it has type 0 or 1, respectively. Sites of type  $s_0$  and  $s_1$  are typically placed at the beginning of two separate paths

that branch out from a junction, directing a spider with different values to different paths (Figure 3.1).

The junction design is used in the constructions for all gate types. Each logic gate has a set of functional sites placed on the paths branching out from the junction. After the spiders take their own paths at the junction according to their values, they will encounter different functional sites. The interactions between the spiders and the functional sites cause changes to the spider and the sites, directing one spider to the output location, to report the result of the gate computation.

Figure 3.1: If a spider has an arm type of 1, it binds to site  $s_1$  at a junction. If a spider has an arm type of 0, it binds to site  $s_0$  at a junction. Here a spider X = 1 follows the upper path by attaching to site  $s_1$ . It cannot follow the lower path.

Before going into the details of each gate, we first introduce some important features of functional sites. (1) A functional site has a state among  $\{on, off, trapped\}$ . The spider can bind to an "on"-state site, cannot bind to an "off"-state site, and cannot leave a "trapped"-state site by itself. (2) A functional site may or may not trap a spider. When it traps a spider, the site's state becomes "trapped". (3) A functional site may contain a signal of "turning on/off" or "switching to 1/0". The signal held in a functional site is sent out once it is attached by a spider. When a spider attaches to a site holding a signal, the signal "turning on/off" is sent to another site, setting its state "on" or "off"; the signal "switching to 1/0" is sent to the spider, changing its value to 1 or 0. When a functional site sends out its signal, it has no signal remaining. Signal transmission is allowed between a site and

a spider that is attached to the site, or between two sites that are adjacent to each other. These features could be implemented via DNA strand displacement as we shall discuss further in Chapter 8. We will discuss the AND and OR gate designs in Section 3.2 and the NOT gate design in Section 3.3.

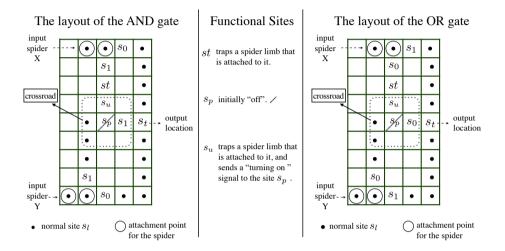

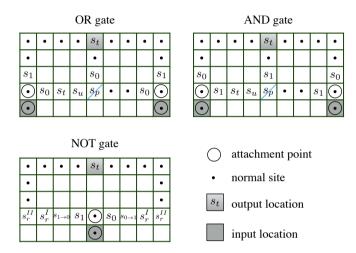

### 3.2 Designs of the AND and OR Gates

We use three types of functional sites  $s_t$ ,  $s_p$ , and  $s_u$  in the designs of the AND and OR gates. Site  $s_t$  can trap the spider attaching to it, so we place a site  $s_t$  at the output location of the gate. The AND gate and OR gate each have two input spiders initially located at the two input locations, which are two junctions as shown in Figure 3.1. Each input spider selects one of two possible paths when computation begins, where one path leads to the output location without any functional sites and the other path is merged into a crossroads in the middle of the lattice. We place an initially "off"-state site  $s_p$  at the heart of the crossroads, which blocks the central path from the crossroads to the output location. We place a site  $s_u$  adjacent to site  $s_p$ , which will send a "turning-on" signal to unblock site  $s_p$  when a spider attaches to it, and trap that spider at the same time. The cooperation between sites  $s_u$  and  $s_p$  guarantees that only when both spiders meet at the crossroads can a spider take the central path to the output location.

Figure 3.2 shows the layout of the AND gate and OR gate. We now explain how the AND gate works under all four possible input assignments; the OR gate follows a similar design. In the AND gate, the two input spiders X and Y are initially placed at two junctions as their input locations. When spiders X and Y are both 0, they both take the path starting with site  $s_0$ , which leads to the output location without any functional sites. In this case, whichever spider reaches the output location will have value 0. The reporting spider reports that the result of  $0 \wedge 0$  is 0. When spider

X=0 and spider Y=1, spider Y takes the path starting with site  $s_1$ , and becomes stuck at the crossroads because site  $s_p$  is "off". Spider X takes the path starting with site  $s_0$ , and will eventually reach the output location, reporting the result of  $0 \wedge 1$  is 0. When spider X=1 and spider Y=0, spider X gets to the crossroads via the path starting with site  $s_1$ , and is trapped at the crossroads due to the sites  $s_t$  and  $s_u$  placed on that path. Spider Y is the only spider that can reach the output location in this case, reporting the result of  $1 \wedge 0$  is 0. When both spiders are 1, they meet at the crossroads. Site  $s_p$  is turned on by the signal sent from site  $s_u$ , so spider Y can take the central path leading to the output location. Since spider X is trapped at the crossroads, only spider Y can reach the output location, reporting the result of  $1 \wedge 1$  is 1. (The preceding description considers a gate in isolation. In Section 3.4, however, we will introduce gate cascades, in which a trapped spider at the output location of an upstream gate is set free and enters the downstream gate via a set of functional sites that connects the two gates.)

Following a similar design, the layout of the OR gate is shown in Figure 3.2. When both spiders are 0, they meet at the crossroads. Spider X is trapped on sites  $s_t$  and  $s_u$ , and spider Y takes the unblocked central path to the output location, reporting the result of  $0 \vee 0$  is 0. Under other input assignments, the 0-valued spider takes the path to the crossroads and becomes stuck there: only the 1-valued spider can reach the output location, reporting the result of  $1 \vee 0$ ,  $0 \vee 1$ , and  $1 \vee 1$  is 1.

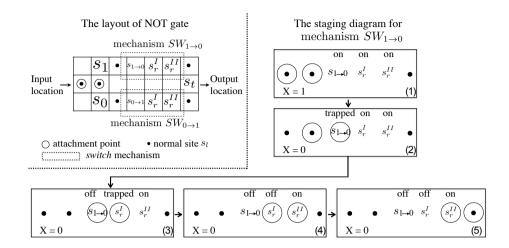

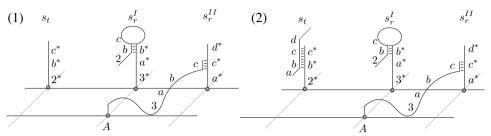

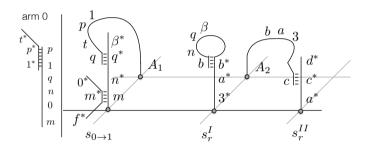

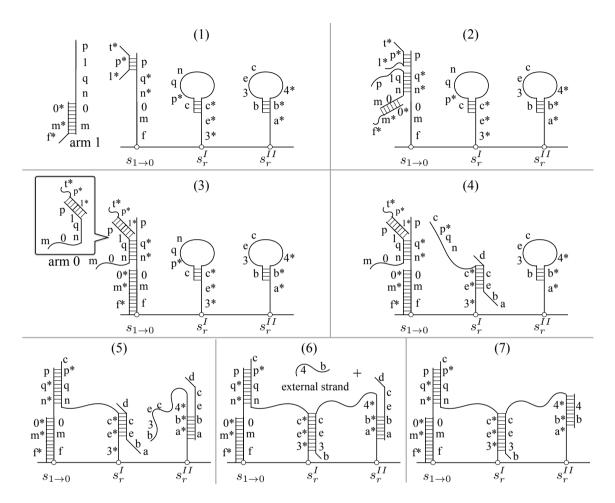

### 3.3 Design of the NOT gate

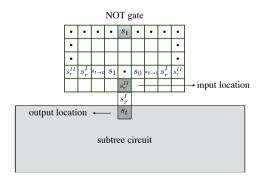

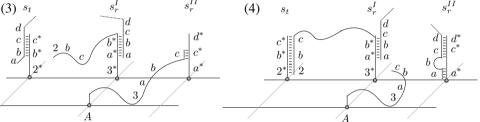

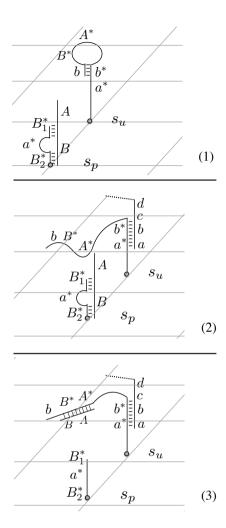

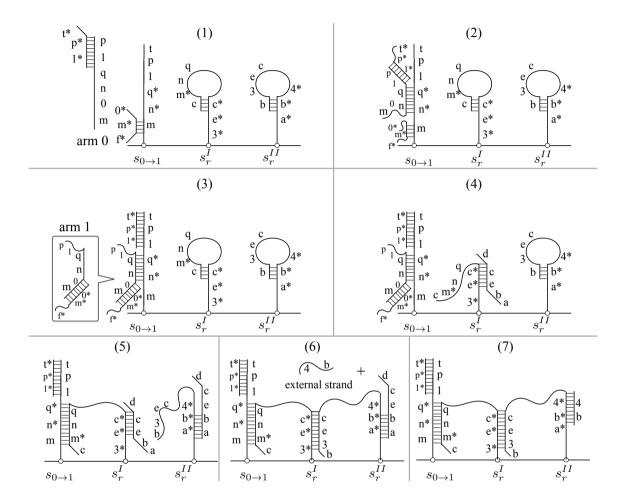

We use five types of functional sites in the NOT gate design. As shown in the layout of the NOT gate in Figure 3.3, site  $s_t$  which can trap a spider that attaches to it is placed on the output location. Sites  $s_{1\to 0}$ ,  $s_r^I$ ,  $s_r^{II}$  and sites  $s_{0\to 1}$ ,  $s_r^I$ ,  $s_r^{II}$  form two different switch mechanisms  $SW_{1\to 0}$  and  $SW_{0\to 1}$  that are laid on two separate paths.

The NOT gate has one input spider which is initially placed at a junction as the input location. Two separate paths branch out from the junction: one is taken by the 1-valued spider and contains mechanism  $SW_{1\to 0}$  that changes the spider value to 0, whereas the other is taken by the 0-valued spider and contains mechanism  $SW_{0\to 1}$  that changes the spider value to 1. When a spider moves through a *switch* mechanism, its value is switched and its backward route is cut off. We explain how mechanism  $SW_{1\to 0}$  works with a 1-valued spider as an example; mechanism  $SW_{0\to 1}$  works analogously.

Mechanism  $SW_{1\to 0}$  is formed by three neighboring functional sites along the horizontal direction:  $s_{1\to 0}, s_r^I, s_r^{II}$ . We use a staging transition diagram in Figure 3.3 to describe how mechanism  $SW_{1\rightarrow 0}$  changes a 1-valued spider to be 0, and cuts off the backward route of the spider. A stage transition shows the change of the spider's location, value, or the site states. At stage (1), all sites are "on" initially. Site  $s_{1\to 0}$  can trap a spider, and contains a "switching to 0" signal that will be sent to its left site when a spider attaches to it. Therefore, when a 1-valued spider attaches to  $s_{1\to 0}$ , it is trapped and receives the signal changing its value to 0, causing a transition to stage (2). At stage (2), since the limb trapped at site  $s_{1\to 0}$  cannot move back, the spider can only move forward by attaching to site  $s_r^I$ , which traps the spider and sends out a "turning off" signal to its left site. When site  $s_{1\to 0}$  receives that signal and turns itself "off", we get to stage (3). At stage (3), the limb trapped on  $s_r^I$  cannot move back, and the spider can only move forward by attaching to site  $s_r^{II}$ , which sends a "turning off" signal to its left site. When  $s_r^I$  receives that signal and turns itself "off", we get to stage (4). At stage (4), the limb on  $s_r^I$  can transit to a normal site on the right of  $s_r^{II}$ , while the limb on  $s_r^{II}$  cannot move back to  $s_{1\to 0}$  which is "off". The spider can only move forward to get to stage (5). At stage (5), sites  $s_r^I$  and  $s_r^{II}$  are "off", and the spider cannot walk back. When a spider goes through these five stages, its value is switched and its backward route is cut off. The mechanism  $SW_{0\to 1}$  comprising  $s_{0\to 1}, s_r^I, s_r^{II}$  follows similar staging transitions, the only difference

being that a 0-valued spider becomes 1 in the stage transition (1) to (2).

### 3.4 Gate Cascades

To construct a large logic circuit, we need to cascade logic gates of the three kinds defined in Section 3.2 and Section 3.3. A wire w connecting an upstream gate and a downstream gate is composed of contiguous normal sites  $s_l$ . To ensure that the spider that reaches the output location exits the upstream gate and never goes back to it, we place two additional sites  $s_r^I$  and  $s_r^{II}$  after site  $s_t$  on the output location, forming an exit mechanism which cuts off the backward route of a spider that moves through it.

The mechanism exit follows similar staging transitions to mechanism  $SW_{1\to 0}$  shown in Figure 3.3. It consists of three neighboring functional sites along the horizontal direction:  $s_t, s_r^I, s_r^{II}$ . We explained the functionality of site  $s_r^I$  and  $s_r^{II}$  at the end of Section 3.3. Site  $s_t$  is designed to trap the spider. Therefore, a staging transition diagram for mechanism exit is similar to the one shown in Figure 3.3, with the only difference that the spider value is unchanged throughout the five stages. For a downstream gate with two inputs, its two input spiders may arrive at different times. Computation of the downstream gate begins when either input spider enters the gate, and the asynchronous arrival of input spiders will not influence the computation accuracy of the gate.

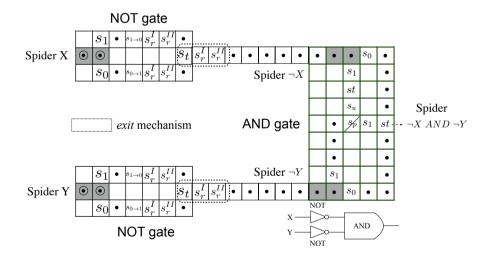

Figure 3.4 illustrates a simple logic circuit implemented by cascading two NOT gates as the inputs to an AND gate. The output location of each NOT gate is connected to an input location of the AND gate via the *exit* mechanism. Spider X and spider Y start to move in the two NOT gates concurrently. When the two spiders move out of the NOT gate, their backward routes are cut off due to the *exit* mechanisms, and they have their values changed to  $\neg X$  and  $\neg Y$ . When either

spider enters the AND gate, gate computation begins, eventually yielding the result  $\neg X \land \neg Y$ .

### 3.5 Simulation Results

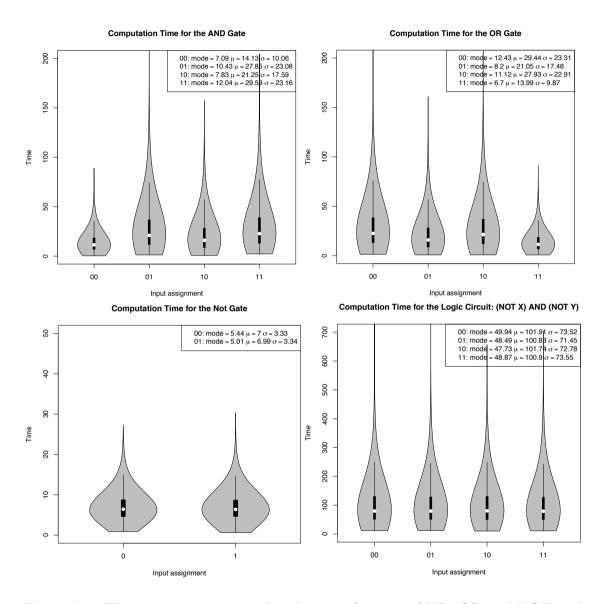

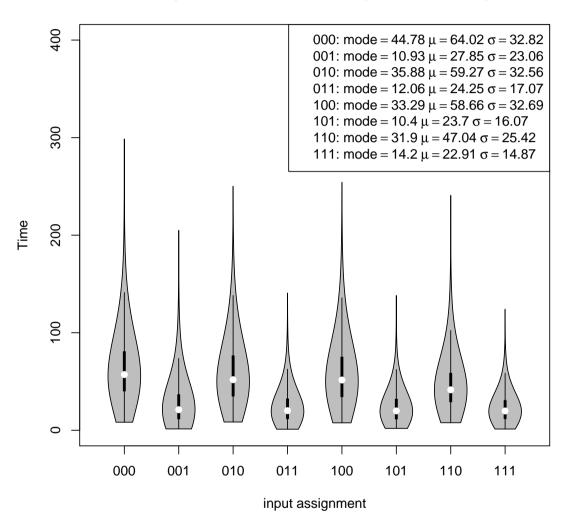

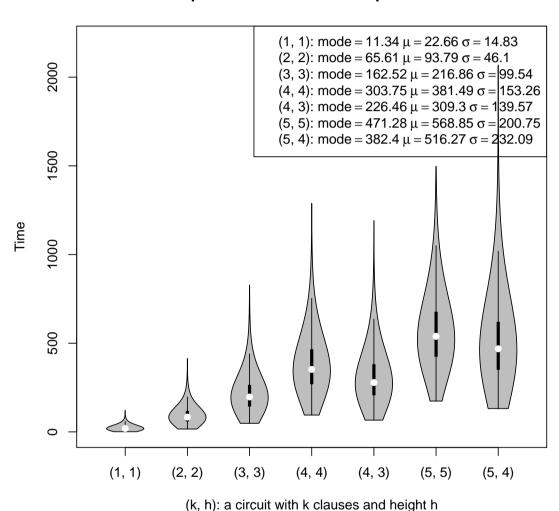

The movement of the spiders can be modeled as a continuous-time Markov process. We use a kinetic Monte Carlo algorithm to simulate gate computations. For each gate, under different assignments, we investigate the computation time using 10,000 iterations in each simulation. We assume the transition rate (the rate at which a spider limb transits from one site to another) of each spider is 1.

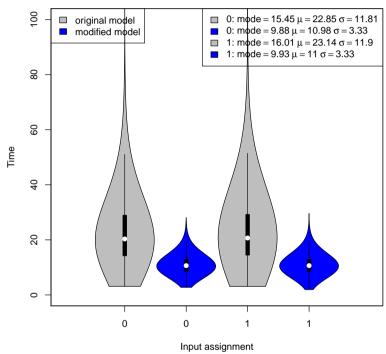

Simulation results for the three basic gates AND, OR, and NOT are shown in Figure 3.5. The computation time of a logic circuit  $\neg X \land \neg Y$  is shown in Figure 3.5 as well. Under a certain input assignment, the computation time follows a long-tailed distribution because spiders move stochastically. The computation time is the time spent on traversing the path taken by the reporting spider that reaches the output location. In all simulation runs, the output spider produced the correct output value.

Figure 3.2: The layout of the AND gate and OR gate. Three functional sites  $s_t$ ,  $s_p$ , and  $s_u$  used in the designs of these two gates are listed in the middle column. Normal site  $s_1$  can only bind to an 1-valued spider and normal site  $s_0$  can only bind to a 0-valued spider. In the AND gate, when both spiders are 1, they meet at the crossroads in the middle. Spider X gets trapped at sites  $s_t$  and  $s_u$ , site  $s_u$  sends a "turning-on" signal to unblock site  $s_p$ , allowing spider Y = 1 to take the unblocked central path from site  $s_p$  to the output location. Under other input assignments, the 1-valued spider gets stuck at the crossroads, so only the 0-valued spider can reach the output location. Therefore, the AND gate yields 1 when both spiders are 0, they meet at the crossroads in the middle and only spider Y = 0 can reach the output location. Under other input assignments, the 0-valued spider gets stuck at the crossroads, so only the 1-valued spider can reach the output location. Therefore, the OR gate yields 0 when both spiders are assigned 0, and yields 1 in all other cases.

Figure 3.3: The layout of gate NOT is shown in the figure. The function of mechanism  $SW_{1\to 0}$  is to switch a spider's value from 1 to 0 and cuts off its backward route. We show how mechanism  $SW_{1\to 0}$  works in a staging transition diagram, where the spider value is expressed as X and the state of each functional site is shown above it.

Figure 3.4: A logic circuit:  $(\neg X \land \neg Y)$ . The input locations of each gate are highlighted in grey. Spiders X and Y exit the NOT gate, becoming spider  $\neg X$  and  $\neg Y$  after passing through the *exit* mechanisms. The AND gate computation begins whenever a spider enters the AND gate. The spider reaching the output location of the AND gate represents the computation result  $\neg X \land \neg Y$ .

Figure 3.5: The computation time distributions for gates AND, OR and NOT under four possible input assignments are shown in the figure. Each group in one gate represents a time distribution under one assignment. The mode, mean time and standard deviation for each group is shown in the legend. The computation time distributions for the logic circuit  $(\neg X \land \neg Y)$  in Figure 3.4 under four possible input assignments are shown in the figure. Each group of data plots is generated from 10,000 simulation trajectories. We use the *vioplot* library in R to plot the data.

## Chapter 4

## **Model Definition**

The molecular spider circuit proposed can be modeled as a continuous time Markov model. The environment in this model contains normal sites that are non-alterable and functional sites that are alterable via the interactions between the molecular spiders and the sites. Here we first give the definitions of the site types and transition rules of functional sites, and then the definition of the entire model.

### 4.1 Site types and transition rules

Sites are categorized into normal sites and functional sites. A normal site  $s \in S_{norm} = \{s_l, s_0, s_1\}$  has no state. Site  $s_l$  binds to the spider's leg. Sites  $s_0$  and  $s_1$  bind to the spider's arm if it has type 0 or 1, respectively.

A functional site  $s \in S_{fun}$  has a state which could be one of "on", "off" and "trapped". The site state transition diagram is:

$$\downarrow \\ trapped \longrightarrow off$$

A spider limb can only attach to an "on"-state site. An "off"-state site is nonalterable. The limb trapped on a "trapped"-state site cannot leave the site by itself. Whether a site can trap a spider is indicated by  $TR \in \{0,1\}$ : a site with TR = 1 will trap a spider when a limb attaches to it. A functional site may change the spider's value, or the state of another site, by sending out a *signal* to the spider or another site. Define

$$signal = (val, d) \text{ or } null, \text{ where } d \in \mathbb{Z}^2 \text{ and } val \in \{\text{on, off, trapped}, 1, 0\}.$$

(4.1)

Suppose a functional site is located at (x, y). If it holds a  $signal = (val, (d_x, d_y))$  then it sends the signal to the location  $(x + d_x, y + d_y)$ , setting the state of the site located there to val. When d = (0,0), the val field of the signal is either 1 or 0, which is sent to the spider, setting the spider's value to 1 or 0.

Therefore, a functional site  $s \in S_{fun}$  can be defined as

$$s = (state, TR, signal). (4.2)$$

The signal held in a site is sent out once a spider limb attaches to the site. When a signal is sent out, the site has no signal remaining, which is express as s = (state, TR, null). A functional site s = (on, null) is equivalent to a normal site, which is non-alterable. Once a signal is received by a site or a spider, the site state or the spider's value is changed according to the signal.

In the logic circuit construction, we use two functional sites  $s_u$  and  $s_p$  in the AND gate and OR gate, and we design a set of functional sites that form different mechanisms in the NOT gate and the gate cascades. Table 4.1 gives the definitions of these functional sites and the transition rules applied to them. A functional site s transits to site s' in the second column, either by receiving a signal or being attached by a spider limb. If s holds a signal, it causes other changes in the last column. In table 4.1, the updated sites s' in the second column is either a normal site or a trapped site. According to the site state transition diagram, a trapped site can only transit

Table 4.1: Definitions of different functional sites used in the circuit construction and the transition rules applied to them. Suppose the location of the site is (x, y), define  $(x', y') = (x + d_x, y + d_y)$ . We use A to indicate the Boolean value of a molecular spider. The value of A is either 1 or 0.

| Transition Rules                             |                                           |                              |  |  |  |

|----------------------------------------------|-------------------------------------------|------------------------------|--|--|--|

| functional site                              | updated site                              | other changes                |  |  |  |

| $s_t = (\text{on}, 1, null)$                 | $s'_t = (\text{trapped}, 1, null)$        |                              |  |  |  |

| $s_{1\to 0} = (\text{on}, 1, (0, (0, 0)))$   | $s'_{1\to 0} = (\text{trapped}, 1, null)$ | A = 0                        |  |  |  |

| $s_{0\to 1} = (\text{on}, 1, (1, (0, 0)))$   | $s'_{0\to 1} = (\text{trapped}, 1, null)$ | A=1                          |  |  |  |

| $s_r^I = (\text{on}, 1, (\text{off}, d))$    | $s_r^{I'} = (\text{trapped}, 1, null)$    | site at $(x', y')$ turns off |  |  |  |

| $s_r^{II} = (\text{on}, 0, (\text{off}, d))$ | $s_r^{II'} = (\text{on}, 0, null) = s_l$  | site at $(x', y')$ turns off |  |  |  |

| $s_u = (\text{on}, 0, (\text{on}, d))$       | $s_u' = (\text{on}, 0, null) = s_l$       | site at $(x', y')$ turns on  |  |  |  |

| $s_p = (\text{off}, 0, null)$                | $s_p' = (\text{on}, 0, null) = s_l$       |                              |  |  |  |

|                                              | when a "turning-on" sig-                  |                              |  |  |  |

|                                              | nal is received                           |                              |  |  |  |

to a "off"-state site that is non-alterable by itself. Since no signals are designed to turn on these "off"-state sites transited from the trapped sites, these "off"-state sites are non-alterable finally. Therefore, all the functional sites in Table 4.1 are alterable initially and become non-alterable finally. The functional sites used in our design are

$$\{s_t, s_{1\to 0}, s_{0\to 1}, s_r^I, s_r^{II}, s_u, s_p\},\$$

where each site s among them includes its site transitions under the transition rules described in Table 4.1. The set of site types is  $S = S_{norm} \cup S_{fun}$ .

A mechanism is a set of neighboring mechanism sites along the same direction. We design three different mechanisms used in the logic circuit construction. The switch mechanism  $SW_{1\to 0}$  ( $SW_0 \to 1$ ) contains sites  $s_{1\to 0}(s_{0\to 1}), s_r^I, s_r^{II}$ , where sites  $s_r^I$ ,  $s_r^{II}$  contains the signal of (off, (-1,0)) which can block its left site. When a spider moves over the switch mechanism, its value is flipped, and its backward route is cut off. The exit mechanism contains sites  $s_t, s_r^I, s_r^{II}$ . When a spider moves over this mechanism, its backward route is cut off.

When a spider limb leaves a site, this limb can reach 4 sites geometrically (shown in Figure 2.1). Since sites have different types, whether a site is available for a limb of a spider depends on the spider value and the site types.

**Definition 1.** Given a spider with value A and a reachable site, we check if the site is available by using the following conditions:

- if the site is already occupied by a limb, it is not available.

- else:

- 1. if the site is a normal site:

- (a) if the site is  $s_l$ , it is available;

- (b) if the site is  $s_1$  and A = 1, it is available;

- (c) if the site is  $s_0$  and A = 0, it is available;

- 2. else if the site is a functional site:

- (a) if the site is  $s_{1\to 0}$  and A=1, it is available;

- (b) if the site is  $s_{0\to 1}$  and A=0, it is available;

- (c) if the site is "on"-state, it is available;

- 3. else, the site is not available.

Using Definition 1, every site is examined among the four reachable sites shown in Figure 2.1. Those available sites are put into a set  $\mathcal{AV}$ .

### 4.2 Model definition.

The *active* multi-spider system with normal sites and alterable sites can be modeled as a continuous-time Markov process. The state of the model is defined as

$$X = (S_1, S_2, \dots, S_n, E), \tag{4.3}$$

where  $S_i = (P_i, A_i)$  ( $1 \le i \le n$ , n is the number of spiders) describes the state of the i-th spider. Set  $P_i = (p_a^i, p_b^i)$  contains attachment points for the i-th spider, and  $A_i \in \{0,1\}$  represents the Boolean value of the spider. The lattice configuration  $E: \mathbb{Z}^2 \to S$  shows the layout of different sites, where S is the set of site types. Normal sites can be regarded as having state "on", TR = 0 and no signal, so the lattice configuration can be redefined as

$$E: \mathbb{Z}^2 \to \{\text{on, off, trapped}\} \times \{1, 0\} \times \mathbb{S},$$

where  $\mathbb{S}$  represents the set of signals.

Given a model state  $X = (S_1, S_2, \ldots, S_n, E)$  at time t, if a limb leaves an attachment point  $p \in P_i \in S_i$ , we use Definition 1 to obtain a set of available sites  $\mathcal{AV}$ . At time  $t + \delta$ , this limb transits to  $p' \in \mathcal{AV}$ , changing the set of attachment points to  $P'_i = P_i - \{p\} \cup \{p'\}$ . The transition rules are used to update  $A_i$ , so that the i-th spider state becomes  $S'_i = (P'_i, A'_i)$ . The transitions rules also updates E, thus the new state is

$$X' = (S_1, S_2, \dots, S_{i-1}, S'_i, S_{i+1}, \dots, S_n, E').$$

## Chapter 5

### Verification

Verification is the procedure of checking if the given circuit yields the expected results under all possible input assignments. The verification of each single gate (AND, OR, NOT) discussed in previous sections checks if all spiders take the intended paths during the gate computation under all possible input assignments. Assuming all mechanisms work properly in each gate, spiders in each gate always take the intended paths under all input assignments, and only one spider can exit the gate. Therefore, all single gates are verified to work properly under all input assignments. Since our design guarantees modularity, and since all gates are verified to work properly, if all gates in a circuit are cascaded correctly and do not interfere with each other, the circuit is verified to work properly. Therefore, to verify a circuit, it remains to check if the layout of the circuit ensures correct cascading.

### 5.1 Geometric Layout Generation

We develop an algorithm to generate the circuit layout. Given a Boolean function, the algorithm converts the function into a circuit tree and generates a two-dimensional

#### Chapter 5. Verification

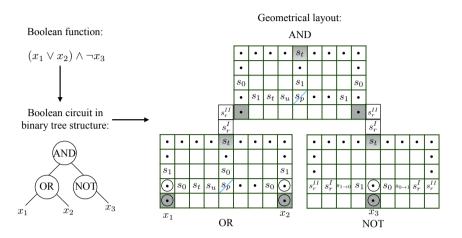

layout according to the circuit tree. A Boolean function can be converted into a logic circuit composed of input variables and logic gates of AND, OR, and NOT. In our design, since all gates have one output and at most two inputs, the logic circuit (which is assumed to be feedforward) can be represented by a binary tree. Each tree node represents a gate. A connection between two nodes represents the cascade between two gates, where the output location of the upstream gate (child node) is connected to the input location of the downstream gate (parent node). Our design does not have the fan-out gate that takes one input and outputs multiple copies of the input; instead each variable occurrence is represented by a molecular spider. For a Boolean function in which a variable appears k times  $(k \geq 1)$ , we must prepare the circuit by placing k molecular spiders, each carrying the Boolean value of that variable, at the appropriate leaf positions in the corresponding binary tree. Using the binary tree representation, the geometric layout problem of a circuit is converted to the problem of constructing a binary circuit tree that represents the given circuit such that gates do not interfere with each other. In the circuit tree construction, the layouts of the tree nodes should not have overlaps, and the layout of a connection between two nodes only joins the layout of the upstream gate at its output location with the layout of the downstream gate at its input location.

Our layout generation algorithm includes two parts: circuit conversion converts a given Boolean function into a circuit tree, whereas circuit tree construction constructs the circuit tree recursively. The circuit tree is a binary Abstract Syntax Tree (AST) representation of the Boolean formula. There are numerous tools that generate the AST for a given Boolean formula, so we only give details of circuit tree construction here, which re-designs all the gates to let them have the same size of geometric layout and constructs the circuit tree by recursively merging subtrees from the leaf nodes to the root node.

### 5.2 Redesign of the Gates.

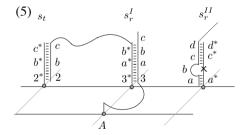

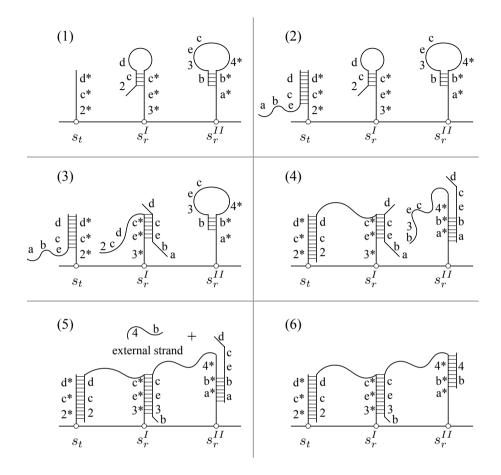

Figure 5.1 shows the layouts of single gates for AND, OR, and NOT. Define  $E_g$ :  $\mathbb{Z}^2 \to S$  where S is the set of site types and  $g \in \{AND, OR, NOT\}$ ,  $E_g$  is the layout of gate g.

Figure 5.1: Geometric layouts of three basic gates with the same size.

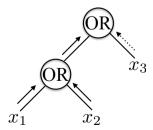

A Boolean function can be expressed in a form of Boolean circuit that is composed of AND gates, OR gates, and NOT gates. Since all the gates have only one output location and at most two input locations, assuming each variable occurrence corresponds to a molecular spider, the Boolean circuit can be represented by a binary AST. A tree node represents a gate, its child nodes represent the upstream gates connected to it, and its parent node is the downstream gate it connects to. For example, a Boolean circuit  $(x_1 \vee x_2) \wedge \neg x_3$  can be represented by a binary tree containing three nodes, where the root node is AND gate and it has two child nodes of OR gate and NOT gate. Each node can be mapped to its corresponding layouts shown in Figure 5.1. The child-parent relation is mapped to a contiguous set of sites connecting an upstream gate and a downstream gate. Therefore, given a Boolean circuit in a binary tree structure, the geometric layout of the circuit is converted to the

#### Chapter 5. Verification

construction of the tree. Figure 5.2 shows an example of this conversion procedure.

Figure 5.2: A Boolean function  $(x_1 \lor x_2) \land \neg x_3$  can be represented by a binary tree. Each tree node is mapped to a gate layout among the layouts predefined in Figure 5.1. The geometric layout of the circuit can be converted into the construction of a binary tree using the predefined tree nodes.

### 5.3 Circuit Tree Construction.

Figure 5.1 has provided the layouts of all gates that will be used in the circuit construction. Given a circuit tree, the generation of the circuit layout is to recursively merge the layout of the root node with the layouts of its subtrees. The merging procedure follows a Depth-First-Search (DFS) routine. Leaf nodes representing the input variables do not have layouts. The result of merging a root node (gate) with a leaf node (variable) is the layout of the root node and additional information indicating the initial position of the variable. For example, circuit  $(x_1 \vee x_2) \wedge \neg x_3$  in Figure 5.2 is the result of merging the layouts of NOT gate (right subtree) and OR gate (left subtree) with the layouts of downstream gate AND (root node). The layout of the merged circuit  $(x_1 \vee x_2) \wedge \neg x_3$  includes the cascading paths between gate AND and gates NOT, OR. Initial positions of variables  $x_1, x_2$  and  $x_3$  are also

#### Chapter 5. Verification

determined. We discuss the merging procedure between a root node (R) and its subtrees (left subtree Left and right subtree Right) in two cases.

#### 5.3.1 Case 1: the root node is a NOT gate

Suppose the NOT gate only has the right subtree. If Right is a leaf node representing a variable, we place that variable at the input location of the NOT gate and return the layout of the NOT gate. Otherwise we create a new layout  $E_{merged}: \mathbb{Z}^2 \to S$  containing the layouts of the root node  $E_R$  and the right subtree  $E_{Right}$ . In the merged layout, as shown in Figure 5.3, the subtree tree is placed below the root node and they keep unit distance to each other vertically. Cascading path between the output location of the subtree and the input location of the root node is constructed using the normal sites. An exit mechanism consisting of sites  $s_t, s_r^I$  and  $s_r^{II}$  is placed on the cascading path connecting the output location of the subtree circuit and the input location of the root node.

Figure 5.3: Merging the layout of a NOT gate with its subtree circuit.

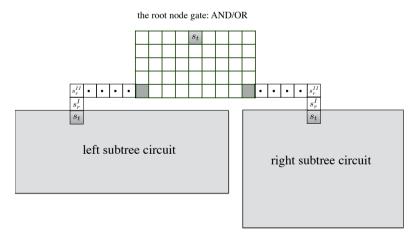

### 5.3.2 Case 2: the root node is an AND/OR gate

If two subtrees are both variables, we return the layout of the root node gate and place the variables at the input locations of the root node gate. If one of the subtree circuits is a variable and the other is a circuit, we use the merging procedure shown in Figure 5.3 to place the subtree circuit below the root node gate and initialize the position of that variable. If both subtrees are circuits, we create a new layout  $E_{merged}: \mathbb{Z}^2 \to S$  containing the layouts of the root node  $E_R$  and the subtrees  $E_{Left}$  and  $E_{Right}$ . In the merged layout, the top of the left subtree is aligned horizontally with the top of right subtree. The two subtrees keep unit distance to each other horizontally. The root node gate is placed in the middle between the output locations of subtrees Left and Right. The root node gate keeps unit distance vertically to its subtrees. Figure 5.4 shows the procedure of merging a root node gate with its two subtree circuits. Two cascading paths containing the exit mechanisms connect the output locations of the subtree circuit and the input locations of the root node gate.

Figure 5.4: Merging the layout of an AND/OR gate with its subtree circuits.

Given a circuit tree that is represented by a binary AST, the procedure of the circuit tree construction ensures that every node in the tree is cascaded correctly with its subtrees. For each node of the tree, its layout and the layouts of its subtrees do

## Chapter 5. Verification

not have overlaps, thus all the gates in the tree do not influence each other. Since all single gates are verified to work properly under all input assignments, and since the circuit layout generation algorithm guarantees the correct cascades between different gates in the circuit, the entire circuit generated using our algorithm is verified to work properly under all input assignments.

# Chapter 6

# Performance

The performance of a circuit is usually measured by its computation speed and computation correctness, and the ability to accommodate the increasing size of the circuit (the number of input variables or the circuit depth). In this section, we analyze the complexity of our design and present some simulation results for a set of example circuits.

# 6.1 Complexity Analysis

In a single gate, the computation time  $t_{\text{gate}}$  is the traversal time of the spider that reaches the output location. Since the spider moves on the track stochastically, the computation time  $t_{\text{gate}}$  is a random variable following a long-tailed distribution, as shown in Figure 3.5.

When a spider leaves a gate or enters a gate, its backward route is cut off due to the functionality of the *exit* mechanism, so the computation time of a single gate  $t_{gate}$  can be used to estimate the computation time t of a circuit. For any n-variable Boolean function, it can be transformed into 3-CNF, which is a conjunction of m

## Chapter 6. Performance

clauses, each a disjunction of at most three literals. Since the circuit design allows parallel evaluation, for a clause  $m_i = (l_1^i \vee l_2^i \vee l_3^i)$ , the computation time of  $m_i$  is

$$t_{m_i} \le 2 \times (t_{\text{OR}} + t_{\text{NOT}}) = O(1).$$

Since each clause needs time  $t_{m_i}$ , to evaluate m clauses in parallel, we need  $\log m$  AND gate computations that cost  $t_{\text{AND}} \times \log m$ , which totally use time

$$t = t_{\text{AND}} \times \log m + t_{m_i} = O(\log m).$$

For any Boolean function in 3-CNF with m clauses, there are at most 3m spiders representing the literals. For each clause, at most three NOT gates and two OR gates are needed if all the literals are the negation of a variable, which is a constant number. For m clauses, there need to be m-1 AND gates. Therefore, the total space complexity is O(m). Hence, the circuit design is scalable because circuit size in the design scales linearly with formula size, and evaluation time is logarithmic in the formula size.

# 6.2 Simulation Results

Here we look at how the computation time varies with the size of the circuit on a set of examples. We investigate a small set of circuits that are in the form of 3-CNF where there are no NOT gates. We first investigate a single clause  $(x_1 \lor x_2 \lor x_3)$ . Computation time distributions of this single-clause circuit under all possible input assignments are shown as the violin plots in Figure 6.2. Each group of plots in Figure 6.2 represents the computation time distribution under one input assignment. The results show that computation time is influenced by the input assignment for a fixed circuit. Different input assignments lead to different computation paths for the

#### Chapter 6. Performance

input spiders, where each computation path starts from the initial location of the spider and ends at the output location of the circuit. A spider taking the shorter path is more likely to be the reporting spider to reach the output location, which terminates the computation. Therefore, computation time is the time which the reporting spider takes to terminate the computation. Since different input assignments lead to different computation paths of the reporting spider, and different lengths lead to different computation time, computation time for a fixed circuit varies with different input assignments. For the single-clause circuit  $(x_1 \lor x_2 \lor x_3)$  whose circuit structure is shown in Figure 6.1, there are two lengths of computation paths of the reporting spider. When  $x_3 = 1$ , spider  $x_3$  has a shortcut to the output location (indicated by the dotted arrow); otherwise spider  $x_3$  would wait in the root OR gate until either spider  $x_1$  or spider  $x_2$  takes the path indicated by the solid arrows to participate in the root-node gate computation. When  $x_3 = 1$ , spider  $x_3$  is more likely to be the reporting spider. The right path taken by spider  $x_3$  is relatively shorter, so the computation time is relatively shorter. In the results shown in Figure 6.2, four groups of plots with  $x_3 = 1$  are similar to each other, and the mean time and standard deviations of these four groups are smaller compared with other four groups because  $x_3$  is more likely to be the reporting spider and walks through a shorter path. When  $x_3 = 0$ , the reporting spider is more likely to take a longer path passing two gates, so the mean computation time and standard deviation are greater, as shown in the groups 000, 010, 100, and 110 of Figure 6.2.

Figure 6.1: The circuit structure of  $(x_1 \lor x_2 \lor x_3)$ . In our design the maximum number of fan-in of a single gate is 2, and the fan-out is 1 for all gates.

#### Chapter 6. Performance

Table 6.1: Example circuits evaluated in this section.

| no. | (k,h) | Circuit Structure                                                                                                                                     |

|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.  | (1,1) | $x_1 \lor x_2 \lor x_3$                                                                                                                               |

| 2.  | (2,2) | $(x_1 \lor x_2 \lor x_3) \land (x_1 \lor x_2 \lor x_4)$                                                                                               |

| 3.  | (3,3) | $(x_1 \lor x_2 \lor x_3) \land (x_1 \lor x_2 \lor x_4) \land (x_1 \lor x_3 \lor x_4)$                                                                 |

| 4.  | (4,4) | $(x_1 \lor x_2 \lor x_3) \land (x_1 \lor x_2 \lor x_4) \land (x_1 \lor x_3 \lor x_4) \land (x_2 \lor x_3 \lor x_4)$                                   |

| 5.  | (4,3) | $((x_1 \lor x_2 \lor x_3) \land (x_1 \lor x_2 \lor x_4)) \land ((x_1 \lor x_3 \lor x_4) \land (x_2 \lor x_3 \lor x_4))$                               |

| 6.  | (5,5) | $(x_1 \lor x_2 \lor x_3) \land (x_1 \lor x_2 \lor x_4) \land (x_1 \lor x_3 \lor x_4) \land (x_2 \lor x_3 \lor x_4) \land (x_1 \lor x_2 \lor x_5)$     |

| 7.  | (5,4) | $((x_1 \lor x_2 \lor x_3) \land (x_1 \lor x_2 \lor x_4)) \land ((x_1 \lor x_3 \lor x_4) \land (x_2 \lor x_3 \lor x_4) \land (x_1 \lor x_2 \lor x_5))$ |

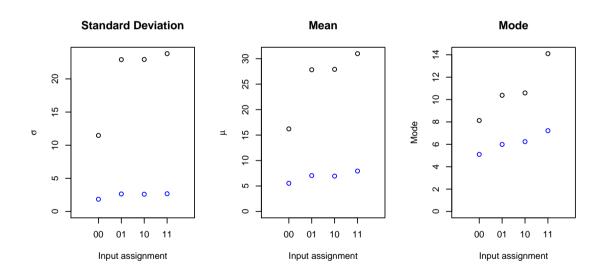

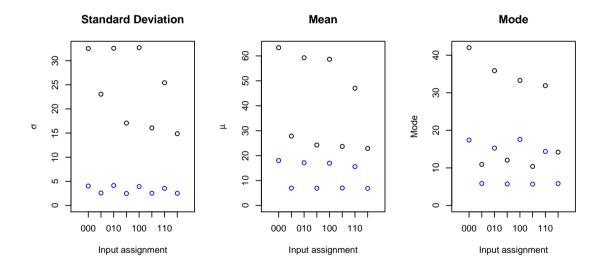

Assigning 1 to all the variables, we investigate a group of circuits in the form of 3-CNF where the number of clauses of the circuit is from 1 to 5. Figure 6.3 shows the simulation results. We use (k, h) to represent a circuit having k clauses and height h. Table 6.1 lists 7 different circuit structures that we will simulate. The results in Figure 6.3 show that as the circuit size (the number of clauses) increases, the mode, mean computation time, and standard deviation increase. Having fixed the size of the circuit, the mode, mean computation time, and standard deviation increase as the circuit height increases, which is reflected in the groups (4,4) and (4,3), and the (5,5) and (5,4) groups shown in Figure 6.3.

The result of complexity analysis shows that our circuit design scales linearly as the circuit size increases. We use simulation to investigate what factors influence circuit performance, and we find that different input assignments lead to different computation time distributions for a fixed circuit, and the mode, mean computation time, and standard deviation increase as the circuit size and circuit height increase when we fix the input assignment.

## Computation Time for Circuit (x1 OR x2 OR x3)

Figure 6.2: Simulation results of circuit  $(x_1 \lor x_2 \lor x_3)$  under all input assignments. Each group of plots represents the computation time of the circuit under one input assignment. Input assignments for variables  $x_1, x_2$  and  $x_3$  are represented by binary strings as shown in the legend. For example, 101 represents the input assignment  $x_1 = 1, x_2 = 0, x_3 = 1$ . The legend shows the mode, mean and standard deviation for each group. Each group of data plots is generated from 5000 simulation trajectories. We use the *vioplot* library in R to plot the data.

## **Computation Time for a Group of Circuits**

Figure 6.3: Simulation results of a group of circuits having clause number from 1 to 5 under the input assignments where all variables are 1. In the legend, each group (k,h) represents the computation time distribution of a circuit having k clauses and height h. We show the mode, mean time and standard deviation for each group in the legend. Each group of data plots is generated from 5000 simulation trajectories. We use the *vioplot* library in R to plot the data.

# Chapter 7

# Circuit Predictability

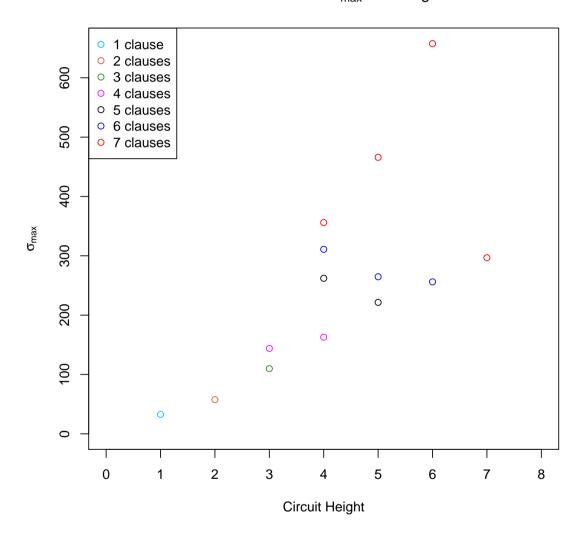

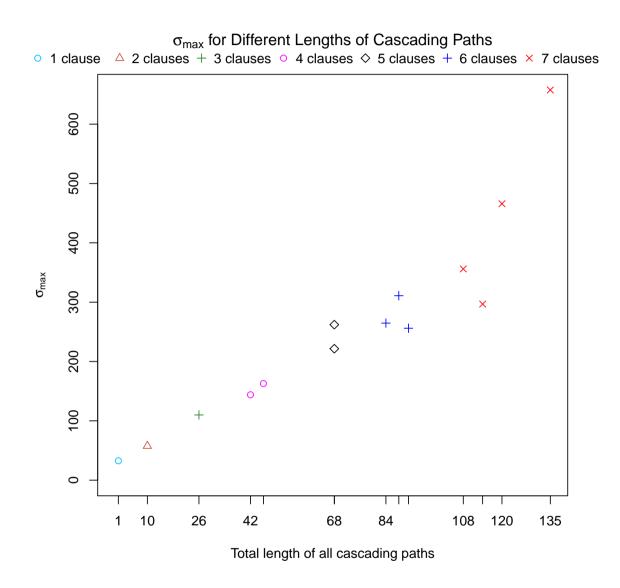

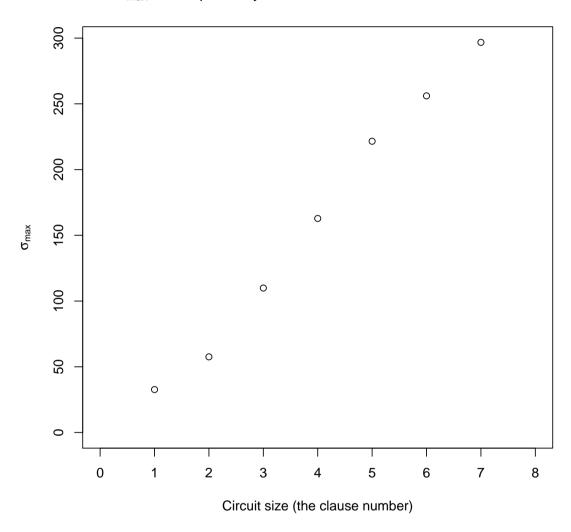

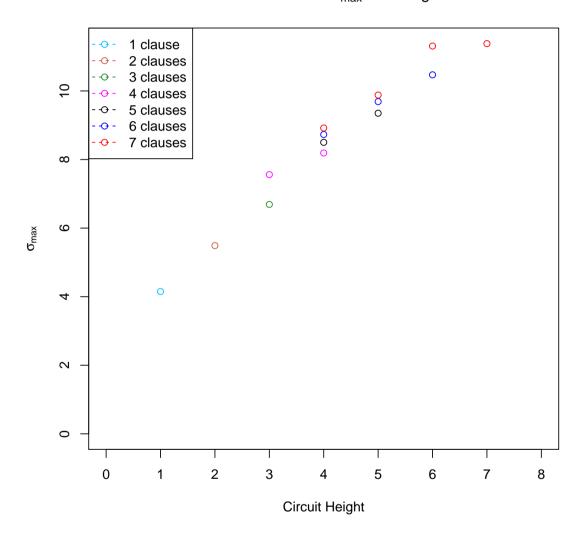

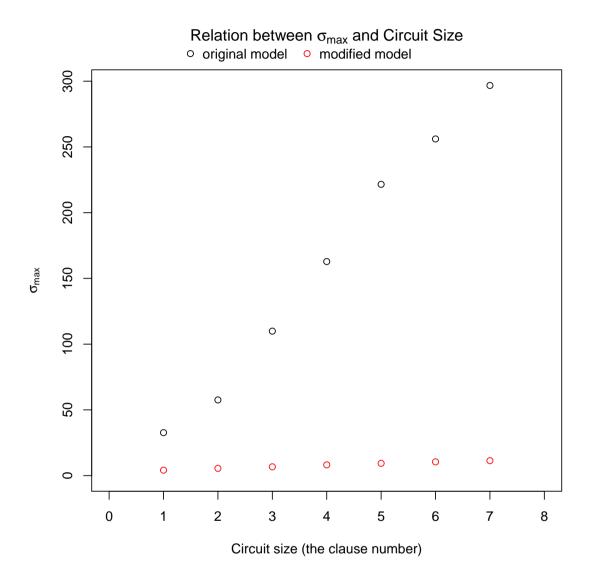

In Section 3.5 and chapter 6, we have shown simulation results for each single logic gate (AND, OR, NOT) and a group of circuits that are in 3-CNF (the clause number of these circuits is from 1 to 5). Simulation results show the computation time of a circuit follows a long-tailed distribution. As circuit size increases<sup>1</sup>, computation time variance increases, making it hard to predict circuit performance. Therefore, we should consider circuit predictability as an important measure to evaluate the circuit performance using the extended molecular spider system besides computation time and computation correctness. For a circuit under a certain input assignment, the smaller standard deviation of computation time  $\sigma$  indicates it is easier to predict the circuit. Simulation results in Chapter 6 show that different input assignments would lead to different computation time, thus leading to different time deviations. For a circuit having n variables, there are  $m = 2^n$  possible input assignments, and m different time deviations. Denote the maximum time deviation by  $\sigma_{max}$ , we use  $\sigma_{max}$  to measure the circuit predictability.

There we investigate the circuit in the form of 3-CNF, so the circuit size refers to the clause number k.

# 7.1 Improving Circuit Predictability

Improving circuit predictability means reducing  $\sigma_{max}$ . As discussed in Section 6.2, computation time is the time which the reporting spider takes to terminate the computation. Since molecular spiders move stochastically back and forth in the extended system, the less time they spend on walking backward the smaller time deviation will be obtained. To increase the circuit predictability, we need to reduce the time that the reporting spider spends on the backward route under all input assignments. To this end, we can shorten the lengths of all computation paths or change the behaviors of the molecular spiders to improve the circuit predictability. We propose two methods accordingly. **Method 1** reduces the height of the circuit tree. In this way, we believe the lengths of all computation paths can be shortened generally, and circuit predictability can be improved. **Method 2** makes molecular spiders move one-directionally on the preprogrammed track, thus the time spent on the backward route is eliminated and the time deviations under all input assignments are decreased.

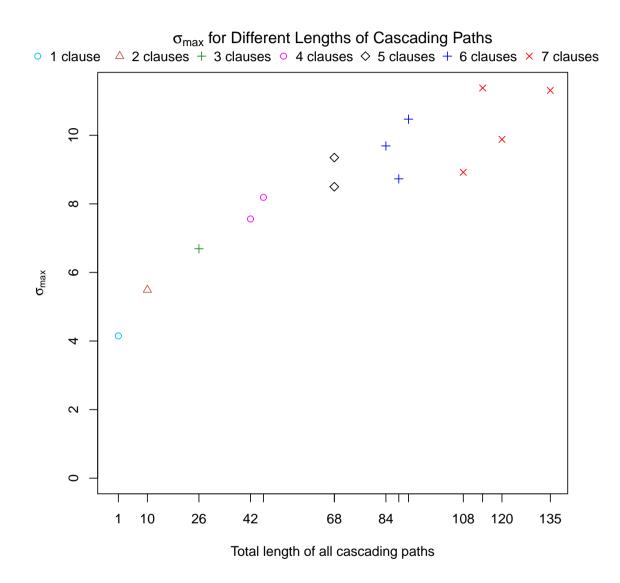

We will show whether **Method 1** and **Method 2** are valid in Sections 7.2 and 7.3 via simulations. For convenience, the circuits being investigated are cascaded in the form of 3-CNF without negation. We will simulate a group of circuits having between 1 and 7 clauses. For each circuit, there are different heights of circuit trees. We will calculate  $\sigma_{max}$  for different heights of circuit trees. In Section 7.2, we will present the relation between the circuit height and the circuit predictability, and judge whether **Method 1** is valid. In Section 7.3, we will compare the computation time deviations between two models, the original model where molecular spiders move bi-directionally and the modified model where molecular spiders only move forward. We call the modified model *One-directional* model, and we will judge whether **Method 2** can improve the circuit predictability.

For a circuit having k clauses, the possible height h of the circuit tree is

$$\lceil \log k \rceil + 1 \le h \le k,\tag{7.1}$$

so there are  $k - \lceil \log k \rceil$  different circuit heights for a k-clause circuit. Suppose the circuit has n variables, then there are  $2^n(k - \lceil \log k \rceil)$  number of computations that need to be simulated. Because we target exploring the relation between the circuit height and the circuit predictability, there is no need to explore all possible conditions of the input variables for a k-clause circuit. In order to make it computationally feasible, we assume each variable only appears once in a clause, and choose n to be the smallest possible value that could guarantee there are no duplicated clauses in the circuit. To avoid duplicated clauses, k and n must satisfy:

$$\binom{n}{3} \ge k. \tag{7.2}$$

The circuits being simulated in **Method 1** and **Method 2** can be expressed as a set  $\{(k,h)\}$ , where (k,h) denotes a circuit tree having k clauses and height h. The number of variables n and k,h satisfy constraint  $1 \le k \le 7$  and Equations (7.1) and (7.2).

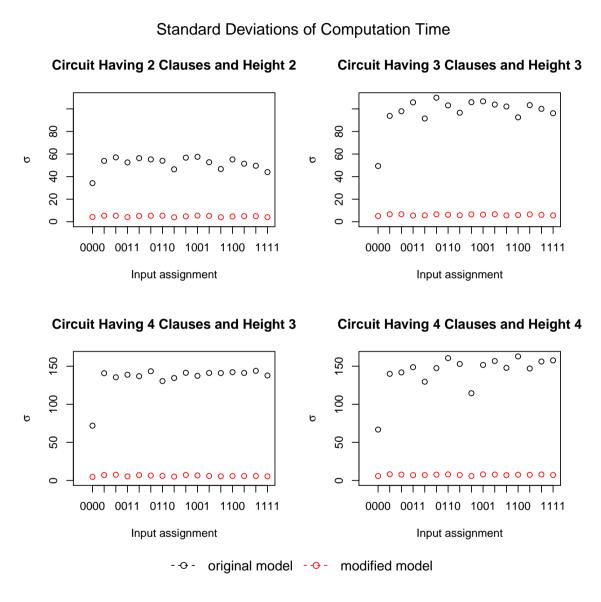

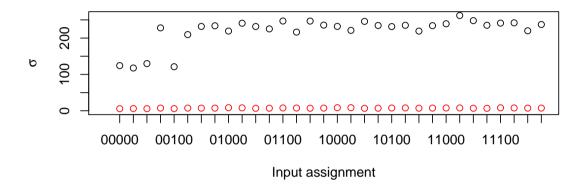

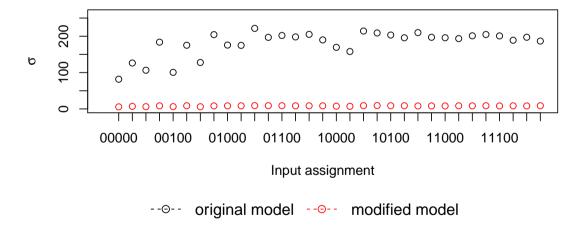

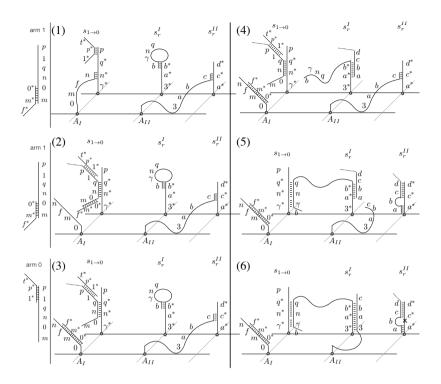

# 7.2 Method 1: Height Reduction

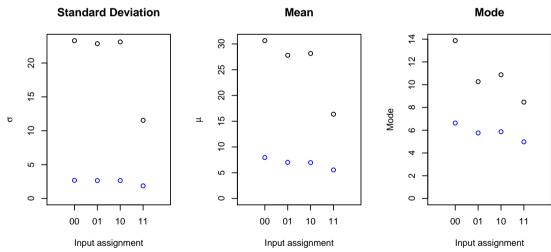

For a 3-CNF circuit denoted by (k, h) where k denotes the clause number and h denotes the circuit height, if k is fixed, the height of the circuit tree is from  $\lceil \log k \rceil + 1$  to k. We simulate circuits having between one and seven clauses. For each circuit, we use 1000 trajectories to calculate the time deviation under each input assignment. We calculate  $\sigma_{max}$  for each circuit, which are shown in Table 7.1. Standard deviation of computation time for a fixed circuit (k, h) varies with the change of input assignments. Boolean formulas for the circuits (k, h) are presented in Table 7.2. Simulation results are presented in Figures 7.8 to 7.11 in the next section

Table 7.1: The values of  $\sigma_{max}$  for circuits having between 1 and 7 clauses. Circuit (k, h) has k clauses and height h.

| no. | (k,h) | $\sigma_{max}$ | no. | (k,h) | $\sigma_{max}$ |

|-----|-------|----------------|-----|-------|----------------|

| 1.  | (1,1) | 32.69          | 8.  | (6,4) | 310.94         |

| 2.  | (2,2) | 57.57          | 9.  | (6,5) | 264.72         |

| 3.  | (3,3) | 109.9          | 10. | (6,6) | 256.07         |

| 4.  | (4,3) | 143.94         | 11. | (7,4) | 356.04         |

| 5.  | (4,4) | 162.83         | 12. | (7,5) | 465.95         |

| 6.  | (5,4) | 262.1          | 13. | (7,6) | 657.61         |

| 7.  | (5,5) | 221.55         | 14. | (7,6) | 296.78         |

(Section 7.2). Each diagram contains plots in two different colors. The black plots represent the the standard deviation under all possible input assignments. The blue plots represent simulation results in a modified model where spiders only move forward, which will be discussed in Section 7.3. Figure 7.8 shows the time deviations for circuits (2,2), (3,3), (4,3), (4,4). Figure 7.9 shows the time deviations for circuits (5,4), (5,5). Figure 7.10 shows the time deviations for circuits (6,4), (6,5), (6,6). Figure 7.11 shows the time deviations for circuits (7,4), (7,5), (7,6), (7,7).

In Figure 7.1, we show the relation between circuit height and  $\sigma_{max}$ . In each diagram in Figure 7.1, we use different colors to indicate the circuits with different number of clauses. In Figure 7.1, we can tell that  $\sigma_{max}$  increases as the height increases in the magenta-color plots, which represent the circuits with 4 clauses. However, in the black and blue plots (5-clause circuit and 6 clause circuit),  $\sigma_{max}$  decreases as the circuit height increases. In the red plots (7-clause circuit),  $\sigma_{max}$  goes up and down as the circuit height increases. Therefore, there exists no linear relation between the circuit height and the measure of the circuit predictability ( $\sigma_{max}$ ), Method 1 is NOT valid.

38

Table 7.2: Boolean formulas for the 3-CNF circuits having between 1 and 7 clauses.

| (1 1) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| (k,h) | Circuit Structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| (1,1) | $x_1 \lor x_2 \lor x_3$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |