# University of New Mexico UNM Digital Repository

**Electrical and Computer Engineering ETDs**

**Engineering ETDs**

7-12-2014

# Dynamically Reconfigurable Architectures and Systems for Time-varying Image Constraints (DRASTIC) for Image and Video Compression

yuebing jiang

Follow this and additional works at: https://digitalrepository.unm.edu/ece etds

#### Recommended Citation

jiang, yuebing. "Dynamically Reconfigurable Architectures and Systems for Time-varying Image Constraints (DRASTIC) for Image and Video Compression." (2014). https://digitalrepository.unm.edu/ece\_etds/127

This Dissertation is brought to you for free and open access by the Engineering ETDs at UNM Digital Repository. It has been accepted for inclusion in Electrical and Computer Engineering ETDs by an authorized administrator of UNM Digital Repository. For more information, please contact disc@unm.edu.

| Yuebing Jiang                                                                       |               |

|-------------------------------------------------------------------------------------|---------------|

| Electrical and Computer Engineering                                                 |               |

| Electrical and Computer Engineering  Department                                     |               |

|                                                                                     |               |

| This dissertation is approved, and it is acceptable in quality and for publication: | form          |

| Approved by the Dissertation Committee:                                             |               |

| Dr. Marios S. Pattichis                                                             | , Chairperson |

| Dr. Christos G. Christodoulou                                                       |               |

| Dr. James R. Lyke                                                                   |               |

| Dr. Constantinos Pattichis                                                          |               |

|                                                                                     |               |

|                                                                                     |               |

|                                                                                     |               |

|                                                                                     |               |

## Dynamically Reconfigurable Architectures and Systems for Time-varying Image Constraints (DRASTIC) for Image and Video Compression

by

#### Yuebing Jiang

B.S., Xi'an Jiaotong University, 2008

#### DISSERTATION

Submitted in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

Engineering

The University of New Mexico

Albuquerque, New Mexico

May, 2014

Submitted by: Yuebing Jiang

Supervisor: Dr. Marios S. Pattichs

Department of Electrical and Computer Engineering

University of New Mexico

COMMITTEE MEMBERS:

Dr. Christos Christodoulou

Department of Electrical and Computer Engineering

University of New Mexico

Dr. James Lyke

Air Force Research Labs

Dr. Constantinos Pattichis

Department of Computer Engineering, University of Cyprus

University of Cypress

©2014, Yuebing Jiang

# Dedication

To my parents, Zuochen Jiang and Xizhi Jiang,

their pure, bright and beautiful love,

supported my stumble in the course of

seeking love and truth.

# Acknowledgments

I would like to express my gratitude to my advisor, Dr. Marios S. Pattichis, for his support, advice and encouragement during my years of graduate school. The patience and time spent on me are truly invaluable. Both the research topic and ideas owns large contributions from him. Thanks for supporting me when I needed help.

I would like to thank my dissertation committee for their time and support in reviewing and checking this work.

Thanks to staff and friends in the Department of Electrical and Computer Engineering of UNM, DGNSS Solutions LLC, UNM Hospitals, K&A Wireless LLC, Dolby Laboratory and Real Communications, Inc. A lot of experience was gained from you and I really enjoy our friendship.

## Dynamically Reconfigurable Architectures and Systems for Time-varying Image Constraints (DRASTIC) for Image and Video Compression

by

#### Yuebing Jiang

B.S., Xi'an Jiaotong University, 2008

Ph.D., Engineering, University of New Mexico, 2014

#### Abstract

In the current information booming era, image and video consumption is ubiquitous. The associated image and video coding operations require significant computing resources for both small-scale computing systems as well as over larger network systems. For different scenarios, power, bitrate and image quality can impose significant time-varying constraints. For example, mobile devices (e.g., phones, tablets, laptops, UAVs) come with significant constraints on energy and power. Similarly, computer networks provide time-varying bandwidth that can depend on signal strength (e.g., wireless networks) or network traffic conditions. Alternatively, the users can impose different constraints on image quality based on their interests.

Traditional image and video coding systems have focused on rate-distortion optimization. More recently, distortion measures (e.g., PSNR) are being replaced by more sophisticated image quality metrics. However, these systems are based on fixed hardware configurations that provide limited options over power consumption. The use of dynamic partial reconfiguration with Field Programmable Gate Arrays (FPGAs) provides an opportunity to effectively control dynamic power consumption by jointly considering software-hardware configurations.

This dissertation extends traditional rate-distortion optimization to rate-quality-power/energy optimization and demonstrates a wide variety of applications in both image and video compression. In each application, a family of Pareto-optimal configurations are developed that allow fine control in the rate-quality-power/energy optimization space. The term Dynamically Reconfiguration Architecture Systems for Time-varying Image Constraints (DRAS-TIC) is used to describe the derived systems. DRASTIC covers both software-only as well as software-hardware configurations to achieve fine optimization over a set of general modes that include: (i) maximum image quality, (ii) minimum dynamic power/energy, (iii) minimum bitrate, and (iv) typical mode over a set of opposing constraints to guarantee satisfactory performance. In joint software-hardware configurations, DRASTIC provides an effective approach for dynamic power optimization. For software configurations, DRASTIC provides an effective method for energy consumption optimization by controlling processing times.

The dissertation provides several applications. First, stochastic methods are given for computing quantization tables that are optimal in the rate-quality space and demonstrated on standard JPEG compression. Second, a DRASTIC implementation of the DCT is used to demonstrate the effectiveness of the approach on motion JPEG. Third, a reconfigurable deblocking filter system is investigated for use in the current H.264/AVC systems. Fourth, the dissertation develops DRASTIC for all 35 intra-prediction modes as well as intra-encoding for the emerging High Efficiency Video Coding standard (HEVC).

| Li | st of        | Figures                                                                       | xiv    |  |  |  |

|----|--------------|-------------------------------------------------------------------------------|--------|--|--|--|

| Li | st of        | Tables                                                                        | XX     |  |  |  |

| 1  | Introduction |                                                                               |        |  |  |  |

|    | 1.1          | Motivation                                                                    | 2      |  |  |  |

|    | 1.2          | Thesis statement                                                              | 2      |  |  |  |

|    | 1.3          | Contributions                                                                 | 3      |  |  |  |

|    | 1.4          | Dissertation Overview                                                         | 4      |  |  |  |

| 2  |              | EG Compression Using Quantization Table Optimization Based on Pertual Quality | -<br>7 |  |  |  |

|    | 2.1          | Abstract                                                                      | 7      |  |  |  |

|    | 2.2          | Introduction                                                                  | 8      |  |  |  |

|    | 2.3          | A Multi-Objective Optimization Formulation                                    | 9      |  |  |  |

|    | 0.4          | $M_{cd} = 1$                                                                  | 10     |  |  |  |

|   | 2.5 | Result | SS                                                                  | 12 |

|---|-----|--------|---------------------------------------------------------------------|----|

|   | 2.6 | Conclu | asion                                                               | 17 |

| 3 | DR  | ASTIC  | C DCT for MJPEG                                                     | 19 |

|   | 3.1 | Abstra | act                                                                 | 19 |

|   | 3.2 | Introd | uction                                                              | 20 |

|   | 3.3 | Backg  | round and related work                                              | 24 |

|   |     | 3.3.1  | Dynamic Reconfiguration Based on Multi-objective Optimization       | 24 |

|   |     | 3.3.2  | Rate-Distortion-Complexity Control                                  | 25 |

|   |     | 3.3.3  | DCT hardware implementations                                        | 26 |

|   |     | 3.3.4  | A separable implementation of the 2D DCT based on Chen's algorithm  | 28 |

|   |     | 3.3.5  | Video image quality assessment using SSIM                           | 29 |

|   |     | 3.3.6  | Quantization table specification using a quality factor             | 30 |

|   | 3.4 | v      | namically Reconfigurable Architecture System for Time-Varying Image |    |

|   |     | Const  | raints (DRASTIC)                                                    | 30 |

|   |     | 3.4.1  | Constrained optimization formulation                                | 30 |

|   |     | 3.4.2  | Hardware design                                                     | 32 |

|   |     | 3.4.3  | Pareto Front and Constraint Satisfaction                            | 34 |

|   |     | 3.4.4  | Scalable Control of Reconfiguration Overhead                        | 35 |

|   |     | 3.4.5  | Scalable DRASTIC Controller                                         | 36 |

|   | 3.5 | Result |                                                                     | 37 |

|   |     | 3.5.1 Pareto-front estimation & comparisons to full 2D DCT implementations    | 37         |

|---|-----|-------------------------------------------------------------------------------|------------|

|   |     | 3.5.2 DRASTIC mode implementation & comparison to optimized static approaches | 39         |

|   |     |                                                                               |            |

|   |     | 3.5.3 DRASTIC Mode Transition Example                                         | 41         |

|   | 3.6 | Conclusion and future work                                                    | 42         |

| 4 | AΓ  | Synamically Reconfigurable Deblocking Filter for H.264/AVC Codec              | 51         |

|   | 4.1 | Abstract                                                                      | 51         |

|   | 4.2 | Introduction                                                                  | 52         |

|   | 4.3 | Deblocking Algorithm and Deblocking quality assessment                        | 54         |

|   | 4.4 | Methodology                                                                   | 56         |

|   | 4.5 | Results                                                                       | 57         |

|   | 4.6 | Conclusion                                                                    | 59         |

| 5 | Hig | h Efficiency Video Coding (HEVC)                                              | 65         |

|   | 5.1 | Background and Related work on HEVC                                           | 66         |

|   |     | 5.1.1 Coding Tools                                                            | 67         |

| 6 | DR  | ASTIC for HEVC intra-prediction mode implementation                           | <b>7</b> 4 |

|   | 6.1 | Abstract                                                                      | 74         |

|   | 6.2 | Introduction                                                                  | 75         |

|   | 6.3 | Unified Reference Sample Indexing and Accessing                               | 76         |

|   |                   | 0.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Unified reference sample indexing              | 70                         |

|---|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------|

|   |                   | 6.3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Planar mode                                    | 78                         |

|   |                   | 6.3.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DC mode                                        | 78                         |

|   |                   | 6.3.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Angular mode                                   | 79                         |

|   | 6.4               | Metho                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | dology and Implementation                      | 81                         |

|   |                   | 6.4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Pipeline Organization                          | 81                         |

|   |                   | 6.4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | System Integration                             | 82                         |

|   | 6.5               | Result                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | s                                              | 83                         |

|   |                   | 6.5.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Unified Reference Sample Indexing Verification | 83                         |

|   |                   | 6.5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Synthesis Results                              | 84                         |

|   |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                |                            |

| 7 | DR                | ASTIC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | C for HEVC intra-encoding at the Frame Level   | 87                         |

| 7 | <b>DR</b> .       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | C for HEVC intra-encoding at the Frame Level   | <b>87</b>                  |

| 7 |                   | Abstra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                |                            |

| 7 | 7.1               | Abstra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | act                                            | 87                         |

| 7 | 7.1<br>7.2        | Abstra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | uction                                         | 87<br>88                   |

| 7 | 7.1<br>7.2        | Abstraction Introduced The control of the control o | uction                                         | 87<br>88<br>89             |

| 7 | 7.1<br>7.2<br>7.3 | Abstraction Introduced The control of the control o | uction                                         | 87<br>88<br>89<br>92       |

| 7 | 7.1<br>7.2<br>7.3 | Abstraction Introduced The control of the Control o | nct                                            | 87<br>88<br>89<br>92<br>93 |

| 7 | 7.1<br>7.2<br>7.3 | Abstraction The control of The Contr | net                                            | 87<br>88<br>89<br>92<br>93 |

| Re | References 1 |        | 107                     |     |

|----|--------------|--------|-------------------------|-----|

|    | 8.2          | Future | e Work                  | 103 |

|    | 8.1          | Conclu | asion                   | 102 |

| 8  | Con          | clusio | and Future Work         | 102 |

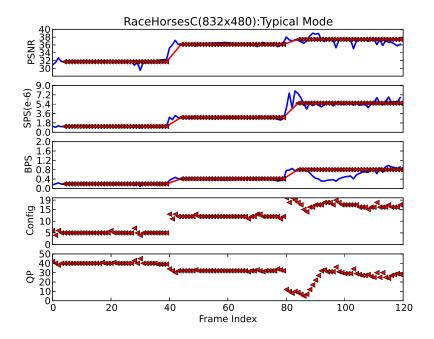

|    |              | 7.5.4  | Typical Mode            | 100 |

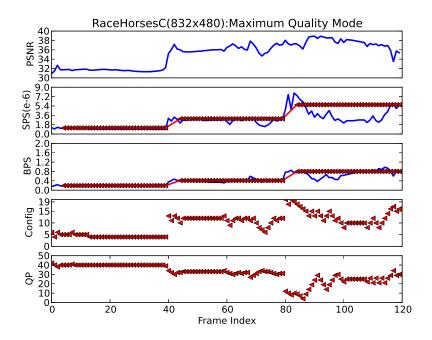

|    |              | 7.5.3  | Maximum Quality Mode    | 99  |

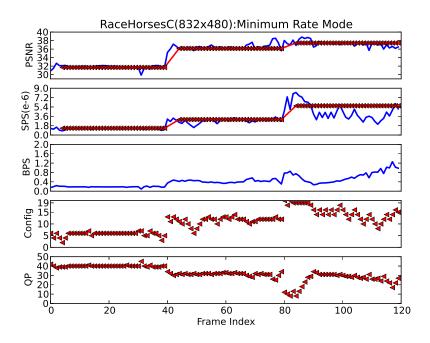

|    |              | 7.5.2  | Minimum Rate Mode       | 98  |

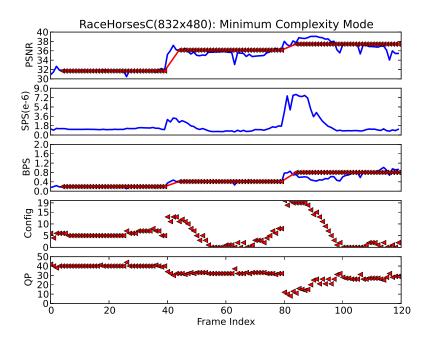

|    |              | 7.5.1  | Minimum Complexity Mode | 97  |

# List of Figures

| 2.1 | Simulated Annealing (SA) Optimization for computing a Rate-SSIM optimal point                                                                                                                                                                                                                | 13 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

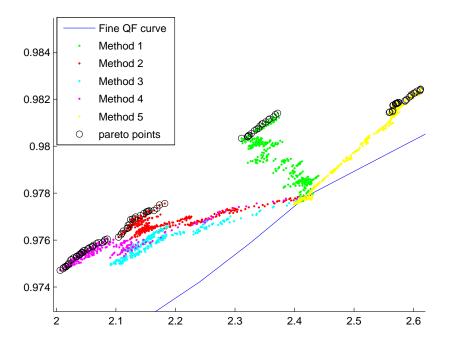

| 2.2 | Rate-SSIM comparisons for all methods for the Lena image at QF=95. The circled points represent Pareto-optimal results                                                                                                                                                                       | 15 |

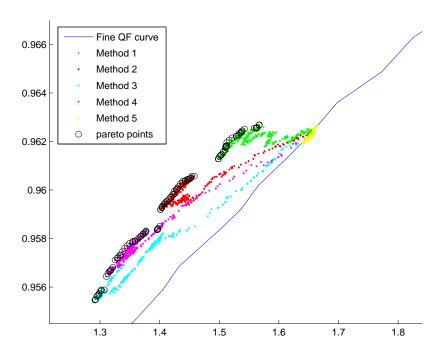

| 2.3 | Rate-SSIM comparisons for all methods for the Lena image for QF=90. The circled points represent Pareto-optimal results                                                                                                                                                                      | 16 |

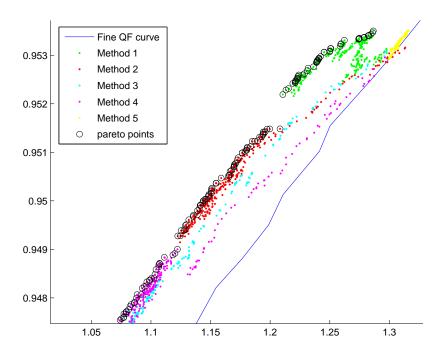

| 2.4 | Rate-SSIM comparisons for all methods for the Lena image at QF=85. The circled points represent Pareto-optimal results                                                                                                                                                                       | 17 |

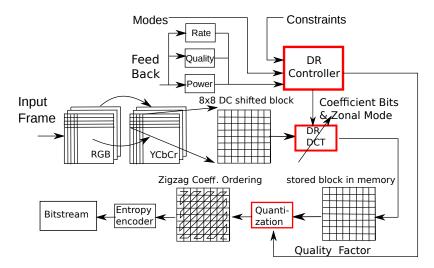

| 3.1 | Dynamically Reconfigurable Architecture System for Time varying Image Constraints (DRASTIC) for motion JPEG                                                                                                                                                                                  | 22 |

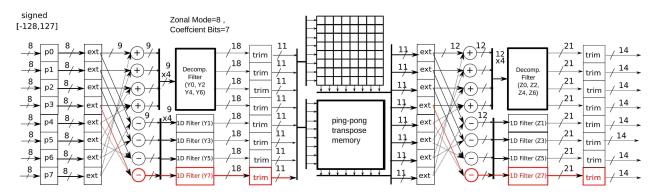

| 3.2 | Scalable data path for the 2D-DCT using ping-pong transpose memory. The number of bits used at each stage are given in the figure. The input image block is assumed to be of size 8 with signed, 8-bit integer values. The removal of the highest frequency components is highlighted in red | 32 |

| 3.3 | Scalable Decompose filter implementation of the matrix-vector product given                    |    |

|-----|------------------------------------------------------------------------------------------------|----|

|     | in (3.4). Refer to Fig. 3.2 for how the decompose filter fits the DCT core. The                |    |

|     | inputs $S_{ij}$ refer to the $X(i) + X(j)$ sum of equation (3.3). The outputs corre-           |    |

|     | spond to $Y(0)$ , $Y(2)$ , $Y(4)$ , $Y(6)$ of (3.3). The datapath associated with the          |    |

|     | highest frequency component is highlighted in red. Note how tracing back-                      |    |

|     | wards from each output, we can generate a scalable datapath that removes                       |    |

|     | the circuitry associated with each frequency component                                         | 33 |

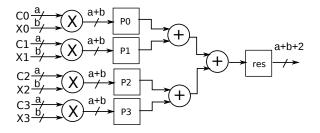

| 3.4 | Implementation of the 1D filters shown in Fig. 3.2. Here, CO-C3 refer to the                   |    |

|     | DCT Kernel coefficients and X0-X3 refer to sums and differences computed                       |    |

|     | on the input data (see Fig. 3.2)                                                               | 33 |

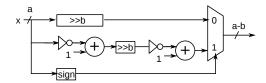

| 3.5 | Signed integer trimming of a-bit input x to an (a-b)-bit output by truncat-                    |    |

|     | ing the output towards zero (floor operation). This component is used to                       |    |

|     | control the bit-width in the optimization process.                                             | 34 |

| 3.6 | General framework for DRASTIC mode implementation                                              | 43 |

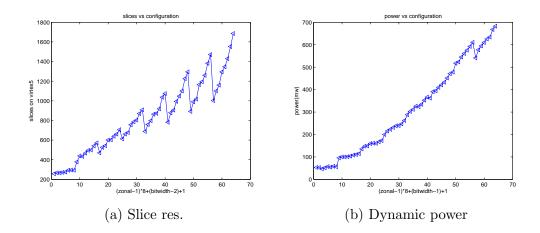

| 3.7 | Resource allocation and estimated dynamic power consumption for 64 hard-                       |    |

|     | ware configurations based on bit<br>width values: $2 \leq WL \leq 9$ and zonal values:         |    |

|     | $1 \leq \mathcal{Z} \leq 8$ . (a) Slice resources as a function of the zonal configuration and |    |

|     | bit width. (b) Dynamic power consumption as a function of zonal config-                        |    |

|     | uration and bit width. From the dynamic power results, it is clear that a                      |    |

|     | scalable set of DCT architectures has been achieved                                            | 44 |

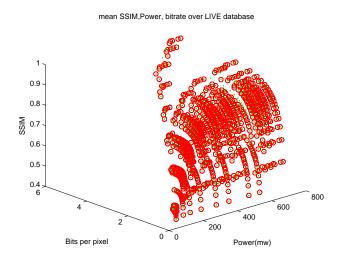

| 3.8 | Pareto front estimation for the joint space of SSIM, bit rate, and dynamic                     |    |

|     | power consumption. The Pareto front is estimated using the UT LIVE image                       |    |

|     | database. Pareto optimal configurations are highlighted using red circles                      | 44 |

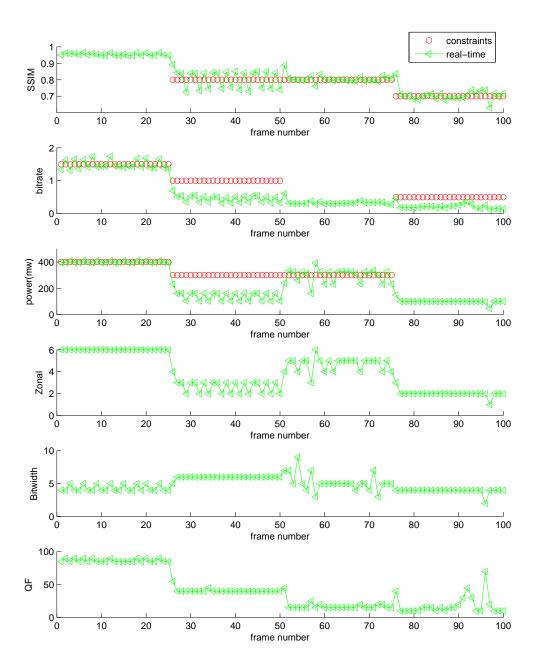

| 3.9 | DRASTIC reconfiguration results for switching between modes for the Fore-                      |    |

|     | man video. Here, the proposed reconfiguration settings are used (RecC=5, $$                    |    |

|     | RecP=1)                                                                                        | 47 |

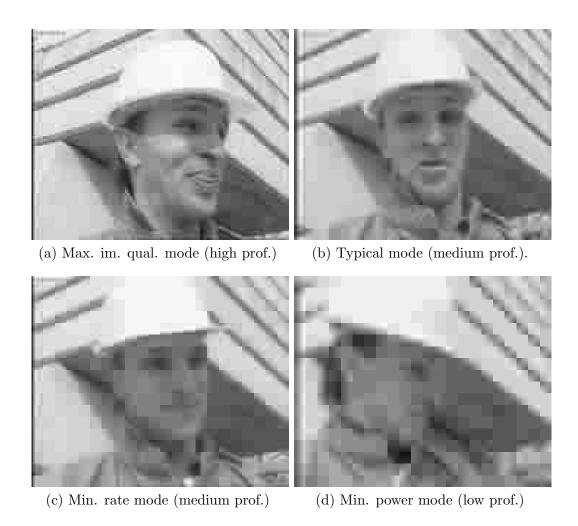

| 3.10 | DRASTIC mode transition example results. (a) Max img qual. mode                 |    |

|------|---------------------------------------------------------------------------------|----|

|      | (n=5): SSIM=0.95, Rate=1.36bps, DP=395mW which gives exceptional                |    |

|      | image quality while meeting the high-profile constraints. (b) Typical mode      |    |

|      | (n=35): SSIM=0.84, Rate=0.51bps, DP=161mW which meets all of the                |    |

|      | medium-profile constraints at a much lower bitrate. (c) Min rate mode           |    |

|      | (n=60): SSIM=0.79, Rate=0.31bps, DP=312mW which is right at the                 |    |

|      | boundary of the image quality and dynamic power constraints (medium-            |    |

|      | profile) while using significantly less bitrate. (d) Min power mode ( $n=85$ ): |    |

|      | SSIM=0.69, Rate=0.18bps, DP=100mW which is at the boundary of the               |    |

|      | image quality constraint for the low-profile, unable to further reduce power,   |    |

|      | but still operating at a very low bitrate.                                      | 48 |

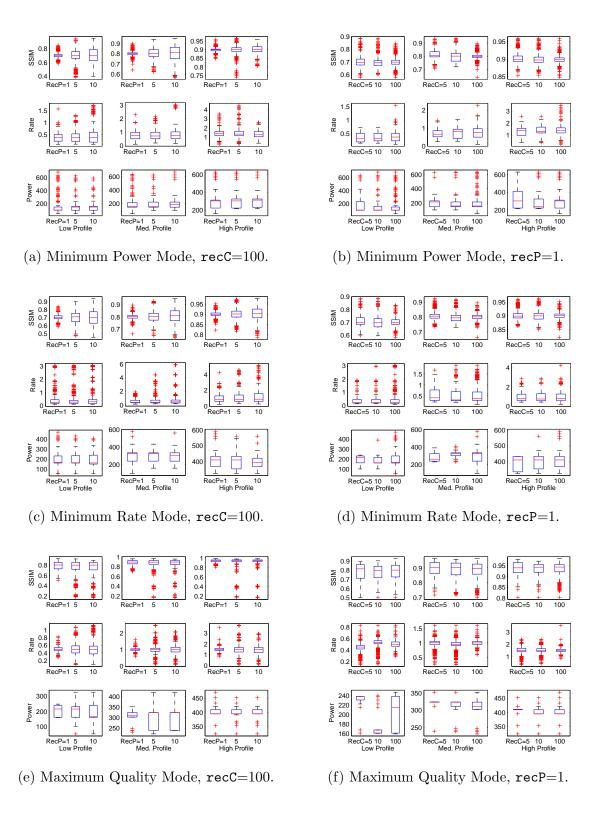

| 3.11 | DRASTIC mode performance                                                        | 49 |

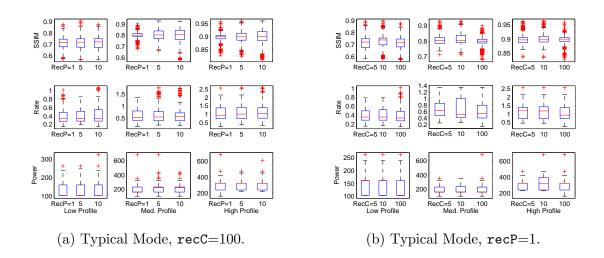

| 3.12 | DRASTIC performance for the typical mode as a function of the reconfigu-        |    |

|      | ration period RecP and the number of reconfigurations RecC                      | 50 |

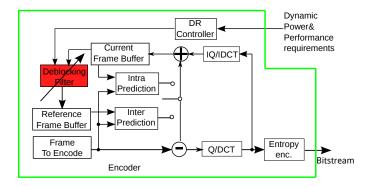

| 4.1  | Dynamically reconfigurable DCT architecture for H.264 encoder                   | 53 |

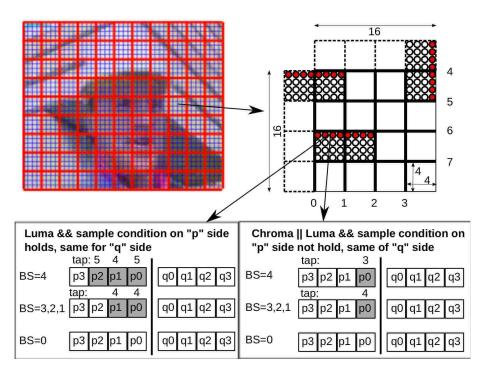

| 4.2  | Deblocking filtering operation flow. Deblocking filtering is applied to the     |    |

|      | shaded pixels shown in the lower figures. For further details, we refer to [1]. | 54 |

| 4.3  | Assignment of boundary strength $BS$ . Here, MV refers to motion vector and     |    |

|      | Diff. Ref. refers to a change in the reference frame                            | 55 |

| 4.4  | Deblocking filter results for foreman video frame 2 where DBF works as          |    |

|      | expected. In this example, we are using H.264/AVC JM 18.2 with $QP=42$ .        |    |

|      | We demonstrate the results for: (a) original image, (b) $BSKill = 0$ gives      |    |

|      | SSIM=0.8182, (c) $BSKill=1$ gives SSIM=0.8155, (d) $BSKill=2$ gives             |    |

|      | SSIM=0.8145, (e) $BSKill=3$ gives SSIM=0.8005, and (f) $BSKill=4$               |    |

|      | gives SSIM=0.7882                                                               | 60 |

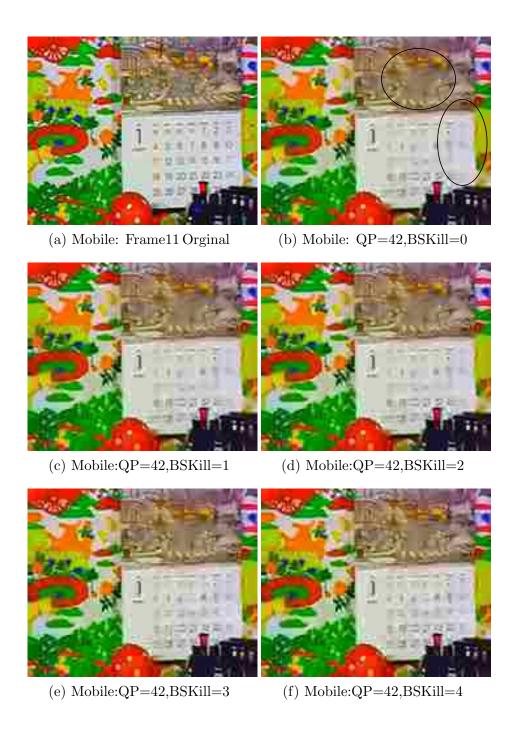

| 4.5 | Deblocking filter results for mobile video frame 11 where DBF can perform                                                                                         |    |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | worse than expected. In this example, we are using $\mathrm{H.264/AVC}\ \mathrm{JM}\ 18.2$                                                                        |    |

|     | with $QP = 42$ . We demonstrate the results for: (a) original image, (b)                                                                                          |    |

|     | BSKill = 0 gives SSIM=0.7203, (c) $BSKill = 1$ gives SSIM=0.7199, (d)                                                                                             |    |

|     | BSKill = 2 gives SSIM=0.7194, (e) $BSKill = 3$ gives SSIM=0.7358, and (f)                                                                                         |    |

|     | BSKill=4 gives SSIM=0.7365. To see the effects of over-filtering, compare                                                                                         |    |

|     | the two ellipsoidal regions shown in (b) with the original image in (a), and                                                                                      |    |

|     | the rest of the sub-figures.                                                                                                                                      | 61 |

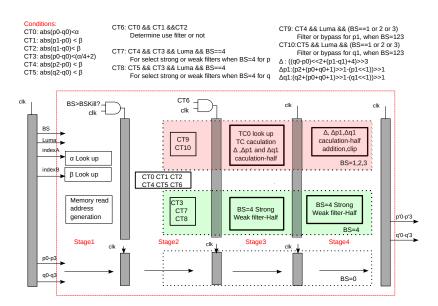

| 4.6 | Deblocking filter implementation using a 4-stage pipeline. The diagram                                                                                            |    |

|     | shows the full-filter implementation (BSKill $= 0$ ). The other 4 modes are                                                                                       |    |

|     | implemented by simply removing logic from the full-filter. The pink regions                                                                                       |    |

|     | are implemented for weaker-edges $(BS=1,2,3)$ . The green regions are im-                                                                                         |    |

|     | plemented for strong edges ( $BS=4$ ). In the bottom of the figure, we have                                                                                       |    |

|     | a FIFO implementation that is used for the case of no filtering $(BS=0)$                                                                                          | 62 |

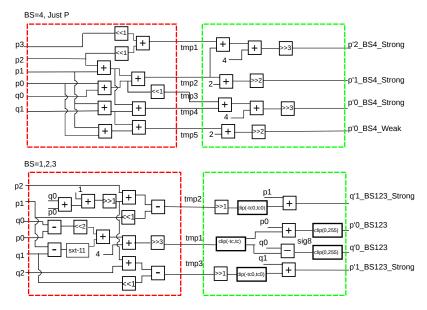

| 4.7 | A two-stage pipeline implementation of the strong and weaker filter halves                                                                                        |    |

|     | (see Fig. 4.6)                                                                                                                                                    | 63 |

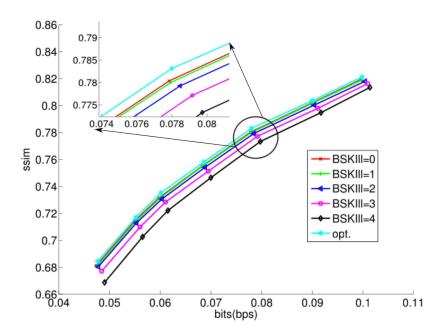

| 4.8 | R-D performance with BSKill mode and opt. mode. Tested over 11 QCIF                                                                                               |    |

|     | videos, each video has 64 frames, with "IPPPPPPP" GOP                                                                                                             | 64 |

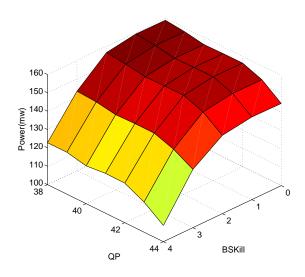

| 4.9 | Dynamic power as a function of BSKill and QP. Refer to Table 4.5                                                                                                  | 64 |

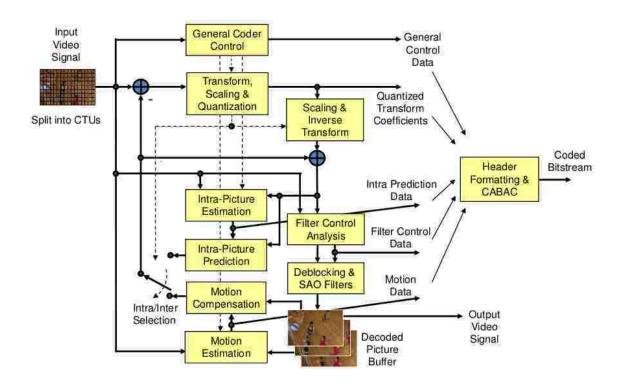

| 5.1 | HEVC encoder diagram [2]                                                                                                                                          | 67 |

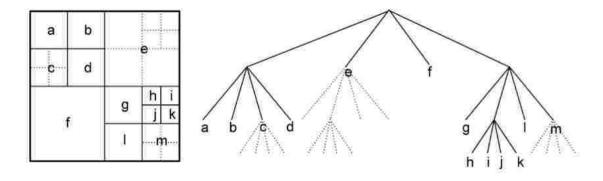

| 5.2 | Example of a nested quad-tree structure (right part) for dividing a given                                                                                         |    |

|     | coding tree block (left part, in black) into prediction blocks (solid gray lines) and transform blocks (dashed gray lines) of variable size. The order of parsing |    |

|     | the prediction blocks follows their labeling in alphabetical order [3]                                                                                            | 68 |

## List of Figures

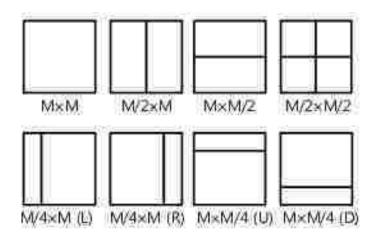

| 5.3 | Modes for splitting a CB into PBs for inter prediction. For intra prediction, only quad-tree spliting is allowed [2]                                                                                                                                                                                                                                            | 69 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

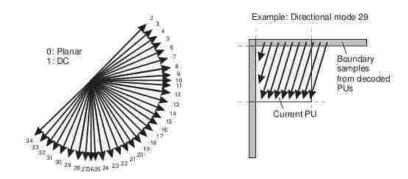

| 5.4 | The 35 intra-prediction modes using 33 directions [2]                                                                                                                                                                                                                                                                                                           | 69 |

| 5.5 | Transform matrix for HEVC standard                                                                                                                                                                                                                                                                                                                              | 71 |

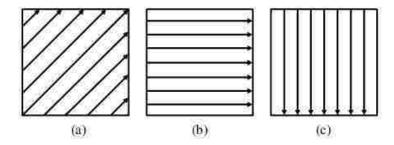

| 5.6 | Coefficient scanning direction in HEVC. The intra mode implicitly selects the 3 modes. The inter mode only uses the diagonal up-right mode                                                                                                                                                                                                                      | 72 |

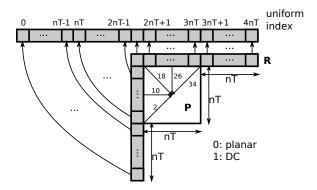

| 6.1 | Unified reference sample indexing for PU size of $nT \times nT$ . Here, $4nT + 1$ reference pixels $R$ are used to obtain $nT \times nT$ predicted samples $P$ . The prediction directions are shown for several prediction modes $(2,10,18,26,34)$ .                                                                                                           | 77 |

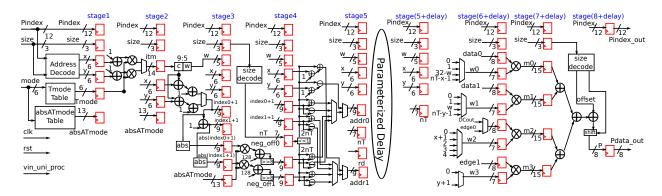

| 6.2 | Datapath for the pipelined $uni\_proc$ circuit using $size = log2(nT) - 2$ , $Pindex = y \times nT + x$ , and $mode \in [0, 34]$ . Parameter $delay$ is used to notify number of cycles for RAM operation between address assertion and data to be ready. When using BRAM on virtex 5 FPGA, $delay = 2$                                                         | 79 |

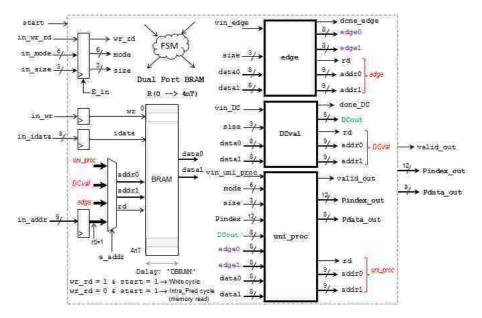

| 6.3 | Integrated system integration using pipelined uni_proc circuit                                                                                                                                                                                                                                                                                                  | 83 |

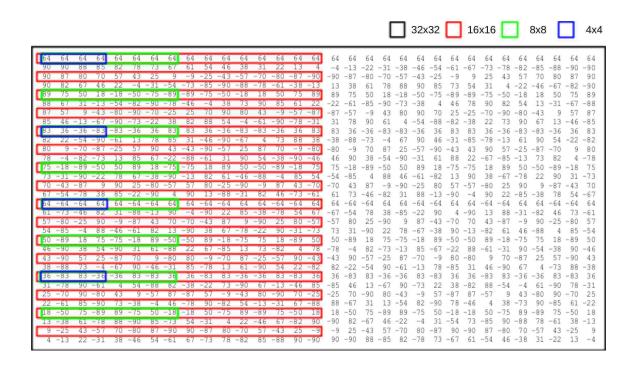

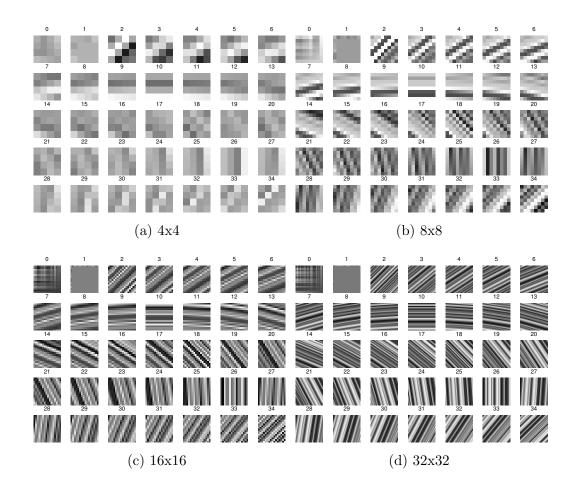

| 6.4 | 35 modes of intra prediciton for HEVC, for PU sizes from 4x4 to 32x32, with random generated reference samples for each PU size                                                                                                                                                                                                                                 | 84 |

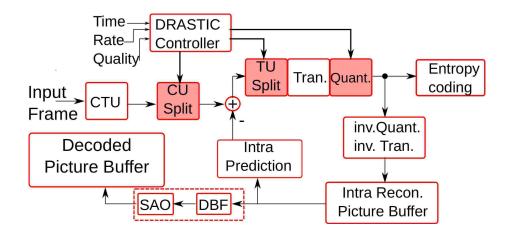

| 7.1 | Diagram for DRASTIC HEVC Intra Encoding System                                                                                                                                                                                                                                                                                                                  | 90 |

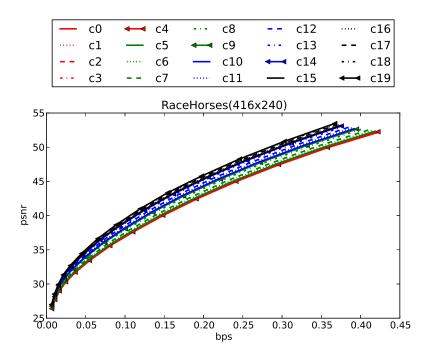

| 7.2 | The projection of the rate-distortion-energy space on the rate-distortion space for the RaceHorses video. Here, bps refers to the number of bits-per-sample. Note that all of the configurations are Pareto-optimal in the sense that it takes more energy (time) to provide better rate-distortion per-formance. The video frame is of size $432 \times 240$ . | 93 |

## List of Figures

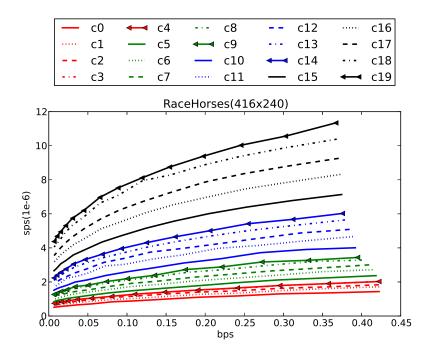

| 7.3 | The projection of the rate-distortion-energy space on the rate-complexity                                                                                |     |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | space where complexity is measured in terms of the number of seconds per                                                                                 |     |

|     | sample (sps) and it is assumed to be proportional to the consumed energy                                                                                 |     |

|     | (from $E=Pt$ ). The space is Pareto-optimal in the 3-dimensional space in                                                                                |     |

|     | that longer computation times increase the PSNR                                                                                                          | 94  |

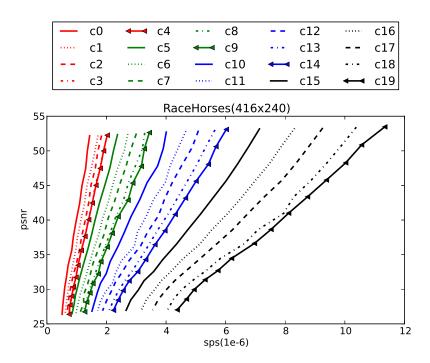

| 7.4 | The projection of the rate-distortion-energy space on the distortion-complexity space where complexity is assumed to be proportional to the consumed en- |     |

|     | ergy (from $E=Pt$ ). The space is Pareto-optimal in the 3-dimensional space.                                                                             | 95  |

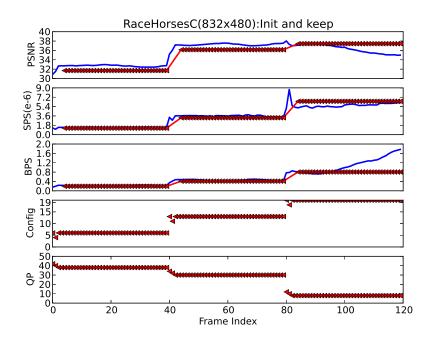

| 7.5 | Results based on initialize and hold                                                                                                                     | 96  |

| 7.6 | Results from minimum complexity mode                                                                                                                     | 98  |

| 7.7 | Results for minimum rate mode                                                                                                                            | 99  |

| 7.8 | Results for maximum quality mode                                                                                                                         | 100 |

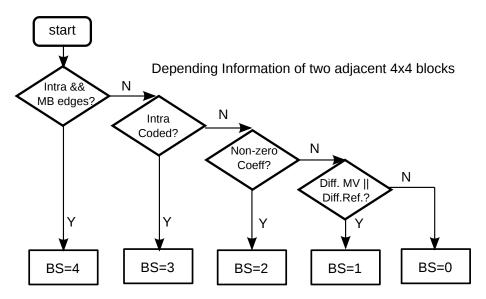

| 7.0 | Results for typical mode                                                                                                                                 | 101 |

# List of Tables

| 2.1 | Method 1 results for the Lena (512 $\times$ 512) image                                                                                                                                              | 13 |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Method 2 results for the Lena $(512 \times 512)$ image based on the low-frequency exponential rule                                                                                                  | 14 |

| 2.3 | Method 3 results for the Lena (512 $\times$ 512) image based on discretized Gaussian model                                                                                                          | 14 |

| 2.4 | Method 4 results for the Lena $(512 \times 512)$ image based on the low-frequency exponential rule and discretized Gaussian model                                                                   | 14 |

| 2.5 | Method 5 results for the Lena (512 $\times$ 512) image based on the high-frequency exponential rule                                                                                                 | 14 |

| 2.6 | Method 1 results for the LIVE database using leave one out validation on the median QT (QF=95). Here, we report the average, and the percentile results (min, 25th, 50th, 75th, max) on rate change | 17 |

| 2.7 | Method 2 results for the LIVE database using leave one out validation on the median QT (QF=95). Here, we report the average, and the percentile results (min, 25th, 50th, 75th, max) on rate change | 18 |

#### List of Tables

| 2.8 | Method 5 results for the LIVE database using leave one out validation on                       |    |  |

|-----|------------------------------------------------------------------------------------------------|----|--|

|     | the median QT (QF=95). Here, we report the average, and the percentile                         |    |  |

|     | results (min, 25th, 50th, 75th, max) on rate change                                            | 18 |  |

| 3.1 | Synthesized results for DCT Cores on XC5VLX110T-1FF1136                                        | 45 |  |

| 3.2 | DRASTIC constraint profiles. The constraints represent the bounds for (i)                      |    |  |

|     | image quality $(Q_{min})$ , (ii) the bitrate $(B_{max})$ , (iii) and dynamic power $(P_{max})$ |    |  |

|     | as described in section 4.4                                                                    | 46 |  |

| 3.3 | DRASTIC mode savings over the use of the optimized maximum setting                             |    |  |

|     | for each mode for the 9 testing videos. Here, the savings are computed as                      |    |  |

|     | a percentage of the average performance metric. For example, for dynamic                       |    |  |

|     | power, the percentage savings computed using $(P_{max} - P_{avg})/P_{avg} * 100$ where         |    |  |

|     | $P_{avg}, P_{max}$ are computed from the selected DRASTIC architectures. For dy-               |    |  |

|     | namic power and bitrate constraints, higher percentages indicate higher sav-                   |    |  |

|     | ings. For image quality, lower percentages are preferred since they indicate                   |    |  |

|     | that the resulting videos will be of higher quality. The proposed reconfig-                    |    |  |

|     | uration (Prop. Rec.) refers to RecC=5, RecP=1 while full reconfiguration                       |    |  |

|     | refers to RecC=100, RecP=1. The proposed reconfiguration requires $5\%$ of                     |    |  |

|     | the overhead of the full reconfiguration. Also, note that the savings are con-                 |    |  |

|     | servative since they assume an optimal pre-selection of the static architecture.               | 46 |  |

| 3.4 | A comparison of FPGA implementations of 2D DCTs. Dynamic power re-                             |    |  |

|     | sults are estimated for the operating frequency. Given the small number                        |    |  |

|     | of cycles required by the proposed approach, it is clear that the proposed                     |    |  |

|     | method yields the most energy efficient approach                                               | 50 |  |

| 4.1 | Scalable DBF modes based on BSKill parameter setting                                           | 56 |  |

#### List of Tables

| 4.2 | Average bitrate results for all 11 videos. GOP encoding is "IPPPPPPP". See                   |     |

|-----|----------------------------------------------------------------------------------------------|-----|

|     | Table 4.3 for corresponding SSIM values. Opt refers to the optimal method                    |     |

|     | that is described in Section 4.4                                                             | 58  |

| 4.3 | Average SSIM results for the setup described in Table 4.2                                    | 58  |

| 4.4 | Deblocking filter synthesis results. DBF was implemented on XC5VLX110T(Vin                   | tex |

|     | 5) device. Clock frequency was constrained to 100 MHz                                        | 59  |

| 4.5 | Power simulation results for Foreman video. Dynamic power is estimated                       |     |

|     | using XPower                                                                                 | 59  |

| 6.1 | Look up table for angle $A_{mode}$ parameters for angular prediction mode.                   |     |

|     | $T(mode) = 32 \times tan(A_{mode}), AT(mode) = 256 \times actan(A_{mode}) \dots \dots \dots$ | 81  |

| 6.2 | synthesis results on xc5vlx110t with speed grade -3 using Xilinx ISE 13.2 $$ .               | 85  |

| 6.3 | Total cycles to generate one prediction block and average cycles for one                     |     |

|     | prediction pixel, on decoder side, delay=2                                                   | 86  |

| 7.1 | Depth control for CU and TU candidate sizes based on DepthConfig                             | 92  |

| 7.2 | Finer depth control for the CU, TU sizes using FinerDepthConfig                              | 92  |

# Chapter 1

## Introduction

Digital image and video coding are computing intensive operations. Given the strong and still growing demand for processing and communications of digital images and videos, there is strong interest in the precise control of video communications, especially under certain constraints. The development of a platform that can provide fine control on power, bitrate, and image quality, we can lead to significant improvements in image and video processing and communications applications (e.g., video conferencing, remote sensing, home surveillance, web browsing).

Real-time constraints can come from many different sources. For example, video communication systems need to meet real-time constraints on available network bandwidth. This requires that the video be adaptively compressed at different bitrates so as to allow for communication within the available bandwidth. Energy constraints can be especially tight on mobile devices. For example, a low power mode is needed when no recharge station is available. Furthermore, a user's interest in video content determines minimum levels of desired video quality.

The use of Dynamic Partial Reconfiguration (DPR) allows FPGA devices to change hardware configuration of different parts of the device without the need for a restart [4]. On

#### Chapter 1. Introduction

an FPGA, we can use bitstreams to reconfigure the configurable logic blocks(CLBs), inputoutput blocks(IOBs), block RAMs, clock resources, and also re-route signals. For Xilinx FPGAs, the configuration memory is organized into one-bit wide frames, where each frame can be written to and read from independently. Thus, changing a small portion of the device can be performed quickly using a small size bitstream that can be reconfigured in a short time. For video processing applications, given the large amounts of data involved, small configuration bitstreams do not impose significant overhead.

#### 1.1 Motivation

Traditional RD [5] optimization in video coding can significantly benefit from a redesign that incorporates power [6–8] or complexity [9–11] considerations, so as to extend battery life for mobile devices. For software implementations, power consumption can be modeled as a function of supply power and video coding mode (e.g., block search mode, frame-encoding type, etc), or a memory access power model [8]. Also for software implementations, complexity is usually measured as executing time or using a weighted sum of different complexity measures, (e.g., based on time, memory access complexity, parallelization, etc [11]). For hardware-software co-design, especially when using DPR [12], we can directly estimate power based on specific hardware configuration. Furthermore, in this case, effective control can be based on the use of Rate-Distortion-Power (RDP) optimization and constraints.

#### 1.2 Thesis statement