### University of New Mexico UNM Digital Repository

**Computer Science ETDs**

**Engineering ETDs**

7-1-2012

# Energy consumption in networks on chip : efficiency and scaling

George Bezerra

Follow this and additional works at: https://digitalrepository.unm.edu/cs etds

#### **Recommended** Citation

Bezerra, George. "Energy consumption in networks on chip : efficiency and scaling." (2012). https://digitalrepository.unm.edu/cs\_etds/21

This Dissertation is brought to you for free and open access by the Engineering ETDs at UNM Digital Repository. It has been accepted for inclusion in Computer Science ETDs by an authorized administrator of UNM Digital Repository. For more information, please contact disc@unm.edu.

George B. P. Bezerra

Candidate

Computer Science

Department

This dissertation is approved, and it is acceptable in quality and form for publication:

Approved by the Dissertation Committee:

Stephanie Forrest , Chairperson

Melanie Moses

Payman Zarkesh-Ha

Dorian Arnold

# Energy Consumption in Networks on Chip: Efficiency and Scaling

by

### George B. P. Bezerra

B.S., Electrical Engineering, University of Campinas, Brazil, 2005M.S., Computer Engineering, University of Campinas, Brazil, 2006

### DISSERTATION

Submitted in Partial Fulfillment of the Requirements for the Degree of

> Doctor of Philosophy Computer Science

The University of New Mexico

Albuquerque, New Mexico

July, 2012

©2012, George B. P. Bezerra

# Dedication

To my parents, Gisele and Agildo, for their support and encouragement.

# Acknowledgments

I would like to thank my advisor, Stephanie Forrest, for her support and mentoring. I would also like to thank my dissertation committee that helped me to mature my work. I am also very thankful to my friends in Albuquerque, who were always supportive and helped me during difficult times in my PhD. Thanks to my friends from the Adaptive Lab, who were always interested in discussing ideas and helping each other with solving new problems. Thanks to the faculty, technical support, and staff from the Computer Science department who helped making this dissertation possible.

# Energy Consumption in Networks on Chip: Efficiency and Scaling

by

George B. P. Bezerra

B.S., Electrical Engineering, University of Campinas, Brazil, 2005

M.S., Computer Engineering, University of Campinas, Brazil, 2006

PhD., Computer Science, University of New Mexico, 2012

#### Abstract

Computer architecture design is in a new era where performance is increased by replicating processing cores on a chip rather than making CPUs larger and faster. This design strategy is motivated by the superior energy efficiency of the multi-core architecture compared to the traditional monolithic CPU. If the trend continues as expected, the number of cores on a chip is predicted to grow exponentially over time as the density of transistors on a die increases.

A major challenge to the efficiency of multi-core chips is the energy used for communication among cores over a Network on Chip (NoC). As the number of cores increases, this energy also increases, imposing serious constraints on design and performance of both applications and architectures. Therefore, understanding the impact of different design choices on NoC power and energy consumption is crucial to the success of the multi- and many-core designs.

This dissertation proposes methods for modeling and optimizing energy consumption in multi- and many-core chips, with special focus on the energy used for communication on the NoC. We present a number of tools and models to optimize energy consumption and model its scaling behavior as the number of cores increases. We use synthetic traffic patterns and full system simulations to test and validate our methods. Finally, we take a step back and look at the evolution of computer hardware in the last 40 years and, using a scaling theory from biology, present a predictive theory for power-performance scaling in microprocessor systems.

| Li             | st of | Figures                                         | xiii |

|----------------|-------|-------------------------------------------------|------|

| List of Tables |       | viii                                            |      |

| 1              | Intr  | oduction                                        | 1    |

|                | 1.1   | Contributions and organization                  | 3    |

| <b>2</b>       | Bac   | kground Information                             | 5    |

|                | 2.1   | Network on Chip                                 | 5    |

|                |       | 2.1.1 NoC Topologies                            | 8    |

|                | 2.2   | Memory and Communication Models in CMP $\ldots$ | 11   |

|                |       | 2.2.1 Models of Parallel Architectures          | 11   |

|                |       | 2.2.2 Cache Coherence                           | 14   |

|                | 2.3   | Mapping and Scheduling                          | 19   |

| 3              | Pow   | ver Scaling in NoC Topologies                   | 23   |

#### viii

|   | 3.1 | A Theoretical Model of Power Scaling                | 24 |

|---|-----|-----------------------------------------------------|----|

|   | 3.2 | Analysis of the Scaling Behavior                    | 27 |

|   | 3.3 | Experimental Results                                | 28 |

|   |     | 3.3.1 Simulation Infrastructure                     | 28 |

|   |     | 3.3.2 Results                                       | 29 |

|   | 3.4 | Conclusion                                          | 30 |

| 4 | Mo  | deling NoC Communication Locality using Rent's Rule | 32 |

|   | 4.1 | Rent's Rule Traffic patterns                        | 33 |

|   |     | 4.1.1 Rent's Rule for Parallel Programs             | 33 |

|   |     | 4.1.2 Generating Rent's Rule Traffic Patterns       | 34 |

|   | 4.2 | Other Synthetic Workloads                           | 36 |

|   | 4.3 | Modeling Energy Consumption                         | 38 |

|   | 4.4 | Experimental Results                                | 39 |

|   |     | 4.4.1 NoC Energy Consumption                        | 39 |

|   |     | 4.4.2 Varying the Rent's Exponent                   | 41 |

|   | 4.5 | Discussion and Conclusion                           | 43 |

| 5 | Dat | a Placement Optimization for Chip Multi-Processors  | 45 |

|   | 5.1 | Related Work                                        | 46 |

|   | 5.2 | The Data Placement Problem                          | 47 |

|   | 5.3                                                                         | The C                                                   | ommunication Graph                                                                                                    | 50                                                                     |

|---|-----------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|

|   | 5.4                                                                         |                                                         | act Algorithm for Optimized Data                                                                                      | 50                                                                     |

|   |                                                                             | Placen                                                  | lent                                                                                                                  | 52                                                                     |

|   |                                                                             | 5.4.1                                                   | Greedy Approach                                                                                                       | 53                                                                     |

|   |                                                                             | 5.4.2                                                   | Description of the Model                                                                                              | 55                                                                     |

|   | 5.5                                                                         | Experi                                                  | mental results                                                                                                        | 57                                                                     |

|   |                                                                             | 5.5.1                                                   | Simulation setup                                                                                                      | 57                                                                     |

|   |                                                                             | 5.5.2                                                   | Results                                                                                                               | 58                                                                     |

|   |                                                                             | 5.5.3                                                   | Sensitivity Analysis                                                                                                  | 61                                                                     |

|   | 5.6                                                                         | Discus                                                  | sion                                                                                                                  | 63                                                                     |

|   | 5.7                                                                         | Summ                                                    | ary                                                                                                                   | 63                                                                     |

|   |                                                                             |                                                         |                                                                                                                       |                                                                        |

|   |                                                                             |                                                         |                                                                                                                       |                                                                        |

| 6 | The                                                                         | eoretica                                                | l Analysis of NoC Energy Consumption                                                                                  | 66                                                                     |

| 6 | <b>The</b><br>6.1                                                           |                                                         | d Analysis of NoC Energy Consumption Rule for Multi-Core Systems                                                      |                                                                        |

| 6 |                                                                             | Rent's                                                  |                                                                                                                       | 67                                                                     |

| 6 | 6.1                                                                         | Rent's<br>Modeli                                        | Rule for Multi-Core Systems                                                                                           | 67                                                                     |

| 6 | 6.1<br>6.2                                                                  | Rent's<br>Modeli<br>Modeli                              | Rule for Multi-Core Systems                                                                                           | 67<br>68                                                               |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>                               | Rent's<br>Modeli<br>Modeli<br>Relate                    | Rule for Multi-Core Systems       .         ing Communication Locality       .         ing Energy Consumption       . | 67<br>68<br>71                                                         |

|   | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> </ul> | Rent's<br>Modeli<br>Modeli<br>Relate                    | Rule for Multi-Core Systems                                                                                           | <ul> <li>67</li> <li>68</li> <li>71</li> <li>72</li> <li>73</li> </ul> |

| 6 | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> </ul> | Rent's<br>Modeli<br>Modeli<br>Relate                    | Rule for Multi-Core Systems                                                                                           | 67<br>68<br>71<br>72                                                   |

|   | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> </ul> | Rent's<br>Modeli<br>Modeli<br>Relate<br>Summ<br>General | Rule for Multi-Core Systems                                                                                           | <ul> <li>67</li> <li>68</li> <li>71</li> <li>72</li> <li>73</li> </ul> |

|     | 7.1.2  | Rent's rule                                                                                                          | 79  |

|-----|--------|----------------------------------------------------------------------------------------------------------------------|-----|

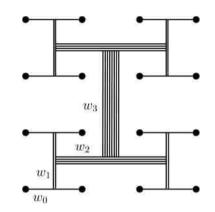

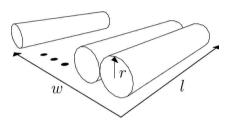

| 7.2 | A unit | fied model of network scaling                                                                                        | 82  |

|     | 7.2.1  | Length                                                                                                               | 84  |

|     | 7.2.2  | Thickness                                                                                                            | 85  |

|     | 7.2.3  | Width                                                                                                                | 86  |

| 7.3 | Allom  | etric scaling                                                                                                        | 87  |

|     | 7.3.1  | Volume                                                                                                               | 87  |

|     | 7.3.2  | Wire length                                                                                                          | 89  |

|     | 7.3.3  | Fractal dimension                                                                                                    | 90  |

| 7.4 | Energ  | y-delay product                                                                                                      | 91  |

|     | 7.4.1  | Resistance                                                                                                           | 92  |

|     | 7.4.2  | Capacitance                                                                                                          | 93  |

|     | 7.4.3  | Latency                                                                                                              | 93  |

|     | 7.4.4  | $Bandwidth \ldots \ldots$ | 94  |

|     | 7.4.5  | Energy                                                                                                               | 94  |

|     | 7.4.6  | Delay                                                                                                                | 95  |

|     | 7.4.7  | Energy $\times$ Delay                                                                                                | 96  |

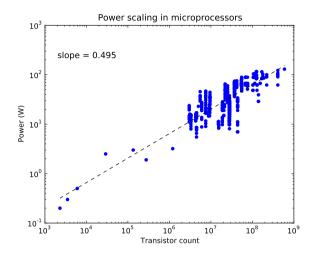

| 7.5 | Power  | and performance $\ldots$            | 99  |

|     | 7.5.1  | Power                                                                                                                | 99  |

|     | 7.5.2  | Performance                                                                                                          | 101 |

|    | 7.6 Discussion                                   | 103 |

|----|--------------------------------------------------|-----|

|    | 7.7 Conclusion                                   | 105 |

| 8  | Conclusions                                      | 107 |

| Aj | pendices                                         | 109 |

| A  | Derivation of CPD for Arbitrary Traffic Patterns | 110 |

| в  | Proof of Total Unimodularity                     | 114 |

| С  | The Fourth Scaling Dimension                     | 117 |

| Re | erences                                          | 120 |

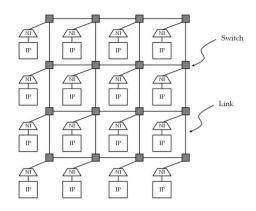

| 2.1 | Basic structure of an NoC.                                                                                                                                              | 7  |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

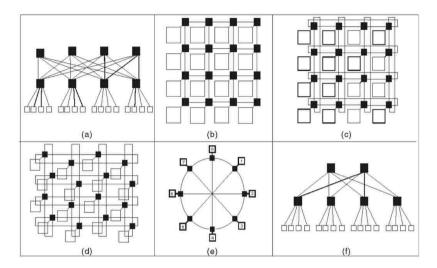

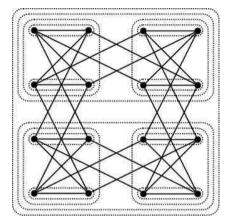

| 2.2 | NoC topologies. (a) Fat tree, (b) mesh, (c) torus, (d) folded-torus,<br>(e) octagon, (f) butterfly fat tree. (Figure reproduced from [73].)                             | 9  |

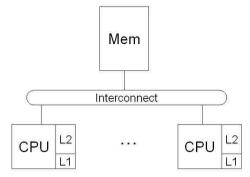

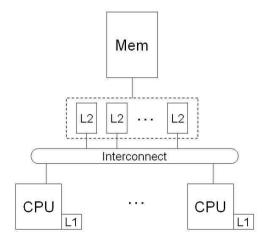

| 2.3 | Centralized shared memory architecture, also called UMA. All CPU nodes access a single physical memory. L1 and L2 correspond to private level 1 and level 2 caches      | 11 |

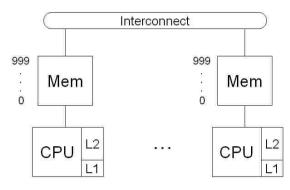

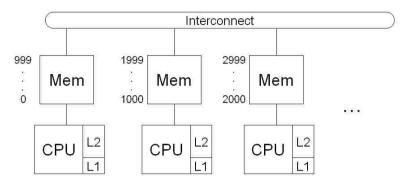

| 2.4 | Distributed memory architecture. Memory address spaces are independent and private to each CPU.                                                                         | 12 |

| 2.5 | Distributed shared memory architecture. Memories are physically distributed but share a same address space.                                                             | 13 |

| 2.6 | Non-uniform cache access (NUCA) architecture. This system has a centralized shared memory, but different from the UMA architecture, the level 2 caches are also shared. | 13 |

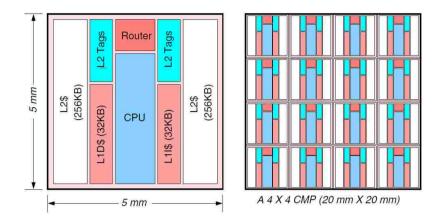

| 2.7 | Tiled chip multi-processor architecture. (Figure reproduced from [97])                                                                                                  | 14 |

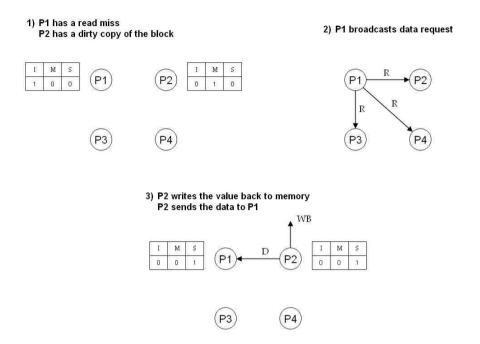

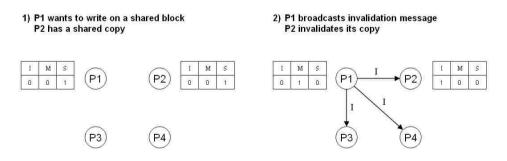

| 2.8 | Basic steps of a snooping protocol when a processor requests data.<br>The fields I, M, and S correspond to the invalidate, modified, and                                                                                                             |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|     | shared bits. R represents a data request, D data reply, and WB data write-back to memory                                                                                                                                                             | 17 |

| 2.9 | Basic steps of a snooping protocol when a processor wants to write<br>on shared data. The fields I, M, and S correspond to the invalidate,<br>modified, and shared bits. The arrows associated with a letter I are<br>invalidate messages            | 17 |

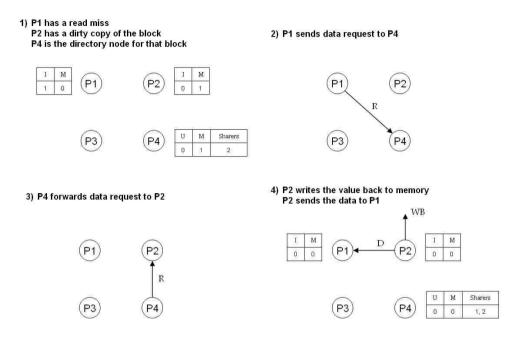

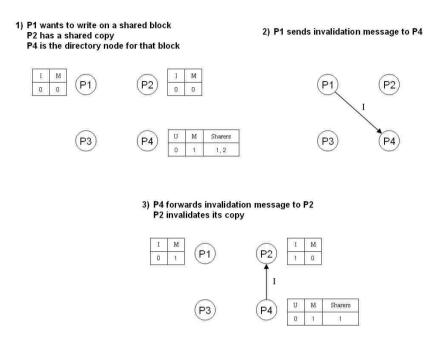

| 2.1 | Basic steps of a directory-based protocol when a processor requests<br>data. The fields I, M, and U correspond to the invalidate, modified,<br>and uncached bits. R represents a data request, D data reply, and<br>WB data write-back to memory     | 18 |

| 2.1 | 1 Basic steps of a directory-based protocol when a processor wants<br>to write on shared data. The fields I, M, and U correspond to the<br>invalidate, modified, and uncached bits. The arrows associated with<br>a letter I are invalidate messages | 19 |

| 2.1 | 2 Task graph                                                                                                                                                                                                                                         | 20 |

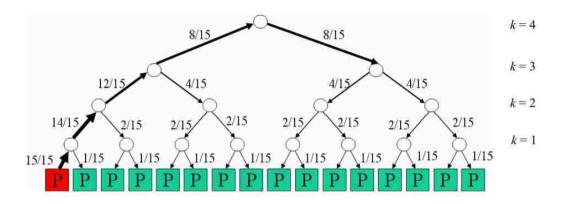

| 3.1 | Flow of packets injected by one processor in a binary tree network<br>with 16 processor nodes. The numbers represent the fraction of the<br>flow passing through each path of the tree. The values of k represent<br>the levels of the tree          | 25 |

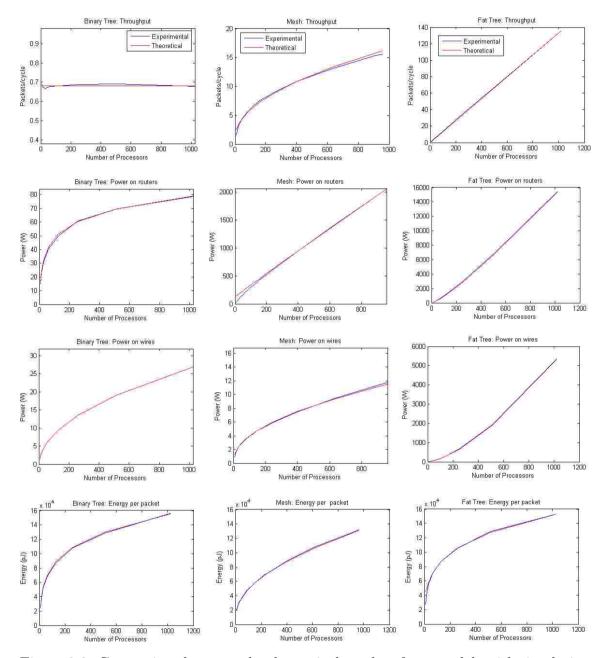

| 3.2 | Comparison between the theoretical results of our models with sim-<br>ulation results                                                                                                                                                                | 31 |

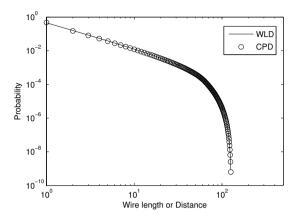

| 4.1 | Comparison between the wire length distribution given by $[25]$ and                         |    |

|-----|---------------------------------------------------------------------------------------------|----|

|     | the communication probability distribution produced by the Rent's                           |    |

|     | rule traffic generator.                                                                     | 35 |

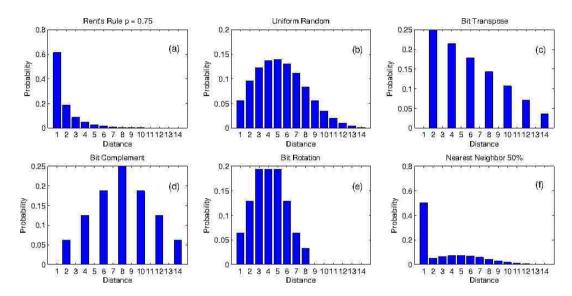

| 4.2 | CPD of different traffic patterns on a $8{\times}8$ mesh network. (a) Rent's                |    |

|     | rule with Rent's exponent of 0.75.(b) Uniform random. (c) Bit trans-                        |    |

|     | pose. (d) Bit complement. (e) Bit rotation. (f) Nearest neighbor                            |    |

|     | with localization factor of $50\%$                                                          | 38 |

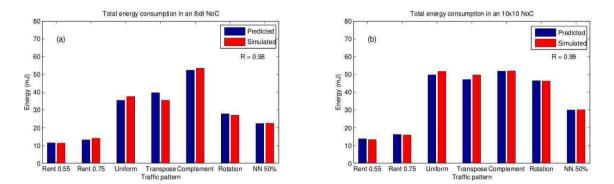

| 4.3 | Predicted and simulated energy consumption for (a) $8{\times}8$ mesh NoC                    |    |

|     | on 65nm and (b) $10 \times 10$ mesh NoC on 45nm                                             | 40 |

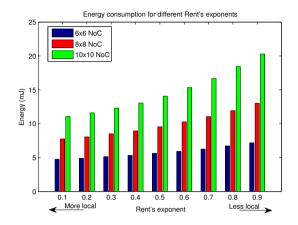

| 4.4 | Energy consumption of $6 \times 6$ , $8 \times 8$ , and $10 \times 10$ NoCs for Rent's rule |    |

|     | traffic as a function of the Rent's exponent                                                | 43 |

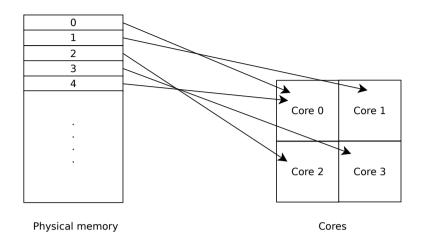

| 5.1 | Blocks of physical memory are assigned to home nodes present on the                         |    |

| 0.1 | cores. The blocks are uniformly distributed in an interleaved manner.                       | 48 |

|     | cores. The blocks are uniformly distributed in an interfeaved manner.                       | 40 |

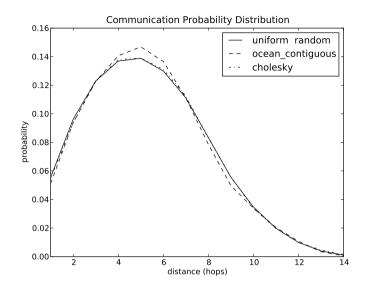

| 5.2 | Communication probability distribution for two benchmark applica-                           |    |

|     | tions compared to uniform random traffic. Data were collected on a                          |    |

|     | system with standard (uniform) mapping                                                      | 49 |

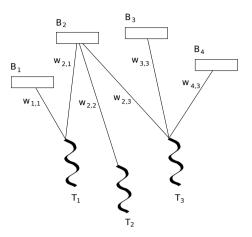

| 5.3 | Simple illustration of a communication graph. There is no commu-                            |    |

|     | nication between two threads or between two blocks, only between a                          |    |

|     | thread and a block.                                                                         | 51 |

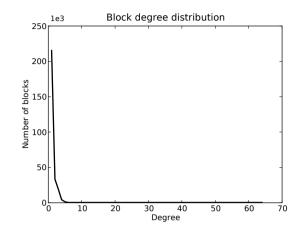

| 5.4 | Degree distribution of blocks for the ocean_contiguous application.                         | 52 |

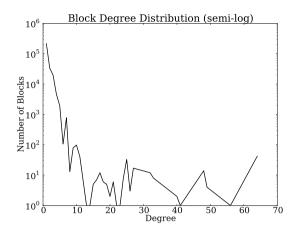

| 5.5 | Semi-log plot of the block degree distribution for the ocean_contiguous                     |    |

|     | application                                                                                 | 53 |

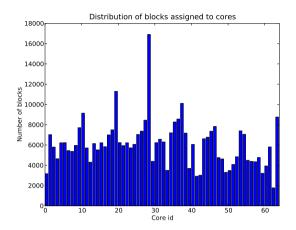

| 5.6 | Distribution of the number of blocks assigned to each core for the                          |    |

|     | cholesky application using a greedy approach.                                               | 54 |

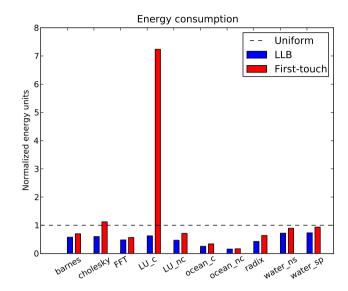

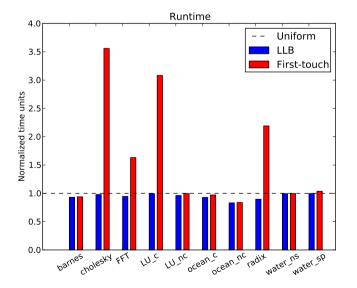

| 5.7 | Energy consumption of LLB and first-touch normalized by the energy consumption of the uniform mapping.                                                                         | 60 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.8 | Runtime of LLB and first-touch normalized by the runtime of the uniform mapping.                                                                                               | 60 |

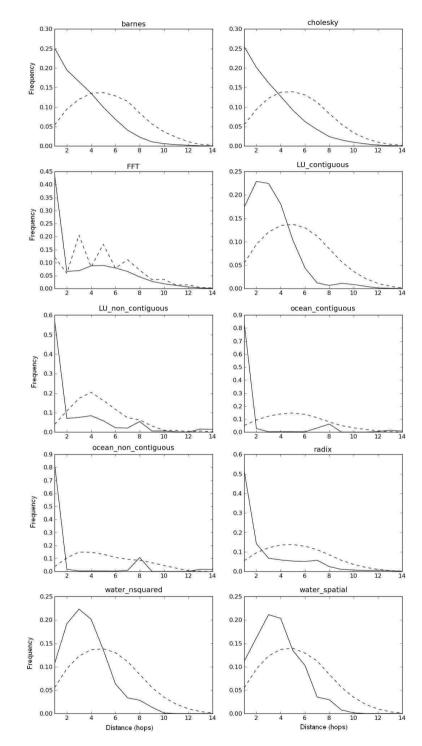

| 5.9 | Communication probability distribution of benchmark applications before (dashed line) and after (solid line) optimization with LLB                                             | 65 |

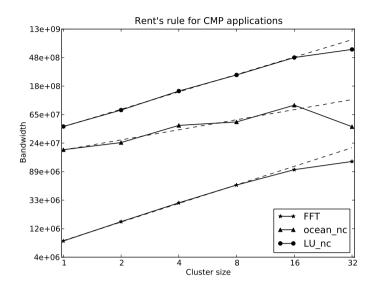

| 6.1 | Rent's rule for three CMP applications. The solid line corresponds to the result of the partitioning algorithm. The dashed line is a linear approximation in the log-log scale | 68 |

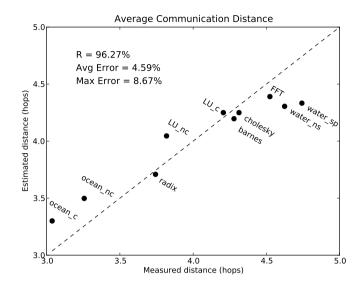

| 6.2 | Measured and estimated communication distance for CMP applica-<br>tions. The dashed line indicates perfect agreement between empirical<br>and theoretical values               | 70 |

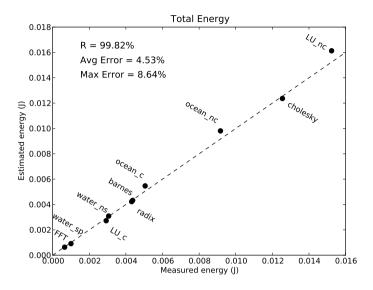

| 6.3 | Measured and estimated energy consumption of CMP applications.<br>The dashed line indicates perfect agreement between empirical and<br>theoretical values.                     | 72 |

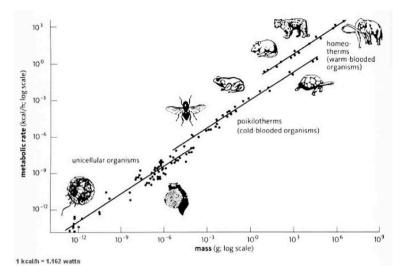

| 7.1 | Kleiber's law.                                                                                                                                                                 | 77 |

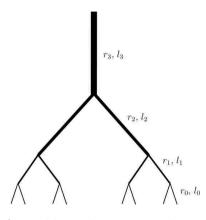

| 7.2 | Illustration of a fractal branching network structure with branching factor 2                                                                                                  | 79 |

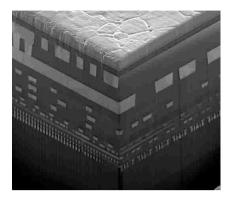

| 7.3 | Cross section of twelve layers of interconnect. Figure reproduced from [94]                                                                                                    | 80 |

| 7.4 | Visualization of the hierarchical interpretation of Rent's rule                                                                                                                | 81 |

| 7.5 | Schematic of the hierarchical model of network scaling                                                                                                                         | 83 |

| 7.6 | The scaling of power consumption as a function of the number of           |

|-----|---------------------------------------------------------------------------|

|     | transistors for 523 microprocessors of different vendors and techno-      |

|     | logical generations                                                       |

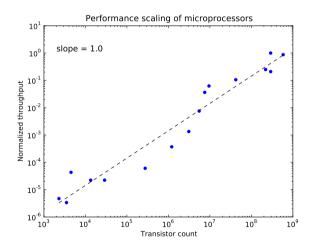

| 7.7 | The scaling of throughput as a function of the number of transistors      |

|     | for 16 Intel microprocessors of different technological generations $102$ |

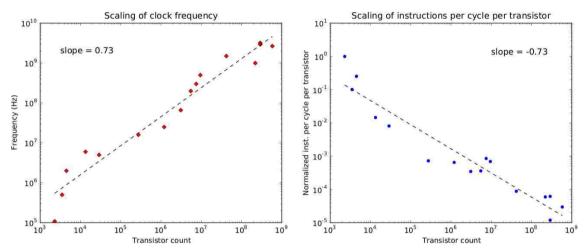

| 7.8 | The scaling of frequency and of instruction per cycle per transistor.     |

|     | As frequency has increased, each transistor computed proportionally       |

|     | less per cycle                                                            |

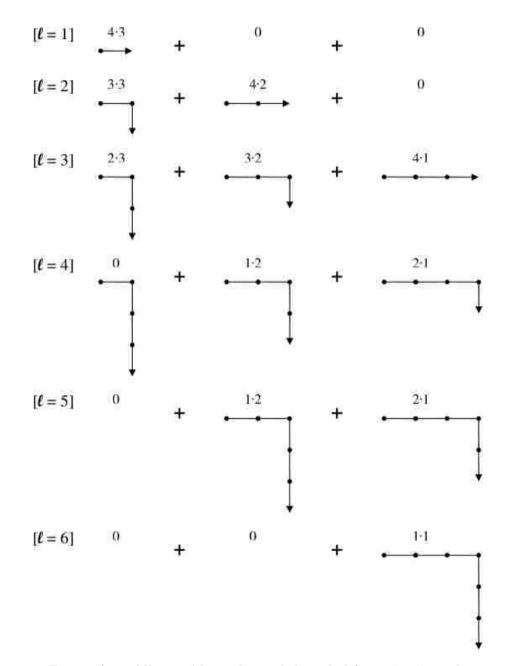

| A.1 | All possible paths with length $l$ for a $4 \times 4$ mesh                |

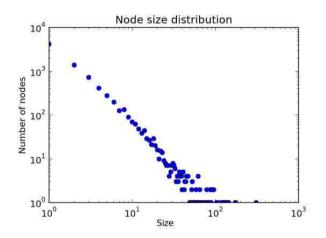

| C.1 | Power-law distribution of node sizes for a binary tree with 100,000       |

|     | nodes and depth 20                                                        |

# List of Tables

| 3.1 | Closed-form solutions for power on different topologies                                                                                                                                                                    | 27 |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2 | Theoretical estimates for scaling in different topologies according to asymptotic analysis.                                                                                                                                | 27 |

| 4.1 | Predicted and simulated energy values for 8×8 and 10×10 NoCs. The uncertainty values arise from the limited number of packets sampled from the CPD                                                                         | 41 |

| 5.1 | Percent improvement in energy and runtime for the LLB and first-touch (FT) data placement (relative to the uniform mapping). Also shown is the total traffic for each method in number of messages                         | 59 |

| 5.2 | Average percentage energy savings and runtime improvement for<br>LLB when testing a previously generated mapping on 20 different<br>inputs per program. Also shown is the similarity between the com-<br>munication graphs | 62 |

| 6.1 | Rent's rule parameters $p$ and $b$ for CMP applications                                                                                                                                                                    | 69 |

| 7.1 | List of all the scaling dimensions defined in this chapter                                                                                                                                                                 | 84 |

List of Tables

# Chapter 1

# Introduction

Over the last 40 years, the monolithic CPU design has scaled in performance by six orders of magnitude, following exponential trends dictated by Moore's law. However, the traditional sources of performance improvement—e.g. instruction level parallelism and clock frequency increase—have saturated. Computer architecture design has entered a new era, in which performance is increased by adding more CPUs (or cores) to a chip instead of making larger and faster ones. As transistor density continues to increase fostered by process technology improvement, an exponential growth in the number of cores on a chip is expected in the following years [84].

This shift of the industry towards the multi-core architecture is motivated primarily by energy and power consumption. With the highly complex circuits and high clock frequency of modern billion-transistor CPUs, we have reached the limit of how much power (and heat) can be dissipated on a chip and cooled by air. Increased demand for embedded systems, such as smartphones, tablets and netbooks, has also raised the concern for energy and power consumption. Because these devices have limited energy resources, embedded processors are designed to minimize energy con-

#### Chapter 1. Introduction

sumption and increase battery life. Energy is also a major concern in servers and data centers. Currently, the energy used for operating and cooling servers accounts for about 1% of all the electricity in the United States [56]. A study shows that the energy bill for data centers worldwide more than doubled between 2000 and 2005 [57]. With increasing demand for Web content, this situation is expected to worsen in the upcoming years. In modern High-Performance Computing (HPC) systems, power is also the biggest constraint. The exascale computing challenge aims at improving the performance of supercomputers by  $1000 \times$  in 10 years, but current trends in energy consumption for such machines render this goal unattainable [54]. A large investment is underway to increase the energy efficiency of supercomputers, in the US and worldwide, to avoid the energy bottleneck in the future generation of HPC machines.

The multi-core architecture is a viable alternative to the traditional monolithic design because parallelization is a more energy-efficient way of improving performance [39]. Because performance of individual cores is not expected to increase significantly in the future, the energy used per core for computation will likely decrease with miniaturization. However, cores need to communicate at increased rates as the system grows in size, which increases the energy consumption used for communication on the Network on Chip (NoC). This energy will vary considerably depending on the behavior of applications and on the locality of their communication patterns, but it will invariably increase, imposing serious constraints on design and performance of both applications and architectures.

This dissertation focuses on predictive mathematical modeling and optimization of energy and power consumption in multi-core chips. We present a number of software tools and mathematical models to optimize energy consumption and predict scaling patterns, and use synthetic traffic patterns and full system simulations to test and validate our methods. Finally, we take a step back and look at the evolution of computer hardware over the last 40 years and, employing an interdisciplinary approach, devise a theoretical framework for analyzing power-performance scaling in microprocessor systems in general.

### 1.1 Contributions and organization

The remainder of this dissertation is divided into 7 chapters:

- Chapter 2. This chapter reviews the background material that is required for reading this dissertation. We give an introduction to networks on chip focusing on their basic architecture and topologies. Also included is a review of memory and communication models in parallel architectures, such as shared and distributed memory systems. Finally, we discuss traditional methods for thread-mapping and scheduling used for optimizing runtime and energy consumption in parallel architectures.

- Chapter 3. This chapter analyzes the impact of different NoC topologies on the scaling of power consumption. Using a simple model of inter-core communication, we provide an asymptotic analysis of power and performance in network on chip topologies. The results of the theoretical model are then compared to simulations, with an excellent agreement between theory and experiment. The chapter concludes with a surprising result: Although power and performance may vary widely among topologies, their energy efficiency is approximately the same, and the traffic pattern is a more important factor of efficiency than topology.

- Chapter 4. The most important component of NoC energy consumption is the communication locality of the network traffic pattern. This chapter analyzes the impact of commonly used artificial workloads and proposes a new synthetic

traffic pattern based on Rent's rule. This new method has the advantage of matching observed data and the ability of, by varying a single parameter, emulate a continuum of applications with varying degrees of communication locality.

- **Chapter 5.** Here, we take a deeper look into the multi-core architecture and analyze how the execution of applications can be optimized in order to reduce energy consumption. We propose a method for data placement optimization in sharedmemory CMPs, which reduces NoC energy consumption by 50% on average on scientific benchmarks, outperforming a state-of-the-art method. Different from other approaches in the literature which are heuristic-based, our method is exact and can be solved in polynomial time. The experiments in this chapter were performed using full-system simulations and 64 cores.

- **Chapter 6.** In this chapter, we use a theoretical framework based on Rent's rule to analyze the minimum possible energy consumption of an application. We show that applications with low Rent's exponents can be highly optimized for low energy consumption, while applications with high Rent's exponent are bound to be energy-inefficient. Our model shows an excellent match with experimental results obtained using full-system simulations.

- Chapter 7. This chapter puts together many of the elements developed in the previous chapters and, employing an interdisciplinary approach, proposes an innovative mathematical framework for the study of power-performance scaling in general-purpose microprocessors. This theory, inspired by Metabolic Scaling Theory in biology, analyzes power as being determined by the geometry of computer interconnects. The proposed analysis leads to extremely simple laws that describe the scaling of power and performance in microprocessors over several orders of magnitude.

- Chapter 8. This chapter concludes the dissertation.

# Chapter 2

# **Background Information**

This chapter covers the background information on networks on chip and computer architectures required by the subsequent chapters. Section 2.1 introduces the NoC communication structure and reviews its properties and most common topologies. Section 2.2 reviews the common memory and communication models used in parallel architectures. Special focus is given to shared memory systems, which is the dominant architectural organization for multi-core chips. Finally, Section 2.3 introduces the basic ideas of communication locality and, consequently, energy optimization through mapping and scheduling of threads.

### 2.1 Network on Chip

Cores need to communicate to share load and decrease the running time of applications. Different modules typically communicate on a chip using dedicated buses. This communication architecture can be very efficient for a small number of devices, but it lacks scalability for large systems. As the system grows, increased competition for network usage leads to frequent collisions, and starvation is more likely to oc-

cur. Moreover, as more units are attached to the network and the bus grows in size, the capacitance of the wires increases and the energy cost of switching a single bit becomes too high, leading to excessive power consumption. Finally, as capacitance increases, the time necessary for the residual currents to die away in order to perform a new switching also increases, leading to a prohibitively low bandwidth.

To cope with these limitations, the computer architecture research community proposed a concept called Networks on Chip (NoC). The NoC is a packet-switched interconnection network for Systems on Chip (SoC), in which modules (also called *Intellectual Properties*—IPs) communicate by sending and receiving messages. Figure 2.1 depicts the basic structure of an NoC. In this design, switches handle temporary storing and forwarding of packets and the implementation of routing and arbitration protocols. The network interface (NI) provides the interface between the IP and the network and is responsible for many functions, such as packetization and de-packetization of messages, clock adaptation, flow control, and implementing the network protocols [26]. It serves as a standard interface between any device and the network, thus allowing for reuse of IPs. When a module needs to communicate, the message to be sent is divided into packets that are sent to a switch, which forwards the packets to another switch, until the message arrives at the appropriate destination.

A SoC can be homogeneous or heterogeneous. In a homogeneous SoC, all IPs are of the same type, such as cores in a Chip Multi-Processor (CMP), used for general-purpose computing. Heterogeneous SoCs are commonly used for applicationspecific tasks, such as in embedded systems. The SoC approach, using an NoC for communication, has many advantages over the traditional interconnect design used in monolithic CPUs. The point-to-point, dedicated wires of monolithic architectures are one of the main drawbacks of the traditional system. These unstructured wires lead to low bandwidth, low duty factor and high power consumption, and also increase

Figure 2.1: Basic structure of an NoC.

the complexity of the design. Based on these considerations, the advantages of a NoC for SoCs were summarized by [24] as follows:

- 1. Predictable electrical parameters enable high-performance circuits. Unstructured wires have parasitic capacitances and crosstalk noise that are difficult to predict. As a result, in order to ensure reliability, very conservative circuits must be used to drive and receive these wires, leading to excessive power consumption. The well structured and predictable wires of a NoC allow for aggressive circuit techniques, which can reduce power dissipation by a factor of ten and increase wire propagation by three times, while also improving bandwidth.

- 2. Universal interface facilitates reuse of components. By introducing a universal interface for IPs and the network, components can be reused in many systems, thus reducing complexity and simplifying circuit implementation.

- 3. Design and testing are facilitated. Since the system is modular and components are reused, design and testing of entire systems is mostly concerned with optimization of a regular, generic communication medium with predictable parameters. CAD issues involved in the design of dedicated, customized circuits

in specific components, such as wiring routing, are avoided.

- 4. Duty factor of the wires is improved. In traditional chip designs, individual signals must travel as fast as possible to their specific destination, leading to an excessive number of dedicated global wires which are active only 10% of the time, in average. The aggregated flux of information in general-purpose NoCs can provide wire duty factors close to 100%.

- 5. Enable the use of fault-tolerant strategies. With technology scaling and decrease in the voltage usage wires become more susceptible to noise and faults. Eventually, it will be impossible to completely avoid such errors (called upsets) in communication, and the system must be able to deal with them. A NoC architecture can implement error-identification/error-correction protocols that make the system tolerant to faults.

- 6. *Wire pipelining.* Globally asynchronous protocols allow for wire pipelining, thus increasing bandwidth and making communication independent of latency.

- 7. *Scalability*. The NoC architecture is scalable; the aggregated bandwidth increases with network size.

### 2.1.1 NoC Topologies

The NoC depicted in Figure 2.1 uses a 2D mesh topology. However, many other NoC topologies have been proposed, most of which were adapted from the parallel computing world. Some of the most popular NoC topologies are shown in Figure 2.2.

An important property of a topology is bisection bandwidth scaling. The *bisection* width is the number of wires that must be cut to divide the network into two equal sets of nodes, and the *bisection bandwidth* is the collective bandwidth over these wires. As

Figure 2.2: NoC topologies. (a) Fat tree, (b) mesh, (c) torus, (d) folded-torus, (e) octagon, (f) butterfly fat tree. (Figure reproduced from [73].)

more nodes are attached to the network, a larger volume of communication and more bandwidth is required. If the network bandwidth does not scale appropriately with the number of nodes, excessive traffic leads to high message latency and decreased performance. However, networks with high bisection bandwidth require more routers and more wires per node, which consume considerable area and increase the cost of the system.

Many studies have been dedicated to comparing topologies in the NoC literature. Pande *et al.* [74, 73] compared five topologies, studying throughput, latency, energy consumption and area requirements, using nearest-neighbor local traffic with different injection rates. They reported results for system sizes up to 256 cores, showing a trade-off between topologies that provide better throughput and latency but have high power and wiring overhead, versus topologies with lower performance and reduced power consumption. Kreutz *et al.* [60] analyzed bit energy consumption and latency for mesh, torus, and fat tree topologies on 16-node networks, using Romberg integration, Fast Fourier Transform, and an image processing application to generate workloads. They concluded that the fat tree minimizes latency and the mesh

topology consumes the least energy.

Boroni and Concer [11] compared ring, spidergon, and mesh topologies under uniform random, homogeneous sources and destinations, and hotspot traffic patterns. They simulated networks ranging from 8 to 32 cores, measuring throughput and latency as a function of injection rate. The spidergon performed the best. Boroni et al. [10] extended this work, studying systems up to 64 cores and adding the crossbar topology, which slightly outperformed the spidergon. Rahmati *et al.* [78] analyzed latency and power consumption for mesh and WK-recursive topologies with 16 cores and uniform traffic. WK-recursive was found to be superior to mesh in terms of latency and power consumption for low traffic, but the two were similar under heavy traffic. A similar comparison by Suboh *et al.* [87] included the spidergon, also concluding that the WK-recursive network had the best performance. Koohi *et al.* [55] and Mirza-Aghatabar *et al.* [69] analyzed  $6 \times 6$  mesh and torus networks with uniform random, hot-spot, nearest-neighbor, and first matrix transpose traffic. They measured latency, power consumption, and throughput, finding that the torus has higher power dissipation than the mesh but performs better in terms of power/throughput.

Topologies are usually compared in terms of power, throughput, and latency, as a function of packet injection rate and under different traffic patterns, but an important aspect of a topology is how easily it can be implemented on chip. Since chips are two-dimensional, topologies such as mesh and torus are more naturally suited to physical implementation on a die. Topologies also constrain the routing algorithms that can be used. Because the routers, and not the wires, are the main bottleneck in terms of latency and bandwidth in an NoC, routing must be simple enough so that the routing decision can be made as quickly as possible. A simple yet deadlock-free algorithm is xy- or dimension-order routing, which is designed for regular topologies, such as mesh and torus. Because of these advantages, these two topologies are usually considered the best candidates for NoC [47].

Figure 2.3: Centralized shared memory architecture, also called UMA. All CPU nodes access a single physical memory. L1 and L2 correspond to private level 1 and level 2 caches.

### 2.2 Memory and Communication Models in CMP

How do cores communicate? What kind of information is exchanged among them and how is it structured? The answer to these questions depends on the particular memory and communication models adopted in a given CMP architecture. In this section, we review the main communication models for multi-processing, with special emphasis on the models suited to implementation on chip.

### 2.2.1 Models of Parallel Architectures

There are two main models of parallel architectures: shared memory and distributed memory. In shared memory architectures, multiple processors share a single memory address space. As will be explained in Section 2.2.2, communication between shared-memory processors occurs implicitly by cache coherence. Figure 2.3 depicts the basic structure of a *centralized shared memory* architecture, where multiple processors access a single physical memory. This architecture is also called *uniform memory access* (UMA), from the fact that all processors have a uniform latency to memory.

Figure 2.4: Distributed memory architecture. Memory address spaces are independent and private to each CPU.

In *distributed memory* systems, the memory is physically distributed among processors and each processor has private access to its local memory. In such architectures, communication occurs explicitly by message passing. Figure 2.4 shows the basic structure of a distributed memory system. Notice that the address space is private to each memory.

Intermediate paradigms exist between these two extremes. The *distributed shared memory* architecture is a shared memory system in which memory is physically distributed. Each processor is associated with a local memory, but all memories in the system use the same address space, as depicted in Figure 2.5. Such architectures are also called *non-uniform memory access* (NUMA), because local memory access has lower latency than remote memory access.

The next model is the *non-uniform cache access* architecture (NUCA). The NUCA architecture is a variation of the UMA system, where the higher level cache is also shared (Figure 2.6). More specifically, the L2 caches are distributed but they share a single address space. Therefore, at any moment in time there can be only one copy of a memory block in the L2 cache. There are several advantages of shared cache, especially for on-chip multi-processor systems. First, the total cache capacity increases, which increases the cache hit ratio and reduces main memory bandwidth

Figure 2.5: Distributed shared memory architecture. Memories are physically distributed but share a same address space.

requirements. Also, cache coherence at the L2 level is not necessary, thus reducing the complexity of the system. The trade-off is that processors have to access blocks of memory that are stored in caches at remote locations, which increases cache hit time and on-chip bandwidth demands. Fortunately, the NoC design provides high on-chip bandwidth and low latencies, making the shared cache a viable alternative.

NUCA is the dominant architecture in commercial multi-core systems. Because

Figure 2.6: Non-uniform cache access (NUCA) architecture. This system has a centralized shared memory, but different from the UMA architecture, the level 2 caches are also shared.

Figure 2.7: Tiled chip multi-processor architecture. (Figure reproduced from [97])

the number of cores in those architectures is usually small, most systems employ a single memory bank for all L2 (or L3) caches, similar to Figure 2.6. However, this design is not scalable because, as the number of processors increases, some processors will be located far away from the memory bank and will have a much higher cache latency than others. A more scalable solution is shown in Figure 2.7. This tiled CMP architecture has an L2 cache associated with each processor and an NoC is used for remote cache access and cache coherence. Either shared or private caches can be implemented in this architecture.

#### 2.2.2 Cache Coherence

In order to understand how communication occurs in shared memory systems, in this section we briefly review the cache coherence problem and its basic implementation protocols. Suppose the following sequence of events occurs in a shared-memory computer:

- 1. Multiple processors hold the same memory block in their private cache.

- 2. One of the processors writes to that memory block.

3. In order to ensure that all processors see this change, it is necessary that the other copies be updated with the new information.

Based on the above, we can define cache coherence as follows: cache coherence is the property that guarantees that all processors see the same value in a shared memory address. The easiest and safest way to accomplish this is by updating all copies as soon as any processor writes on it. However, this leads to poor parallel processing performance because all processors have to stall until their copies are updated. As a result, relaxed models exist in which the copy update might be delayed. Memory consistency is the property that guarantees that the correct result of the program will not be affected by delays in the memory updates. Many consistency models exist, which define when the cache copies must be updated, such as sequential and processor consistency. The implementation of memory consistency is called synchronization. In shared memory systems, synchronization can be implemented implicitly using cache coherence.

There are two basic ways of implementing cache coherence, namely the snooping and the directory-based protocols. The snooping protocol has reduced latency, but requires a broadcast media and, therefore, is not scalable. The directory-based protocol is scalable to large number of processors, but it has increased latency and a slightly higher implementation overhead. Next, we give a brief introduction to both protocols.

#### **Snooping Protocol**

In this protocol, every cache that has a copy of the data from a block of physical memory also has a copy of the sharing status of the block, but no centralized state is kept. To keep track of the state of a block stored in cache, three bits are associated to each copy:

- Invalid—States whether the copy in cache is valid (up to date) or not.

- *Modified*—States whether the copy has been modified. If true, the cache holds the unique updated copy.

- *Shared*—States whether the copy is shared by other processors. In this state, the copy is read only.

When a processor wants to access some data that is not in cache, it broadcasts a data request message to the other processors. If one of these processors has the data, it will send the data to the requesting processor. If no processor has the data in cache, the requesting processor fetches the value directly from memory. Figure 2.8 contains a diagram illustrating this situation for a write-back cache, with emphasis on the communication between processors. When a processor wants to write on shared data it must send an invalidate message to the other processors. It then acquires block ownership and is free to write on the block. A diagram showing the main steps is given in Figure 2.9.

Because of broadcasting, the snooping protocol consumes excessive bandwidth and is limited to a small number of processors, such as 2 to 4. A more scalable option for cache coherence is given by the directory-based protocol.

#### **Directory-based Protocol**

The directory-based protocol avoids broadcasting by keeping the shared status of a block in just one location, called the *directory node*. The directory keeps track of all memory locations that might be cached. This protocol achieves scalability by making each processor the directory node of a different part of the physical memory.

Similar to the snooping protocol, whenever a processor wants to access data that are not in its cache it must request the data. However, instead of broadcasting a

Figure 2.8: Basic steps of a snooping protocol when a processor requests data. The fields I, M, and S correspond to the invalidate, modified, and shared bits. R represents a data request, D data reply, and WB data write-back to memory.

request message, it now sends a message exclusively to the directory node responsible for that block. The directory node then forwards the request to some other node that has a copy, or it might fetch the data from memory and forward it to the requesting

Figure 2.9: Basic steps of a snooping protocol when a processor wants to write on shared data. The fields I, M, and S correspond to the invalidate, modified, and shared bits. The arrows associated with a letter I are invalidate messages.

Figure 2.10: Basic steps of a directory-based protocol when a processor requests data. The fields I, M, and U correspond to the invalidate, modified, and uncached bits. R represents a data request, D data reply, and WB data write-back to memory.

processor if no processor has a cached copy. Note that the directory node must know whether the copy is cached and it also must keep track of what processors have a shared copy. To accomplish this, two new fields are necessary in the directory:

- Uncached—A bit stating whether a block of memory has no copies in cache.

- *Sharers*—A bit vector with all processors that share a cached copy.

Figure 2.10 shows the basic steps of a data request in the directory protocol.

When a processor needs to write on shared data, it must request ownership to the directory node, which sends invalidate messages to all processors that share the data. The requesting node then acquires ownership to write on the data. This process is illustrated in Figure 2.11.

Figure 2.11: Basic steps of a directory-based protocol when a processor wants to write on shared data. The fields I, M, and U correspond to the invalidate, modified, and uncached bits. The arrows associated with a letter I are invalidate messages.

Note that the directory-based protocol always requires one additional step than the snooping protocol. However, this solution exchanges slightly increased latency for higher scalability. Many other events can occur in cache coherence that are not described above. There are also several implementation details that were not covered. A more thorough account of snooping and directory-based protocol is given in [39].

### 2.3 Mapping and Scheduling

When running a parallel application on multiple processors, the compiler or the operating system decides *where* (in what cores) and *when* tasks should run. The former problem is called *application mapping* and the latter *application scheduling*. Oftentimes deciding *when* implies defining *where* the application should run and vice-

Figure 2.12: Task graph.

versa. Therefore it is not always the case that these two problems are independent of each other.

Most mapping and scheduling techniques rely on a graph-based description of applications called Task Graph (TG). The TG is a directed acyclic graph in which nodes correspond to tasks and edges correspond to control dependencies, meaning that a task can only start after the antecedent ones have completed. A task is any collection of operations that can be executed independently. Weights associated to edges indicate the CPU time required to conclude the execution of a task. Figure 2.12 depicts a typical example of a task graph.

The objective of mapping and scheduling is usually to minimize the execution time of applications and/or energy consumption. These optimization objectives are closely tied to maximizing communication locality, since the shorter the communication distances the less energy and latency involved in communication. Even in its simplest versions, mapping and scheduling are NP-Hard problems that require heuristics to be solved in practice. Lei and Kumar [62] proposed a genetic algorithm for mapping task graphs to an NoC, targeting execution time minimization. They assume a heterogeneous NoC, in which tasks have different execution times depending

#### Chapter 2. Background Information

on the selected IP, and used synthetic TGs as experimental data. Hu and Marculescu [45] proposed a mapping and scheduling method to minimize energy consumption on a heterogeneous 2D mesh NoC, in which energy is modeled using the bit-energy approach. Their algorithm decides what tasks will be executed in each processing element and, if more than one task is assigned to the same processor, when each task will be executed. They used artificial data generated using Task Graphs For Free (TGFF) [28] and a set of benchmark multimedia applications.

Chen et al. [17] proposed a compilation-based approach for mapping and scheduling applications on CMP. The approach works by first scheduling a TG on virtual processors targeting performance optimization and then by mapping the virtual processors onto physical processors. This second step occurs in a topology-aware manner in order to maximize locality. Locality is improved by locating processors that share data near one another. They tested their method on the SpecFP2000 benchmark [40]. Kandemir and Chen [49] proposed an operating system-based scheduler for CMP which increases data locality in two ways. Firstly, the processes that do not share data are scheduled in different cores and, secondly, processes that could not be executed at the same time due to dependencies but share data are mapped to the same core. Their scheduler targets performance optimization and the data used consists of array-based image/video processing applications. Pop and Kumar [76] present a methodology based on GA to map and schedule applications for multithreaded heterogeneous cores. They tested their technique on a  $2 \times 2$  NoC using TGFF synthetic data. Saeidi et al. [80] presented a Matlab tool for mapping and scheduling applications on homogeneous NoC platforms. Task graph data are synthetically generated and mapping is performed using a GA.

The works above employ static mapping and scheduling, which are performed at compile time. This approach has the advantage of reduced execution overhead, but might lead to poor performance in unpredictable environments and is architecture

#### Chapter 2. Background Information

dependent. An alternative approach is dynamic scheduling, which is performed at execution time. Dynamic scheduling leads to higher execution overhead, but is architecture independent, and is preferable for unpredictable applications and computing environments. Most dynamic techniques are based on sub-optimal, greedy solutions. State-of-art dynamic schedulers include work stealing (WS) and parallel depth first (PDF). WS works by maintaining a double ended work queue for each processor. When forking a new thread, the thread is placed on top of the local queue. When a processor looks for ready-to-execute tasks, it looks in its local queue first and takes a task off the queue if there is any. If the queue is empty, it checks the work queues of other processors and "steals" a task from the bottom of the queue. In PDF, when a core completes a task, it is assigned the ready-to-execute tasks that the sequential program would have executed the earliest. As a result, PDF tends to schedule tasks in a way that in some sense tracks the sequential execution. A comparison between WS and PDF shows that PDF provides better cache usage, thus optimizing performance relative to WS [18].

# Chapter 3

# Power Scaling in NoC Topologies

Interconnection networks of future multi- and many-core microprocessor systems will be required to deliver high performance at low power consumption to tens or even hundreds of cores [84]. In order to design energy efficient Networks on Chip (NoC) for systems of this magnitude it is necessary to understand how different network designs scale in terms of power and performance as the number of cores increases.

An important decision in NoC design is the network topology. Topological parameters, like hop count, bisection bandwidth, and wiring layout are closely related to the performance and power dissipation of a network, and may have considerable impact on scalability. NoC topologies have been studied extensively, e.g., [60, 74], and many alternative topological structures have been proposed [36, 51, 50, 66, 83]. However, few of these works focus on scaling.

In this chapter, we devise a theoretical model for power scaling in NoC topologies under uniform random traffic and use this model to analyze the trade offs between power and throughput in NoC. Uniform random traffic is a commonly used traffic pattern for NoC topology evaluation in which all nodes have an equal probability of talking to each other. In this study, we selected three topologies: binary tree, 2D mesh, and fat tree, which differ considerably in their bisection bandwidth scaling—O(1),  $O(N^{1/2})$ , and O(N), respectively, where N is the number of cores—, thus covering a representative range of scaling behaviors. In order to verify our theoretical model, we performed computer simulations using Orion [90] to measure power and throughput of the network topologies as a function of the number of cores.

### 3.1 A Theoretical Model of Power Scaling

Dynamic power dissipation in NoC topologies has two components: power consumed on the routers and power consumed by driving the wires between routers. In the following analysis, we assume that power on each router is proportional to the flow of packets in the router, i.e., the number of packets the router processes per unit of time. For each wire, we assume that power is proportional to the flow of packets times the wire length, since for repeated wires power increases linearly with the number of repeated segments. Secondary effects, such as the switch control path and virtual channel allocation, were ignored here for the sake of simplicity. Total power in a given network is obtained by summing up over all routers and all wires. Finally, accuracy is improved by normalizing the router and wire components of total power by the flow on the busiest router and busiest wire, respectively, as those components represent potential bottlenecks to the performance of the topology and constrain the maximum power of the whole network.

As an example, consider the binary tree with 16 processor nodes shown in Figure 3.1. Each processor injects one unit of flow of packets in the network, which will be equally divided between the other 15 nodes, assuming uniform random traffic. The figure illustrates how the flow generated by one processor is distributed over the entire tree. The total flow on the network is obtained by summing the flow injected by all 16 processors. Notice the routing algorithm must be considered when

Figure 3.1: Flow of packets injected by one processor in a binary tree network with 16 processor nodes. The numbers represent the fraction of the flow passing through each path of the tree. The values of k represent the levels of the tree.

computing this flow. For binary and fat trees, nearest-common-ancestor routing was used.

According to the figure, a given processor sends all its packets to a router at the first level of the tree (k = 1) to which it is directly connected. All the other routers at the same level receive 2 units of flow from this processor. Thus, each router at level 1 receives  $2 \times \frac{15}{15}$  units of flow coming from the 2 processors to which it is directly connected, and  $14 \times \frac{2}{15}$  units of flow from the remaining 14 processors. Since there are 8 routers at this level, total flow at level 1 of the tree is  $8 \times \left(\frac{30}{15} + \frac{28}{15}\right) = \frac{456}{15}$ . Applying the same reasoning to all the levels of the tree and generalizing for an arbitrary number of processors, the following equation is obtained for the total flow on the routers,

$$Flow_{routers}(N) = \frac{N}{N-1} \sum_{k=1}^{\log N} \left[ (N-2^k) + (N-2^{k-1}) \right],$$

(3.1)

where N is the number of processors. Power is obtained by normalizing equation 3.1 by the flow on the top router, which after some simplification yields:

Routers <sub>binary tree</sub>(N) =

$$\frac{c_r}{2N - 3 \cdot 2^{\log N - 1}} \left[ 2N \log N - 3 \cdot \sum_{k=1}^{\log N} 2^{k-1} \right],$$

(3.2)

where  $c_r$  is a constant that defines the power per packet in a router. For wires, the equation of flow will be similar to that of routers, but in order to calculate power it is necessary to weight the flow by the wire length at each level. For binary and fat trees, the H-tree layout was adopted, thus the length of the wires doubles at each hierarchical level. Since the die size is assumed to be constant as the number of processors increases, the length of the shortest wires decreases as N. Consequently, the length l(k) of a wire at level k becomes,

$$l(k) = \frac{l_0 2^k}{\sqrt{N}},\tag{3.3}$$

where  $l_0$  is a constant denoting the length of shortest wire segment. The final equation for power on wires in a binary tree is:

Wires <sub>binary tree</sub> =

$$\frac{c_w}{\sqrt{N}(N-2^{\log N-1})} \sum_{k=0}^{\log N-1} (N-2^k)2^k$$

, (3.4)

where  $c_w$  is a constant that defines power per packet per wire segment. The same method when applied to mesh leads to the following equations:

$$Routers_{mesh} = \frac{c_w \cdot 8}{N-1} \sum_{x=1}^{\sqrt{N}-1} \left[ x \left( N - x\sqrt{N} \right) \right], \qquad (3.5)$$

Wires <sub>mesh</sub> =

$$\frac{c_w \cdot 8}{N^{3/2}} \sum_{x=1}^{\sqrt{N-1}} \left[ x \left( N - x \sqrt{N} \right) \right],$$

(3.6)

where the variable x represents the x-coordinates for one side of a squared mesh. For the mesh topology, the xy-routing algorithm was used in the computation of flows. Finally, for the fat tree topology the power equations are given as:

Routers fat tree

$$(N) = \frac{c_r \cdot N}{N-2} \sum_{k=1}^{\log N} (N-2^k),$$

(3.7)

Routers fat tree

$$(N) = \frac{c_r \cdot N}{\sqrt{N} (N-2)} \sum_{k=0}^{\log N-1} (N-2^k) 2^k,$$

(3.8)

| Topology    | Power on Routers                                           | Power on Wires                                                                                |  |  |

|-------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------|--|--|

| Binary tree | $c_r \cdot 4 \log N - 6 - \frac{6}{N}$                     | $\frac{c_w \cdot 2}{N^{3/2}} \left( N^2 - 2N - \frac{4^{\log N}}{3} - \frac{4}{3} \right)$    |  |  |

| Mesh        | $c_r \cdot 4N$                                             | $\frac{c_w \cdot 4(N-1)}{3\sqrt{N}}$                                                          |  |  |

| Fat tree    | $\frac{c_r \cdot N}{N-2} \left( N \log N - 2N + 2 \right)$ | $\frac{c_w \cdot \sqrt{N}}{N-2} \left( N^2 - 2N - \frac{4^{\log N}}{3} - \frac{4}{3} \right)$ |  |  |

Table 3.1: Closed-form solutions for power on different topologies.

Table 3.2: Theoretical estimates for scaling in different topologies according to asymptotic analysis.

| Topology    | Total Power  | Throughput   | Energy per packet |

|-------------|--------------|--------------|-------------------|

| Binary tree | $O(N^{1/2})$ | O(1)         | $O(N^{1/2})$      |

| Mesh        | O(N)         | $O(N^{1/2})$ | $O(N^{1/2})$      |

| Fat tree    | $O(N^{3/2})$ | O(N)         | $O(N^{1/2})$      |

# 3.2 Analysis of the Scaling Behavior

Here we give closed form solutions, shown in Table 3.1. Next, we characterize the asymptotic behavior of these topologies, observing that, for large enough values of N, the highest order terms dominate. For instance, in binary tree, power on the routers scales as  $O(\log N)$  and power on the wires as  $O(N^{1/2})$ , thus the wire component dominates total power dissipation. For a 2D mesh, power is dominated by the routers as O(N), and in the fat tree by the wires as  $O(N^{3/2})$ . Finally, by dividing power by throughput we measure energy per packet. Under uniform random traffic, throughput is expected to scale as the bisection bandwidth. Table 3.2 summarizes the expected scaling behavior of power, throughput, and energy per packet for all three topologies resulting from asymptotic analysis.

The values in Table 3.2 show that, although the topologies analyzed vary widely in

terms of power dissipation and throughput, energy per packet for all three networks scales in the same way. This result is somewhat surprising, given the emphasis in the literature about which NoC topologies are the most energy efficient. Notice that, since energy per packet is the same, the resulting power consumption in each topology is proportional to throughput times the average energy per packet. Thus, there is a linear trade-off between power and throughput, and topologies able to achieve high performance will, consequently, have high power consumption. This theoretical finding formalizes experimental results reported in the literature [74].

Therefore, for uniform random traffic and large enough N, the above analysis suggests that topology has negligible influence on the scaling of packet energy consumption.

### **3.3** Experimental Results

#### 3.3.1 Simulation Infrastructure

All simulations were performed using Orion 1.0. For each topology, networks with 8 up to 1024 processor nodes were simulated and average power and throughput were measured as a function of the number of cores. Orion calculates router power into three separate components: memory, arbiter, and crossbar power. Links are automatically divided into repeated wire segments, based on length. Traffic injection rates were set high enough in each run to saturate the network. As a consequence, actual packet injection is proportional to maximum throughput, and may vary with both the topology and the traffic pattern.

All simulations were run in a  $0.1\mu m$  process, which is the standard for Orion 1.0. Packets are comprised of 4 flits of 64 bits. Routers have 2 to 4 physical ports, 4 virtual channels, and a 12-flit output buffer. Each link is composed of 2 unidirectional, 64-bit channels. A credit policy was used to account for buffer availability on routers. The routing algorithm used for the mesh topology was xy-routing, and for the binary and fat trees we used nearest-common-ancestor routing with randomized upward paths.

#### 3.3.2 Results

In the following experiments, uniform random traffic is simulated and the results are compared with the theoretical predictions of the model presented in Section 3.2. Figure 3.2 shows the curves obtained for the three topologies. The confidence intervals are too small to be visible in the graphs. However, there is an excellent agreement between the theoretical model and the simulated results; the computed  $R^2$  correlation coefficients were above 0.99 for all the curves.

The scaling behavior of throughput and power varies for each topology. For instance, fat tree achieves the highest throughput, with linear increase in the number of delivered packets per cycle as N increases. It also has the highest power consumption, since both, power on routers and power on wires scale super-linearly with the number of cores, as  $O(N \log N)$  and  $O(N^{3/2})$ , respectively. In binary tree, the scaling of power consumption is relatively small: power on routers grows as  $O(\log N)$  and on wires as  $O(N^{1/2})$ , a slower than linear rate of increase in both cases. However, its throughput remains constant and does not scale with the number of cores. Mesh represents an intermediate case, with moderate throughput and power scaling. For this topology, power on routers scales approximately linearly with N, and faster than power on wires, which increases as  $O(N^{1/2})$ .

In contrast to power and throughput, the scaling curves of energy efficiency for the three topologies are remarkably similar. This result agrees with the theoretical predictions of the asymptotic analysis in Section 3.2, and shows that topological properties, such as bisection bandwidth, number of routers and wire layout, which

have high impact on throughput and power, have little influence on the overall energy efficiency of the networks.

Although they are similar, the energy efficiency curves are not identical. Some discrepancy is expected because, as predicted by the theory, scaling in the three topologies is the same only for large values of N. Also, implementation details of the simulations may affect the scaling constants of each topology in a slightly different way. For example, because in the mesh topology, power on the routers scales faster than power on the wires, using a smaller constant for power on the routers will favor mesh over binary and fat tree in the scaling of energy per packet.

The experimental results show that, for uniform random traffic, energy per packet increases significantly as the number of cores increases and sending a message over the network becomes increasingly expensive. This happens because uniform random traffic lacks any locality of communication, leading to poor NoC scalability.

# 3.4 Conclusion

In order to design scalable multi-core architectures with thousands of cores, it is important to understand how power consumption on the NoC increases as the number of cores increases. In this chapter, we presented a theoretical model for the scaling of power and performance of different NoC topologies under uniform random traffic. Our main result is that there is a linear trade-off between throughput and power, i.e., topologies that deliver higher performance have higher power consumption and vice-versa, in a linear fashion. As a result, energy efficiency scales in the same way independent of the topology. In this scenario, locality of communication and not topology is the main variable affecting energy efficiency, as will be seen in subsequent chapters. Our models showed excellent agreement with simulation results, which validates the accuracy of our theoretical approach.

Figure 3.2: Comparison between the theoretical results of our models with simulation results

# Chapter 4

# Modeling NoC Communication Locality using Rent's Rule

Rent's rule is an empirically observed pattern in VLSI designs that describes the communication structure between logic gates on a chip. Using derivations based on Rent's rule, the Wire Length Distribution (WLD) of a circuit can be estimated from its Rent's exponent and coefficient, p and k [25]. This distribution describes the communication locality in the circuit and, therefore, is related to many properties of the system, such as chip area, signal delay, power consumption, and wire routability [86].

In Systems on Chip (SoC), similar information is provided by the Communication Probability Distribution (CPD) of applications. The CPD describes the probability that packets will travel a certain distance in the Network on Chip (NoC) for a given traffic pattern. This distribution is directly related to the energy consumption of an application, because the larger the distance traveled by packets, the more energy is used. Since current NoCs use 30 to 40% of the power budget [88, 43], it is desirable for the distance traveled by packets to be as small as possible in order to minimize

this cost.