# University of New Mexico UNM Digital Repository

**Electrical and Computer Engineering ETDs**

**Engineering ETDs**

8-28-2012

# Growth, processing and chracterization of gallium nitride based coaxial LEDs grown by MOVPE

Ashwin Rishinaramangalam

Follow this and additional works at: https://digitalrepository.unm.edu/ece etds

# Recommended Citation

Rishinaramangalam, Ashwin. "Growth, processing and chracterization of gallium nitride based coaxial LEDs grown by MOVPE." (2012). https://digitalrepository.unm.edu/ece\_etds/217

This Dissertation is brought to you for free and open access by the Engineering ETDs at UNM Digital Repository. It has been accepted for inclusion in Electrical and Computer Engineering ETDs by an authorized administrator of UNM Digital Repository. For more information, please contact disc@unm.edu.

| Ashwin Krishnan Rishinaramangalam                                                        |

|------------------------------------------------------------------------------------------|

| Candidate                                                                                |

| Electrical and Computer Engineering  Department                                          |

| Department                                                                               |

| This dissertation is approved, and it is acceptable in quality and form for publication: |

| Approved by the Dissertation Committee:                                                  |

| Dr. Ganesh Balakrishnan , Chairperson                                                    |

|                                                                                          |

| Dr. Sanjay Krishna                                                                       |

|                                                                                          |

| Dr. Sang Han                                                                             |

| Dr. Thomas Rotter                                                                        |

|                                                                                          |

|                                                                                          |

|                                                                                          |

|                                                                                          |

|                                                                                          |

|                                                                                          |

|                                                                                          |

|                                                                                          |

# GROWTH, PROCESSING AND CHARACTERIZATION OF GALLIUM NITRIDE BASED COAXIAL LEDS GROWN BY MOVPE

by

# ASHWIN KRISHNAN RISHINARAMANGALAM

B.Tech., Electrical Engineering, The Indian Institute of Technology, Madras, July 2006

# **DISSERTATION**

Submitted in Partial Fulfillment of the Requirements for the Degree of

**Doctor of Philosophy Engineering**

The University of New Mexico Albuquerque, New Mexico

July, 2012

©2012, Ashwin K Rishinaramangalam

# **DEDICATION**

This work is dedicated to my mother, Mrs. R. Kala Krishnan and my father, Mr. R.V. Krishnan, whose continued support and push for tenacity throughout my life has been unparalleled.

This work is also dedicated to my teachers and near and dear friends, who have taught me the meaning of life through both, forgettable and unforgettable incidents.

Finally, I dedicate this work to the almighty lord.

विद्या ददाति विनयं

#### **ACKNOWLEDGEMENTS**

It is my immense pleasure to thank Dr. Stephen Hersee for his immaculate guidance and constant source of encouragement in the course of the research. I feel extremely indebted to you, sir for seeing a researcher in me and constantly motivating me towards achieving this degree.

I would also like to thank Mike Fairchild, without who this dissertation would not have been possible. I am indebted to you, Mike, for the growth of all the samples and the timely maintenance of the reactor to enable research and development of this unique device.

I would also like to thank Dr. Ganesh Balakrishnan for choosing to chair my dissertation committee, who also was a constant source of encouragement and guidance. I really look forward to working with you over the next few years, Gunny.

I would also like to thank Dr. Sanjay Krishna, Dr. Sang Han, Dr. Ralph Dawson and Dr. Thomas Rotter for their support in the research evaluation and for serving on my dissertation committee.

I would also like to thank Dr. Lei Zhang and Dr. Rajeev Shenoi for their invaluable inputs during the microelectronic processing of the devices. I would also like to thank Steve Wawrzyniec and Douglas Wozniak for timely maintenance of the cleanroom equipment and also constant source of discussions during process development. I would also like to thank Chris Hains for his inputs during the preparation

of the manuscript and the defense PowerPoint presentation. I would like to thank Darryl

Shima for performing the cross-section TEM of the samples.

A friend should be one in whose understanding and virtue we can equally confide,

and whose opinion we can value at once for its justness and its sincerity<sup>1</sup>. In that regards,

I would like to thank my friends, in particular, Srikanth, Pramod, Krishnaprasad,

Geetanjali, and Soumik for their timely support, constant encouragement and their fun

company during my duration of stay here in Albuquerque. I would also like to thank my

friends outside Albuquerque, in particular, Ashwin Pejaver, Auditya, Arunachalam,

Aparna and Harini for their invaluable moral support during the course of this journey

towards a doctorate degree.

Family is not an important thing, it's everything<sup>2</sup>. I am extremely indebted to my

parents, Mrs. R. Kala Krishnan and Mr. R. V. Krishnan, and my brother, Anirudh, who

have always been unselfishly supportive, encouraging and have believed in me in all my

endeavors. I would also like to thank the Dasgupta family and the Memon family for their

support and treating me as their own member.

In the end, I would like to thank the almighty god for everything my life has to

offer.

- Ashwin Rishinaramangalam

Albuquerque, NM

July 2012

<sup>1</sup>Robert Hall

<sup>2</sup> Michael J. Fox

vi

# GROWTH, PROCESSING AND CHARACTERIZATION OF GALLIUM NITRIDE BASED COAXIAL LEDS GROWN BY MOVPE

by

### Ashwin Krishnan Rishinaramangalam

B.Tech., Electrical Engineering, The Indian Institute of Technology, Madras, 2006Ph. D., Engineering, University of New Mexico, 2012

# ABSTRACT

Gallium nitride (GaN) based coaxial (core-shell type) light emitting diodes (LEDs) offer a wide range of advantages. The active region of these LEDs is located on non-polar, {1100} m-plane GaN sidewalls, which helps eliminate the quantum confined Stark effect (QCSE) and improve the radiative recombination efficiency of LEDs. The recent evolution of a catalyst free, scalable, repeatable and industrially viable device quality GaN nanowire and nanowall metal organic vapor phase epitaxy (MOVPE) growth process has enhanced the possibility of these LEDs going into production from laboratory.

Previous work has shown that these nanowires exhibited an intense photoluminescence (PL), in spite of their large surface-area to volume ratio, and lasing was observed when these nanowires were optically pumped at high intensity. In this dissertation, it is shown that as long as the GaN three dimensional (3D) structures have their critical dimension below a micron, the threading defect (TD) density along the c-direction approaches zero. A TD that enters into this structure bends towards the surface

( $\{1\overline{1}00\}$  m-plane side wall) in its vicinity, thereby reducing its dislocation line energy. The possibility of growing zero defect GaN templates is extremely important in the breakdown voltage improvement, the reverse bias leakage current reduction and efficiency droop reduction.

This growth method has also been extended to device quality micron sized features, thereby presenting us with opportunity to study and explore LEDs of different sizes and shapes. In addition to the microstructure growth, two different repeatable approaches have been identified and demonstrated for the microelectronic processing of these micron-sized LEDs. Despite being far from perfect, the characterization results obtained from these LEDs have been encouraging. The technological challenges associated with the fabrication of the coaxial LEDs are also discussed in this dissertation.

# TABLE OF CONTENTS

| LIST OF FIGURES                                                      | xii |

|----------------------------------------------------------------------|-----|

| LIST OF TABLES                                                       | xix |

| Chapter1 Introduction                                                | 1   |

| 1.1 LEDs based on GaN material system                                |     |

| 1.1.1 Crystallographic orientations in wurtzite GaN                  |     |

| 1.1.2 Growth of wurtzite group-III nitrides and origin of threading  |     |

| defects                                                              | 6   |

| 1.1.3 Requirements of a highly efficient, high power, droop free     |     |

| LED                                                                  | 12  |

| 1.2 Coaxial LED expected attributes.                                 |     |

| 1.2.1 Absence of QCSE in GaN based coaxial LED                       |     |

| 1.2.2 Absence of threading defects in GaN based coaxial LED          |     |

| 1.2.3 High power emission for small coaxial LED footprint area       |     |

| 1.2.4 Polarized light emission in GaN based coaxial LED              |     |

| 1.2.5 Other attributes of UNM's coaxial LED based on GaN             |     |

| 1.1 Outline of the                                                   | 20  |

| dissertation                                                         |     |

| References                                                           | 23  |

|                                                                      |     |

| Chapter 2 Coaxial Nanowire LEDs grown by MOVPE                       | 27  |

| 2.1 Coaxial LEDs based on catalytic growth                           |     |

| 2.2 Coaxial LEDs based on non-catalytic growth                       |     |

| 2.3 Electrical and optical simulations studies of coaxial LEDs       |     |

| 2.4 Analysis of previous work                                        |     |

| References                                                           | 53  |

| Chantan 2 Three ding Defeat Elimination in CaN Nanastructures        | 57  |

| Chapter 3 Threading Defect Elimination in GaN Nanostructures         |     |

| 3.1.1 Functions of the FIB-SEM set                                   |     |

| 3.1.2 Theory of ion-milling                                          |     |

| 3.1.2 Theory of foll-filling                                         | 00  |

| nanostructures                                                       | 61  |

| 3.2 Experimental XTEM evidence for bending of threading defects      |     |

| 3.2.1 Bending of threading defects in GaN nanowires                  |     |

| 3.2.2 Bending of threading defects in GaN nanowalls                  |     |

| 3.3 Analysis of bending of threading defects                         |     |

| 3.3.1 Elastic energy reduction in TDs                                |     |

| 3.3.2 Bending of TDs caused due to image forces near surfaces        |     |

| 3.3.3 Analysis of TDs in GaN nanostructures grown at UNM             |     |

| 3.4 Coaxial nanostructures: Study of defects                         |     |

| 3.5 Study of threading defects in 3D grown GaN based microstructures |     |

| 3.6 Conclusion                                                       |     |

| References                                                           |     |

|                                                                      |     |

| Chapter 4 MOVPE Growth of 3D GaN Structures                             | 89  |

|-------------------------------------------------------------------------|-----|

| 4.1 Growth of 3D GaN structures                                         | 89  |

| 4.1.1 Growth of planar GaN substrate                                    | 90  |

| 4.1.2 Deposition of dielectric for SAG                                  | 92  |

| 4.1.3 Patterning of dielectric for growth mask                          |     |

| 4.1.4 Reactive ion etching of growth dielectric                         |     |

| 4.1.5 Pulsed MOVPE selective area growth of GaN                         |     |

| 4.2 Understanding the growth of 3D GaN structures: Capture radius       |     |

| calculation                                                             | 108 |

| 4.3 Understanding growth of GaN in annulus patterns                     |     |

| 4.4 Growth of GaN nanowires in selective area nanowire growth (SANG)    |     |

| patterns                                                                | 119 |

| 4.5 Conclusion.                                                         |     |

| References                                                              | 126 |

|                                                                         |     |

| Chapter 5 Growth of Coaxial 3D structures based on GaN                  |     |

| 5.1 Growth of p type GaN shell on n-type GaN core                       |     |

| 5.2 Growth of p-AlGaN shell on n-GaN core                               |     |

| 5.3 Growth of InGaN shell on n-GaN core                                 |     |

| References                                                              | 144 |

| Chapter 6 Processing and Characterization of Coaxial LEDs based on GaN  | 146 |

| 6.1 Process 1.1: Liftoff based p-metal process                          |     |

| 1 1                                                                     |     |

| Step 1: Photolithography: p-metal mask                                  |     |

| Step 2: Angled deposition of p-metal by e-beam evaporation              |     |

| Step 3: Photolithography: n-metal mask                                  |     |

| Step 4: Inductively coupled plasma (ICP) etching                        |     |

| Step 5: Deposition of n-metal by e-beam evaporation                     |     |

| Step 6: Thermal annealing of metal layers                               |     |

| 6.2 Process 1.2: Non-liftoff based p-metal process                      |     |

| Step 1: Angled e-beam evaporation of p-metal layers                     |     |

| Step 2: Patterning of p-metal side: Acid based wet etch                 |     |

| 6.3 Estimation of dielectric thickness for coaxial LED based on GaN     |     |

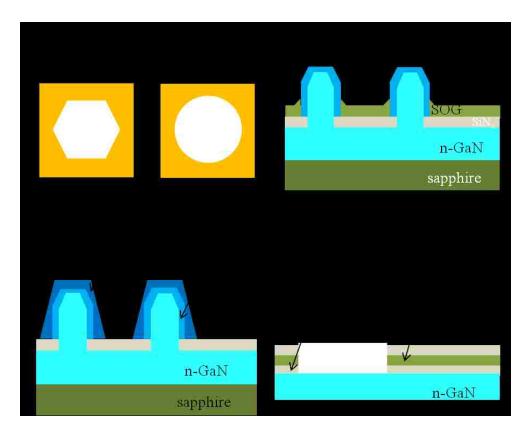

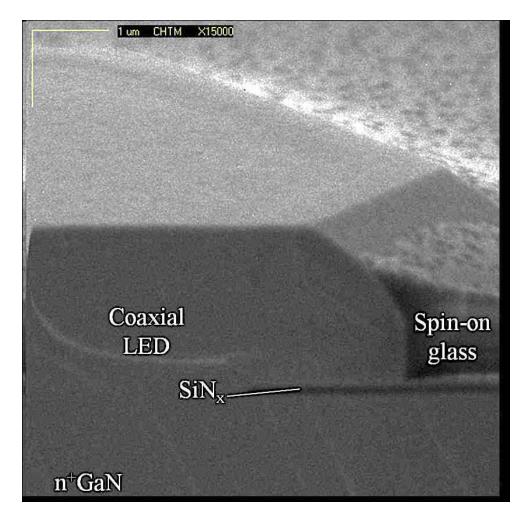

| 6.4 Elimination of stray growth on growth dielectric                    |     |

| 6.5 Elimination of current leakage through gaps between microstructures |     |

| 6.6 Characterization of pAlGaN-nGaN coaxial LEDs                        |     |

| 6.6.1 Processing of coaxial LED using spin on dielectric                |     |

| 6.6.2 Thin metal layer contacts to p-GaN                                |     |

| 6.6.3 Electrical and optical characterization of coaxial LEDs           |     |

| 6.6.4 Results and discussion                                            |     |

| 6.7 Conclusions                                                         |     |

| References                                                              | 185 |

| Chapter 7 Conclusions and future work                                   | 186 |

| Appendix A: Conference and Journal Publications                         | 190 |

# LIST OF FIGURES

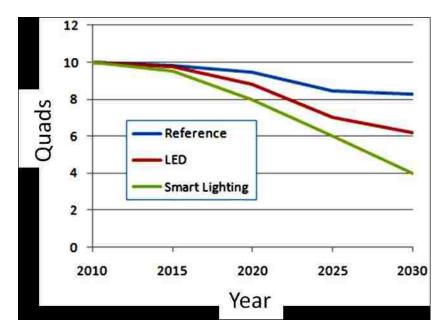

| Fig. 1.1 The comparison of the energy savings proposed by DOE upon using of LEDs and the savings that is possible using smart lighting sources, graph reproduced from [chapter 1, reference 2]. 1 Quad is defined as equal to 172million barrels of oil                                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

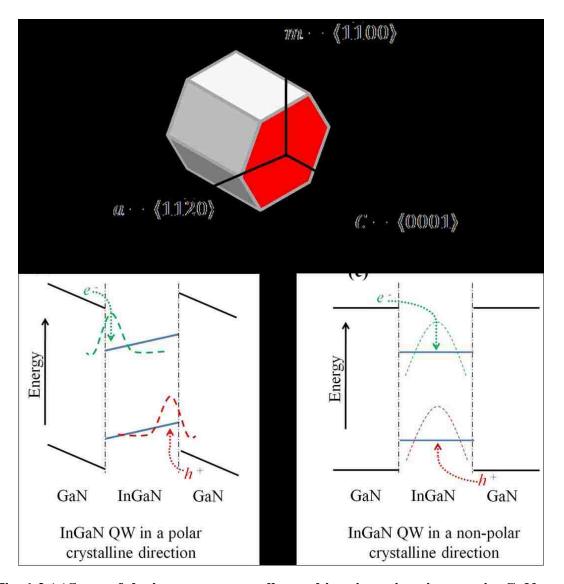

| Fig. 1.2 (a) Some of the important crystallographic orientations in wurtzite GaN and energy band diagram of InGaN QW sandwiched by GaN barrier layers, showing QCSE (b) in c-plane structures and absence of QCSE (c) in m-plane structures                                                                                                                                                                |

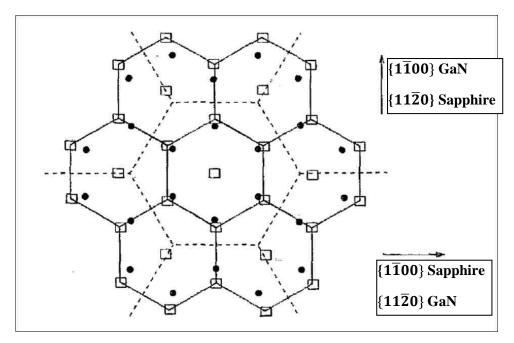

| Fig. 1.3 The projection of bulk c-plane sapphire and GaN showing the Ga atoms in GaN and Al atoms in sapphire for the observed epitaxial growth orientation, figure reproduced from [chapter 1, reference 3]. The black circles are Al-atom positions and the dashed lines represent sapphire c-plane unit cell. The squares are Ga-atom positions and the solid lines represent the GaN c-plane unit cell |

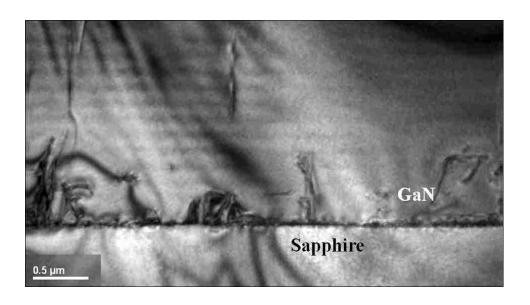

| Fig. 1.4 TEM micrograph of the c-plane sapphire-GaN interface showing the threading defects originating at the interface due to the lattice mismatch between sapphire and GaN                                                                                                                                                                                                                              |

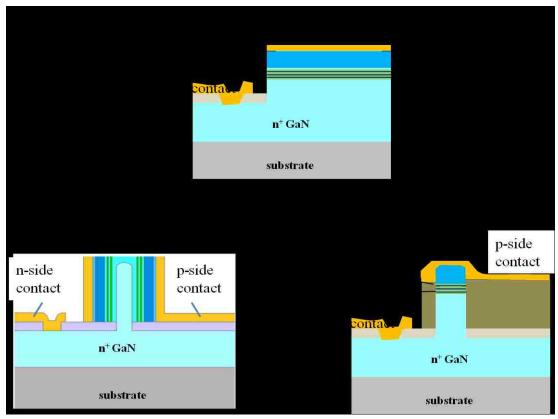

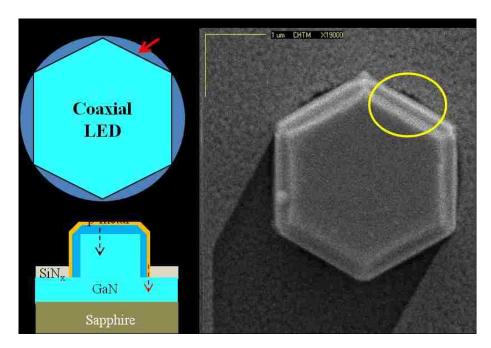

| Fig. 1.5 The cross-section illustrations of (a) a conventional planar heterostructure, (b) a coaxial heterostructure and (c) a non-coaxial 3D grown heterostructure, GaN based LED, respectively. In all cases, the vertical direction is the $c$ <0001> direction                                                                                                                                         |

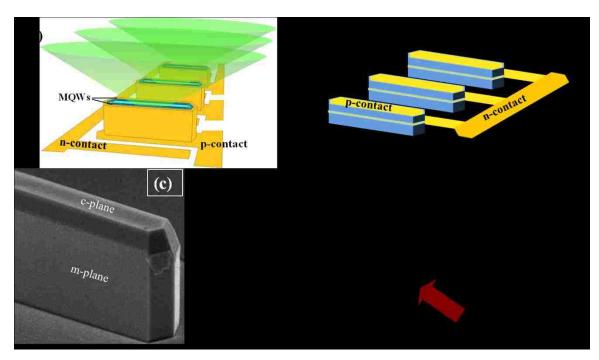

| Fig. 1.6 (a) and (b) The comparison of a coaxial LED with respect to 3D grown non-coaxial LED of a similar area foot print. (c) a scanning electron microscope image of a wall structure and (d) illustration of a nanowall structure, in which only one of these dimensions needs to be nanoscale (<1μm) to get a threading defect free device                                                            |

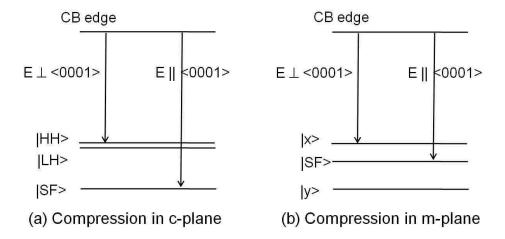

| Fig. 1.7 Conduction and Valence band line ups at k=0 for InGaN on GaN in (a) c-plane and (b) m-plane. The electronic transitions are shown with the optical polarization of the emitted photon corresponding to the transition. 'E' represents the direction of electric field of the emitted photon corresponding to the transition, figure reproduced from [chapter 1, reference 12]                     |

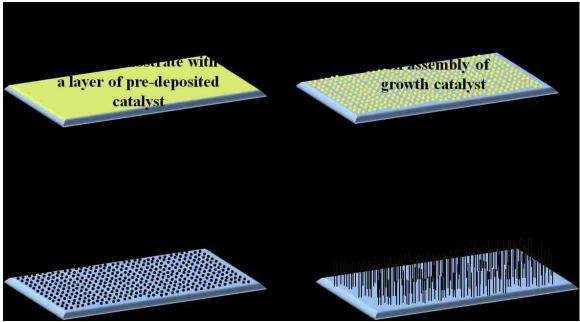

| Fig. 2.1 The 'VLS' growth mechanism initiated with a self assembled growth catalyst is described                                                                                                                                                                                                                                                                                                           |

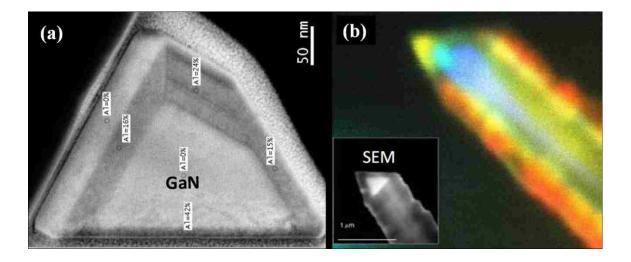

| Fig. 2.2 (a) The cross-section STEM image of a Coaxial nanowire structure and (b) the corresponding composite CL image showing multicolor emission from an InGaN shell due to an In composition distribution, both images reproduced from [chapter 2, reference 3]                                                                                                                                         |

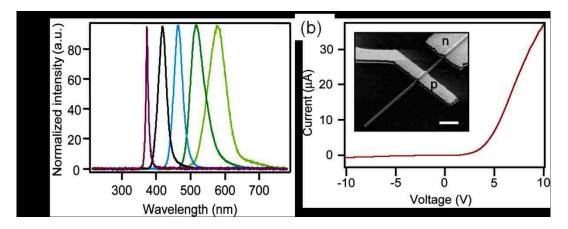

| Fig. 2.3 (a) EL spectra from five representative multicolor coaxial nanowire LEDs. and (b) the corresponding I vs. V curve of a coaxial LED shown in the inset SEM image, both images reproduced from [chapter 2, reference 2]                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

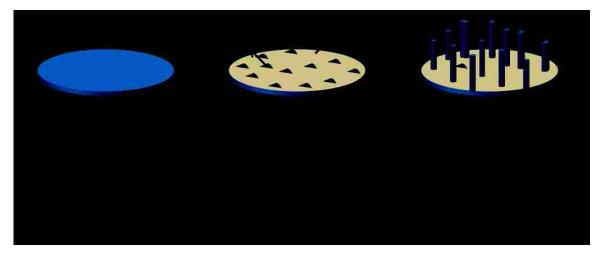

| Fig. 2.4 The pictographic illustration of the non-catalytic, template free GaN nanowire growth pursued by Koester <i>et al.</i> [chapter 2, reference 15]35                                                                                                                                                                                                             |

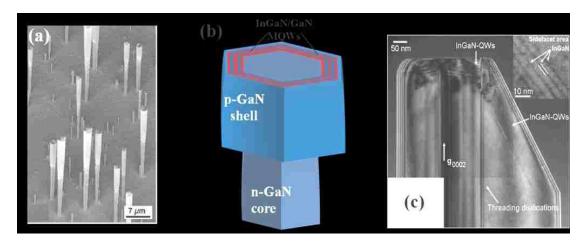

| Fig. 2.5 (a) SEM images of core-shell LEDs grown by Koester et al., image reproduced from [ref] and (b) illustrates the structure of the coaxial LED shown in SEM. (c) XTEM micrograph of core-shell GaN LED grown by Bergbauer et al. showing the propagation of a threading defect along the length of the nanowire, image reproduced from [chapter 2, reference 22]3 |

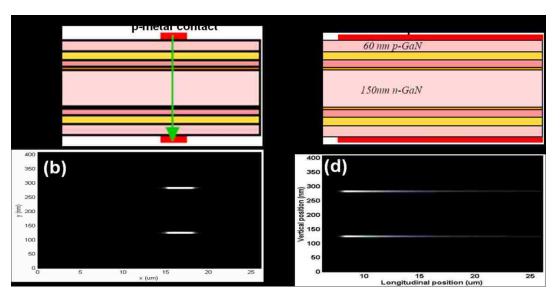

| Fig. 2.6 The simulated cross-section image of a Coaxial nanowire structure with a smaller area coaxial metal p-contact (a) in comparison with a larger area coaxial transparent ITO contact (c) and the corresponding map of the light generated in the respective coaxial LEDs (b) and (d), images reproduced from [chapter 2, reference 7 and 8], respectively        |

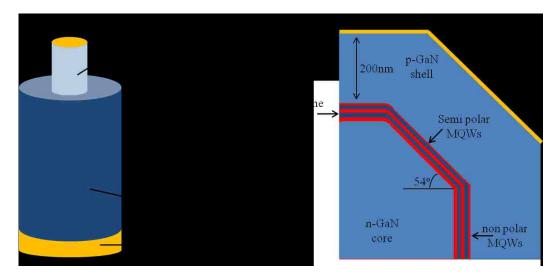

| Fig. 2.7 (a) The coaxial nanowire structure simulated by Connors <i>et al.</i> [chapter 2, reference 25] and (b) the cross-section of the coaxial LED structure simulated by Deppner <i>et al.</i> [chapter 2, reference 26] showing the three MQW's on the polar, semipolar and nonpolar GaN orientations                                                              |

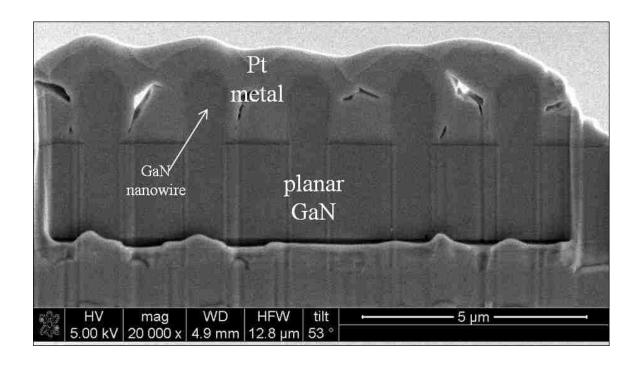

| Fig. 3.1 Cross-section SEM image of GaN based nanowire array structures thinned by a FIB at Evans Analytical, California, showing Pt deposited on the nanowire structures                                                                                                                                                                                               |

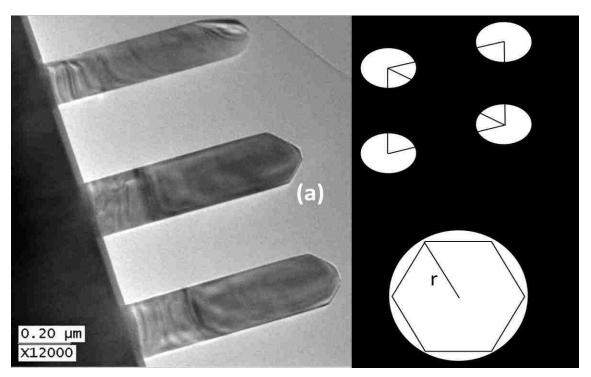

| Fig. 3.2(a) XTEM of a 200nm diameter GaN nanowire on a 500nm pitch (b) a pictorial representation of a section of the array of holes and the hexagonal GaN filling in the hole, as explained in [chapter 3, reference 22]6.                                                                                                                                             |

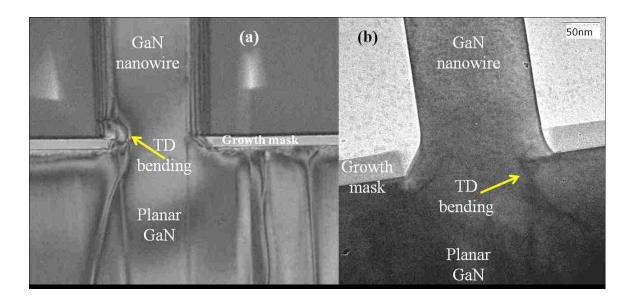

| Fig. 3.3 (a) XTEM image of a GaN nanowire showing a TD bending towards the {1100} sidewall after having entered the nanowire and (b) a XTEM image of GaN nanowire showing the bending by 90° and termination of a TD near the growth pattern mask                                                                                                                       |

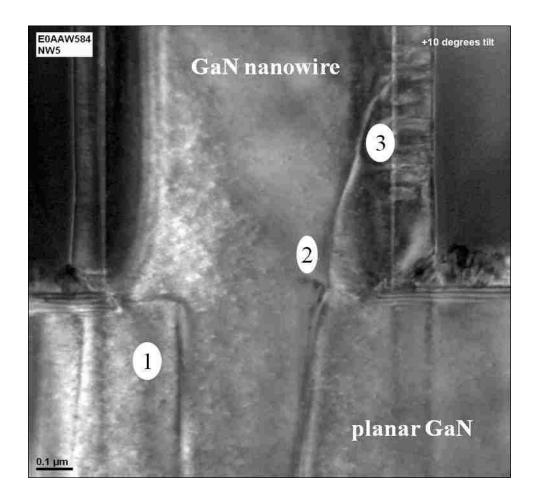

| Fig. 3.4 XTEM image of a GaN nanowire taken at a 10° tilt showing three TDs labeled, (1) is observed to bend 90° to terminate near the growth mask, (2) is observed to bend and disappear in middle of the nanowire and (3) is observed to enter the nanowire, but bends in multiple steps, finally reaching the {1100} sidewall                                        |

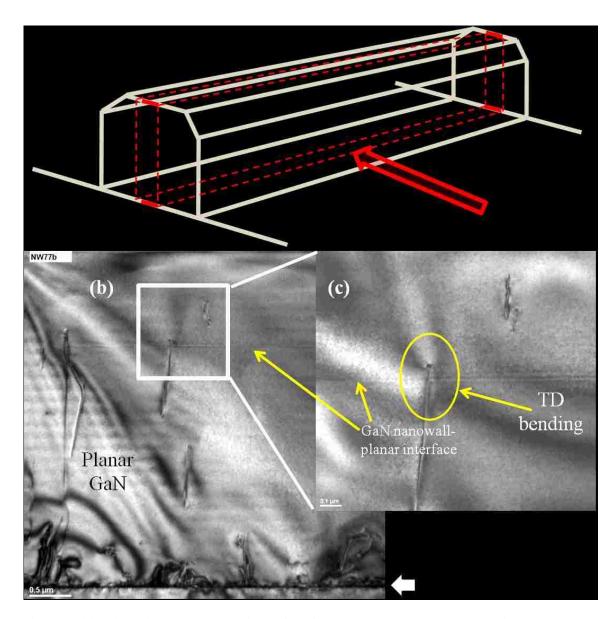

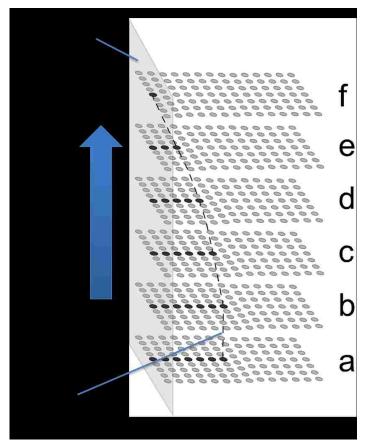

| Fig. 3.5 (a) Pictorial representation of a GaN nanowall sample showing the cross-section at which the XTEM image (b) was obtained. (b) shows bending of the TDs after the GaN nanowall-planar interface. (c) shows a closer view of the TD bending and disappearance in the nanowall, indication of bending towards a surface                                           |

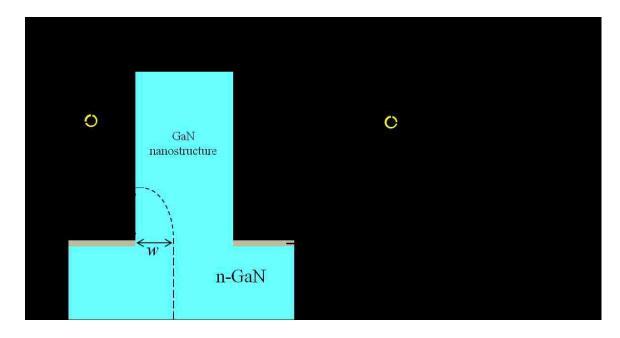

| Fig. 3.6 (a) The pictographic illustration of a TD bending towards the sidewall of GaN nanostructure due to the image force acting on the edge TD located at a distance 'w', as shown in (b)                                                                                                                                                                                 | .71 |

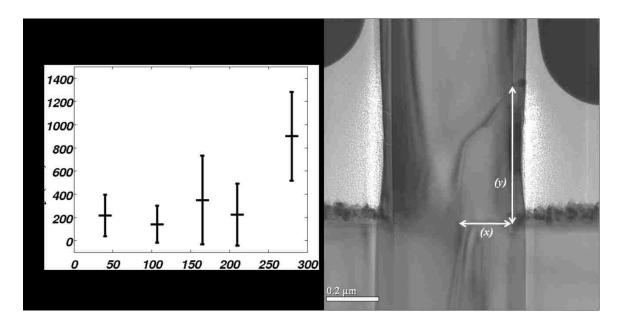

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Fig. 3.7 The correlation of the [0001] length of the TD with the lateral distance from the nanostructure sidewall surface is shown. The TD [0001] length and the lateral distance from the sidewall facet is defined in (b)                                                                                                                                                  | 73  |

| Fig. 3.8 A simple model illustrating the TD elimination by climb. The model is shown here for a simple cubic crystal, for understanding, but is proposed to be valid even for hexagonal dielemental semiconductor like GaN                                                                                                                                                   | .74 |

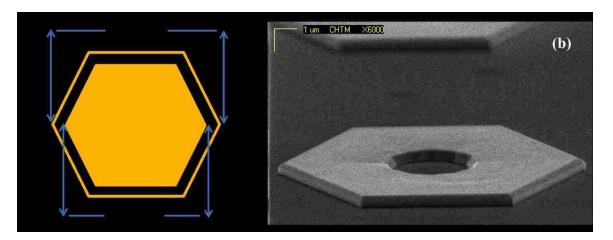

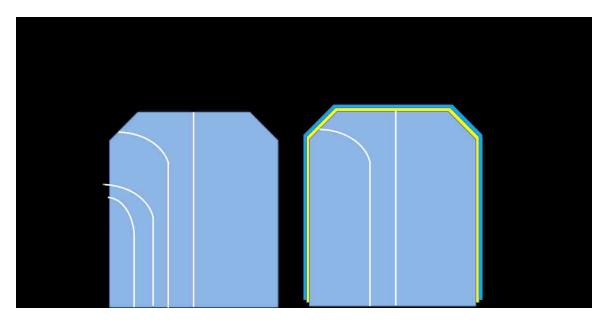

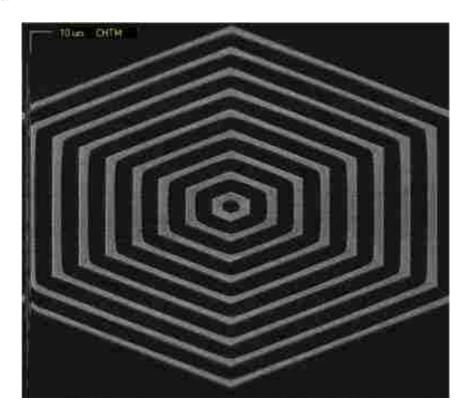

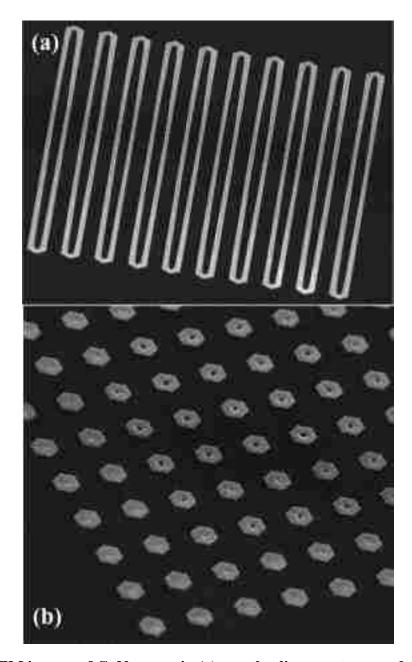

| Fig. 3.9 (a) shows an illustration of annulus hexagonal growth patterns and (b) shows a SEM image of GaN grown selectively in hexagonal annulus patterns illustrated in (a). These structures would also promote TD elimination by mechanisms discussed in this section                                                                                                      | .75 |

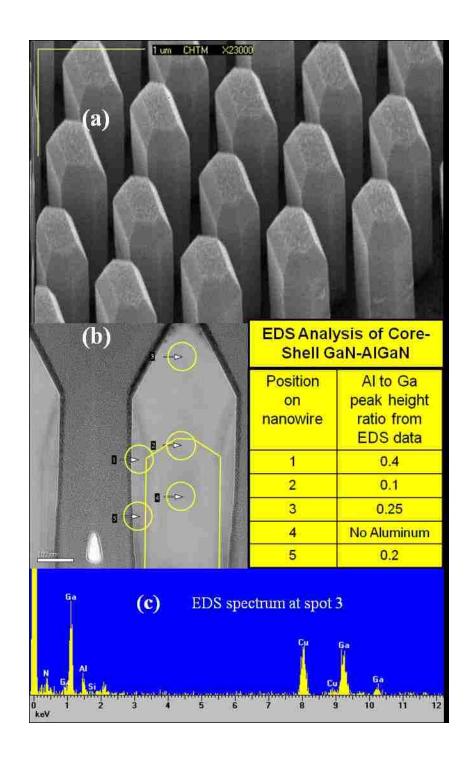

| Fig. 3.10 (a) a 45° tilt SEM image of GaN-AlGaN core-shell nanowire is shown, whose XTEM image has been shown in (b) with the EDS measurements at different locations on the nanowire. The EDS spectra ((c) shows an example of an EDS spectrum at location 3 in (b)) show the presence of Al in all locations except 4, indication of a GaN core surrounded by AlGaN shell. | .77 |

| Fig. 3.11 (a) a 45° tilt SEM image of GaN-InGaN core-shell nanowire showing indium segregation in the form of petals. (b) XTEM of GaN-InGaN coreshell nanowire showing a crater in the InGaN layer                                                                                                                                                                           | .79 |

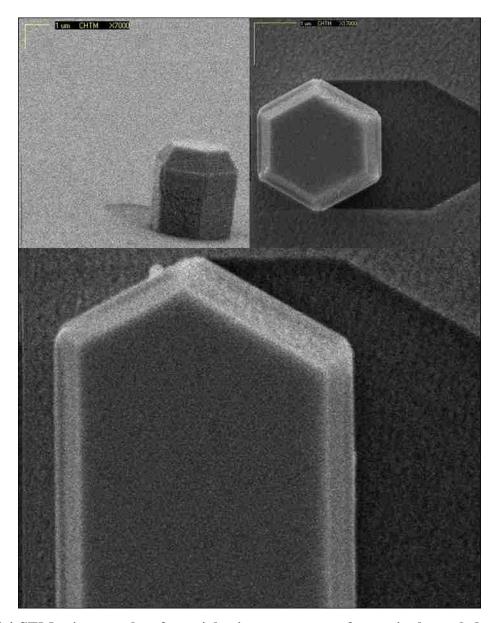

| Fig. 3.12 The cross-section SEM of a 3D GaN microstructure grown by pulsed MOVPE. The cross-section was prepared using FIB                                                                                                                                                                                                                                                   | .81 |

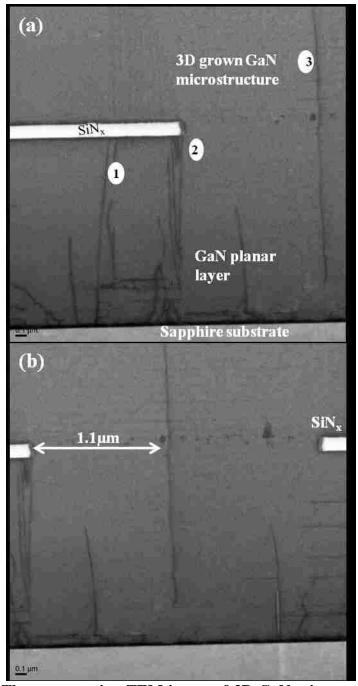

| Fig. 3.13 (a) The cross-section TEM image of 3D GaN microstructure showing the three TDs labeled 1, 2 and 3. The bottom image represents the low magnification version of the top image, illustrating the lateral distance of the TD from the sidewall.                                                                                                                      | .82 |

| Fig. 3.14 A pictographic illustration of the TDs in a 3D GaN microstructure showing the bending of TDs in close proximity to sidewall and also the TDs further interior of the structure just propagate without bending. This could be beneficial for TD free m-plane active regions, as shown in (b)                                                                        | 83  |

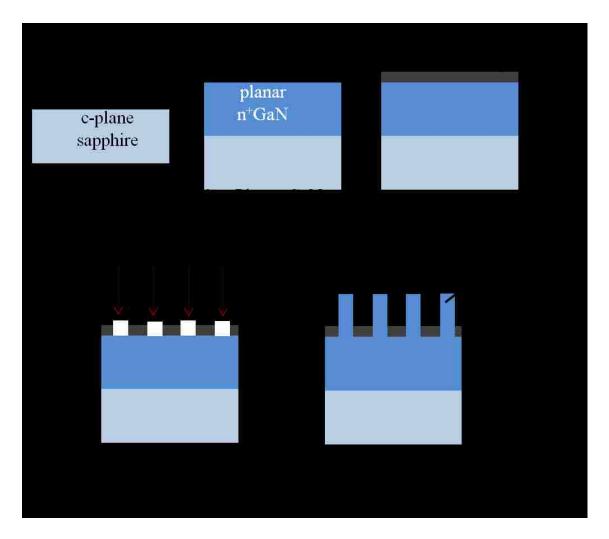

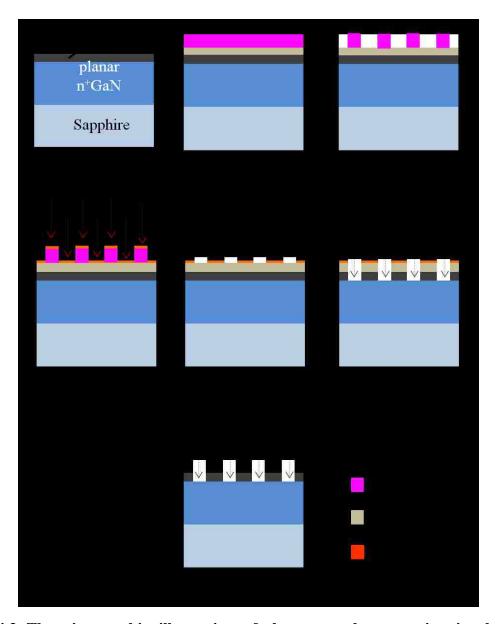

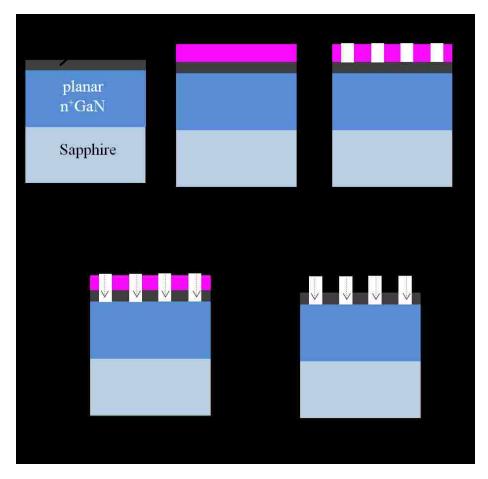

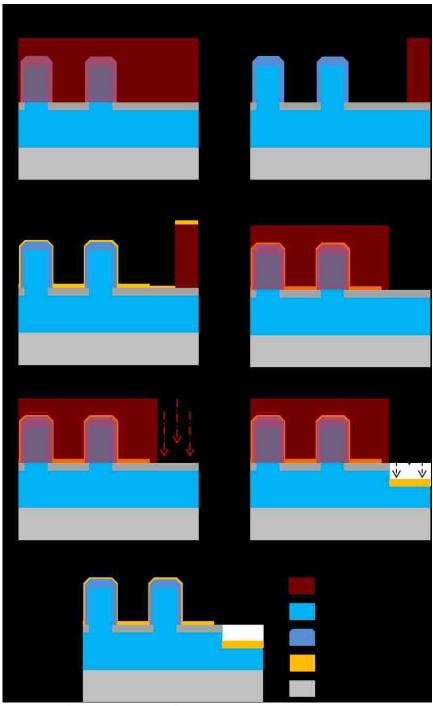

| Fig. 4.1 An overview of the various steps involved in the growth of GaN 3D structures using SAG technique without the use of a catalyst                                                                                                                                                                                                                                      | .90 |

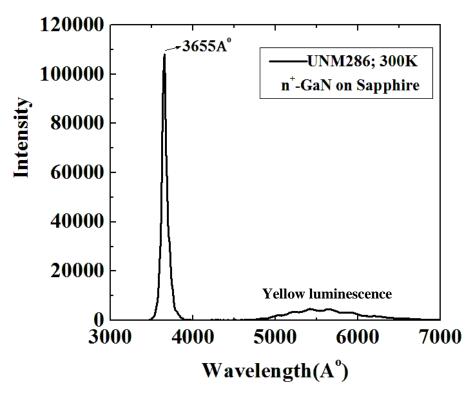

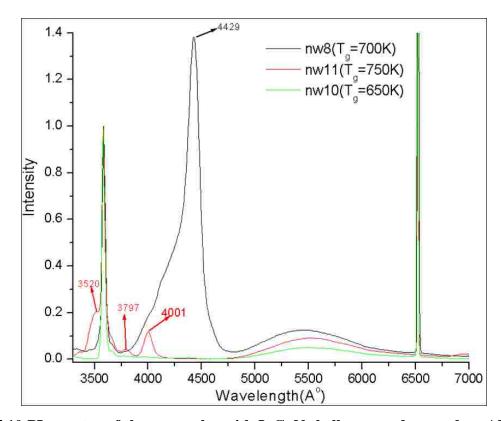

| Fig. 4.2 Photoluminescence (PL) spectrum of 2.25µm thick n+GaN (Sample#UNM286) grown on c-plane sapphire is shown. The sharp PL peak is indicative of a good crystalline material. The yellow luminescence indicated is discussed in section 5.2 of chapter 5                                                                                                                | .92 |

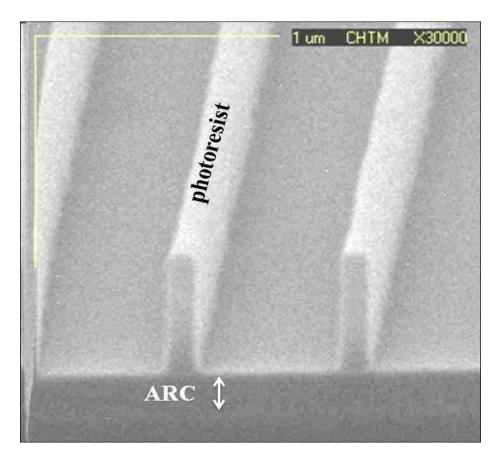

| Fig. 4.3 The pictographic illustration of the nanoscale processing involved in patterning of dielectric $(SiN_x)$ to define regions to grow GaN nanowires shown                                                                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 4.4 The SEM micrograph of photoresist patterned by a single exposure interferometric lithography is shown                                                                                                                  |

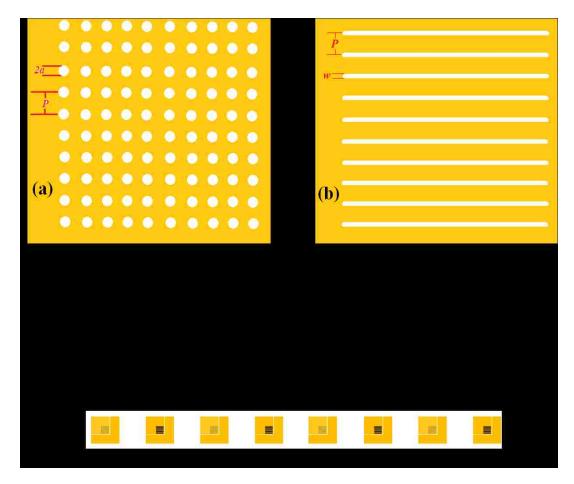

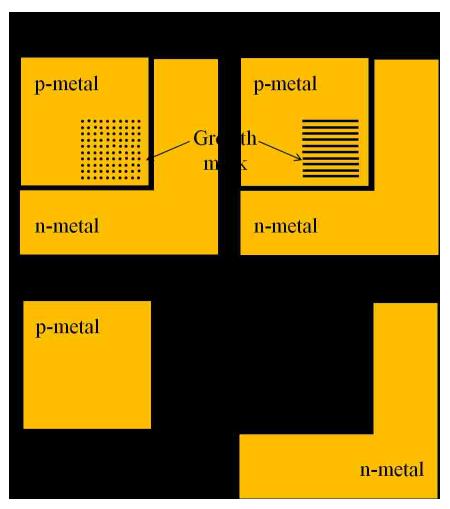

| Fig. 4.5 COLED growth mask is pictographically illustrated with the circular and line aperture patterns. The vertical row of different sized LEDs is shown in (c)96                                                             |

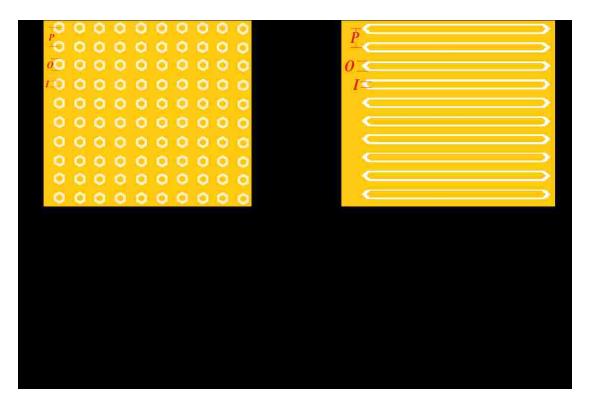

| Fig. 4.6 The hexagonal and line annulus patterns in the COLED growth mask is pictographically illustrated                                                                                                                       |

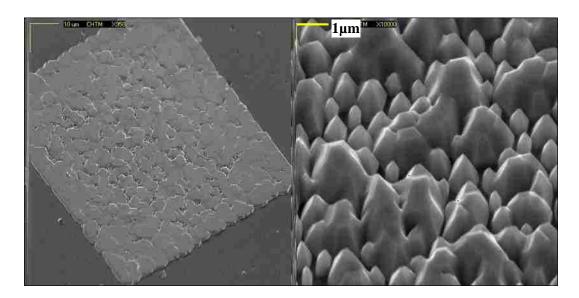

| Fig. 4.7 The pictographic illustration of the regular photolithography patterning of the growth dielectric $(SiN_x)$ using COLED growth mask98                                                                                  |

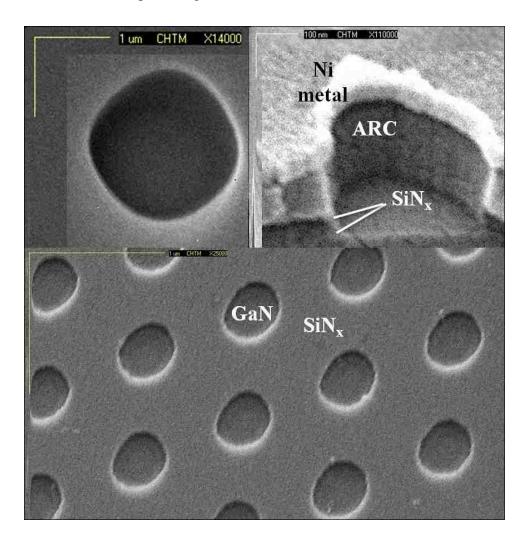

| Fig. 4.8 The SEM images of growth dielectric (SiN <sub>x</sub> ) etched using the RIE101                                                                                                                                        |

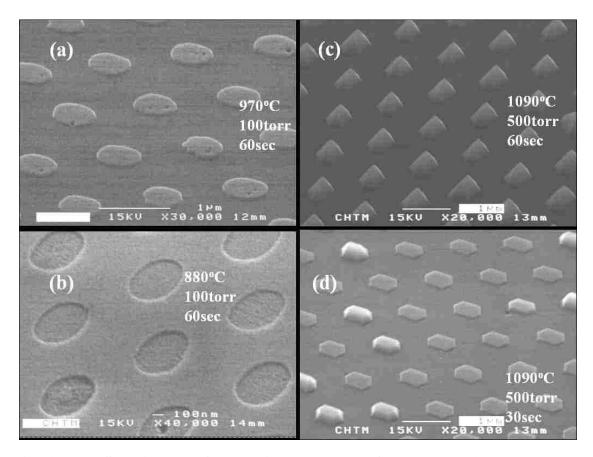

| Fig. 4.9 The SEM images of nucleation growths performed at varied temperature, pressure and time are shown. (a) seems to be the most optimal condition to start the nanowire growth                                             |

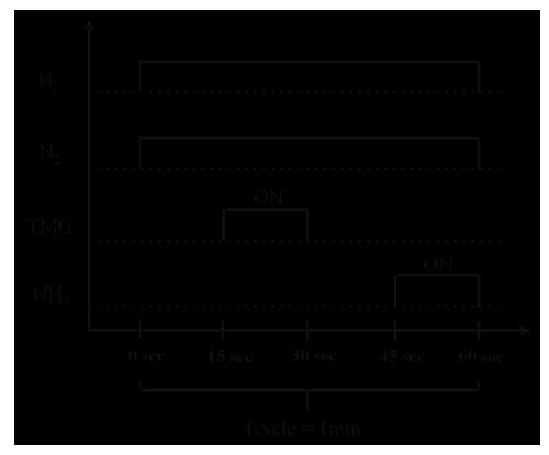

| Fig. 4.10 A pictographic illustration of a cycle of the pulsed MOVPE growth of GaN                                                                                                                                              |

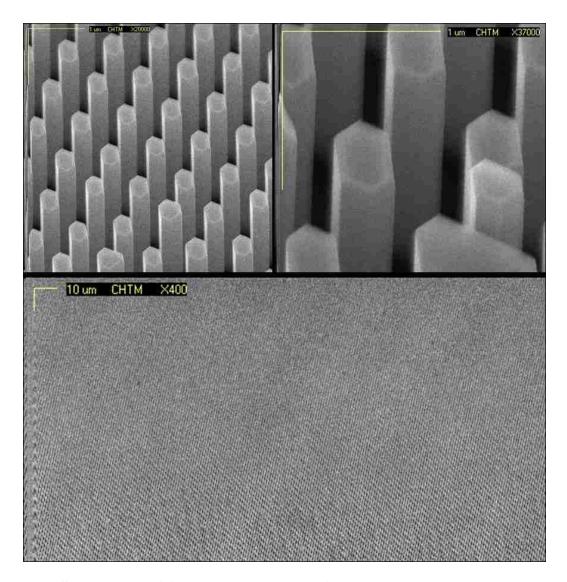

| Fig. 4.11 SEM images of GaN nanowires grown for 150 cycles is shown105                                                                                                                                                          |

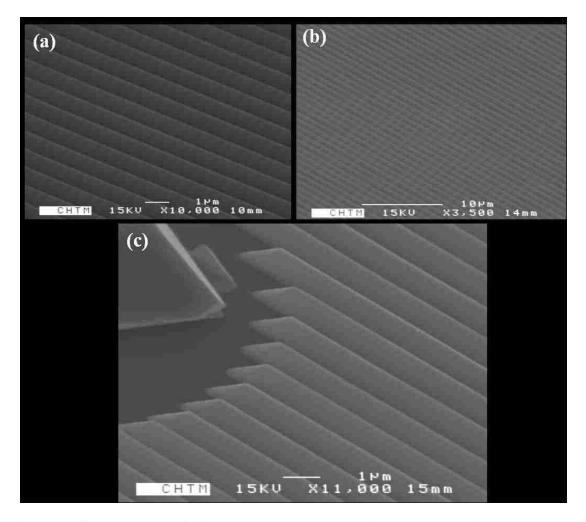

| Fig. 4.12 SEM images of GaN nanowalls grown using pulsed MOVPE growth is shown. The line apertures are aligned parallel to the $\{11\bar{2}0\}$ plane of sapphire to produce smooth $\{1\bar{1}00\}$ GaN planes                 |

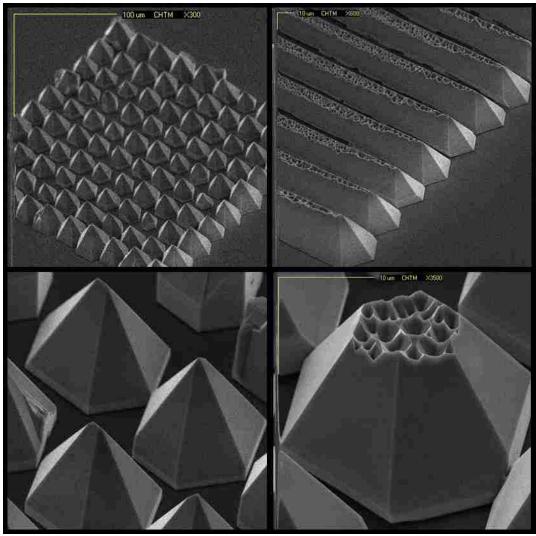

| Fig. 4.13 SEM images of GaN microstructures grown by pulsed MOVPE107                                                                                                                                                            |

| Fig. 4.14 (a) shows plot of the variation of the height h of the microstructures and (b) shows the plot of the lateral growth parameter ( $\%\Delta$ ) vs. the aperture diameter (2a)                                           |

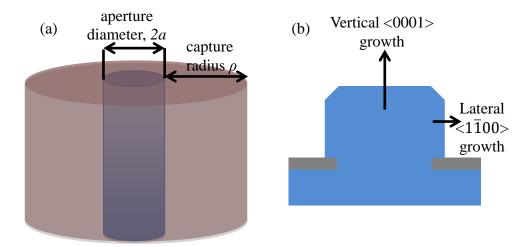

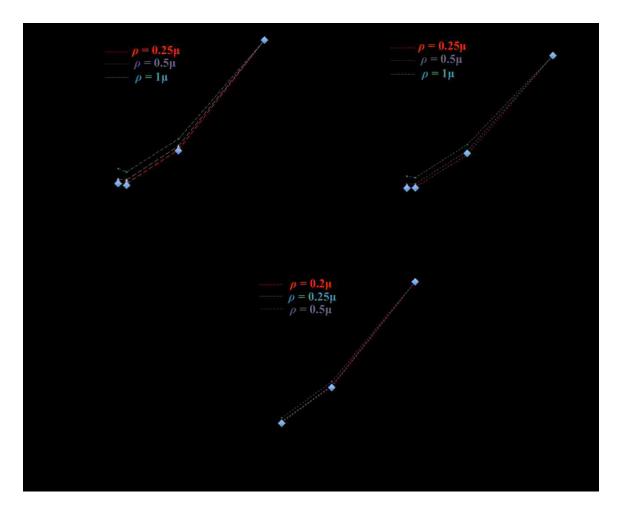

| Fig. 4.15 (a) shows the capture radius, $\rho$ as defined in this section; growth nutrients falling in the cylindrical area would contribute to the vertical <0001> growth and lateral <1 $\overline{1}$ 00> growth             |

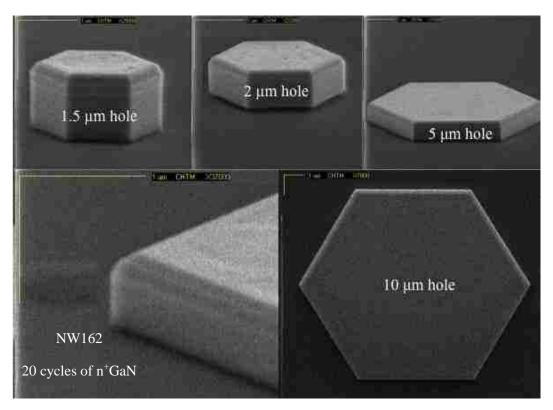

| Fig. 4.16 SEM images of different size microstructure in NW162111                                                                                                                                                               |

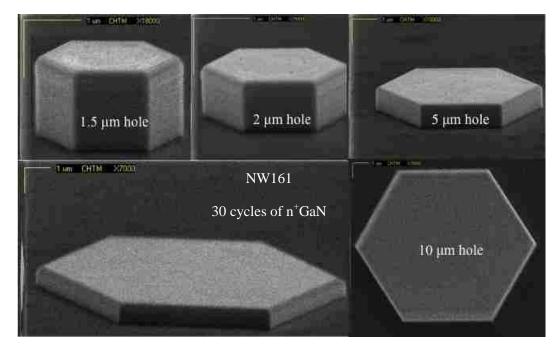

| Fig. 4.17 SEM images of different size microstructure in NW161111                                                                                                                                                               |

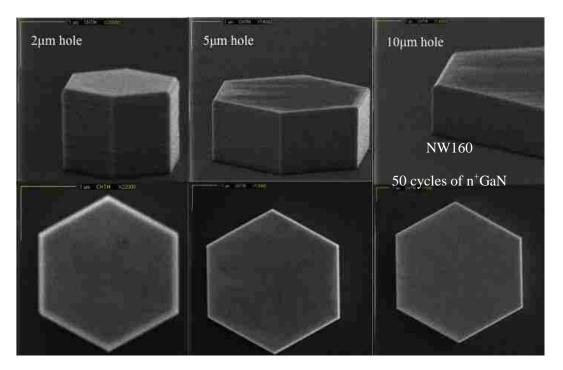

| Fig. 4.18 SEM images of different size microstructure in NW160                                                                                                                                                                  |

| Fig. 4.19 The growth volume ( <i>V</i> ) of each of the structure is plotted as a function of the original aperture diameter ( <i>2a</i> ) for different values of capture radii and the actual volume data is represented by • |

| Fig. 4.20 SEM image of a multi-hexagonal annulus pattern is shown. These structures could potentially be threading defect free, but also present us with a large active area, thus leading to a high power threading defect free LED                | 4 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

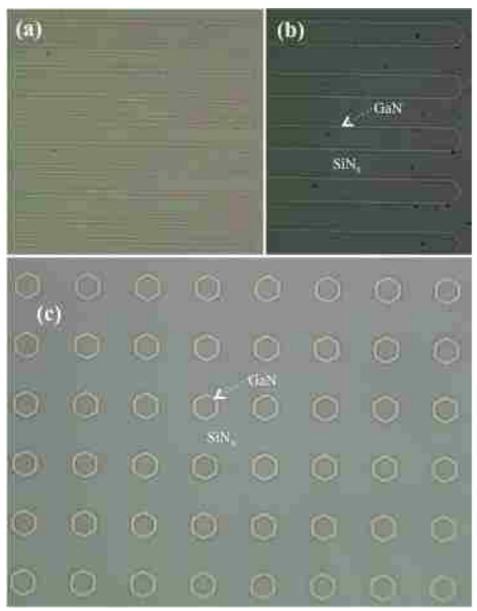

| Fig. 4.21 Optical microscope images of annulus patterns etched in growth dielectric (SiN <sub>x</sub> )                                                                                                                                             | 5 |

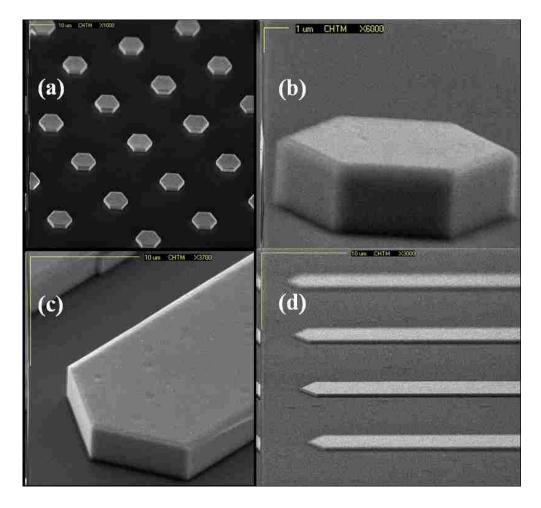

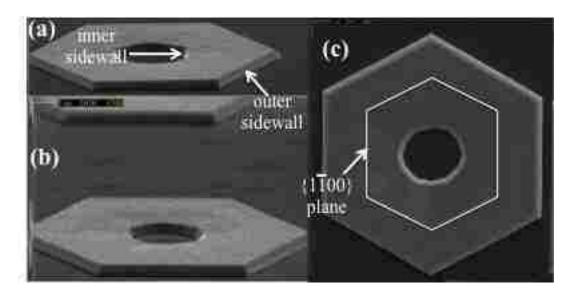

| Fig. 4.22 SEM images of GaN grown in hexagonal annulus apertures are shown. (c) shows the origin of new crystallographic planes in the inner concave side of the annulus structures                                                                 | 7 |

| Fig. 4.23 SEM images of GaN grown in (a) annulus line apertures and (b) hexagonal annulus apertures is shown, indication of the difference in growth rate in the structures on the edge of a given group and those near the center                  | 8 |

| Fig. 4.24 The pictographic illustration of the nanoscale processing involved in patterning of dielectric $(SiN_x)$ patterns to define regions to grow GaN nanowires in the selective area nanowire growth (SANG) is shown12                         | 0 |

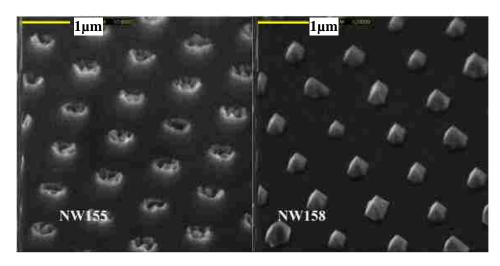

| Fig. 4.25 The GaN nanowires grown in the SANG patterns with a V-III ratio of 550, which was used in the other nanowire and microstructure growths described in the earlier sections                                                                 | 1 |

| Fig. 4.26 SEM images of NW155 (V-III ratio = 2460) and NW158 (V-III ratio = 1080) are shown. These images are illustrating the fact that a lower V-III was needed to achieve GaN nanowires                                                          | 2 |

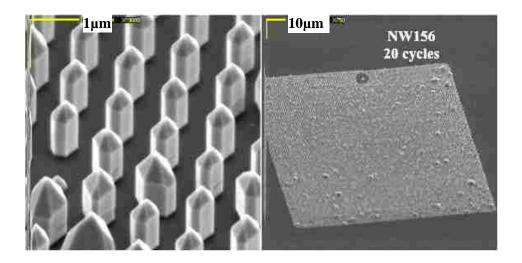

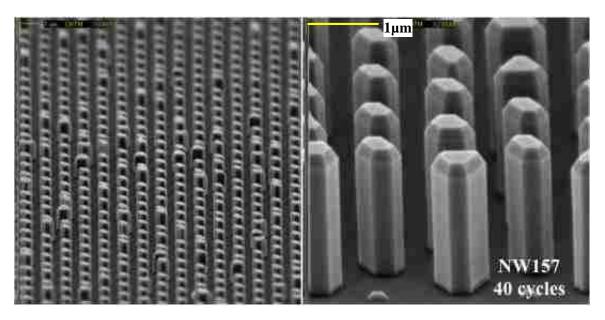

| Fig. 4.27 SEM images of NW156 (V-III ratio = 878) are shown. The GaN nanowire growth has been achieved, but the nanowires have pyramidal tops, indicating a necessity of a higher V-III ratio to get flat top nanowires by reducing the growth rate | 2 |

| Fig. 4.28 SEM images of NW157 (V-III ratio=965) are shown. The GaN nanowires have flatter tops, in comparison to NW156. A slight increase in V-III could improve the flatness of the top facet of the nanowires                                     | 3 |

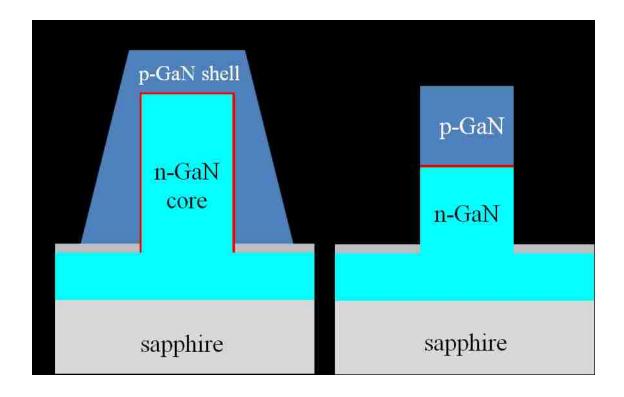

| Fig. 5.1 (a) The structure of a coaxial p-n homo junction GaN based LED compared with (b) the structure of a non-coaxial p-n homo junction GaN based LED analyzed and reported in [chapter 5, reference 6]                                          | 3 |

| Fig. 5.2 SEM micrographs of p-n homo junction coaxial GaN based LEDs13                                                                                                                                                                              | 0 |

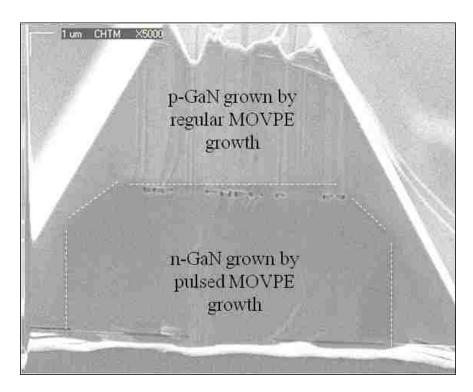

| Fig. 5.3 The cross-section SEM image of a p-n homo junction GaN based LED13                                                                                                                                                                         | 1 |

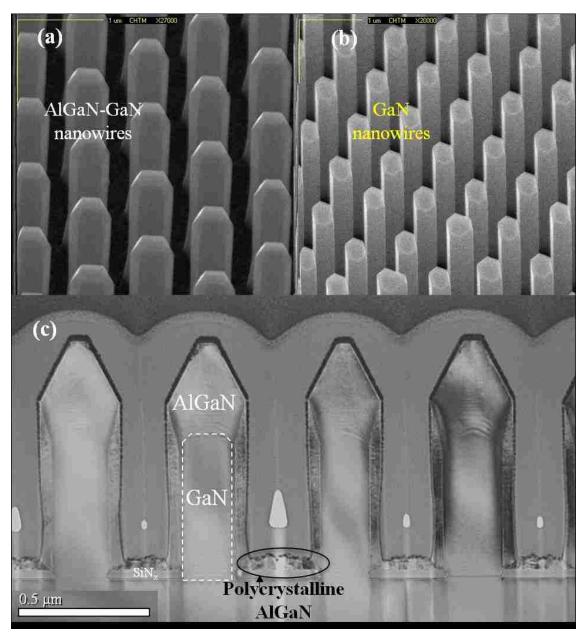

| Fig. 5.4 (a) SEM micrographs of AlGaN-GaN coaxial structures in comparison with (b) core GaN nanowires, (c) shows the cross-section TEM image of an array of AlGaN-GaN coaxial nanowires                                                                                                                                                                                            | 134  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

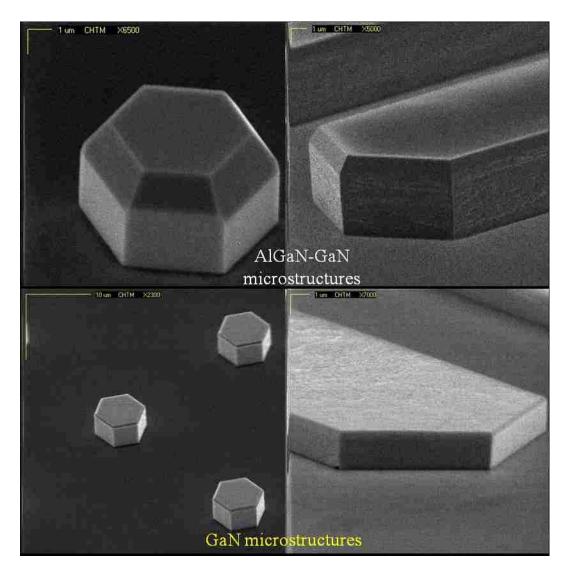

| Fig. 5.5 The SEM micrographs of AlGaN-GaN coaxial microstructures and their comparison with core GaN microstructures. The GaN microstructures have flat tops, while the AlGaN-GaN coaxial structures have pyramidal tops.                                                                                                                                                           | 135  |

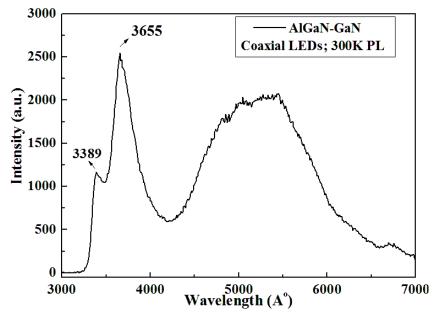

| Fig. 5.6 PL spectrum of NW#73B (an AlGaN - GaN coaxial LED sample) at 300K                                                                                                                                                                                                                                                                                                          | 136  |

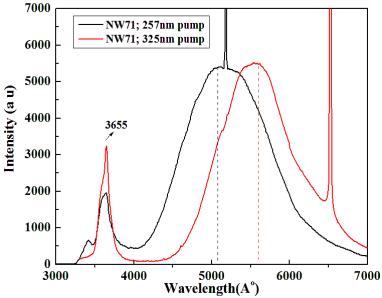

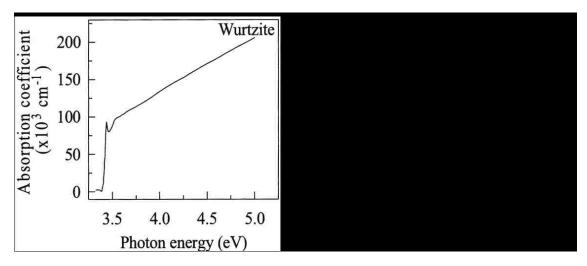

| Fig. 5.7 PL spectra of nw71 (AlGaN-GaN coaxial LEDs) using two lasers (Ar:ion-257nm and He-Cd-325nm wavelength)                                                                                                                                                                                                                                                                     | 136  |

| Fig. 5.8 (a) shows the absorption coefficient of wurtzite GaN as a function of incident photon energy in eV, image reproduced from [chapter 5, reference 9] and (b) shows a simple illustration of the energy band diagram of GaN with transition between the energy level of the donor and the defect (group III vacancies) energy level corresponding to the yellow luminescence. | 137  |

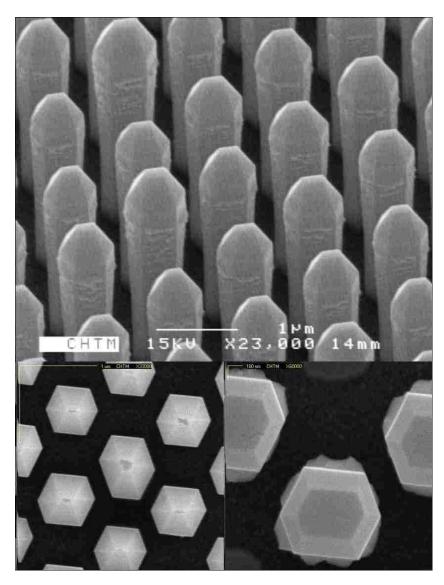

| Fig. 5.9 SEM images of InGaN-AlGaN-GaN coaxial structures grown by MOVPE1                                                                                                                                                                                                                                                                                                           | 140  |

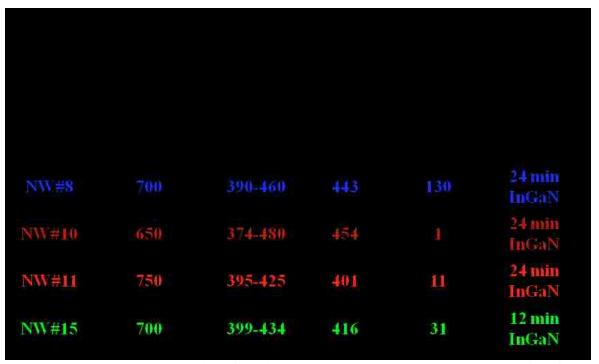

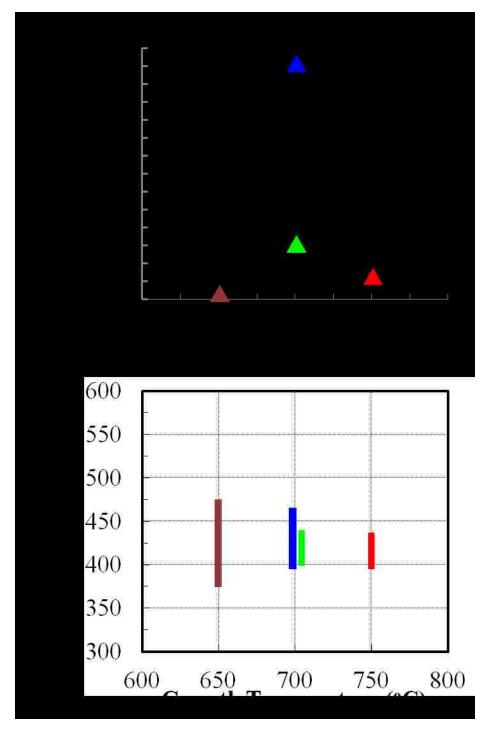

| Fig. 5.10 PL spectra of three samples with InGaN shell wrapped around an AlGaN-GaN coaxial structure grown at three different temperatures are shown.                                                                                                                                                                                                                               | 142  |

| Fig. 5.11 The plot of the intensity of 77K InGaN PL was shown in (a), (with reference to the intensity of the GaN PL) and the line width of the InGaN PL was shown in (b), for samples, whose InGaN layer was grown at different temperatures.                                                                                                                                      | 143  |

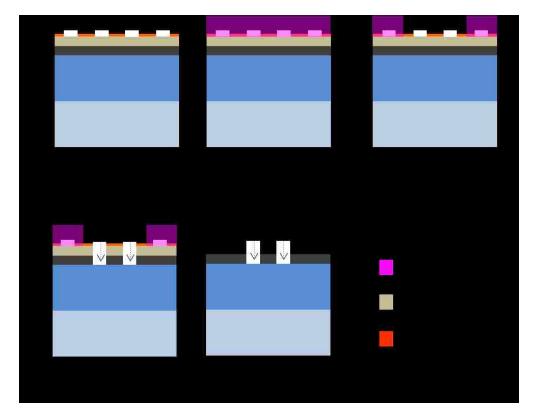

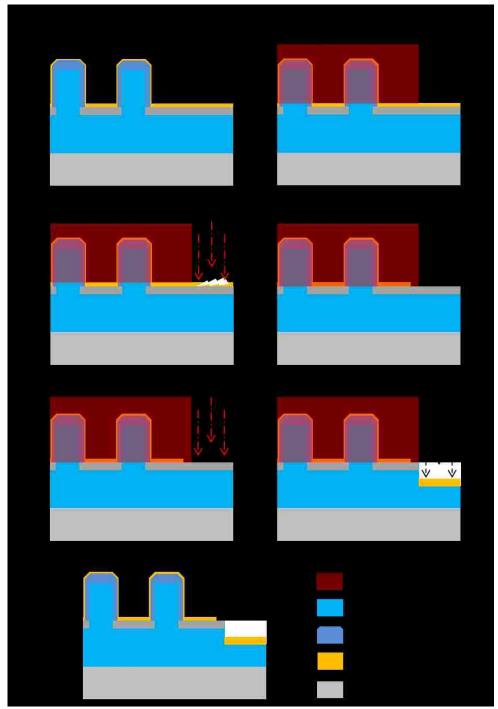

| Fig. 6.1 The schematic illustration of the steps involve in process 1.1 (p-metal liftoff based coaxial LED process)                                                                                                                                                                                                                                                                 | 147  |

| Fig. 6.2 The pictographic illustration of the three COLED masks aligned to each other is shown in (a); (b) shows mask2 (p-metal mask) and (c) shows mask3 (n-metal mask). Each of these masks is a dark field mask open in the golden sections shown                                                                                                                                | 149  |

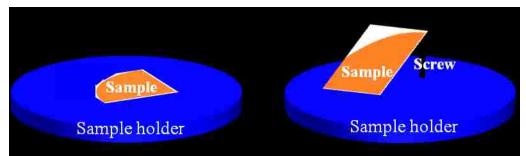

| Fig. 6.3 (a) shows the conventional wafer loading mechanism into the metal evaporator and (b) shows the non-conventional angled loading mechanism                                                                                                                                                                                                                                   | 151  |

| Fig. 6.4 SEM micrographs of coaxial microstructures after a single angled p-metal evaporation run. The shadow is reminiscent of the existing coaxial LED structure.                                                                                                                                                                                                                 | .152 |

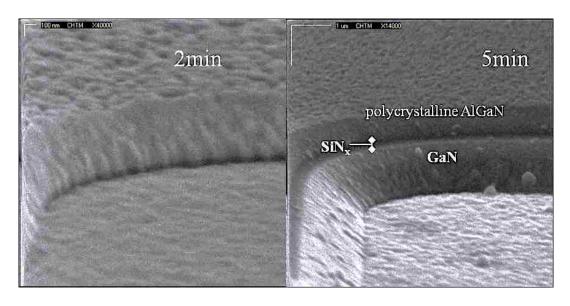

| Fig. 6.5 SEM images of a coaxial LED sample etched using the ICP for 2min and 5min respectively.                                                                                                                                                                                                                                                                                    | 154  |

| Fig. 6.6  | The schematic illustration of the steps involved in coaxial LED process 1.2 (non-liftoff based p-metal process)                                                                                                                                                                                                                                                          |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

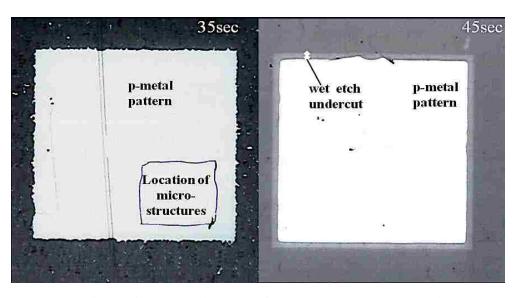

| Fig. 6.7  | The optical microscope images of test structures etched with aqua regia for 35sec and 45sec, respectively                                                                                                                                                                                                                                                                |

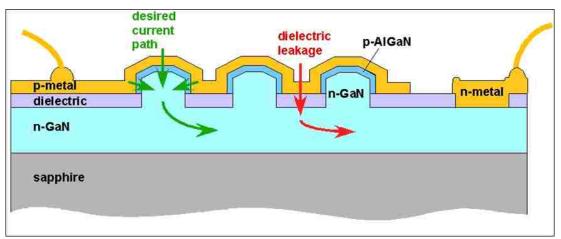

| Fig. 6.8  | The cross-section of the coaxial LED showing the desired current path and a possible leakage path through the growth dielectric layer159                                                                                                                                                                                                                                 |

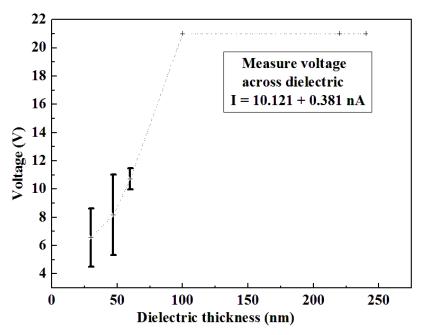

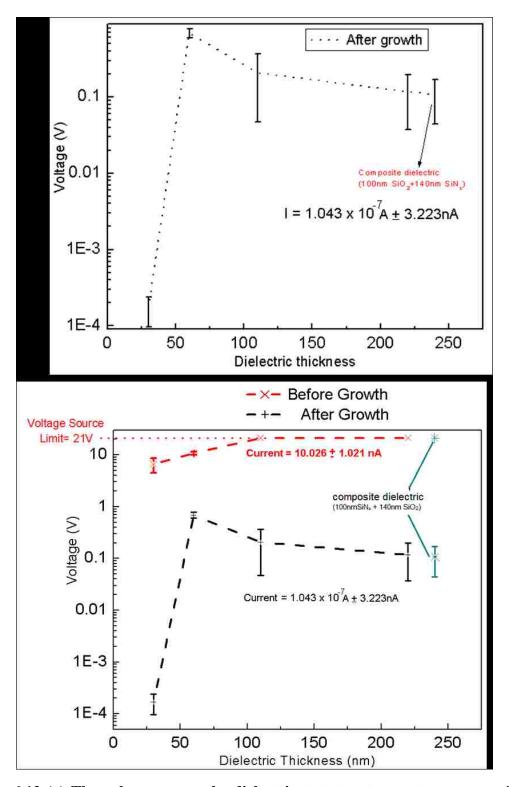

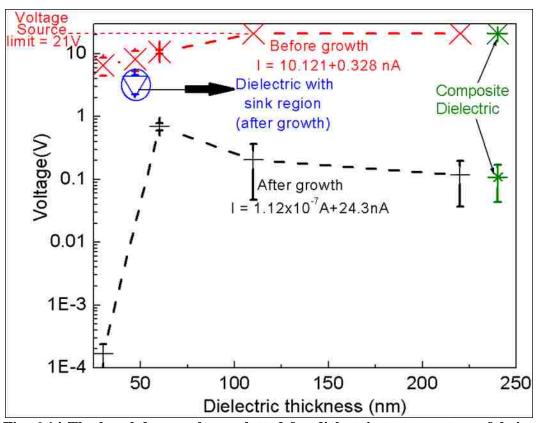

| Fig. 6.9  | The breakdown voltage plotted as a function of dielectric thickness. The breakdown voltage is defined for a current = 10nA. For dielectric thicknesses above 100nm, the voltage source meter limit (21V) was reached                                                                                                                                                     |

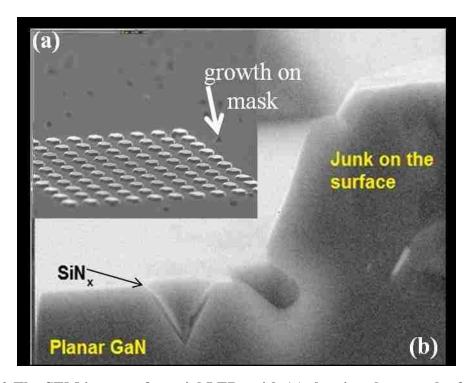

| Fig. 6.10 | The SEM images of coaxial LEDs with (a) showing the growth of stray 3D GaN islands on the dielectric and (b) showing the cross-section of the 3D GaN islands                                                                                                                                                                                                             |

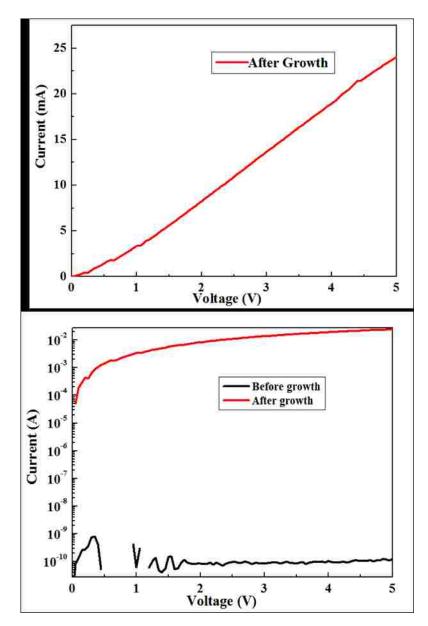

| Fig. 6.11 | The current-voltage characteristics of dielectric test structures (a) fabricated on test samples that were subjected to growth conditions and (b) shows the I-V characteristics comparison of representative samples, one subjected and one not subjected to pulsed MOVPE growth conditions164                                                                           |

| Fig. 6.12 | 2 (a) The voltage across the dielectric test structures at a current of 0.1μA plotted on a log scale and (b) the combination of Fig. 9 and Fig. 12(a) on the same log-linear plot showing the difference in breakdown voltage, as defined in section 6.3                                                                                                                 |

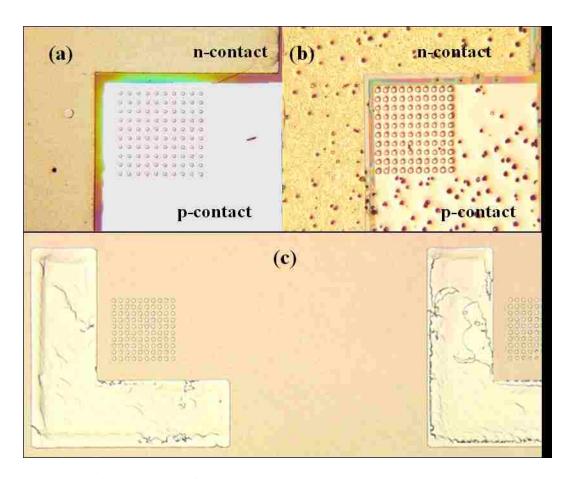

| Fig. 6.13 | (a) Coaxial LED fabricated on growth patterns with sink shown in (c), in comparison to (b) that shows coaxial LED fabricated on growth patterns without sink. The growth mask is clean in (c), devoid of GaN islands, in comparison to the samples grown on patterns without sink                                                                                        |

| Fig. 6.14 | The breakdown voltage plotted for dielectric test structures fabricated on four different samples, 1) SiNx on GaN, 2) SiNx on GaN subjected to pulsed MOVPE growth conditions, 3) composite dielectric (140nm SiNx on 110nm SiO2) subjected to both the cases mentioned in 1) and 2) and 4) SiNx on GaN patterned with growth sink, subjected to MOVPE growth conditions |

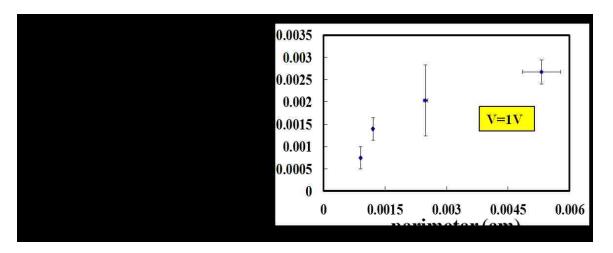

| Fig. 6.15 | The current leakage mechanism observed in coaxial LEDs with insufficient lateral growth to fill the gaps between the circular apertures and the coaxial structures with regular hexagonal cross-section. The black arrow in the LED schematic represents the desired current direction and red arrow indicates the direction of leakage current observed                 |

| fabricated, showing the current leakage through the gaps mentioned in Fig. 6.15 and (b) shows the plot of the current measured at V=1V, as a function of the perimeter of different sized coaxial wire microstructured devices                                                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fig. 6.17 The four possible methods of eliminating the current leakage highlighted in Fig. 15 is described. (1) The use of hexagonal growth apertures instead of circular, (2) use of spin-on glass, (3) additional p-GaN pyramidal outer shell to cover the gaps and (4) LOCOS                              |

| Fig. 6.18 The cross-section SEM image of a coaxial LED sample fabricated with spin-on glass, followed by a 5min etch back to expose the top and a portion of sidewalls of the LED structure                                                                                                                  |

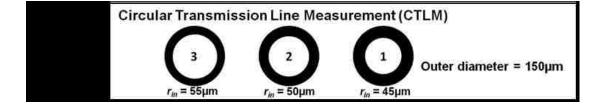

| Fig. 6.19 I vs. V characteristics of different circular transmission line model (CTLM) patterns shown in (a), fabricated on p-GaN using thin p-metal layers, are shown in (b). The transmission coefficient calculated at 327nm, of the thin metal layers fabricated on p-GaN on sapphire is shown in (c)176 |

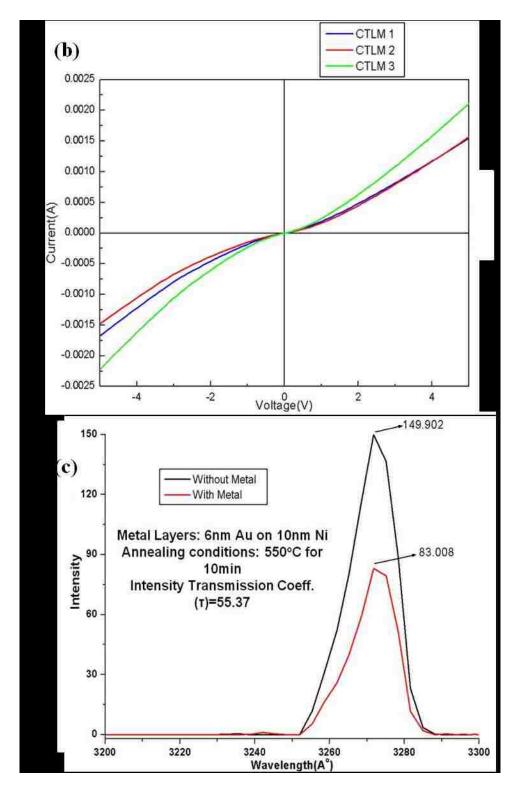

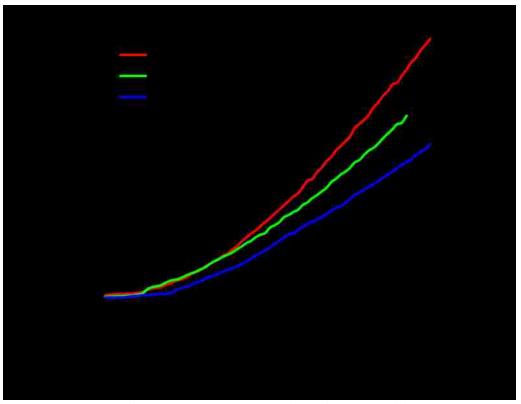

| Fig. 6.20 Current vs. voltage characteristic of representative microstructured coaxial LED devices, wires (a) and walls (b) are shown                                                                                                                                                                        |

| Fig. 6.21 The equivalent circuit of a real diode under consideration in coaxial LEDs178                                                                                                                                                                                                                      |

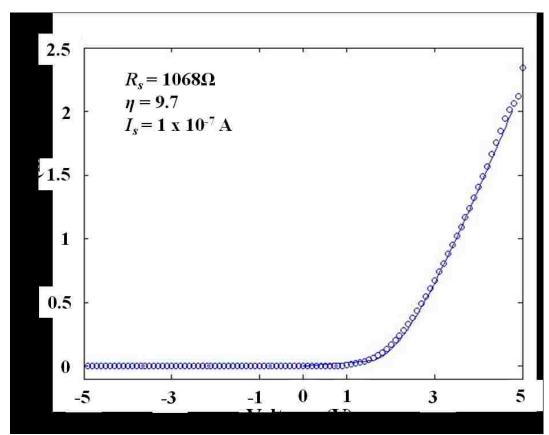

| Fig. 6.22 The plot of current vs. voltage data points (o) together with the best fit <i>I</i> vs. <i>V</i> characteristic simulated (solid line) using MATLAB is shown. The parameters calculated are also shown in the plot                                                                                 |

| Fig. 6.23 The plot of the photocurrent obtained from the silicon detector used, as a function of the device current, for representative coaxial wall LEDs of different sizes                                                                                                                                 |

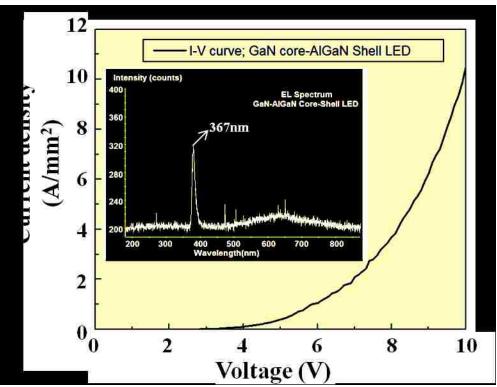

| Fig. 6.24 Current vs. voltage characteristic of a 10µmwall device (device#NW104_06_04) and the electroluminescence spectrum (inset image) obtained from the same device                                                                                                                                      |

| LIST OF TABLES                                                                                                                                                                                                                                                                                               |

| Table 1.1 Comparison of three common substrates used to grow c-plane wurtzite  GaN                                                                                                                                                                                                                           |

| Table 2.1 Comparison of the growth techniques employed to grow GaN nanowires51                                                                                                                                                                                                                               |

| Table 5.1 The 77K PL details of various nanowire samples with a layer of InGaN grown around the nanowires                                                                                                                                                                                                    |

# Chapter 1

# Introduction

Energy saved is energy generated. In addition to improved financial capital and environmental quality, the conservation of energy sources is extremely important for increased personal security and human comfort. Light Emitting Diodes (LEDs) are poised to play a very important role in this effort. As per the Energy Efficiency and Renewable Energy (EERE) program of the Department of Energy (DOE), USA, LED lighting technology is bound to reduce the U.S. light energy expenditure by about one-quarter and contribute significantly to the nation's climate change solutions. In terms of capital, it is estimated to save about \$120 billion in energy costs over the next two decades and avoid 246 million metric tons of carbon emission over the same period [1].

Fig. 1.1 The comparison of the energy savings proposed by DOE upon using of LEDs and the savings that is possible using smart lighting sources, graph reproduced from [2]. 1 Quad is defined as equal to 172million barrels of oil

However, simple LED bulbs replacing the incandescent lamps and compact fluorescent lamps are not the only solution to the world's energy problems. An LED light source with a control system is what the future world would be looking at, to meet the DOE's roadmap. This is one of the visions of the NSF funded Smart Lighting Engineering Research Center (SLERC). A smart lighting system should be designed in such a way that it can be more efficient, healthier and more interactive than the simple electric bulbs of today. Smart Lighting Systems would include the ability to measure and control the intensity, color, polarization, and modulation of light to enable new lighting functionality. The control system would also decide when the light would be on or off. Once successful, this lighting system that is fully controllable would deliver at least two times the energy savings of the conventional first wave LED lighting technology, as shown in Fig. 1.1. This would be roughly equivalent to the elimination of over 300 coal powered plants with the reduction in greenhouse gas emissions and air pollution and decrease in America's dependence on foreign energy sources [2]. Gallium Nitride (GaN) material system has been used in manufacturing of visible blue LEDs and laser diodes for over two decades, ever since technologists have dreamt of a full spectrum solid-state lighting future. In the following sections, LEDs based on the GaN material system, the various factors affecting their performance and the requirements for a highly efficient, high power LED are discussed.

#### 1.1 LEDs based on GaN material system

The binary compound semiconductor GaN is a direct band gap material with a band gap of 3.39eV at 300K. This band gap corresponds to the 364nm wavelength, which falls in the ultraviolet range. The process of alloying GaN with aluminum (Al) would

result in increasing the band gap from 3.39eV until 6.1eV, which is the band gap of aluminum nitride (AlN). Hence, most of the UV LEDs have now been manufactured by alloying a little percentage (x) of aluminum to GaN to form Al<sub>x</sub>Ga<sub>1-x</sub>N [24, 25, 26]. This alloyed material when used in the LED active region would generate UV light of wavelengths below 364nm. However, upon alloying GaN with indium (In), the band gap can be reduced; thereby the emission wavelength of the LEDs can be increased, so as to emit in the visible region. The alloying of GaN with indium would result in decreasing the band gap from 3.39eV till about 0.7eV, which corresponds to the band gap of InN. Blue LEDs have now been highly developed and considerably efficient with indium percentage (x) in In<sub>x</sub>Ga<sub>1-x</sub>N of about 15-20%. However, there aren't any LED chips that provide highly efficient LED operation from the green (>500nm emission wavelength) through to the red with semiconductor alloys made from the AlGaInN materials system. This is typically referred to as the "Green Gap" problem. In addition to this, another issue plaguing today's GaN based LEDs is "efficiency droop". The drop in the external quantum efficiency of the LEDs when they are operated at high power is called efficiency droop. To understand these problems, it is first worth looking into some of the important aspects of substrates, growth and processing of GaN based LEDs discussed in the following sub-sections.

# 1.1.1 Crystallographic orientations in wurtzite GaN

There are three common crystalline structures shared by GaN and its family; wurtzite, zincblende and rocksalt structures. The wurtzite structure is the most thermodynamically stable structure for group-III nitrides and wurtzite GaN and its ternary alloys are the most commonly used material for making visible and deep UV

LEDs and laser diodes. The wurtzite GaN structure is a combination of two hexagonally close packed (HCP) sub-lattices, each with either Ga (Al or In) or N [20]. Some of the different crystallographic orientations in the wurtzite crystal structure have been shown in Fig. 1.2(a). Because of the asymmetry, the wurtzite crystals have two lattice constants, 'a' in the c-plane and 'c' perpendicular to the c-plane of the wurtzite crystal shown in Fig 2.

Fig. 1.2 (a)Some of the important crystallographic orientations in wurtzite GaN and energy band diagram of InGaN QW sandwiched by GaN barrier layers, showing QCSE (b) in c-plane structures and absence of QCSE (c) in m-plane structures

In GaN, the covalent bond between a 'Ga' atom and an 'N' atom is in reality, partially ionic [4, 5]. This leads to a significant spontaneous polarization electric field in the c-oriented GaN crystals. The strong electro negativity of 'N' leads to the localization of the electron cloud near the 'N' atom, hence creating a partial negative charge on the atom. This leads to a partial positive charge on the Ga atom and thus a dipole is created, which leads to a spontaneous polarization electric field in the material by itself. In case of heterostructures (for e.g. GaN/In<sub>x</sub>Ga<sub>1-x</sub>N/GaN as shown in Fig. 1.2) grown in the cdirection, the wurtzite semiconductor nitrides lack inversion symmetry and hence exhibit these piezoelectric fields when strained along the <0001>. The strain is the resultant of the lattice mismatch between GaN and In<sub>x</sub>Ga<sub>1-x</sub>N. The lattice mismatch, together with the spontaneous polarization, is manifested as polarization charges at the heterojunction interfaces. The resultant electric field due to these polarization charges at the interface causes band bending even during flat band conditions and forces the carriers to opposite ends of the quantum well as shown in Fig. 1.2(b). The disruption of flat band condition in the quantum well leads to a lesser electron-hole spatial overlap and a lower band gap as compared to the quantum well. This phenomenon is known as the quantum confined stark effect (QCSE). The lesser electron-hole spatial overlap leads to lower electron-hole recombination (lower internal quantum efficiency) than that is anticipated under forward bias diode turn on conditions. As the forward bias voltage is increased, the bent bands shown in Fig. 1.2(b) start to flatten out, thereby increasing the effective band gap of the quantum well, leading to a blue-shift in the electroluminescence emission. This polarization electric field is increased as the percentage of indium in In<sub>x</sub>Ga<sub>1-x</sub>N is increased, thereby leading to a poor green emission, in comparison to blue LEDs. This is

one of the reasons for the "Green Gap" problem. One way to tackle this is to make the quantum well thin (~2.5nm), so as to make sure there is a significant spatial overlap of the carrier distributions. The order of thickness required is far less than the conventional zinc blend quantum well sizes. Thus, there is a clear trade off required between carrier separation in the wells that favors thin wells and good confinement and photogeneration that favors thicker wells.

The  $<1\overline{1}00>$  direction (vector corresponding to the m-plane GaN), however, lacks the piezoelectric field that is always present in the [0001] direction. Thus, the band bending is now eliminated in the flat band condition, which promotes better spatial overlap of the electron and hole distributions, as shown in Fig. 1.2(c). These crystallographic orientations that lack the spontaneous polarization electric field are often described as non-polar orientations. Kim *et al.* [11] fabricated and demonstrated a thick InGaN MQW LED on  $\{1\overline{1}00\}$  m-plane non-polar GaN substrate. It was shown that the LED had external quantum efficiency (EQE) of 45% at pulse driven conditions. The EQE remained within 10 % of the 20mA value, even at higher currents. Kim *et al.* also demonstrated m-plane LEDs that showed absence of polarization electric fields. The peak emission wavelength was plotted versus the drive current. As the drive current increased, there was no blue shift observed, which is the typical signature of the QCSE in c-plane GaN based LEDs, as described earlier.

# 1.1.2 Growth of wurtzite group-III nitrides and origin of threading defects

GaN is not natively available in nature. This is due to the low solubility of nitrogen in gallium and the higher vapor pressure of nitrogen on GaN [20]. As a result of this, the bulk GaN growth must resort to high temperature and high pressure growth

procedures. There is no process known till date of producing bulk GaN substrates by Czochralski and Bridgman-Stockbarger techniques that is available for most other III-V semiconductors. Hence, there is a need to grow GaN and its family of semiconductors heteroepitaxially on other natively available substrates that also have a wurtzite structure.

Table 1.1 Comparison of three common substrates used to grow c-plane wurtzite GaN

|                            | Sapphire        | SiC                           | Silicon       |

|----------------------------|-----------------|-------------------------------|---------------|

| Δa/a <sub>o</sub> (%)      | -13.8           | -3.5                          | 17            |

| Electrical<br>Conductivity | insulating      | n-type SiC is a semiconductor | semiconductor |

| Cost                       | cheap, up to 6" | expensive                     | cheap         |

Most of the GaN commercial LEDs and Laser Diodes (LDs) are grown on c-plane sapphire, which also has a hexagonal lattice like that of GaN. In addition to sapphire, silicon carbide and silicon (111) are some of the substrates on which the growth of c-plane GaN is being carried out, both in industry and research. Table 1.1 compares the different substrates that are used to grow c-plane GaN. The lattice mismatch of c-plane GaN with respect to c-plane sapphire is about 30% at 300K with respect to the 'a' lattice parameter. However, when c-plane GaN is grown on c-plane sapphire, the observed lattice mismatch is about 16% at 300K. This is because the smaller cells of aluminum atoms on the c-plane sapphire are oriented 30° away from the larger sapphire unit cell as shown in Fig. 1.3.

Fig. 1.3 The projection of bulk c-plane sapphire and GaN showing the Ga atoms in GaN and Al atoms in sapphire for the observed epitaxial growth orientation, figure reproduced from [3]. The black circles are Al-atom positions and the dashed lines represent sapphire c-plane unit cell. The squares are Ga-atom positions and the solid lines represent the GaN c-plane unit cell.

GaN thin films were first epitaxially grown by Maruska and Tietjen in 1969 using the reaction of gallium monochloride (GaCl) with ammonia (NH<sub>3</sub>) [27]. Ever since, a lot of methods like hydride vapor phase epitaxy (HVPE), metal organic vapor phase epitaxy (MOVPE, also known as metal organic chemical vapor deposition, MOCVD) and molecular beam epitaxy (MBE), have been used to grow GaN thin films on sapphire. Nakamura *et al.* [10] designed an atmospheric pressure MOCVD reactor for nitride growth, which has formed the basis of a lot of the MOCVD reactors used for group-III nitride growth. The ability to perform repeatable device quality single crystalline epitaxial growth has made MOCVD the widely used technique in industry to grow GaN. Trimethyl gallium (TMG), trimethyl aluminum and trimethyl indium are the respective group-III precursors used for gallium, aluminum and indium respectively, while ammonia

NH<sub>3</sub> is typically used precursor for nitrogen. GaN and AlxGa1-xN ternary alloys are normally grown at temperatures in excess of 900°C to about 1100°C. However, the growth of In<sub>x</sub>Ga<sub>1-x</sub>N ternary alloys is normally carried out at lower temperatures in the range of 650°C-800°C. However, GaN ({0001} c-plane) has also been grown on c-plane sapphire by reactive atom source MBE [38, 39, 40, 41 and 42]. The most important aspect of the MBE growth of GaN is the ability to grow device quality single crystalline material at lower temperatures, in comparison to HVPE or MOVPE. Yoshida et al. [38] were one of the first to grow GaN on sapphire by reactive MBE using a two-step process. Firstly, an aluminum nitride (AlN) wetting layer (buffer layer) was deposited on the cplane sapphire wafer at 1100°C. Following this, the temperature of the substrate was reduced to 700°C and GaN was epitaxially grown. Lei et al. [39] were one of the first to grow epitaxial films of wurtzite GaN on (001) silicon using MBE (electron cyclotron resonance (ECR) assisted plasma). The epitaxial GaN film was grown in two steps in a Varian GenII MBE system with an ECR source attached to one of its effusion cell ports. Firstly, a GaN-buffer was grown at low temperature (175-400°C) following which, the temperature was raised to about 600°C and the rest of the GaN film was grown at the higher temperature. In case of HVPE or MOVPE, ammonia has been used as the chemical source of nitrogen. However, predissociation of nitrogen has been employed as the basic technique of providing the nitrogen flux in MBE reactors. In the above growths mentioned, the cracking of gas source (NH<sub>3</sub> or N<sub>2</sub>) was determined to be the growth ratelimiting step, mainly due to the large binding energy of molecular nitrogen (9.5 eV) that makes it extremely challenging to be used as a gas source for nitride based MBE growth systems.

Heteroepitaxy of GaN on lattice mismatched substrates results in the GaN being strained on the substrate. For thickness beyond the critical thickness of GaN on sapphire, GaN relaxes and the strain energy is released by the formation of threading defects in the order of  $10^8 - 10^{10}$  cm<sup>-2</sup> as shown in Fig. 1.4. In addition to this, the thermal expansion coefficient of sapphire is far higher than that of GaN, thereby leading to cracking of thick films [16].

Fig. 1.4 TEM micrograph of the c-plane sapphire-GaN interface showing the threading defects originating at the interface due to the lattice mismatch between sapphire and GaN

The threading defects propagate along the material until they reach the surface where the defect energy is released. Hence, it is highly likely to find threading defects in the active region of the LED. The high density of threading defects are thought to be the reason for the failure of GaN lasers [10] and the electrical breakdown of GaN p-n junctions [17]. They also play an important role in the increase of the reverse leakage current in LEDs [9]. Although, papers have been published indicating the internal quantum efficiency being immune to the threading defect density [7, 8], Dai *et al.* [28]

have demonstrated that the IQE is significantly dependent on the threading defect density. They performed room temperature photoluminescence measurements on InGaN/GaN multi quantum well (MQW) heterostructures to verify this.

The threading defects entering the In<sub>x</sub>Ga<sub>1-x</sub>N quantum well also result in the generation of V-shaped defects that cause higher index facet growth at a reduced growth rate and thus result in pit formation [6]. This is more pronounced as the percentage of indium (y) in In<sub>v</sub>Ga<sub>1-v</sub>N is increased. Hence, the elimination of threading defects is one more potential solution to the "Green Gap" problem. Nguyen et al. [35] have recently evaluated the IQE of their defect-free nanowire LEDs, wherein they have been successful in demonstrating nearly zero efficiency droop at current densities of 640A/cm<sup>2</sup>. Therefore, threading defect elimination could also present us with a potential solution to reduce, if not eliminate, the efficiency droop. New growth techniques are being devised to try reducing the threading defects. Nanoheteroepitaxy [18] has been proposed for a long time as one of the potential solutions for defect density reduction. This technique exploits selective epitaxial growth methodology using modern lithography methods for the patterning. This type of selective area growth (SAG) followed by lateral epitaxial overgrowth (also known as ELOG) has shown tendencies to be successful in limiting the defects by localizing them to selected regions of the wafer [19]. Two sets of devices, one grown on sapphire and the other grown on epitaxial laterally overgrown GaN substrates, were compared by Nakamura et al. [10]. The devices on the lower defect ELOG substrate had an operation time in the excess of 10,000 hours and 9nA reverse current at -20V, while that on sapphire had only around 300hrs of operable time and 1μA reverse current at -20V, respectively. Ferdous et al. [14] demonstrated an exponential increase in the

reverse leakage current density with increase in the defect density. It was also demonstrated that most of this leakage current was flowing through the device and not its surface. Hence, it can be concluded from the above observations that reducing the threading defect density would result in improving the device performance in a lot of ways.

# 1.1.3 Requirements for a highly efficient, high power droop free LED

In summary, the requirement of an LED based on GaN is that it should be highly efficient and it should be able to emit at high drive currents with constant internal quantum efficiency. In principle, the efficiency of GaN based LEDs can be improved by improving the recombination rate of the electrons and holes in the active region of the LED. This could be achieved by providing a better spatial over lap of the electrons and holes in the quantum wells by eliminating the QCSE. In other words, growing quantum wells on the non-polar GaN crystallographic orientations would lead to a better spatial overlap of electrons and holes in the active region. However, the methods of growing non-polar GaN and their ternary alloys are not very straight forward as growing c-plane GaN on c-plane sapphire.  $\{1\overline{1}00\}$  m-plane GaN has been grown on other substrates like γ-LiAlO<sub>2</sub> (100) [30] by Sun et al. However, these γ-LiAlO<sub>2</sub> substrates are thermally and chemically unstable, which makes their preparation prior to the growth and the actual growth very difficult [29]. γ-LiAlO<sub>2</sub> has been restricted to use only in MBE because of its instability at the MOCVD growth conditions. γ-LiAlO<sub>2</sub> is actually a mixed oxide (mixture of lithium Oxide (Li<sub>2</sub>O) and aluminum oxide(Al<sub>2</sub>O<sub>3</sub>)) that decomposes at temperatures around 1040°C into its constituents. The lithium oxide is volatile and escapes as a gas under the MOCVD growth conditions. Thus, it is difficult to use  $\gamma$ - LiAlO<sub>2</sub> as a viable growth substrate for MOCVD growth of GaN. Moreover,  $\gamma$ -LiAlO<sub>2</sub> is at least three times more expensive as compared to c-plane sapphire. Hang *et al.* [34] have recently demonstrated the growth of m-plane GaN on  $\gamma$ -LiAlO<sub>2</sub> by MOCVD too, but have reported similar instability issues. Thus, there is a need for different strategies to grow m-plane GaN in a cheaper and a much more reliable manner. The efficiency can be further improved by eliminating the threading defects in the active region of the LED. The elimination of threading defects would not only lead to higher internal quantum efficiency, but also would lead to a lower reverse leakage current, a higher reverse breakdown voltage and also a longer device lifetime. In addition to all these, improved carrier confinement in defect free active regions would also enhance the possibility of eliminating the efficiency droop at higher operating current levels, corresponding to high power operation.

The growth of GaN nanowires by MOCVD [21, 31, 32 and 33] without the use of a catalyst is an alternative procedure of producing m-plane GaN to grow the LED active regions on the non-polar m-plane. The methods used by Koester *et al.* [31], and Bergbauer *et al.*[32] to grow InGaN/GaN MQW structures on the m-plane of the GaN nanowires will be discussed in chapter 2 of this thesis. It has also been demonstrated in chapter 3 of this thesis that GaN nanostructures grown by the non-catalytic selective area MOCVD growth are threading defect free.

In summary, a coaxial LED based on GaN is one that we anticipate will incorporate all of the above requirements and some others to present us with the near perfect, state of the art and industrially viable visible LED. This thesis presents the

underlying intricacies involved in the fabrication of this device. The following sections deal with the motivation and background to this thesis.

# 1.2 Coaxial LED expected attributes

Fig. 1.5 the cross-section illustrations of (a) a conventional planar heterostructure, (b) a coaxial heterostructure and (c) a non-coaxial 3D grown heterostructure, GaN based LED, respectively. In all cases, the vertical direction is the c < 0001 > direction.

A coaxial LED consists of a core and a shell, just like in optical fiber geometry. The cross section of a coaxial LED is shown in Fig 1.5(b), in comparison with a conventional planar GaN based LED shown in Fig. 1.5(a) and also the cross section of a non-coaxial 3D grown LED on a similar scale is shown in Fig. 1.5(c). The core material is made up of a slightly higher refractive index material, as compared to the immediate shell to allow for natural guiding of light, thereby improving the external quantum efficiency (EQE). The coaxial LED discussed in this thesis is fabricated on a single crystal GaN nano/micro structure (wire form or a wall form) based on a scalable, non-catalytic, GaN MOCVD growth process. The salient features of the GaN based coaxial LED and comparison with the planar and the non-coaxial nanowire LED will be addressed in the following sub-sections.

# 1.2.1 Absence of QCSE in the GaN based coaxial LED

The side wall of this type of GaN based coaxial LED is the {1100} m-plane. This side wall is extremely important because the active region is on this plane, as opposed to being on the {0001} plane in conventional (c-plane) planar and the non-coaxial nanowire based LEDs. The partial ionic nature of the gallium-nitrogen covalent bond in GaN leads to a significant spontaneous polarization field in the crystal structure along the c [0001] direction. This is true, even in the ternary Al<sub>x</sub>Ga<sub>1-x</sub>N and In<sub>y</sub>Ga<sub>1-y</sub>N ('x' and 'y' being the % of Al and In, respectively) alloys. Due to lattice mismatch between ternary alloys (InGaN) on GaN, an additional strain induced piezoelectric field causes the energy bands in the quantum well to spatially bend, even during flat band conditions. This leads to disruption of the spatial overlap of electrons and holes at a given bias voltage. However, the m-plane in GaN crystallographic structure (Fig. 1.2) lacks the piezoelectric field

present in the [0001] direction. Thus, the band bending is eliminated in the flat band condition, which promotes better spatial overlap of the electron and hole distributions.

# 1.2.2 Absence of threading defects in GaN based coaxial LEDs

The absence of a native substrate for GaN growth has resulted in planar GaN based LEDs having a threading defect (TD) density in the range 10<sup>8</sup> to 10<sup>10</sup> cm<sup>-2</sup>. Nakamura [10] demonstrated that the TDs were centers for leakage currents and played an important role in reducing the reverse breakdown voltage. It was also demonstrated that devices that had a lot of TDs also had a very low operation time. In this respect, the coaxial LED is different from its planar counterparts. It was observed using bright-field cross-sectional transmission electron microscopy (XTEM) analysis that when a TD entered the nanostructure, the defect found a surface in the vicinity and bent towards it [15]. This procedure of defect elimination was found to be more prominent and energetically favored, than the conversion into another defect type. It is proposed that the driving force for this elimination process is the reduction of the dislocation line energy. This line energy is reduced for a TD that bends and terminates at a sidewall compared to a TD that continues to propagate along the nanostructure. This TD elimination mechanism is expected to occur in any GaN nanostructure that has a surface in close proximity to the TD.

#### 1.2.3 High power emission for small coaxial LED foot print area

The coaxial LED is a wrap around LED as shown in Fig. 1.6(a). In comparison to a given foot print of area of a planar LED, or a non-coaxial LED (Fig. 1.6(b)), the coaxial LED has a larger active region area. From a simplified mathematical relationship, it is

possible to relate the optical power output by the LED,  $P_{optical}$  as being proportional to the current (product of current density and area) as follows: -

$$P_{optical} = EQE \times J_{LED} \times Area \times \frac{hc}{e\lambda_{peak}}$$

EQE is the external quantum efficiency,  $J_{LED}$  is the current flowing through the LED per unit area, e is the magnitude of charge of an electron and  $\lambda_{peak}$  is the peak of the electroluminescence spectrum of a given LED. Let us assume that we have a coaxial wall LED array of length 250 $\mu$ m and thickness 0.5 $\mu$ m as shown in Fig. 1.6(d). The effective area of emission from this device, even if it is 1 $\mu$ m tall, is four times that of a planar LED in the same foot print area.

Fig. 1.6 (a) and (b) The comparison of a coaxial LED with respect to 3D grown non-coaxial LED of a similar area foot print. (c) a scanning electron microscope image of a wall structure and (d) illustration of a nanowall structure, in which only one of these dimensions needs to be nanoscale ( $<1\mu m$ ) to get a threading defect free device.

Hence, if we assume that if a given diode current density, the external quantum efficiency of the c-plane LED and the m-plane LED are similar in magnitude, we could then anticipate four times the optical power would be generated in the coaxial LED, in comparison to either a planar LED, or a non-coaxial LED, in the same foot print area. The height of these wall devices can be increased with respect to the amount of optical output power required, by increasing the growth time.

### 1.2.4 Polarized light emission in GaN based coaxial LED

In addition to the absence of the QCSE, the m-plane LEDs have one more important property. A quantum well fabricated on the m-plane of GaN is bound to favor one polarization of emitted light to the other. This can be explained from the valence band structure analysis of m-plane  $In_yGa_{1-y}N$  (y corresponds to % mole fraction of indium in the ternary alloy).

Under unstrained conditions, the crystal-field split-off band (SF) consists of the  $p_z$  orbitals (|Z>). This is located below the heavy-hole (HH) and light-hole (LH) bands, which are degenerate and are both an equal mixture of  $p_x$  - and  $p_y$  orbitals (|X> and |Y>)[12]. When  $In_xGa_{1-x}N$  is fabricated on the c-plane of GaN, InGaN undergoes biaxial compressive strain. This strain is isotropic in both the x and y directions (a and m axes directions). This implies that the crystal symmetry is unchanged and hence the energy band diagrams do not change much, except for the loss of degeneracy of the HH and LH bands, as shown in Fig 1.7(a).