# University of New Mexico UNM Digital Repository

**Electrical and Computer Engineering ETDs**

**Engineering ETDs**

2-8-2011

# A Physical Unclonable Function derived from the power distribution system of an integrated circuit

Ryan Lee Helinski

Follow this and additional works at: https://digitalrepository.unm.edu/ece etds

#### Recommended Citation

$Helinski, Ryan \ Lee. "A \ Physical \ Unclonable \ Function \ derived \ from \ the \ power \ distribution \ system \ of \ an \ integrated \ circuit." \ (2011).$   $https://digitalrepository.unm.edu/ece\_etds/115$

This Dissertation is brought to you for free and open access by the Engineering ETDs at UNM Digital Repository. It has been accepted for inclusion in Electrical and Computer Engineering ETDs by an authorized administrator of UNM Digital Repository. For more information, please contact disc@unm.edu.

| Can | Lyan Lee Helinski                                                                      |

|-----|----------------------------------------------------------------------------------------|

| Е   | Electrical and Computer Engineering                                                    |

| De  | epartment                                                                              |

|     |                                                                                        |

| T   | his dissertation is approved, and it is acceptable in quality nd form for publication: |

| A   | pproved by the Dissertation Committee:                                                 |

|     | And Justic 1/7/200 , Chairperson                                                       |

| 1   | 2 Nov 21                                                                               |

| 1   |                                                                                        |

|     | Dr. Dhruva J. Acharyya DI Acharypa 11/8/2011                                           |

|     | Taym Zarlah-4 11,8,2010                                                                |

|     |                                                                                        |

|     |                                                                                        |

|     |                                                                                        |

| _   |                                                                                        |

|     |                                                                                        |

|     |                                                                                        |

| _   |                                                                                        |

|     |                                                                                        |

|     |                                                                                        |

### A Physical Unclonable Function Derived from the Power Distribution System of an Integrated Circuit

by

#### Ryan L. Helinski

B.S., Computer Engineering, Univ. of Maryland, Baltimore County, 2006 M.S., Computer Engineering, Univ. of Maryland, Baltimore County, 2008

#### DISSERTATION

Submitted in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

Engineering

The University of New Mexico

Albuquerque, New Mexico

December, 2010

©2010, Ryan L. Helinski

# Dedication

This work is dedicated to my parents Albert and Mary who have made this possible through their love and support.

# Acknowledgments

I thank Dr. Jim Plusquellic for inviting me to join this research and for his support and contributions on my master's thesis and further on this dissertation. I would also like to thank Dr. Sani Nassif of IBM Austin Research Laboratory for his support of this research.

To everyone at the Electrical and Computer Engineering Department at the University of New Mexico who made this possible, thank you.

To my colleague Jim Aarestad and my sister Lauren who both helped to edit this document, thank you.

This research would not have been possible without R (http://www.r-project.org/), LabVIEW, Perl (http://www.perl.org/), GNU Octave (http://www.gnu.org/software/octave/), and Subversion (http://subversion.tigris.org/).

This document was typeset in L<sup>A</sup>T<sub>E</sub>X<sup>1</sup> using VIM<sup>2</sup>. The L<sup>A</sup>T<sub>E</sub>X styles are based on the UMBC template by Eric Eaton<sup>3</sup>, and the UNM template by James Howse and Neall Doren<sup>4</sup>.

<sup>1</sup>http://www.latex-project.org/

<sup>&</sup>lt;sup>2</sup>http://www.vim.org/

<sup>&</sup>lt;sup>3</sup>http://www.umbc.edu/gradschool/etd/latex.html

<sup>4</sup>http://www.math.unm.edu/~nedoren/latex/

### A Physical Unclonable Function Derived from the Power Distribution System of an Integrated Circuit

by

#### Ryan L. Helinski

#### ABSTRACT OF DISSERTATION

Submitted in Partial Fulfillment of the Requirements for the Degree of

Doctor of Philosophy

Engineering

The University of New Mexico

Albuquerque, New Mexico

December, 2010

### A Physical Unclonable Function Derived from the Power Distribution System of an Integrated Circuit

by

#### Ryan L. Helinski

B.S., Computer Engineering, Univ. of Maryland, Baltimore County, 2006M.S., Computer Engineering, Univ. of Maryland, Baltimore County, 2008

Ph.D., Engineering, University of New Mexico, 2010

#### Abstract

Hardware support for security mechanisms such as authentication, cryptographic protocols, digital rights management and hardware metering depend heavily on the security of embedded secret keys. The current practice of embedding this key as digital data in the Integrated Circuit (IC) weakens security because the keys can be learned through attacks. Physical Unclonable Functions (PUFs) are a recently-proposed alternative to storing digital keys on the IC. A PUF leverages the inherent manufacturing variations of an IC to define a random function. However, poor performance under PUF quality criteria such as the level of randomness and reproducibility in the responses have detracted from their adoption and widespread use. In this dissertation, I propose several ways to define a novel PUF using the Power Distribution System (PDS) of an IC. First, I describe the hardware primitive and test setup that is required to obtain the PUF responses. Then, I evaluate the analog

PUF responses from silicon against standard PUF quality metrics in order to qualify the strengths and weaknesses of the proposed PUF. I show that the analog PUFs exhibit very high levels of randomness and reproducibility, but are sensitive to changes in temperature. Next, I propose extensions to our PUF that enable an exponential number of Challenge/Response Pairs (CRPs) with respect to the number of hardware resources, as well as yielding a marginal increase in the level of randomness. I also use these same analog measurements from silicon to simulate an integrated implementation of the PUF that takes a digital challenge and returns a digital response. I show that the integrated architecture also exhibits high levels of randomness and reproducibility, and is also resistant to changes in temperature. Future work includes designing and building a new IC that implements a more-powerful hardware primitive that will improve both the number and accuracy of the measurements, as well as additional hardware that will allow the challenge and response generation to be performed on-chip.

| Li       | st of | Figures                        | XIII |

|----------|-------|--------------------------------|------|

| Li       | st of | Tables                         | xix  |

| Li       | st of | Acronyms                       | xxi  |

| 1        | Intr  | $\mathbf{roduction}$           | 1    |

| <b>2</b> | Bac   | kground                        | 6    |

|          | 2.1   | PDS Variation Characterization | 6    |

|          | 2.2   | Physical Unclonable Functions  | 7    |

|          |       | 2.2.1 Applications             | 8    |

|          |       | 2.2.2 Techniques               | 9    |

|          | 2.3   | PUF Metrics                    | 11   |

| 3        | PD    | S Characterization             | 14   |

|          | 3.1   | PDS Architecture               | 15   |

|   | 3.2 | Power Grid Equivalent Circuit Model          | 18         |

|---|-----|----------------------------------------------|------------|

|   | 3.3 | PDS Resistance Measurement Procedure         | 22         |

|   |     | 3.3.1 Branch Current Calculation             | 24         |

|   | 3.4 | PDS Resistance Equations                     | 26         |

|   |     | 3.4.1 Horizontal Resistance Analysis         | 26         |

|   | 3.5 | Noise Analysis                               | 30         |

|   | 3.6 | Analysis of Power Grid Resistance Variations | 33         |

|   |     | 3.6.1 Statistical Analysis                   | 33         |

|   |     | 3.6.2 Alternative RMC Analysis               | 35         |

|   | 3.7 | Conclusion                                   | 37         |

| 4 | Usi | ng PDS Variations as a PUF                   | 38         |

|   | 4.1 | Analog PUF Definition                        | 39         |

|   | 4.2 | Experimental Results                         | 44         |

| 5 | Ext | ension of the PUF and Evaluation of Metrics  | 49         |

|   | 5.1 | Multiple-Shorting Scenarios                  | 50         |

|   | 5.2 | Single-Bit Probability Analysis              | 54         |

|   | 5.3 | Collision Probability Analysis               | 56         |

|   | 5.4 |                                              | <b>5</b> 0 |

|   | 9.4 | Entropy Analysis                             | 59         |

| 6 | Ten | aperature Effects                                                                            | 67  |

|---|-----|----------------------------------------------------------------------------------------------|-----|

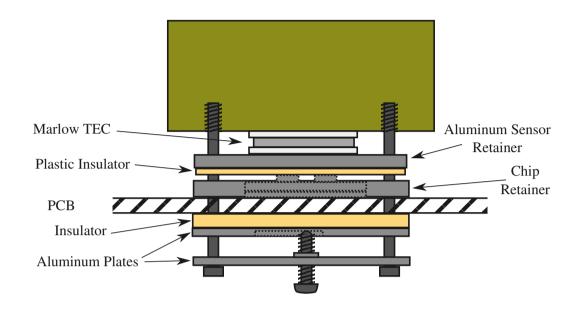

|   | 6.1 | Modifying the Experiment Setup                                                               | 68  |

|   |     | 6.1.1 On-Chip Thermistor                                                                     | 70  |

|   |     | 6.1.2 GE Thermistor Characterization                                                         | 74  |

|   |     | 6.1.3 Controlling On-Chip Temperature                                                        | 77  |

|   | 6.2 | Noise Analysis                                                                               | 83  |

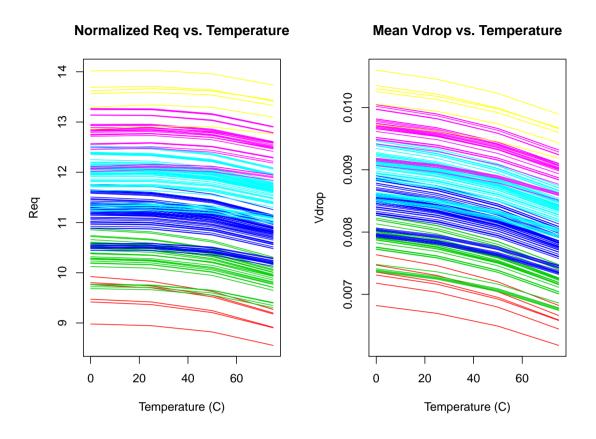

|   | 6.3 | Effects on Analog $R_{\rm eq}$ and $V_{\rm drop}$ PUFs $\ \ldots \ \ldots \ \ldots \ \ldots$ | 93  |

|   |     | 6.3.1 Temperature Effects on Analog PUFs                                                     | 93  |

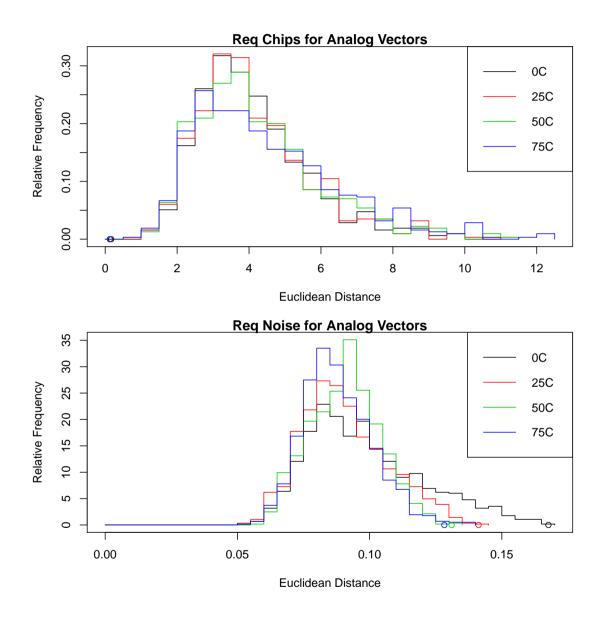

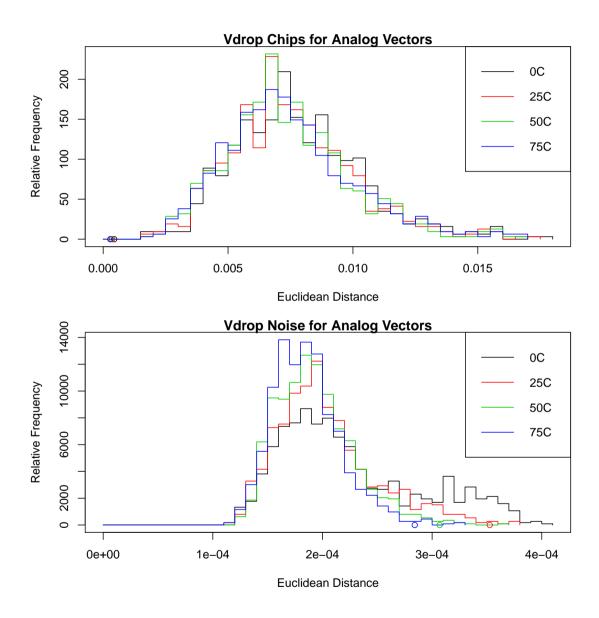

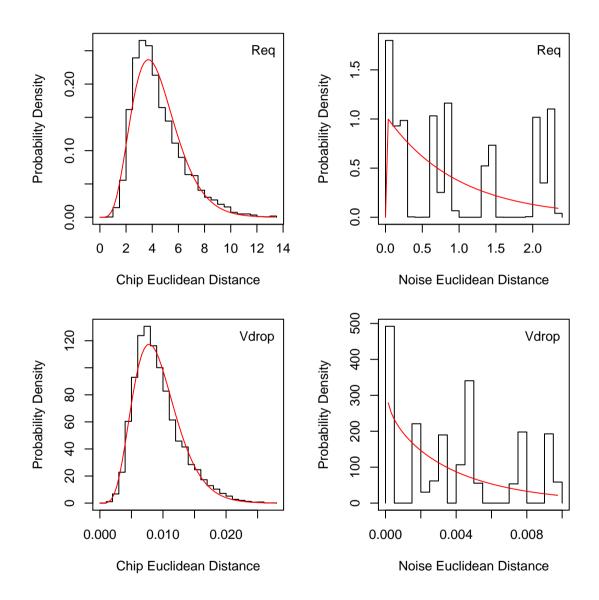

|   |     | 6.3.2 Probability Analysis                                                                   | 94  |

|   |     | 6.3.3 Vector Angles                                                                          | 102 |

|   | 6.4 | Effects on Digital $R_{eq}$ and $V_{drop}$ PUFs                                              | 107 |

|   |     | 6.4.1 Function of Temperature                                                                | 107 |

|   |     | 6.4.2 Aliasing Probability                                                                   | 111 |

|   |     | 6.4.3 Hamming Distances                                                                      | 113 |

|   |     | 6.4.4 Bit Probabilities                                                                      | 117 |

|   | 6.5 | Observe Net Leakage Current                                                                  | 118 |

| 7 | Fut | ure Work                                                                                     | 123 |

|   |     |                                                                                              |     |

|   | 7.1 | Extensions to Hardware Primitive                                                             |     |

|   | 7.2 | Integrated Architecture                                                                      | 125 |

|   | 7.3 | Integrated Architecture with an ADC                                                          | 126 |

|              | 7.4 Short-term Goals |     |

|--------------|----------------------|-----|

| 8            | Conclusions          | 129 |

| $\mathbf{A}$ | Signature Tables     | 133 |

| В            | Code Statistics      | 136 |

| Re           | eferences            | 137 |

| 3.1  | Power grid architecture                                                                                                                                                                                                                                           | 15 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.2  | Instrumentation setup                                                                                                                                                                                                                                             | 16 |

| 3.3  | Block diagram of the test structure (a) and details of the Resistance Measurement Circuit (RMC) (b)                                                                                                                                                               | 17 |

| 3.4  | 1-port and 2-port power-up schemes to determine appropriate resistance model. Since the stimulus transistors can be modeled as a current source with a known voltage, the non-linearity and process variations inherent to the transistors do not affect the test | 19 |

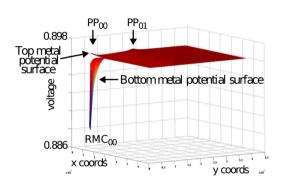

| 3.5  | Top and bottom voltage profile of 2-port simulation experiment of the test chip grid                                                                                                                                                                              | 21 |

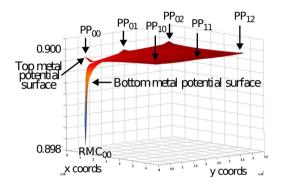

| 3.6  | Top and bottom voltage profile of 6-port simulation experiment of a commercial grid                                                                                                                                                                               | 21 |

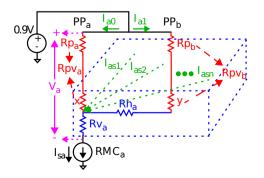

| 3.7  | Complete model: 1 <sup>st</sup> test                                                                                                                                                                                                                              | 22 |

| 3.8  | Complete model: 2 <sup>nd</sup> test                                                                                                                                                                                                                              | 22 |

| 3.9  | Complete model: 3 <sup>rd</sup> test                                                                                                                                                                                                                              | 23 |

| 3.10 | Power schemes investigated                                                                                                                                                                                                                                        | 27 |

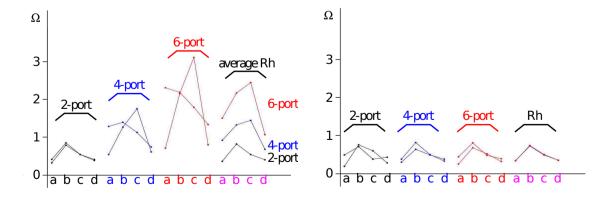

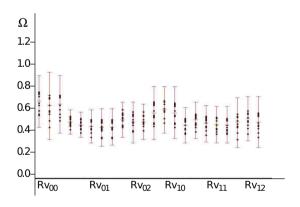

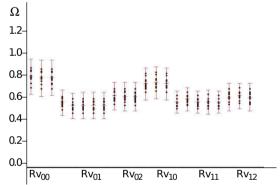

| 3.11 | $R_{\rm pv}$ and $R_{\rm v}$ results under different power-up configurations          | 28 |

|------|---------------------------------------------------------------------------------------|----|

| 3.12 | $R_{\rm h}$ values from Eq.'s 3.12 and 3.13                                           | 29 |

| 3.13 | $R_{\rm h}$ values from Eq.'s 3.9 and 3.10                                            | 29 |

| 3.14 | Resistance network on the test chips                                                  | 31 |

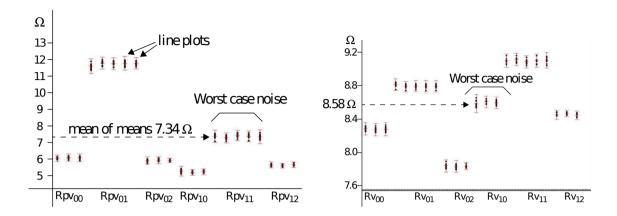

| 3.15 | Noise analysis of $R_{\rm pv}$ s                                                      | 32 |

| 3.16 | Noise analysis of $R_{\rm v}$ s                                                       | 32 |

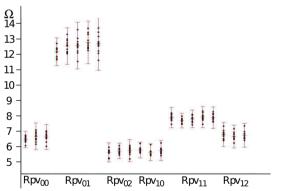

| 3.17 | $R_{\mathrm{pv}}$ analysis for $\mathrm{CS}_1$                                        | 34 |

| 3.18 | $R_{\rm pv}$ analysis for ${\rm CS_2}$                                                | 34 |

| 3.19 | $R_{\rm v}$ analysis for ${\rm CS_1}$                                                 | 35 |

| 3.20 | $R_{\rm v}$ analysis for ${\rm CS_2}$                                                 | 35 |

| 3.21 | Alternative RMCs used in special experiments                                          | 35 |

| 3.22 | Alternative RMC $R_{\rm v}$ analysis for ${\rm CS_1}$                                 | 36 |

| 3.23 | Alternative RMC $R_{\rm v}$ analysis for ${\rm CS}_2$                                 | 36 |

| 3.24 | $R_{\rm h}$ analysis for ${\rm CS_1}$                                                 | 37 |

| 3.25 | $R_{\rm h}$ analysis for ${\rm CS_2}$                                                 | 37 |

| 4.1  | Review of PUF circuit operation theory                                                | 39 |

| 4.2  | (a) Connections of a modified version of the SMC and (b) details of the modified SMC. | 41 |

| 4.3  | On-chip instrumentation for signature generation                                      | 43 |

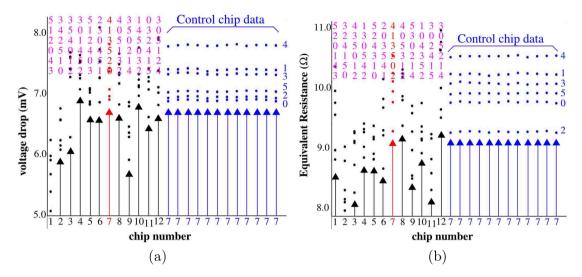

| 4.4  | (a) Voltage drop signatures for 12 chips and 12 control samples. (b) Equivalent resistance signatures for the same 12 chips and 12 control |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | samples                                                                                                                                    | 45 |

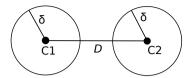

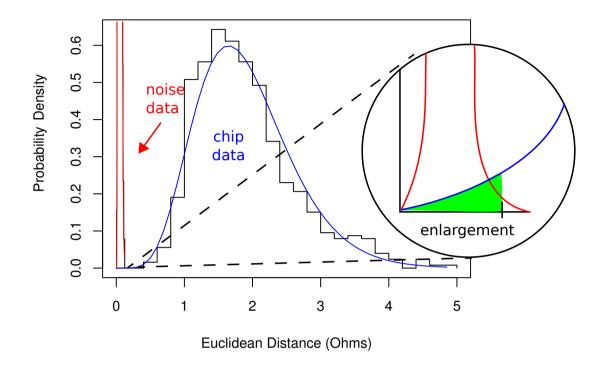

| 4.5  | Illustration of the Euclidean distance $D$ between two chips $C_1$ and $C_2$ and the uncertainty $\delta$ introduced by noise              | 46 |

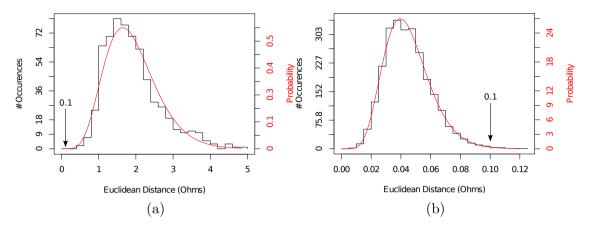

| 4.6  | Histogram of chip (a) and noise (b) equivalent resistance distances and Gamma function fit                                                 | 47 |

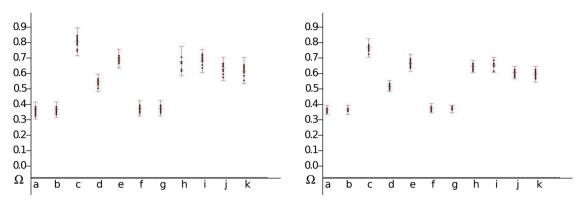

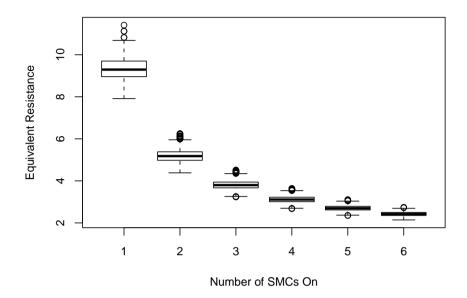

| 5.1  | Box plots of 1-on through 6-on $(x$ -axis) ER values $(y$ -axis) measured from 36 chips                                                    | 52 |

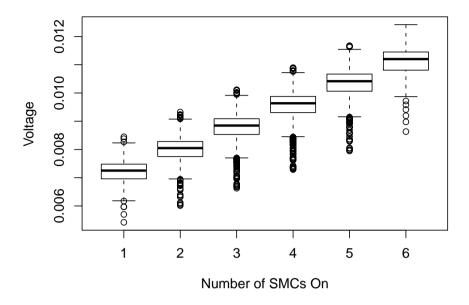

| 5.2  | Box plots of 1-on through 6-on $(x$ -axis) VDrop values $(y$ -axis) measured from 36 chips                                                 | 53 |

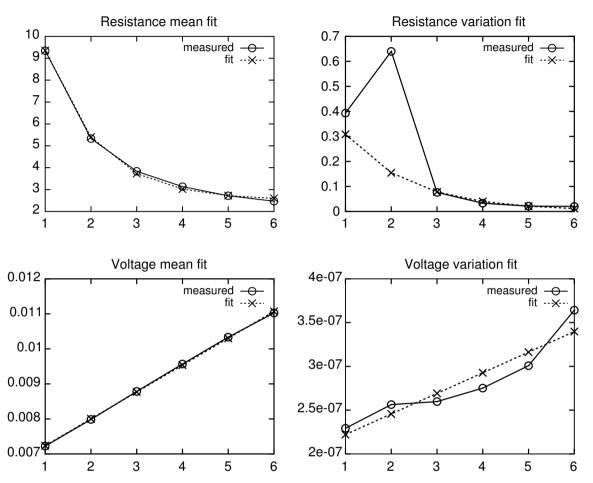

| 5.3  | Trends and fits of means and variances of ERs and VDrops for the multiple-on scenarios                                                     | 54 |

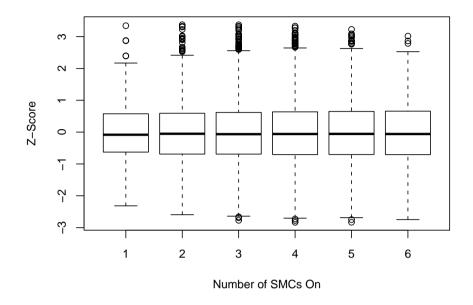

| 5.4  | Scaled box plots of 1-on through 6-on $(x$ -axis) ER values $(y$ -axis) measured from 36 chips                                             | 55 |

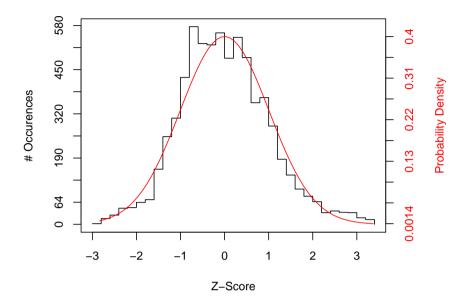

| 5.5  | Histogram and Gaussian fit of standardized ERs from 192 responses and 36 chips.                                                            | 56 |

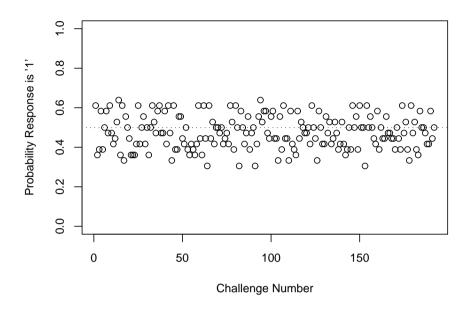

| 5.6  | Single-bit probability analysis of the ER PUF                                                                                              | 57 |

| 5.7  | Gamma function fit of noise (left) and chip (right) ER Euclidean distance (ED) histograms                                                  | 58 |

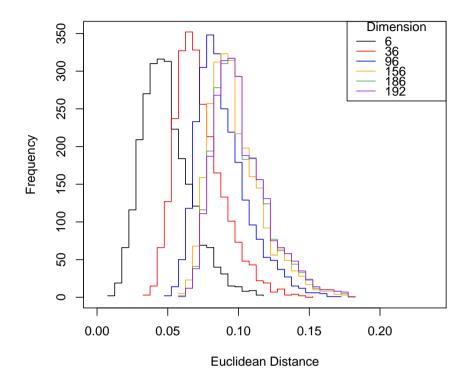

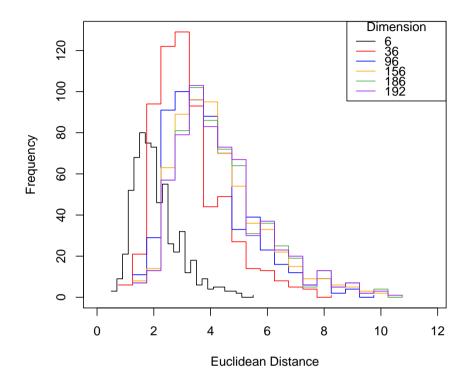

| 5.8  | ER ED cumulative PDFs of noise for groups 1-on through 6-on                                                                                | 60 |

| 5.9  | ER ED cumulative PDFs of chips for groups 1-on through 6-on                                                                                | 61 |

| 5.10 | Collision probability using ER response vector sizes from 6 to 192.                                                                        | 62 |

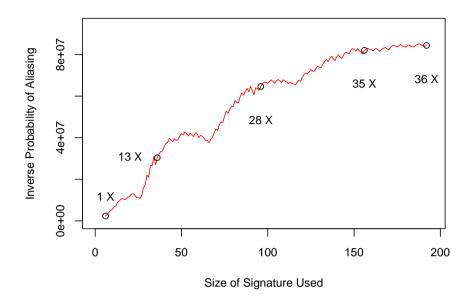

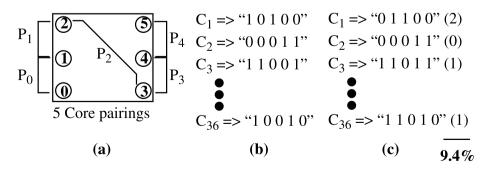

| 5.11 | Pairing and analysis illustration.                                                                                                | 62 |

|------|-----------------------------------------------------------------------------------------------------------------------------------|----|

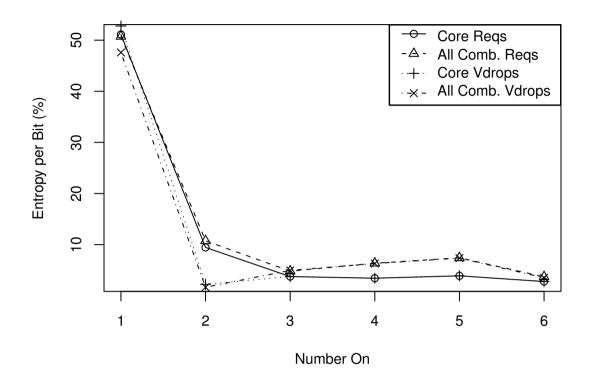

| 5.12 | Entropy analysis of VDrops and ERs                                                                                                | 64 |

| 6.1  | Clamshell apparatus cross-sectional diagram                                                                                       | 69 |

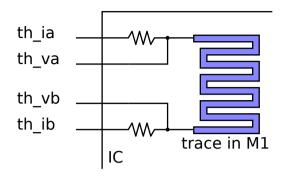

| 6.2  | On-chip resistor for characterizing resistance                                                                                    | 70 |

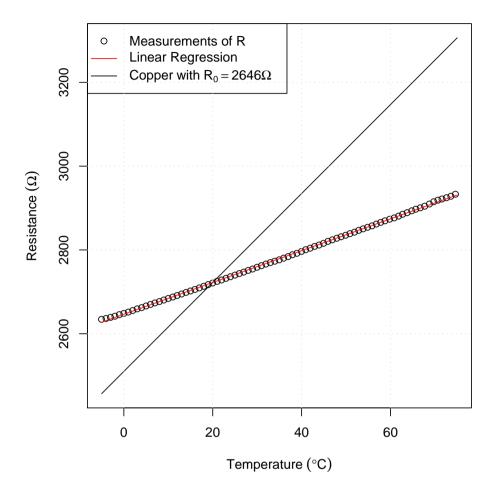

| 6.3  | On-chip resistance versus temperature                                                                                             | 71 |

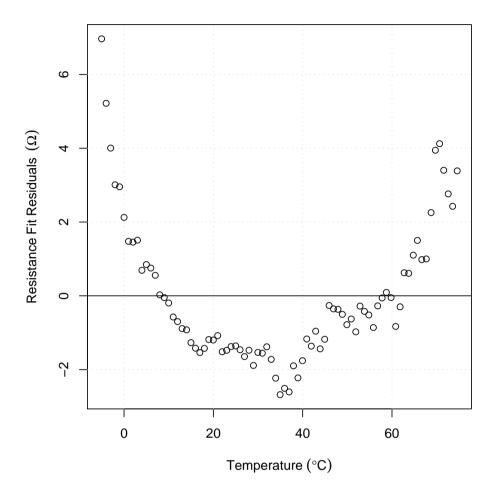

| 6.4  | Residuals for linear regression of on-chip resistance versus temperature                                                          | 72 |

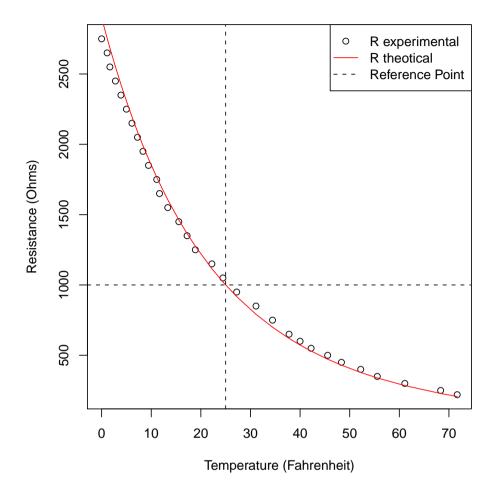

| 6.5  | GE RL1007-624 thermistor characterization                                                                                         | 75 |

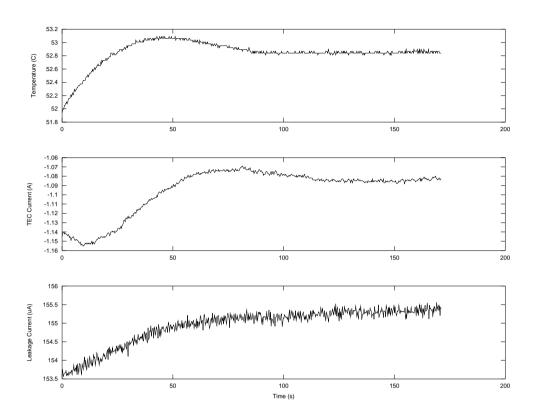

| 6.6  | Example transition from 52 to 53 degrees Celsius                                                                                  | 78 |

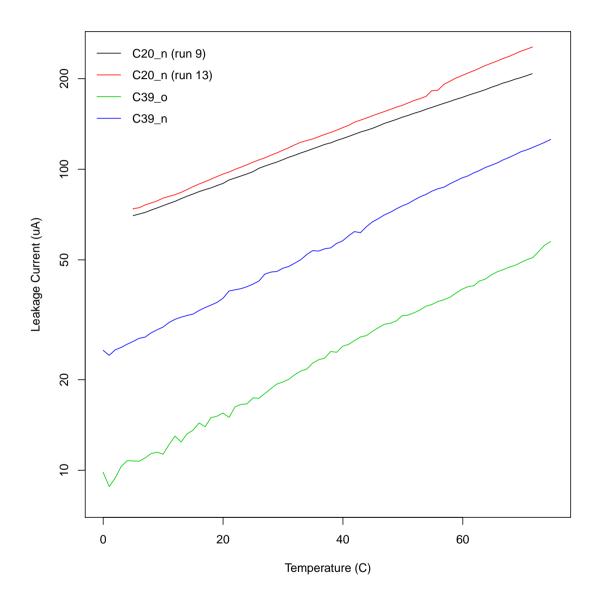

| 6.7  | Trends of leakage current versus temperature, $y$ -axis is logarithmic .                                                          | 79 |

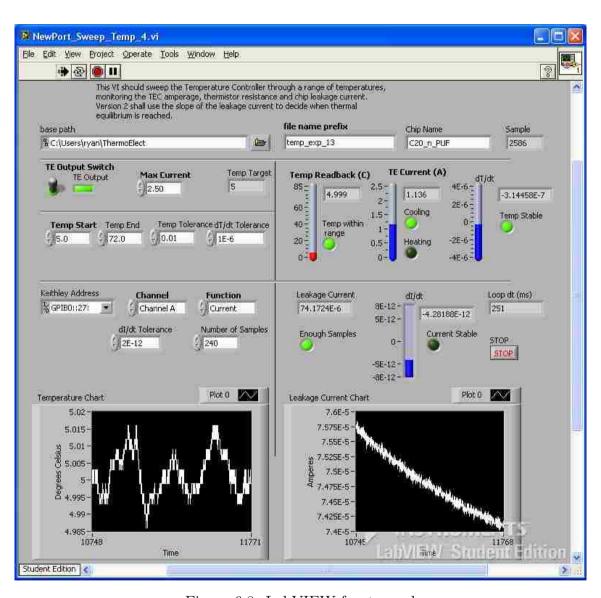

| 6.8  | LabVIEW front panel                                                                                                               | 82 |

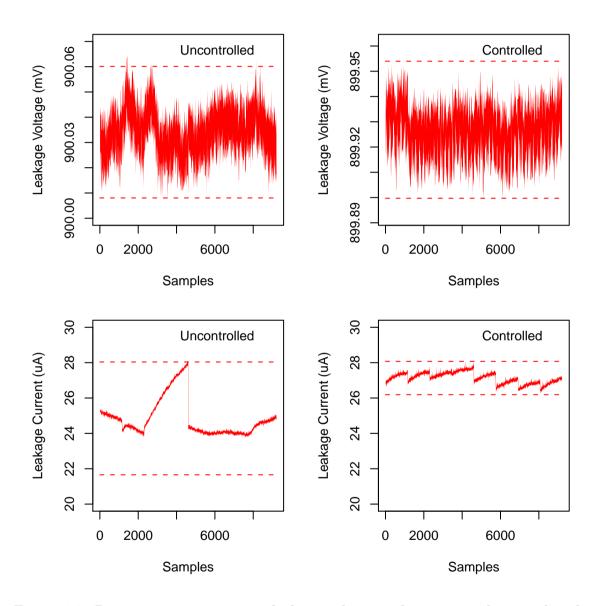

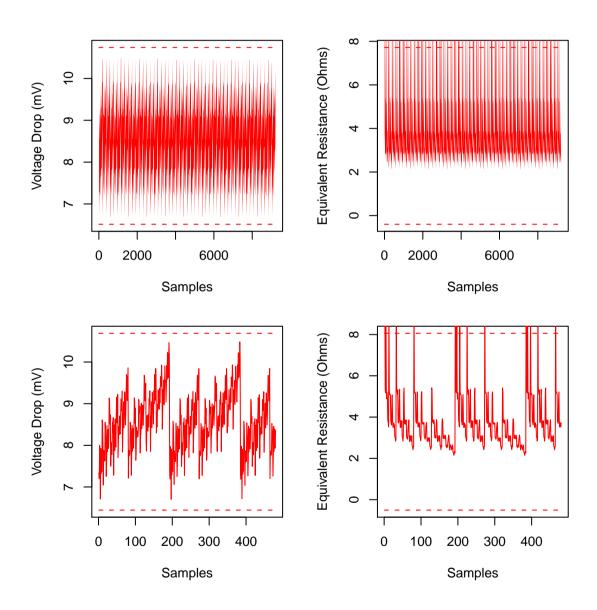

| 6.9  | Raw measurement noise: leakage voltage and current without and with active temperature control                                    | 84 |

| 6.10 | Voltage and current measured under shorting condition without temperature control (result similar when temperature is controlled) | 89 |

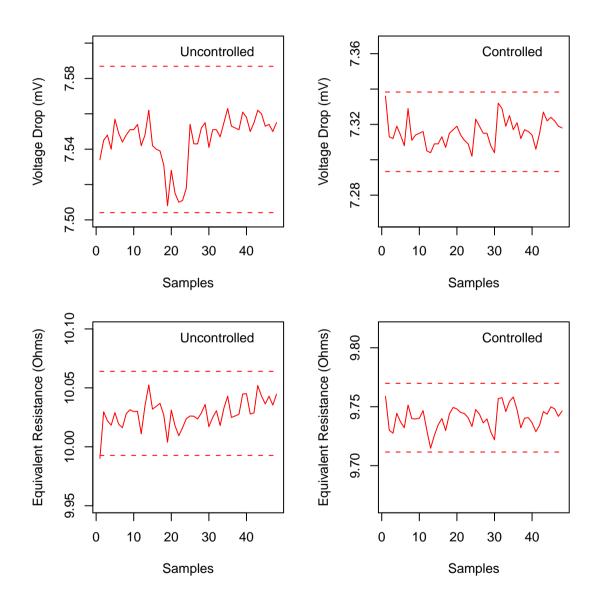

| 6.11 | $V_{\rm drop}$ and $R_{\rm eq}$ measurement noise with and without temperature control                                            | 90 |

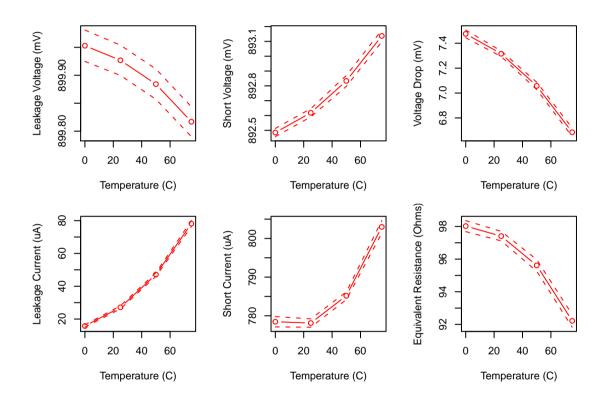

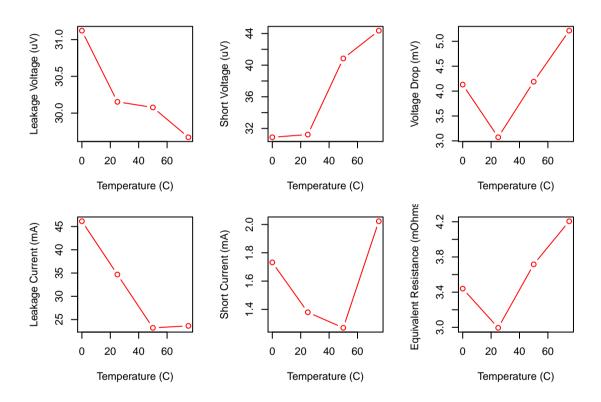

| 6.12 | Mean and standard deviations of various measurements versus temperature                                                           | 91 |

| 6.13 | $3\sigma/\mu$ relative noise floor for various measurements versus temperature                                                    | 92 |

| 6.14 | 72-point mean $R_{\rm eq}$ versus temperature for the 192-values of the noise sample                                              | 95 |

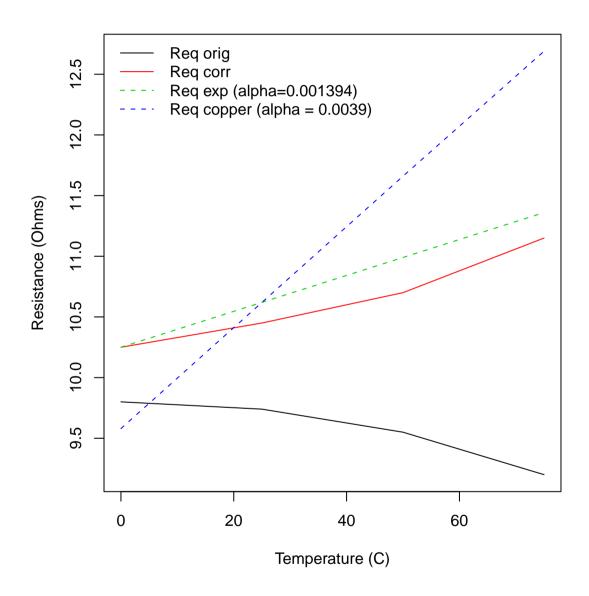

| 6.15 | Histograms of $R_{\rm eq}$ vector inter- and intra-chip Euclidean distances $\ .$                                                 | 98 |

| 6.16 | Histograms of $V_{drop}$ vector inter- and intra-chip Euclidean distances                                                                                                                                                                                                                                                 | 99  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.17 | Histograms of aggregate (0 - 75°C) $V_{\rm drop}$ and $R_{\rm eq}$ vector inter- and intra-chip Euclidean distances                                                                                                                                                                                                       | 100 |

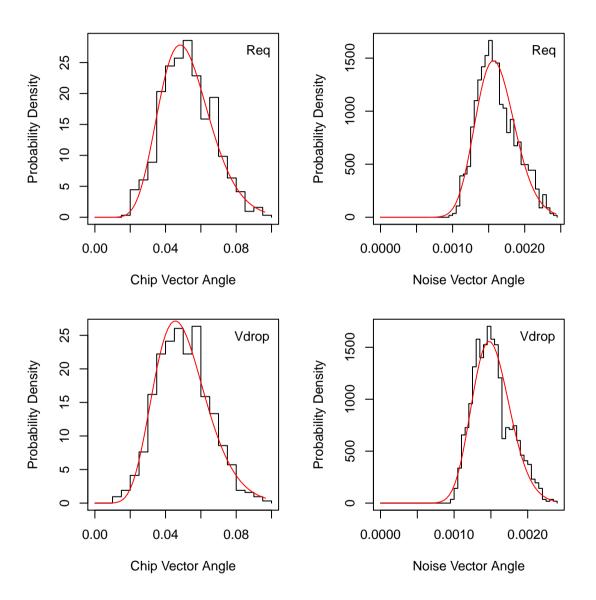

| 6.18 | Histograms of nominal (25°C) $V_{\rm drop}$ and $R_{\rm eq}$ vector inter- and intrachip vector angles                                                                                                                                                                                                                    | 105 |

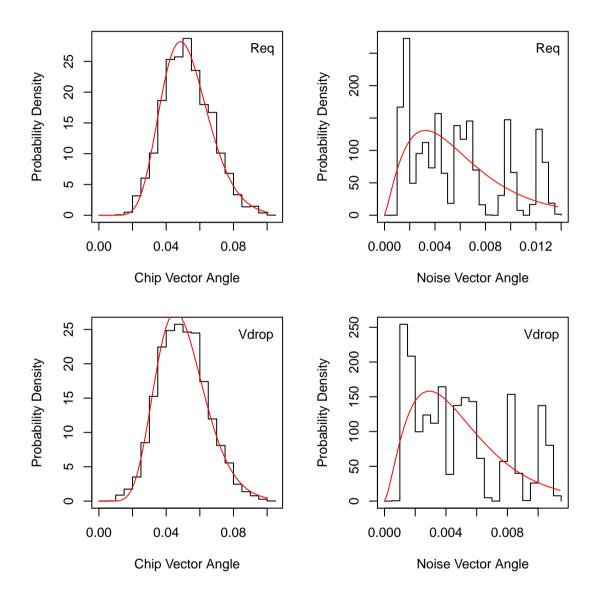

| 6.19 | Histograms of aggregate (0 - 75°C) $V_{\rm drop}$ and $R_{\rm eq}$ vector inter- and intra-chip vector angles                                                                                                                                                                                                             | 106 |

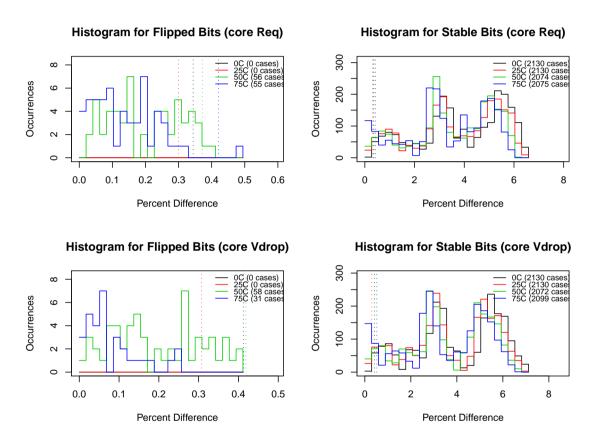

| 6.20 | Histograms of Percent Differences $(100 \times (x-y)/x)$ for <i>core</i> bits that flipped (left) and bits that were stable (right) for $R_{eq}$ (top) and $V_{drop}$ (bottom). Each plot includes the four temperature points between 0 and 75°C. The vertical lines indicate the corresponding measurement noise floor. | 109 |

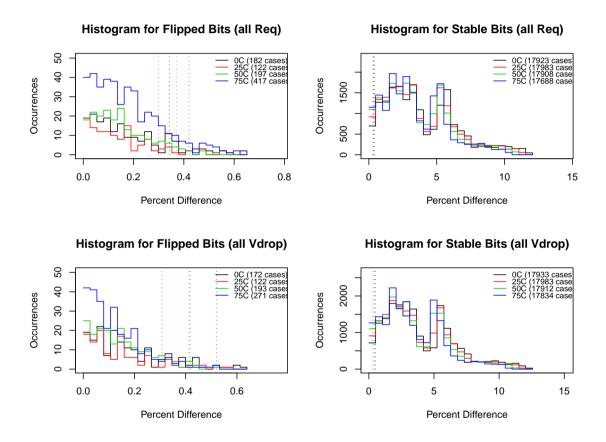

| 6.21 | Histograms of Percent Differences $(100 \times (x-y)/x)$ for all bits that flipped (left) and bits that were stable (right) for $R_{eq}$ (top) and $V_{drop}$ (bottom). Each plot includes the four temperature points between 0 and 75°C. The vertical lines indicate the corresponding measurement noise floor.         | 110 |

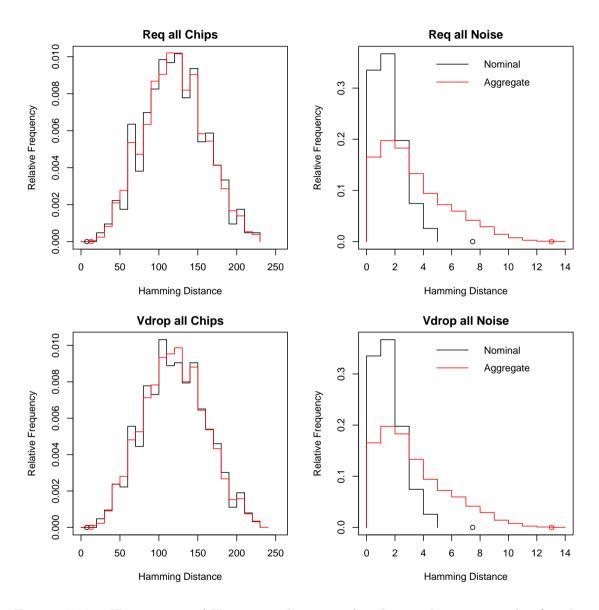

| 6.22 | Histograms of Hamming distances for chip and noise samples for the $V_{\rm drop}$ and $R_{\rm eq}$ PUFs, using the "all" construction                                                                                                                                                                                     | 115 |

| 6.23 | Histograms of Hamming distances for chip and noise samples for the $V_{\rm drop}$ and $R_{\rm eq}$ PUFs, using the "core" construction                                                                                                                                                                                    | 116 |

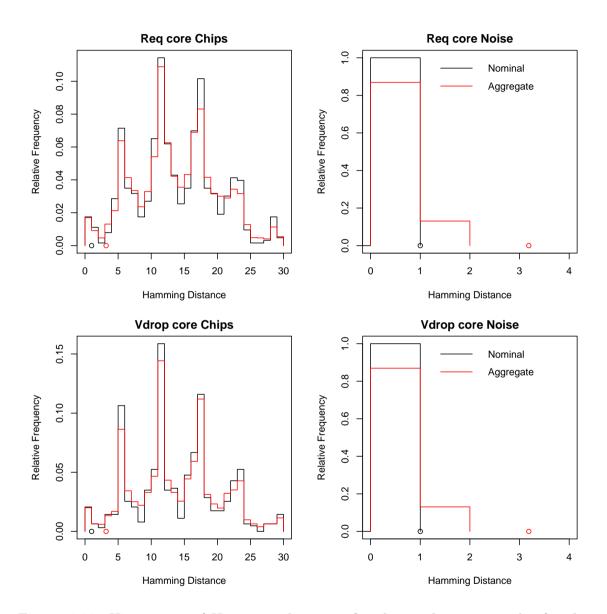

| 6.24 | The observe transistor physical circuit view                                                                                                                                                                                                                                                                              | 119 |

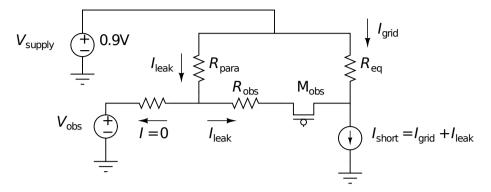

| 6.25 | Original and corrected equivalent resistance versus temperature                                                                                                                                                                                                                                                           | 122 |

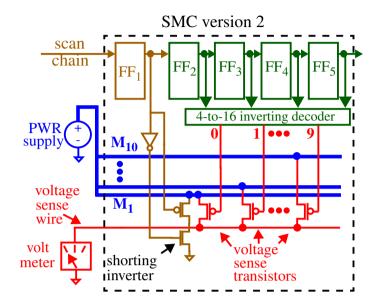

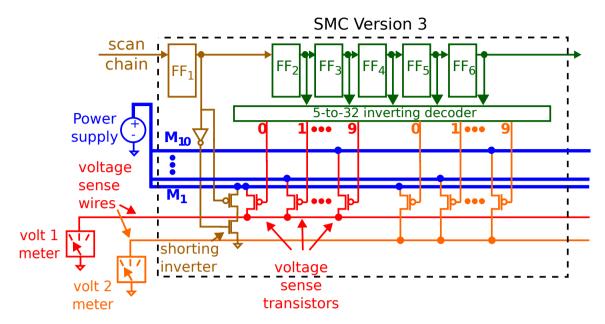

| 7 1  | SMC with multiple sense transistors for different metal layers                                                                                                                                                                                                                                                            | 124 |

| 7.2 | Extension of SMC primitive shown in Figure 7.1 to support two volt- |    |

|-----|---------------------------------------------------------------------|----|

|     | age sense wires.                                                    | 27 |

# List of Tables

| 3.1 | Numerical analysis of 1-port and 2-port simulation and hardware                                                |    |

|-----|----------------------------------------------------------------------------------------------------------------|----|

|     | experiments                                                                                                    | 20 |

| 3.2 | Numerical analysis of 6-port simulations of a low-resistance PDS                                               | 22 |

| 4.1 | Probability that the Euclidean distance between chips is less than 99.7% of all noise Euclidean distances      | 48 |

| 5.1 | Chip configurations and number of response                                                                     | 50 |

| 5.2 | Collision Analysis                                                                                             | 60 |

| 5.3 | Discrete Signature Metrics                                                                                     | 65 |

| 6.1 | Fitted model parameters for leakage current versus temperature us-                                             |    |

|     | ing the model $I_{leak} = e^{mT+b} = e^b e^{mT} \dots \dots \dots$                                             | 80 |

| 6.2 | Noise Levels without Temperature Control                                                                       | 88 |

| 6.3 | Noise Levels with Temperature Control (25°C)                                                                   | 88 |

| 6.4 | Review of previous estimates of probability. Note: the DAC2010 $V_{drop}$ results were previously unpublished. | 96 |

#### List of Tables

| 6.5  | Results of probability analysis for various combinations of analog $R_{\rm eq}$ and $V_{\rm drop}$ and different temperature points                                                                       | 97  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 6.6  | Results of probability analysis for analog $R_{\rm eq}$ and $V_{\rm drop}$ , in the nominal and aggregate case, using vector angles                                                                       | 103 |

| 6.7  | Results of probability analysis of digital PUF signatures for various combinations of $R_{eq}$ and $V_{drop}$ , core and all, and nominal temperature (25°C) and aggregate (worst-case) over 0°C and 75°C | 112 |

| 6.8  | Mean inter-chip and noise Hamming distances, reported in percent bits                                                                                                                                     | 114 |

| 6.9  | Single-bit probabilities for binary signatures (ideally $50\%$ )                                                                                                                                          | 118 |

| 6.10 | Bit flip probabilities for binary signatures (ideally $0\%$ )                                                                                                                                             | 118 |

| A.1  | Chip ER signature for chip 1                                                                                                                                                                              | 134 |

| A.2  | Chip ER signature for chip 2                                                                                                                                                                              | 135 |

# List of Acronyms

PUF Physical Unclonable Function

IC Integrated Circuit

RMC Resistance Measurement Circuit

SMC Stimulus/Measurement Circuit

CRP Challenge/Response Pair

**PDS** Power Distribution System

**HD** Hamming Distance

**ED** Euclidean Distance

**FEOL** Front End-of-Line

**BEOL** Back End-of-Line

**PP** Power Port

GCSM Global Current Source Meter

LCA Local Current Ammeter

VSW Voltage-Sense Wire

#### List of Tables

PG Power Grid

KVL Kirchhoff's Voltage Law

KCL Kirchhoff's Current Law

**PDF** Probability Density Function

**CDF** Cumulative Distribution Function

ER Equivalent Resistance

VDrop Voltage Drop

NTC Negative Temperature Coefficient

PTC Positive Temperature Coefficient

TCR Temperature Coefficient of Resistance

**TEC** Thermo-Electric Cooler

**SNR** Signal to Noise Ratio

ADC Analog-to-Digital Converter

### Chapter 1

### Introduction

It is widely accepted that the level of systematic and random process-induced variations in devices and interconnects is increasing as technologies are aggressively scaled [1, 2], and the sources of lithographic and non-lithographic process variations continue to grow [3, 4, 5]. *Process variations* impact key electrical parameters, including threshold voltage, resistance and capacitance, and have a significant impact on power and delay. For advanced technologies, it becomes increasingly important to understand and track process variations in order to model the process and avoid delays in time-to-market. In particular, new *methods and test structures* are needed to reduce the manufacturing development and yield learning cycle times, and to support rapid product and process debug. One technique is to include so-called "process monitors" directly into production designs. I propose such a structure and show that it can be used to understand interconnect resistance variations.

Many hardware security and trust mechanisms depend on the availability of secret keys that serve as a unique identity of each Integrated Circuit (IC). These keys serve as the basis for many higher-level hardware security mechanisms such as identification, authentication, remote activation, hardware metering and/or encryption.

Conventionally, secret keys are stored using fuses, flash or EPROM on the chip immediately after the IC is manufactured. For all mechanisms except identification, it is critical that access to this key remains restricted to the hardware circuits on the chip (i.e., remains secret). Unfortunately, since the keys are non-volatile, they are subject to both invasive and non-invasive physical attacks by adversaries who may be able to extract the key and thereby defeat the security mechanisms on which the key is built. Also, once a digital key is known, it becomes possible to produce *clone chips* that have the same key, which is as simple as programming the compromised key into a new chip, in most cases.

Methods of utilizing the same process variations I mentioned earlier, which are undesirable in the context of product quality, are sought to provide new hardware primitives for applications to hardware security. A trend in the literature is to leverage existing methods of characterizing process variations and design new circuits to serve these needs. The vulnerability of embedded digital keys to attacks can be mitigated if the keys are derived from the inherent, statistically-random manufacturing variations of the IC instead of being stored in a ROM. Physical Unclonable Functions (PUFs) embody structures that are sensitive to these silicon process variations can be used to generate keys which are a function of the specific random process variations of the device [6]. The process variations in sub-micron technologies are extremely difficult to control, and therefore creating two ICs that have the same random function is extremely difficult. In other words, a PUF is easy to fabricate, but practically impossible to duplicate. This is referred to as the "unclonable" property of PUFs, and is the hardware analog of a mathematical one-way function [7]. Typically, a PUF consists of a complex arrayed structure, each part of the structure producing what I will call "physical property". Whether it is the speed of a ring oscillator or the delay of a path, the physical properties are in turn used to produce a 1 or a 0, depending on the process variations specific to the device. Unlike the ROM methods that I mentioned earlier, PUF keys are also "volatile", which means

that the key is not present without the circuit in a fully-functional state (i.e., intact and powered on). Physical intrusions that involve de-processing the IC are considered to alter the function that the PUF originally had, and are therefore destructive to the PUF. For these two reasons, the most-attractive way to attack a PUF is to study its Challenge/Response Pairs (CRPs) and create a system that responds the same way. This is known as the "spoofing attack", where the attacker does not produce a counterfeit chip, but rather masquerades as a known chip over a network or other communication medium. The best defense against spoofing is to increase both the number and unpredictability of the CRPs. Since PUFs are "unclonable" and "volatile", they have the potential to revolutionize next-generation security and trust infrastructures in ICs.

However, since real PUFs are not ideal, other properties such as randomness and reproducibility also need to be considered. Randomness relates to the uniqueness of the function between ICs and specifies the probability that the function will have the same mapping on different ICs. Randomness is a function of the number of properties, the size of the CRPs and the statistical independence of the responses. Ideally, each bit in each response is like a fair coin and is a 0 exactly half of the time and a 1 the other half. In practice, the bits tend to be a biased toward 0 or 1, and the responses are somewhat dependent. Reproducibility relates to the integrity of the function under different environmental variations. Ideally, the response is always the same, but in practice the bits can flip and this has to be taken into account. More quality metrics are explained later, in Section 2.3. PUFs can be classified by the type of components that affect their function; e.g., MOSFETs, metal wires, insulator dielectric, etc. Each of these components is affected by process variations, which detract from the reproducibility of the PUF. However, some components are more sensitive than others. For example, the effect of ambient temperature on FET saturation current is quadratic, RO frequency (or inversely, path delay) is linear, and leakage current is exponential.

Typically, a PUF circuit includes an *interface* for retrieving a unique set of response vectors  $\{R_1, R_2, \ldots, R_n\}$  from a variety of different challenge vectors  $\{C_1, C_2, \ldots C_m\}$ . This interface serves two functions: (1) the PUF functions more like a RAM rather than a register, and (2) the underlying physical properties that define the function can be hidden. More formally, a PUF can be defined as a function

$$R = f(C), \quad f: \mathcal{B}^n \to \mathcal{B}^m,$$

(1.1)

where the challenge C is n bits and the response R is m bits. Typically, n = m, and the number of hardware resources p is at least  $n \times m$ . Since there is a response for each challenge, there are  $2^n$  responses, and therefore the number of responses is exponential to the number of hardware resources. The total number of response bits is therefore  $m2^n$ . Having an exponential number of challenges is ideal since cloning or spoofing then requires matching a large number of CRPs, which is intractable for large n.

A common method of using these physical properties to produce a bit is to pair two identical structures together and use the difference between them. I refer to this type of implementation as "differential". It is effective at balancing the process variations in order to produce an approximately-equal number of 1's and 0's. Using a "differential" method also means that the resulting bits are resistant to environmental variations that have a common-mode effect on the properties. For example, if two ring oscillator frequencies are 43MHz and 45MHz at one temperature, but increase to 44MHz and 47MHz at another temperature, then the relative difference is preserved and hence is resistant to changes in temperature. I will revisit this concept later in the discussion of the integrated PUF architecture, which is differential.

In this dissertation, I present the theory of a new PUF that is defined using resistance variations in Power Distribution System (PDS) (or power grid) of an IC. In Chapter 3, I present techniques for measuring resistance variations in the PDS that is enabled by an embedded primitive and external instrumentation. Then in

Chapter 4, I show that these same resistances which are useful for understanding process variations can be used to define a PUF and I evaluate the potency of the PUF to distinguish one IC from one another using the metric of the probability of aliasing. In Chapter 5, I describe extensions of this PUF that increase the number of CRPs from linear to exponential and I apply several other quality metrics that characterize the performance and security of the PUF. However, in order for a PUF to be used as a low-level primitive in hardware security applications, it needs to be integrated on-chip. To solve this problem, Chapter 4 also presents an architecture that implements the PUF on-chip and has digital input and output. In Chapter 5 and 6, I show that this architecture is also a viable PUF implementation. In Chapter 6, the previous analysis is repeated with temperature control and the temperature sensitivity of the various PUF implementations is evaluated. In Chapter 7, I present plans for implementing the integrated architecture, as well as extensions to the hardware primitive that should make it both more powerful and more accurate. Chapter 8 reviews the theory and presents reflections on what I learned.

# Chapter 2

### Background

This chapter provides a discussion of previous work in the areas of studying process variation in Section 2.1, building hardware security with PUFs in Section 2.2 and quality metrics for PUFs in Section 2.3. This builds upon the overview and definitions set forth in Chapter 1.

### 2.1 PDS Variation Characterization

There is a wide spectrum of published works on measuring and analyzing process variations. The techniques proposed in [8, 9] make use of ring oscillators and other types of test structures to track variations in Front End-of-Line (FEOL) parameters or single wire/via variations in Back End-of-Line (BEOL) parameters. For example, the authors of [8] propose a logic characterization vehicle to investigate the yield and performance impact of process variations. The authors of [10] proposed digitally-configurable ring oscillators to measure the effects of process variations on performance. A framework for the statistical design of experiments to measure the variance in critical dimensions of gate poly-silicon is proposed in [11]. A test struc-

ture to measure cell-to-cell delay mismatch due to process variations is proposed in [12], and another for the statistical characterization of local device mismatches is proposed in [13]. The authors of [14] propose a test structure that enables the extraction of spatial- and layout-dependent variations in both transistor and interconnect structures.

The techniques proposed in [9, 15, 16, 17, 18] focus on the measurement and analysis of resistance variations, but again, the work is limited to isolated test structures (wires, vias, etc.). For example, the authors of [15] and [16] propose test structures for characterizing wire resistance mismatch. Resistance measurement and analysis techniques for line width and step variation are described in [17] and [18]. In [9], dishing and erosion in non-ideal copper Chemical-Mechanical Planarization (CMP) is described, and dummy feature insertion techniques are proposed to reduce its impact on resistance variations. To my knowledge, [19] was the first time a technique has been proposed for measuring resistance variations in the PDS.

In [19], we proposed a test infrastructure that supports measurement of the PDS resistance characteristics for tracking BEOL process variations. The method enables a fast, first-order analysis of metal resistivity, and facilitates the identification of process problems. Since it is designed as a minimal augmentation to an existing design, it also serves to enable the resistance characteristics of the PDS to be evaluated for validation purposes, and provides meaningful data in the context of an actual circuit design, as opposed to the use of isolated test structures. This method is explained in Chapter 3.

### 2.2 Physical Unclonable Functions

Although the topic is relatively new, there is also a broad spectrum of work on PUFs (sometimes called Physical Unknown Functions[20], or Physical Random Functions

[21]), that can be classified by their technique (Section 2.2.2) and its application (Section 2.2.1).

#### 2.2.1 Applications

Many applications of PUFs have been proposed including IC identification [22], labeling RFID tags, addressing wireless sensor nodes, IC process quality control [23], providing unique keys for encryption [24], IP protection on FPGA's [25, 26], authentication via challenge-response protocols [21, 27], and remote service and feature activation [28].

The authors of [29, 21, 22, 30] explain that, if an IC was able to provide its own unique physical identifier, then this signature could be used in the same way that human fingerprints are. That is, the signatures of known (and authorized) ICs could be collected, and the IC could output its signature later in the field. This could be used for tracking purposes, Return Materials Authorization (RMA), and detection of hardware piracy (e.g., counterfeit ICs, over-manufacturing, etc.).

Authentication is a mechanism by which the IC is identified via a challengeresponse protocol. The term authentication means that the identity of the response is also verified. As the authors of [21, 31, 27] explain, a chip ID alone is not sufficient for authentication, since the response is always the same and can be reproduced. Instead, a secret key is embedded that enables the IC to generate a unique response to a challenge, which is generated each time. That way, so long as the key is secret, the authentication mechanism is not vulnerable to spoofing.

The authors of [24, 32] propose that PUFs be used to integrate secret keys for the use in cryptography. The author of [20] explains that, just as algorithmic one-way functions are critical to cryptography in software, PUFs are useful to cryptography in hardware. Specifically, an ideal PUF has the property that it is easy to generate a

response, but difficult to predict one, and PUFs are therefore inherently asymmetric.

Intellectual Property (IP) protection in FPGAs is presented as a major problem in [33, 24, 26, 34]. FPGA IP are bit streams that describe large functional blocks (like a microprocessor) and are licensed to be used to build larger designs or are complete designs themselves. These bit streams are generally stored in SRAMs, which makes them vulnerable to copying since the SRAM can be read directly. Therefore, methods are sought to stop that bit stream from working on FPGAs other than those authorized. The authors of [24] propose new protocols for the IP protection problem on FPGAs, that are based on public-key cryptography, and exploit PUFs derived from SRAM start-up conditions.

The authors of [28, 35] describe remote activation schemes that enable IC designers to lock each IC either once or at every start-up and then to enable it remotely. In [28], their objectives were realized by adding a few states to the finite state machine (FSM) of a design and by adding control signals that are a function of the unique IDs. In effect, the hardware "locks up" waiting for an activation code specific to that IC. This enables the designer, who knows the unique internal control signals, to issue a unique activation code that unlocks only that IC. This mechanism offers protection against unauthorized use of Intellectual Property (IP) and hardware piracy (the illegal manufacturing of ICs).

#### 2.2.2 Techniques

Various PUF techniques have been proposed, including mismatched delay-lines [36, 37, 21, 31, 27] and Ring Oscillators (ROs) [38, 34], exploiting inherent SRAM power-on patterns [26, 24], MOS device mismatch [29, 22, 38, 23, 34] and input-dependent leakage patterns [39].

The authors of [26] proposed that the start-up values of embedded SRAM mem-

ories be used to create a PUF, especially in FPGAs where the start-up values can be accessed. When first powered on, SRAM memories are in an unstable state. The mis-match of the transistors composing the SRAM cells dictate the final start-up value of a 0 or a 1. Hence, a PUF can be constructed by dedicating some of the intrinsic SRAM memories (they used 64 bits) to be read only.

The authors of [36, 37, 21, 27] propose using delay properties of ICs for identification. Delay-based approaches involve mismatch in both MOS devices and interconnects. In [36], the authors apply the relative mismatch of delay lines, which are dependent on random process parameters, to generating unique signatures. The authors of [37] propose integrating the delay fingerprint hardware into the functional design, which enables identification and Trojan circuit detection.

The authors of [22] propose that the relative current-driving capabilities of transistors, which are a function of random polysilicon crystal formations, be exploited. To utilize these random formations, they proposed that MOSFET device mismatches be detected by comparing their current against a reference current. The resulting ones and zeros form the fingerprint (PUF). The authors of [29] propose that the MOSFET threshold voltages, which are a function of the random placement of impurity dopant atoms, be exploited. Frequently, a ROM-like structure is used that allows the PUF to be compact and easily read.

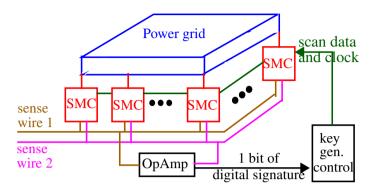

In [40], we proposed two PUFs which are described in Chapter 4. One PUF utilizes the voltage drop across the power grid due to a current being drawn through the grid. We call this the voltage drop PUF and it is a function of both metal resistance and transistors. The second PUF utilizes the global current in order to measure the equivalent resistance of the power grid. We call this the equivalent resistance PUF and it is a function of only the power grid, which is a function of specific metal resistances. This is an attractive property because the resistance of the power grid is marginally affected by environmental variations. In fact, resistance is a

linear function of temperature, and temperature is the only environmental parameter that directly affects metal resistance. Moreover, the distributed nature of the power grid makes it more prone to both random and systematic process variation effects, thereby decreasing its collision probability with other chips. Another significant advantage of using the power grid as a PUF is that it is an existing, distributed resource in every design. Therefore, the overhead of the power grid PUF is limited to the challenge/response circuitry which is well below 1% of the chip area. To our knowledge, this was the first time that a PDS measurement architecture has been proposed as a PUF.

#### 2.3 PUF Metrics

Many metrics for PUFs have been established to assess their quality and security [41]. The major categories of metrics are *predictability*, *reverse-engineering*, *collision* and *sensitivity*, and are defined as follows.

The first type of vulnerability is predictability. In the context of pseudo-random number generators, if the generator being used is known, and the last output is known, then an attacker can accurately compute subsequent outputs. A similar attack is considered in the context of PUFs whereby an attacker learns several CRPs and tries to model unknown responses. The susceptibility of the PUF to this type of attack is related to how unique the responses are from one another. Three metrics for qualifying this are the single bit probability  $P(R_i = 0, 1)$ , the conditional probability  $P(R_i = 0, 1|R_j = 0, 1)$  and the Hamming distances between responses. Following is a description of these three metrics.

The single bit probability metric is the probability of response bit i, under all possible challenges, being a zero or a one. In the degenerate case, the output bits are zeros and ones, but are invariant under different challenges. In the ideal case,

$P(R_i = 0) = P(R_i = 1) = \frac{1}{2}$  and each output bit is like a flip of a coin for a given IC and a given challenge. The conditional probability metric addresses the independence between response bits. In the degenerate case, all of the output bits are the exactly the same (a zero or a one), but they can still all change under different challenges. In the ideal case, the result of flipping any bit in the challenge is a random set of half of the bits flipping in the response. As shown in [41], the effect of different challenge bits is not always the same; some challenge bits can affect the output more than others, and this is an artifact of the architecture. The Hamming distance between responses is another, more systematic method of addressing the same issue as the conditional probability, and is more amenable to computational analysis.

The second type of vulnerability is susceptibility to reverse-engineering. This vulnerability is a matter of how accurately the PUF can be modelled given a set of CRPs. In the ideal case, each m-bit response is independent from the rest. In that case, knowing all but one response does not increase the accuracy of guessing that last response; it still contains new information. For example, a plot of the modeling accuracy versus the number of CRPs tends to start at near zero (a guess) and then approach 100% with an exponential decay. To resist this weakness, the PUF circuit should obfuscate the physical properties of the system well so that the responses are highly "non-linear" or uncorrelated to the challenge. An example PUF interface that is highly "linear" would be simply XORing the n-bit input with n physical properties to produce the output. This would score very poorly against this metric. As mentioned earlier, other forms of reverse-engineering are considered destructive and therefore the original function is destroyed during the attack.

The third metric for PUFs is collision vulnerability. The previous metrics have only considered the set of responses from a single IC. Collision vulnerability considers how differentiable or distinguishable ICs are to one another. This is the essence of the power of the PUF to separate ICs, and is easily quantified by a collision

probability—there is one collision in every x ICs. In the ideal case, each IC is as different as possible from one another; in this case, we use the upper bound on the number of m-bit binary strings and we say that a PUF is resistant to collision attacks if the probability of collision approaches one in every  $2^m$  ICs. In the degenerate case, each IC has  $2^n$  possibly-distinct responses, but those responses are identical from IC to IC. Realities that detract from are systematic similarities that manifest in the layout-level of the PUF circuitry. These effects cause each IC to tend to have a similar response, detracting from the PUFs utility.

The last metric used to evaluate PUFs is the sensitivity of the PUF to environmental variations. Ideally, the response of a PUF to a given challenge is invariant over time and under different operating conditions such as temperate and supply voltage level. Unfortunately, these environmental variations tend to affect the PUF and cause the response to change. Depending on the components involved, some implementations are more sensitive than others. For example, the effect of ambient temperature on FET saturation current is quadratic, RO frequency (or, inversely, path delay) is linear, and leakage current is exponential.

A common approach to overcoming environmental variations in the physical quantities being measured is to pair them together so that they vary in the same way, and their differential persists even under different conditions. Another way to solve this problem is to use error-correcting codes. A designer would choose the complexity of the PUF (the number of physical properties) in order to achieve the desired level of collision, and then add an extra, say 15% in order to account for environmental variations. Then, in practice, a response would be recorded and then later the IC would give the same response, and one could use the Hamming distance between those responses to see if they are within some distance from one another.

# Chapter 3

# PDS Characterization

This chapter is organized into several sections, following the structure of our paper [19]. First, the architecture of the power grid, the on-chip support circuitry and the experiment setup are described in Section 3.1. Next, a model for the power grid is developed and validated with experimental data in Section 3.2. The experimental procedure for conducting PDS resistance measurements is given in Section 3.3. Finally, the simultaneous equations that need to be solved to obtain the resistance components of the PDS are described in Section 3.4. Finally, the resolution limits of our measurements are discussed in Section 3.5.

The results reported in this paper are derived from chips fabricated in a 65nm technology from IBM, and are therefore meaningful to state-of-the-art practices. However, the PDS measured in the hardware experiments was not designed to minimize ohmic IR and inductive  $L\frac{di}{dt}$  voltage drops, and from this perspective it does not conform to a typical PDS of a commercial product. In particular, the resistances of many of the PDS components of our test chips are larger—some by more than an order of magnitude—than those found in commercial chips. In order to validate our technique for commercial applications, we supplement our test chip results with

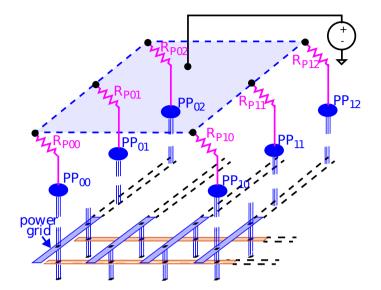

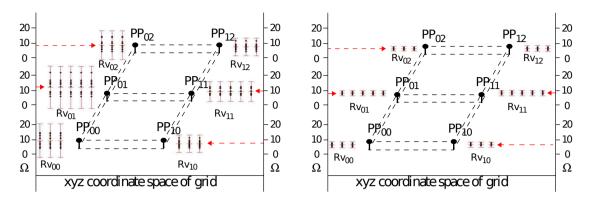

Figure 3.1: Power grid architecture

data from a simulation model that is representative of commercial designs.

## 3.1 PDS Architecture

A high-level representation of the power grid architecture used in the simulation and hardware experiments is shown in Figure 3.1. The bottom portion shows that adjacent metal layers are routed at right angles to each other in a mesh configuration with vias between the intersections. The ground (GND) grid, which is not shown, is interleaved with the power grid and routed in a similar fashion. Both grids are routed across the ten metal layers available in the 65 nm process. The width of the wires and the granularity of the mesh vary across the metal layers. In particular, the widths of the lower metal tracks are smaller and the granularity is finer than the widths and granularity of the metal wires in the upper layers. This feature of the power grid is typical of commercial designs [42].

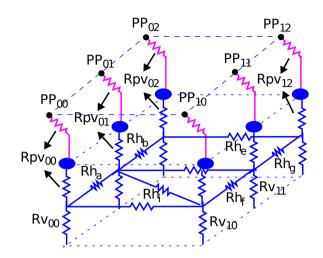

The power grid is connected to a set of six C4s or PP in the top metal layer. The

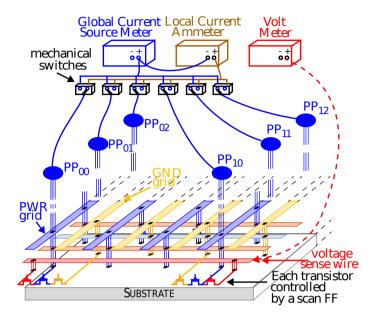

Figure 3.2: Instrumentation setup

Power Ports (PPs) are shown as ovals in the figure and are labeled PP<sub>00</sub> through PP<sub>12</sub>. Commercial power grids can have hundreds of such PPs. The C4s enable the power grid to be connected to the power supply, either through a membrane-style probe card (during wafer probe) or through the package wiring. The finite resistances of PP connections are represented as series resistances  $R_{Pxy}$  (where x, y are indices), in Figure 3.1. The measurement technique proposed in this work requires the measurement of branch currents through each of the PPs. For packaged chips, the PPs are typically wired into a power plane(s) within the package before being routed off-package through the power pins. Therefore, it is not possible to apply our technique directly to packaged parts without additional on-chip support circuits (beyond those described herein). We assume in the remainder of the paper that our technique is applied at wafer probe, where it is possible to access the PPs directly.

In our test setup, we emulate a wafer probe environment in our packaged chips by dedicating a separate package pin for each of the six PPs. The details of the test setup are shown in Figure 3.2. The package pins that are connected to the

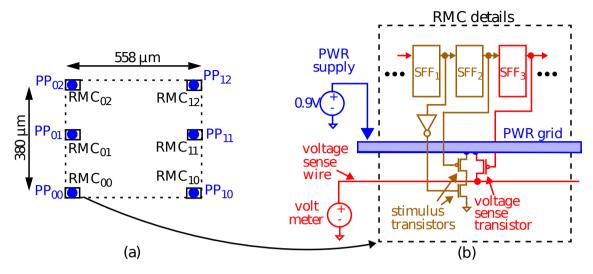

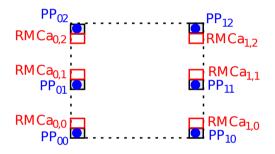

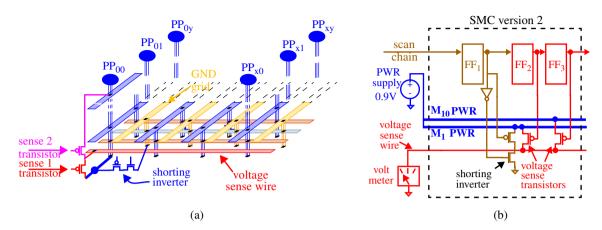

Figure 3.3: Block diagram of the test structure (a) and details of the RMC (b)

PPs are routed onto a PCB to a set of six mechanical, low-resistance switches. The switches can be configured in a left or right position. The left and right outputs of the switches each connect to a common wire that is routed to the Global Current Source Meter (GCSM) and Local Current Ammeter (LCA), respectively, as shown in the figure.

The GCSM provides 0.9 V to the PDS and can measure current with a precision of approximately 300 nA. The LCA is wired in series between the switches and the GCSM and allows measurement of the individual PP (local) currents at the same level of precision. For example, the switch configuration in Figure 3.2 allows measurement of the local PP<sub>00</sub> current  $I_{00}$ , as well as the global current.

In addition to branch currents, our technique to measure resistance also requires on-chip voltage measurements. The voltage is measured in our experiments using an additional (test-only) pin that is connected internally to a globally-routed Voltage-Sense Wire (VSW). A voltmeter is connected to this pin off-chip, as shown in Figure 3.2.

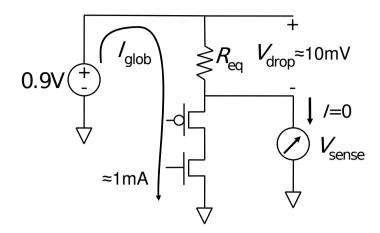

The last element of the test infrastructure is shown along the bottom of Figure 3.2 and in more detail in Figure 3.3. A RMC is inserted under each of the six C4s. The RMC consists of stimulus transistors, a voltage-sense transistor and a set of three scan flip-flops (SFFs). The outputs of the SFFs connect to the gates of the three transistors<sup>1</sup> as shown in Figure 3.3(b). The stimulus transistors provide a controlled stimulus—that is, a short between the power and ground grid—when the states of the SFF<sub>1</sub> and SFF<sub>2</sub> are set to 0. The voltage on the Metal 1 (bottom) layer of the power grid is measured using the voltage-sense transistor, which is enabled when a 0 is placed in SFF<sub>3</sub>.

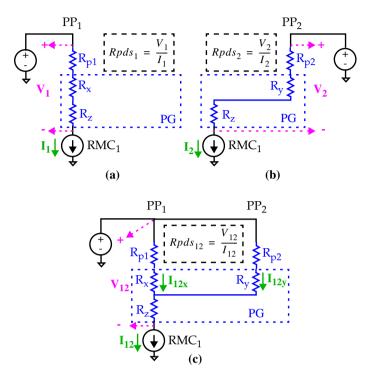

# 3.2 Power Grid Equivalent Circuit Model

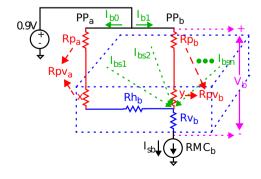

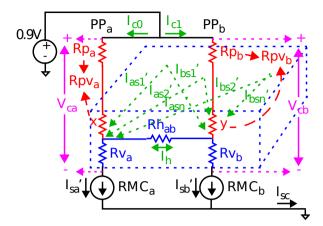

The equivalent resistance models shown for the power grid in Figure 3.4(a), 3.4(b) and 3.4(c) were deduced from SPICE DC simulation data collected from a resistance model of the test chip's power grid. The power grid resistances, given as  $R_x$ ,  $R_y$  and  $R_z$ , represent the equivalent resistance of an entire mesh of resistors in the simulation model. The resistances  $R_{p1}$  and  $R_{p2}$  represent the external connection or probe resistances to the power grid.

The models shown in Figures 3.4(a) and 3.4(b) are referred to as 1-port experiments because only one PP is connected to the power supply—the others are left floating. Similarly, the configuration in 3.4(c) is called a 2-port experiment. The stimulus in each configuration is provided by RMC<sub>1</sub>, which is depicted as a current source. The currents and voltage drops are labeled symbolically for each of the three experiments, e.g.  $I_1$  and  $V_1$ .

<sup>&</sup>lt;sup>1</sup>The stimulus as shown in our test structures was designed to serve other purposes beyond those described in this paper. A more efficient implementation would use only the p-channel transistor portion of the series transistor pair.

Figure 3.4: 1-port and 2-port power-up schemes to determine appropriate resistance model. Since the stimulus transistors can be modeled as a current source with a known voltage, the non-linearity and process variations inherent to the transistors do not affect the test.

Our objective is to verify that the equivalent resistance models of Figure 3.4 are valid representations of the actual PDS. Assuming they are valid, then

$$R_{\text{pds},12} = \frac{1}{\frac{1}{R_{\text{pl}} + R_{\text{x}}} + \frac{1}{R_{\text{p2}} + R_{\text{y}}}} + R_{\text{z}} = \frac{1}{\frac{1}{R_{\text{pds},1} - R_{\text{z}}} + \frac{1}{R_{\text{pds},2} - R_{\text{z}}}} + R_{\text{z}}$$

(3.1)

expresses the relationship between the equivalent resistances in the three models  $R_{\text{pds},1}$ ,  $R_{\text{pds},2}$  and  $R_{\text{pds},12}$ . Each of these is defined as  $V_i/I_i$  where  $V_i$  is the voltage drop and  $I_i$  is the total current, for i=1,2 or 12 (see dashed boxes in Figure 3.4). For example, the first element on the right side of the equation gives the parallel resistance of the upper network in Figure 3.4(c), expressed using the equivalent resistances in Figures 3.4(a) and 3.4(b). The second element on the right side of the equation accounts for the shared resistance  $R_z$  that is in series with the parallel

network.

As mentioned earlier, we confirmed these models using a numerical analysis of data collected from a simulation model and from one of the 65 nm test chips. The values of the equivalent resistances that were computed are presented in Table 3.1, and compared with the values measured from hardware. Columns two, three and four give the equivalent resistances computed using data from the configurations shown in Figures 3.4(a), 3.4(b) and 3.4(c), respectively. The measured value of  $R_{\rm pds,12}$  agrees with the value predicted by Eq. 3.1. The values of  $R_{\rm z}$  in the fifth column are derived by solving Eq. 3.1 for  $R_{\rm z}$ .

|            | $R_{\mathrm{pds},1}$ | $R_{ m pds,2}$ | $R_{\mathrm{pds,12}}$ | $R_{\rm z}$ | $R_{\rm x}$   | $R_{\rm z}/(R_{\rm x}+R_{\rm z})$ |

|------------|----------------------|----------------|-----------------------|-------------|---------------|-----------------------------------|

| Simulation | $14.05 \Omega$       | $20.04~\Omega$ | $12.10 \Omega$        | 8.18 Ω      | $0.63~\Omega$ | 92.9%                             |

| Hardware   | $14.24 \Omega$       | $20.02~\Omega$ | $12.27~\Omega$        | 8.38 Ω      | $0.62~\Omega$ | 93.1%                             |

Table 3.1: Numerical analysis of 1-port and 2-port simulation and hardware experiments.

The series resistance combinations  $R_{\rm p1} + R_{\rm x}$  and  $R_{\rm p2} + R_{\rm y}$  are represented by the terms in the denominator of Eq. 3.1, as indicated before, but the three tests as shown in Figure 3.4 are not sufficient to determine the individual values (e.g.,  $R_{\rm p1}$  and  $R_{\rm x}$ ). We were able to derive the individual values by creating a simulation model that closely approximates one of our test chips<sup>2</sup> The estimated values for  $R_{\rm p1}$  and  $R_{\rm p2}$  derived in this fashion are 5.24  $\Omega$  and 11.71  $\Omega$ , respectively.

The estimated values of  $R_x$  and  $R_y$  are easily obtained once  $R_{p1}$  and  $R_{p2}$  are known. The  $R_x$  values are given in the sixth column of Table 3.1 (the  $R_y$  values are similar). When compared with the  $R_z$  values in the fifth column, it is clear that  $R_x$  is smaller by more than an order of magnitude. Given that  $R_x$  and  $R_z$  are both grid equivalent resistances, this data indicates that the paths followed by the branch

<sup>&</sup>lt;sup>2</sup>The actual values can be measured by adding voltage observe points in the PDS's top metal layer directly beneath the C4s, as discussed later.

currents  $I_{12x}$  and  $I_{12y}$  from Figure 3.4(c) are common over a large fraction of the vertical resistance of the power grid. The last column in the table gives the fraction of common resistance at nearly 93%. The wire characteristics described for the power grid in Section 3.1 support this result. There, we disclosed that the resistance of the wires in the upper layers of the power grid is smaller than that of the wires in the lower layers.

Figure 3.5: Top and bottom voltage profile of 2-port simulation experiment of the test chip grid.

Figure 3.6: Top and bottom voltage profile of 6-port simulation experiment of a commercial grid

Our simulation model enabled a more detailed investigation of the spatial distribution of currents through the power grid. Figure 3.5 shows a 3-D voltage profile for the 2-port simulation model with RMC<sub>00</sub> enabled (see Figure 3.4(a)). The voltage potential surfaces of both the top-most metal layer and bottom-most metal layer are superimposed. For most of the x-y dimension of the grid, the top and bottom surface potentials are nearly identical, indicating that current from remote PPs, e.g. PP<sub>01</sub>, remains in the top portion of the grid until reaching the potential well near PP<sub>00</sub>. At this point, the branch currents from other PPs combine and traverse the majority of the vertical dimension together. This type of current behavior will tend to amplify the magnitude of local IR drops.

We performed another simulation on our power grid with much smaller via and

wire resistance-per-square resistances to determine how the values in Table 3.1 would change for a PDS that better represents a commercial design. The  $R_{\rm p}$ s were also reduced by a factor of twenty to model the contact resistance of a typical probe card. The voltage profile of this grid is shown in Figure 3.6 and its resistance characteristics are given in Table 3.2.  $R_{\rm pds,00}$  is the equivalent resistance measured with RMC<sub>00</sub> enabled. It is a factor of eight times smaller than the value in the second column of Table 3.1. The lower resistances of the metal wires in this model are also reflected in columns three and four. However, the fraction in column five is still significant at 80.6%, and therefore, the lower resistance of this grid only partially explains the current distribution characteristics. We determined using other grid configurations that the most significant factor affecting this fraction is the overall architecture of the Power Grid (PG). For example, PGs configured such that each layer has the same resistance produce a fraction of 50%.

|            | $R_{\rm pds,00}$ | $R_{\rm z}$   | $R_{\rm x}$   | $R_{\rm z}/(R_{\rm x}+R_{\rm z})$ |

|------------|------------------|---------------|---------------|-----------------------------------|

| Simulation | $1.74~\Omega$    | $1.47~\Omega$ | $0.35 \Omega$ | 80.6%                             |

Table 3.2: Numerical analysis of 6-port simulations of a low-resistance PDS.

## 3.3 PDS Resistance Measurement Procedure

Figure 3.8: Complete model: 2<sup>nd</sup> test.

Figure 3.9: Complete model: 3<sup>rd</sup> test.

One of our goals is to define a set of tests that provide data to solve for six unknown resistances in the PDS. The three tests and corresponding equivalent circuit models are shown in Figures 3.7, 3.8 and 3.9. The six resistances, two of which are the sum of two series resistances, are labeled  $R_{pv,a} = R_{p,a} + x$ ,  $R_{v,a}$ ,  $R_{pv,b} = R_{p,b} + y$ ,  $R_{v,b}$ ,  $R_{h,a}$  and  $R_{h,b}$ , where 'p' indicates probe, 'v' denotes vertical and 'h' denotes horizontal. As noted in the previous section, is not possible to separate the series resistances, e.g.  $R_{p,a} + x$ , unless capability is added to the infrastructure to allow the voltage to be sensed at the point where the C4 attaches to the power grid.

According to the models,  $R_{\text{ha}}$ ,  $R_{\text{hb}}$  and  $R_{\text{hab}}$  identify the same resistance and therefore represent only a single unknown. From simulation experiments, we find there are actually small differences in these resistances. The equations that we present later treat  $R_{\text{ha}}$  and  $R_{\text{hb}}$  in a special way and as separate variables. The values derived from our equations represent a good estimate of  $R_{\text{ha}}$ ,  $R_{\text{hb}}$  and  $R_{\text{hab}}$ .

Each test provides two independent equations, enabling values to be derived for the six resistances from the solution to a system of simultaneous equations (to be described). The third test shown in Figure 3.9 requires enabling both RMC<sub>a</sub> and RMC<sub>b</sub> and measuring two voltages,  $V_{\rm ca}$  and  $V_{\rm cb}$ . Under the proposed infrastructure,

it is necessary to measure each of these sequentially by enabling the appropriate voltage sense transistor.

The current and voltages shown in Figures 3.7, 3.8 and 3.9 are calibrated to remove the impact of leakage currents. This is an important step to obtaining a meaningful result in modern technologies, given the trend of increasing background leakage currents. Calibration is carried out by measuring the currents and voltages, as given in Figures 3.7 and 3.8, and under a forth configuration in which both RMC<sub>a</sub> and RMC<sub>b</sub> are disabled. These leakage currents are subtracted from the values measured under the three tests.

#### 3.3.1 Branch Current Calculation

Unlike the 1-port and 2-port experiments shown earlier, the multi-port scheme introduces a set of additional currents, such as those labeled  $I_{as1}$ ,  $I_{as2}$  through  $I_{asn}$  in Figure 3.7. These currents originate from the PPs distributed across the PG. The total current, e.g.  $I_{sa}$  in Figure 3.7, includes their contribution. Although it is straightforward to compute these supplementary currents, only the *total* current is needed in the equations given in the next section<sup>3</sup>.

The only currents that cannot be measured individually are the stimulus currents,  $I'_{\rm sa}$  and  $I'_{\rm sb}$ , shown in Figure 3.9. They are labeled using the prime symbol because they are related to the 'unprimed' values measured under the first and second tests. Under ideal conditions, the sum of current,  $I_{\rm sa} + I_{\rm sb}$ , measured under the first and second tests, is equivalent to  $I'_{\rm sa} + I'_{\rm sb}$  (or  $I_{\rm sc}$ ). However, the p-channel stimulus transistors are not ideal current sources, and the small change in  $V_{\rm DS}$  introduced by having both RMC<sub>a</sub> and RMC<sub>b</sub> enabled reduces their magnitudes.

$<sup>^3</sup>$ In our experiments, we compute the total current as the sum of the calibrated power port currents.

In our experiments, the difference is small—at most a couple  $\mu$ As—and can be derived using

$$\Delta I_{\rm s} = I_{\rm sa} + I_{\rm sb} - I_{sc} \tag{3.2}$$

where the constituent currents (right-hand side of the equation) are the total currents measured under each of the three tests. From simulation experiments, we determined that the reduction in current given by  $\Delta I_{\rm s}$  splits nearly equally across both RMC<sub>a</sub> and RMC<sub>b</sub> in the third test. This holds under the condition that the resistance characteristics of the PDS as measured from either stimulus location are similar—a reasonable assumption given the uniform architecture of the power grid. We examined a variety of resistance configurations and found that the magnitudes of  $I'_{\rm sa}$  and  $I'_{\rm sb}$  are well approximated using

$$I_{\rm sa}' = I_{\rm sa} - \frac{\Delta I_{\rm s}}{2} \tag{3.3}$$

$$I'_{\rm sb} = I_{\rm sb} - \frac{\Delta I_{\rm s}}{2}. \tag{3.4}$$

The supplemental currents, e.g.  $I'_{as1}$ , as well as the current across  $R_{hab}$ , e.g.  $I_h$ , as shown in Figure 3.9, can also be derived but are not needed to solve the set of equations given in the next section.

# 3.4 PDS Resistance Equations

The first four equations are derived from the models shown in Figures 3.7, 3.8 and 3.9 using Kirchhoff's Voltage Law (KVL).

$$V_{\rm a} = I_{\rm a0} \cdot R_{\rm pva} + I_{\rm sa} \cdot R_{\rm va} \tag{3.5}$$

$$V_{\rm ca} = I_{\rm c0} \cdot R_{\rm pva} + I'_{\rm sa} \cdot R_{\rm va} \tag{3.6}$$

$$V_{\rm b} = I_{\rm b1} \cdot R_{\rm pvb} + I_{\rm sb} \cdot R_{\rm vb} \tag{3.7}$$

$$V_{\rm cb} = I_{\rm c1} \cdot R_{\rm pvb} + I_{\rm sb}' \cdot R_{\rm vb} \tag{3.8}$$

Equations 3.5 through 3.8 yield values for  $R_{\text{pva}}$ ,  $R_{\text{va}}$ ,  $R_{\text{pvb}}$  and  $R_{\text{vb}}$  directly if solved as a set of simultaneous equations.

### 3.4.1 Horizontal Resistance Analysis

The equations that we use to compute values for  $R_{\rm ha}$  and  $R_{\rm hb}$ , Equations 3.9 and 3.10, are *not* consistent with KVL applied to the models in Figures 3.7 and 3.8. In particular,  $R_{\rm ha}$  is multiplied by the total current  $I_{\rm sa}$ , in contrast to the model, which indicates the multiplier should be the branch current  $I_{\rm a1}$ .

$$V_{\rm a} = I_{\rm a1} \cdot R_{\rm pvb} + I_{\rm sa}(R_{\rm ha} + R_{\rm va})$$

(3.9)

$$V_{\rm b} = I_{\rm b0} \cdot R_{\rm pva} + I_{\rm sb}(R_{\rm hb} + R_{\rm vb}) \tag{3.10}$$

$$R_{\rm h} = R_{\rm ha} + R_{\rm hb} \tag{3.11}$$

Given that  $I_{\rm a1}$  is strictly less than  $I_{\rm sa}$ , the values obtained for  $R_{\rm ha}$  and  $R_{\rm hb}$  using Equations 3.9 and 3.10 underestimate the actual values. Interestingly, the sum of  $R_{\rm ha}$  and  $R_{\rm hb}$  using these equations produces a good estimate of their actual value, under the assumption that  $R_{\rm ha}$  is nearly equal to  $R_{\rm hb}$ , as we noted above, is reasonable. We use  $R_{\rm h}$  to represent the sum as given by Equation 3.11

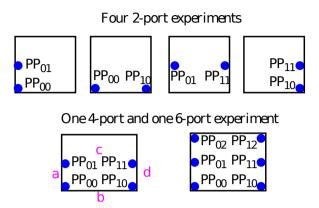

Figure 3.10: Power schemes investigated

To demonstrate that these equations provide a better estimate of the  $R_h$  resistances over those derived using KVL, which are

$$V_a = I_{a1}(R_{pvb} + R_{ha}) + I_{sa} \cdot R_{va}$$

(3.12)

$$V_b = I_{b0}(R_{pva} + R_{hb}) + I_{sb} \cdot R_{vb}, \tag{3.13}$$

we conducted a sequence of experiments using a variety of PP configurations. The criteria that we used to determine the best analytical form is based on the consistency of the results across the different PP configurations. Intuitively, the values computed for the six horizontal resistances should remain consistent, independent of the power-up scheme. However, this is not the case for  $R_{\rm ha}$  and  $R_{\rm hb}$  if Equations 3.12 and 3.13 are used.

We computed the values of the six resistances using hardware data from each of the PP configurations shown in Figure 3.10. The upper portion of the figure shows four 2-port experiments while the bottom portion shows a 4-port and a 6-port experiment. For each of the four 2-port experiments, the three tests described in Section 3.3 were applied using a pair of RMCs located underneath the labeled PPs. These twelve tests were also applied to the 4-port and 6-port configurations.

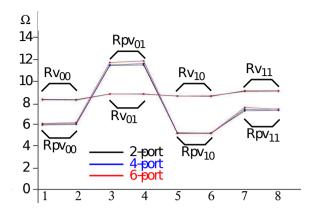

Figure 3.11:  $R_{pv}$  and  $R_{v}$  results under different power-up configurations