# Lehigh University Lehigh Preserve

Theses and Dissertations

2011

# Coding for storage: disk arrays, flash memory, and distributed storage networks

Nattakan Puttarak Lehigh University

Follow this and additional works at: http://preserve.lehigh.edu/etd

#### Recommended Citation

Puttarak, Nattakan, "Coding for storage: disk arrays, flash memory, and distributed storage networks" (2011). *Theses and Dissertations*. Paper 1144.

This Dissertation is brought to you for free and open access by Lehigh Preserve. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of Lehigh Preserve. For more information, please contact preserve@lehigh.edu.

# CODING FOR STORAGE: DISK ARRAYS, FLASH MEMORY AND DISTRIBUTED STORAGE NETWORKS

by Nattakan Puttarak

A Dissertation

Presented to the Graduate Committee of Lehigh University in Candidacy for the Degree of Doctor of Philosophy in Electrical Engineering

Lehigh University September 2011 © Copyright 2011 by Nattakan Puttarak All Rights Reserved

| (Date)      |                                                     |

|-------------|-----------------------------------------------------|

|             |                                                     |

|             | Professor Tiffany Jing Li<br>(Dissertation Advisor) |

| (Accepted I | Date)                                               |

|             | Professor Tiffany Jing Li<br>(Dissertation Advisor) |

|             | Professor Shalinee Kishore                          |

|             | Professor Meghanad D. Wagh                          |

To my parents, my sister, my brother-in-law, and my niece.

#### Acknowledgements

This PhD work would not have been completed without a great deal of support and guidance from a number of people. In order to show my gratitude towards these people, I would like to dedicate this page to them.

First of all, I would like to deeply thank the most important person that made this dissertation possible, my advisor, Professor Tiffany Jing Li, for giving me the opportunity to join this research group. With her constant guidance, expertise, energy and inspiration, she has been my best mentor, and advisor. I have developed not only my technical skills, attitudes and knowledge, but also unconsciously learned how to attain an optimistic perspective of life from her. This work would not have been possible without her.

I would also like to express my gratitude to the rest of my committee members: Professor Shalinee Kishore, Professor Meghanad D. Wagh and Professor Liang Cheng who have provided valuable feedback, direction and support in my research.

I would like to thank Thai Government and the King Mongkut's Institute of Technology Lardkrabang (KMITL) for the scholarship which has supported me throughout the entire graduate program in US.

I would not have gone through my PhD experience without the constant interaction with my fellow lab colleagues and friends. Many thanks to Dr. Peiyu Tan, Dr. Xingkai Bao, Dr. Kai Xie, Phisan Kaewprapha, Dr. Vitchanetra

Hongpinyo, and Yang Liu for the invaluable discussion, great support, unconditional help, and friendship.

Last but not least, I would like to dedicate this dissertation to my family. I am so grateful to my parents, sister, brother-in-law and my niece whom I could not have asked for anything more, for their support and encouragement and for always being there for me when I am facing hardships. I will not be the person I am today without them.

## Contents

| $\mathbf{A}$ | ckno  | wledge  | ements                                                | vii |

|--------------|-------|---------|-------------------------------------------------------|-----|

| $\mathbf{A}$ | bstra | ıct     |                                                       | 1   |

| 1            | Inti  | roducti | ion                                                   | 3   |

|              | 1.1   | Disk I  | Orives and The Distributed Data Storages              | 6   |

|              |       | 1.1.1   | Notations and Definitions of Disk Arrays              | 8   |

|              |       | 1.1.2   | Backgrounds of the RAID levels and erasure-correcting |     |

|              |       |         | codes                                                 | 9   |

|              | 1.2   | Codin   | g Theory for Data Storages                            | 13  |

|              |       | 1.2.1   | Reed-Solomon (RS) Codes                               | 15  |

|              |       | 1.2.2   | LDPC Codes                                            | 17  |

|              |       | 1.2.3   | Parity Array Codes                                    | 19  |

|              | 1.3   | Flash   | Drives                                                | 25  |

|              |       | 1.3.1   | NOR vs. NAND Flash Memory                             | 27  |

|              | 1.4   | Outlin  | ne                                                    | 30  |

| 2            | MD    | S code  | es for disk arrays                                    | 33  |

|              | 2.1   | Introd  | luction                                               | 33  |

|              |       | 2.1.1   | MDS Codes and Their Properties                        | 34  |

|              |       | 2.1.2   | Literature Reviews                                    | 35  |

|              | 2.2   | CGR     | Codes                                                 | 37  |

|              |       | 2.2.1   | Code Construction and Algorithms                      | 37  |

|   | 2.3 | Proofs   | of CGR Array Codes                                                                      | 44  |

|---|-----|----------|-----------------------------------------------------------------------------------------|-----|

|   |     | 2.3.1    | Proofs of an MDS Property of CGR Codes                                                  | 44  |

|   |     | 2.3.2    | Perfect One-Factorization (P1F) as the Inter-Ring Edges                                 |     |

|   |     |          | Shifting Index Assigning Algorithm                                                      | 52  |

|   | 2.4 | Dual (   | CGR Codes                                                                               | 58  |

|   |     | 2.4.1    | Proofs of Duality of CGR Codes                                                          | 59  |

|   | 2.5 | Conne    | ction to B-Codes                                                                        | 63  |

|   |     | 2.5.1    | Discussion                                                                              | 67  |

|   | 2.6 | Low-D    | ensity MDS Array Codes                                                                  | 69  |

|   |     | 2.6.1    | Low-Density CGR Codes                                                                   | 71  |

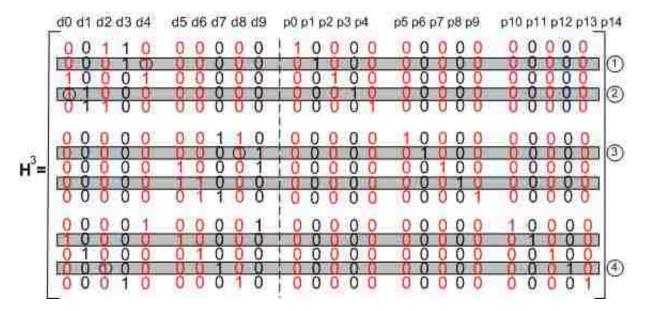

|   |     | 2.6.2    | Data Recovery via Parity-Check Matrix                                                   | 76  |

| 3 | Nes | ted cod  | des with Hierarchical protection for distributed stor-                                  | -   |

|   | age | netwo    | rks                                                                                     | 81  |

|   | 3.1 | Introd   | $\operatorname{uction}  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots  \ldots$ | 82  |

|   |     | 3.1.1    | Background of Luby Transform (LT) Codes                                                 | 84  |

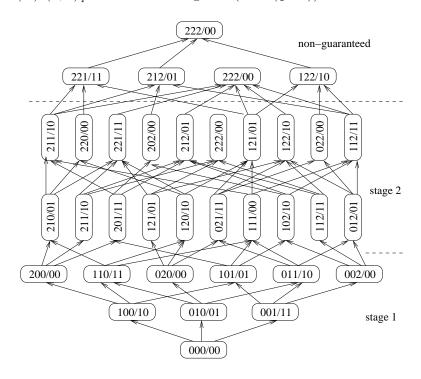

|   | 3.2 | The M    | DS-LT Nested Codes                                                                      | 87  |

|   |     | 3.2.1    | The Code Construction                                                                   | 88  |

|   |     | 3.2.2    | The Consideration of Hierarchical Nested Erasure Codes                                  | 92  |

|   | 3.3 | The H    | orizontal-Vertical Single Parity Check (HVSPC) Codes .                                  | 99  |

|   |     | 3.3.1    | Simulation Results and Analysis                                                         | 101 |

|   | 3.4 | Summa    | ary                                                                                     | 104 |

| 4 | Cod | ling for | r flash memory                                                                          | 107 |

|   | 4.1 | Introd   | $\operatorname{uction}$                                                                 | 107 |

|   |     | 4.1.1    | How Flash Memories work?                                                                | 108 |

|   |     | 4.1.2    | Literature Reviews                                                                      | 110 |

|   |     | 4.1.3    | The Number of Writes Consideration                                                      | 115 |

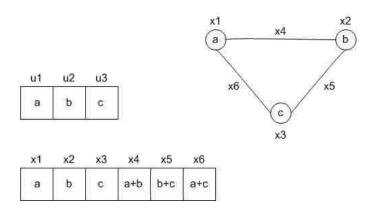

|   | 4.2 | The W    | Vord-write Efficient and Bit-write Efficient (WEBE) Codes                               | 116 |

|   |     | 4.2.1    | Problem Formulation and New Concepts                                                    | 118 |

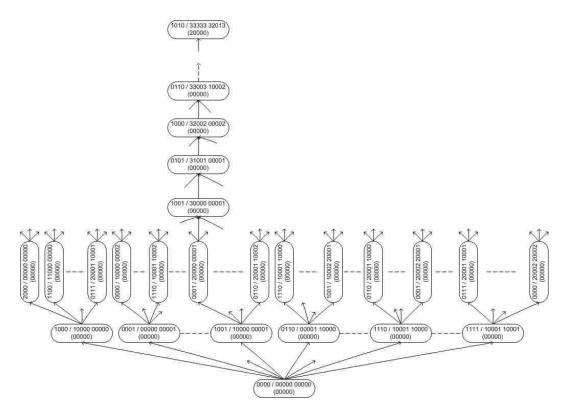

|   |     | 422      | Design WEBE Codes for $k=2$                                                             | 122 |

|    |       | 4.2.3  | Design WEBE Codes for General $k$ | 130 |

|----|-------|--------|-----------------------------------|-----|

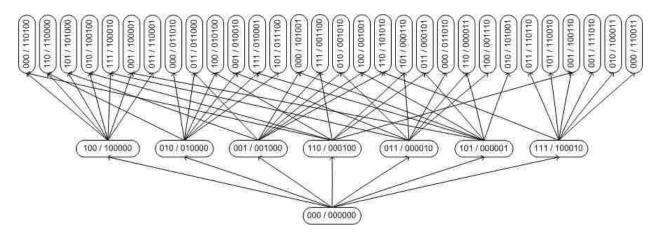

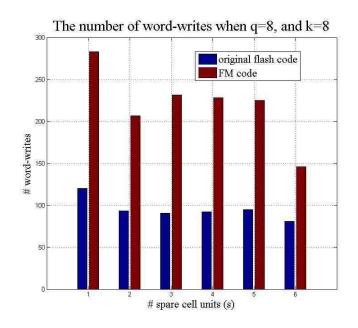

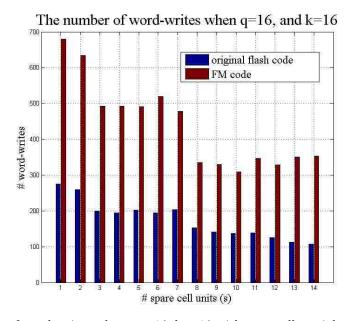

|    | 4.3   | Flash  | Marker (FM) Codes                 | 137 |

|    |       | 4.3.1  | FM Code Construction              | 139 |

|    |       | 4.3.2  | Simulation Results                | 145 |

|    |       | 4.3.3  | Discussion                        | 148 |

|    | 4.4   | Conclu | ısion                             | 150 |

| 5  | Sun   | nmary  | and Future Works                  | 151 |

|    | 5.1   | Data I | Disks                             | 152 |

|    | 5.2   | The D  | istributed Storage Networks       | 152 |

|    | 5.3   | Flash  | Memories                          | 153 |

| Bi | bliog | raphy  |                                   | 155 |

## List of Tables

| 1.1 | Strengths and weaknesses of standard RAID levels      | 14 |

|-----|-------------------------------------------------------|----|

| 1.2 | An example of a simple EVENODD code                   | 20 |

| 1.3 | An $(5 \times 5)$ array of X-code                     | 21 |

| 1.4 | An $(4 \times 6)$ array of RDP code                   | 22 |

| 1.5 | An $(4 \times 8)$ array of STAR code                  | 23 |

| 1.6 | Erasure codes for disk storage arrays                 | 25 |

| 1.7 | The properties and performances of NOR and NAND flash |    |

|     | memories                                              | 30 |

| 2.1 | $B_0$                                                 | 50 |

| 2.2 | $B_1$                                                 | 51 |

| 2.3 | $B_2$                                                 | 52 |

| 2.4 | $B_3$                                                 | 53 |

| 2.5 | $B_4$                                                 | 54 |

| 2.6 | $B_5$                                                 | 55 |

| 2.7 | $B_6$                                                 | 56 |

| 2.8 | Update complexity and decoding complexity             | 69 |

| 2.9 | The array $CGR(K_2, C_5)$ code                        | 73 |

# List of Figures

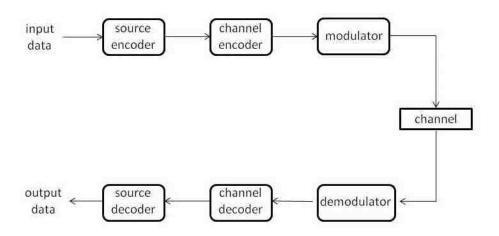

| 1.1  | The wireless communication system model                           | 4  |

|------|-------------------------------------------------------------------|----|

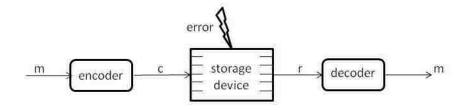

| 1.2  | The data read/write model                                         | 5  |

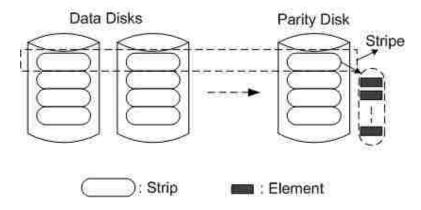

| 1.3  | The illustration of terminology in an horizontal erasure code .   | 8  |

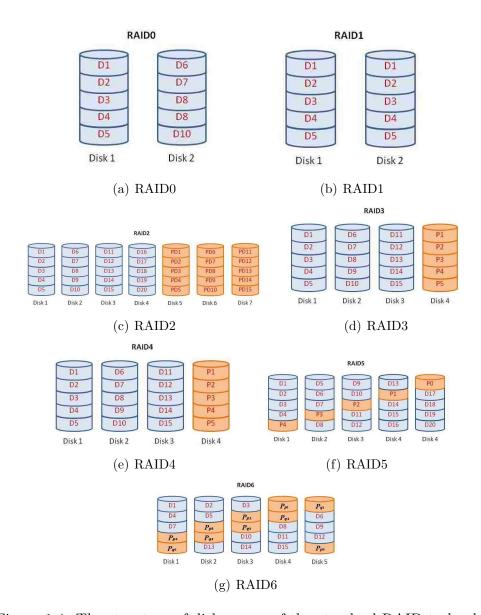

| 1.4  | Optional caption for list of figures                              | 11 |

| 1.5  | The Reed Solomon (RS) codes for disk arrays                       | 16 |

| 1.6  | An example of a simple LDPC code with $n=3, m=2$                  | 17 |

| 1.7  | The $HoVer_{v,h}^t[r,c]$ codes                                    | 24 |

| 1.8  | MOS memory tree                                                   | 26 |

| 2.1  | CGR graphs constructed from base graphs. Left: base graphs        |    |

|      | $K_2$ and $K_4$ ; right: resultant CGR graphs $CGR(K_2, C_5)$ and |    |

|      | $CGR(K_4, C_7)$                                                   | 38 |

| 2.2  | Labeling of 3-regular $CGR(K_2,C_5)$                              | 40 |

| 2.3  | Complete graph $K_6$                                              | 43 |

| 2.4  | A ring of complete graph of $(K_4, C_7)$                          | 48 |

| 2.5  | A Hamiltonian cycle formed by 2 survivors of $(K_4, C_7)$         | 57 |

| 2.6  | Complete graph $K_4$ after trimming $K_6$                         | 57 |

| 2.7  | Graph representing a row in $H$                                   | 62 |

| 2.8  | Graph representing a row in $H$ of the dual code                  | 63 |

| 2.9  | A super graph represents a $CGR(K_4, C_7)$ code, where each super |    |

|      | node has 7 nodes and there are 7 edges represented in each inter- |    |

|      | edge                                                              | 64 |

| 2.10 | (a) Structure of CGR code. (b) Structure of $B_{2n+1}$ code       | 68 |

| 2.11 | Optional caption for list of figures                                                                    | 74   |  |

|------|---------------------------------------------------------------------------------------------------------|------|--|

| 2.12 | A row-decoding process of the $H$ matrix of $CGR(K_2, C_5)$ code                                        | 78   |  |

| 2.13 | A column-decoding process of the $H$ matrix of $CGR(K_2, C_5)$ code                                     |      |  |

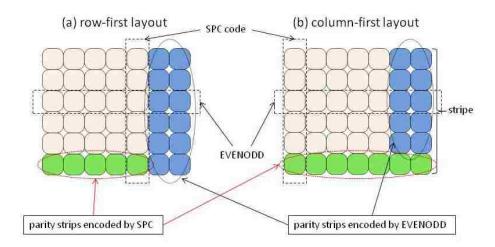

| 3.1  | Two types of stripe layouts of $\operatorname{GRID}(\operatorname{SPC},\operatorname{EVENODD})$ codes . | 83   |  |

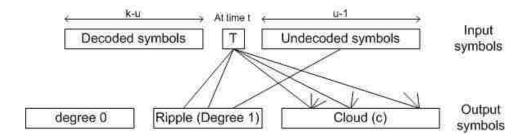

| 3.2  | The decoding process when there are $u-1$ input symbols are undecoded                                   | 86   |  |

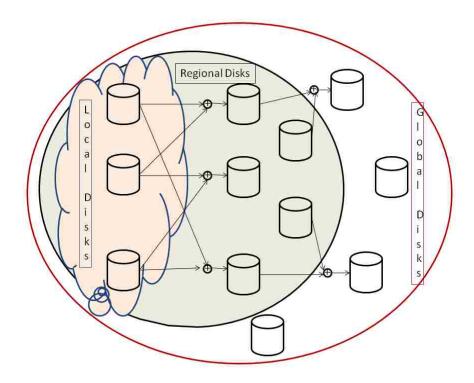

| 3.3  | The basic structure of nested codes with Hierarchical protection for distributed storage networks       | 89   |  |

| 3.4  | Code array structure where $M$ global disks are all parity disks constructed from LT codes              | 92   |  |

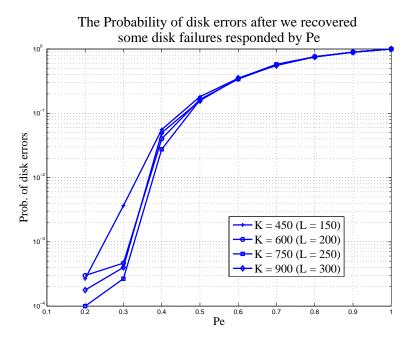

| 3.5  | The probability of residual disk errors versus the raw disk failure rate $(P_e)$                        | 93   |  |

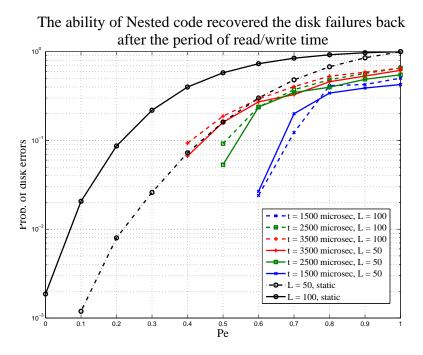

| 3.6  | The ability of the hierarchy nested erasure code to recover failed disks in time period $t$             | 94   |  |

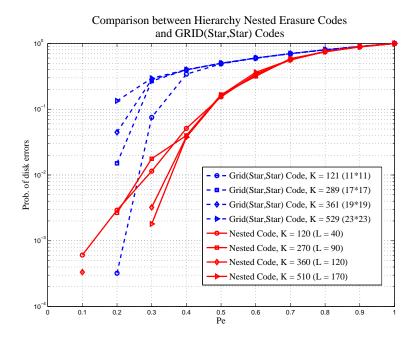

| 3.7  | Comparisons the probability of disk errors between Grid codes and hierarchy nested erasure codes        | 95   |  |

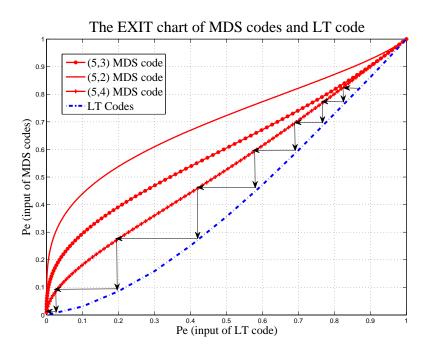

| 3.8  | The EXIT chart of LT codes and MDS codes                                                                | 97   |  |

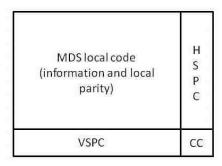

| 3.9  | The array structure                                                                                     | 100  |  |

| 3.10 | The organization of MDS local code in the array of size $x \times y$                                    | 100  |  |

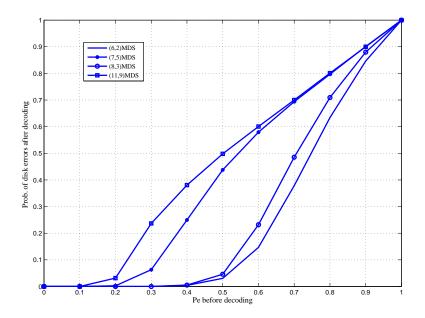

| 3.11 | The probability of disk failures after applying the layered coding scheme.                              | 101  |  |

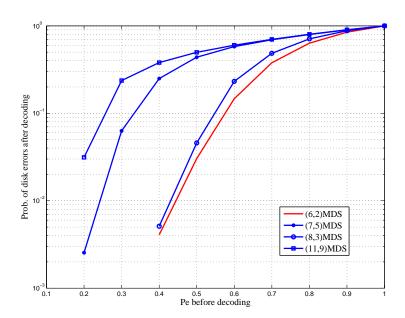

| 3.12 | The probability (in log-scale) of disk failures after applying the layered coding scheme                | 102  |  |

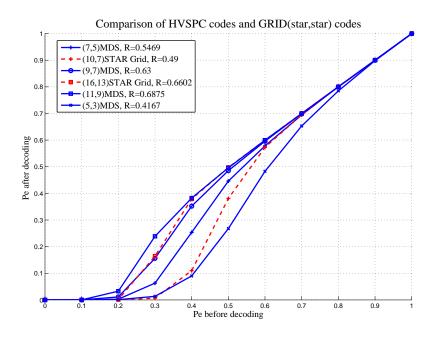

| 3.13 | The comparison of HVSPC codes and GRID(STAR,STAR) codes                                                 | s103 |  |

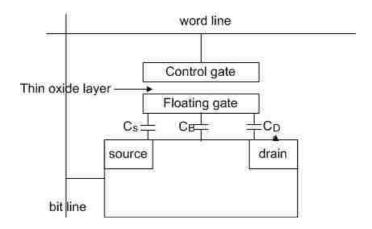

| 4.1  | Schematic cross section of flash memory                                                                 | 109  |  |

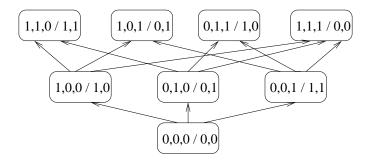

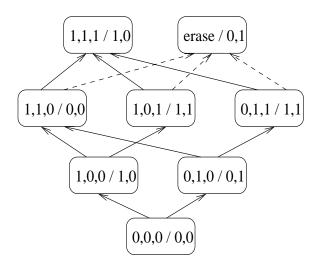

| 4.2  | A $(3,2)_2$ flash code that achieves the maximum word-write efficiency 2                                | 121  |  |

| 4.3  | A $(3,2)_2$ flash code (floating code in [46]) that achieves the      |     |

|------|-----------------------------------------------------------------------|-----|

|      | maximum bit-write efficiency, but not the maximum word-write          |     |

|      | efficiency                                                            | 122 |

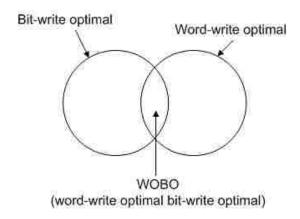

| 4.4  | Relation between bit-write optimality and word-write optimality.      | 123 |

| 4.5  | The proposed $(3,2)_q$ flash code                                     | 127 |

| 4.6  | An example of a simple $(6,3)_q$ WEBE code                            | 134 |

| 4.7  | A $(6,3)_2$ WEBE code that achieve an asymptotically optimal          |     |

|      | word-writes                                                           | 134 |

| 4.8  | One example of layout structures of $(n,k)_q$ WEBE code               | 138 |

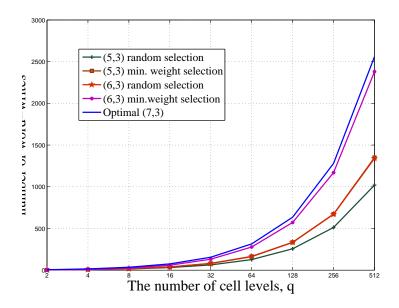

| 4.9  | The number of word-writes $(5,3)_q$ and $(6,3)_q$ WEBE codes for      |     |

|      | the various value of $q$                                              | 138 |

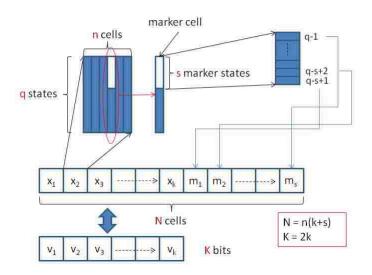

| 4.10 | The relation of s marker states, s spare cells of $(N, K, s)_q$ FM    |     |

|      | code                                                                  | 142 |

| 4.11 | An example of cell-state updates of $(15,4,1)_4$ FM code shown        |     |

|      | in $Example\ 6$ (all cells shown in the parentheses are spare cells). | 146 |

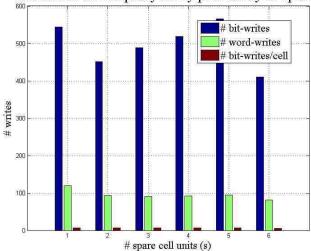

| 4.12 | The number of bit-writes of $(N, K, s)_q$ FM codes when the num-      |     |

|      | ber of spare-cell units $(s)$ is increased                            | 147 |

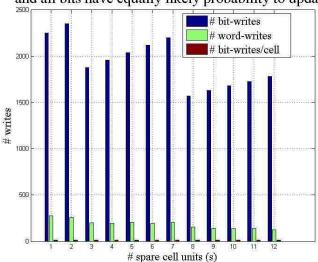

| 4.13 | The number of word-writes of $(N, K, s)_q$ FM codes when the          |     |

|      | number of spare-cell units $(s)$ is increased                         | 149 |

|      |                                                                       |     |

#### Abstract

The explosive demand for digital data storage with higher areal density, larger storage capacity, higher reliability and fault tolerance, easier accessibility, cheaper management and better scalability, poses tremendous challenge on the storage industry. Researchers and practitioners have been working hard to tackle the problem in various aspects from system architecture to signal processing, coding, control and storage media. This doctoral research explores emerging coding technologies that will potentially lead to new and better storage systems to meet some of the above demanding goals. In this dissertation, we consider three important storage systems: hard disk arrays consisting of few disks, distributed storage networks consisting of hundreds of and thousands of disks, and flash memories. However, the coding for disk storages and the one for flash memories are different in terms of purposes, functionality, and technology.

In the case of disk arrays, we propose to develop new erasure codes to achieve optimal spatial efficiency while requiring only minimal encoding and decoding complexity. Specifically, we demonstrate the idea of constructing class of nested graphs, termed *complete-graph-of-ring (CGR) graphs*, and use them to form a class of optimal array codes, termed *CGR codes*. CGR codes are maximum distance separable (MDS), and hence achieve the best space efficiency. Systematic and concrete constructing methods for CGR codes and

their dual codes are developed. It is shown that these codes not only deliver optimal erasure protection with low complexity, but they also provide a rich array of code rates and code lengths, many of which are suitable for storage systems. The MDS array codes are also presented as the systematic low-density (sparse) array codes shown by the generator matrix and parity-check matrix.

For large distributed storage networks, we propose to develop layered coding strategies to achieve good erasure protection, without causing unbearable communication overhead. By dividing the entire system in layered clusters and designing appropriate erasure coding for each layer, we show that a good trade-off between protection capability, redundancy overhead, communication overhead, and computational complexity can be achieved. Additionally, the proposed strategy also provides the flexibility and scalability much need for large systems.

In the case of flash memories, we propose to develop new coding schemes to best map cell states to data bits and vice versa. Our goal is to maximize the writing time in each cell state before a block-erased process is required. The existing strategies can at the best achieve the "conventional bound" under the assumption that any one bit update will inevitably cause a cell state rises. We demonstrate an idea which allows some two-bit updates to be represented by only one cell state rises (rather than two cell states rise), a direction that people have not thought before. We also introduce the concept of word-write efficiency and optimality, and propose new classes of "word-efficient bit-efficient (WEBE) codes" and "word-optimal bit-optimal (WOBO) codes." To achieve flexibility and adaptivity, and further improve the lifespan of flash memories, we introduce the "flash marker (FM) codes," which reserve a set of cells for the most active bits in order to avoid a block erasure. From all of the above, we have beaten the conventional performance bound and opened new possibilities for data representation in flash memories.

### Chapter 1

#### Introduction

We live in a "YouTube" age, in which an enormous amount of digital information is created every day. The explosive surge of data poses a serious demand for cheaper, better, and more reliable data storage that is portable (e.g. flash memory) and/or accessible anywhere and anytime (e.g. storage networks). Today's data storage industry is undergoing a paradigm shift, from a single prevailing media (e.g. magnetic hard disks) to a rich variety of media (e.d. magnetic hard disks, CD, DVD, and solid state storage), and from individual disks or small arrays of disks to very large storage networks comprising hundreds or thousands of (distributed) storage nodes. What this implies in research is the need to invent new storage technologies and improve existing ones.

The demand for massive storage comes with not just the requirement for a high storage capacity, but also for a high density (i.e. small space), fast accessibility, better reliability and fault tolerance, easy management, and good scalability. In the end, the efficiency of the storage technology is also measured by the per-unit (dollar) cost to store and maintain digital data, and every effort is made to minimize this cost while maintaining a high availability and reliability of the system.

Compared to the wireless communication system model as shown in Fig. 1.1, instead of transmitting encoded symbols/information from source to receiver via various communication channels, in case of data storage, we read/write (store) information in the same disk for the numerous times. As shown in Fig. 1.2, the error on a storage device might be sporadic or bursty. In the latter case, the error source may be the classical scratch, the error from read/write failure, or controller [2].

Figure 1.1: The wireless communication system model

This dissertation is centered around two types of storage devices: hard disk drives, which are and will remain the dominant large-volume data storage devices for the foreseeable near future, and flash drives (or flash memories), which are the dominant portable storage device that is gaining an increasingly large market for small to medium volumes. The "Coding Theory" is commonly called upon to improve and achieve the ability to efficiently store, access and

Figure 1.2: The data read/write model

transfer information in data disks and flash memories in a reliable way.

Since today's massive data can not be handled by only a single hard disk, but rather must rely on the collection of multiple disks, we consider two levels of hard disk collections: in the small scale, we consider disk arrays, and in the large scale, we consider data centers (or distributed data storage systems) consisting of hundreds of or thousands of storage nodes, each of which comprising an array of disks. To achieve reliable and fast-recovery data storage that is essential to support data availability, persistence, and integrity, we exploit advanced erasure coding technology. Array codes—a class of linear erasure codes play an important role in storage systems, due to their simplicity such that the encoding and decoding procedures are performed only by exclusive-OR (XOR) operations. Specifically, (array) codes that achieve the maximal spacial efficiency or the Singleton bound are called maximum distance separable (MDS) (array) codes. We propose to search for new directions and new ways to construct MDS array codes. We will look specifically into constructions relating to graph and set theory. Our research goal is to achieve MDS with rich choices of code lengths and rates, and with minimal encoding and decoding complexity possible.

Flash drives are a young technology but potentially very promising. They

have desirable properties including high data density, fast reading time, physical robustness (can withstand drops) and small sizes. Hence, they have found wide application in portable devices such as MP3 player, mobile phones, digital cameras, or computer laptops. Compared to hard disks and optical disks where the media provide two distinctive states to represent (i.e. store) 0s and 1s, flash memories have many levels of cell states that can be used to represent digital data. The state can be easily increased by injecting an electron into the cell level, but to decrease the cell state level one must erase the entire block and reprogram all the cells, a procedure called black erasure which is both costly and slow [45]. Hence, in order to achieve the full efficiency of flash memories, the proposed research targets developing strategies to maximize the limited life cycle of flash memories, namely the life span, or to maximize the number of writing before the erasing process is needed. Here we will investigate new ideas and ways to efficiently map information bits into cell states and to represent the writing levels when a charge is added (written) into a flash memory.

# 1.1 Disk Drives and The Distributed Data Storages

Since a huge amount of information is stored and transferred among many storage and data centers, data loss due to disk failure (i.e. erasure) is a major issue that may affect the reliability of this system. Reliability and performance of storage systems are a big concern, and are an important aspect of the reliability and performance of the overall cyber infrastructure. A recent trend in storage is that, instead of using a very expensive, high performance, and large capacity disk storage to store voluminous data, a group of several cheaper, low-density and lower capacity disks are combined into one logical unit called

a "disk array". Disk arrays provide a cost-effective means to mitigate the problem of data loss, since they contain multiple redundant disk drives to address the fault tolerance. There are several key aspects in this multiple disk storage mechanism as mentioned in the following.

- Reliability: fault tolerance and robustness, which must be built into the system to recover/tolerate disk failures. If there is a failure, the system is not reliable.

- Availability: the ability for the system to work in times of individual disk failure. When a system can continue to work even in the presence of a failure of one or more disks, the system is called to be available.

- Scalability: the ability to gracefully support a system when a data center grows in size or when two data centers merge.

- Flexibility: the ability to be arranged or configured in different ways to satisfy different system requirements.

- Capacity: the ability to handle thousand of disks within the same network to collectively provide massive storage capability.

- Speed: time efficiency in accessing required information. The faster the access speed, the better the delay time should be minimized as much as possible.

The well-known disk arrays used in industry are the Reliable/Redundant Arrays of Inexpensive/Independent Disks (RAID) system was proposed by Patterson, et al. in 1988 [17]. RAID systems can offer fault tolerance and a higher throughput level than a single hard drive. In addition, RAID provides a combination of outstanding data availability, highly scalable performance, high capacity, and recovery.

#### 1.1.1 Notations and Definitions of Disk Arrays

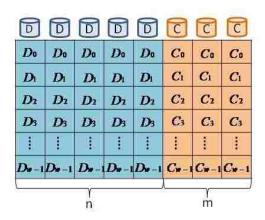

For clarity and consistency of the use of common terms in storage and erasure codes, we express and state all the definitions here to avoid confusion. Following the convention in [9], [11], and [39], the terminology used throughout this dissertation is represented in Fig. 1.3, which shows a horizontal erasure code.

Figure 1.3: The illustration of terminology in an horizontal erasure code

Data is a chunk of bytes or blocks containing unmodified user data, while parity is a chunk of bytes or blocks that hold the redundancy generated from user data (by erasure code, typically XOR operations). The element is a unit of data or parity which corresponds to a bit within a code symbol. The stripe is a set of data or parity elements that can be referred as a codeword in the coding theory terminology. In addition, a set of elements in a stripe stored in the same disk is called a strip, which is known as a code symbol. The disk array system is a collection of a "pile" of multiple stacks that fills the disk's capacity. Note that a stack is a collection of many stripes. A horizontal code is an array code in which data and parity elements are in the same stripe but in the separate strip as shown in Fig.1.3. A vertical code is an array code in which each strip contains both data and parity within a stripe, or there are both data and parity strips stored in one disk.

# 1.1.2 Backgrounds of the RAID levels and erasure-correcting codes

RAID or the Reliable/Redundant Arrays of Inexpensive/Independent Disk system is now an industry standard. It is a popular classification for disk arrays [32] which was first introduced as RAID0 in the late 1980s. Since then there are many versions of RAID using techniques based on replication and erasure coding that have been introduced to allow the recovery of disk failures and to provide high reliability. Instead of providing only a single disk, RAIDs employ an array of independent disks, accessed in parallel to collectively achieve a high throughput.

- RAID0: This does not provide redundancy or any fault tolerance, but only improve performance by providing additional storage and maximizing the access speed. The technique used in this RAID0 is solely on striping for load balancing purposes. The probability of disk failures increases when the number of disk drives increases.

- RAID1: Data is written and stored in the redundant disk known as mirroring disk. Whenever data is written into one disk, the same data is also written into a redundant one, so that it uses twice as many disks as a non-redundant disk array. This offers the benefit of reliability at the cost of doubling the storage space.

- RAID2: This RAID can tolerate one erasure using a Hamming code.

Three parity disks are required to protect four data disks. So, its redundancy is one less than mirroring.

- RAID3: This RAID employs single parity check coding scheme that can recover 1 disk failure. However, in this level data is conceptually interleaved bit-wise over the data disks and a single parity disk is added

to tolerate any single disk failure. From Fig.1.4(d), the parity disk stores the XORing data from all data disks; for example,  $P1 = D1 \oplus D6 \oplus D11$ .

- RAID4: This can handle one erasure by using a block-interleaved parity disk array which is similar to the bit-interleaved parity disk array but data is interleaved in blocks rather than in bits. So, in Fig.1.4(e) each data D and parity P is represented in block. The size of these blocks is called the striping unit. Parity is easily computed by XORing the new data for each disk. It is similar to RAID3 in that P1 = D1⊕D6⊕D11, but since it is in a larger size, this parity disk may easily become a bottleneck.

- RAID5: The fault tolerance is covered by the capacity of one disk among N disks, but this level reduces the problem of a bottleneck in RAID4 by using the block-interleaved distributed parity disk array. The advantage of this method is that data are distributed over all of the disks rather than over all but one, so it allows all disks to participate in read/write operations. As shown in Fig.1.4(f), a parity disk P0 is computed by XORing data over stripe units D1, D5, D9, and D13. This property also reduces disk conflicts in the large requests. Even when a single disk fails, data can still be recovered from the parity information that reside in the rest of the disks.

- RAID6: This RAID level provides fault tolerance up to two erasures by providing P + Q redundancy. It is different from RAID5 as it has two additional disks to recover the loss of two disks. This RAID level utilizes several different types of erasure coding techniques such as Reed-Solomon (RS) code, EVENODD code, or X-code. However, each code has its own limitation which will be discussed later.

To summarize, RAID0 solely provides an organization of all stripes on the disks in order to balance load for performance purpose. RAID1 can protect one

Figure 1.4: The structure of disk arrays of the standard RAID technology

erasure by using a "mirroring" technique, whereas RAID2, RAID3, and RAID4 can also protect one erasure but using various techniques of coding. RAID6 can tolerate two erasures by providing double parity disks constructed from special designed parity codes such as EVENODD code, or Reed Solomon (RS) code. To achieve a highly available and reliable RAID system, the technique of bitwise parity checking is heavily exploited to correct errors and tolerant disk failures.

RAID performance is evaluated from the update complexity and the number of check disk overheads [33]. The *update complexity* refers to the number of XOR operations required for encoding and decoding if there is at least one disk failure. Additionally, the *encoding/decoding complexity* is also used to measure the complexity of the code construction by monitoring the number of XOR operations the code uses when encoding and decoding.

The Markov chain reliability models are also used to estimate the mean time to data loss (MTTDL). To compute the MTTDL, two important parameters: (1) the mean time to failure (MTTF), and (2) the mean time to repair (MTTR) which is the expected time to recover a system from a failure, are used based on the reliability model [32]. Let the disk failure rate be  $\lambda$  and the repair rate be  $\mu$ , so that  $MTTR=1/\mu$  and  $MTTF=1/\lambda$ . For example, in the single error-correcting RAID, where there are  $n_G$  disk-array groups each with G data disks and 1 check disk, we can compute the MTTDL as follows [34]:

$$MTTDL = \frac{(MTTF_{disk})^2}{n_G G(G+1)MTTR_{disk}}$$

(1.1)

The strengths and weaknesses of the afore-mentioned standard RAID levels are shown in Table 1.1. There are special RAIDs called "Nested (Hybrid)

RAIDs" [18], which provide redundancy by combining two or more of the standard levels of RAID. For example, RAID 0+1 (or RAID 01) is used for both replicating and sharing data among disks by building from many chunks of RAID0 and then mirroring (RAID1), and RAID 1+0 (or RAID 10) provides fault-tolerance by creating a striped set from a series of mirrored drives, but it still has the same cost problem as RAID1. The difference between RAID 01 and RAID 10 is the location of RAID system: RAID 01 is a mirror of stripes while RAID 10 is a stripe of mirrors [18]. Moreover, the RAID parity (or RAID s) provides an error-protection scheme called "parity" by simple XOR operations. Although, this special RAIDs may better fault-tolerance than the standard ones, they also increase the complexity for implementation.

#### 1.2 Coding Theory for Data Storages

This section will investigate the practical and popular existing erasure codes in disk storages for tolerating disk erasures/failures. An erasure code is designed to recover the erasures (i.e. bits loss or erased) rather than to correct errors (i.e. bits altered or flipped). The key property of an (n, k) erasure code, which encodes k parts of source data to a total of n parts of encoded data and which guarantees to correct e erasures, is that the original k parts of data can be reconstructed from any (n-e) parts of encoded data. The number of erasures that can be recovered is upper bounded by  $e \leq d_{min} - 1$ , where  $d_{min}$  is the minimum distance of the code.

The optimal (n, k) erasure codes have the property that any k out of n coded bits/data are sufficient to recover the original message. An optimal erasure code is known as a maximum distance separable (MDS) code, since its minimum distance is  $d_{min} = n - k + 1$ , the largest possible distance promised by the theory. In this work, we study 3 types of erasure codes that are relevant to

| RAID Levels | Strengths                                          | Weaknesses                                              |

|-------------|----------------------------------------------------|---------------------------------------------------------|

| RAID0       | Highest performance                                | No data protection, any disk fails results in data loss |

| RAID1       | Very high performance and                          | High redundancy cost over-                              |

|             | data protection, very mini-                        | head, wasteful in storage ca-                           |

|             | mal penalty on write perfor-                       | pacity                                                  |

| DAIDO       | mance                                              | N. C. C.                                                |

| RAID2       | Previously used for RAM error environments correc- | No practical use; Same performance can be achieved      |

|             | tion (known as a Hamming                           | by RAID3 at lower cost                                  |

|             | Code ) and in disk drives be-                      | by ItAID5 at lower cost                                 |

|             | fore the use of embedded er-                       |                                                         |

|             | ror correction                                     |                                                         |

| RAID3       | Excellent performance for                          | Not well-suited for                                     |

|             | large, sequential data re-                         | transaction-oriented net-                               |

|             | quests                                             | work applications; Single                               |

|             |                                                    | parity drive does not sup-                              |

|             |                                                    | port multiple, simultaneous                             |

| DAID4       | D + + : :                                          | read and write requests                                 |

| RAID4       | Data striping supports mul-                        | Write requests suffer from same single parity-drive     |

|             | tiple simultaneous read requests                   | bottleneck as RAID3 and                                 |

|             | questis                                            | RAID5 offers equal data                                 |

|             |                                                    | protection and better                                   |

|             |                                                    | performance at same cost                                |

| RAID5       | Best cost/performance                              | Write performance is slower                             |

|             | for transaction-oriented                           | than RAID0 or RAID1                                     |

|             | networks; Very high per-                           |                                                         |

|             | formance, very high data                           |                                                         |

|             | protection; Supports multi-                        |                                                         |

|             | ple simultaneous reads and                         |                                                         |

|             | writes; Can also be opti-                          |                                                         |

|             | mized for large, sequential requests               |                                                         |

| RAID6       | Allows up to two hard                              | Require a minimum of 5                                  |

| 1011100     | drives to crash, high avail-                       | drives, servers with large ca-                          |

|             | ability solutions                                  | pacity requirements                                     |

|             | ·                                                  | 1 - 0 -                                                 |

Table 1.1: Strengths and weaknesses of standard RAID levels  $\,$

data storage networks which are Reed-Solomon (RS) codes, low-density parity check (LDPC) codes, and array codes.

#### 1.2.1 Reed-Solomon (RS) Codes

Reed-Solomon (RS) codes are the most well-known and the most used MDS codes in communications. They achieve the Singleton bound with equality,  $d_{min} \leq n - k + 1$ , and are therefore MDS. RS codes were first introduced in 1960 by Reed and Solomon. This code construction is based on Galois Field  $(GF(2^W))$  operation for W is positive integer. RS codes provide a wide range of code rates from 0 to 1. However, Galois Field arithmetic is rather complex, especially for large fields. RS codes are generally considered not very scalable.

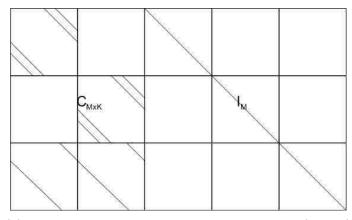

A simplified construction [19] of RS codes for data storage is described in the form of Vandermonde matrices assuming there are m data symbols and e erasures (where  $m + e \le 1 + 2^n$ ). The length-(m + e) codeword is computed by multiplying the length-m vector of the data by an m-by-(m + e) coding matrix. In addition, this code can be made systematic by simple row reduction of the coding matrix, which diagonalizes the initial m-by-m portion of the matrix. So, the encoding matrix can be constructed by an m-by-m identity matrix followed by an m-by-e checksum computation matrix. Note that a Vandermonde matrix is a type of matrix that has a geometric progression in each row as shown below.

$$\begin{bmatrix} 1 & \alpha_1 & \alpha_1^2 & \cdots & \alpha_1^{n-1} \\ 1 & \alpha_2 & \alpha_2^2 & \cdots & \alpha_2^{n-1} \\ 1 & \alpha_3 & \alpha_3^2 & \cdots & \alpha_3^{n-1} \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ 1 & \alpha_m & \alpha_m^2 & \cdots & \alpha_m^{n-1} \end{bmatrix}$$

Further, an Vandermonde matrix has the property that any square submatrix has full rank and is invertible.

Figure 1.5: The Reed Solomon (RS) codes for disk arrays

For disk array application that targets n data disks and m parity disks such that the entire pool of (n+m) disks can tolerate any m disk failures, the RS code must be defined in  $GF(2^W)$  where  $2^W \ge n + m$ . An illustration is shown in Fig. 1.5.

RS codes in general require complex GF arithmetics. Although, the Vandermonde matrix representation makes encoding and decoding of an RS code a little simpler than otherwise, it nevertheless remains a dense code. Hence, every time fresh data written into the disks or data gets modified, many associated disks need to be read in order to compute the new parity. This causes severe impairments to the computation load and especially the input/output (I/O) throughput of the system.

#### 1.2.2 LDPC Codes

A class of linear block codes called the low-density parity check (LDPC) code was first introduced by R. Gallager in the early 1960s [20]. The codes are constructed using bipartite graphs and promise performance closed to the Shannon limit. In a bipartite graph representation, a set of vertices represented columns in an LDPC parity check matrix and another set represent rows. The ith left vertice (variable nodes) is linked to the jth right vertice (check nodes), if and only if there is "1" in the jth row and ith column of the parity check matrix. A good LDPC code usually require a large girth, g, which is the smallest cycle in the graph. A large girth improves the decoding performance of the sum-product algorithm.

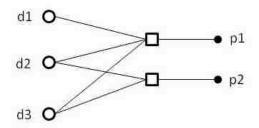

Figure 1.6: An example of a simple LDPC code with n = 3, m = 2

LDPC codes can be encoded and decoded by using simple XOR operations. LDPC codes are shown to be asymptotically optimal codes which means that they achieve the Singleton bound when  $n \to \infty$ . However, for small values of n, such as a few or a few tens, an LDPC code is far from MDS. An example of a bipartite graph describing a simple LDPC code is shown in Fig.1.6. There are n=3 data disks  $d_1, d_2$ , and  $d_3$ , and m=2 parity disks which are computed by XORing the data disks. The parity  $p_1$  is computed by XORing  $d_1, d_2$ , and  $d_3$ , while the parity  $p_2$  is computed by XORing  $d_2$  and  $d_3$ . The corresponding parity matrix is shown below.

$$H = \left[ \begin{array}{ccc|c} 1 & 1 & 1 & 1 & 0 \\ 0 & 1 & 1 & 0 & 1 \end{array} \right]$$

This parity check matrix, H, has dimension  $m \times (m+n)$  for a (5,3) code. However, for a matrix to be called *low-density*, the number of 1's in the matrix should be sparse. In general, there are two types of LDPC codes that have been described in the academic literature.

- 1. Regular LDPC Codes: A LDPC code is called  $(w_c, w_r)$ -regular if a parity matrix H contains exactly  $w_c$  1's per column and  $w_r = w_c \frac{n}{m}$  1's per row, where  $w_c \ll m$ .

- 2. Irregular LDPC Codes: If the number of 1's per row or per column is not constant, the code is called an *irregular* code.

Irregular LDPC codes usually outperform regular LDPC codes for very large code lengths.

The code rate of the LDPC code is  $R = \frac{n}{n+m}$ . The overhead factor (f) is defined as the average number of fn of disks that need to be accessed to reconstruct the n lost data disks (note that f>1). A carefully optimized irregular LDPC code can become space optimal  $(f\to 1)$ , when the size of n goes to infinite  $(n\to\infty)$ .

### 1.2.3 Parity Array Codes

Recently, a class of very promising codes based solely on XOR operations, while maintaining good storage efficiency, are introduced when carefully designed their performances can be optimal or nearly optimal. Thus, these codes are more efficient and ubiquitous than the RS code in terms of computation complexity.

**Definition 1.2.1.** An array code is an erasure-correcting code that is solely computed by simple binary XOR operations. The information and parity(redundant) bits are placed in a two-dimensional array of size  $(m \times n)$  rather than a one-dimensional vector.

In an array code, data- and parity-bits are usually represented in a 2-dimensional array. Each column can be viewed as a disk, while each row can be viewed as a strip of the disk. There are 2 types of parity array codes: (1) the horizontal parity array codes where disks store all data or all parity, and (2) the vertical parity array codes where all devices store both data and parity. The vertical parity array codes are more preferable since they have symmetry, such that encoding/decoding complexity is distributed evenly across the disks. An example of an array code with one parity row that can recover from any two column erasures is given below. The first row contains pure information bits and the second row contains parity bits that are computed from the information bits as specified. Hence this code is a vertical parity array code that involves 4 disks altogether with a code rate of  $\frac{1}{2}$ , and can tolerate 2 concurrent disk failures.

| a            | b            | c            | d            |

|--------------|--------------|--------------|--------------|

| $c \oplus d$ | $d \oplus a$ | $a \oplus b$ | $b \oplus c$ |

For the decoding process, for example, if disk (column) 1 and 3 are lost, recovering data a and c can be done by the following computations.

$$a = d \oplus (d \oplus a) \tag{1.2}$$

$$c = b \oplus (b \oplus c) \tag{1.3}$$

#### **EVENODD** Codes

EVENODD codes are known as the "grandfather" of array codes introduced in 1995 [7]. This code is a horizontal MDS array code which can protect and recover 2 erasures. The code word is two-dimensional horizontal and geometrical array with two additional parity columns: one horizontal strip and the other along the diagonals through the stripe. However, the number of data columns (p) needs to be a prime number. The number of rows is r=p-1, and the strip count is n=p+2. The layout example for p=3 in Table 1.2 shows the basic construction. The code is a (5,3) MDS code defined by a  $2\times 5$  array.

| $d_{0,0}$ | $d_{0,1}$ | $d_{0,2}$ | $P_0$ | $Q_0$ |

|-----------|-----------|-----------|-------|-------|

| $d_{1,0}$ | $d_{1,1}$ | $d_{1,2}$ | $P_1$ | $Q_1$ |

Table 1.2: An example of a simple EVENODD code

The first parity is computed by  $P_i = \bigoplus_{j=0}^{p-1} d_{i,j}$ , where  $0 \le i \le p-2$ . To compute the second parity (Q), we first compute the syndrome (S), which is  $S_i = \bigoplus_{j=0}^{p-1} d_{p-1-j,j}$ , and then  $Q_i = S \oplus \bigoplus_{j=0}^{p-1} d_{i-j,j}$ .

#### X-Codes

The X-code was presented as a nother simple optimal MDS code. This code is a vertical parity array code constructed by m=2, n=p-2, where p is the prime number. The  $(n+2) \times p$  code array is represented by n rows of data, 2 rows of parity, and p=n+2 columns. So X-code can correct 2 erasures [8].

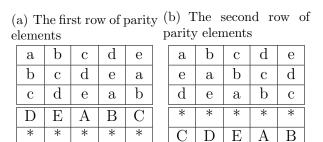

An example of p=5 is given in Table 1.2.3. The left plot shows the pattern of computing the first row of parity elements, while the right plot shows the second row of parity elements. Each parity element is represented by an upper case letter and such a parity element is computed by XORing the set of data elements labeled by the corresponding lower case letter.

Table 1.3: An  $(5 \times 5)$  array of X-code

From the construction of X-code, it is clear that two parity rows are independently obtained, and each information bit affects only one parity bit in each parity row. Thus, all parity bits depend solely on information bits, but not from among themselves. The update complexity is exactly 2 since a single data bit needs only updating in two parity bits [8].

#### The Row-Diagonal Parity (RDP) Codes

The row-diagonal parity (RDP) code [37] is proposed as a double fault tolerant array code, which like the X-code, is also a variation of the EVENODD code. The code is described by a  $(p-1) \times (p+1)$  array, where p is a prime number greater than 2. It provides the last two columns as two parity columns, so the first p-1 columns contain information bits.

(a) The first column of par- (b) The second columns of ity elements parity elements

| a | a | a | a | A | * |

|---|---|---|---|---|---|

| b | b | b | b | В | * |

| С | c | С | С | С | * |

| d | d | d | d | D | * |

| d | С | b | a | * | D |

|---|---|---|---|---|---|

| c | b | a | * | d | С |

| b | a | * | d | С | В |

| a | * | d | c | b | A |

Table 1.4: An  $(4 \times 6)$  array of RDP code

Table 1.4 illustrates an example layout to construct two columns of parity of  $(4 \times 6)$  RDP code. The first and second parity columns are named as the row parity column and the diagonal parity column, respectively. Also, each parity element is represented by an upper case letter and such a parity element is computed by XORing the set of data elements labeled by the corresponding lower case letter. In this code, the missing diagonal does not have a corresponding diagonal parity.

#### Array codes that can correct more than 2 erasures

For large systems, array codes which can handle more than two erasures are required to improve the reliability of disk storage. Here are some examples that are MDS or nearly MDS codes.

1. <u>STAR codes</u>: This MDS code is an extended version of EVENODD codes that protects 3 erasures [35].

| a | * | d | С | b | * | * | A |

|---|---|---|---|---|---|---|---|

| b | a | * | d | С | * | * | В |

| С | b | a | * | d | * | * | С |

| d | С | b | a | * | * | * | D |

Table 1.5: An  $(4 \times 8)$  array of STAR code

The first two parity columns are computed the same as the ones of EVENODD codes by using the syndrome, so without the third parity column the STAR codes are just the EVENODD codes. The third parity is computed by XORing the information symbols within the diagonal line of slope -1 as shown in Table. 1.5.

- 2. WEAVER codes: This code is a vertical parity array code that can tolerate higher failures. There exist specific realizations of WEAVER codes of m=2, n=2 and m=3, n=3, which tolerate double and triple disk failures, respectively, and are MDS. However, WEAVER codes in general are not MDS codes.

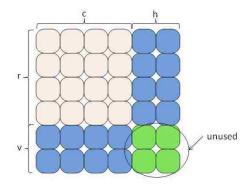

- 3. <u>HoVer codes</u>: This code is a combination of horizontal and vertical parity array code. The general parameters of HoVer codes are  $HoVer_{v,h}^t[r,c]$ , where t is the number of fault tolerance this code can handle, v is the number of coding rows (vertical parity), h the number of coding columns (horizontal parity), r is the number of data rows, and r is the number of data columns. All parameters are illustrated with the array structure in Fig. 1.7. Even through, this code is not an MDS code, it is still interesting as it provides good flexibility in code design. This code is also known as turbo product code or block turbo code [9].

Figure 1.7: The  $HoVer_{v,h}^t[r,c]$  codes.

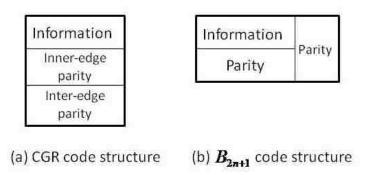

4. B-Codes: A novel technique to construct an MDS array code using a perfect 1-factorization (P1F) of the graph theory is introduced and proposed in [8]. This code has dimension  $n \times 2n$ , where n is an integer greater than 2. The first n-1 rows store information bits, while the bits in the last row are parity bits. Because of the property of P1F technique, any two information bits are not used to compute any pair of parity bits and result in each information bit is protected by exactly 2 parity bits contained in other columns. This code reaches the optimal update complexity.

B-codes achieve the Singleton bound, so they are optimal in terms of space efficiency. There are a lot of researches inspired by this code and they are presented in [15], [53], [40], to name but a few.

Table 1.6 summarizes these three types of important erasure codes: RS codes, LDPC codes, and array codes.

| Erasure code       | Characteristics                                                                                                                                                                                                     |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reed-Solomon Codes | <ol> <li>Optimal MDS code, space efficient</li> <li>Flexible code length and rate since it works for any n and m</li> <li>Use GF (Galois field) operations, computationally complex, and hence expensive</li> </ol> |

|                    | 4. Dense code, so I/O throughput can be poor                                                                                                                                                                        |

| LDPC Codes         | Binary encoding/decoding     Good performance at long code lengths                                                                                                                                                  |

|                    | <ul><li>3. Less structural (hardware implementation can be tricky)</li><li>4. Performance is far from optimal at short</li></ul>                                                                                    |

|                    | lengths (storage systems use short erasure codes)                                                                                                                                                                   |

| Array Codes        | <ol> <li>Well structured</li> <li>Space efficient</li> </ol>                                                                                                                                                        |

| Array Codes        | 3. Binary encoding and decoding (suitable for hardware implementation)                                                                                                                                              |

|                    | 4. There are not many MDS array codes, and most of them correct only 2 to 3 erasures                                                                                                                                |

Table 1.6: Erasure codes for disk storage arrays

# 1.3 Flash Drives

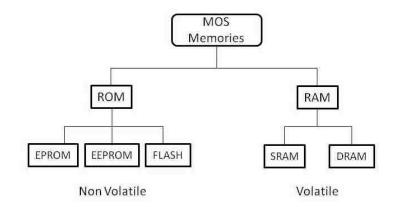

The past decade has witnessed an explosive growth in semiconductor memories, especially the flash memory, driven by cellular phones and other electronic portable devices such as GPS and MP3 players. The semiconductor memories are divided into two branches which are based on the complementary metal-oxide-semiconductor (CMOS) technology as shown in Fig. 1.8.

This section will explain the technology of flash memories, an important class of solid-state memory, and their current trend in industry fields. Flash memory is a particular type of EEPROM or Electronically Erasable Programmable Read Only Memory. It is a non-volatile memory that maintains stored information without requiring a power source. Compared to the hard disks and optical disks which provide two distinctive states to represent 0s and 1s, flash memories have many levels of cell states that can represent the digital data. To increase the cell state level can be achieved by injecting the electron into the cell level is easy, but to decrease its level is both costly and slow since it has to erase the whole block. Furthermore, frequent block erasing can deteriorate the life time of flash memories since the overall life time is limited by the counting of erase operations.

Figure 1.8: MOS memory tree

There are 2 different types of flash memories in terms of logical technologies to map data: NAND and NOR flash memories which are described in the following.

NOR Flash: In NOR flash memory, a standard MOSFET is resembled in each cell and each cell has two gates which are stacked vertically. The common drain connection called bit line is connected to each cell and can be read directly in order to fast read for the fast program execution. • NAND Flash: The memory cells are connected in series and also connected to the bit line and source line through two selected transistors in order to increase capacity and decrease cost of flash memory. It has a smaller cell size and lower die cost than NOR flash [44].

In both types, write operations can only clear bit or change their cell value from 1 to 0. To set bit or change their cell value from 0 to 1 needs to erase an entire block of memory [51]. Since each bit in a NOR flash is cleared once per erase cycle, it suffers from high erase times. Unlike a NOR flash, a NAND flash is not directly addressable by the processor. It is accessed by a page (or block). However, after a page is full, an erase cycle must be required. Because of this properties, the storage management techniques for each type of flash memory are different from the magnetic disks.

# 1.3.1 NOR vs. NAND Flash Memory

There are some difference between NOR and NAND flash memories because of their performance and different using propose. NOR flash is very similar to a Random Access Memory (RAM) device and has enough address pins to map its entire media which allows for easy access to each and everyone of its bytes. NAND flash has more complicated I/O interface since it is interfaced to each other serially between bit line that may vary from one device to another or from vendor to vendor. The basic cell in NAND flash is a MOSFET transistor with a floating gate which tunnels a charge during write operations and removes during erasing operations. NAND Flash, which was designed with a very small cell size to enable a low cost-per-bit of stored data, has been used primarily as a high-density data storage medium for consumer devices such as digital still cameras and USB solid-state disk drives.

NOR flash is suitable and ideal for low-density, high-speed read applications, which are mostly read only, so it is often referred to as code-storage applications. Because code can be directly executed in place, NOR is ideal for storing firmware, boot code, operating systems, and other data that changes infrequently. On the other hand, NAND flash is developed for higher-density data storage, and achieves a smaller cell size that leads to a smaller chip size and lower cost-per-bit since it can connect eight memory transistors in a series. Thus, NAND flash systems perform faster write and erase operations by programming blocks of data, so that it is ideal for low-cost, high-speed program/erase applications and usually referred to as data-storage applications [31].

However, to increase the performance and reliability of flash hardware, the well-designed software strategies are effectively applied. The proposes of flash memory management software include [51]:

- 1. Avoiding data loss: The most important goal in managing flash memory is to assure that no data is lost due to an interrupted operation or the failure of device. Several techniques can achieve this goal, for example, (i) rewrite operations: new data can be written and verified before the old data is deleted, so that neither power loss nor other interruption can result in the loss of both old and new data, and (ii) bad block management: this is the software management that can prevent data being written to failed memory blocks since it can check which blocks are bad and avoid writing to those block from the beginning. Moreover, at the nearly the end of flash memory life, the good software management can implement a fruitful strategy such as placing the entire flash unit in a read-only state, thereby avoiding data loss when the number of block errors exceeds a predefined number [51].

- 2. Improving the effective performance: There are two ways to improve the

performance which are compaction and multi-threading. Compaction identifies which block is obsolete or full that can be erased, then copies any valid data to a new location before erasing the blocks to make them available for reuse. Multi-treading system helps to organize read operations by allowing high-priority read requests to interrupt low-priority maintenance operations. It can reduce read latency by orders of magnitude compared to a single-thread solution.

3. Maximizing flash memory life span: The Wear-levelling algorithm is a famous technique that can prevent overuse of memory blocks. It can monitor block usage to identify high-use areas and low-use area containing static data, then swap the static data into the high-use areas. Also, it balances write operations across all available blocks by choosing the optimal location for each write operation.

The decision between NAND and NOR memory will ultimately depend on both technical and pricing requirements of the device being built. Whatever type or combination of flash is used, it is prudent to include memory management software to prevent data loss while improving the performance and maximizing the lifespan of the memory [2].

We can conclude the properties and performances of both NOR and NAND flash memories in Table 1.7.

In data storage applications, NAND flash memory is often used because of its characteristics we described above. However, the major drawback/limitation of NAND flash memory is that it has the limitation in updating (writing) times so it degrades the lifespan of flash memory. In this work, we will apply coding techniques to solve this problem. The objective is to maximize the number of writes before a memory needs to be erased and reset the whole block to be ready to write a new data again.

| NAND Flash                           | NOR Flash                        |  |  |  |

|--------------------------------------|----------------------------------|--|--|--|

| core cells connected in series (nor- | core cells connected in parallel |  |  |  |

| mal 8 or 16 cells)                   | (common ground)                  |  |  |  |

| high density                         | lower density                    |  |  |  |

| medium read speed                    | high read speed                  |  |  |  |

| high write speed                     | slow write speed                 |  |  |  |

| high erase speed                     | slow erase speed                 |  |  |  |

| an indirect or I/O like access       | a random access interface (good  |  |  |  |

| (good for data storage)              | for code execution)              |  |  |  |

Table 1.7: The properties and performances of NOR and NAND flash memories

## 1.4 Outline

In the rest of this dissertation, we will discuss coding techniques for disk arrays in Chapter 2 and for distributed large-scale data centers in Chapter 3, and for flash memory are in Chapter 4.

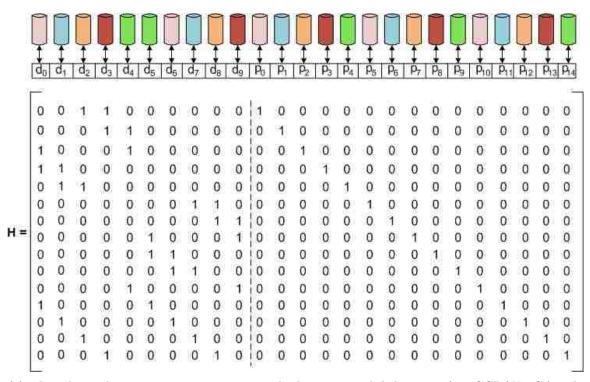

In Chapter 2, we propose a new class of optimal MDS codes constructed from graphs which can achieve the Singleton bound and which are based only on simple XOR operations. These codes termed complete-graph-of-ring (CGR) codes can recover the maximal disk failure with minimal spare disks and are particularly useful for disk arrays. Additionally, these codes can be considered as a modification of LDPC codes.

Extending the MDS coding results developed in Chapter 2 as well as those proposed in the literature, next in Chapter 3, we tackle the data protection and disk recovery issue in the context of large data centers. Accounting for the possibility of splitting a data center and merging two data centers, we propose layered protection, and develop a nested coding architecture with hierarchical protection for distributed storage networks.

Chapter 4 presents and discusses coding schemes for flash memories. The goal is to improve their life cycles and maximize the number of writing times before a block erasure. Both word-efficient bit-efficient (WEBE) codes and flash marker (FM) codes are introduced and analyzed in terms of the number of bit-writes and the number of word-writes they can guarantee before the block erasure is needed. We present the new code design idea, discuss its feasibility and efficiency, and estimate its performance.

Chapter 5 concludes this dissertation and discusses the future industrial trends of both disk storages and flash memory. In the research work, many coding techniques have been studied, improved, and generated in the pipeline. We can extend our work and develop our codes for various applications.

# Chapter 2

# MDS codes for disk arrays

This chapter presents practical coding techniques for data disks in order to combat disk failures or erasures. We investigate various types of array codes, due to their simplicity and high I/O throughput. Since maximum distance separable codes are space optimal, we focus on graph constructions of MDS array codes or nearly-MDS array codes. We also study MDS array codes in the form of "low-density (sparse)" matrices and propose the algorithm for encoding/decoding.

# 2.1 Introduction

Storage of digital data has become a necessary part of our life in today's information age. Huge volumes of data information are created, transferred, and stored everyday. Reliable and fast-recovery data storage is essential to support data availability, persistence, and integrity. Various techniques for increasing storage reliability have been actively exploited, including powerful

error correction codes applied inside each block/sector of a disk to protect against bit errors or bit loss, and, more recently, efficient erasure codes applied between disks (or blocks and sectors) to protect against a disk (block/sector) failure [3]-[13]. The latter, generally referred to as redundant/reliable arrays of inexpensive/independent disks, or, RAID, is becoming an important industrial standard [16]. A key technical challenge of RAID is the design of efficient erasure codes that can recover a target number of device failures with minimal redundancy, namely, maximum distance separable codes. An array code is not always MDS, but an MDS array code is particularly desirable for combating data loss caused by disk failure in disk arrays. The properties of MDS codes will be discussed later in the next section.

### 2.1.1 MDS Codes and Their Properties

Space-optimal or MDS codes have several desirable properties.

**Theorem 2.1.1.** [35] Consider an (n, k) error correcting code that encodes k message (data) symbols to n codeword symbols, where  $n \geq k$ . Such a code can usually tolerate a loss of e symbols during transmission, where  $e \leq n - k$ . When e = n - k, the code meets the Singleton Bound, and is called an MDS code.

**Theorem 2.1.2.** [36] An (n, k, d) code C with a generator matrix G = [I, A], where I is a rank-k identity matrix and A is a  $k \times (n - k)$ -matrix, is an MDS code if and only if every square sub matrix of A is nonsingular.

**Theorem 2.1.3.** Let C be an (n, k) linear code with minimum distance  $d_{min}$ , then the following statements are equivalent:

- 1. C is an MDS code.

- 2. The code C' dual to C is an MDS code.

- 3.  $d_{min} = n k + 1$ .

- 4. The code can correct any set of e = n k erasures.

- 5. Any k columns of the k-by-(n-k) generator matrix for C are linearly independent.

- 6. If a generator matrix for C is in the standard form [I, A], then every square submatrix of A is nonsingular.

- 7. Given any  $d_{min}$  coordinate positions, there is a (minimum weight) code word whose non-zero entries are in precisely these positions.

The MDS codes achieve the largest possible minimum distance  $(d_{min})$  among linear codes of the same size, and therefore provide the best data loss recovery capability within a given code size.

#### 2.1.2 Literature Reviews

We provide a quick review of the existing array codes. More detailed discussion can be found in Chapter 1.

The EVENODD codes [7] are the first and the most well-known class of MDS array codes that have inspired many subsequent designs of good array codes. The perspective of this code is to overcome the drawback of traditional array codes which is the linear increase of the update complexity as the number of columns increases. EVENODD codes and their generalizations are designed

based on independent parity columns resulting in a more efficient information update.

However, EVENODD codes have only two logic parity symbols, which means that they can recover up to two disk failures, while the generalized EVENODD code can tolerate three disk failures. Hence, the general question arises as whether it is possible to develop MDS array codes with larger erasure correcting capability and with similar low complexity. X-Codes developed in [8] provides a good answer. X-Codes boast a simple geometrical structure and an update complexity of exactly 2. Since the distance of X-codes is 3, it can recover up to 2 disk failures with lower complexity. Another class of MDS codes, named B-Codes, and their dual codes [3] also have distance 3 and their update complexity is also optimal, which is exactly 2. Additionally, a perfect one-factorization (P1F) of complete graphs is a technique to construct B codes. Both P1F technique and a graphical structure make B-code simply to implement and easy to construct an array code. Efficient decoding algorithms are introduced for both erasure and error correcting for B-codes.

There are some array codes that can tolerate more than 3 erasures. These codes [7, 6, 8, 3] have parity in either horizontal or vertical positions. J. Hafner also introduced the code which has parity bits in both horizontal and vertical positions, termed HoVer codes [9]. The HoVer codes proposed by Hafner can tolerate more than 3 erasures, but unfortunately they are only approximately MDS codes.

This work is inspired by the beauty of graph representation of these array codes, especially B-codes, and their MDS properties. We are interested in finding answers to the following questions. What kind of graphs would lead us to MDS codes? What would be the conditions and the properties of such graphs? How could we construct an MDS code from such a graph? The experiments in [9] suggest that some code settings are MDS codes, but some

are not, while [3] successfully constructs the code based on a specific setting of graphs. Here, we explore the possibility of finding generalized ideas for the array codes based on graph structures as well as looking for systematic ways to construct such codes. Our study results in a new class of MDS codes from a new class of graphs in the next section.

## 2.2 CGR Codes

In this section, we propose a new erasure code construction technique to reduce disk failures and increase the capability of fault tolerance. The proposed method systematically builds MDS codes from an efficient class of nested graphs, termed *complete-graph-of-rings* (CGR). The resultant codes, termed "CGR codes", and theirs dual codes require minimal encoding/decoding complexity.

# 2.2.1 Code Construction and Algorithms

The proposed CGR codes are constructed in three steps:

- 1. Building the appropriate CGR graph of the appropriate parameters

- 2. Mapping the CGR graph to an array code

- 3. Reordering by left-cyclically shifting rows (following the perfect 1-factorization technique) in the array code to achieve MDS

The notations and definitions:

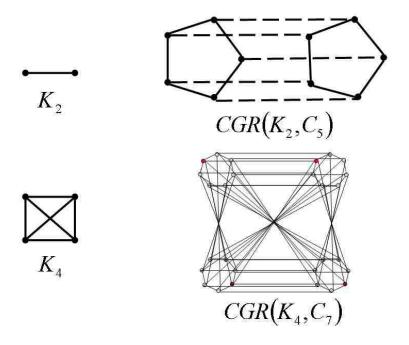

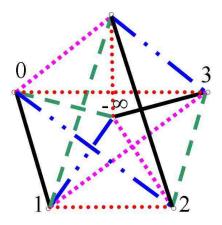

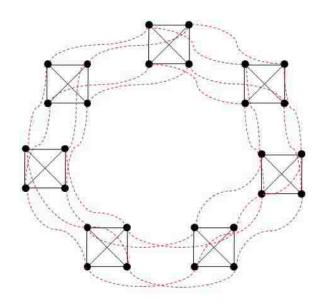

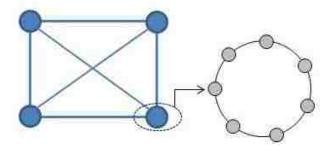

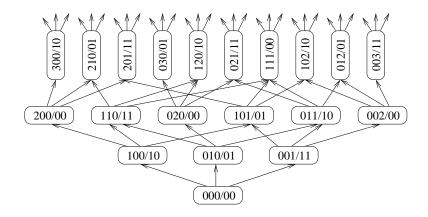

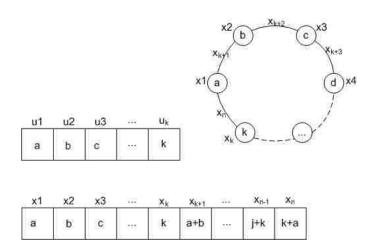

Let  $K_v$  be a complete graph (or base graph) with v vertices and  $\frac{v(v-1)}{2}$  edges, and each vertex has a degree of v-1. The ring graph is denoted by  $C_n$  with n edges. So, we can define the CGR graph by  $CGR(K_{v_1}, C_{v_2})$ , where we replace each vertex of a complete graph  $K_{v_1}$  with a ring graph  $C_{v_2}$ , and replace each edge connecting two vertices in  $K_{v_1}$  with a group of  $v_2$  parallel edges connecting the respective vertices in two rings. The examples of  $CGR(K_2, C_5)$  and  $CGR(K_4, C_7)$  are illustrated in Fig. 2.1.

Figure 2.1: CGR graphs constructed from base graphs. Left: base graphs  $K_2$  and  $K_4$ ; right: resultant CGR graphs  $CGR(K_2, C_5)$  and  $CGR(K_4, C_7)$ .

The sufficient conditions that allow a CGR graph to convert to an MDS code is given as follows.

**Theorem 2.2.1.** If a CGR graph  $\Upsilon_{v_1,v_2}$  constructed from a complete graph  $K_{v_1}$  and a ring graph  $C_{v_2}$  satisfying the following conditions: (1)  $v_1$  is even, and (2)  $v_2 = v_1 + 3$ , then there exists a way to place all the vertices and

edges in an array of  $\frac{v_2v_1}{2} \times v_2$ . When the vertices are interpreted as data bits and the edges connecting two vertices are interpreted as parities associated with two data bits, the resultant array defines an array code of parameters  $(N, K, d_{min}) = (v_1, 2, d_{v_1} - 1)$  capable of correcting up to  $(v_2 - 2)$  erasures. Its dual code is a  $(v_2, v_2 - 2, 3)$  MDS code capable of correcting up to 2 erasures.

We now present the detailed algorithms for each of the three steps in constructing an MDS CGR code.

#### Algorithm 1: Graph Construction and Labeling

This algorithm constructs a  $(v_1+1)$ -regular CGR graph  $\Upsilon_{v_1,v_2}$  from a complete graph  $K_{v_1}$  and a set of  $v_1$  rings  $C_{v_2}$ , where  $v_2$  is even and  $v_2=v_1+3$ .

- 1. Take a set of  $v_1$  number of rings  $C_{v_2}$ . Label the vertices of the first ring counter-clockwise as  $0, 1, \dots, v_2 1$ ; label the vertices of the next ring similarly as  $v_2, v_2 + 1, \dots, 2v_2 1$ , and so on, until all the rings are labelled. We have altogether  $v_1$  rings or  $v_1$  sets of vertices, where the vertices of the jth ring are labelled by  $\mathbf{V}_j = \{jv_2, jv_2 + 1, \dots, (j+1)v_2 1\}$ , for  $j = 0, 1, \dots, v_1 1$ .

- 2. Each edge inside a ring, termed a ring edge, is marked by the pair of vertices on both ends. We have altogether  $v_1$  sets of ring edges, where the edges of the jth ring are labelled by  $\mathbf{E}_j = \{(jv_2, jv_2+1), (jv_2+1, jv_2+2), ..., ((j+1)v_2-2, (j+1)v_2-1), ((j+1)v_2-1, jv_2)\}, \text{ for } j=0,1,...v_1-1.$

- 3. For any pair of rings, connect their indexes using  $v_2$  parallel *inter-ring* edges, such that the lowest index of one ring is connected to the lowest index of the other, the next lowest is connected to the next lowest, and

so on. We have altogether  $v_1(v_1 - 1)/2$  sets of inter-ring edges, labelled respectively as  $\mathbf{E}_{i,j} = \{(iv_2, jv_2), (iv_2 + 1, jv_2 + 1), ..., ((i + 1)v_2 - 1, (j + 1)v_2 - 1)\}$ , for  $0 \le i < j \le v_1 - 1$ .

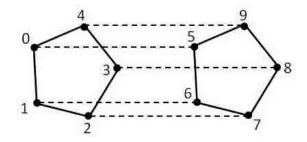

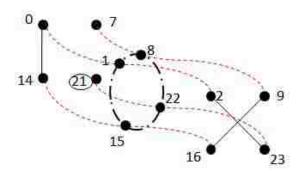

<u>Example 1:</u> An example of labeling the vertices for  $CGR(K_2,C_5)$  is shown in Fig. 2.2. Each vertex has 2 ring edges and 1 inter-ring edges connecting between rings. This graph possesses many desirable properties, including symmetry and regularity (all vertices have the same number of degree 3).

Figure 2.2: Labeling of 3-regular  $CGR(K_2,C_5)$ .