#### Lehigh University Lehigh Preserve

Theses and Dissertations

2012

# Metal Oxide Thin Film Transistors on Paper Substrate: Fabrication, Characterization, and Printing Process

Nackbong Choi *Lehigh University*

Follow this and additional works at: http://preserve.lehigh.edu/etd

#### **Recommended** Citation

Choi, Nackbong, "Metal Oxide Thin Film Transistors on Paper Substrate: Fabrication, Characterization, and Printing Process" (2012). *Theses and Dissertations*. Paper 1245.

This Dissertation is brought to you for free and open access by Lehigh Preserve. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of Lehigh Preserve. For more information, please contact preserve@lehigh.edu.

# Metal Oxide Thin Film Transistors on Paper Substrate: Fabrication, Characterization, and Printing Process

by

Nack-Bong Choi

Presented to the Graduate and Research Committee

of Lehigh University

in Candidacy for the Degree of

Doctor of Philosophy

in

**Electrical Engineering**

Lehigh University

January 2012

Approved and recommended for acceptance as a dissertation in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

Date

Dissertation Advisor (Miltiadis K. Hatalis)

Accepted Date

Committee Members:

Dr. Miltiadis K. Hatalis (Committee Chair)

Dr. James Hwang

Dr. Svetlana Tatic-Lucic

Dr. Ruiqing Ma

# **Table of Contents**

| List of Tablesvii                                       |

|---------------------------------------------------------|

| List of Figures ix                                      |

| Abstract1                                               |

| Chapter 1 3                                             |

| Introduction                                            |

| 1.1 Research motivation                                 |

| 1.2 Dissertation Goals                                  |

| 1.3 Overview of the thesis                              |

| Chapter 2                                               |

| Paper substrate for flexible and disposable electronics |

| 2.1 Paper structure and papermaking process             |

| 2.2 Properties of paper substrate17                     |

| 2.3 Paper selection for TFT fabrication                 |

| 2.4 Planarization and patterning properties                       | . 22 |

|-------------------------------------------------------------------|------|

| Chapter 3                                                         | . 31 |

| N channel a-IGZO TFT on paper substrate                           | . 31 |

| 3.1 TFTs on paper substrate                                       | . 32 |

| 3.2 Low temperature gate dielectric                               | . 34 |

| 3.3 Fabrication of a-IGZO TFT on paper substrate                  | . 38 |

| 3.4 Electrical characterization techniques of TFT                 | . 42 |

| 3.4.1 Mobility & threshold voltage                                | . 42 |

| 3.4.2 Subthreshold swing and interface trap density               | . 45 |

| 3.4.3 Output characteristics                                      | . 46 |

| 3.5 Electrical characteristics of a-IGZO TFT on paper             | . 46 |

| 3.6 Electrical characteristics of methyl siloxane gate dielectric | . 52 |

| 3.6.1 Thickness effect                                            | . 52 |

| 3.6.2 Annealing effect                                            | . 57 |

| Chapter 4                                                         | . 66 |

| P channel Cu <sub>2</sub> O thin film transistor                  | . 66 |

| 4.1 Cu <sub>2</sub> O TFT                                         | . 67 |

| 4.2 Properties of Cu <sub>2</sub> O thin films                    | . 69 |

| 4.2.1 Optical bandgap                                             | . 69 |

| 4.2.2 Hall mobility                                                    |

|------------------------------------------------------------------------|

| 4.3 Fabrication and optimization of Cu <sub>2</sub> O TFT73            |

| 4.3.1 Fabrication of Cu <sub>2</sub> O TFT73                           |

| 4.3.2 Effect of deposition condition75                                 |

| 4.3.3 Post-annealing effect                                            |

| 4.3.4 Plasma treatment                                                 |

| 4.4 Material analysis of Cu <sub>2</sub> O thin film90                 |

| 4.5 P-N diode on paper substrate                                       |

| Chapter 5 107                                                          |

| Study of offset roll printing for thin film transistor application 107 |

| 5.1 Printing technologies 108                                          |

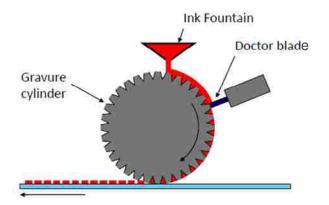

| 5.1.1 Gravure printing 110                                             |

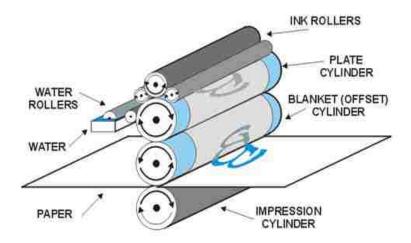

| 5.1.2 Offset printing 111                                              |

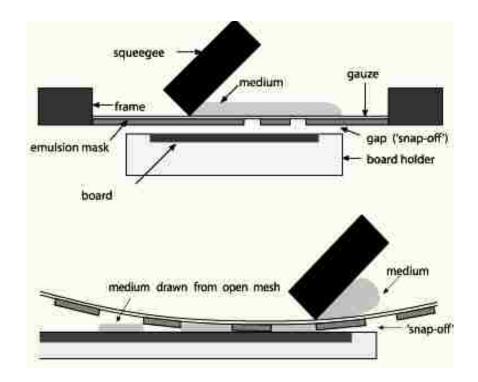

| 5.1.3 Screen printing 112                                              |

| 5.1.4 Inkjet printing 113                                              |

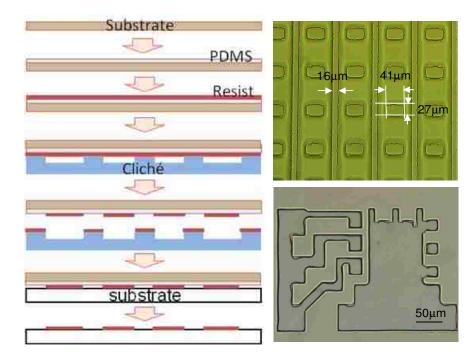

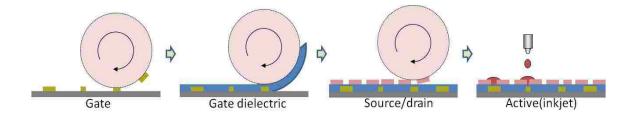

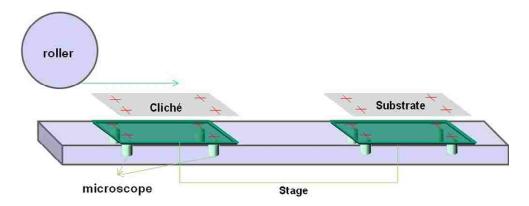

| 5.2 A modified offset roll printing for TFT application 114            |

| 5.2.1 Blanket 116                                                      |

| 5.2.2 Printing plate (Cliché) 117                                      |

| 5.2.3 Surface energy analysis                                          |

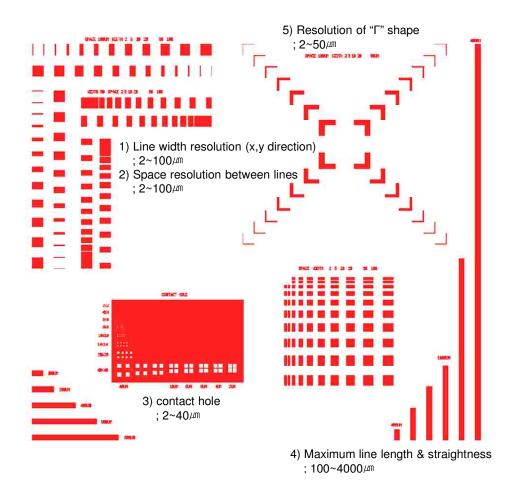

| 5.2.4 Design of test patterns                      | 131 |

|----------------------------------------------------|-----|

| 5.2.5 Ink                                          | 132 |

| 5.2.6 Printing process optimization and results    | 133 |

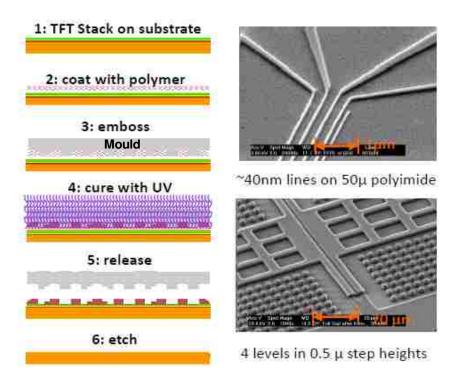

| 5.3 A novel imprint lithography                    | 137 |

| Chapter 6                                          | 142 |

| Conclusions                                        | 142 |

| 6.1 Conclusion of this work                        | 142 |

| 6.2 Recommendation for future research             | 144 |

| Appendix A                                         | 147 |

| Registration for the modified offset roll printing | 147 |

| Appendix B                                         | 148 |

| Process/Parameter for TFT fabrication              | 148 |

| Vita                                               | 153 |

| Publications                                       | 154 |

# **List of Tables**

| Table 1.1 Cost and CTE comparison between paper and representative flexible                  |

|----------------------------------------------------------------------------------------------|

| substrates4                                                                                  |

| Table 2.1 Advantages and drawbacks of each substrate for flexible electronic                 |

| application18                                                                                |

| Table 2.2 Material properties of typical flexible substrates                                 |

| Table 2.3 Commercially available planarization materials                                     |

| Table 3.1 Comparison of TFT devices                                                          |

| Table 3.2 Chemical stability of SOG and PMMA                                                 |

| Table 3.3 Electrical properties of a-IGZO TFTs on paper substrate                            |

| Table 4.1 P-type oxide semiconductor materials                                               |

| Table 4.2 Hall effect measurement results of Cu <sub>2</sub> O thin film73                   |

| Table 4.3 Standard Gibbs energy of formation at 298.15K in J/mol74                           |

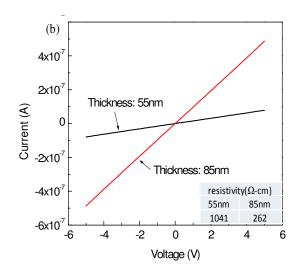

| Table 4.4 $Cu_2O$ resistivity extracted from the I-V characteristics shown in figure 4.8 (a) |

|                                                                                              |

| Table 5.1 Manufacturing cost comparison between conventional photolithography and            |

| printing process                                                                             |

| Table 5.2 Comparison of typical printing process.    1                                                                                       | 110 |

|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 5.3 Etching methods and results for Si-cliché1                                                                                         | 24  |

| Table 5.4 Advancing and receding contact angles on blankets (Methly-vinyl-silicone,                                                          |     |

| PDMS), cliché (Si), and thin film (Mo, SiO <sub>2</sub> ) and their surface energy measured by the                                           | ;   |

| water droplet. $\alpha$ is defined by $\gamma_{l\nu}(1 + \cos \theta_{a(s1)})$ , $\beta$ is defined by $\gamma_{l\nu} \cos \theta_{a(s2)}$ 1 | .28 |

# **List of Figures**

| Fig. 1.1 EPLaR process to fabricate flexible electronics                                  |

|-------------------------------------------------------------------------------------------|

| Fig. 1.2 Backside etching process of a metal substrate for flexible electronics7          |

| Fig. 1.3 High-end and low-cost application of flexible electronics                        |

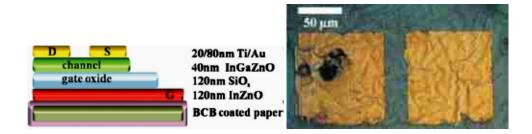

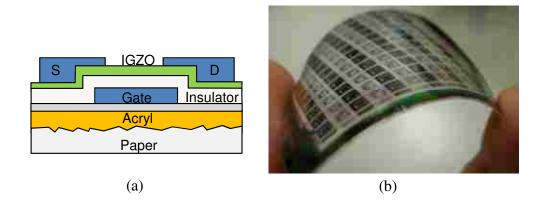

| Fig. 1.4 Schematic diagram and InGaZnOx TFT image on paper substrate9                     |

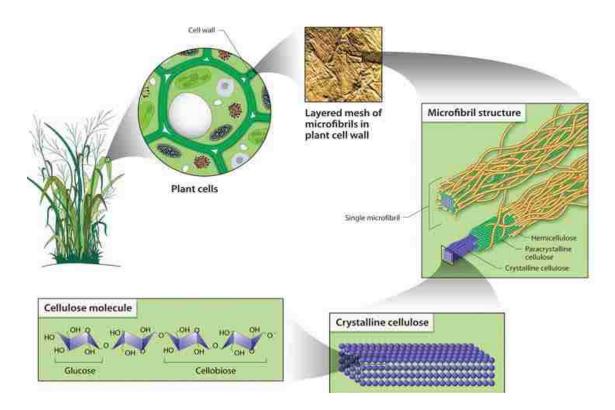

| Fig. 2.1 Structure of cellulose. Cellulose is the main component of paper14               |

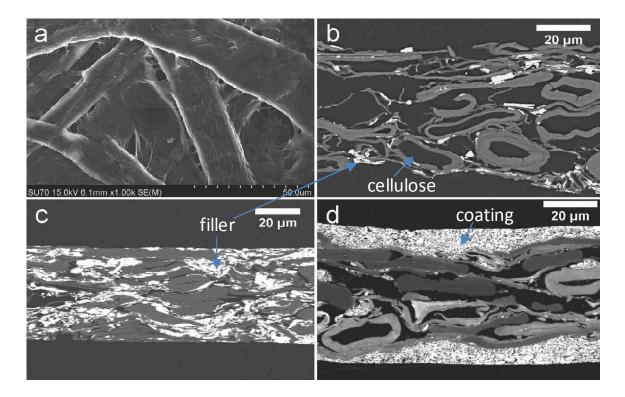

| Fig. 2.2 SEM micrographs of (a) cellulose fiber (b) the cross-section of newsprints (c)   |

| supercalendered paper (d) coated paper15                                                  |

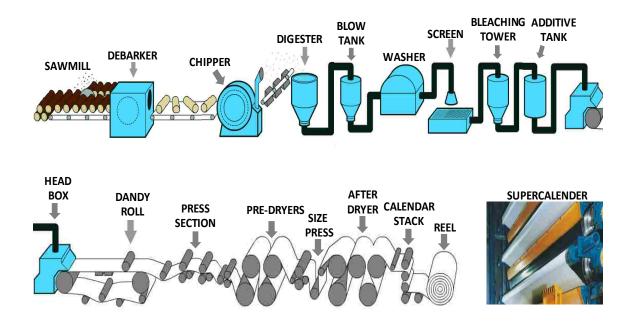

| Fig. 2.3 Paper making process16                                                           |

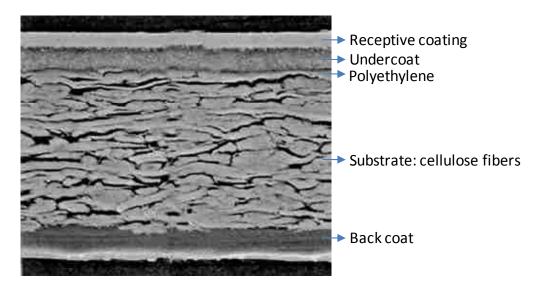

| Fig. 2.4 SEM cross-section of an inkjet printable photo paper21                           |

| Fig. 2.5 Optical images of each paper after annealing21                                   |

| Fig. 2.6 Optical images of (a) Mo on a silicone coated parchment paper (b) Mo and $SiO_2$ |

| on an inkjet printable paper. Before deposition, planarization layer was coated on both   |

| papers22                                                                                  |

| Fig. 2.7 Optical microscopic images of paper surface a) inkjet printable paper, b) glossy |

| laser jet paper, c) a silicon coated parchment paper26                                    |

| Fig. 2.8 3D AFM images of (a) plain paper (b) glossy inkjet-printable paper (c) glossy                 |

|--------------------------------------------------------------------------------------------------------|

| laser jet paper                                                                                        |

| Fig. 2.9 AFM images (a) Acrylate (AC818) coated inkjet printable paper, (b) Acrylate                   |

| (AC818) coated glossy laser jet paper, (c) photoacryl (PC403) coated inkjet printable                  |

| paper, (d) photoacryl (PC403) coated glossy laser jet paper27                                          |

| Fig. 2.10 Optical microscopic images of photolithographically patterned resolution chart               |

| with known widths and spacings on planarized glossy paper. (a) positive patterns (b)                   |

| negative patterns                                                                                      |

| Fig. 2.11 Molybdenum patterns on a paper substrate by using liftoff process28                          |

| Fig. 3.1 Orbital drawing of ionic amorphous oxide semiconductor33                                      |

| Fig. 3.2 Transfer and output characteristics of InGaZnO4-based TFTs fabricated on a                    |

| paper substrate                                                                                        |

| Fig. 3.3 Chemical structure of SOG                                                                     |

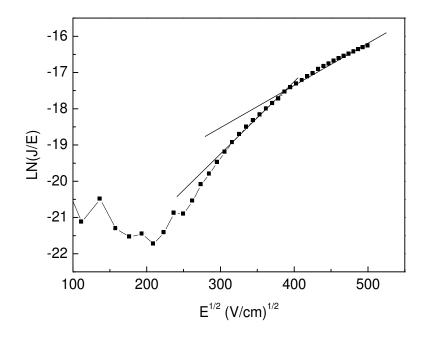

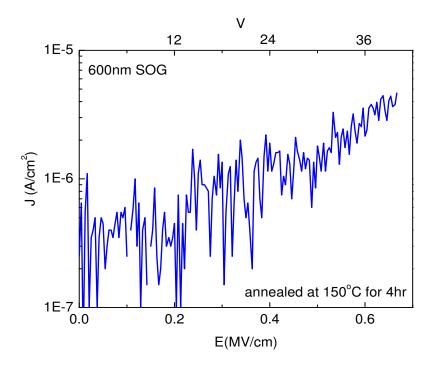

| Fig. 3.4 The logarithmic current density over electric field vs. electric field <sup>1/2</sup> (Poole- |

| Frenkel emission) for 600nm thick SOG insulator                                                        |

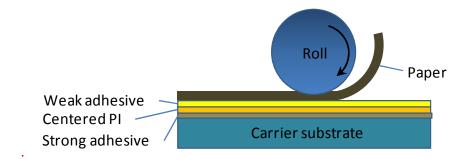

| Fig. 3.5 Bonding & debonding process using double side adhesive film40                                 |

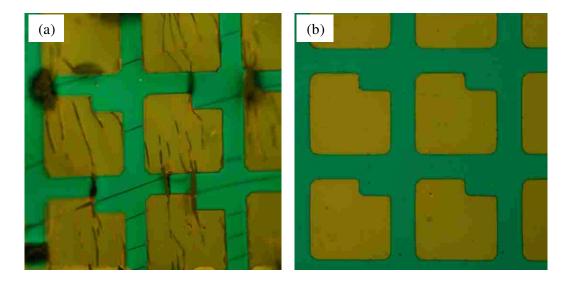

| Fig. 3.6 Optical micrograph of the patterns on a paper substrate after PECVD $SiO_2$                   |

| deposition (a) paper substrate without bonding on carrier substrate, (b) paper substrate               |

| bonded on carrier substrate by the adhesive film41                                                     |

| Fig. 3.7 (a) Schematic cross section of the fabricated a-IGZO TFT and (b) photograph of                |

| a-IGZO TFT array with methyl siloxane based gate dielectric on the planarized paper41                  |

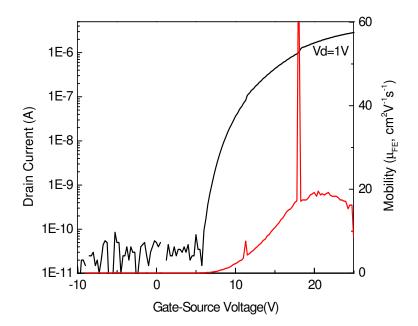

| Fig. 3.8 Transfer and field effect mobility curve of a-IGZO TFT with 600nm thick SOG          |

|-----------------------------------------------------------------------------------------------|

| gate dielectric on paper substrate; W/L=30µm/30µm43                                           |

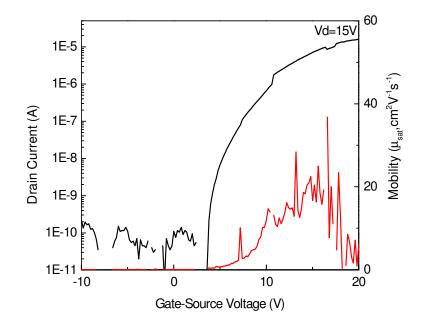

| Fig. 3.9 Transfer and saturation mobility curve of a-IGZO TFT with 600nm thick SOG            |

| dielectric on paper substrate; W/L=30µm/30µm44                                                |

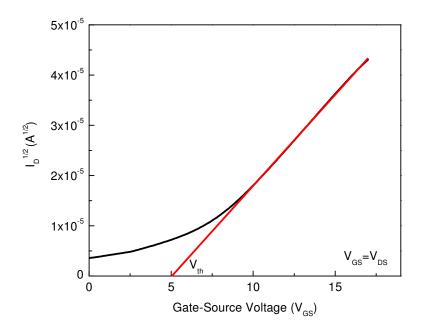

| Fig. 3.10 Threshold voltage determination of a-IGZO TFT by the saturation extrapolation       |

| technique (600nm thick SOG dielectric, W/L=30µm/30µm)45                                       |

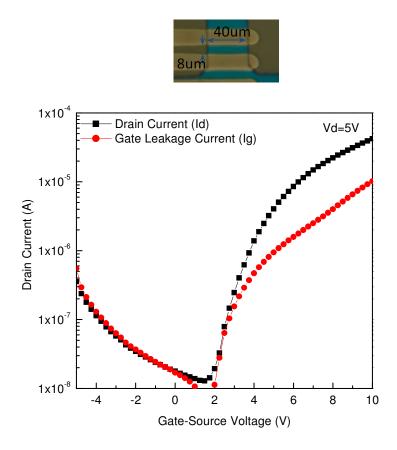

| Fig. 3.11 Transfer characteristics and gate leakage current of a-IGZO TFT with low            |

| temperature (140°C) 200nm thick SiO <sub>2</sub> on the planarized paper substrate47          |

| Fig. 3.12 Transfer characteristics and gate leakage current of a-IGZO TFT methyl              |

| siloxane gate dielectric on planarized paper substrate49                                      |

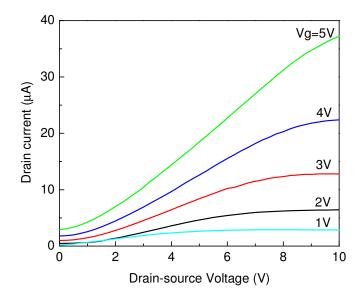

| Fig. 3.13 Output characteristics of n-channel a-IGZO TFT with W/L=40µm/8µm. Gate              |

| dielectric is 200nm thick SiO <sub>2</sub> deposited at 140°C51                               |

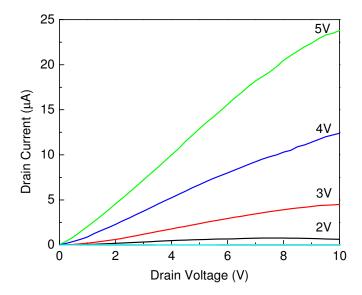

| Fig. 3.14 Output characteristics of n-channel a-IGZO TFT with W/L= $30\mu$ m/ $30\mu$ m. Gate |

| dielectric is 600nm thick SOG cured at 140°C for 2.5hrs                                       |

| Fig. 3.15 Output characteristics of n-channel a-IGZO TFT with W/L=8µm/8µm. The                |

| device was fabricated on oxidized Si wafer and gate dielectric was 600nm thick SOG            |

| cured at 150°C for 3hr. After fabrication, post annealing was performed at150°C for           |

| 1hrs                                                                                          |

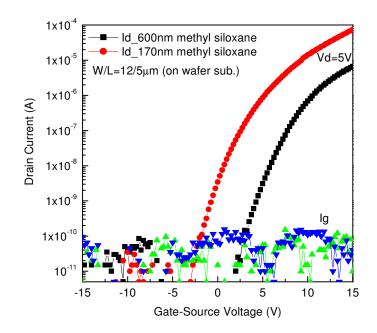

| Fig. 3.16 Transfer curve of a-IGZO TFT according to the thickness variation of methyl-        |

| siloxane (SOG). The devices were fabricated on oxidized Si wafer. SOG dielectric was          |

| cured at 150°C for 3hrs and post-annealed at150°C for 2hrs after fabrication54                |

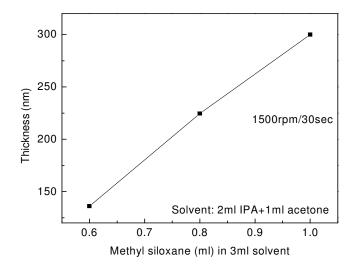

| Fig. 3.17 Thickness variation according to the amount of SOG in 2ml IPA and 1ml                      |

|------------------------------------------------------------------------------------------------------|

| acetone                                                                                              |

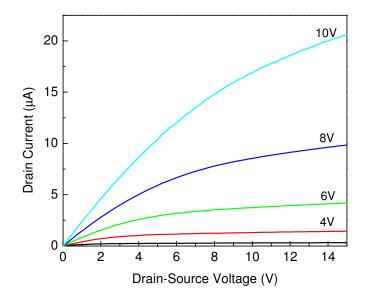

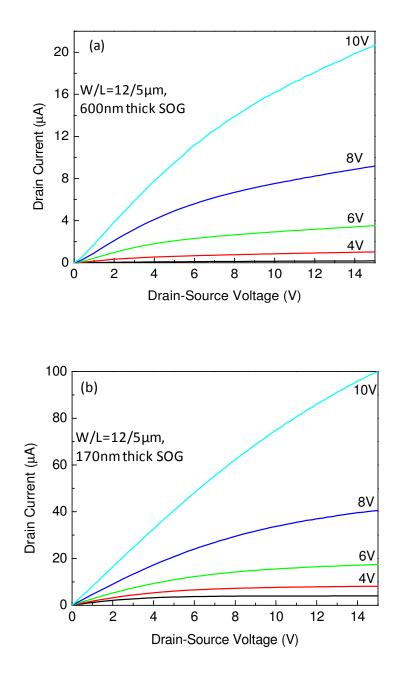

| Fig. 3.18 Output characteristics of a-IGZO TFT according to the thickness variation of               |

| methyl-siloxane (SOG). The devices were fabricated on oxidized Si wafer. SOG                         |

| dielectric was cured at 150°C for 3hrs and post-annealed at150°C for 2hrs after                      |

| fabrication55                                                                                        |

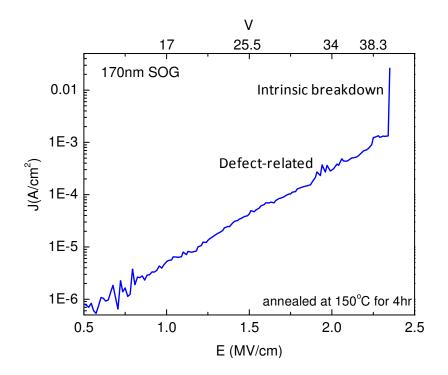

| Fig. 3.19 J-E curve of 170nm thick SOG annealed at 150°C for 4hr56                                   |

| Fig. 3.20 J-E curve of 600nm thick SOG annealed at 150°C for 4hr56                                   |

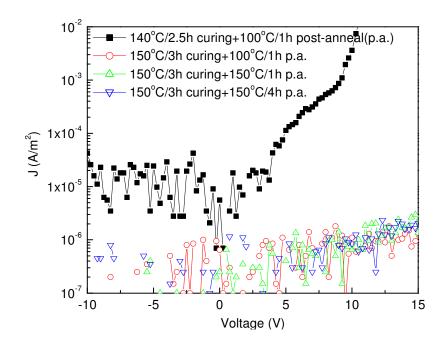

| Fig. 3.21 J-V characteristics of 600nm thick methyl siloxane in Metal-Insulator-Metal                |

| structure according to thermal budget                                                                |

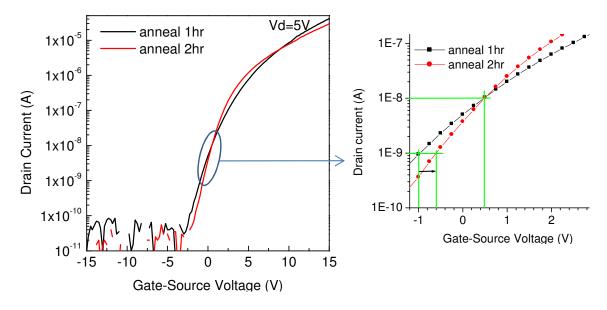

| Fig. 3.22 Transfer characteristic according to annealing time; a-IGZO TFT with W/L=8                 |

| μm/8μm; 150nm thick methyl siloxane on oxidized wafer58                                              |

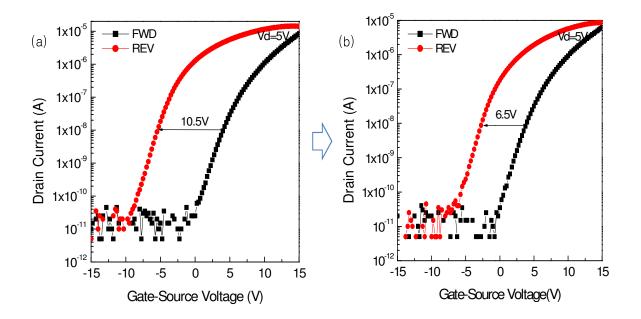

| Fig. 3.23 Hysteresis characteristics of a-IGZO TFT after (a) 1hr and (b) 2hr post                    |

| annealing at 150°; a-IGZO TFT with 170nm thick SOG gate dielectric on oxidized silicon               |

| wafer61                                                                                              |

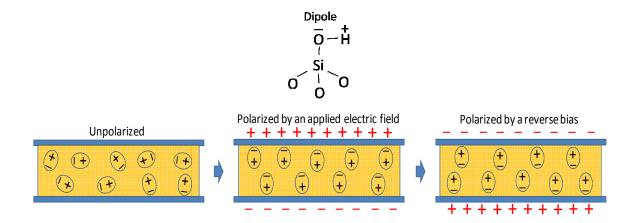

| Fig. 3.24 Schematic of dipole polarization in organic dielectric61                                   |

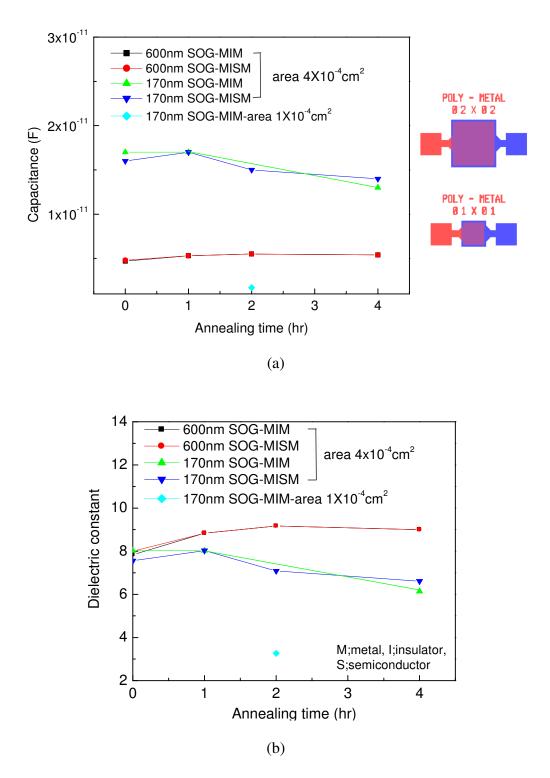

| Fig. 3.25 (a) Measured capacitance (b) calculated dielectric constant as a function of               |

| annealing time. Annealing temperature is 150°C62                                                     |

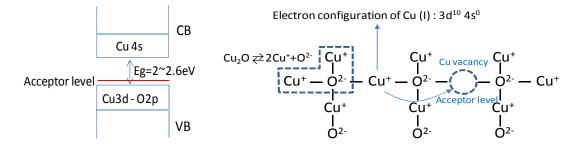

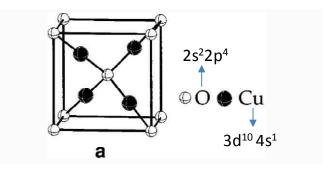

| Fig. 4.1 Schematic energy-level structure and conduction mechanism for $Cu_2O$ 68                    |

| Fig. 4.2 Crystal structure Cu <sub>2</sub> O69                                                       |

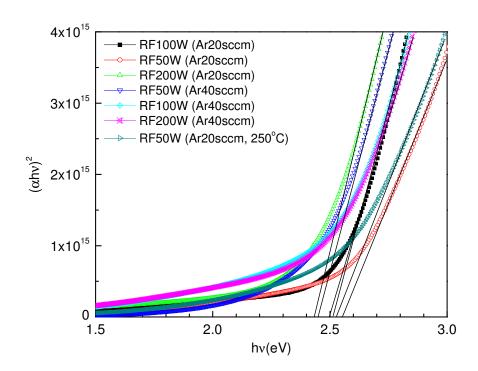

| Fig. 4.3 The hv dependence of $(\alpha hv)^2$ of Cu <sub>2</sub> O thin film according to deposition |

| conditions. Note that the intercept with hv axis indicates the bandgap energy of Cu <sub>2</sub> O70 |

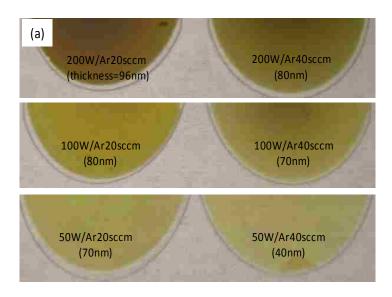

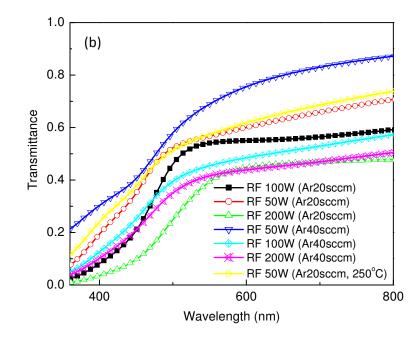

| Fig. 4.4 (a) Photographs and (b) transmittance of Cu <sub>2</sub> O thin film according to deposition |

|-------------------------------------------------------------------------------------------------------|

| conditions71                                                                                          |

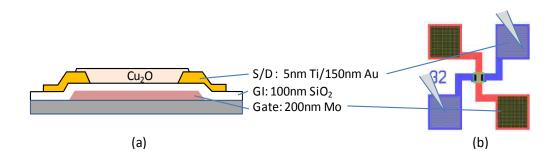

| Fig. 4.5 (a) Bottom gate and bottom contact TFT structure, (b) measurement of channel                 |

| resistance                                                                                            |

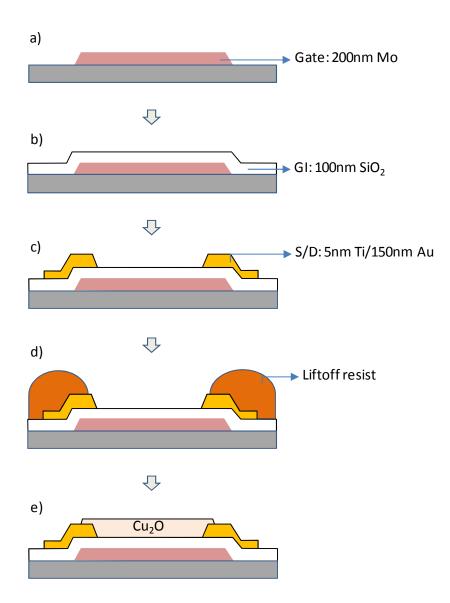

| Fig. 4.6 Cross-sectional view of Cu <sub>2</sub> O TFT fabrication step by step75                     |

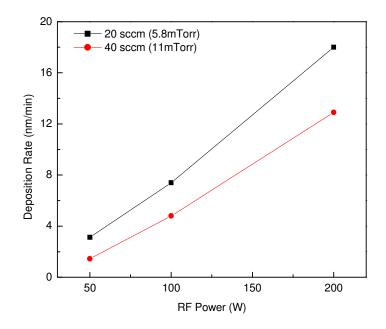

| Fig. 4.7 Deposition rate according to RF power and Ar gas flow rate                                   |

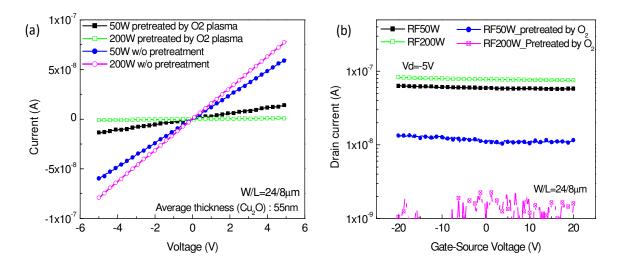

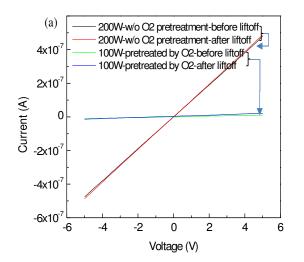

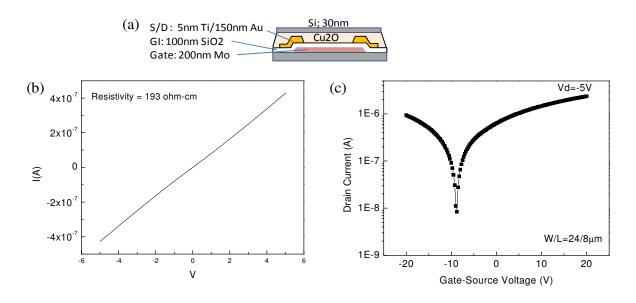

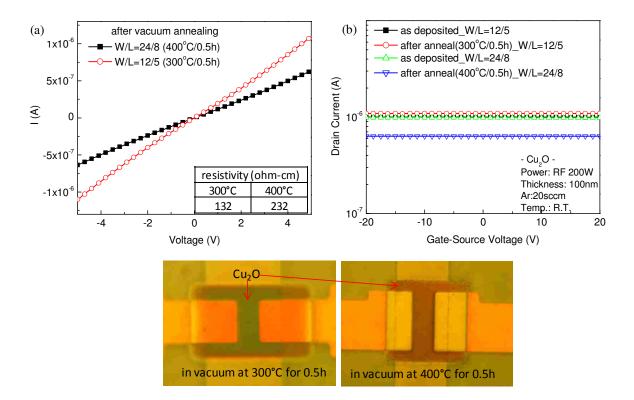

| Fig. 4.8 Effect of deposition power and oxygen plasma pretreatment on $Cu_2O$ TFT. (a)                |

| Channel I-V characteristic (b) transfer curve (W/L=24/8µm)77                                          |

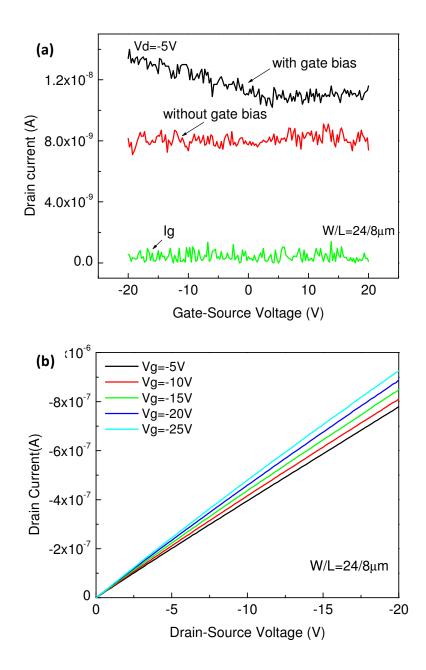

| Fig 4.9 (a) Transfer curve, (b) output characteristics of $Cu_2O$ TFT (RF 50W, thickness;             |

| 55nm)                                                                                                 |

| Fig. 4.10 I-V characteristics of $Cu_2O$ (a) before and after liftoff process, and (b)                |

| according to channel thickness variation                                                              |

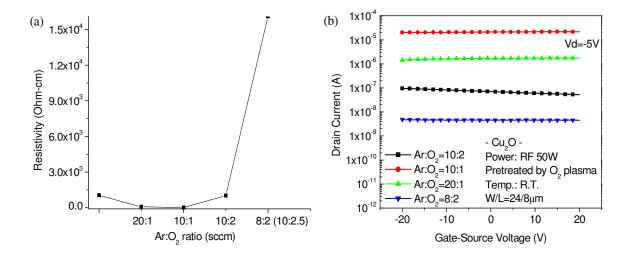

| Fig. 4.11 According to the variation of $Ar:O_2$ ratio during sputtering process, (a)                 |

| resistivity variation of Cu <sub>2</sub> O, (b) transfer curve of Cu <sub>2</sub> O TFTs81            |

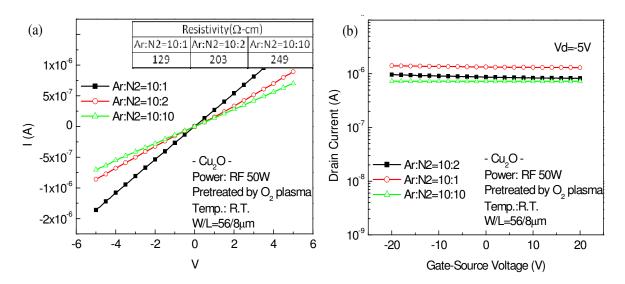

| Fig. 4.12 According to the variation of $Ar:N_2$ ratio during sputtering process, (a) I-V             |

| characteristics and (b) transfer curve of $Cu_2O$ TFT                                                 |

| Fig. 4.13 (a) TFT structure, (b) I-V characteristic, and (c) transfer curve of $Cu_2O$ TFT.           |

| Substrate was annealed at 200°C for 10min before Cu <sub>2</sub> O deposition82                       |

| Fig. 4.14 (a) TFT structure, (b) I-V characteristic, and (c) transfer curve of $Cu_2O$ TFT.           |

| Substrate was annealed at 500°C for 5min before Cu <sub>2</sub> O deposition                          |

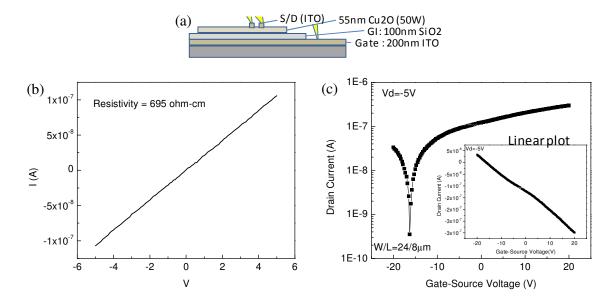

| Fig. 4.15 (a) XRD peaks for $Cu_2O$ films according to deposition temperature (room                   |

| temperature (R.T.) and 200°C). [Adapted from Ref.15]                                                  |

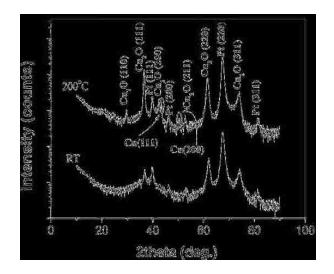

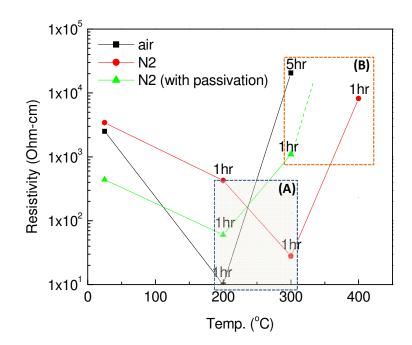

| Fig. 4.16 Transfer curve of $Cu_2O$ TFT according to annealing conditions. (a) in air (b) in               |

|------------------------------------------------------------------------------------------------------------|

| N <sub>2</sub> (c) in N <sub>2</sub> (TFT with SiOxNy passivation)85                                       |

| Fig. 4.17 Resistivity variation of $Cu_2O$ layer as a function of annealing time in air and $N_2$          |

|                                                                                                            |

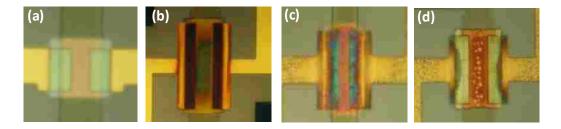

| Fig. 4.18 Optical images of $Cu_2O$ TFTs (a) as-fabricated, (b) after annealing in air at                  |

| 300°C for 5hrs, (c) after annealing in $N_2$ at 400°C for 1hr, (d) after annealing in $N_2$ at             |

| 300°C for 1hr (with SiO <sub>x</sub> N <sub>y</sub> passivation)                                           |

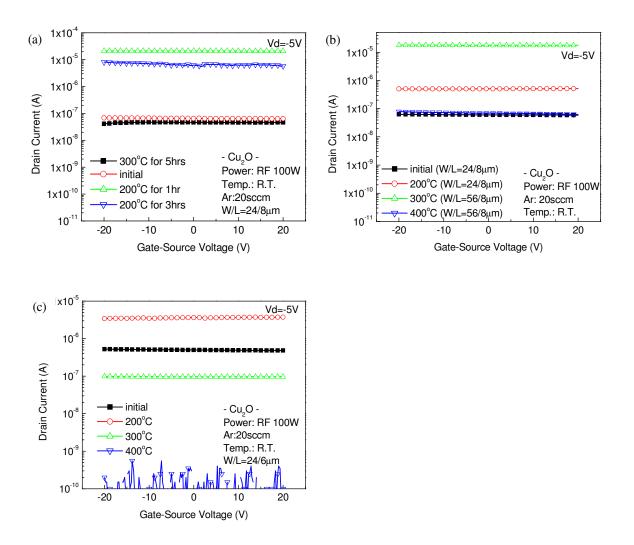

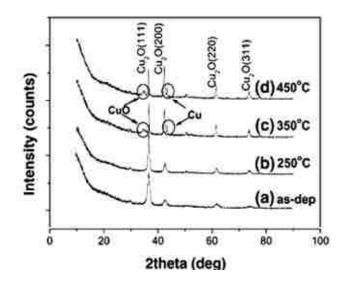

| Fig. 4.19 XRD peaks of $Cu_2O$ with the annealing temperature in $N_2$ ambient for 1min                    |

|                                                                                                            |

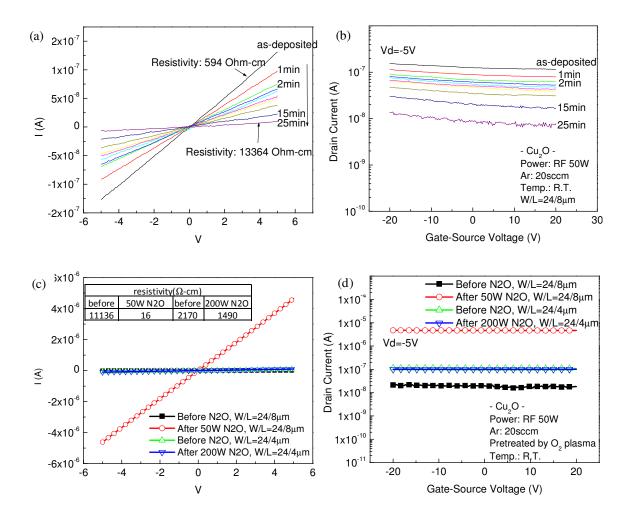

| Fig. 4.20 (a) and (c): I-V characteristics, (b) and (d): transfer curve of Cu <sub>2</sub> O TFT. (a) and  |

| (b): oxygen plasma with 100W RF power. (c) and (d): $N_2O$ plasma with 50W and 200W                        |

| RF power                                                                                                   |

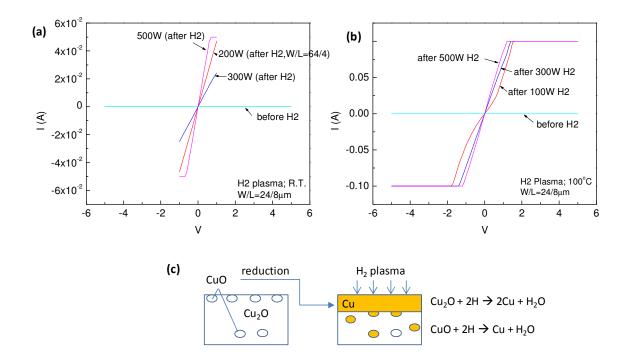

| Fig. 4.21 I-V characteristics of $Cu_2O$ films after $H_2$ plasma. (a) at room temperature for             |

| 1min, (b) at 100°C for 1min. (c) is a schematic of $H_2$ plasma effect on Cu <sub>2</sub> O film           |

| including CuO phase                                                                                        |

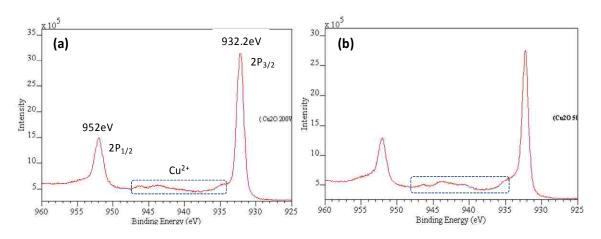

| Fig. 4.22 XPS analysis of $Cu_2O$ films. (a) RF deposition power of 200W, and (b) 50W.                     |

|                                                                                                            |

| Fig. 4.23 XPS analysis of Cu <sub>2</sub> O powder obtained from 99.99% Cu <sub>2</sub> O sputter target93 |

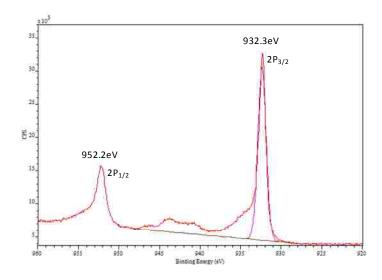

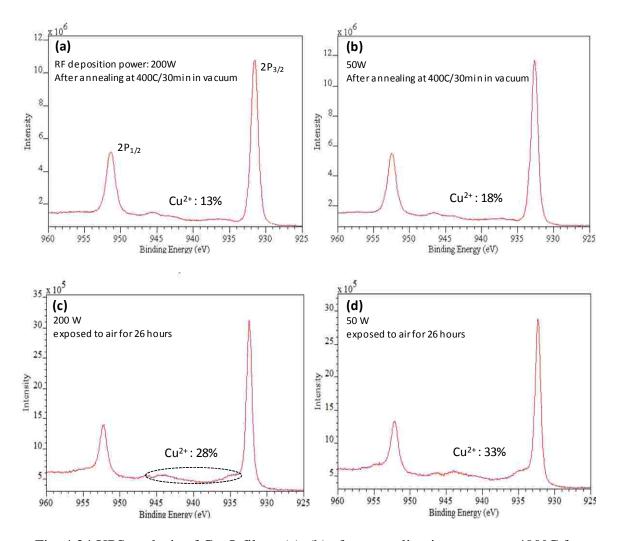

| Fig. 4.24 XPS analysis of $Cu_2O$ films. (a), (b) after annealing in vacuum at 400°C for                   |

| 30min, and then (c), (d) exposed to air for 26hrs94                                                        |

| Fig. 4.25 Effect of vacuum annealing. (a) I-V characteristic, (b) transfer curve of $Cu_2O$                |

| TFT95                                                                                                      |

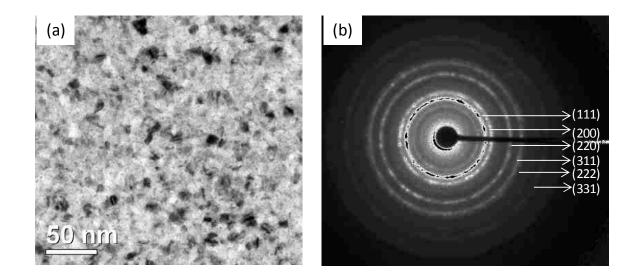

| Fig. 4.26 (a) TEM image and (b) SAD patterns of the as-deposited Cu <sub>2</sub> O film95                 |

|-----------------------------------------------------------------------------------------------------------|

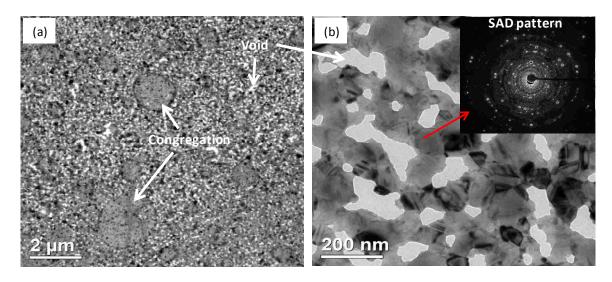

| Fig. 4.27 (a), (b) TEM image and (b), (c) SAD pattern of the $Cu_2O$ film annealed at                     |

| $300^{\circ}$ C for 30min in vacuum (base pressure; $9 \times 10^{-7}$ Torr)                              |

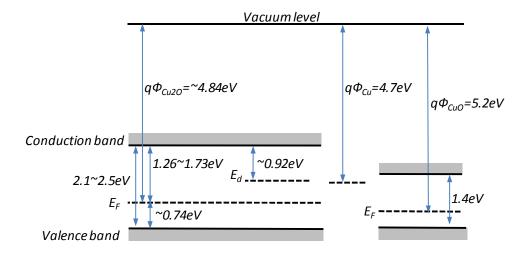

| Fig. 4.28 Energy band structure of Cu <sub>2</sub> O, Cu and CuO96                                        |

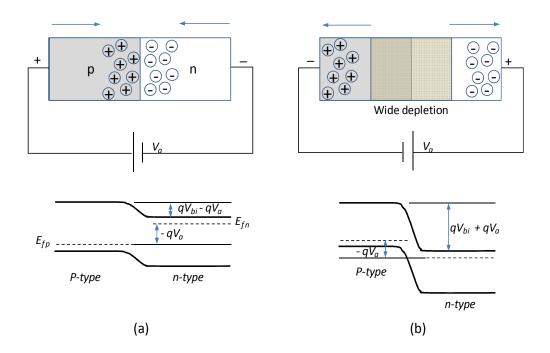

| Fig. 4.29 Schematic space-charge model for p-n junction and energy-band diagram                           |

| (a) forward bias (b) reverse bias                                                                         |

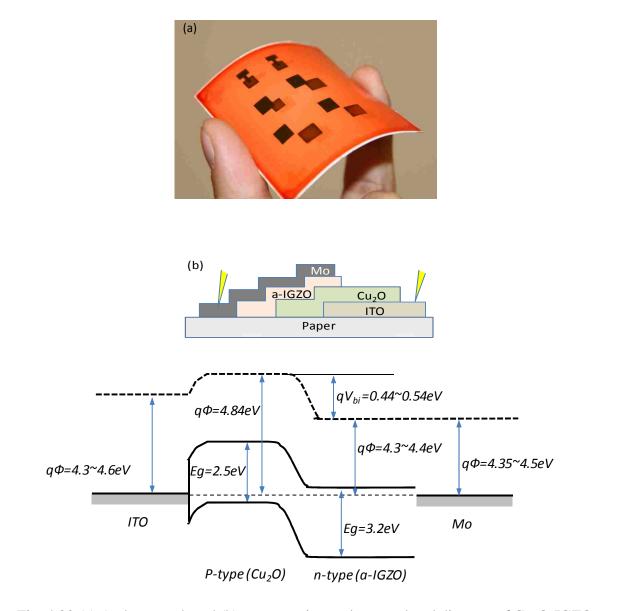

| Fig. 4.30 (a) A photograph and (b) cross-section and energy band diagram of $Cu_2O$ -IGZO                 |

| P-N diode on paper substrate100                                                                           |

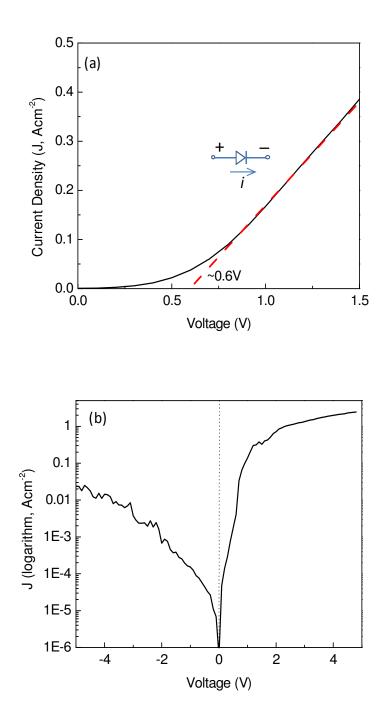

| Fig. 4.31 J-V characteristics of Cu <sub>2</sub> O-IGZO P-N diode on paper substrate, (a) linear plot     |

| (b) logarithmic plot101                                                                                   |

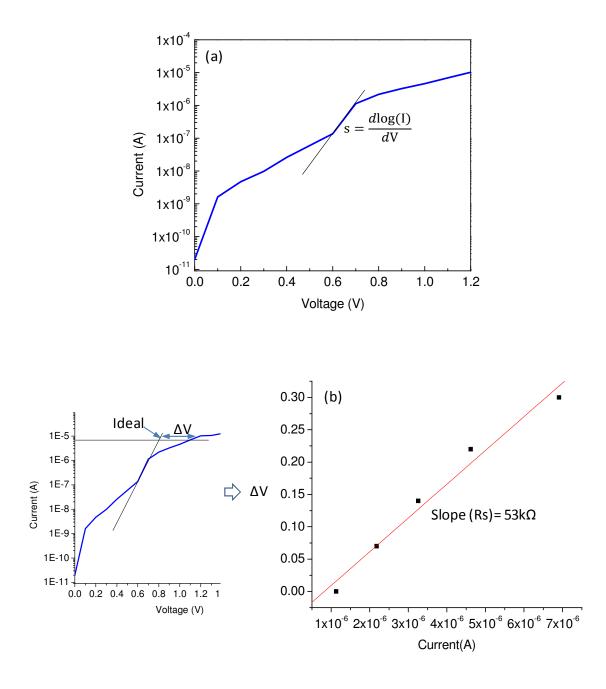

| Fig. 4.32 (a) Log(I) versus V (b) $\Delta V$ versus I plot to determine Rs for Cu <sub>2</sub> O-IGZO P-N |

| diode102                                                                                                  |

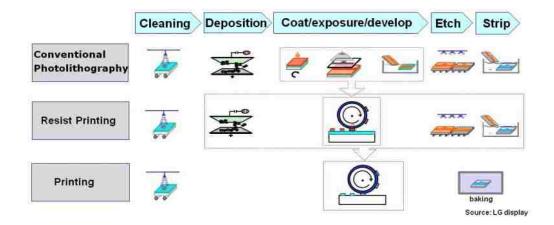

| Fig. 5.1 Process schematic of photolithography, resist printing, and direct printing                      |

| process                                                                                                   |

| Fig. 5.2 Schematic of gravure printing110                                                                 |

| Fig. 5.3 Conventional offset lithography111                                                               |

| Fig. 5.4 Schematic of screen printing112                                                                  |

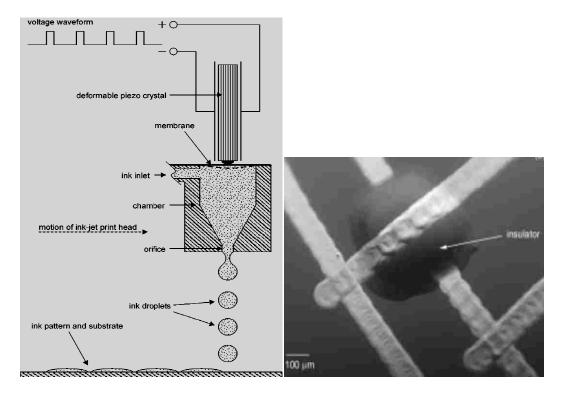

| Fig. 5.5 Schematic of the piezo inkjet printing system and optical image of printed                       |

| 1                                                                                                         |

| electrode and insulator                                                                                   |

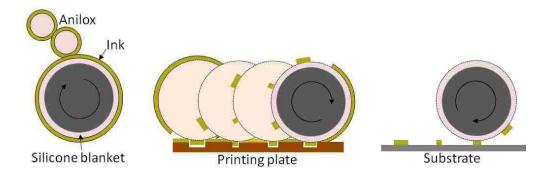

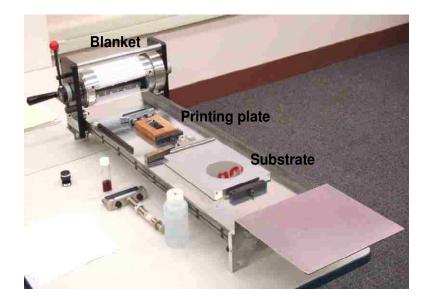

| Fig. 5.6 Schematic of a modified offset roll printing115                                                  |

|                                                                                                           |

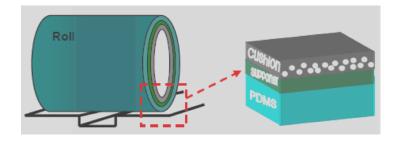

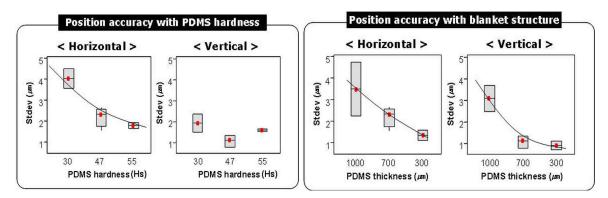

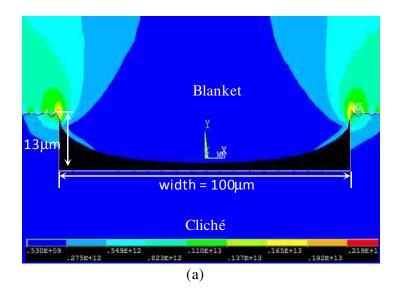

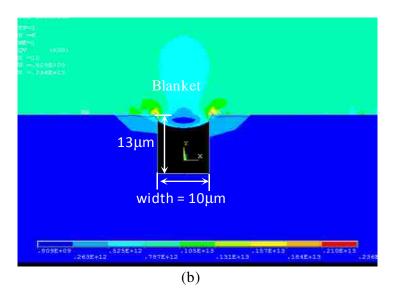

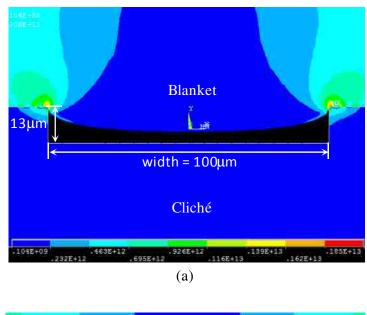

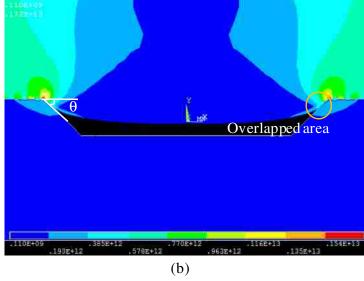

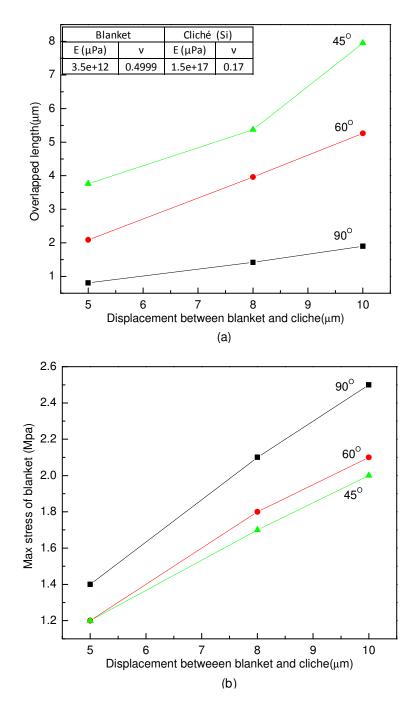

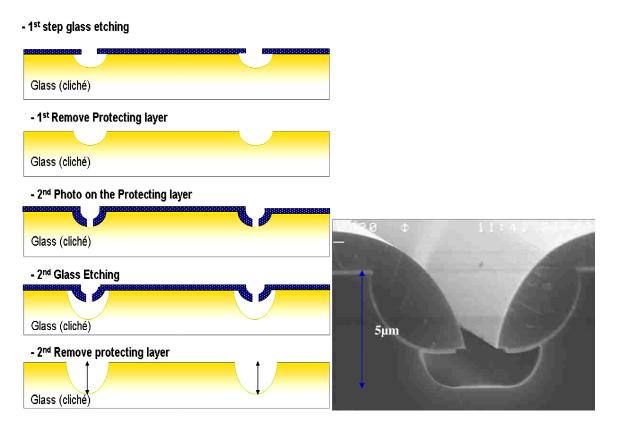

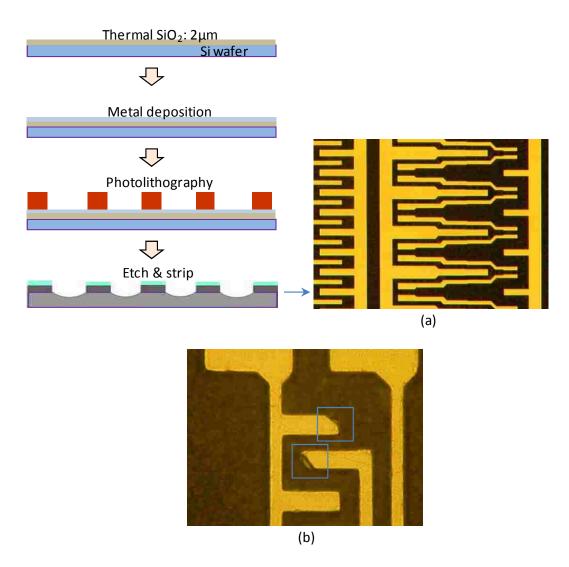

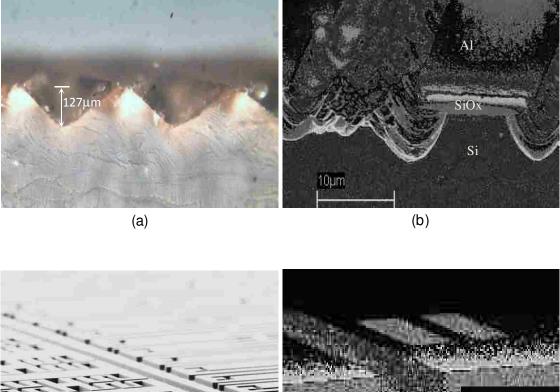

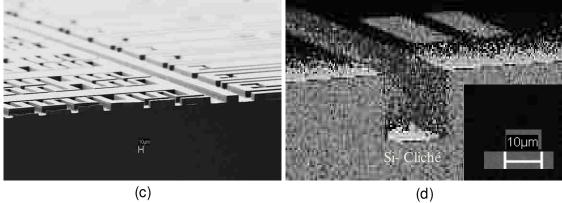

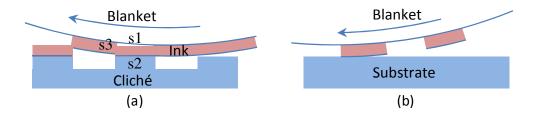

Fig. 5.9 Variation of position accuracy with PDMS hardness and thickness......117 Fig. 5.10 Surface energy measured by dynamic sessile drop method. Distilled water (polar) and diiodemethane (nonpolar, hydrophobic) are used as standard test liquids....117 Fig. 5.11 Finite element analysis to investigate blanket deformation with the variation of cliché width (a) 100µm (b) 10µm, under 10µm vertical motion of the stage towards the Fig. 5.12 Finite element analysis to investigate overlapped area between a blanket and the sidewall of cliché with the variation of sidewall's angle ( $\theta$ ) (a)  $\theta = 90^{\circ}$  (b) $\theta = 45^{\circ}$ (conventional cliché angle), under 5µm vertical motion of the stage towards the blanket Fig. 5.13 Finite element analysis (a) overlapped length between a blanket and the sidewall of cliché (b) the maximum stress of the blanket contacted with a cliché as a function of roll pressure (controlled by the height of cliché stage). The angle of sidewall of a cliché split with 45°, 60°, and 90°. The pattern width used for simulation is 100µm Fig. 5.14 The process step to fabricate the glass printing plate by using two step etching and a cross sectional view of the multi-etched cliché plate ......123 Fig. 5.15 Schematic of cliché fabrication method by using PE mode dry-etch (a) Optical image of cliché (b) shoulder of metal layer worn out after rolling ......125 Fig. 5.16 (a) Optical cross-section of a conventional flexo plate, (b) SEM image of the Sicliché etched by PE mode dry-etch, (c) and (b) SEM images of the Si-cliché etched by

| Fig. 5.17 Optical images of the Si-cliché etched by the deep RIE127                       |

|-------------------------------------------------------------------------------------------|

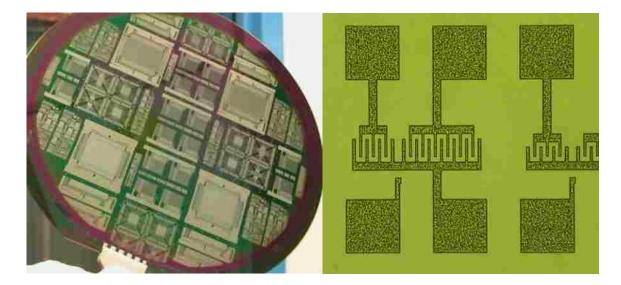

| Fig. 5.18 Dynamic sessile drop method128                                                  |

| Fig. 5.19 Concept of ink transfer (a) from a blanket to a cliché, (b) from a blanket to a |

| substrate130                                                                              |

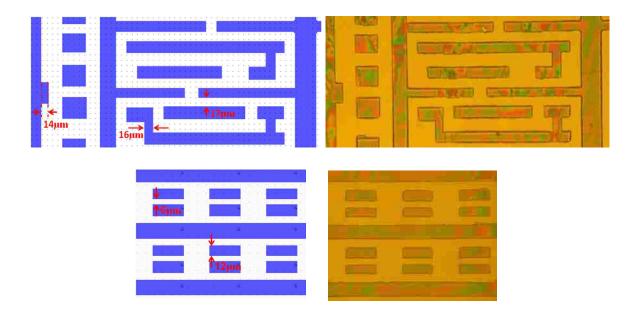

| Fig. 5.20 Design of test patterns for a modified offset roll printing                     |

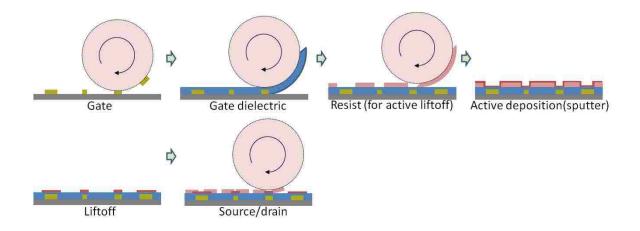

| Fig. 5.21 Concept of TFT fabrication process using the modified offset roll printing and  |

| the liftoff of semiconductor133                                                           |

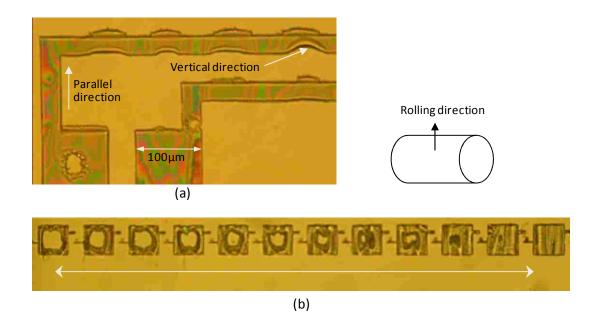

| Fig. 5.22 (a) Edge shape according to the rolling direction under high rolling speed      |

| (~100mm/sec) (b) missing patterns by non-uniform rolling pressure134                      |

| Fig. 5.23 Design of patterns (left) and corresponding printed etch-resists (right)135     |

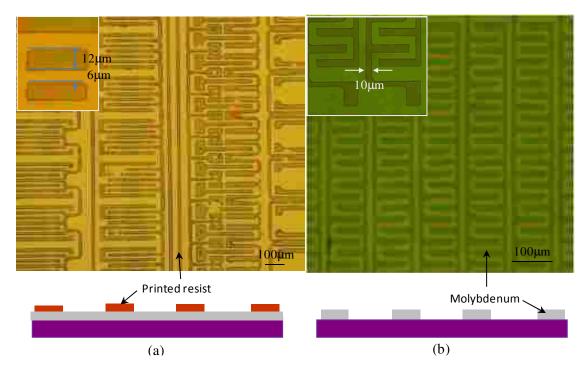

| Fig. 5.24 (a) Printed etch-resist (b) molybdenum pattern using the printed etch-resist136 |

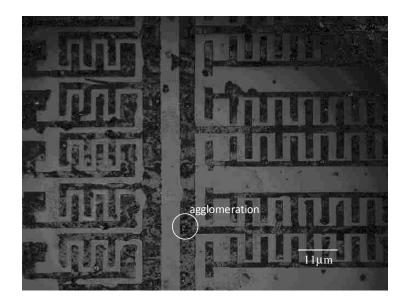

| Fig. 5.25 Optical microscope image of printed silver-paste                                |

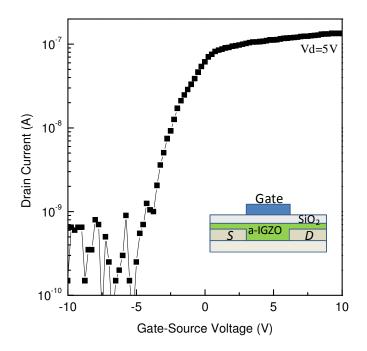

| Fig. 5.26 Electrical transfer curve of a-IGZO TFT fabricated by using the printed etch-   |

| resist                                                                                    |

| Fig. 5.27 Imprint lithography process                                                     |

| Fig. 5.28 Novel imprint lithography process and printed polymer patterns139               |

| Fig. 6.1 Transfer curves of top gate P3HT TFT (a) PMMA and (b) CYTOP (low polarity        |

| dielectric) as the dielectric145                                                          |

| Fig. 6.2 Combination of an offset roll printing and inkjet printing for TFT               |

| fabrication146                                                                            |

### Abstract

Flexible electronics is an emerging next-generation technology that offers many advantages such as light weight, durability, comfort, and flexibility. These unique features enable many new applications such as flexible display, flexible sensors, conformable electronics, and so forth. For decades, a variety of flexible substrates have been demonstrated for the application of flexible electronics. Most of them are plastic films and metal foils so far. For the fundamental device of flexible circuits, thin film transistors (TFTs) using poly silicon, amorphous silicon, metal oxide and organic semiconductor have been successfully demonstrated. Depending on application, low-cost and disposable flexible electronics will be required for convenience. Therefore it is important to study inexpensive substrates and to explore simple processes such as printing technology.

In this thesis, paper is introduced as a new possible substrate for flexible electronics due to its low-cost and renewable property, and amorphous indium gallium zinc oxide (a-IGZO) TFTs are realized as the promising device on the paper substrate. The fabrication process and characterization of a-IGZO TFT on the paper substrate are discussed. a-IGZO TFTs using a polymer gate dielectric on the paper substrate demonstrate excellent performances with field effect mobility of ~20 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, on/off current ratio of ~10<sup>6</sup>, and low leakage current, which show the enormous potential for flexible electronics application. In order to complement the n-channel a-IGZO TFTs and then enable complementary metal-oxide semiconductor (CMOS) circuit architectures, cuprous oxide is studied as a candidate material of p-channel oxide TFTs.

In this thesis, a printing process is investigated as an alternative method for the fabrication of low-cost and disposable electronics. Among several printing methods, a modified offset roll printing that prints high resolution patterns is presented. A new method to fabricate a high resolution printing plate is investigated and the most favorable condition to transfer ink from a blanket to a cliché is studied. Consequently, a high resolution cliché is demonstrated and the printed patterns of 10µm width and 6µm line spacing are presented. In addition, the top gate a-IGZO TFTs with channel width/length of 12/6µm is successfully demonstrated by printing etch-resists.

This work validates the compatibility of a-IGZO TFT on paper substrate for the disposable microelectronics application and presents the potential of low-cost and high resolution printing technology.

## **Chapter 1**

### Introduction

#### **1.1 Research motivation**

Flexible electronics is an emerging area with possible applications in displays, sensors, medical electronics, identification tags, smart cards, and so forth [1-3]. Advantages of the flexible electronics are bendable, conformally shaped, lightweight, unbreakable, and roll-to-roll manufacturable. Therefore, they have the potential to accomplish novel applications that are not restricted by the use of rigid substrates.

In most cases, flexible electronics includes a flexible substrate and essential circuits that consist of several thin film devices. A variety of flexible substrates, including metal foil, thin glass, and plastic film have been investigated for the application of flexible electronics [4, 5]. Plastic substrate is generally transparent and flexible, so the research of flexible substrates has been focused on plastic substrates for a long time. However, most of them have critical drawbacks, such as large thermal expansion causing the misalignment of layer to layer during the TFT process and low process temperature impeding the performance of the TFT device. Thin glass (~100µm) is stable up to 500°C,

so high performance TFT device can be fabricated on it. Furthermore, it does not require any gas barrier or planarization layer. However, handling thin glass substrate is challenging due to its fragile nature. Metal substrate such as stainless steel foil offers excellent thermal stability and high mechanical strength, but it involves planarization process and opaque nature. The cost of the introduced flexible substrates so far is typically higher than the commercial liquid crystal display (LCD) glass substrate. Compared to those substrates, paper substrate offers attractive advantages, such as lowcost, disposability, renewability, and abundant natural resource [6], which are appropriate for low-cost and novel application such as disposable electronics. The coefficient of thermal expansion (CTE) of paper substrate is approximately 2-16 ppm, smaller than that of most plastic substrates excluding polyimide (PI) film [7]. Besides, it turns yellow at 150°C, which is similar to the Tg value of most plastic substrates. Table 1.1 shows the cost and CTE comparison of commercially available flexible substrates. Compared to the other flexible substrates, the cost per unit area of paper substrates is 10% or less [7].

| Substrate            | Cost per unit area $(\$/m^2)$ | CTE (ppm/°C) |

|----------------------|-------------------------------|--------------|

| Stainless steel foil | 50~100                        | 10           |

| Polyimide film       | 100~120                       | 14~20        |

| Coated paper         | ~ 5                           | 2~16         |

Table 1.1 Cost and CTE comparison between paper and representative flexible substrates.

Organic thin film transistors (TFTs), amorphous silicon (a-Si) TFTs, low temperature poly silicon (LTPS) TFTs, and oxide TFTs have been realized on the flexible substrates [8-10]. Even though organic TFTs are one of the best candidates for flexible electronics due to their flexibility, there is still a need for flexible electronic materials that would offer more improved carrier mobility and long-term reliability [11]. LTPS and a-Si TFTs need to overcome process temperature issues since most flexible substrates require low process temperature [12, 13]. Thanks to high mobility, low processing temperature, and simple process, oxide TFTs, especially amorphous indium gallium zinc oxide (a-IGZO TFTs) have been studied for active matrix liquid crystal displays and active matrix organic light emitting diodes [14].

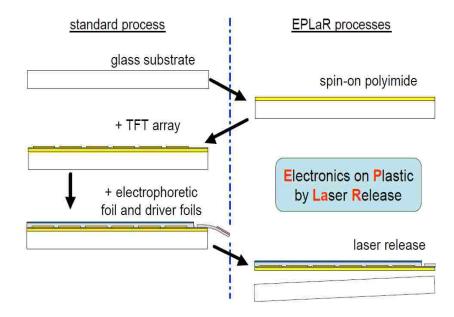

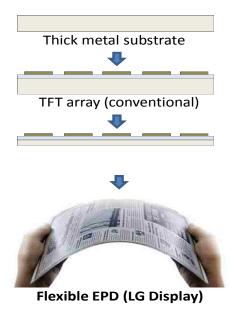

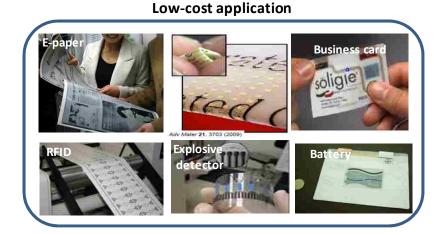

Meanwhile, many researchers have fabricated flexible electronics by using conventional photolithography process. However, free standing flexible substrate is obviously not applicable to mass-production, as robots generally handle the substrates in the fabrication plant (FAB). For this reason, a few handling techniques available in the FAB have been introduced. For the plastic substrate application, Philips Research Lab proposed EPLaR (Electronics on Plastic by Laser Release) in figure 1.1 [15]. After spincoating polyimide on glass substrate, a conventional TFT is fabricated on PI coating under 300°C. After fabricating all devices, the backside of glass is exposed to UV laser for the delamination. a-Si TFT and a-IGZO TFT can be fabricated on PI films by using this method. LG Display proposed the metal etching process to fabricate a metal foil based flexible substrate. A 600µm thick metal substrate is utilized to build TFT and display devices in conventional FAB, and the backside of metal substrate is etched by chemical up to around 100µm after finishing all processes as illustrated in figure 1.2 [16]. Printing is the ultimate process for low cost flexible electronics. However, the printing technology is still not matured to realize high resolution and high quality device since the inaccurate registration of printing causes the misalignment of layer to layer and the printable materials are not satisfying the requirements of device characteristics. On the other hand, this printing process is an excellent choice for low-cost applications, such as electronic newspaper, RFID, battery, simple sensor, and disposable electronic business card. Therefore printing process for paper substrate is investigated in chapter 5 for low-cost process.

Fig. 1.1 EPLaR process to fabricate flexible electronics [Adapted from Ref. 15].

Fig. 1.2 Backside etching process of a metal substrate for flexible electronics.

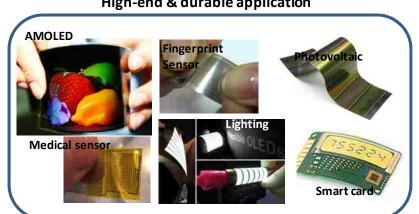

According to the requirements of each application, flexible electronics can be categorized into high-end and low-cost application as shown in figure 1.3. The combination of conventional TFT fabrication process and metal foil or PI substrate is preferable to high-end application. The combination of printing process and paper substrate is appropriate to the application requiring low-cost and disposable electronics.

#### High-end & durable application

Fig. 1.3 High-end and low-cost application of flexible electronics.

Recently, a-IGZO TFTs on a paper substrate have been reported with the potential for the new flexible electronics, as shown in figure 1.4 [17]. However, the morphology of the paper used in reference [17] was too rough for the fine featured TFTs; furthermore, low mobility and high gate leakage current were presented due to the gate dielectric of low temperature SiO<sub>2</sub> and rough surface. In order to verify the realization of high quality TFT device on paper, this work focuses on achieving high performance device on paper substrate and printing technology is also researched for low-cost process. Challenges in this study are 1) to identify and optimize a suitable paper substrate for TFT process, 2) to achieve high performance a-IGZO TFTs on the paper substrate at a low process temperature ( $\leq$ 150°C), 3) to explore p-channel oxide TFTs in order to complement the nchannel a-IGZO TFTs and then enable CMOS circuit architectures, and 4) to improve roll printing technology as an alternative method for low cost TFT fabrication.

Fig. 1.4 Schematic diagram and InGaZnOx TFT image on paper substrate [Adapted from Ref. 17].

#### **1.2 Dissertation Goals**

The first goal of this dissertation is to understand and optimize the paper substrate for microelectronics fabrication in order to achieve novel flexible electronics. The second goal is to validate a-IGZO TFT with excellent device performance on the paper substrate through studying polymer gate dielectric. The last goal is to investigate and improve printing technology to reduce manufacturing cost for the realization of flexible and disposable electronics. In addition, a new p-type metal oxide material is explored to attain CMOS circuit with a-IGZO TFT.

#### **1.3 Overview of the thesis**

In Chapter 2, the paper making process and the properties of paper substrate are introduced. Among various commercially available paper substrates, a promising candidate is selected. Thermal behavior and planarization process are explored for microelectronics fabrication. Patterning characteristics using photolithography is examined on the paper substrate. In the final part of this chapter, the realizable fabrication methods of flexible display are presented. Chapter 3 focuses on the fabrication and characterization of a-IGZO TFT devices on the paper substrate. Study of polymer gate dielectric is detailed and an approach to characterize the key parameters of TFT is discussed. P-type oxide semiconductors compatible with low process temperatures have been rarely studied due to limited and elusive material resources. Therefore, the cuprous oxide of p-type semiconductor is studied for the realization of CMOS with N-channel a-IGZO TFT in Chapter 4. Chapter 5 focuses on printing technology enabling to reduce manufacturing cost for the realization of low-cost flexible and disposable electronics. Principal printing technologies are introduced at first section and then a modified offset roll printing is investigated in detail. Chapter 6 summarizes the results of this thesis, provides conclusion and discusses the area of future research.

#### References

[1] W. Wong and A. Salleo, "Flexible Electronics", Springer, (2009)

[2] J. Engel, J. Chen and C. Liu, "Development of polyimide flexible tactile sensor skin",J. Micromech. Microeng., Vol. 13, pp. 359-366, (2003)

[3] L. Yang, L. J. Martin, D. Staiculescu, C.P. Wong, and M. M. Tentzeris, "*Conformal Magnetic Composite RFID for Wearable RF and Bio-Monitoring Applications*", IEEE Trans. Microwave Theory and Techniques, Vol. 56, No. 12, pp. 3223-3230, (2008)

[4] T. K. Chuang, M. Troccoli, P. C. Kuo, A. Jamshidi, and M. K. Hatalis, "Top-emitting 230 dots/in. Active-Matrix Polymer Light-Emitting Diode Displays on Flexible Metal Foil Substrates", Appl. Phys. Lett., Vol. 90, pp. 151114, (2007)

[5] C. D. Sheraw, L. Zhou, J. R. Huang, D. J. Gundlach, T. N. Jackson, M. G. Kane, I. G. Hill, M. S. Hammond, J. Campi, B. K. Greening, J. Francl, and J. West, "Organic thinfilm transistor-driven polymer-dispersed liquid crystal displays on flexible polymeric substrates", Appl. Phys. Lett., Vol. 80, No. 6, pp. 1088-1090, (2002)

[6] F. Eder, H. Klauk, M. Halik, U. Zschieschang, G. Schmid, and C. Dehm, "Organic electronics on paper", Appl. Phys. Lett., Vol. 84, No. 14, pp. 2673-2675, (2004)

[7] Daniel Tobjörk and Ronald Österbacka, "Paper Electronics", Adv. Mater. DOI: 10.1002/adma.201004692, (2011)

[8] G. H. Gelinck, H. E. A. Huitema, E. V. Veenendaal, E. Cantatore, L. Schrijnemakers, J. B. P. H. Van Der Putten, T. C. T. Geuns, M. Beenhakkers, J. B. Giesbers, B. H. Huisman, E. J. Meijer, E. M. Benito, F. J. Touwslager, A. W. Marsman, B. J. E. Ven Rens, and D. M. De Leeuw, *"Flexible active-matrix displays and shift registers based on solution-processed organic transistors"*, Nature materials, Vol. 3, pp. 106-110, (2004)

[9] K. Long, A. Z. Kattamis, I. C. Cheng, H. Gleskova, S. Wagner, and J. C. Sturm, "Stability of Amorphous-Silicon TFTs Deposited on Clear Plastic Substrates at 250°C to 280°C", IEEE Electron Device Lett., Vol.27, No. 2, pp. 111-113, (2006)

[10] K. Nomura, H. Ohta, A. Takagi, T. Kamiya, M. Hirano, and H. Hosono, "Roomtemperature fabrication of transparent flexible thin-film transistors using amorphous oxide semiconductors", Nature, Vol. 432, pp. 488-492, (2004)

[11] N. B. Choi, D. W. Kim, H. S. Seo, C. D. Kim, H. C. Kang, M. J. Kim, and I. J. Chung, *"Fine-Patterned Organic Thin Film Transistors using Solution Organic Semiconductor Materials"*, Jpn. J. Appl. Phys., Vol. 46, No. 3B, pp. 1333-1336, (2007)

[12] D. Striakhilev, A. Nathan, Y. Vygranenko, P. Servati, C. Lee, and A. Sazonov, "Amorphous Silicon Display Backplanes on Plastic Substrates", J. Display Technol., Vol. 2, No. 4, pp. 364-371, (2006)

[13] M. N. Troccoli, A. J. Roudbari, T. Chuang, and M. K. Hatalis, "*Polysilicon TFT circuits on flexible stainless steel foils*", Solid State Electronics, Vol. 50, pp. 1080-1087, (2006)

[14] J. Park, T. Kim, D. Stryakhilev, J. Lee, S. An, Y. Pyo, D. Lee, Y. Mo, D. Jin, and H. Chung, *"Flexible full color organic light-emitting diode display on polyimide plastic substrate driven by amorphous indium gallium zinc oxide thin-film transistors"*, Appl. Phys. Lett., Vol. 95, pp. 013503, (2009)

[15] Ian French, "Gen II e-Books with Flexible Displays", Flexible Electronics & Displays Conference, (2009)

[16] Y. I. Park, "*Flexible & E-Paper Technology in LG Display*", Flexible Electronics & Displays Conference, (2011)

[17] W. Lim, E. A. Douglas, D. P. Norton, S. J. Pearton, F. Ren, Y. W. Heo, S. Y. Son, and J. H. Yuh, "Low-voltage indium gallium zinc oxide thin film transistors on paper substrates", Appl. Phys. Lett. 96, pp. 053510, (2010)

### **Chapter 2**

### Paper substrate for flexible and disposable electronics

In this chapter, paper is introduced as a promising substrate for flexible and disposable electronics. First main components and fabrication process of paper are presented, and then the properties of paper substrates are discussed and compared with different substrates, such as metal foil and plastic. In the last part of this chapter the surface roughness of paper substrate and planarization layer are discussed for the realization of micron size features. Glossy paper planarized by acrylate polymer is introduced as a new low cost flexible substrate and its rms surface roughness of 1nm is comparable to commercial glass substrate.

#### 2.1 Paper structure and papermaking process

Paper is one of very familiar substrates for human being for a long time, and it has been utilized as material for packaging, exhibiting and storing information. In addition, paper is the most inexpensive flexible substrate in daily life due to abundant natural resources, and eco-friendly since it is composed of renewable material. For these advantages, paper has recently been explored as a potential substrate for low-cost and disposable electronics [1-3]. Paper is made by pressing and drying process of pulp, which is a mixture of cellulose fibers [4]. Cellulose fiber with the molecular formula of  $(C_6H_{10}O_5)_n$  consisted of de glucose is the structural component of the cell wall of wood as described in figure 2.1 [5]. Wood also contains a dark element, lignin that binds the cellulose fibers together [5]. The exposure of lignin to air and sunlight turns paper yellow because of oxidation; lignin molecules react and become less stable [6]. To eliminate lignin for a fine white paper, a chemical solvent process is utilized. The paper made without lignin is white and resists yellowing.

Fig. 2.1 Structure of cellulose. Cellulose is the main component of paper [Copyright; US

DOE. 2005. Genomics : GTL Roadmap].

Fig. 2.2 SEM micrographs of (a) cellulose fiber (b) the cross-section of newsprints (c) supercalendered paper (d) coated paper [Adapted from Ref. 7].

Figure 2.2 is the SEM images of various paper substrates [7]. The cellulose fibers in paper are bound by hydrogen bonding and the fiber matrix is filled by fillers including calcium carbonate (CaCO3), chalk, and clay, which increase the uniformity of surface and brightness of paper [8, 9]. The surface of supercalendered paper and coated paper is smooth so it offers excellent potential for the fabrication of microscale electronics on paper. Figure 2.3 shows the papermaking process that consists of the paper forming section, the press section and the drying section to reduce the moisture [10]. At the beginning of the process, wood logs are chipped after debarking process. Heating in digester vessel with chemicals to dissolve the lignin makes the cellulose fibers suspended

in water. Then the pulp is washed to eliminate the chemicals and is passed through refiner after bleaching process. The refiner coarsens the surface of the cellulose fibers so they adhere together when shaped into a sheet. Dyes and additives are added to give the desired properties in additive tank. Wet pulp then moves to the forming fabric that makes the fibers linked and forms a mat of paper. The paper passes through a series of heated cylinders after pressed between water-absorbing textiles. Then a size press supplies a starch solution to both sides of the paper to prevent ink absorption into paper during printing. After another drying, the paper travels through a series of hard pressure rollers located at the end of a papermaking process, which is named as a calendering process that provides a smooth surface of the paper.

Fig. 2.3 Paper making process [Copyright; Lindenmeyr Munroe & International Paper].

#### 2.2 Properties of paper substrate

The advantages and drawbacks of paper substrate are compared with stainless steel foil and plastic substrate in Table 2.1, and the material properties of typical flexible substrates are summarized in Table 2.2. Most of plastic substrates have demerits of high coefficient of thermal expansion (CTE) that causes thermal stress between thin film and substrate attributed to thermal TFT process. The high CTE and low Tg are also problems in the curing step of printed organic material in printing process, thus finally deforms the substrate. The deformation induces the misalignment of layer to layer and the peeling defect of thin film. Among plastic substrates in table 2.2, polyethylene naphthalate (PEN) and polyimide (PI) would be possible choices due to their thermal (CTE of ~20ppm) and chemical reliability [11]. The stainless steel substrate such as SUS 304 and SUS 430 offers the strong advantages of low CTE (~10ppm) and high process temperature  $(\sim 600^{\circ}C)$ , which can integrate the high quality device on it. However the stainless steel foil contains the surface roughness from 0.1 to 1µm related to rolling direction and irregular particulate inclusion. Surface polishing and planarization coating are the common approach to attain the smooth surface. However, the use of organic planarization layer that only withstands below 300°C restricts the process temperature through TFT fabrication.

Compared to stainless steel and plastic substrate, the strongest merits of paper substrate are human-friendly and low-cost attributed to easy recycling and abundant natural resources. Recycled pulp that unwanted components are removed by chemical is also used as raw material in paper fabrication process [12]. The main challenge of paper substrate is to control the surface roughness and to prevent any absorption of solvents and chemicals. Supercalendaring process that is a stack of calenders consisting of alternating rolls is recommended to increase paper's density, smoothness and gloss after the paper making process [13]. In addition, it is necessary to minimize particulate inclusion through maintaining the clean roll process. Polymer coating on both side of paper is beneficial to planarize the rough surface and to avoid the absorption of solvents or water.

Table 2.1 Advantages and drawbacks of each substrate for flexible electronic

| Substrates              | Advantages                                                                              | Drawbacks                                                                                    |  |

|-------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|

| Paper                   | Inexpensive, disposable,<br>renewable, abundant natural<br>resource, low CTE            | Opaque, rough surface, low<br>process temperature, weak<br>resistance to chemical absorption |  |

| Plastic                 | Transparent, smooth surface                                                             | High CTE, low process<br>temperature, moisture and gas<br>barrier                            |  |

| Stainless<br>steel foil | Low CTE, strong resistance to<br>chemicals, impermeability, high<br>process temperature | Opaque, rough surface                                                                        |  |

| application | [7, | 15] | • |

|-------------|-----|-----|---|

|-------------|-----|-----|---|

Thermal resistance also needs to be considered as the important characteristic of paper substrate for the TFT application since substrates are exposed to thermal step during photolithography and printing process. Normal paper turns yellow at 150°C and ignites at 233°C [14]. Yellowish temperature of 150°C is similar to the Tg value of most plastic substrates, except for PI and polyether sulfone (PES). Compared to polymer

substrates that offer high CTE of 20~70ppm, the paper substrate presents relatively lower CTE of 2~16ppm and thus is expected to offer dimensional stability through the TFT fabrication process [7].

|                                                                 | Properties |                        |                      |                 |  |  |

|-----------------------------------------------------------------|------------|------------------------|----------------------|-----------------|--|--|

| Substrate Type                                                  | Tg<br>(°C) | Chemical compatibility | Transmittance<br>(%) | CTE<br>(ppm/°C) |  |  |

| LCD Glass [15]                                                  | 600        | Good                   | ~92                  | 5               |  |  |

| Stainless Steel Foil [15]                                       | >600       | Good                   | -                    | 10              |  |  |

| PET (Polyethylene terephthalate,<br>Melinex <sup>®</sup> ) [16] | 78         | Weak                   |                      | 20-25           |  |  |

| PC (Poly Carbonate, Lexan®) [16]                                | ~150       | Weak (in stripper)     | ~90                  | 60~70           |  |  |

| PES (Polyether sulfone,<br>Sumilite <sup>®</sup> ) [16]         | ~220       | Weak (in stripper)     | ~90                  | ~50             |  |  |

| PEN(Polyethylene Naphthalate,<br>Teonex <sup>®</sup> ) [16]     | 121        | Good                   | ~90                  | 18~20           |  |  |

| PI (Polyimide, Kapton®) [17]                                    | ~370       | Good                   | Yellow               | 14~20           |  |  |

| Paper (cellulose) [7]                                           | ~150       | Weak                   | -                    | 2~16            |  |  |

Table 2.2 Material properties of typical flexible substrates.

## **2.3 Paper selection for TFT fabrication**

Among commercially available paper substrates, a silicone coated parchment paper is known to withstand temperature up to ~200°C and also prevents the absorption of water and solvent due to its hydrophobic surface. To prevent unnecessary misunderstandings, parchment paper is different from parchment, animal skin [18]. The present parchment paper is made by paper pulp followed by silicone coating with high density, stability, heat resistance, and low surface energy. Thus it offers non-stick property for baking in an oven. However, its surface is too rough to fabricate fine featured TFTs, even after planarization coating, since it is produced for baking, not electronic device application. In order to successfully fabricate a silicone coated parchment paper for electronic device application, silicone needs to be coated after supercalendering process. This approach can be achieved by paper making company which possesses all equipments.

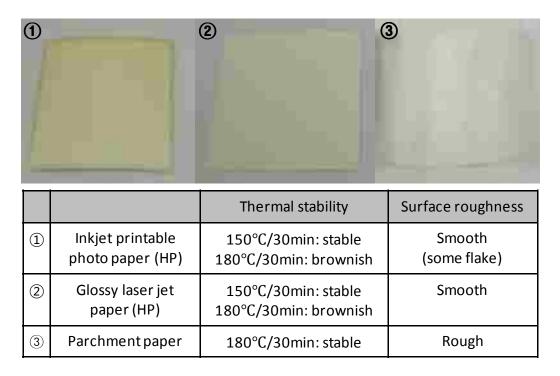

In this study, two kinds of glossy printable papers are examined due to its smooth surface. One is the inkjet printable photo paper (HP products) in figure 2.4 consisting of top coating (receptive coating and polyethylene), cellulose paper, and back side coating of polymer. The receptive coating is designed to absorb ink quickly so it absorbs water and solvents during TFT process. The other paper is a glossy laser jet paper designed to offer a higher heat resistance to prevent the deformation of the paper during printing. Gloss is achieved by the calendaring process with highly polished chromium cylinder on a coated surface. Figure 2.5 shows the results of thermal stability of each paper. The color of papers is not changed by the thermal annealing of 150°C for 30min, but become brownish at 180°C.

Fig. 2.4 SEM cross-section of an inkjet printable photo paper [Copyright; HP].

Fig. 2.5 Optical images of each paper after annealing.

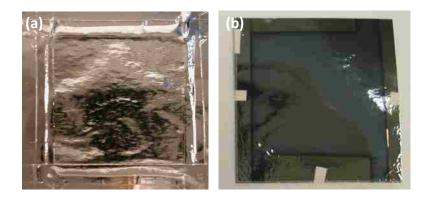

For coating test, an inkjet printable paper and a parchment paper are compared after planarization coating. Metal layer of molybdenium is deposited in sputter at room temperature and  $SiO_2$  is deposited in PECVD at 140°C. In figure 2.6, a parchment paper presents the rough surface wrinkled by the strain of the deposited Mo layer. On the other hand, the inkjet printable paper shows excellent heat resistance in PECVD and smooth surface. Even after the deposition of Mo and  $SiO_2$  double layer, the substrate is stable as shown in figure 2.6 (b).

Fig. 2.6 Optical images of (a) Mo on a silicone coated parchment paper (b) Mo and SiO<sub>2</sub> on an inkjet printable paper. Before deposition, planarization layer was coated on both papers.

## **2.4 Planarization and patterning properties**

In order to realize thin film based devices on a paper substrate, it is necessary to demonstrate that micron size features can be patterned on it. Compared to the commercial glass and silicon wafer substrate, the surface of typical papers is too rough to fabricate thin film electronics and thus planarization using polymer coating is considered to improve the surface morphology of papers in this chapter. The planarization layer has been typically prepared by spin coating and curing method. However, the spin coating on paper is not simple since paper is not rigid as much as glass and metal substrate. Therefore the suggested approach is to coat the planarization polymer at the coating process which already exists in the papermaking process. Some of papermaking processes, such as roll coating and calendar, need to be modified for electronic paper application. Table 2.3 shows the available planarization materials utilized to planarize the rough surface of metal foils and passivate the TFT [19]. These materials have been proven to be stable in all chemical used in TFT fabrication. Acrylate (AC818 from Kolon Chemical) is one of most popular material to planarize and passivate the color filter of LCD. Photoacryl (PC403 from JSR co.) is used as the passivation of TFT for high aperture ratio LCD. The recommended curing temperature of the two materials is 230°C for 30min. Cyclotene (BCB) is known to offer excellent planarization property, however it requires the long annealing time of 5 hr at 250°C.

| Material   | Model | Uses                              | Organic Laver   |

|------------|-------|-----------------------------------|-----------------|

| Acrylate   | AC818 | Planarization of LCD color filter | Organic Layer   |

| Photoacryl | PC403 | Passivation of LCD backplane      | Paper substrate |

| Cyclotene  | BCB   | Passivation of LCD backplane      |                 |

Table 2.3 Commercially available planarization materials.

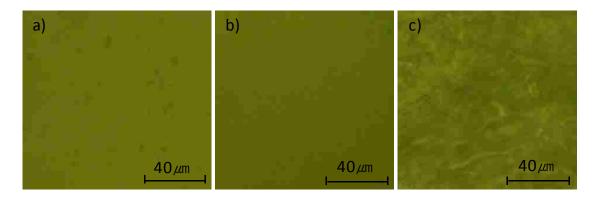

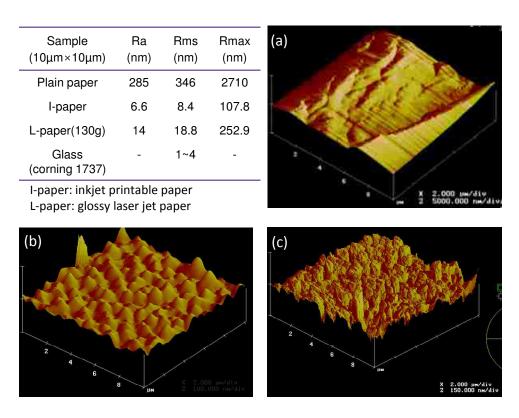

Figure 2.7 is the optical microscopic surface images of each paper substrate, and figure 2.8 presents atomic force microscopy (AFM) images of plain paper, inkjet

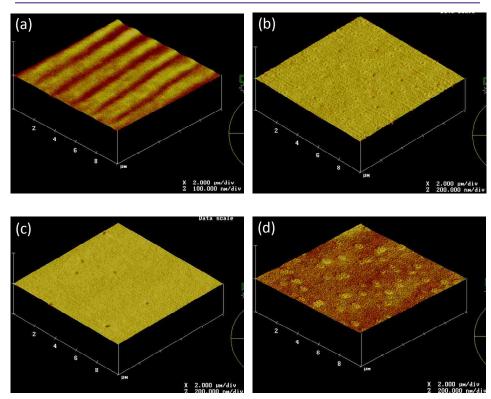

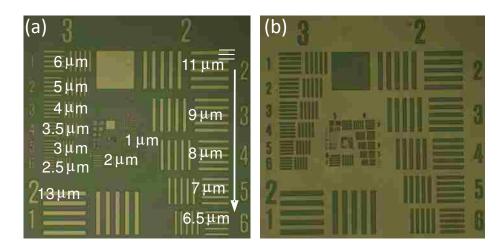

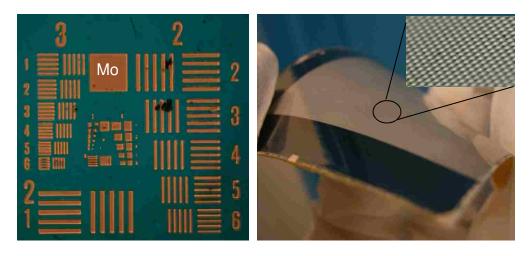

printable paper, and glossy laser jet paper. The inkjet printable paper offers smooth surface but it contains some microscopic cavities suspected to be created in papermaking process. A glossy laser jet paper doesn't include any cavity but it is rougher than the inkjet printable paper in AFM result. In case of a silicone coated parchment paper, the surface is very rough so it could not be measured by AFM. Even though the two printable papers present a good surface roughness, they are still rough for microelectronic fabrication and also need to be protected from any water and solvents absorption. Therefore, 3µm thick epoxy acrylate copolymer (AC-818 from Kolon Chemical) and photoacryl were coated on top side of two papers respectively and followed by curing at 150°C for 1hr. Surface roughness was analyzed by AFM before and after planarization. The glossy inkjet-printable paper and glossy laser jet paper substrates offer root-meansquare (RMS) roughness of 8.4nm and 18.8nm before planarization coating. However, they are reduced to 1~2nm after planarization in figure 2.9. These are quite analogous to the roughness (1~4nm) of typical glass substrate (Corning 1737). A glossy inkjet printable paper was selected to evaluate the patterning characteristics on it, because the thick glossy inkiet printable paper of 300µm is more useful for handling and spin-coating than thin laser jet paper of 100µm. After planarization, liftoff resist and photoresist were sequentially spin-coated on the paper and followed by baking process in oven at 150°C and 100°C, respectively. Then the substrate was exposed with a mask that contains resolution chart with known widths and spacing ranging from submicron to 13µm. Both positive and negative fine patterns were formed by photolithography on the planarized paper, and width and spacing of each pattern are well defined from 13µm to 1µm as

shown in figure 2.10. This result is also comparable to the typical TFT channel length of  $4\sim6\mu m$  for LCD. In addition, molybdenum (Mo) was deposited on the substrate in sputter chamber for liftoff process and patterned in edge bead removal (EBR) solution. Mo is also successfully formed on paper substrate as shown in figure 2.11.

Fig. 2.7 Optical microscopic images of paper surface a) inkjet printable paper, b) glossy laser jet paper, c) a silicon coated parchment paper.

Fig. 2.8 3D AFM images of (a) plain paper (b) glossy inkjet-printable paper (c) glossy

laser jet paper.

| Sample<br>(10μm×10μm) | Ra<br>(nm) | Rms<br>(nm) | Rmax<br>(nm) |

|-----------------------|------------|-------------|--------------|

| I-paper + AC818       | 1.0        | 1.2         | 7.4          |

| I-paper + PC403       | 0.3        | 0.5         | 15.6         |

| L-paper + AC818       | 0.9        | 1.7         | 27.7         |

| L-paper + PC403       | 1.6        | 2.0         | 16.9         |

| Glass (corning 1737)  | -          | 1~4         | -            |

Fig. 2.9 AFM images (a) acrylate (AC818) coated inkjet printable paper, (b) acrylate (AC818) coated glossy laser jet paper, (c) photoacryl (PC403) coated inkjet printable paper, (d) photoacryl (PC403) coated glossy laser jet paper.

Fig. 2.10 Optical microscopic images of photolithographically patterned resolution chart with known widths and spacings on planarized glossy paper. (a) positive patterns (b) negative patterns

Fig. 2.11 Molybdenum patterns on a paper substrate by using liftoff process

## References

[1] Adam C. Siegel, Scott T. Phillips, Michael D. Dickey, Nanshu Lu, Zhigang Suo, George M. Whitesides, *"Foldable Printed Circuit Boards on Paper Substrates"*, Advanced Functional Materials, Vol. 20, Issue 1, pp. 28–35, (2010)

[2] M. Härting, D.T. Britton, D. Knoesen, W. Egger, "Positron lifetime and micro structural characterization of a-Si:H deposited by low temperature HW-CVD on paper substrates", Applied Surface Science Vol. 252, Issue 9, pp. 3188-3193, (2006)

[3] J. Kim, S. Park, T. Jeong, M. Bae, S. Song, J. Lee, I. Han, D. Jung, and S. Yu, "*Paper as a Substrate for Inorganic Powder Electroluminescence Devices*", Electron Devices, IEEE Transactions on, Vol. 57, Issue 6, pp. 1470 – 1474, (2010)

[4] Jay Shah and R. Malcolm Brown, "*Towards electronic paper displays made from microbial cellulose*", Applied Microbiology and Biotechnology, Vol. 66, No. 4, pp. 352-355, (2005)

[5] J. Pérez, J. Muñoz-Dorado, T. de la Rubia and J. Martínez, "Biodegradation and biological treatments of cellulose, hemicellulose and lignin: an overview", International Microbiology, Vol. 5, No. 2, pp. 53-63, (2002)

[6] Cyril Heitner, "Photochemistry of Lignocellulosic Materials; Chapter1. Light-Induced Yellowing of Wood-Containing Papers", American Chemical Society, pp. 2–25, (1993)

[7] Daniel Tobjörk and Ronald Österbacka, "Paper Electronics", Adv. Mater. DOI: 1002/adma. 201004692, (2011)

[8] H. Greinecker, "Filler for paper, card or board, a process for its manufacture, and paper, card or board containing the filler", US Patent 4,405,744, (1983)

[9] Wadood Hamad, "*Cellulosic materials: fibers, networks, and composites*", Kluwer Academic Publishers, (2002)

[10] Sabit Adanur, "*Paper Machine Clothing: Key to the Paper Making Process*", Asten, (1997)

[11] J. Liu, T. Lee, C. Wen, and C. Leu, "*High-performance organic-inorganic hybrid plastic substrate for flexible displays and electronics*", J. Soc. Inf. Display, Vol. 19, Issue 1, pp. 63-69, (2011)

[12] D. Tatsumi, T. Higashihara, S. Kawamura and T. Matsumoto, "*Ultrasonic treatment to improve the quality of recycled pulp fiber*", Journal of Wood Science, Vol. 46, No. 5, pp. 405-409, (2000)

[13] K. Peiponen, M. Juuti, R. Silvennoinen, and A. Oksman, "Diffractive-opticalelement-based glossmeter and low coherence interferometer in assessment of local surface quality of paper", Opt. Eng. 45, pp. 043601, (2006)

[14] C. Schonfeld, "Device for fixing toner images", US Patent 6,067,437, (2000)

[15] William S. Wong, and Alberto Salleo, "Flexible electronics: materials and applications", Springer, (2009)

[16] W. A. MacDonald, M. K. Looney, D. MacKerron, R. Eveson, R. Adam, K. Hashimoto, K. Rakos, "*Latest advances in substrates for flexible electronics*", Journal of the SID 15/12, pp. 1075, (2007)

[17] DuPont, "Technical Data Sheet", (2011)

[18] Ronald Reed, "The nature and making of parchment", 1<sup>st</sup> edition, Elmete Press, (1975)

[19] N. Choi, "A 4 inch qVGA flexible AMOLED using a-Si TFT on ultra thin stainless steel foil", 7th Ann. Flexible Electronics & Displays Conference, Vol. 17, (2008)

# **Chapter 3**

# N channel a-IGZO TFT on paper substrate

a-IGZO TFTs is explored as the possible TFT technology on paper substrate in this chapter. First the fabrication approach of a-IGZO TFT on paper substrate is presented, and then polymer gate dielectric is discussed as the gate dielectric of a-IGZO TFT on paper substrate since paper only withstands up to 150°C. In addition, characterization method and results of the a-IGZO TFTs are detailed in the last part of this chapter. In summary, a-IGZO TFTs with methyl-siloxane based gate dielectric is fabricated on a glossy paper substrate at low processing temperature ( $\leq$ 150°C). Compared to the silicon dioxide gate dielectric deposited at 140°C in PECVD, a-IGZO TFTs using a methyl-siloxane based dielectric demonstrates excellent performances with field effect mobility of ~20 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>, on/off current ratio of ~10<sup>6</sup>, and low leakage current, which show the enormous potential for flexible electronics application.

#### **3.1 TFTs on paper substrate**

The development of electronics on paper substrate dates back to 1960s as Brody and colleagues at Westinghouse reported a TFT of tellurium on a strip of paper [1]. After this approach, TFTs on paper substrate have rarely reported for the past decades. Since the early 2000s, flexible electronics using plastic and metal foil substrate have been investigated by several research groups [2-7]. In 2004 Eder et al. presented pentacene TFT on paper with carrier mobility of  $0.2 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$  [8]. Even though organic TFT and a-Si:H TFT have been demonstrated on flexible substrates, device performance is limited by the low mobility and poor reliability (mobility of organic TFT;  $0.1 \sim 3 \text{cm}^2 \text{V}^{-1} \text{s}^{-1}$ , a-Si:H;  $0.5 \sim 1 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ ). After Hosono et al. presented a-IGZO TFT with the mobility of  $10 \text{cm}^2 \text{V}^{-1} \text{s}^{-1}$  on PET substrate in 2004 [9], a-IGZO TFT has been extensively studied for microelectronics application owing to high mobility, low processing temperature and simple process. In 2008, Fortunato et al. introduced the GIZO TFT using cellulose-fiberbased paper as gate dielectric [10]. Table 3.1 compares the properties of each TFT device available for microelectronics.

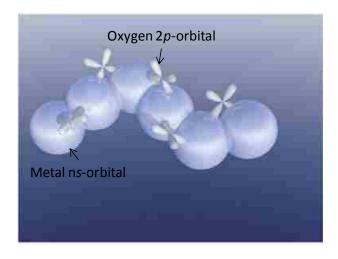

N-type amorphous oxide semiconductors such as a-IGZO have large electron mobility since the bottom of conduction band in these materials is mainly composed of spatially spread metal *s* orbitals that facilitate carrier transport. The magnitude of direct overlap between adjacent metal s orbitals is relatively large, and is not affected even in an amorphous structure because metal-oxygen-metal bonds is retained in amorphous state that distorts the chemical bonds, as illustrated in figure 3.1. Therefore, carriers transport through the path of metal cation's ns orbitals. These features are completely different from conventional silicon semiconductor that has carrier transport path composed of highly directional  $sp^3$  orbitals [9].

|                                 | a-Si TFT                 | Oxide TFT               | Organic TFT              | Poly-Si TFT                      |

|---------------------------------|--------------------------|-------------------------|--------------------------|----------------------------------|

| Deposition Process              | PECVD                    | Sputter                 | Printing                 | CVD & Excimer<br>Laser Annealing |

| Max. process temperature (step) | 150~350°C<br>(GI)        | ≤350°C<br>(GI)          | 150~200°C<br>(curing)    | $\leq$ 500°C (activation)        |

| TFT mobility                    | 0.5~1cm <sup>2</sup> /Vs | 5~10cm <sup>2</sup> /Vs | 0.1~3cm <sup>2</sup> /Vs | 100~200cm <sup>2</sup> /Vs       |

| On/off current ratio            | ~106                     | ~106                    | ~106                     | ~106                             |

| TFT reliability                 | excellent                | excellent               | not enough               | excellent                        |

| Туре                            | mostly n-type            | mostly n-type           | mostly p-type            | n and p-type                     |

Table 3.1 Comparison of TFT devices

Fig. 3.1 Orbital drawing of ionic amorphous oxide semiconductor [Adapted from Ref. 9]

### **3.2** Low temperature gate dielectric

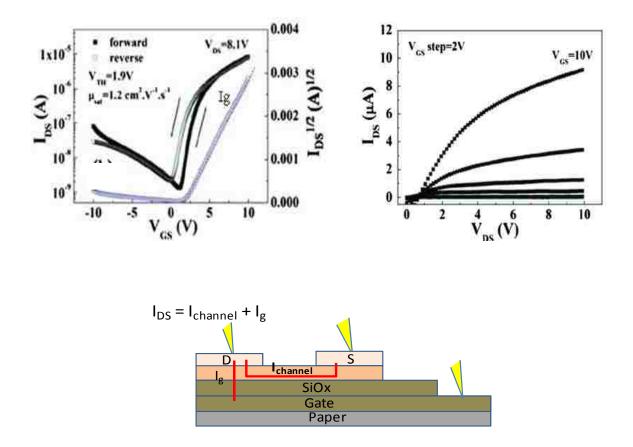

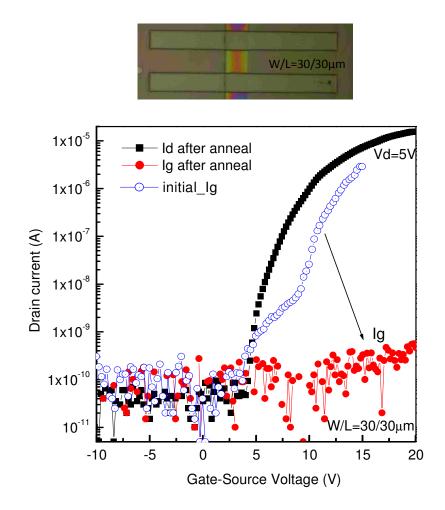

A low temperature TFT process is required for TFTs on paper since the temperature tolerance of a paper substrate is approximately 150°C. The highest temperature of typical oxide TFTs is around 350°C and it mainly results from the PECVD deposition temperature of SiO<sub>2</sub> dielectric. One of the objectives of the proposed works is to investigate a suitable gate dielectric at less than 150°C. a-IGZO TFTs with SiO<sub>2</sub> dielectric on paper substrate have been reported by Lim et al. and its electrical characteristics are shown in figure 3.2 [11]. However, low mobility and high gate leakage current were observed due to its low temperature  $SiO_2$  (<100°C) and rough surface. In the work reported in reference [11], two critical problems exist. One is cracking of the inorganic gate dielectric, and the other is high gate leakage current. As shown in the transfer curve of figure 3.2, the gate leakage current  $(I_g)$  nearly overlaps with sourcedrain current (I<sub>DS</sub>). It implies that the I<sub>DS</sub> in the graph is not the exact drain current and it may include gate leakage current,  $I_{DS} = I_{channel} + I_g$ . In general, it is known that SiO<sub>2</sub> deposited at low temperature exhibits high interface trap density and very low charge to breakdown [12]. The low mobility and high subthreshold swing of a-IGZO TFTs with low temperature SiO<sub>2</sub> are mainly attributed to charge trapping caused by high interface trap density.

Fig. 3.2 Transfer and output characteristics of InGaZnO4-based TFTs fabricated on a paper substrate [Adapted from Ref. 11]

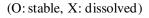

In order to improve device characteristics and process stability, polymer gate dielectric has been investigated in this study. Fluoropolymer (CYTOP), polyvinylphenol (PVP), and poly methyl methacrylate (PMMA) are known as the successful gate dielectric of organic TFTs in another study [13]; and methyl-siloxane based dielectric (Spin-on-glass (SOG) from Honeywell), which contained 15 wt% CH<sub>3</sub> (methyl) groups bonded to Si atoms in the Si-O backbone as illustrated in figure 3.3, is known to have high crack resistance, excellent planarization effect, as well as strong chemical resistance

[14]. In this study, both SOG and PMMA were initially evaluated as possible dielectrics. SOG cured at150°C for 3hrs was stable in all chemicals used in TFT process but PMMA was dissolved in stripper and EBR solvent, as summarized in Table 3.2.

| Polymer         | Stripper<br>(10min) | Developer<br>(5min) | EBR<br>(5min) | DI:HCl=20:1<br>(10min) | Acetone<br>(10min) |

|-----------------|---------------------|---------------------|---------------|------------------------|--------------------|

| Methly siloxane | Ο                   | 0                   | 0             | 0                      | Ο                  |

| PMMA            | X                   | 0                   | X             | 0                      | 0                  |

Table 3.2 Chemical stability of SOG and PMMA.

Fig. 3.3 Chemical structure of SOG.

In low temperature dielectric, the gate leakage current is a main issue. Thus understanding dielectric leakage current is essential to develop a new dielectric. Gate leakage current can be interpreted by several mechanisms such as Schottky emission, hopping, Fowler Nordheim Tunneling, and Poole-Frenkel effect [15]. DC conduction in a dielectric can be mainly interpreted by Schottky emission and Poole Frenkel effect. In Schottky emission, the presence of an electric field at the barrier modifies the emission current as it reduces the potential barrier between the two materials [16]. In Poole-Frenkel effect, the insulator can conduct electricity by electric field that enhances the excitation of electrons trapped in localized states into the insulator conduction band [17]. Poole Frenkel results from lowering of the potential barrier at donor-like sites under an applied electric field. Schottky and Poole Frenkel emission are expressed by [18],

Schottky emission:

$$J = AT^2 \exp\left(\frac{q}{kT}\sqrt{\frac{qE}{4\pi\varepsilon_o\varepsilon}} - \frac{q\Phi_s}{kT}\right)$$

(3.1)

Poole-Frenkel emission:

$$J = BE \exp\left(\frac{q}{kT}\sqrt{\frac{qE}{\pi\varepsilon_o\varepsilon}} - \frac{q\Phi_{PF}}{kT}\right)$$

(3.2)

where J the current density, A and B are constant, E, q,  $\Phi_s$ ,  $\Phi_{PF}$ ,  $\varepsilon$ ,  $\varepsilon_o$ , k, and T are applied electric field, electronic charge, barrier height for the injecting electrons (Schottky emission), voltage barrier (in zero applied electric field), permittivity, permittivity in vacuum, Boltzmann constant, and temperature, respectively.

If Schottky emission is dominant, the  $\ln(J)$  vs.  $E^{1/2}$  plot shows a straight line, while when Poole-Frenkel emission is the main mechanism, the  $\ln(J/E)$  vs.  $E^{1/2}$  plot shows a straight line. Figure 3.4 shows the plotted  $\ln(J/E)$  vs.  $E^{1/2}$  of SOG insulator. The dominant conduction mechanism in this field range is considered to be a Poole-Frenkel emission.

Fig. 3.4 The logarithmic current density over electric field vs. electric field<sup>1/2</sup> (Poole-Frenkel emission) for 600nm thick SOG insulator.

## **3.3 Fabrication of a-IGZO TFT on paper substrate**

In this work, HP inkjet printable photo paper (coated paper) with the roughness of 8.4nm was used as the substrate for a-IGZO TFT fabrication. From a 210 mm by 297 mm square paper sheet, 50mm by 50mm was simply cut by using scissors. The inkjet printable photo paper presents relatively smooth surface than other paper candidates and the rear side of it is anti-absorbing due to a polyethylene coating. Top side of this paper usually has an inkjet receptive coating designed to absorb ink quickly, so it also absorbs water and solvents during TFT process. In order to prevent any absorption and improve surface roughness, 3µm thick epoxy acrylate copolymer (AC-818KL from Kolon Chemical) that has been used as planarization material in LCD was coated on top side of

the paper and followed by curing at 150°C for 1 hr. Then 100nm thick  $SiO_2$  was deposited in sputter at room temperature to prevent outgassing from planarization layer. Two different gate dielectrics were compared; a) low temperature PECVD deposited SiO<sub>2</sub>, and b) methyl siloxane based dielectric. Bottom gate inverted staggered a-IGZO TFTs having PECVD  $SiO_2$  dielectric were first fabricated on the planarized paper. AlNd/Mo double layer as gate and source-drain electrodes were patterned by liftoff process. AlNd plays a role in low resistivity electrode and Mo prevents the formation of Al<sub>2</sub>O<sub>3</sub> on AlNd surface. 200 nm thick SiO<sub>2</sub> deposited with a rate of 4.8nm/min at 140°C by PECVD was used as gate dielectric. Cracks were observed on the entire substrate after  $SiO_2$  deposition as shown in figure 3.6 (a). These cracks are attributed to thermal expansion mismatch between organic planarization layer and SiO<sub>2</sub> because one side coated paper substrate by organic layer is heated up during PECVD process, so it bends, and then the expanded organic layer tries to recover during cooling in contrast with SiO<sub>2</sub> trying to maintain its dimension. We used double side adhesive film that is designed to bond and debond flexible substrate on carrier substrate, to restrict the expansion of organic layer on paper substrate. The adhesive films consist of a centered PI film and adhesive layers at double side. A strong adhesive is stuck on a carrier substrate and a paper substrate is bonded on a weak adhesive side by a laminator as shown in figure 3.5. This approach withstands up to approximately 200°C and is stable in photolithography chemicals.

Fig. 3.5 Bonding & debonding process using double side adhesive film.