#### **Lehigh University** Lehigh Preserve

Theses and Dissertations

2019

# Tailoring Transactional Memory to Real-World Applications

Tingzhe Zhou Lehigh University

Follow this and additional works at: https://preserve.lehigh.edu/etd

Part of the Computer Sciences Commons

#### Recommended Citation

Zhou, Tingzhe, "Tailoring Transactional Memory to Real-World Applications" (2019). Theses and Dissertations. 5579. https://preserve.lehigh.edu/etd/5579

This Dissertation is brought to you for free and open access by Lehigh Preserve. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of Lehigh Preserve. For more information, please contact preserve@lehigh.edu.

## Tailoring Transactional Memory to Real-World Applications

by

Tingzhe Zhou

Presented to the Graduate and Research Committee of Lehigh University in Candidacy for the Degree of Doctor of Philosophy in

Computer Science

Lehigh University

May, 2019

© Copyright by Tingzhe Zhou 2019 All Rights Reserved

| Date                                 |

|--------------------------------------|

| Dissertation Advisor                 |

| Committee Members:                   |

| Prof. Michael Spear, Committee Chair |

| Prof. Hank Korth                     |

| Prof. Roberto Palmieri               |

|                                      |

Approved and recommended for acceptance as a dissertation in partial fulfillment of the

# Acknowledgements

The life for a Ph.D. student is the combination of happiness, arduousness, and adventurousness. I have been told thousands of times about how hard to get a Ph.D. in computer science. However, I was super lucky to have so many friendly, wise, and patient people helped me and made my Ph.D. life much more relaxed and unforgettable than it supposed to be.

I want to express my heartfelt gratitude to my advisor, professor Michael Spear, for his invaluable guidance, and continuous support, caring, patience, and encouragement. Prof. Spear has always been enthusiastic and helpful for answering all kinds of questions (from raising new ideas to writing and debugging the code). I could not keep making progress on my research projects without his selfless guidance and endless patience. Apart from research, he also comforted me when I was struggling with difficulties, taught me how to arrange things efficiently, and encouraged me when I was about to give up. Furthermore, Prof. Spear was super generous about taking vacation time, going for internships, and traveling for conferences. With his generous support, I went through a diversified and colorful Ph.D. life. I could not express how lucky am I worked under his guidance.

I am grateful to the advice from all of my committee members. Specifically, I genuinely thank Prof. Roberto Palmieri for his numerous practical suggestions and encouragement towards my research and my life, and Prof. Hank Korth for his tips on academic writing, presentation, and open-mind for broad research areas. I want to express my gratitude to Dr. Victor Luchangco for helping me polishing papers and being extremely patient for answering questions. I sincerely appreciate their precious time and insightful suggestions regarding my Ph.D. proposal, general exam, and dissertation. I would also like to thank

Dave Dice and Tim Harris for their advice and guidance during the conduct of some of my research.

Special thanks go to my internship managers: Amit Sharma (Microsoft Dynamic CRM), Guoqing Xu (Google Cloud AI), Nicholas Murphy (Google Node Storage), Maged M. Michael and Dave Watson (Facebook System Software). I could not have so many enlightened, productive and joyful industry experiences without their continuous encouragement, endless patient towards my questions, and delicately arranged events.

Infinite thanks to my Lehigh lab-mates and my friends for their continuing support. I appreciate the precious lab-survival-manual from Yujie Liu and Wenjia Ruan. I want to express my thank to Pantea Zardoshti, for whom hosting so many inspiring and cheering conversations during the past three years. She also made our lab lovely and pleasant for work. Special thanks to my friend Hongmin Wang for being so supportive when I was thinking to pursue a Ph.D. in the U.S. Sincere thank you all, my dear friends, Guotai Xiong, Mengyan Li, Zixun Yang, Wenbo Li, Haoxiang Wu, Qinghan Xue, Yujie Ji for the broad spectrum of help and care in my personal life.

Last but not least, I want to thank my parents, Lan Yi and Faxiang Zhou, for always having my back and loving me unconditionally.

Most of the work presented in this dissertation was supported in part by the National Science Foundation under Grant CAREER-1253362, and through financial support from Oracle. Any opinions, findings, and conclusions or recommendations expressed in the dissertation are my own and those of my coauthors and do not necessarily reflect the views of the National Science Foundation.

# Contents

| A                | ckno   | wledge                  | ements                                                                 | iv   |

|------------------|--------|-------------------------|------------------------------------------------------------------------|------|

| L                | ist of | Table                   | ${f s}$                                                                | x    |

| L                | ist of | Figur                   | es                                                                     | xi   |

| $\mathbf{L}^{:}$ | ist of | Algor                   | rithms                                                                 | xiii |

| A                | bstra  | ıct                     |                                                                        | 1    |

| 1                | Intr   | $\operatorname{roduct}$ | ion                                                                    | 3    |

|                  | 1.1    | Trans                   | actional Memory                                                        | 5    |

|                  |        | 1.1.1                   | The C++ TM Technical Specification (TMTS) Overview $\ \ldots \ \ldots$ | 6    |

|                  |        | 1.1.2                   | Implementations                                                        | 7    |

|                  |        | 1.1.3                   | Case study: Transactional Memory in GCC $\ldots$                       | 9    |

|                  |        | 1.1.4                   | Advanced Features                                                      | 11   |

|                  | 1.2    | Apply                   | ring Transactional Memory in Real-World Applications                   | 13   |

|                  |        | 1.2.1                   | Transactional Lock Elision                                             | 13   |

|                  |        | 1.2.2                   | Facilitating the Implementation of Concurrent Data Structures          | 17   |

|                  |        | 1.2.3                   | Persistent Transactional Memory                                        | 19   |

|                  | 1.3    | Disser                  | tation Motivation                                                      | 22   |

|                  |        | 1.3.1                   | Thesis Statement                                                       | 23   |

|                  | 1.4    | Contr                   | ibutions                                                               | 23   |

|                  | 1.5    | Organ                   | nization                                                               | 31   |

| 2 | Sup | portin  | g Precise Memory Reclamation          | 33 |

|---|-----|---------|---------------------------------------|----|

|   | 2.1 | Introd  | luction                               | 33 |

|   | 2.2 | Specifi | ication                               | 36 |

|   | 2.3 | Imple   | mentations                            | 37 |

|   |     | 2.3.1   | System Model                          | 37 |

|   |     | 2.3.2   | Strict Implementations                | 38 |

|   |     | 2.3.3   | Relaxed Implementations               | 40 |

|   | 2.4 | Using   | Revocable Reservations                | 43 |

|   |     | 2.4.1   | Singly Linked List                    | 43 |

|   |     | 2.4.2   | Doubly Linked List                    | 45 |

|   |     | 2.4.3   | Unbalanced Binary Search Tree         | 46 |

|   | 2.5 | Evalua  | ation                                 | 48 |

|   |     | 2.5.1   | Linked Lists                          | 50 |

|   |     | 2.5.2   | Window Size                           | 52 |

|   |     | 2.5.3   | The Impact of Allocator Algorithm     | 53 |

|   |     | 2.5.4   | Unbalanced Search Trees               | 54 |

|   | 2.6 | Conclu  | usions                                | 56 |

| 3 | Sun | portin  | g Complex Patterns of Synchronization | 58 |

| J | 3.1 | -       | luction                               | 58 |

|   | 3.1 |         | o2 and x265                           | 59 |

|   | 3.3 | _       |                                       |    |

|   | 5.5 | •       | Problems with TLE and Oviessense      | 61 |

|   |     | 3.3.1   | Problems with TLE and Quiescence      | 62 |

|   |     | 3.3.2   | Programatically Avoiding Quiescence   | 64 |

|   | 0.4 | 3.3.3   | Pitfalls                              | 66 |

|   | 3.4 |         | Phase Locking and x265                | 67 |

|   | 3.5 |         | ional Considerations                  | 69 |

|   | 3.6 |         | ation                                 | 71 |

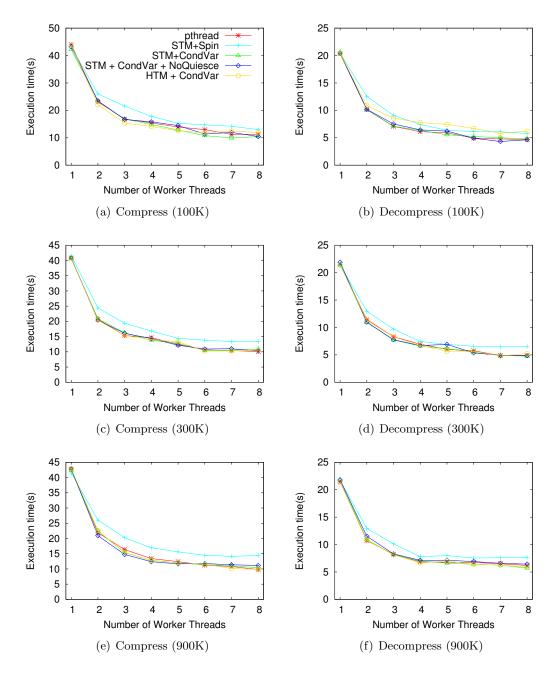

|   |     | 3.6.1   | PBZip2                                | 71 |

|   |     | 362     | x265                                  | 73 |

|   |     | 3.6.3  | Is Quiescence Overhead Important?                                 | 74  |

|---|-----|--------|-------------------------------------------------------------------|-----|

|   | 3.7 | Conclu | usions                                                            | 77  |

| 4 | Sup | portin | g Irrevocable and Long-Running Operations                         | 78  |

|   | 4.1 | Introd | uction                                                            | 78  |

|   | 4.2 | A Mot  | tivating Example                                                  | 79  |

|   | 4.3 | Exten  | ding TM with Atomic Deferral                                      | 81  |

|   |     | 4.3.1  | Implementing Atomic Deferral                                      | 81  |

|   |     | 4.3.2  | Transaction-Friendly Mutex Locks                                  | 84  |

|   |     | 4.3.3  | Practical Concerns                                                | 85  |

|   | 4.4 | Progra | amming With Atomic Defer                                          | 86  |

|   |     | 4.4.1  | Basic Logging                                                     | 86  |

|   |     | 4.4.2  | Durable Output                                                    | 87  |

|   |     | 4.4.3  | Opening Files as Output                                           | 88  |

|   | 4.5 | Perfor | mance Evaluation                                                  | 89  |

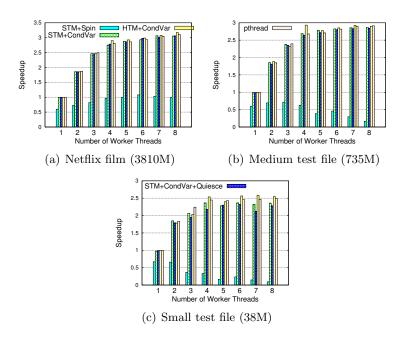

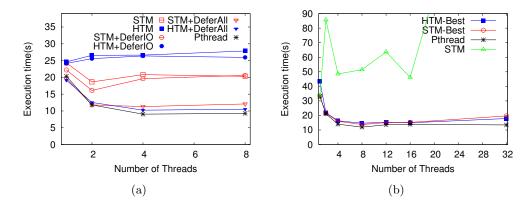

|   |     | 4.5.1  | Performance of atomic_defer on a Transactional I/O Microbenchmark | 90  |

|   |     | 4.5.2  | Performance of atomic_defer on PARSEC Dedup                       | 92  |

|   | 4.6 | Conclu | usions                                                            | 94  |

| 5 | Sup | portin | g Data Persistence                                                | 96  |

|   | 5.1 | Introd | uction                                                            | 96  |

|   | 5.2 | System | n Model for Persistence                                           | 98  |

|   |     | 5.2.1  | Hardware Support for Persistence                                  | 99  |

|   |     | 5.2.2  | Position-Independence                                             | 100 |

|   |     | 5.2.3  | Hardware Memory Diversity                                         | 100 |

|   |     | 5.2.4  | Static Separation                                                 | 101 |

|   |     | 5.2.5  | Multiple Persistent Regions                                       | 102 |

|   |     | 5.2.6  | Models Considered in this Chapter                                 | 102 |

|   | 5.3 | Univer | rsal Persistent TM Transformation                                 | 102 |

|   |     | 5.3.1  | Ensuring Correctness for Common-Case Transactions                 | 104 |

|   |     | 5.3.2  | Ensuring Progress and Instrumentation                             | 106 |

| Bi | iography 139   |        |                                              |     |

|----|----------------|--------|----------------------------------------------|-----|

| Bi | Bibliography 1 |        |                                              | 123 |

| 6  | Con            | clusio | ns and Future Work                           | 121 |

|    | 5.6            | Conclu | usions                                       | 119 |

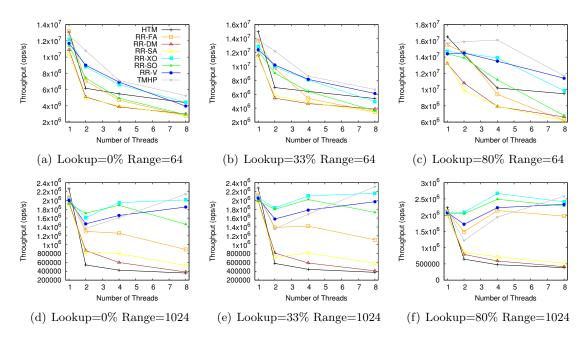

|    |                | 5.5.2  | Performance in the Ideal Persistence Model   | 119 |

|    |                | 5.5.1  | Performance in the General Persistence Model | 118 |

|    | 5.5            | Comb   | ining Optimizations                          | 116 |

|    |                | 5.4.4  | Deferred Flushing                            | 115 |

|    |                | 5.4.3  | Fence Pipelining                             | 114 |

|    |                | 5.4.2  | Memory Alignment and Logging Granularity     | 112 |

|    |                | 5.4.1  | Captured Memory                              | 110 |

|    | 5.4            | PTM    | Optimizations                                | 110 |

|    |                | 5.3.3  | Performance of Naive PTM and STM             | 108 |

# List of Tables

| 1.1 | Microbenchmark speedup for optimized PTM                                   | 31  |

|-----|----------------------------------------------------------------------------|-----|

| 5.1 | Overhead of self-referential pointers                                      | 100 |

| 5.2 | Speedup from the last allocation tracking optimization (single-thread)     | 111 |

| 5.3 | Speedup of aligned memory and coarse-grained logging for single thread ex- |     |

|     | ecution                                                                    | 112 |

| 5.4 | Speedup of fence pipelining for TLRW on single thread execution            | 114 |

| 5.5 | Speedup of Deferred Flushing                                               | 115 |

# List of Figures

| 1.1 | Runtime for Locks (left) and Transactional Memory (right)                           | 6  |

|-----|-------------------------------------------------------------------------------------|----|

| 1.2 | The privatization problem: If Thread 2 is executing speculatively, and is not       |    |

|     | aware that Thread 1 commits, races may occur between accesses to the node           |    |

|     | containing the value 10                                                             | 12 |

| 1.3 | In-memory application seamlessly persists across power failures                     | 20 |

| 1.4 | Inserting node ${\tt c}$ to a doubly linked list under different programming models | 21 |

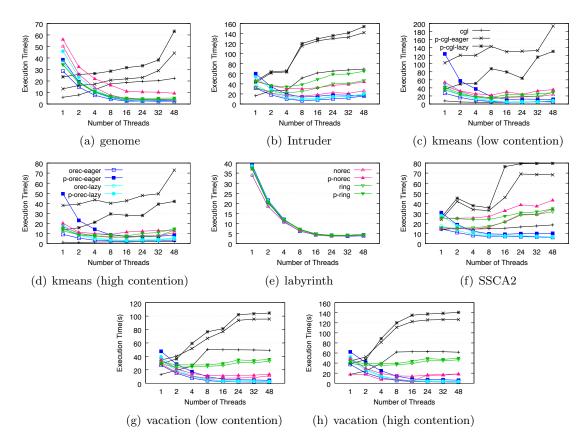

| 1.5 | PTM execution on STAMP benchmarks, using the default parameters                     | 29 |

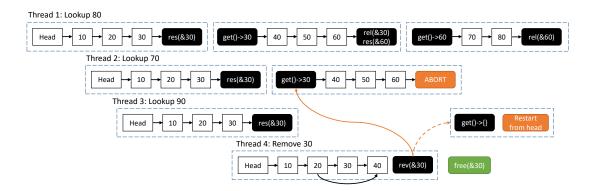

| 2.1 | Concurrent operations on a linked list, with hand-over-hand transactions and        |    |

|     | revocable reservations. Time advances to the right. Dashed boxes indicate           |    |

|     | transactions, and filled black rectangles represent operations on the revoca-       |    |

|     | ble reservation shared object ("res", "get", "rel", and "rev" correspond to         |    |

|     | reserving a value, getting a previously reserved value, releasing a reservation,    |    |

|     | and revoking all reservations for a specific value)                                 | 35 |

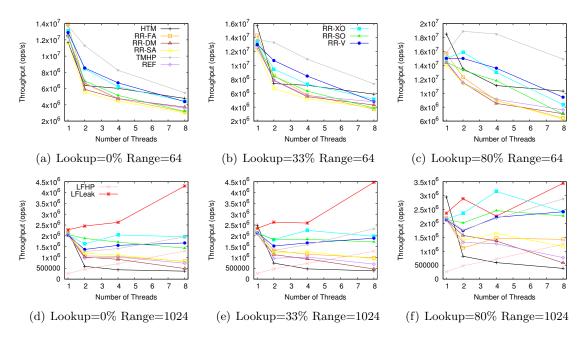

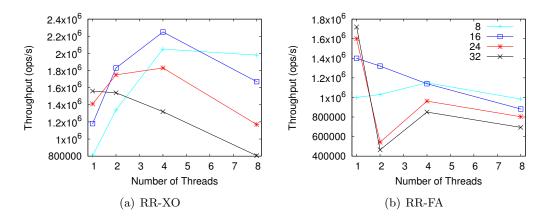

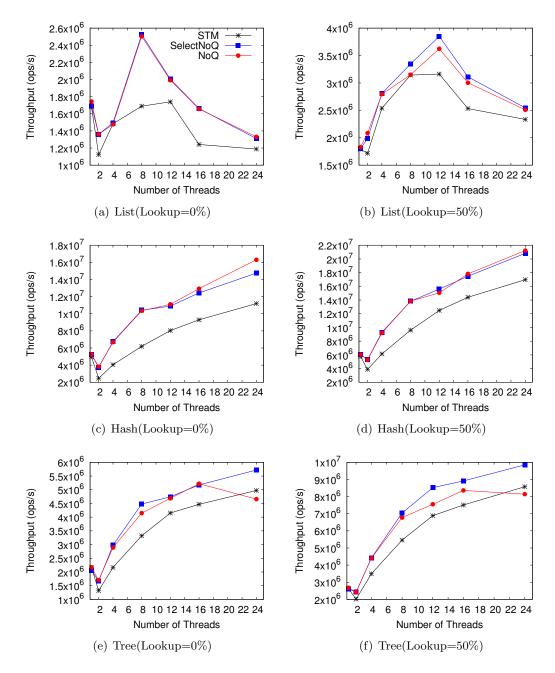

| 2.2 | Singly linked list microbenchmark                                                   | 50 |

| 2.3 | Doubly linked list microbenchmark                                                   | 52 |

| 2.4 | Impact of window size                                                               | 53 |

| 2.5 | Impact of allocator                                                                 | 54 |

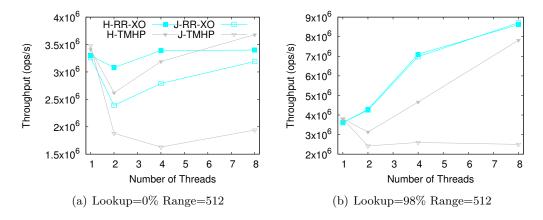

| 2.6 | Internal binary search tree microbenchmark                                          | 55 |

| 2.7 | External binary search tree microbenchmark                                          | 56 |

| 3.1 | HEVC wavefront parallel processing [93]                                             | 61 |

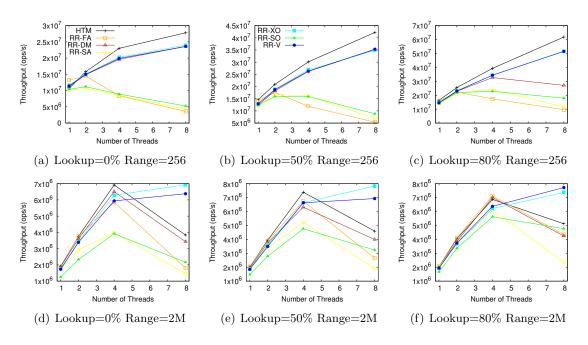

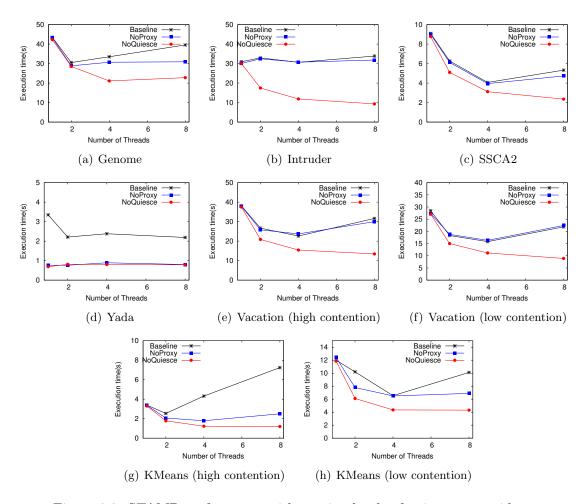

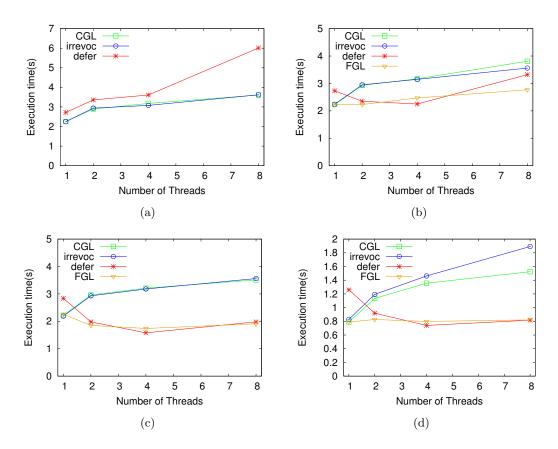

| 3.2 | STAMP performance with varying levels of quiescence-avoidance                       | 64 |

| 3.3 | Performance of Transactionalized PBZip2                                               | 70  |

|-----|---------------------------------------------------------------------------------------|-----|

| 3.4 | Performance of Transactionalized x265                                                 | 72  |

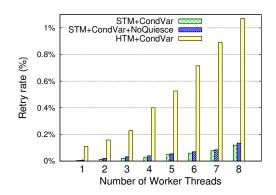

| 3.5 | Retry rate for Netflix test (10M Transaction Commits)                                 | 73  |

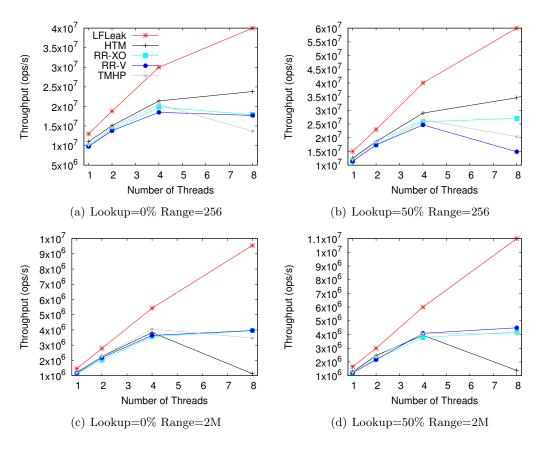

| 3.6 | Performance of TM.NoQuiesce on microbenchmarks                                        | 76  |

| 4.1 | Motivation for atomic defer. On the left, $T_1$ 's transaction includes a long        |     |

|     | running operation using $C$ . On the right, $C$ is locked, and then the operation     |     |

|     | on ${\cal C}$ is deferred until after the transaction commits. The use of locking and |     |

|     | deferral of the operation on $C$ enables the operations by threads $T_2$ and $T_3$    |     |

|     | to progress more quickly, without violating serializability                           | 79  |

| 4.2 | Atomic_defer performance on an I/O microbenchmark                                     | 91  |

| 4.3 | Performance of PARSEC dedup with atomic_defer                                         | 92  |

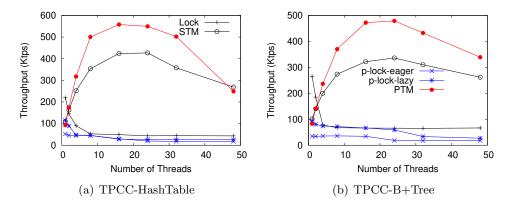

| 5.1 | Transactional TPCC benchmark performance. When the program data is in                 |     |

|     | DRAM, synchronization is achieved using a single coarse lock or transactions.         |     |

|     | When the program data is in NVM, synchronization is achieved using a coarse           |     |

|     | lock + undo (eager), a coarse lock + redo (lazy), or persistent transactional         |     |

|     | memory                                                                                | 97  |

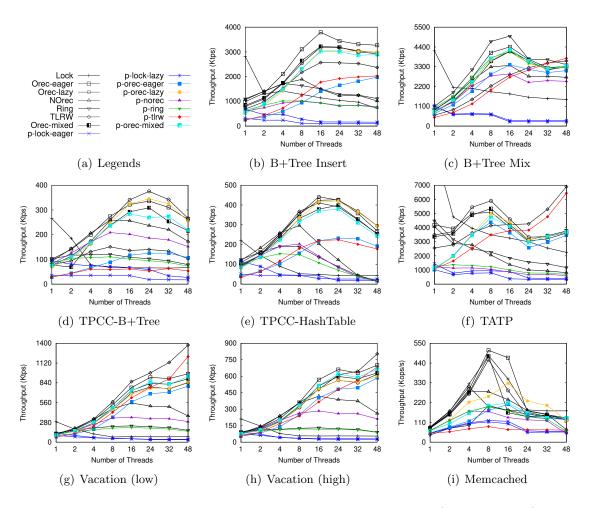

| 5.2 | Performance comparison of STM to naive PTM (general model)                            | 107 |

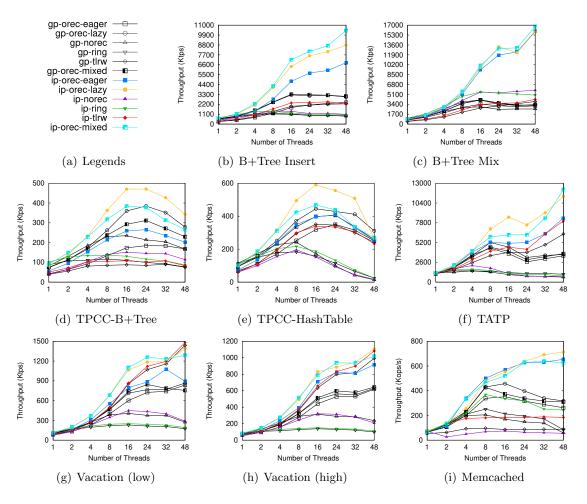

| 5.3 | Optimized performance of PTM algorithms. The GP prefix indicates that the             |     |

|     | PTM uses the optimizations that are appropriate in the General Persistence            |     |

|     | model. IP indicates that additional optimizations were applied, based on the          |     |

|     | more limited Ideal Persistence model.                                                 | 117 |

# List of Algorithms

| 1  | Example instrumentation performed by GCC                                          | 9  |

|----|-----------------------------------------------------------------------------------|----|

| 2  | Pseudocode of Transactional Lock Elision (TLE) with Intel RTM $$                  | 15 |

| 3  | Irrevocability-induced delays                                                     | 26 |

| 4  | Sequential specification for the revocable reservation shared object              | 36 |

| 5  | Basic revocable reservation algorithm (RR-FA): a linked list simulates a fully    |    |

|    | associative cache of reservations. All functions are called from an active trans- |    |

|    | action                                                                            | 38 |

| 6  | Exclusive Owner Revocable Reservation algorithm (RR-XO): an array of thread       |    |

|    | IDs is used to indicate which thread currently holds a reservation for all ref-   |    |

|    | erences that hash to any given array entry                                        | 41 |

| 7  | Version-based Revocable Reservation algorithm (RR-V): an array of integers        |    |

|    | is used to coordinate revocation and reservation operations                       | 42 |

| 8  | Singly linked list with revocable reservations. Nodes consist of a value and a    |    |

|    | next pointer, and the head initially points to a sentinel node                    | 44 |

| 9  | Unbalanced binary search tree with revocable reservations. Nodes consist of       |    |

|    | a value, two child pointers, and a flag indicating whether they are the left or   |    |

|    | right child of their parent. The root is a sentinel node with only a left child.  | 47 |

| 10 | Proxy privatization: When the privatizer's transaction commits and invali-        |    |

|    | dates the vector update thread's transaction, the potential race is between       |    |

|    | line 4 of the proxy thread and the rollback of the vector thread's transaction.   | 63 |

| 11 | Producer/consumer workload                                                        | 66 |

| 12 | A non-serializable critical section in x265                                   | 68  |

|----|-------------------------------------------------------------------------------|-----|

| 13 | A ready flag avoids lock nesting, facilitating transactionalization           | 68  |

| 14 | Implementation of atomic deferral                                             | 82  |

| 15 | A transaction-friendly, reentrant mutex lock                                  | 84  |

| 16 | Diagnostic logging from a critical section                                    | 86  |

| 17 | Durable output with guaranteed order                                          | 87  |

| 18 | MySQL critical sections in file pool management that are used in asynchronous |     |

|    | I/O                                                                           | 88  |

| 19 | An example of deferring I/O and system calls                                  | 91  |

| 20 | Deferring reliable output in PARSEC dedup                                     | 93  |

| 21 | Universal transformation from STM to PTM                                      | 105 |

### Abstract

Transactional Memory (TM) promises to provide a scalable mechanism for synchronization in concurrent programs, and to offer ease-of-use benefits to programmers. Since multi-processor architectures have dominated CPU design, exploiting parallelism in programs is essential to achieve better performance and get further speedup as hardware upgrades increase the number of cores, instead of CPU frequency. However, lock-based synchronization is tricky to use, especially when applications have irregular or hard-to-predict memory access patterns. TM is considered as an alternative synchronization method to locks.

Emerging Non-Volatile Memory (NVM) or Persistent Memory (PM) technologies fundamentally reshape the memory and storage hierarchies by providing a single memory that is dense, byte-addressable, fast, and able to retain its contents without consuming energy. However, the CPU cache and registers are expected to remain volatile. Programming directly with PM is difficult and error-prone due to the additional instrumentation required for failure atomicity. The overlap between TM and PM instrumentation is substantial, making TM an appealing programming model for PM.

Evolving computer architecture brings various challenges to programmers. Transactional memory seems to be a silver bullet to solve them all. It is surprising that there have been few examples of TM being used in "real" software, especially considering that hardware TM is beginning to see widespread availability.

In this dissertation, we conduct comprehensive experiments to identify technical challenges that prevent programmers from using TM. We demonstrate that the existing TM platform and common parallel programming models are not compatible in several scenarios, such as optimistic concurrency control with fast and immediate memory reclamation, complex synchronization patterns, irrevocable or long-running operations, and data persistence. These features are requirements of real-world applications. We explain how to tailor TM in a practical and efficient way to support these features. Our target is to increase our fundamental understanding of how the concurrent threads of real-world programs interact, and to extend transactional programming models and systems, so that they are able to support these requirements efficiently and without significantly increasing programmer effort.

### Chapter 1

### Introduction

From small digital devices such as smartphones, tablets, and smartwatches, to personal computers and large servers, multiprocessors are replacing single processor systems in all areas of computing. The trend for multi-core processors is not surprising because manufacturers have realized it is impossible to increase clock frequencies in a single chip without overheating. Multiprocessors have became the promising architecture to leverage the increasing density of transistors enabled by Moore's law. This change also brings challenges to programmers and system developers. In old days, the speedup of systems and software depended heavily on the increasing frequency of the CPU. But now, in order to get further improvement, programmers need to exploit parallelism in programs. This requires that programmers rewrite their code into concurrent tasks, and coordinate these tasks with dedicated and correct synchronization methods.

The most well-known technology to synchronize multiple threads is the mutual exclusion lock [31]. A lock guarantees only one thread can hold it at any time. Programmers associate locks with data, and then construct code regions ("critical sections") that only access that data while holding the lock. However, lock-based programming is notoriously difficult and error prone: First, programmers have to choose the granularity of locks: implementations that use a small number of coarse grained locks are usually straightforward but limit concurrency; fine grained locking scales better but introduces latency, and could possibly result in complicated locking protocols (e.g., using fine grained locks to implement a concurrent balanced binary trees). Second, lock-based codes are not composable. Small

critical sections protected by locks can not be reused to create big critical sections without knowing the implementation details. Third, locking introduces problems such as deadlock (e.g., two threads holding different locks and waiting for each other to release the lock), livelock (threads are changing status without making forward progress), priority inversion (lower priority threads holding the lock and blocking the higher priority threads), and convoying [46] (e.g., when a thread using hand-over-hand locking to traverse a linked list, it blocks all other threads from bypassing it). All in all, it is difficult to write lock-based programs that provide good performance while remaining easy to maintain and extend.

Transactional Memory (TM) [56] was first proposed more than two decades ago, as a hardware mechanism for simplifying the creation of concurrent data structures. Subsequent research has considered expanding the role of TM to a full-fledged programming model, in which programmers use coarse grained transactions as the primary means of synchronizing threads [14]. As a language extension proposed in response to difficulties faced when synchronizing programs with locks, it is easiest to understand the benefit TM offers to a programmer via comparison: Lock-based programming requires the programmer to reason about what code regions cannot run concurrently without risking a data race, and then to craft a fine grained locking methodology that allows as much concurrency as possible while also preventing incorrect concurrent executions. Transactional programming avoids the second step: regions that cannot always run concurrently without affecting correctness are marked as lexically scoped transactions, and then a run-time system, possibly accelerated by specialized hardware, runs transactions as sandboxed speculations. If a set of speculations conflict, the run-time system rolls at least one back, and typically it also takes some action to ensure that at least one will eventually complete. If concurrent speculations do not conflict, then the run-time system allows them to complete. By monitoring the behavior of speculations at a fine granularity (e.g., addresses of individual memory accesses), only true conflicts result in serialization, and thus more concurrency is possible than with locks.

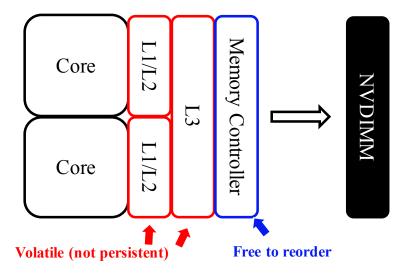

The potential of TM is not restricted to parallel programming. As CPU architectures evolve through time, another essential hardware component is also improving: In the computer memory hierarchy, storage has been considered either faster but volatile (e.g., CPU

registers, DRAM) or slower but durable (e.g., flash, disk). Emerging Non-volatile Memory (NVM) or Persistent Memory (PM) technologies such as 3D-Xpoint [89], PCM [67] and STT-RAM [114] fundamentally reshape the memory and storage hierarchies by providing a single memory that is dense, byte-addressable, fast, and able to retain its contents without consuming energy.

Although PM can provide similar access latency, larger volume, and lower price-perbyte than DRAM, the non-volatile feature of PM brings challenges for traditional system and software designs. Since CPU caches and registers are expected to remain volatile, and store operations can be reordered and delayed as they leave the cache and reach main memory (unless directly using write-through instructions to bypass the cache), programmers need to explicitly put fence and flush instructions into their programs to control the time when updates happen in the PM. However, they cannot persist data across cache lines without additional instrumentation. The overlap between TM and PM instrumentation is substantial, which makes TM an appealing programming model for PM. This motivates investigations of transactional programming models to access PM [15, 45, 66], and lead to several concurrent persistent TM (PTM) libraries [18, 59, 69, 116].

#### 1.1 Transactional Memory

Transactional Memory (TM) [56] was originally proposed as a hardware extension to facilitate the creation of scalable nonblocking data structures. The appeal of TM is its simplicity: a programmer need only wrap an operation inside of a language-level "transaction", and then a run-time system executes the transaction, making use of custom hardware and/or compiler-generated software instrumentation. The run-time system monitors the low-level memory accesses of transactions, and allows concurrent transactions to execute simultaneously as long as their memory accesses do not conflict (i.e., if concurrent transactions access datum D, then they may not all commit unless none write to D; otherwise, at least one must roll back and try again).

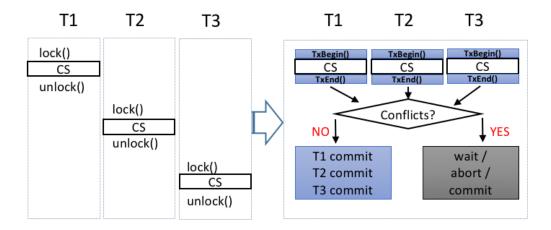

Figure 1.1 depicts a program executing under two different programming models. CS represents a critical section. On the left side, the lock is used to protect those critical

Figure 1.1: Runtime for Locks (left) and Transactional Memory (right)

sections. The right side represents the transactional execution. The lock serializes the execution of different critical sections, no matter whether they conflict or not. For transactional execution, three threads launch the speculative execution concurrently. If no memory conflict happens during the execution, three transactions can commit. Otherwise, a contention manager [48] will decide whether to delay the execution of conflicting transactions to let others commit, or explicitly abort at least one transaction so others can make progress.

#### 1.1.1 The C++ TM Technical Specification (TMTS) Overview

In C++ [61], TM is presented as a block construct: a lexically-scoped block of code is designated as a transaction, and any early termination or exception thrown from the block will cause the TM system to commit or abort the transaction before returning control flow to an outer scope. When multiple threads attempt transactions simultaneously, their behavior should be indistinguishable from a situation in which transactions run one at a time. In practice, the run-time system will typically execute transactions speculatively, using hardware transactional memory (HTM) support or compiler instrumentation to run transactions concurrently, track their memory accesses, detect memory conflicts, and abort/retry transactions as necessary to ensure correct behavior. The implementation of TM is not, however, part of the C++ TMTS.

The C++ TMTS [61] introduces an API containing a handful of keywords to support

transactional execution. We limit our discussion to three: synchronized and atomic indicate the beginning of a lexically-scoped transaction, and transaction\_safe indicates that a function can be called from within a lexically-scoped transaction.

The primary feature of the TMTS is the notion of an atomic block. A program that uses atomic blocks will produce output that is equivalent to an execution in which the atomic blocks executed in some serial order, without overlap. However, under the hood, TM is expected to be used to execute those blocks concurrently. The atomic block is allowed to "cancel" itself. To support cancellation, the compiler must prove that an atomic transaction does not perform any operations that are externally visible before the transaction commits (e.g., I/O operations). Thus atomic transactions can only contain functions with transaction\_safe annotations, which indicate that the functions' effects can be undone.

A synchronized transaction is free to perform irrevocable operations [118] (such as I/O and system calls), which cannot be undone. Synchronized blocks cannot cancel. When a synhronized transaction requires irrevocability, no concurrent transactions are allowed until the irrevocable synchronized block completes.

#### 1.1.2 Implementations

TM can be implemented in hardware (HTM), software (STM), or a combination of the two (Hybrid TM).

When TM is implemented in hardware, two hardware instructions are used to indicate the boundaries of a transaction [121]. The TxBegin instruction creates a register checkpoint and informs the cache controller of the need to monitor memory accesses for conflicts with other threads. The TxEnd instruction discards the checkpoint and informs the cache controller that tracking is no longer needed. During the transaction's execution, a set of sufficient conditions on the behavior of the cache dictate whether the transaction remains valid: if the transaction reads a location, then the corresponding cache line must remain in the cache until commit; if the transaction writes a location, then the corresponding cache line must not be evicted or shared with other processors before commit. If a condition is violated, the transaction aborts, and the checkpoint is restored.

When TM is implemented in software, the compiler inserts function calls at the points

where a transaction begins and ends. It also inserts a function call in place of each memory access within the transaction [91]. These function calls connect to a library that performs checkpointing, tracks the memory accesses of each transaction, and manages shared metadata for detecting transaction conflicts. For simplicity, one may think of the shared metadata as a table of readers/writer locks, which are acquired as a transaction progresses, and released at the commit point of the transaction. STM algorithms vary with regard to shared metadata implementation, protocols for detecting conflicts, and mechanisms for buffering writes.

HTM has lower latency than STM: there are no per-access function calls or explicit management of metadata (e.g., redo and undo logs). However, HTM is less flexible: there is no opportunity to introduce any nuance in how conflicts are resolved (e.g., the contention management for HTM can be summarized as requester-wins, which means a later transaction will always abort previous transactions if conflicts exist between them). In contrast, STM can defer conflict resolution until at least one transaction is guaranteed to succeed. Furthermore, HTM is tightly coupled with the cache controller, and thus hardware transactions cannot access more data than fits in the cache, or survive interrupts and system calls. Thus HTM does not guarantee forward progress and needs to have a fall-back strategy. For transactions that deterministically fail to complete in hardware, a common approach is to temporarily serialize all transactions, execute the failing transaction in isolation and without hardware protection, and then re-enable concurrency. This serialized path hurts performance. An alternative is to fall back to STM, known as Hybrid TM, which complicates the design but allows more concurrency.

Hybrid TM combines the advantages of both HTM and STM. There are many ways to implement Hybrid TM. One rule to design a fast Hybrid TM system is to maintain a pure-HTM execution path as often as possible [13,22,101] instead of falling back to the software path. To achieve the goal, Hybrid NOrec [22] replaces part of an STM implementation with HTM. The strategy not only makes the HTM path short and unlikely to abort, but also reduces intrinsic overheads when executing the STM path. The primary challenge is to make sure the synchronization in the same path and across different paths are all correct. RH-NOrec [78] takes a step further to introduce three execution paths to increase

#### Algorithm 1: Example instrumentation performed by GCC

the scalability. Hybrid Cohorts [101] separates the HTM and STM execution via different execution phases. This eliminates complex synchronization across two different paths, but can sacrifice concurrency.

#### 1.1.3 Case study: Transactional Memory in GCC

In this section, we describe the interfaces of TM supported by GCC. Programmers or software developers can use such interfaces to employ TM for concurrency control. Moreover, we illustrate how GCC transforms the transactional code to call its TM library. We also demonstrate a practical general-purpose TM algorithm implemented by GCC, called libitm.

GCC's TM support roughly complies with the TMTS [43]. Transaction boundaries, and memory accesses made by a transaction, map to a run-time library that provides numerous TM implementations (HTM, read-only-optimized STM, general-purpose STM, and irrevocability-supporting STM). Algorithm 1 gives an example of how GCC translates a transaction that increments a shared counter.

In the example, a call to TxBegin starts the transaction. Its return value indicates if the transaction can skip per-access memory instrumentation (e.g., it is using HTM or running sequentially as a synchronized block). If not, then each individual load and store becomes a function call, specific to the current TM mechanism. Finally, TxEnd completes the transaction. Despite the apparent simplicity, the ABI to support this instrumentation includes more than 180 public functions: compiler optimizations introduce 40 read functions and 30 write functions, to handle read-before-write, write-after-write, and other common access patterns for 10 primitive data types. Even when HTM is used, the ABI requires two function calls and a branch in every transaction; without HTM, there is a function call on every access. For STM, TxBegin must also checkpoint the thread's architectural state.

Different STM algorithms vary in how they implement TxBegin, TxRead, TxWrite,

TxEnd and TxAbort. GCC's general-purpose STM algorithm (setting ITM\_DEFAULT\_METHOD

= ml\_wt) is a privatization-safe version of TinySTM [39]. The algorithm uses a global

ownership record (orec) table [39] as the shared metadata implementation. Every memory location maps to an entry in this table. An Orec represents either the latest timestamp

at which the associated memory locations have been written, or that the location is currently locked. Below are the implementation details:

TxBegin Set the checkpoint, read the global timestamp, and perform per-thread metadata initialization.

TxRead Read a value directly from memory, and validate the read-set to make sure the running transaction has a consistent view [49]. Abort the transaction if the timestamp of any memory location in its read-set changed.

TxWrite Store the original value in a local undo log. Lock the Orec for this memory location and update the value in-place.

TxEnd If it is a read-only transaction, commit. Otherwise, validate the read-set, get a new timestamp, and set it as the value in the Orecs of all updated locations.

TxAbort Write back the values in undo log, unlock Orecs in the write-set. Then reset the metadata and jump back to the checkpoint.

Logs are widely used in STM algorithms to guarantee that memory updates caused by the aborted transaction should never be seen by other transactions or the non-transactional execution. In the GCC STM algorithm, an undo log is used to capture the original value before the in-place update. If a transaction aborts, the transactional effects can be undone by replaying undo log contents. An advantage of the undo log-based design is that a read can always read directly from memory. Many other STM algorithms (e.g., NOrec [24] and RingSTM [111]) employ redo logs to buffer memory updates, writing back the redo log contents only when the transaction commits. In this case, transaction aborts are cheaper,

because they only need to reset the redo log. However, all read operations need to check the redo log first to get the latest value. Such redirection could be expensive. In practice, no algorithm dominates all others in all scenarios.

Another important design choice is contention management. When transactions repeatedly fail to commit, due to repeated conflicts with other threads, a TM implementation may invoke a contention manager [103], which is responsible for delaying or aborting some transactions in order to increase the likelihood that others may complete. Although contention management policies vary, most TM implementations employ serialization as a last resort: a transaction that fails too many times will request that all other transactions abort, and no new transactions commence, until it completes. Unless the workload exhibits pathological conflicts, serialization should be rare. In GCC, the default is for software transactions to serialize after 100 attempts, and hardware transactions to serialize after two. Dynamically tuning this parameter has been shown to have a significant impact on some workloads [30]. Any nontrivial amount of serialization, however, has a terrible effect on performance, particularly because serialization delays all active transactions, even those from completely unrelated parts of the program (unlike lock-based critical sections, which are partitioned by the locks that they acquire).

#### 1.1.4 Advanced Features

Before introducing applications of TM, it is useful to review some more advanced concepts from TM literature. We first discuss the state of the art in transactional condition synchronization. Then we discuss issues related to memory consistency, which cause the "privatization" and "publication" problems, and we describe the general solutions for both.

Condition Synchronization In most cases, a lock-based critical section in a traditional concurrent program can be replaced by a transaction. This approach does not, however, provide a means for conditional synchronization. The behavior of conditional synchronization breaks atomicity by letting uncommitted transactions wait until the precondition is fulfilled by other transactions. To that end, Harris et al. proposed a special form of self abort, called retry [51]. When an in-flight transaction discovers that some precondition of

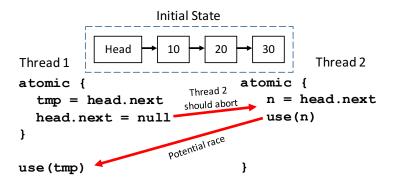

Figure 1.2: The privatization problem: If Thread 2 is executing speculatively, and is not aware that Thread 1 commits, races may occur between accesses to the node containing the value 10.

its completion does not hold, retry is used to immediately abort the transaction and undo its effects. Abstractly, this casts condition synchronization as a scheduling operation, with retry indicating that a transaction should not execute yet. Optimized implementations of retry track the set of locations read by the retrying transaction, and do not re-attempt the transaction until at least one of those locations is modified by another transaction. While the TMTS does not support retry, it can be approximated (albeit somewhat inefficiently) by using self abort from an atomic transaction.

Semantics and Ordering The TMTS does not separate transactional and nontransactional memory: any location can be accessed both transactionally and nontransactionally. In HTM systems, the cost of these semantics is negligible because HTM provides strong atomicity. However, nontransactional memory accesses are not tracked by STM implementations. It presents a challenge to STM implementations known as the *privatization problem* [109]: Although concurrent transactional and nontransactional access to the same location is a data race (which has undefined semantics in C++), a thread that uses a transaction to remove an object from a shared data structure and accesses it nontransactionally afterwards may conflict with another transaction that accessed the same object concurrently but is still "cleaning up". The problem is illustrated in Figure 1.2. Because Thread 2 is executing speculatively, there can be a delay between the point where Thread 1 commits, and the point where Thread 2 recognizes that it must abort. If Thread 1's transaction transitioned data to a state where transactions can no longer access it, then Thread 1 expects to

be able to access the data immediately upon commit. During the window between Thread 1's commit and Thread 2's abort, simultaneous accesses to the list are unsafe.

To avoid this problem, a thread must not access a privatized object nontransactionally until every transaction that may have accessed that object has completed entirely (i.e., committed or aborted, including clean up). Since an STM cannot, in general, determine when an object is privatized, implementations typically wait after committing any writing transaction until every concurrent transaction has completed entirely; this waiting is called quiescing. In the GCC TM implementation, threads quiesce after committing. The quiesce operation involves waiting for all concurrent transactions to commit, abort and clean up or validate.

### 1.2 Applying Transactional Memory in Real-World Applications

In this section, we discuss three important applications of TM. Transactional Lock Elision (TLE) ought to be easily applied on legacy code, and it is taken for granted that using TM to replace locks could result in better scalability. Concurrent building blocks usually contain small critical sections, and they rarely have complex synchronization patterns or irrevocable operations. Thus it is promising to leverage the properties of HTM to create high performance and dedicated algorithms. Last but not the least, directly programming with Persistent Memory (PM) has been shown to be difficult and error-prone [97,104], and TM is becoming the most popular programming model for accessing data in PM due to its ability to provide atomic and durable updates of multiple objects.

#### 1.2.1 Transactional Lock Elision

Transactional Lock Elision (TLE) is the most straightforward use of TM in real-world programs [94,96,100,102,128]. In TLE, a programmer takes as input a lock-based program with less-than-desirable performance, and replaces locks with TM, hoping that in so doing, unnecessary serialization can be avoided. The programmer in this case thinks of TM as a mechanism for achieving lock elision, and is encouraged to ignore advanced features of the

#### TM implementation.

We take HTM and its lock-based fall-back path as an example to illustrate how TLE works. The program executes the HTM fast path first, then falls back to a lock-based execution if the HTM cannot successfully commit. This programming model requires synchronization between the HTM and locks. Suppose a thread is executing in the lock-based critical section and delays in the middle of its execution. At this time, HTM transactions could commit if there was no synchronization between HTM and the lock-based code. Thus, concurrent execution of HTM transactions and lock-based code may introduce non-serializable behavior. To solve this problem, threads have to check the lock state at the beginning of every HTM attempt. If the lock is held by another thread, then the thread waits for the lock to be released. If the lock is available, the thread continues executing the HTM path. If the lock is acquired by another thread during the HTM execution, HTM will abort because of the change to a location (the lock) that it previously read. By doing so, the safety of the concurrent program is guaranteed. However, in order to get better performance, the execution path should remain in HTM as much as possible in order to avoid serialization.

Algorithm 2 presents the pseudocode of an HTM-based TLE retry strategy. More comprehensive applications can be found in [86]. We take Intel's HTM interface, named Restricted Transactional Memory (RTM), as an example. In lines 4, 7, and 9, RTM provides functions for start, explicit abort and successful commit of the transaction. The transaction begins at line 5. Status either indicates that the transaction successfully launched, or it contains the abort code. Line 6 to line 9 are the code executed by RTM. If at any time a transaction aborts, the execution path goes to line 11. Line 12 checks whether HTM aborted because the lock was held by another thread. Line 14 checks whether HTM aborted because of data conflicts. In line 16, excessive aborts or capacity conflicts cause the thread to execute the lock-based path (line 17–19). Otherwise, it retries the HTM path.

The retry policy in this code example is simple. There could be more complicated ones designed for specific applications. Regardless, there are two things we need to take care of: First, the algorithm needs to check the lock status right after HTM starts (line 6), this prevents lock-based code and HTM from running at the same time. Second, we need to wait

Algorithm 2: Pseudocode of Transactional Lock Elision (TLE) with Intel RTM

```

1 RetryCount \leftarrow MAX\_RETRY

2 RETRY:

waitForLockToBeReleased()

3

status \leftarrow \_xbegin() // start the transaction by calling \_xbegin()

if status = \_XBEGIN\_STARTED then

5

inside of HTM execution

check whether the lock has been hold

if check(lock) then

6

\_xabort(REASON)

/* critical section code here */

_xend() // successfully commit the transaction

9

Return

10

else

11

// HTM abort

if status \land \_XABORT\_EXPLICIT then

12

goto RETRY // the lock is held by other thread

13

14

if status \land \_XABORT\_CONFLICT then

RetryCount \leftarrow RetryCount - 1 // data conflict

15

if status \land \_XABORT\_CAPACITY \lor RetryCount = 0 then

16

// HTM abort due to capacity or already attempted MAX times, fall back to slow path

17

* critical section code here */

18

release(lock)

19

20

Return

goto RETRY

```

until the lock is available before we can try HTM (line 3). Suppose one thread is holding the lock: then all other threads that are trying HTM transactions must continuously abort due to the lock being held. Without care, they could fall back to lock-based code after reaching the maximum retry threshold, and execution would degrade to that of a lock-based program.

I/O Problems The effort to standardize TM support in C++ [3] has, to date, taken a pragmatic approach with respect to I/O. Clearly, if transactions are to replace lock-based code, then it must be possible to perform I/O operations on shared data, despite the possibility of concurrent attempts to access that same shared data. However, I/O performance has not seen much attention. In particular, it has been assumed that an I/O transaction can be statically identified by the programmer, and that it is acceptable to serialize all transactions at the time when I/O is attempted, so as to prevent concurrent accesses to the data during the I/O operation. This mechanism, broadly, is known as "irrevocability" [91,110,112,118].

Irrevocability Irrevocability is a coarse-grained mechanism, which allows the execution of arbitrary operations within a transaction, even if those operations cannot be undone. Examples include accessing device registers, arbitrary system calls, communication with other threads via volatile and atomic variables, and I/O. Any student of Amdahl's law will immediately recognize global serialization of transactions as a potentially significant bottleneck. Indeed, Wang et al. inadvertently discovered as much in their exploration of transactional condition synchronization for the PARSEC benchmark suite [117]: in the "dedup" application, output by one pipeline stage eliminates all concurrency and scaling from an application whose lock-based equivalent scales well. The one-size-fits-all nature of irrevocability is costly, but its simplicity is appealing: difficult tasks are no harder with irrevocable transactions than with locks. For example, irrevocability ensures low-level atomicity and durability of output: in applications with durability constraints, it is essential that programmers control the timing of calls to fsync, and the atomicity of an fsync call with respect to preceding write operations, and irrevocability affords this level of control.

Deferred operations Apart from irrevocability, the only other promising approaches to transactional output rely on deferred operations. Many output operations, such as logging and error messages, can be achieved via deferred operations [14,91,102]. More formally, Volos et al. presented a general mechanism for deferring I/O in software transactions, via buffering and "shadow" file descriptors [115]. Unlike irrevocability, deferred output operations do not constrain concurrency. However, they suffer from two problems of their own. First, to ensure that deferral is correct, it is necessary to create an explicit copy of the data to output. This copy is in addition to any copying that occurs as part of a system call, and while it can be optimized in certain cases, it nonetheless introduces latency concerns. Furthermore, for hardware transactions, buffering may result in the working set of the transaction exceeding cache capacity, which could lead to transactions serializing. The second problem with deferred output is that real programs often care about the return value of a write system call. When the write is delayed, it seems that the continuation of the transaction must either (a) ignore the return value, or (b) be scheduled after the output, as a second transaction that is not atomic with the first.

More discussion about I/O problems and existing solutions appears in Section 1.4. In Chapter 4, we introduce our solution: atomic deferral, an extension to TM that allows programmers to move costly operations out of a transaction without changing program behavior. That is, the transaction and its deferred operation appear to execute as one unit from the perspective of other transactions, and the resulting execution remains serializable, for both hardware and software TM implementations.

Apart from I/O, there are many unsolved problems (e.g., third-party libraries, complex synchronization patterns) which prevent TLE from being ready to use in production. In Chapter 3, we discuss other obstacles and propose ad-hoc solutions. Our experience are gained from applying the C++ TMTS to elide locks in two real-world programs, PBZip2 and x265.

#### 1.2.2 Facilitating the Implementation of Concurrent Data Structures

Concurrent data structures are fundamental building blocks in modern programs. In many applications, the performance of concurrent data structures determines the scalability of the program. TM facilitates the implementation of concurrent data structures for the following reasons:

- Synchronization in concurrent data structures is relatively straightforward;

- The size of critical sections fit within HTM capacity in most cases;

- Data structures rarely contain complex concurrency control like irrevocable instructions or condition variables;

- TM is particularly appealing for data structures and applications with irregular or hard-to-predict memory accesses (e.g., the rebalancing operations of a balanced binary search tree mutation), which are difficult to implement efficiently using locks.

Based on that, there are many research papers leveraging TM to craft concurrent data structures with better scalability [27, 32, 63, 75, 120].

Balanced Binary Search Trees (BST) are commonly used in a wide range of applications because they provide a logarithmic bound on search operations. In a concurrent environment, it is notoriously difficult to achieve satisfactory performance by using locks. Two reasons cause this dilemma: rebalancing and indirect deletion. Rebalancing refers to the

problem where an insert or remove operation causes imbalance in the tree, and the operation must restore balance before returning in order to guarantee asymptotic complexity for future operations. Indirect deletion happens when a target node has two children. The target node has to be replaced by its successor node (based on value) and the real delete happens at a leaf node. Fine-grained locking is difficult for balanced BST because when rebalancing happens, the thread traverses upward, which is opposite to the direction the thread traverses to search the elements from root to leaf. This behavior makes lock acquires and releases difficult, because it is impossible to prevent deadlock by acquiring locks in a canonical order. Lock-free approaches are similarly difficult. Existing ways to solve the problem include relaxing the balancing conditions or using coarse-grained synchronization. Another way is to use Read-Copy-Update (RCU) [79]. However, it increases the overhead of copying existing subtrees when changes are needed, and does not allow concurrent writes. Wrapping entire BST functions in HTM transactions is one option. The scalability for this approach will largely depend on the size of the BST and the number of write operations. Siakavaras [32] proposed a new method, which combines HTM and RCU, to implement concurrent balanced BST. The algorithm achieves several appealing results: It allows concurrent update, and it introduces negligible synchronization overhead on reading operations. Although the algorithm suffers from many problems, such as live locking and memory leaks, it provides the best performance among existing algorithms for concurrent, strictly balanced BST.

In previous work [75], we also discovered that HTM can be applied in many cases to accelerate existing non-blocking data structures. For example, hardware instructions such as CAS are directly supported by x86 processors, but only for one machine word. Software emulations of CAS can support multiple words, such as k-compare-and-swap (KCAS) [76]. Wait-free KCAS is expensive but can significantly simplify the design of non-blocking data structures. In this case, HTM can be applied as the simple and fast path for KCAS (atomically updating multiple memory locations). Another example is that update operations for non-blocking data structures usually are implemented by copy-on-write. Updating a bucket in nonblocking hash map [74] would require copying the whole bucket. It is expensive if the bucket contains many elements or the memory capacity is limited. HTM can provide a fast

path for threads to update the bucket in-place. In both cases, synchronization between the fast path and fall-back path is straightforward.

Memory Reclamation Problems Most non-blocking concurrent data structures in research papers do not provide memory management in their implementation [11, 21, 32, 54, 75, 84, 95]. One possible reason is that memory management incurs latency. Hazard pointers [83] allow a data structure node to be reserved by a thread before it is accessed. If another threads intends to delete the node, it has to make sure no one is accessing it by checking the hazard pointer. This method introduces significant overhead because each node access will incur a write fence. Hazard pointers do not allow immediate memory reclamation when there are other threads accessing the candidate node. Epochs [41] have less latency but will delay the reclamation if one thread is blocked in an earlier epoch. It is difficult to bound the time between logical removal and physical reclamation [34], and many scalable techniques accept unbounded worst-case delay for a bounded [83] or unbounded [26] number of items. To avoid these delays, a system might fall back to complex or expensive measures when the amount of unreclaimed memory becomes too great [5, 10, 12, 19]. However, there will always remain programs whose correctness depends on memory being reclaimed immediately, hence the need for precise memory reclamation.

In section 1.4, we discuss the incompatibility between non-blocking techniques and precise memory management. By leveraging the immediate abort property of HTM when accessing de-allocated memory locations, we propose revocable reclamation to bridge the gap between them. A detailed solution and implementation are described in Chapter 2.

#### 1.2.3 Persistent Transactional Memory

Non-volatile byte-addressable memories present an exciting new opportunity for creators of high-performance systems. With non-volatile main memory (NVM) or persistent memory (PM), a program can avoid sources of latency associated with writing to traditional storage media, and instead achieve persistence through memory writes to an PM whose latency is within a constant factor of the speed of RAM.

Due to byte-addressability and fast access, PM is likely to be accessed directly through

Figure 1.3: In-memory application seamlessly persists across power failures

CPU load and store instructions. Combining with non-volatility, PM can dramatically change how software persists data. As we can see in Figure 1.3, data remain volatile unless they reach persistent memory. However, the memory controller decides when and in what order the data write to PM due to hardware optimizations for writes. Without buffering and ordering methods, traditional programming models may cause the program reaching an unpredictable and unrecoverable state when a power failure happens.

Transforming a program to use PM can be nontrivial. Consider an application that persists program data via the file system interface. If the program crashes between file writes, or fails in a way that corrupts RAM, the integrity of the persisted data is not compromised. Similarly, if a fault occurs during a file write, the operating system or hardware (e.g., RAID) is responsible for ensuring write integrity. In contrast, if program memory is also the storage medium, then it is the program's responsibility to ensure the integrity of the data in the face of program crashes at arbitrary points in the program's execution.

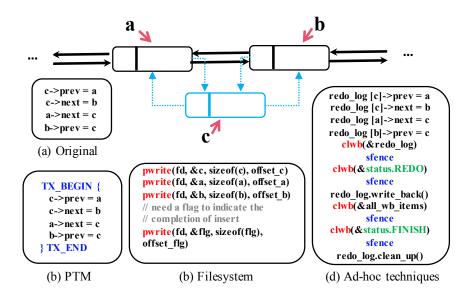

Three programming models have emerged to address this challenge [87]. Figure 1.4 compares using a PTM library, using a file system interface, and directly programming with PM to insert a new node into a persistent doubly linked list:

- (a) represents the original volatile code on DRAM.

- (b) shows the code using PTM library. With persistent transactional memory, pro-

Figure 1.4: Inserting node c to a doubly linked list under different programming models

grammers mark the regions of code, and a run-time system tracks accesses to PM within those regions. The run-time system ensures the atomicity of transactions, using roll-forward or roll-back techniques.

- (c) represents issuing system calls to the PM-aware file systems. Implementing a file system on the PM would simplify programming on PM. Although it looks simple and familiar, many of the performance benefits of PM (such as random byte-addressable access) are lost.

- (d) demonstrates ad-hoc techniques, through which the programmer uses custom assembly instructions to flush data from caches to the NVM, and fences to ensure ordering between these flushes and other accesses to program data. To make sure the doubly linked list remains consistent across failures, four rounds of interacting with PM are necessary: Persisting the redo log; Changing the status to indicate all updates in the transaction can be recovered from the redo log; Writing back the content in the redo log and making them persistent; Updating the status to finish the operation.

For applications with irregular data access patterns, and applications that rely on ad-hoc data structures, the most promising model for interacting with PM is a transactional model. In many ways, PTM resembles software transactional memory: both need instrumentation

of memory accesses. Many researchers [15,45,66] have implemented PTM by transforming existing STM algorithms. However, we could not find any previous research comparing the performance of different PTM algorithms and summarizing the experience via transforming them.

In section 1.4, we present preliminary findings for transforming existing STM algorithms to support data persistence. Details of our work on supporting data persistence are discussed in Chapter 5.

#### 1.3 Dissertation Motivation

Despite significant interest and effort from the research community, TM has not yet seen widespread use in industry. The lack of adoption is particularly surprising given that (a) vendors have supported hardware TM (HTM) in commercially-available processors since 2012 [86], (b) compiler support for software TM (STM) has been present in the GCC compiler since 2012 [42], (c) a Technical Specification for using TM in C++ programs (the TMTS) was announced in 2015 [61], (d) Intel has released NVML [59], a library with a transactional interface to support programming on non-volatile memory.

To understand the problem, we conducted extensive experiments in applying TM in real-world applications. We divide applications into four categories:

- Sophisticated software such as the MySQL InnoDB engine [119], the PBZip2 parallel file compression/decompression toolkit [44], and the x265 media encoder/decoder [93].

- Primary parallel programming benchmarks such as the PARSEC Benchmark Suite [8] and the Stanford Transactional Applications for Multi-processing (STAMP) [85].

- Non-blocking and lock based concurrent data structures [36,62,71,73,74,95].

- Benchmarks for persistent memory, such as a B+ tree microbenchmark, On-line Transaction Processing Benchmark (TPCC) [113] and Telecom Application Transaction Processing Benchmark (TATP) [107].

Some of these applications contain only small critical sections, and naively replacing locks with transactional blocks can improve performance and programmability. Even in these cases, it is possible that the performance will get worse. The costs may originate

from the latency of STM, or continuous transactional aborts triggered by the workload. We can alleviate these problems by applying different STM algorithms or different retry policies. Part of the difficulty of programming with TM is insufficient infrastructure. We spent much time bypassing or reimplementing libraries in our TLE work because many standard libraries lack TM support [65].

The dissertation mainly focuses on applications that can not be transactionalized without dramatic performance degradation or significant effort. For persistent memory, the

research on transactional execution time for PM is still in the early stages. Thus we evaluate the performance of existing TM algorithms with data persistence support to motive the

future persistent transactional memory designs. We believe introducing these challenges

and proposing techniques that tailor TM to them makes a valuable contribution to the

acceptance of TM.

#### 1.3.1 Thesis Statement

In this dissertation, we demonstrate that existing TM platforms and common parallel programming models are not compatible with each other, and even state-of-the-art TM algorithms are not optimal when transformed to support data persistence. We then propose, implement, and evaluate solutions. Our work can be summarized as diversifying the transactional programming model, extending the transactional memory API, and enhancing transactional memory implementations with more features that enable TM to fit the needs of real-world applications.

#### 1.4 Contributions

In this section, we summarize our observations obtained from the practical experience of applying transactional memory in real-world applications. None of the applications are trivial in practice. Following each observation, we either describe our method to solve the problem or present our experience as future research guidelines so that readers can learn from them. We also present related work (if any) and compare it with the ideas we propose. Each topic is expanded in an independent chapter.

# Observation 1: Non-blocking techniques are not compatible with precise memory reclamation.

In traditional lock-based code, when removing a node from the data structure, the node is guaranteed to be exclusively accessed by the removing thread. Thus it is safe to be deleted immediately. For concurrent non-blocking data structures, it is either expensive or impossible to provide information about how many threads are accessing the node when the node is unlinked from the data structure. Thus immediate reclamation of the node is not safe.

HTM not only provides hardware support for speculative execution (non-blocking), but also allows threads to access the data which already may be reclaimed by other threads (this causes HTM transactions to abort immediately). Notice that without HTM, such memory accesses lead to programs crashing (e.g., segmentation faults). This property makes immediate memory reclamation possible for non-blocking data structures implemented with HTM.

Wrapping the entire operation on a data structure in one hardware transaction would make non-blocking techniques compatible with precise memory reclamation. However, like critical sections in lock-based implementations, it is desirable to keep transactions as small as possible, in both time and space (i.e., duration and number of locations accessed): smaller transactions are less likely to conflict and abort. Furthermore, existing hardware support for transactional memory (HTM) [86] typically has capacity limits, which further makes this idea impractical.

We introduce a mechanism to link consecutive transactions by "reserving" a location at the end of a transaction and checking the reservation at the beginning of the next transaction, aborting if the location has changed since the previous transaction committed. By doing so, we link a challenge in TM to the challenge of providing memory safety for non-blocking data structures. That is, now TM must deal with the question of what happens if a reserved location is reclaimed? To avoid this problem, we introduce revocable reservations, which allow threads to revoke all reservations to a specified location. A subsequent transaction that checks a reservation will see that it has been revoked and therefore not attempt to access the formerly reserved location. By leveraging features of HTM, particu-

larly the immediacy of aborts, concurrent operations are able to revoke these reservations and immediately reclaim memory, without compromising correctness. The implementation, application and evaluation of *revocable reservations* are described in Chapter 2.

# Observation 2: Complex patterns of synchronization limit the applicability of a transactional programming model.

To understand the performance of TLE in real-world applications, we applied the C++ TMTS to elide locks in two real-world programs: the PBZip2 file compression tool, and the x265 video encoder/decoder. In both cases, the programs were already carefully crafted to avoid lock contention and to scale.

TLE ought to be easy: the programmer need only replace each lock-based critical section with a transaction. Unfortunately, our experience does not validate the expectation: In x265, the most important critical section was not serializable, and we could not transactionalize it without understanding several thousand lines of code, and changing the way in which threads interacted with one of the central queues in the program; In the case of PBZip2, we found that naively transactionalizing the code works. However, the performance was not competitive to the lock-based version unless we extended the C++ TMTS with a mechanism for relaxing the ordering guarantees on certain transactions.

One contribution made in Chapter 3 is proposing language-level support for transactions to dynamically disable quiescence. Prior work by Yoo et al. [122] suggests that in some workloads, quiescence can be disabled for all transactions. Yoo et al. also showed that in such cases, disabling quiescence for those workloads had a significant improvement on performance. Unfortunately, such an approach is not compositional: any change to the program requires whole-program analysis to determine if globally disabling quiescence remains correct. It also offers no value when transactionalizing PBZip2, because there are few transactions that must privatize (consumer and producer model). We studied transactional memory benchmarks and data structure benchmarks to further explore how quiescence affects the performance of TLE.

By overcoming these difficulties, Chapter 3 demonstrates the first example of the TMTS, as implemented in the GCC compiler, improving the performance of real-world code. Moreover, the improvement spanned both hardware and software implementations of TM.

#### **Algorithm 3:** Irrevocability-induced delays // Unrelated thread // Output thread // Clean-up thread 1 synchronized 1 atomic 1 atomic elt.prepare(data)if elt.sent then use(other)2 $net\_send(\&elt)$ 3 elt.log() $elt.sent \leftarrow true$ elt.reclaim() 4 5 else retry

# Observation 3: Serialization overheads for irrevocable and long-running operations are dramatic.

Broadly speaking, there are three causes of serialization in modern TM: irrevocability, contention management, and capacity management. Capacity management refers to situations in which a transaction's memory footprint is either too large for the TM to handle (as in the case of HTM), or causes too much logging overhead (in STM). In either case, the TM implementation may choose to serialize transactions so that the large transaction can complete efficiently.

When we transactionalized the MySQL Innodb engine and PARSEC benchmarks, we found many I/O operations in critical sections. Moreover, there are long-running computational operations in the PARSEC dedup benchmark, which become the main bottleneck for TLE. Such operations make TLE perform significantly worse than the original lock-based programs.

During profiling, we found that the composition of serialization and quiescence created unexpected latency in transactions (much worse than what was already known). Consider the code in Algorithm 3. An output thread updates an element, using some shared data, and then sends it over the network. The update and send are expected to be a single atomic operation. When the update communication is complete, then a clean-up thread will wake (via retry), log the element, and reclaim its memory. Meanwhile, some other transaction is accessing unrelated data.

When the output thread reaches line 3, GCC's STM will wait for the other transactions to complete, and its HTM support will cause the other transactions to abort. Note that the "unrelated" thread's transaction does not touch any data used by the output thread. It should neither be aborted, nor cause a delay in the output thread. However, incomplete

information about which transactions might be active, and what data they might touch, necessitates conservative behavior in the TM implementation.

If net\_send were safe to call from a transaction, we could still observe significant delays in STM. Suppose that the output thread and an unrelated thread ran concurrently. When the unrelated thread was ready to commit, quiescence would demand that it idle until the output thread completed, in order to ensure that any potential use of privatized data would not race with the output thread's upcoming reads and writes.

These sorts of delay, and the delays that arise from irrevocable execution, also manifest when transactions are serialized to ensure progress. Worse, since TM does not allow the programmer to partition transactions, any serialization or quiescence in any transaction will incur overhead proportional to the total number of active transactions at that instant. In short, I/O, long-running operations, and high contention can result in delays for all concurrent transactions.