UNLV Theses, Dissertations, Professional Papers, and Capstones

5-2011

# Peripheral soldering of flip chip joints on passive RFID tags

Md Syful Islam University of Nevada, Las Vegas

Follow this and additional works at: https://digitalscholarship.unlv.edu/thesesdissertations

🔮 Part of the Manufacturing Commons, and the Materials Science and Engineering Commons

## **Repository Citation**

Islam, Md Syful, "Peripheral soldering of flip chip joints on passive RFID tags" (2011). *UNLV Theses, Dissertations, Professional Papers, and Capstones.* 1042. https://digitalscholarship.unlv.edu/thesesdissertations/1042

This Dissertation is protected by copyright and/or related rights. It has been brought to you by Digital Scholarship@UNLV with permission from the rights-holder(s). You are free to use this Dissertation in any way that is permitted by the copyright and related rights legislation that applies to your use. For other uses you need to obtain permission from the rights-holder(s) directly, unless additional rights are indicated by a Creative Commons license in the record and/or on the work itself.

This Dissertation has been accepted for inclusion in UNLV Theses, Dissertations, Professional Papers, and Capstones by an authorized administrator of Digital Scholarship@UNLV. For more information, please contact digitalscholarship@unlv.edu.

## PERIPHERAL SOLDERING OF FLIP CHIP JOINTS

## ON PASSIVE RFID TAGS

by

## Md Syful Islam

Bachelor of Science in Mechanical Engineering Bangladesh University of Engineering and Technology, Dhaka 1986

Master of Science in Mechanical Engineering Bangladesh University of Engineering and Technology, Dhaka 1990

> Master of Science in Mechanical Engineering Tuskegee University, Tuskegee 2001

A thesis submitted in partial fulfillment of the requirements for the

Doctor of Philosophy in Mechanical Engineering Department of Mechanical Engineering Howard R. Hughes College of Engineering

> Graduate College University of Nevada Las Vegas May 2011

Copyright by Md Syful Islam 2011 All Rights Reserved

## THE GRADUATE COLLEGE

We recommend the dissertation prepared under our supervision by

## **Md Syful Islam**

entitled

## **Peripheral Soldering of Flip Chip Joints on Passive RFID Tags**

be accepted in partial fulfillment of the requirements for the degree of

## **Doctor of Philosophy in Mechanical Engineering**

Zhiyong Wang, Committee Chair

Brendan O'Toole, Committee Member

Woosoon Yim, Committee Member

Vellore Venkatesh, Committee Member

Rama Venkat, Graduate Faculty Representative

Ronald Smith, Ph. D., Vice President for Research and Graduate Studies and Dean of the Graduate College

May 2011

### ABSTRACT

#### **Peripheral Soldering of Flip Chip Joints on Passive RFID Tags**

by

Md Syful Islam

Dr. Zhiyong Wang, Examination Committee Chair Associate Professor of Mechanical Engineering University of Nevada, Las Vegas

Flip chip is the main component of a RFID tag. It is used in billions each year in electronic packaging industries because of its small size, high performance and reliability as well as low cost. They are used in microprocessors, cell phones, watches and automobiles. RFID tags are applied to or incorporated into a product, animal, or person for identification and tracking using radio waves. Some tags can be read from several meters away or even beyond the line of sight of the reader. Passive RFID tags are the most common type in use that employ external power source to transmit signals. Joining chips by laser beam welding have wide advantages over other methods of joining, but they are seen limited to transparent substrates. However, connecting solder bumps with anisotropic conductive adhesives (ACA) produces majority of the joints. A high percentage of them fail in couple of months, particularly when exposed to vibration.

In the present work, failure of RFID tags under dynamic loading or vibration was studied; as it was identified as one of the key issue to explore. Earlier investigators focused more on joining chip to the bump, but less on its assembly, i.e., attaching to the substrate. Either of the joints, between chip and bump or between antenna and bump can fail. However, the latter is more vulnerable to failure. Antenna is attached to substrate, relatively fixed when subjected to oscillation. It is the flip chip not the antenna moves during vibration. So, the joint with antenna suffers higher stresses. In addition to this, the strength of the bonding agent i.e., ACA also much smaller compared to the metallic bond at the other end of the bump.

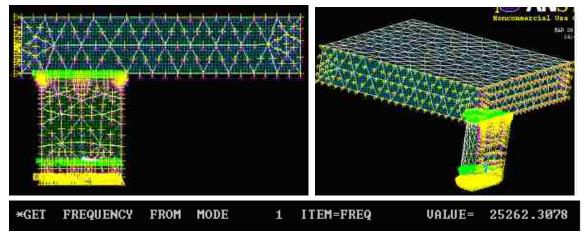

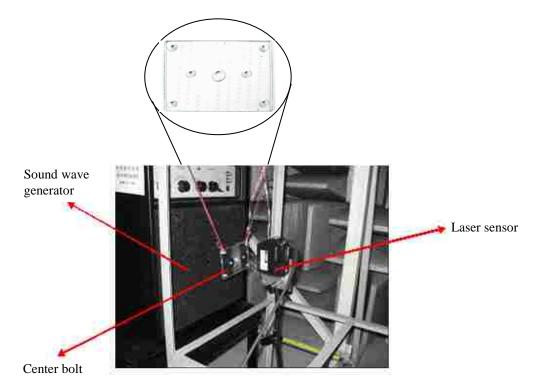

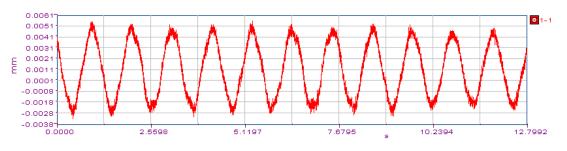

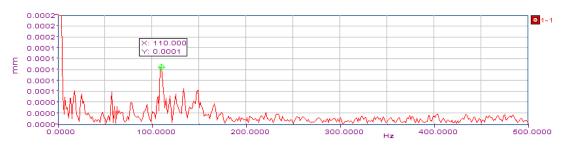

Natural frequency of RFID tags was calculated both analytically and numerically, found to be in kilohertz range, high enough to cause resonance. Experimental investigations were also carried out to determine the same. However, the test results for frequency were seen to be in hundred hertz range, common to some applications. It was recognized that the adhesive material, commonly used for joining chips, was primarily accountable for their failures. Since components to which the RFID tags are attached to experience low frequency vibration, chip joints fail as they face resonance during oscillation. Adhesives having much lower modulus than metals are used for attaching bumps to the substrate antennas, and thus mostly responsible for this reduction in natural frequency. Poor adhesive bonding strength at the interface and possible rise in temperature were attributed to failures under vibration.

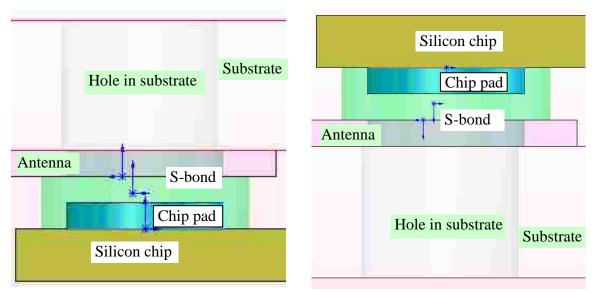

In order to overcome the early failure of RFID tag joints, Peripheral Soldering, an alternative chip joining method was devised. Peripheral Soldering would replace the traditional adhesive joining by bonding the peripheral surface of the bump to the substrate antenna. Instead of joining solder bump directly to the antenna, holes are to be drilled through antenna and substrate. S-bond material, a less familiar but more compatible with aluminum and copper, would be poured in liquid form through the holes on the chip pad. However, substrates compatible to high temperature are to be used; otherwise temperature control would be necessary to avoid damage to substrate. This S-

bond would form metallic joints between chip and antenna. Having higher strength and better adhesion property, S-bond material provides better bonding capability.

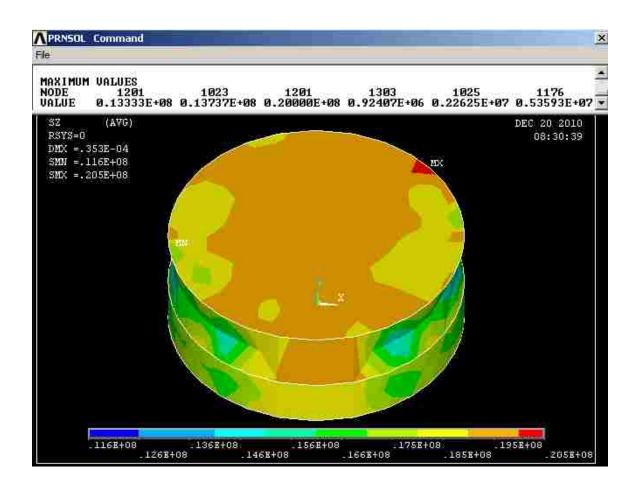

The strength of a chip joined by Peripheral Soldering was determined by analytical, numerical and experimental studies. Strength results were then compared to those of ACA. For a pad size of 60 micron on a 0.5 mm square chip, the new chip joints with S-bond provide an average strength of 0.233N analytically. Numerical results using finite element analysis in ANSYS 11.0 were about 1% less than the closed form solutions. Whereas, ACA connected joints show the maximum strength of 0.113N analytically and 0.1N numerically. Both the estimates indicate Peripheral Soldering is more than twice stronger than adhesive joints.

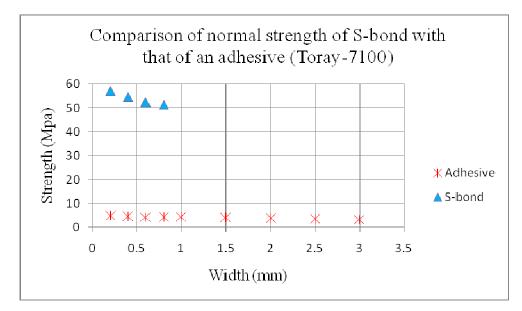

Experimental investigation was carried out to find the strength attained with S-bond by joining similar surfaces as those of chip pad and antenna, but in larger scale due to limitation in facilities. Results obtained were moderated to incorporate the effect of size. Findings authenticate earlier predictions of superior strengths with S-bond. A comparison with ACA strength, extracted from previous investigations, further indicates that S-bond joints are more than 10 times stronger.

Having higher bonding strength than in ACA joints, Peripheral Soldering would provide better reliability of the chip connections, i.e., RFID tags. The benefits attained would pay off complexities involved in tweaking.

| ABSTRACT                                              | iii  |

|-------------------------------------------------------|------|

| LIST OF TABLES                                        | viii |

| LIST OF FIGURES                                       | ix   |

| ACKNOWLEDGMENTS                                       | xi   |

| CHAPTER 1 INTRODUCTION                                | 1    |

| 1.1 RFID tags                                         |      |

| 1.2 Common problems                                   |      |

| 1.3 Flip chip joints                                  |      |

| 1.4 Bonding steps                                     |      |

| 1.4.1 Making UBM                                      |      |

| 1.4.2 Making bumps                                    |      |

| 1.4.2.1 Evaporated UBM / Evaporated solder            |      |

| 1.4.2.2 Sputtered UBM / Electroplated solder          |      |

| 1.4.2.3 Sputtered UBM / Printed solder                |      |

| 1.4.2.4 Electroless UBM / Printed solder              |      |

| 1.4.3 Other solder bumping methods                    |      |

| 1.4.3.1 Stud bump flip chip                           |      |

| 1.5 Joining to antenna/ substrate (assembly)          |      |

| 1.5.1 Adhesive joining                                |      |

| 1.5.2 Thermosonic joining                             |      |

| 1.5.3 Joining with heat                               |      |

| 1.6 Objectives                                        |      |

| CHAPTER 2 LITERATURE REVIEW                           | 21   |

| 2.1 Research related to the formation of UBM and bump | 21   |

| 2.2 Studies cognate to stud bumping                   |      |

| 2.3 Investigations linked to assembly process         |      |

| 2.4 Findings connected to joint characterization      |      |

| CHAPTER 3 RESEARCH APPROACH                           | 41   |

| 3.1 Problem identification                            | 41   |

| 3.2 Vibration modeling                                | 42   |

| 3.2.1 Analytical formulation                          |      |

| 3.2.2 FEA modeling                                    |      |

| 3.2.3 Vibration experiment                            |      |

| 3.3 Results interpretation                            |      |

| 3.4 Alternative joining methods                       | 51   |

| 3.4.1 Long bump bending                               |      |

| 3.4.2 Joining by liquid solidification                |      |

| 3.4.2.1 Connecting bumps with antenna                 |      |

## TABLE OF CONTENTS

| 3.4.2.2 Connecting directly by bonding agent                           | 56  |

|------------------------------------------------------------------------|-----|

| CHAPTER 4 CHIP JOINING BY PERIPHERAL SOLDERING                         | 57  |

| 4.1 Fabrication of peripheral joint                                    | 57  |

| 4.2 Design of Peripheral Soldering joints                              | 59  |

| 4.3 S-bond activation process                                          | 63  |

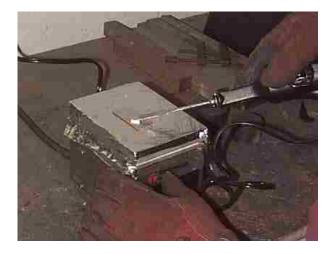

| 4.3.1 Vibrapeen wetting                                                | 65  |

| 4.4 Strength analysis of Peripheral Soldering                          | 66  |

| 4.4.1 Analytical strength estimation                                   | 67  |

| 4.4.2 Strength estimation by FEA                                       | 68  |

| 4.5 Experimental validation                                            | 73  |

| CHAPTER 5 ANALYSIS OF SIZE EFFECT                                      | 74  |

| 5.1 Effect of size on reliability                                      | 74  |

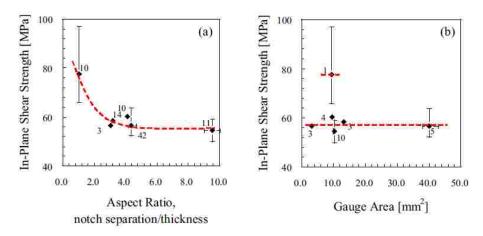

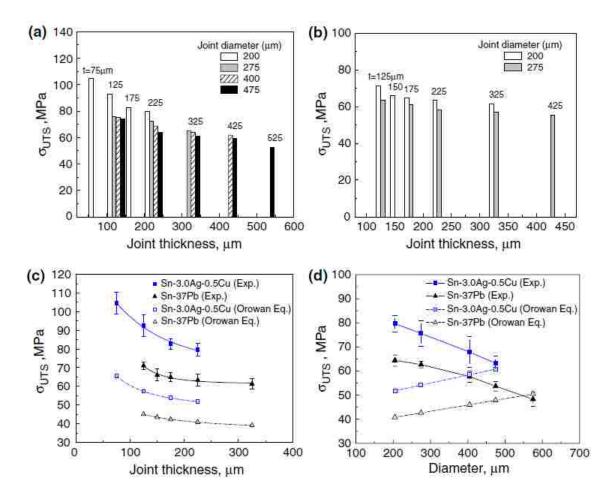

| 5.2 Effect of size on strength                                         | 75  |

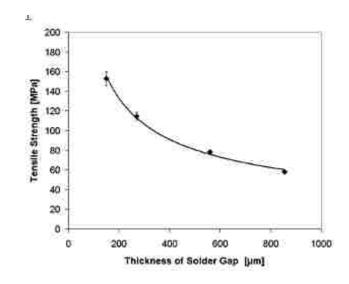

| 5.2.1 Effect of size on solder strength                                | 75  |

| 5.2.2 Effect of size on adhesive strength                              |     |

| 5.2.2.1 Failure criteria using effective length of overlap             |     |

| 5.2.2.2 Failure criteria using adherent thickness                      |     |

| 5.3 Model selection for present work                                   | 89  |

| CHAPTER 6 EXPERIMENTAL VERIFICATION                                    |     |

| 6.1 Fabrication of test specimens                                      | 91  |

| 6.2 Strength tests                                                     | 93  |

| 6.3 Test parameters                                                    | 94  |

| 6.4 Test results and analysis                                          | 94  |

| 6.4.1 Results affected by size effect                                  | 97  |

| 6.4.2 Analysis of moment effect                                        |     |

| 6.4.3 Relation between shear and normal strengths                      |     |

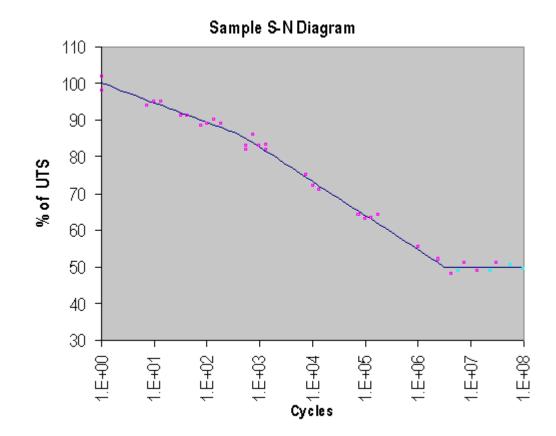

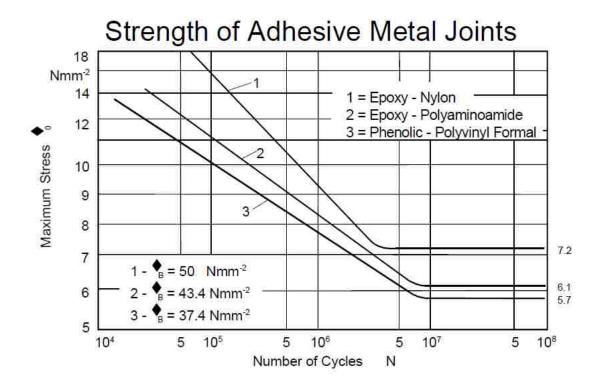

| 6.4.4 Relation between static and fatigue strengths                    | 99  |

| 6.4.5 Effect of surface finish on joint strength                       | 100 |

| 6.4.6 Comparison of chip strengths joined by S-bond with those by ACA. | 101 |

| CHAPTER 7 CONCLUSIONS AND RECOMMENDATIONS                              | 104 |

| 7.1 Conclusions                                                        | 104 |

| 7.2 Recommendations                                                    | 106 |

| REFERENCES                                                             | 107 |

| VITA                                                                   | 113 |

## LIST OF TABLES

| Table 1 | Materials properties used in vibration models                        | 45 |

|---------|----------------------------------------------------------------------|----|

| Table 2 | Materials and dimensions of components                               | 45 |

| Table 3 | Results comparison for natural frequency                             | 45 |

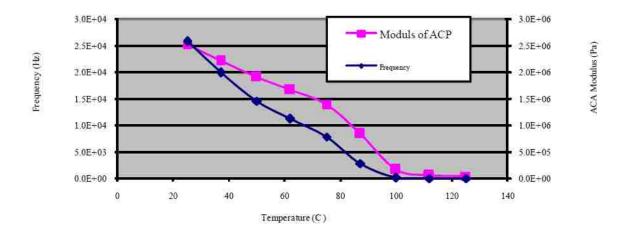

| Table 4 | Effect of temperature on ACA modulus and tag frequency               | 50 |

| Table 5 | Bond strength comparison for a chip connection                       | 73 |

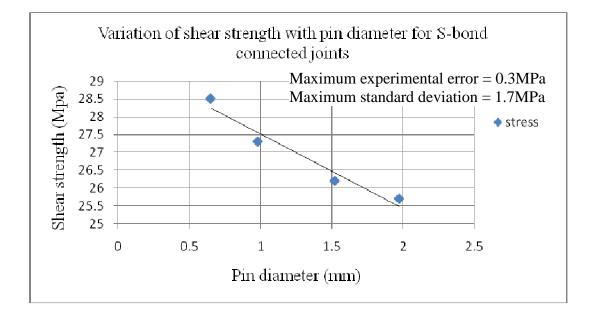

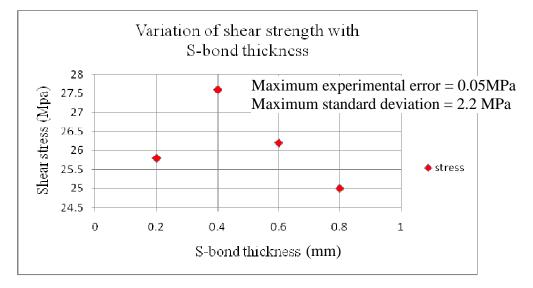

| Table 6 | Bonding strength variation with pin diameter for joining with S-bond | 94 |

| Table 7 | Bonding strength variation with thickness of S-bond material         | 96 |

## LIST OF FIGURES

| Fig. 1  | RFID tags                                                              | 2    |

|---------|------------------------------------------------------------------------|------|

| Fig. 2  | Schematic view of a flip chip joint structure                          | 3    |

| Fig. 3  | UBM design                                                             | 5    |

| Fig. 4  | Wafer with UBM                                                         | 6    |

| Fig. 5  | Solder Bump with UBM covering passivation                              | 6    |

| Fig. 6  | A process chart for UBM and bump formation                             |      |

| Fig. 7  | Evaporation through mask                                               | . 11 |

| Fig. 8  | Evaporation with photoresist                                           | . 11 |

| Fig. 9  | Electroplated bump                                                     |      |

| Fig. 10 | Screen printing                                                        | . 11 |

| Fig. 11 | Electroless plating                                                    | .12  |

| Fig. 12 | Stud bumping                                                           | .12  |

| Fig. 13 | A copper stud bump                                                     | . 15 |

| Fig. 14 | Flip-chip assembly of copper bumped wafers                             | 15   |

| Fig. 15 | Joining of an unbumped chip with adhesive                              | 18   |

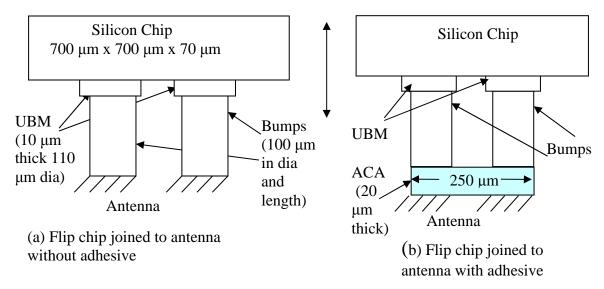

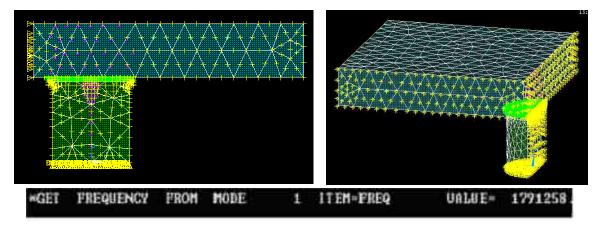

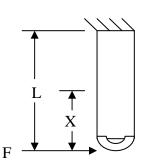

| Fig. 16 | Vibration models                                                       | .43  |

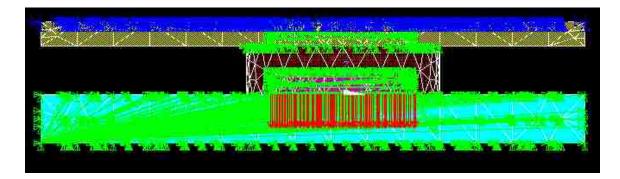

| Fig. 17 | FEA model of a flip chip joint without adhesive                        | . 44 |

| Fig. 18 | FEA model of a flip chip joint with adhesive                           |      |

| Fig. 19 | Vibration experimental set up                                          | . 47 |

| Fig. 20 | Vibration analysis of passive RFID tags                                |      |

| Fig. 21 | Surface integrity of aluminum and gold bumps                           |      |

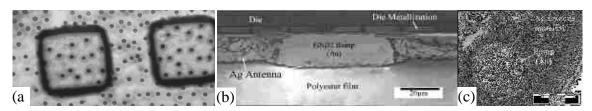

| Fig. 22 | Flip chip bump assembly with adhesive                                  |      |

| Fig. 23 | Effect of temperature on frequency and adhesive modulus                |      |

| Fig. 24 | Some micro drill bits                                                  |      |

| Fig. 25 | Sketch of a bump attached to chip pad                                  |      |

| Fig. 26 | Long bump bending                                                      |      |

| Fig. 27 | Inserted bump-antenna assembly                                         |      |

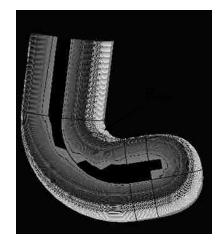

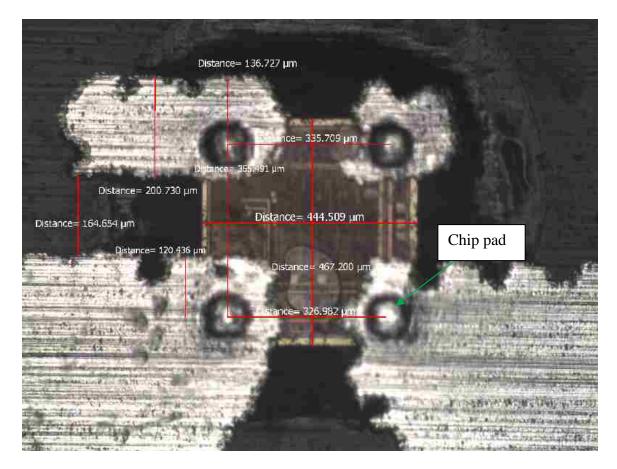

| Fig. 28 | Tilted view of chip joint with antenna connected to chip pad by S-bond |      |

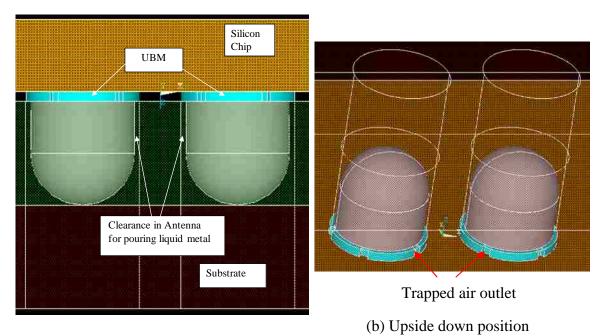

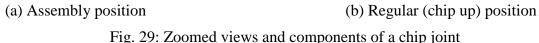

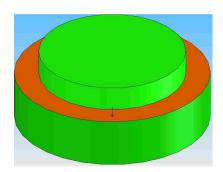

| Fig. 29 | Zoomed views and components of a chip joint                            |      |

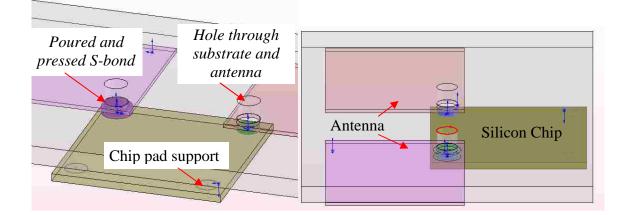

| Fig. 30 | Faces of S-bond bonding with antenna and chip pad                      |      |

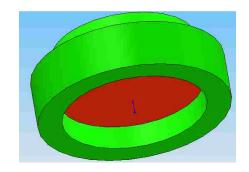

| Fig. 31 | A large size silicon chip                                              |      |

| Fig. 32 |                                                                        |      |

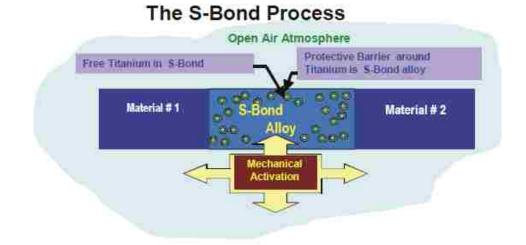

| 0       | Illustration of S-bond processing                                      |      |

| Fig. 34 |                                                                        |      |

| Fig. 35 |                                                                        |      |

| Fig. 36 |                                                                        |      |

| Fig. 37 | ±                                                                      |      |

| Fig. 38 |                                                                        |      |

| Fig. 39 | 1                                                                      |      |

| 8.07    | in S-bond                                                              | 71   |

| Fig. 40 | Stresses in an ACA-connected chip joint with maximum allowable         |      |

| -0      | Loading                                                                | .72  |

| Fig. 41 | -                                                                      |      |

| 0       | Variation of solder shear strength with pad diameter                   |      |

| 0. '2   |                                                                        | . 0  |

| Fig. 43 | Dependency of solder tensile strength with thickness                    | 77  |

|---------|-------------------------------------------------------------------------|-----|

| Fig. 44 | Variation of tensile strength with bump thickness and diameter          | 78  |

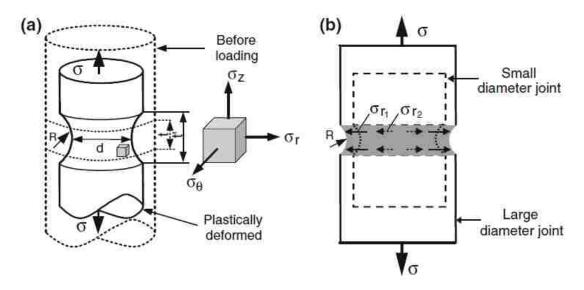

| Fig. 45 | Triaxial stress state and interface stresses in solder joints           | 79  |

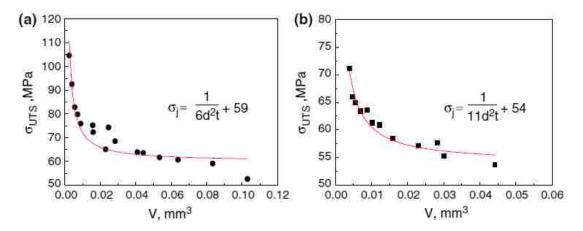

| Fig. 46 | Tensile stress variation with solder volume                             | 80  |

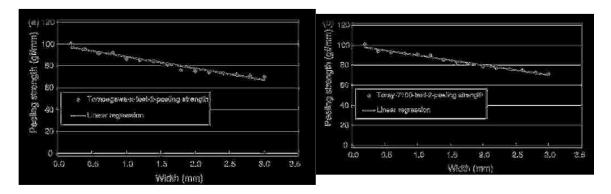

| Fig. 47 | Variation of adhesive peeling strength with width                       | 81  |

| Fig. 48 | Adhesive-bonded joints                                                  | 84  |

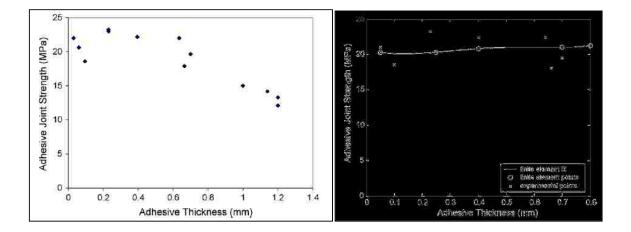

| Fig. 49 | Variation of adhesive strength with thickness                           | 89  |

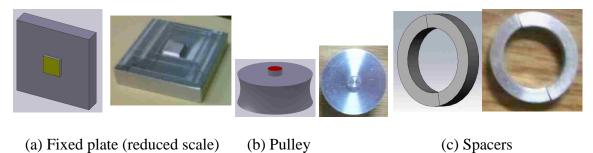

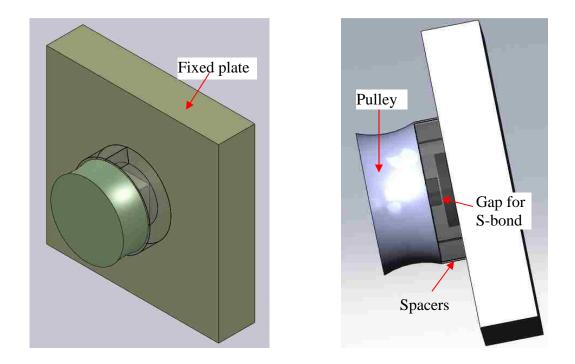

| Fig. 50 | Components of a test specimen                                           | 92  |

| Fig. 51 | Views of a specimen                                                     | 92  |

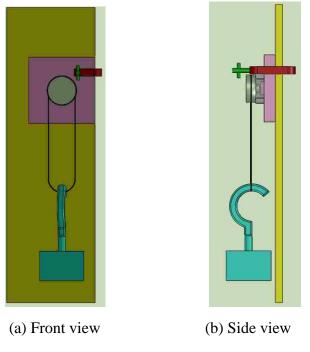

| Fig. 52 | Shear testing of a specimen joined with S-bond                          | 93  |

| Fig. 53 | Shear strength variation with contact pin diameter for S-bond connected |     |

|         | Joints                                                                  | 95  |

| Fig. 54 | Shear stress versus gap size plot for joints with S-bond                | 96  |

| Fig. 55 | Stress versus number of cycles to failure for a metal                   | 99  |

| Fig. 56 | Fatigue strength of adhesive layers under repeated stress               | 100 |

| Fig. 57 | Normal strength comparison of S bond with an adhesive                   | 102 |

|         |                                                                         |     |

#### ACKNOWLEDGMENTS

First of all, the author is grateful to Almighty God Who has enabled him to conduct this research. The author expresses his gratitude to his advisor, Dr. Z. Wang, for his guidance and suggestions as well as informal inspiration that directed toward the successful completion of the research. The author also expresses his gratefulness to Dr. Brendan O'Toole and Department Chair Dr. Woosoon Yim for their support and help for carrying out this research. The author expresses his gratefulness to Dr. Venkatesh for editing a journal paper. The author cordially remembers the cooperation of Dr. Hartmann of Harry Reid Center and Kevin Nelson of machine shop. The author is thankful to other peers including Department Secretary Joan Conway who helped in different issues during the research. The author appreciates providing free ACF samples by Roxanne Jang of 3M and RFID tag samples by Texas Instruments. The author recognizes the sacrifices of his family members for this research. Finally the author expresses his thanks to the committee members for their suggestions and review.

#### CHAPTER 1

### INTRODUCTION

Flip chips or silicon chips are used in billions every year primarily in electronic packaging industries. They are being used in microprocessors, cell phones, watches and automobiles. The boom in flip chip packaging results both from the advantages in its small size (fraction of a millimeter), high performance, wide flexibility, good reliability, and low cost over other packaging methods and from the widening availability of flip chip materials, equipment, and services. This chapter discusses about their different types and methods of joining to substrates.

#### 1.1 RFID tags

RFID stands for Radio Frequency Identification. RFID tags are applied to or incorporated into a product, animal, or person for identification and tracking using radio waves. Some tags can be read from several meters away and beyond the line of sight of the reader. Barcodes, on the other hand, should be visible and only can be scanned from a distance of a foot or less. RFID chips are very similar to barcodes in the sense that a certain amount of data is contained within them, and then transmitted to a reading device which then processes and utilizes the information. They can be scanned through clothes, wallets, and even cars.

There are generally three types of RFID tags: active RFID tags, which contain a battery and can transmit signals autonomously, passive RFID tags, which have no battery and require an external source to provoke signal transmission, and battery assisted passive (BAP) RFID tags, which require an external source to wake up but have significant higher forward link capability providing greater range. The passive type is the

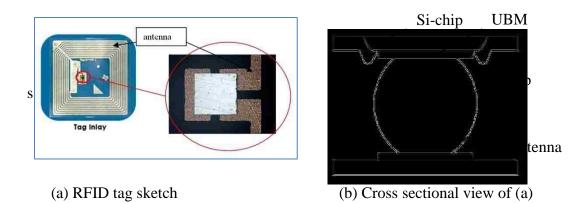

mostly used one; it contains an antenna in which a current induced in it when within range of the RFID reader. The tag then uses that electricity to power the internal chip, which bounces the data back out through the antenna, from where reader picks it up. RFID tags for animals represent one of the oldest uses of RFID technology. Originally meant for large ranches and rough terrain, since the outbreak of Mad Cow Disease, RFID has become crucial in animal identification management. Libraries use RFID tags in the form of square book tag, round CD/DVD tag and rectangular VHS tag. RFID tags are used in enterprise supply chain management to improve the efficiency of inventory tracking and management. Card companies are now looking for payment solutions for adding contactless payment cards to any mobile phone using RFID technology. Governments use RFID applications for traffic management, while automotive companies use various RFID tracking solutions for product management. Many of these solutions may work together in the future, though privacy regulations prevent many initiatives from moving forward at the same pace that technology allows. RFID can be used in a variety of applications, such as: access management, tracking of goods and RFID in retail, tracking of persons and animals, toll collection and contactless payment, machine readable travel documents, smart dust (for massively distributed sensor networks), location based services, tracking sports memorabilia to verify authenticity, airport baggage tracking logistics etc. Some RFID tags are shown in Fig. 1 below.

Fig. 1: RFID tags

#### 1.2 Common problems

Some common problems with RFID are reader collision and tag collision. Reader collision occurs when the signals from two or more readers overlap. The tag is unable to respond to simultaneous queries. Systems must be carefully set up to avoid this problem. Tag collision occurs when many tags are present in a small area; but since the read time is very fast, it is easier for vendors to develop systems that ensure that tags respond one at a time. Moreover some tags fail in few months when subjected to vibrations.

## 1.3 Flip chip joints

Flip chips (integrated circuit chips / dies) are the main component of RFID tags. Flip chip joints are microelectronic assembly in which direct electrical connection of facedown (hence, "flipped") chips are made onto substrates, circuit boards, or carriers, by means of conductive bumps on the chip bond pads. Flip chip components are predominantly semiconductor devices; however, components such as passive filters, detector arrays, and micro electro-mechanical systems (MEMs) devices are also beginning to be used in flip chip form. A schematic view of chip joint is shown in Fig. 2.

Fig. 2: Schematic view of a flip chip joint structure

## 1.4 Bonding steps

Flip chips are joined in three steps: (a) forming UBM (under bump metallization), (b) forming bump, and (c) attaching to antenna (circuit board). In most applications the substrate is integrally connected to the antenna that increases signal reception distance of a chip. Usually the remaining space between the chip and antenna is filled with non-conductive adhesives. Chips are provided with two bonding pads for contacting to external circuit. Some methods avoid the second step, thus join chip UBM directly onto substrate with adhesives with or without the application of bonding compression while others use formation of bump (commonly solder bump) on the UBM and then joining it.

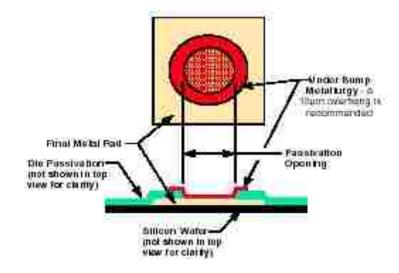

## 1.4.1 Making UBM

The final metal layer of most IC bond pads is aluminum, providing a satisfactory surface for conventional wire bonding. Unfortunately, this surface is inhospitable to most conductive bumps. Aluminum forms an oxide immediately upon exposure to air, and this native oxide is an electrical insulator. Aluminum does not provide a readily solderable surface: neither wettable nor bondable by most solders. Aluminum may corrode over time when not protected from the environment. Consequently, successful bumping must first replace the oxidized aluminum surface with a more hospitable material, the UBM.

Fig. 3: UBM design

This UBM must meet several requirements. It must provide a strong, stable, low resistance electrical connection to the aluminum. It must adhere well both to the underlying aluminum and to the surrounding IC passivation layer, hermetically sealing the aluminum from the environment. The UBM must provide a strong barrier to prevent the diffusion of other bump metals into the IC. The UBM must be readily wettable by the bump metals, for solder reflow. Meeting all these requirements generally requires multiple layers of different metals, such as an adhesion layer, a diffusion barrier layer, a solderable layer, and an oxidation barrier layer. The UBM layers must be compatible metals, which in combination have low internal mechanical stresses. The composite UBM should result from processes that are relatively simple, inexpensive, and easily reproducible in volume production. The design of the UBM should provide a metal layer

that adequately defines and limits the applied bump (hence called, the "bump-limiting metal") while overlapping the die passivation. Fig. 3 shows a typical design layout for UBM relative to the original pad. The IC pad aluminum oxide may be removed by sputter etching, plasma etching, ion etching, or by a wet chemical treatment. Successive UBM layers may be vacuum deposited by evaporation or sputtering, or be chemically plated. UBM deposition processes generally require wafers of IC die, rather than individual die. The wide and growing array of UBM compositions (e.g. Cr:Cr-Cu:Cu, Ti:Ni-V, Ti:Cu, Ti:W: Au, Ni: Au) results in part from the desired bump material and characteristics, in part from the intended end use application, and in part from the experience and the invested capital base of the manufacturer. The required metallurgies are part art, part science, and part accumulated experience. About 75% of UBM currently produced consists of multi-metal layers evaporated or sputtered in a vacuum system. A typical process sequence would be:

- 1. Sputter etches the native oxide to remove oxide and expose fresh aluminum surface.

- 2. Deposit 100 nm Ti / Cr / Al as the adhesion layer.

- 3. Deposit 80 nm Cr: Cu as the diffusion barrier layer.

- 4. Deposit 300 nm Cu / Ni: V as the solder-wettable layer.

- 5. Deposit 50 nm Au as the oxidation barrier layer (optional).

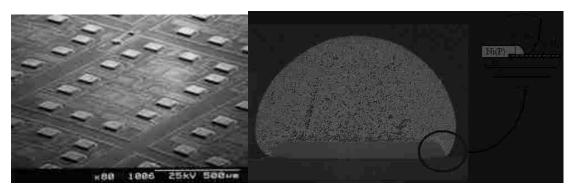

Fig. 4: Wafer with UBM

Fig. 5: Solder bump with UBM covering passivation

Electroless nickel UBM is unique in being a wet-chemical process that requires neither vacuum processing nor masking. Fig. 4 shows a wafer with electroless nickel UBM on the bond pads. The aluminum oxide is chemically etched, and replaced with zinc seed crystals. Nickel is electrolessly plated over the zinc as a barrier layer and solderable layer, and immersion gold is plated over the nickel as an oxidation barrier. The bump normally entirely covers the UBM, concealing it from view. The size of the UBM controls the spread, and therefore affects the resulting height, of a solder bump. Fig. 5 is a cross-section of a solder bump showing the underlying electroless nickel-gold UBM overlapping the die passivation ( $Si_3N_4$ ).

The robustness of a particular UBM depends on its composition, deposition process, and the skills of the manufacturer. Low stress, stable films are desired, and the deposition process governs the initial tensile or compressive stresses within the layers. However, crystalline changes and grain growth within in the metals can change the characteristics of the film throughout its lifetime. For example, the aluminum, nickel, and copper constituents can undergo substantial re-crystallization at temperatures below 150<sup>o</sup>C, changing the structure and stresses. Higher temperatures during reflow or subsequent

processing can cause dissolution of UBM materials. There is no perfectly optimal UBM, and practical UBM formulations require tradeoffs between competing constraints. For example, high temperature or high power applications would benefit from a high copper content, but copper dissolves readily and has a high re-crystallization rate. Electroless nickel UBM is a relatively low cost wet chemical process, but electroless nickel has almost ten times re-crystallization rate of sputtered nickel. The entire UBM/ bump system must reflect a balancing of capabilities and costs. A growing number of suppliers can provide UBM, bumping, or technology transfer and licensing of those skills. While most flip chip users need not and probably should not start out by depositing their own UBM; they should be aware of the tradeoffs to be evaluated in seeking a source to provide UBM. They should also be aware that the related metallurgy depends heavily on experience, and that producing good, reproducible, stable UBM requires more than just a chemistry set and a cookbook.

## 1.4.2 Making bumps

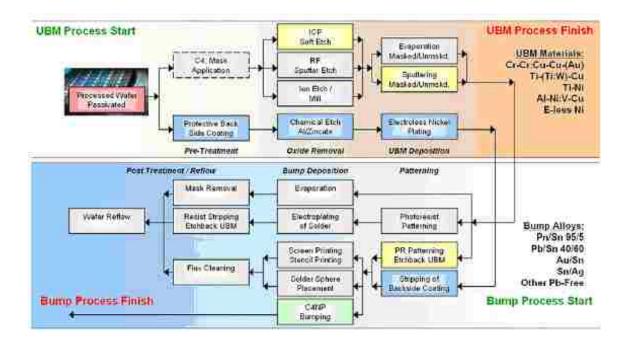

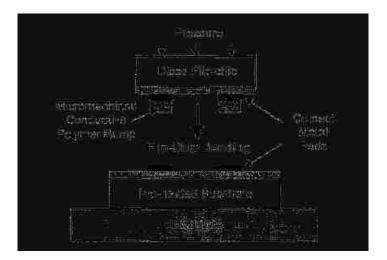

Solder bumps may be formed or placed on the UBM in many ways, including evaporation, electroplating, printing, jetting, stud bumping, and direct placement. The results of these methods may differ in bump size and spacing (pitch), solder components and composition, manufacturing time, cost, equipment required, assembly temperature, and UBM. The bump serves several functions in the flip chip assembly. Electrically, the bump provides the conductive path from chip to substrate. It also offers a thermally conductive path to carry heat from the chip to the substrate. In addition, the bump gives part of the mechanical mounting of the die to the substrate. Finally, it endows with a spacer, preventing electrical contact between the chip and substrate conductors, and acting as a short lead to relieve mechanical strain between board and substrate. A process chart for the formation of UBM and bump is shown in Fig. 6.

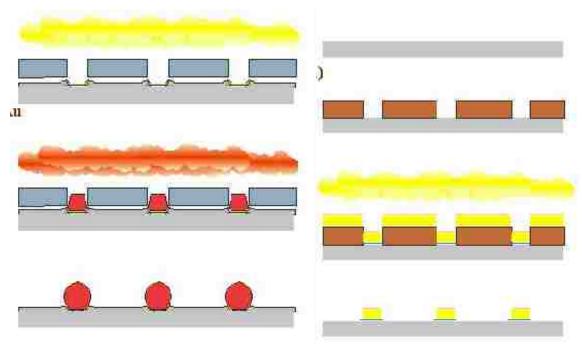

Fig. 6: A process chart for UBM and bump formation

### 1.4.2.1 Evaporated UBM / Evaporated solder

The pioneering IBM controlled collapse chip connection (C4) process was based on evaporation of the UBM and the solder onto the cleaned wafer pads. A metal mask aligned with and mechanically clamped to the wafer at a controlled spacing that defines evaporated deposits. The UBM evaporation is followed by evaporation of high lead solder to form the bumps. Low lead eutectic solder cannot be evaporated because of the difference in vapor pressures of lead and tin. Bump size and shape is determined by the mask openings and spacing. The evaporated solder (Fig. 7, 8) is reflowed to form a spherical solder bump. The evaporated bump allows good control of the alloy and uniform bump heights. The process is limited to high lead solders with binary (twocomponent) alloys. It cannot be easily scaled up to larger wafers, and has a limited throughput, high capital equipment costs and high licensing fees.

### 1.4.2.2 Sputtered UBM / Electroplated solder

Electroplating of solder (Fig. 9) was developed as a less costly and more flexible method than evaporation. The UBM is sputtered or evaporated over the entire surface of the wafer, providing a good conduction path for the electroplating currents. Bumping begins with photopatterning and plating a copper minibump on the bump sites. This thick copper allows the use of high tin eutectic solders without consuming the thin copper UBM layer. A second photopatterning and plating of the solder alloy over the minibump forms the solder bump. The photoresist is then removed from the wafer and the bump is reflowed to form a sphere. Electroplated bumping processes generally are less costly than evaporated bumping. Plating can allow closer bump spacing (up to 50 microns) than other methods of bump formation. It is popular for high bump count (>3,000) chips because of its small feature size and precision. However, plating bath solutions and current densities must be carefully controlled to avoid variations in alloy composition and bump height across the wafer.

### 1.4.2.3 Sputtered UBM / Printed solder

This method was developed in combination of thin film UBM with printed solder bumps by Delco and others to overcome some of the limitations of evaporated and electroplated bumps. Typically, the UBM consists of sputtered aluminum as the adhesion layer, nickel as a solder-wettable barrier layer, and copper as wetting layer. These layers except over the bond pad opening are removed by Photopatterning and etching.

Fig.7: Evaporation through mask

Fig. 8: Evaporation with photoresist

Fig. 9: Electroplated bump

Fig. 10: Screen printing

Fig. 11: Electroless plating

Fig. 12: Stud bumping

Solder is deposited by printing solder (Fig. 10) paste onto the UBM by stencil or other openings and reflowing the solder paste to form a spherical solder bump. Solder paste gives good control of the bump composition, and allows a variety of alloys to be used, including eutectic, lead-free, non-binary, and low alpha particle solders. The resulting process is less costly than evaporated processes, and comparable in cost to electroplating. The UBM adheres well to the bond pad and passivation, protecting the aluminum pad. Printed solder bumps cannot achieve the close spacing of plated bumps, with current production typically limited to 150 micron or greater spacing. Processing of larger (300 mm) wafers will require more costly sputtering equipment.

## 1.4.2.4 Electroless UBM / Printed solder

Electroless plated UBM promises to be the lowest cost approach to solder bumping (Fig. 11), because it eliminates thin film and masking steps and permits batch processing.

The UBM is formed by selective chemical plating, in a wet chemical, maskless process. A protective layer of resist first covers the wafer backside. An alkaline zincate solution removes the bond pad aluminum oxide layer and etches the surface. An electroless plated nickel layer forms the barrier and wettable layer. It is protected from oxidation by an immersion gold layer. The electroless nickel may also be plated higher to form a bump for adhesive or other non-solder flip chip assembly. Electroless Ni-Au UBM requires that all exposed metal other than the pads be passivated or covered with resist. The plating baths must be carefully controlled and kept free of contaminants to insure uniform plating. Solder bump deposition is by stencil printing of solder paste (Fig. 10). The solder bump is reflowed and flux residues are removed. The cost advantages of the electroless UBM solder bump process result from eliminating the masking and metal sputtering required by other methods, and allowing parallel batch processing of multiple wafers, which increases throughput and reduces costs. The solder dispensing process, not the UBM process, limits pitch.

### 1.4.3 Other solder bumping methods

Less common methods of solder bumping include solder bump bonding with solder wire, solder jetting with molten solder, and solder ball placement directly onto the UBM. Solder bump bonding (SBB) uses solder wire in a modified wire bonder to place a ball of solder directly onto the bond pad. The scrubbing action of the wire bonder causes the solder ball to bond to the bond pad. The solder wire is broken off above the bump, leaving the bump on the pad, where it can be reflowed. SBB is a serial process, producing bumps one by one at rates up to about 8 per second. It has advantages in allowing closer spacing than printed bumps. Solder jetting places solder bumps on Ni-Au UBM by controlling a stream of droplets of molten solder. Demand mode jetting systems use piezoelectric or resistive heating to form droplets in much the same manner as an ink-jet printer. Mechanical positioning directs the droplet placement. Continuous mode jetting systems use a continuous stream of solder droplets with electrostatic deflection of the charged droplets to control placement. Solder ball placement bumping depends on directly placing micro-spheres of solder on the UBM, similar to methods well developed for ball-grid array (BGA) and chip scale packages (CSP).

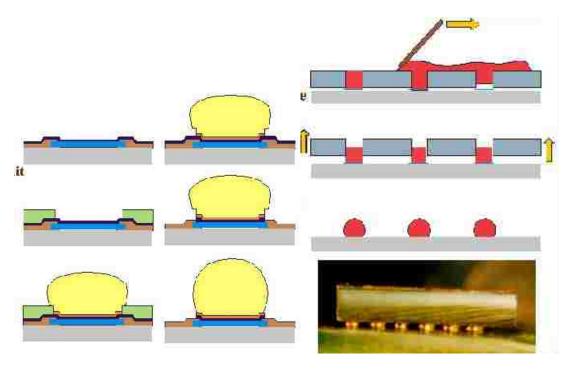

#### 1.4.3.1 Stud bump flip chip

Since stud bumping (Fig. 12) can be done on a wire bonder, it does not require wafers UBM. Single, off-the-shelf die can be bumped and flipped without pre-processing. This makes stud bump flip chip fast, efficient, and flexible for product development, prototyping and low to medium volume production. Because stud bumping is a serial process, the bumping time required increases with the number of bumps. However, high-speed equipment now can place as many as 12 bumps per second. Stud bump assemblies demand more precise die placement equipment and are less tolerant of placement errors than self-aligning solder assemblies.

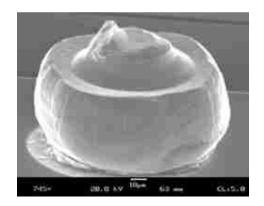

Gold stud bumping process creates conductive gold bumps on the die bond pads, and connects the die to the circuit board or substrate with adhesive or ultrasonic assembly. Stud bumping requires no under-bump metallization (UBM), and thus does not require wafer processing; individual die can be stud bumped as easily as they can be wire bonded. Gold stud bumps are placed on the die bond pads through a modification of the ball bonding process used in conventional wire bonding. In ball bonding, the tip of the gold bond wire is melted to form a sphere. The wire-bonding tool presses this sphere against the aluminum bond pad, applying mechanical force, heat, and ultrasonic energy to create a metallic connection. The wire bonding tool next extends the gold wire to the connection pad on the board, substrate, or lead frame, and makes a stitch bond to that pad, finishing by breaking off the bond wire to begin another cycle. For gold stud bumping, the first ball bond is made as described, but the wire is then broken close above the ball. The resulting gold ball, or stud bump remaining on the bond pad provides a permanent, reliable connection through the aluminum oxide to the underlying metal. The pull-off gold bumps were realized using a Panasonic wire-bonding machine with 1 mil (25  $\mu$ m) gold wire. This resulted in approximately spherical bump of 75 and 50  $\mu$ m in diameter and height respectively. After placing the stud bumps on a chip, they may be flattened (or coined) by mechanical pressure to provide a flatter top surface and more uniform bump heights, while pressing any remaining wire tail into the ball. Immediately after forming, a tool may coin each bump or all bumps on the die may be simultaneously coined by pressure against a flat surface in a separate operation following bumping.

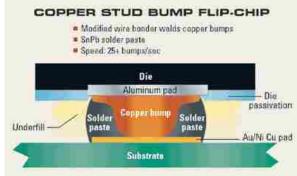

Fig. 13: A copper stud bump

Fig. 14: Flip chip assembly of copper bumped wafers

Gold stud bump can easily achieve pitches of less than 100 microns and be placed on pads of less than 75 microns. A die may be attached by adhesives, or by ultrasonic assembly without adhesive, depending on the die size and the application temperature requirements. Assemblies with gold-to-gold connections may not require undefilling.

Copper stud bumps provide a base for solder-adhesion without requiring UBM or electroless nickel/gold bumps, simplifying the process because they do not require additional wafer fabrication or plating operations. Copper stud bumps are formed with a modified automatic wire bonder at high speeds. Fig. 13 shows a copper stud bump, and Fig. 14 illustrates the assembled structure. The formation of stud bumps is a variation of the wire bonding process. The wire bonder forms a ball on the tip of a wire protruding from the capillary which then descends to the work surface and bonds the ball. Instead of moving on to form a wire loop, as in a typical wire bond, the capillary rises and terminates the wire above the ball before forming a new ball and repeating the process. In the case of the copper stud bump, additional motions occur during the wire termination to produce a flat-shaped bump, preferable for flip-chip. Once the solder is screened on the stud, the chip is placed on the pre-fluxed site on the substrate and reflowed. The capillary underfill is dispensed and cured after the cleaning of the solder residue. The stud bump can alternatively be assembled using no flow underfill (NFU). NFU enables a single reflow that simultaneously attaches the bump to the substrate and cures the underfill. Copper stud bumps typically have shear strength of  $\sim 110$  MPa, comparable with that of the aluminum bond pad. Even though the copper bump is a high-strength interconnection, the solder (tensile strength, 37 MPa; creep strength, ~3 MPa) remains the weak link mechanically. Underfill bonds to both the chip and substrate, mechanically strengthening

the integrity of the joint for improved fatigue strength during thermal cycling. However, thermal-cycle failures have been observed which were attributed to problems at the copper bump/ aluminum bond pad interface.

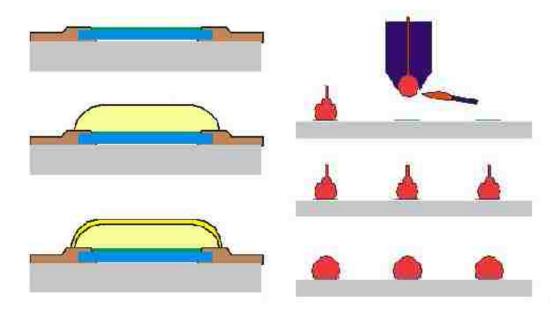

#### 1.5 Joining to antenna/ substrate (assembly)

Bumps are bonded to antenna mostly by adhesives; heating also used in combination. Some methods employ heat without adhesives.

#### 1.5.1 Adhesive joining

Some methods join UBM with antenna directly with adhesives. But majority of the joints are made with bumps joined to antenna with anisotropic conductive film (ACF) or paste (ACP). For direct adhesive bonding, isotropic conductive adhesive (ICA) is dispensed by stencil printing onto the substrate bond pads, or the bumped die may be dipped into a thin layer of adhesive, coating only the bumps with adhesive. Stenciled isotropic adhesive assembly provides a larger quantity of adhesive than dipped assembly, making a mechanically stronger bond. The additional adhesive compensates to some degree for bump height variations. A panelized array of substrates may be simultaneously stenciled in one operation, speeding up assembly. The stenciled adhesive can be inspected or measured before die mount to insure uniformity. However, stenciling requires a high-precision stencil printer and stencils. After the isotropic conductive adhesive is heat cured, a non-conducting underfill adhesive is applied to completely fill the under-chip space. Dipping requires a thin, precisely controlled layer of adhesive and co-planarity of the die and adhesive during the dipping process. Since dipping places adhesive only on the bump surface, the minimum bump spacing is smaller than for stenciling, to pad pitches of 60 microns or less (Riley, 2000). Dipping does not require

additional equipment as stenciling does, since the die mount aligner bonder can be used for dipping. However, dipping requires careful control of the adhesive layer thickness, and dipping is a serial process, lengthening throughput time. A non-conductive adhesive is dispensed or stenciled at the die location on the substrate. The bumped die is pressed against the substrate pads with enough force give compressive dispersion of the adhesive, allowing no adhesive to remain between the stud bump and substrate pad mating surfaces. This pressure is maintained while the assembly temperature is elevated for sufficient time to at least partially cure the adhesive. The chip is mechanically bonded to the substrate by the cured adhesive, with metal-to-metal contact between the bumps and substrate pads. No separate underfill adhesive is required. Non-conductive adhesive has advantages for assembly onto flexible substrates, since the adhesive is cured while in the aligner-bonder, keeping the die fixed in location thereafter. Dispensing the adhesive properly and repeatability requires automated equipment, and the aligner-bonder throughput is determined by curing time, including ramping up and down from the curing temperature.

Fig. 15: Joining of an unbumped chip with adhesive

Underfill adds mechanical strength to the assembly and protects the connections from environmental hazards. However, its most important purpose is to compensate for any thermal expansion difference between the chip and the substrate. Underfill mechanically locks together chip and substrate so that difference in thermal expansion does not break or damage the electrical connection of the bumps. Underfill adhesive may be dispensed along one or more edges of the die, being drawn into the space under the die through capillary action. Heat-curing the underfill adhesive completes the assembly process.

Anisotropic conductive adhesives (film and paste- ACA: ACF/ACP)) consist of an epoxy adhesive with dispersed conductive particles. They are used as electrical-mechanical interconnecting materials for flip-chip to flexible substrates and flip chip to glass substrates. Underfill is also used with ACA. Contact resistance and adhesion strength are two important features of anisotropic conductive adhesive joints. Contact resistance is affected by the curing degree of the adhesive, the bump characteristics, the reflow process and the environmental application conditions. Adhesion strength is affected by bonding temperature, bonding pressure, bubbles in the joints and particle characteristics (Wang et al., 2008).

#### 1.5.2 Thermosonic joining

Prior to the thermosonic bonding, co-planarity of the die and the substrate is carefully aligned to achieve good bonding (Cheah et al., 2001). The bonding procedure begins with the substrate sitting on a heated stage. A vacuum holds the substrate in place. The temperature of the substrate is maintained at 150 °C. The chip is held by the bonding tool with vacuum and is brought into contact with the substrate. When the bonding force is reached a certain level, ultrasonic vibration is applied through the ultrasonic tool for a

predetermined length of time to complete the process. This method is mostly suitable for gold bumps.

## 1.5.3 Joining with heat

For low melting point bumps, chips are placed in flux or solder paste on the substrate and the assembly is reflowed. The joint is formed through the melting of bump, and the paste, where applicable. The high melting point bumps are joined to the substrate by melting either the solder paste or a low melting alloy on the bumps or on the conductors on the substrate (Boustedt, 1998). Joining with heat is simple, but has the inherent danger of chip damage due to shortening of terminals or overheating.

## 1.6 Objectives

Objectives of the present research are:

- (a) to identify the problems in present flip chip joints,

- (b) to suggest an alternate technique for solving existing problems,

- (c) to study the feasibility of the proposed method, and

- (d) to compare the strength of the new method with existing ones.

#### CHAPTER 2

### LITERATURE REVIEW

Researchers develop new flip chip joining methods/ patterns every year; each has a differing set of strengths and limitations, which suit them for differing applications. This chapter discusses about the findings of some earlier investigators.

### 2.1 Research related to the formation of UBM and bump

Mangold and Lance (1998) developed a process for fabricating a solder bump having an improved geometry that included the steps of evaporatively depositing a first metallization system to form a post having a predetermined volume onto an integrated circuit having a passivation layer defining a die pad window, wherein the length of the post was greater than the width of the post, and wherein the length of the post extended beyond the die pad window over the passivation layer, and evaporatively depositing a second metallization system onto the post to form a cap also having a volume, wherein the first metallization system forming the post and the second metallization system forming the cap, when reflowed, formed an eutectic solder bump.

Yap and Lawyer (2004) developed solder bump structure that included a multi layer UBM having a major upper surface with solder wettable cap-layer for containing a solder bump, the multi layer UBM projecting from the substrate with an exposed sidewall; a thin of metal selected from a group consisting of titanium, chrome, titaniumnickel-titanium composite, a titanium-nickel-chrome composite, a titanium-platinumtitanium alloy, and a titanium-nickel-oxidized silicon composite deposited over or under the multi layer UBM and covering the exposed sidewall of the multi layer UBM. The completed solder bump structure was formed by subsequently heating the substrate to melt the solder and wet it back. Another portion of the solder bump structure was initially formed on a separate substrate that was subsequently bonded to the first substrate by means of solder, preferably by using heat.

Yoon et al. (2008) investigated the formation of Au–20 wt. % Sn flip chip solder bumps using sequential electroplating method with Sn and Au. They obtained eutectic Au–20Sn solder bumps with a diameter of 100  $\mu$ m on the patterned silicon wafer. After reflowing and aging at 150 <sup>o</sup>C for up to 1000 h, they investigated the interfacial reaction between the Au–20Sn solder and Ni under bump metallization (UBM). The Au–Ni–Sn, ternary, intermetallic compound (IMC) layer was formed, and the resettlement of  $\delta$ -phase was confirmed during aging. The shear force was also measured to evaluate the effect of the interfacial reactions on the mechanical reliability as a function of aging time. The shear force was stable and the fracture occurred on the Ti/Cu metallization layer independent of the aging time. It was claimed that the results from their study confirmed the mechanical robustness of the Au–20Sn/Ni flip chip solder joint.

Kloeser et al. (2000) developed low cost bumping method by stencil printing. Their experimental work on fine pitch printing showed that, the printing down to 200  $\mu$ m pitch could be performed without quality and yields reduction, with optimized stencil design and solder pastes. This technology was seen suited for high volume applications, and experiences with solder paste printing down to 150  $\mu$ m pitch showed that the printable pitch could be decreased down to pad configurations for wire bonding technology.

Chen et al. (2004) proposed a flip chip bumping method for fabrication of solder bumps on a semiconductor wafer for flip chip application that was intended to a plurality of chip regions which were delimited from each other by a predefined cutting line each of which was formed with a plurality of aluminum or copper based bond pads, and was characterized in the provision of a plating bus over and along the cutting line and connected to each bond pad. By means of this plating bus the required UBM fabrication and solder-bump fabrication could be both carried out through plating. They claimed that it would reduce the cost; since plating process was considerably lower in cost than sputtering or etching process.

Nam et al. (2007) fabricated a flip chip solder bump using a thin dewetting mold and the ultrasonic filling method. The process consisted of filling the cavities of a stainless steel mold with lead-free solder using ultrasonic vibration, and transferring the solder bump pattern of the mold to a substrate using reflow soldering. Pressures, induced by ultrasonic and mold vibration, were predicted analytically, and the ultrasonic pressure was larger than the pressure induced by the surface tension, which trapped the vapor at the mold cavity. Contact and non-contact modes were used to fill the through-hole and blind-hole molds, and the solder bump patterns of the mold were transferred to the Cu pads of a polyimide film through reflow soldering.

Schreiber and Le (1998) invented an integral copper column with a solder bump flip chip. They formed long bumps by connecting the contact pad on chip and the raised feature of the antenna to form an integral copper column. But it required special mandrel to shape the antenna into raised feature.

Chen and Xiao (2007) invented a series of processes and methods to manufacture solder bumps on the wafer, which shrunk the space and reduce the cost of manufacturing. A design method and relevant manufacturing processes were introduced to form an organic material or metal layer, called a Bump-Reflow Control Layer. The pad patterns

23

could be defined by this method. A mechanical part was designed with a hermetic cover to improve the photoresist process. A series of photolithography process including the designing of related mask was introduced to achieve high quality and thick photoresist.

Boustedt (1998) found that, when soldering flip chips, the surface tension of the molten solder pulled the chip to its correct position, i.e., the chip self-aligned. This meant that the mounting did not had to be extremely precise. The solder could only wet to the metal surfaces on the substrate, and as long as the chip and bump were in contact with the correct pad on the surface, the chip self-aligned. Trials with silicon chips showed that the chip could be dislocated as much as 50% of the pad diameter and still resulted in good alignment.

Jiang et al. (2004) developed indium bump fabrication based on both evaporation and electroplating method. Their indium evaporation method was based on a unique positive lithography process and achieved high resolutions whereas electroplating method produced acceptably uniform indium bumps suitable for infrared (IR) focal plane arrays (FPAs) applications. The electroplating method could also be extended to produce high aspect ratio indium bumps or even variable height and diameter indium bumps by a new "multi-stack" technique. The fabrication of multi-color IR FPAs could potentially benefit greatly from this "multi-stack" method. They also proposed an indium bump transfer technique that simplified bump fabrication at a reduced cost. However, Olver (2004) pointed that these indium bumps could damage the devices due to the compression required for assembly. Moreover, they could not be reworked easily.

## 2.2 Studies cognate to stud bumping

Zhong (2001a) evaluated the stud bump bonding (SBB) process for a flip chip in package application. An SBB packaging process, having a reduced number of process steps compared with the typical SBB process, was proposed. The two separate steps of curing of conductive adhesive and underfill epoxy, which for the application targeted in this study needed a total of four hours for curing plus further time for cooling, were not required. It was claimed that the proposed process resulted in a reduced packaging time.

Chaudhuri et al. (2006) mentioned, copper stud bumping using a high-speed automatic wire bonder with the addition of a kit to enable copper ball formation in a protective atmosphere, had the potential to significantly lower the cost of ownership for the flip-chip process. For low- to medium-I/O devices such as or double-data-rate three synchronous dynamic random access memory (DDR3 SDRAM), automotive applications, and sensors, copper stud bumping was significantly less expensive than conventional sputter/print solder paste or electroless plating methods. Incorporating wire bond technology, as a part of the flip-chip bumping process was attractive because existing facilities and infrastructures could be used without the high capital costs required by more expensive sputter/plating facilities.

Osborne et al. (2005) reviewed stud bumping technology and its application along with various bumping material options. It was based on wire bonding technology, using Au and Cu wires. They claimed that cost effectiveness of stud bumping could provide an alternate solution for slim form factor packaging (stacked die, image sensors and LCDs) and for other packaging applications requiring high reliability with high current carrying capability and high use temperature. They found that wire type selection (chemistry, elongation) could affect bump shape and strength. More ductile wire increased tail height variation and decreased coplanarity. Commercially available flip chip attachment was considered suitable for assembly with either gold or copper stud bumps.

#### 2.3 Investigations linked to assembly process

Zakel et al (2003) found that the majority of contemporary flip chip bonders were derived from modified surface mount devices (SMD) – equipment respectively from modified die bonder equipment. The majority of the flip chip assembly processes were based on soldering, however adhesive attach was having a stronger and more important impact in flip chip technology. Adhesive attach was especially interesting in applications on flexible circuits, like LCD drivers and smart cards. The methods of flip attach were all using thermal energy by either reflow convection ovens or a thermal based on heated tools (thermode). They showed a new approach of using laser for a selective attach of Flip chip and surface mount technology (SMT) – type of components. The advantage of laser instead of direct thermal heating was given by extreme high selectivity and by using a localized heat with an extremely good time control in the millisecond range. This minimized the thermal stress induced in the package, and on the substrate minimized allowing implementation of new substrates and new IC's, which were thermally more sensitive. Their paper showed applications of laser flip chip Attach for soldering and for adhesive curing of underfill material, ACF and NCF or NCP - materials. The laser soldering allowed processing of a high variety of solder alloys including eutectic tin lead, lead free SnAgCu and SnAg together with AuSn.

Jung et al. (1995) realized flip chip interconnections to organic substrates using different techniques: soldering using mechanical solder ball bumps and adhesive bonding

26

with isotropic conductive adhesive. Both approaches used an electrolessly deposited nickel gold under bump metallization. While soldering with PbSn solder, restrictions came from the necessary temperature for the reflow process and the requirement of flux. Using alloys with lower melting temperature resulted in higher material costs. Adhesive bonding offered lower process temperatures and was inherently flux less. However, no self-alignment effect was present; precise bonding equipment was needed. Except for the bonding with nonconductive adhesive films, the measured contact resistances were larger than for the soldered ones. Concerns about the environmental impact of lead in the solder did not affect the adhesive. By adjusting the gap distance between chip and substrate, they expected to achieve as reliable interconnections as with soldered ones, because mainly the properties of the underfill determine the performance when subjected to thermal cycling. Failure analysis of the under filled assemblies showed that a fracture along the interface between chip and undefiller occurred. Thus the bumps were separated from the chip, resulting in a complete loss of conductivity. While the under filled assemblies using the mechanical bumps withstood more than 1000 thermal cycles (chip size 7.5 x7.5 mm<sup>2</sup>, test conditions  $-55^{\circ}C/+125^{\circ}C$ ,) without significant increase in contact resistance; the under filled devices with electroplated bumps showed first defects after 750 thermal whereas non-under filled chips showed failure after 10 thermal cycles

Cheah et al. (2001) developed a thermosonic flip chip bonding process using conventional equipment. These were: (i) Gold wire bonder to form pull-off bump on silicon die with gold wire bondable aluminum pads, (ii) Thick or thin film ceramic substrate, (iii) Conventional flip-chip bonder with optional ultrasonic tool to provide alignment, heated stage, thermo-compression loading, ultrasonic power and controllable duration to perform the flip-chip thermosonic flip-chip assembly, and (iv) Conventional dispensing system for underfilling dispensing. The thermosonic flip-chip bonding process was proven to be useful for die with dimension up to 5 x 5 mm and up to 68 input-outputs (I/Os). The following steps were taken to verify the reliability of the process: (i) Die shear test was performed to meet the specified criteria of military standard (MIL-STD-883) with 5 g/bump. (ii) Cross-section of the die to ascertain gold-to-gold diffusion interface. (iii) Thermal cycle and pressure cooker tests to verify the bonding.

Ishii and Aoyama (2004) directly bonded bare flip chip to the substrate. Successful connections were achieved by using a 0.05Au-0.95Sn solder bump and a hydrogenplasma reflow technique. Because the method eliminated the need for any process on the chip wafer, it was very useful in fabricating flip-chip connections for low-cost packaging. The pre-reflow bonded assembly was inserted into the hydrogen-plasma chamber and exposed to the plasma for 2 min at 220°C. After the plasma treatment, the connection between the chip and substrate was examined. Failure observed in SEM view of bump cross section. SiO<sub>2</sub> separation film formed on the Au-Sn interface.

Tuetsu et al. (2005) found that short-pulsed laser generated localized heat and induced minimal thermal stress on the area beyond the joined surfaces, on the chip and substrate, and the interconnections that join them. The exact amount of thermal energy required could be provided in one short-duration laser pulse, in the areas of interest. It was not necessary to heat an entire substrate up to reflow temperatures to melt and reflow an interconnection of a few microns. Additionally, that same ability could be applied to the rapid thermal curing of materials, such as underfill, commonly associated with flip chip assembly. However, Kordas et al. (2006) mentioned difficulties arouse with the laser

soldering process when flip-chips or other tile-type components were mounted, since the joints formed were between the component and the PCB. In such cases, the laser beam had to be applied from the side (parallel to the PCB) or either through the component or through the PCB (both perpendicular to the PCB). Due to simple optical reasons, the first option (illumination from the side) enabled soldering along the perimeter of the component. Considering a numerical aperture of 0.1 mm for the focusing optics (which was already a rather small value) and a typical flip chip and PCB distance of 100  $\mu$ m, maximum soldering distance from the side of the chip was ~1 mm. Therefore, in the case of large chips/ arrays, the inner joints could not be realized. The second alternative for laser soldering—with a beam through the component— was dismissed due to scattering of the beam on the metal patterns of the chip and due to the high risk of a possible component failure caused by the high-intensity laser beam. Since the only feasibility criterion for illumination through the PCB is high transparency of PCB dielectrics at the wavelength of the laser beam, the third option appears to be the obvious one.

Jokinen and Ristolainen (2002) made flip chip interconnections on very flexible polyethylene naphthalate substrates using anisotropic conductive film. Two kinds of chips were used: chips of normal thickness and thin chips. The thin chips were very thin, only 50  $\mu$ m thick. Due to the thinness of the chips they were flexible and the entire joint was bendable. The reliability properties of the interconnections established with these two different kinds of chips were compared. In addition, the effect of bending of the chip and joint area on the joint reliability was studied. Furthermore, part of the substrates was dried before bonding and the effect of that on the joint performance was investigated. The pitch of the test vehicles was 250 lm and the chips had 25  $\mu$ m high gold bumps. For resistance analysis there were two four-point measuring positions in each test vehicle. For finding the optimal bonding conditions for the test vehicles, the bonding was done using two different bonding pressures, of which the better one was chosen for the final tests. Furthermore, the test vehicles were subjected to thermal cycling tests between -40 and +25 <sup>o</sup>C (half-an-hour cycle) and to a humidity test (85%/85 <sup>o</sup>C). Part of the test vehicles was bent during the tests. Finally, the structures of the joints were studied using scanning electron microscopy.

Rasul and Olson (2005) developed an unbumped flip chip on paper assembly technology using ACA that reduced processing steps by eliminating screen-printing for the wafer bumping. Combined with elimination of thermal curing, the process enabled high throughput and lower overall cost.

## 2.4 Findings connected to joint characterization

Nicewarner (1999) compared several flip-chip interconnection methods by measuring interconnect resistance before and after exposure to environments including preconditioning,  $85^{\circ}$ C/85% RH exposure,  $150^{\circ}$ C storage, and  $0\pm100^{\circ}$ C temperature cycling. It was seen that solder bumps over electroless nickel had lower bond pad resistance than electroplated solder over Cr/Cr-Cu/Cu UBM and the performance was as well or better when exposed to temperature cycling, high temperature storage, or humidity. Silver filled epoxy adhesive did not achieve consistent low resistance connections when assembled and failed to survive humidity exposure. Gold stud bumps with thermoplastic adhesive exhibited a significant increase in resistance over temperature due to a high thermal expansion coefficient. Gold stud bumps with thermoset adhesive had electrical and environmental test behavior similar to solder. Aluminum bond pads showed a small increase in resistance due to environmental exposure while electroless nickel-plated pads remained stable.

Wang et al. (2006) applied carbon nano tubes in integrated circuit packaging, as the bump interconnection for flip chip, due to their special electrical, mechanical and thermal properties, which might promote both the performance and reliability of the flip chip packaging. Moreover, carbon nano tubes could be formed according to a precisely predefined small-scale pattern, which made extremely high-density interconnection possible. Vertically aligned carbon nano tubes were grown on silicon in the form of square arrays of different sizes, heights and pitches. Attempts to use thermal compression and anisotropic conductive adhesive to bond chips carrying carbon nano tube bumps with ceramic substrates were also executed. Mechanical testing was performed afterward to determine the strength of the bonding interfaces. The strength of the bonding by thermal compression was very weak, in the range from 1.9 to 7.0 g/mm<sup>2</sup>. The bonding by anisotropic conductive adhesive was much stronger, indicating a possible approach to bond chips carrying carbon nano tube bumps.

Koo et al. (2008) investigated the effect of displacement rate and intermetallic compound growth on the shear properties of the electroplated Sn–37Pb (wt.%) flip-chip solder bumps with Cu UBM after multiple reflows. The compounds Cu6Sn5 and Cu3Sn were formed at the interface after one reflow, and their thick nesses increased with increasing reflow number up to 10. The shear properties peaked after four reflows, and then decreased with increasing reflow number. Increasing displacement rate increased the shear force, but decreased the displacement until fracture. The tendency toward the brittle

fracture characteristics was intensified with increasing displacement rate and reflows number.

Zhong (2001b) evaluated flip chip on flame retardant (FR-4) and ceramic substrates using gold bumps with ACF, ACP or NCA. Flip chips were assembled on test vehicles for temperature cycling and humidity tests. The reliability performance of the process was compared. It was seen that adhesives could give satisfactory reliability when bonding parameters were optimized.

Using laser ultrasonic system, Erdahl et al. (2008) measured the free vibration response of the chips attached to the printed circuit board. The algorithm of mode isolation (AMI) was applied to the vibration response data in order to extract the modal parameters of the chip. They estimated the first natural frequency to be about 101 kHz. They were able to identify the presence of open solder bumps between a flip chip and the circuit board. The most basic approach of monitoring the natural frequency and damping ratio was not definitive in detecting open solder joints because the natural frequencies of the chips with open solder joints were too similar to those for chips without open solder joints relative to experimental scatter. On the other hand, the first mode shape was seen to be significantly different between the reference and damaged chips, so that one could discern many of the damaged chips by comparing the first mode shape of each with the average reference shape. The variation in the shape of a higher frequency mode was also studied, revealing that this mode was not sensitive to damage relative to experimental scatter. The observation that a higher frequency mode was less sensitive to open joints than the first mode indicated that the stiffness of the solder joints became negligible relative to the stiffness of the chips at higher frequency.

Lau et al. (1996) determined the mechanical and vibration responses of 225-pin, 324pin and 396-pin plastic ball grid array (PBGA) solder joints. Bending and twisting experiments determined the effects of overload environmental stress factors on the mechanical responses of the solder joints. The effects of shipping and functional environmental stress factors on the vibration responses of the solder joints were determined by out-of-plane vibration experiments and a mathematical analysis. They found that natural frequencies were ranging from 95 Hz to 105 Hz and the average measured value of these four measurements is about 100 Hz. These values were very close to those predicted by the simple analytical model.

Zhou and Dasgupta (2006) studied flip chip joints for both Sn3.9Ag0.6Cu (SAC) and Sn37Pb (SnPb) assemblies, under vibration loading. The natural frequencies and mode shapes were extracted from the FEA modal analysis and compared with experimental results. The dominant modes from experiment and simulation were compared. The first fundamental natural frequency both from experiment and FEA was found to be 72 Hz. By matching the fundamental natural frequency from simulation, the boundary stiffness for the rotational spring was calibrated to be 9N-m/Rad. Using this rotational spring constant, the simulation results for the remaining mode shapes and natural frequencies were found to agree well with experiment results. The natural frequency of the second dominant mode is 411Hz from experiment and 415Hz from simulation. Simulation and experiment provide the same mode shape for these modes.

Basaran et al. (2002) presented a test program that was performed to study inelastic behavior of solder joints of ball grid array (BGA) packages. The test data showed that solder joints responded elastically at room temperature under either shock or sine

vibration loading. Inelastic deformation might be still accumulating, albeit very slowly. At elevated temperature, both shock and vibration induced significant inelastic shear deformation in solder joints, thus shortening the fatigue life of solder joints. The solder joints suffered more severe damage at lower vibration frequencies than at higher ones. At 100°C, the test data showed that dynamic loading with frequencies higher than 1,000 Hz had little effect on the solder inelastic response. They found that solders behaved elastically for higher frequencies and inelastically for lower frequencies. At lower frequencies the period of the loading was higher. The time-dependent inelastic deformations were directly related to the period of the load. When the load had a longer period, the material had more time to creep. Consequently for vibrations with small frequencies, creep dominated the response. It was concluded that contrary to popular belief, the solder alloy did not remain in the elastic region regardless of the frequency of loading and the acceleration level. With a low melting point (183°C) and high viscoplastic characteristics, an eutectic solder alloy showed creep behavior during dynamic loading processes, which could not be underestimated in solder joint fatigue life prediction.

Basaran and Chandaroy (1998) studied low and high cycle fatigue behavior of a solder joint between a leadless ceramic chip carrier and a printed wiring board. It was observed that damage experienced due to vibrations could be significant. When the material was in the elastic range, the higher frequency led to higher damage in each cycle. But when the solder behavior was inelastic, lower frequency vibrations caused higher damage in each cycle than in higher frequency loads. Vibrations could lead to

quick accumulation of fatigue damage. This was due to a high repetition of the vibration cycles in each thermal cycle.

Zhou et al (2009) examined interconnect durability of SAC305 electronic assemblies under harmonic and random vibration test loads and compared to that of Sn37Pb assemblies. Under constant-amplitude harmonic loading, a comparison was drawn between SAC305 and Sn37Pb assemblies when similar specimens were excited at their natural frequency. The natural frequency of the test printed wire board (PWB) was identified by measuring its dynamic response to "white noise" excitation, with an accelerometer located at the center of the PWB. The fast Fourier transform (FFT) of the measured accelerometer response indicated that the first natural frequency of the PWB was168 Hz. Isothermal vibration durability generally decreased as the temperature increases, for both Sn37Pb and SAC305 assemblies. Increasing the duration of pre-aging at a constant elevated temperature decreased the time to failure (TTF) for both Sn37Pb and SAC305 assemblies when they were exposed to vibration durability testing. The influence appeared to be more severe for Sn37Pb than for SAC305. There were at least two competing failure sites: one in the bulk of the solder material in the join, and another in the copper trace/pad on the PWB below the solder joint. The SAC305 assemblies were found to be generally less durable than the Sn37Pb assemblies at the load levels examined in this study, but there appeared to be crossover amplitude beyond which the SAC305 assemblies might be more durable.

Ratchev et al (2003) studied the reliability and failure modes of eutectic Sn-Ag-Cu solder joints and compared to eutectic Sn-Pb-Ag ones. There occurred two different failure modes: brittle fracture and fatigue. The results showed that with a Ni/Au surface

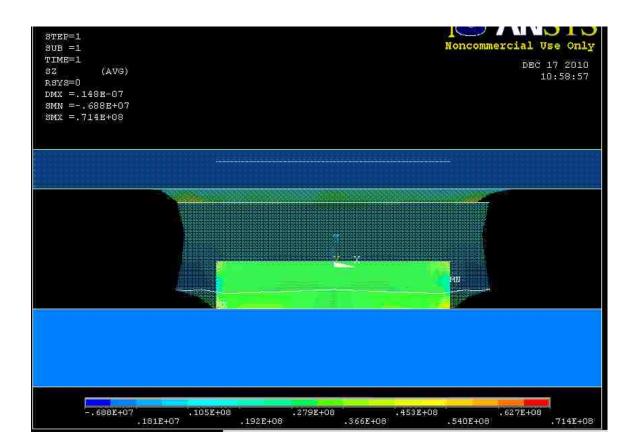

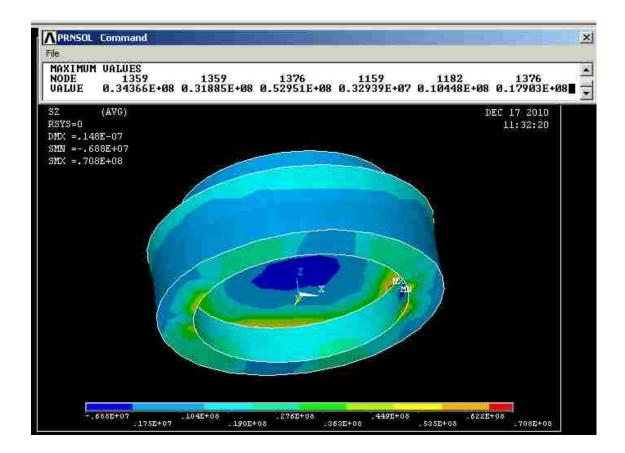

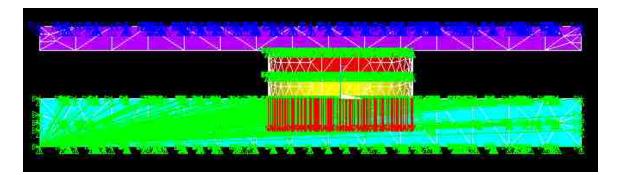

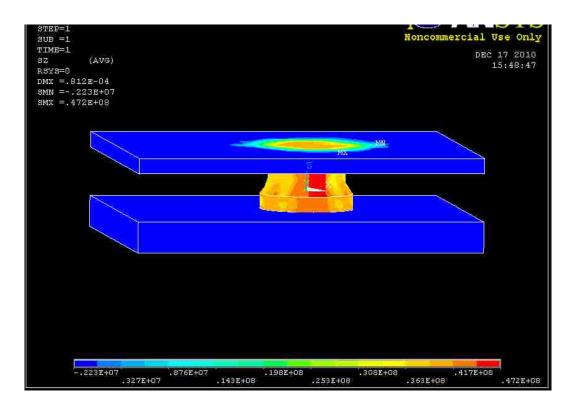

finish the reliability of Sn-Ag-Cu solder was much better than the one of Sn- Pb-Ag solder. First of all, when the joint was deformed at high strain, the chance of brittle fracture at the NiAu interface was significantly reduced when using Sn-Ag-Cu solder. The reason was a reduced formation of the brittle (AuNi)Sn<sub>4</sub> intermetallic at the UBM interface, responsible for the brittle fracture mode. Second, after deformation at low strain, both solders failed due to solder fatigue, but the Sn-Ag-Cu showed a better lifetime. This better reliability of the Sn-Ag-Cu solder was attributed to a new solder fatigue mechanism: the crack propagates through the bulk of the solder in a web-fashion way, linking the Au containing particles, formed in the volume. This was beneficial for the joint reliability as it hindered the crack propagation.