# University of Central Florida STARS

**Electronic Theses and Dissertations**

Doctoral Dissertation (Open Access)

# In-Memory Computing Using Formal Methods and Paths-Based Logic

2018

Alvaro Velasquez University of Central Florida

Find similar works at: https://stars.library.ucf.edu/etd

University of Central Florida Libraries http://library.ucf.edu

Part of the <u>Computer Sciences Commons</u>

### STARS Citation

Velasquez, Alvaro, "In-Memory Computing Using Formal Methods and Paths-Based Logic" (2018). *Electronic Theses and Dissertations*. 6222. https://stars.library.ucf.edu/etd/6222

https://stars.horary.uci.cua/cta/0222

This Doctoral Dissertation (Open Access) is brought to you for free and open access by STARS. It has been accepted for inclusion in Electronic Theses and Dissertations by an authorized administrator of STARS. For more information, please contact lee.dotson@ucf.edu.

## IN-MEMORY COMPUTING USING FORMAL METHODS AND PATHS-BASED LOGIC

by

ALVARO VELASQUEZ B.S. University of Central Florida, 2014 M.S. University of Central Florida, 2016

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in the Department of Computer Science in the College of Engineering and Computer Science at the University of Central Florida Orlando, Florida

Spring Term 2018

Major Professor: Sumit Kumar Jha

© 2018 Alvaro Velasquez

### ABSTRACT

The continued scaling of the CMOS device has been largely responsible for the increase in computational power and consequent technological progress over the last few decades. However, the end of Dennard scaling has interrupted this era of sustained exponential growth in computing performance. Indeed, we are quickly reaching an impasse in the form of limitations in the lithographic processes used to fabricate CMOS processes and, even more dire, we are beginning to face fundamental physical phenomena, such as quantum tunneling, that are pervasive at the nanometer scale. Such phenomena manifests itself in prohibitively high leakage currents and process variations, leading to inaccurate computations. As a result, there has been a surge of interest in computing architectures that can replace the traditional CMOS transistor-based methods. This thesis is a thorough investigation of how computations can be performed on one such architecture, called a crossbar. The methods proposed in this document apply to any crossbar consisting of two-terminal connective devices. First, we demonstrate how paths of electric current between two wires can be used as design primitives in a crossbar. We then leverage principles from the field of formal methods, in particular the area of bounded model checking, to automate the synthesis of crossbar designs for computing arithmetic operations. We demonstrate that our approach yields circuits that are state-of-the-art in terms of the number of operations required to perform a computation. Finally, we look at the benefits of using a 3D crossbar for computation; that is, a crossbar consisting of multiple layers of interconnects. A novel 3D crossbar computing paradigm is proposed for solving the Boolean matrix multiplication and transitive closure problems and we show how this paradigm can be utilized, with small modifications, in the XPoint crossbar memory architecture that was recently announced by Intel.

To my parents, without whose sacrifice this would not have been possible.

### ACKNOWLEDGMENTS

I would like to thank my advisor, Dr. Sumit Kumar Jha, for his continued support and encouragement. He was instrumental in providing me with the intellectual freedom and guidance necessary to succeed in this discipline. I would also like to extend my sincerest gratitude to my friend and mentor Dr. K. Subramani for enhancing my knowledge of combinatorial optimization and complexity theory, as well as for providing a respite from the toils of research.

My gratitudes are also with many researchers from the Air Force Research Laboratory. From the autonomous command and control systems branch (RISC), I would like to thank Dr. Robert Wright for hosting and involving me in his cutting-edge research on deep reinforcement learning and Dr. Nathaniel Gemelli and Dr. Jeffrey Hudack for advice and help in the interviewing process and the inner workings of the laboratory. From the trusted systems branch (RITA), I am grateful to Steven Drager for hosting me multiple times and for being constructively critical of my research agenda and Dr. Matthew Anderson for his help and generosity.

Credit is also due to Dr. Nathaniel Cady and Zahiruddin Alamgir for their contributions in making some of the theories in this thesis a physical reality. Finally, I would like to thank Dr. Gary Leavens and Dr. Annie Wu for taking time out of their busy schedules to join my defense committee.

This research would not have been possible without the financial support of the National Science Foundation Graduate Research Fellowship Program (GRFP) and award #1438989 titled "XPS: EXPL: FP: Collaborative Research: Formal methods based algorithmic synthesis of more-than-Moore nano-crossbars for extreme-scale computing", the Air Force Research Laboratory, and my own Alma Mater, the University of Central Florida. The views expressed herein are my own and do not necessarily reflect the views of these great institutions.

# TABLE OF CONTENTS

| LIST OF FIGURES                       | ix  |

|---------------------------------------|-----|

| LIST OF TABLES                        | /ii |

| CHAPTER 1: INTRODUCTION               | 1   |

| CHAPTER 2: BACKGROUND                 | 6   |

| Memristors                            | 6   |

| Crossbar Computing                    | 8   |

| Sneak Paths                           | 10  |

| CHAPTER 3: LITERATURE REVIEW          | 14  |

| Logic Synthesis Methods               | 14  |

| Formula-Dependent Memristor Placement | 16  |

| Rectifying-Memristor Crossbars        | 17  |

| Networks of Interconnected Crossbars  | 19  |

| CHAPTER 4: PATHS-BASED LOGIC          | 21  |

| Irreducible Paths in Crossbars        | 22  |

| Universality of Paths-Based Logic                 | 29 |

|---------------------------------------------------|----|

| CHAPTER 5: DESIGN AUTOMATION                      | 35 |

| Bounded Model Checking                            | 39 |

| Experimental Results                              | 43 |

| Fault Tolerance                                   | 47 |

| Crossbar Networks                                 | 49 |

| CHAPTER 6: HETEROGENEOUS CROSSBARS                | 52 |

| Limitations of Paths-Based Logic                  | 52 |

| Heterogeneous Crossbars                           | 54 |

| Design Automation                                 | 58 |

| Fault Tolerance                                   | 62 |

| Experimental Results                              | 64 |

| Concluding Remarks                                | 65 |

| CHAPTER 7: DESIGN AUTOMATION OF VOLTAGE SEQUENCES | 67 |

| Methodology                                       | 69 |

| Results                                           | 73 |

| Illustrative Execution of 1-bit Full Adder                   | 74 |

|--------------------------------------------------------------|----|

| Conclusion and Future Work                                   | 76 |

| CHAPTER 8: BOOLEAN MATRIX MULTIPLICATION WITH 3D CROSSBARS 7 | 78 |

| Methodology                                                  | 31 |

| Experimental Results                                         | 36 |

| Concluding Remarks                                           | 38 |

| CHAPTER 9: TRANSITIVE CLOSURE WITHIN 2-LAYERED MEMORY        | 39 |

| Methodology                                                  | €  |

| All-Pairs Shortest Paths                                     | )1 |

| Complexity                                                   | )3 |

| Universal Computation                                        | )3 |

| Experimental Results                                         | )8 |

| Energy and Latency Considerations                            | )9 |

| Concluding Remarks                                           | 11 |

| CHAPTER 10: CONCLUSION                                       | 13 |

| LIST OF REFERENCES                                           | 15 |

### LIST OF FIGURES

- 3.4 Red dashed lines denote the flow of current and  $\mathbb{M}_*(\phi^{(i)})$  represents the crossbar that computes the  $i^{th}$  clause of the Boolean formula  $\phi$ , which must be in either disjunctive normal form (top) or conjunctive normal form (bottom). . . 20

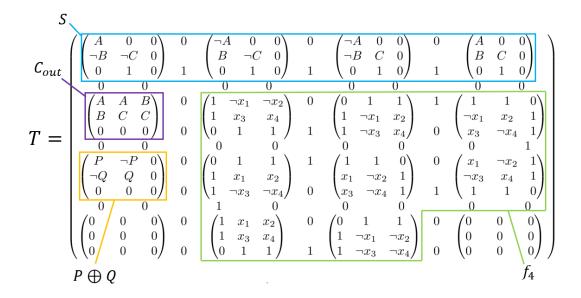

- 3.5 Network of crossbars method described in [3]. Here,  $S = (A \land \neg B \land \neg C) \lor$  $(\neg A \land B \land \neg C) \lor (\neg A \land \neg B \land C) \lor (A \land B \land C)$  and  $C_{out} = (A \land B) \lor (A \land C) \lor (B \land C)$  are the sum and carry-out bits over inputs  $A, B, C \in \{0, 1\}$ , and  $f_4$  is a 4-bit parity function over inputs  $x_1, x_2, x_3, x_4 \in \{0, 1\}$ . . . . . . 20

- 4.3 Memristor crossbars using our NNF construction for Boolean formulas  $(A \land B)$  (left),  $(A \lor B)$  (center),  $A \oplus B \equiv (A \lor B) \land (\neg A \lor \neg B)$  (right), where A = B = 1 and the source and destination wires are  $R_1$  and  $R_{|R|}$ , respectively. 33

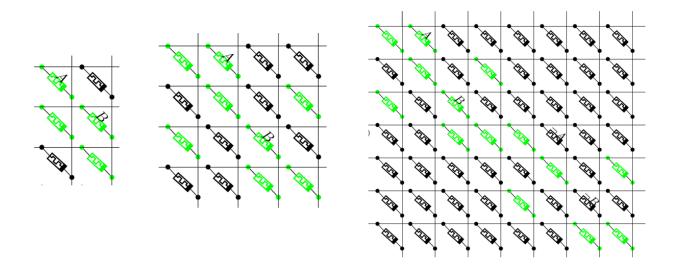

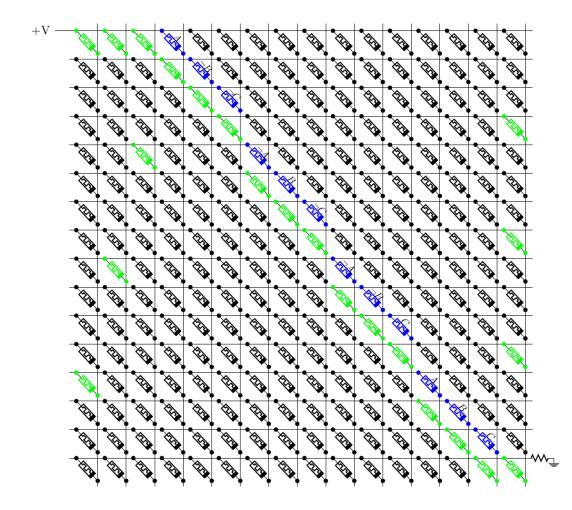

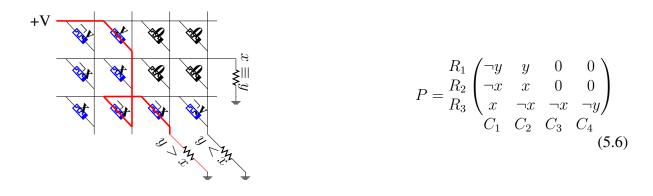

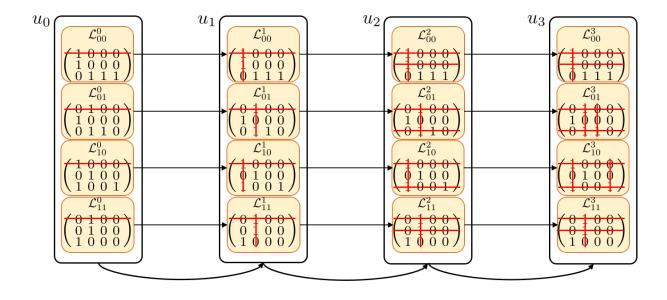

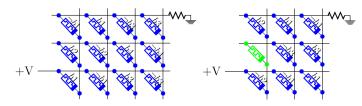

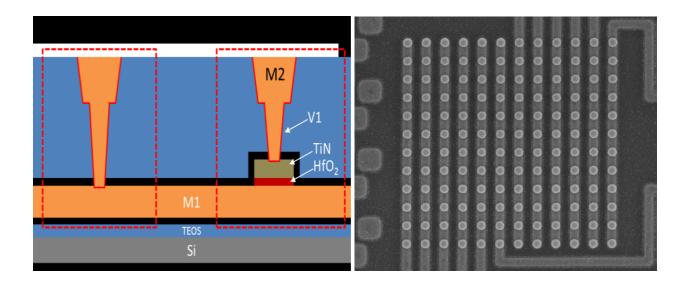

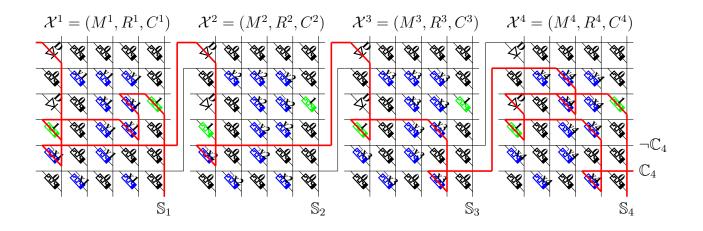

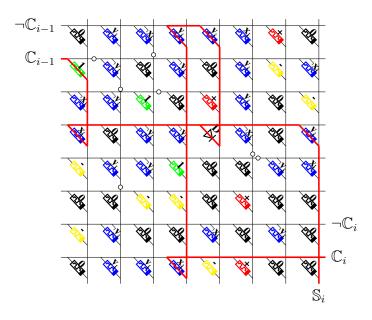

- 5.2 The finite state machine  $\mathcal{L}$  given the design P (5.6) for the comparator in Fig. 5.1. There are 4 sub-automata  $\mathcal{L}_{00}, \mathcal{L}_{01}, \mathcal{L}_{10}, \mathcal{L}_{11}$  corresponding to each evaluation vector  $\alpha \in \mathbb{B}^2$ . Each state  $u_t$  in  $\mathcal{L}$  is the union of states of its 43 5.3 Crossbar design visualization of a 4-bit parity and the sum bit of a full adder. 44 5.4 Crossbar design visualization of a full adder. 45 5.5 (left) Schematic cross-section of a memristor used in this work. (right) SEM View of a  $12 \times 12$  memristor crossbar array. Crossbar arrays were fabricated at SUNY Polytechnic Institute on 300 mm wafers using a modified IBM 65 nm 10LPe process flow. 46

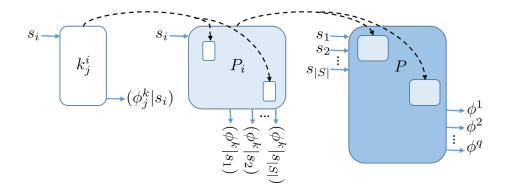

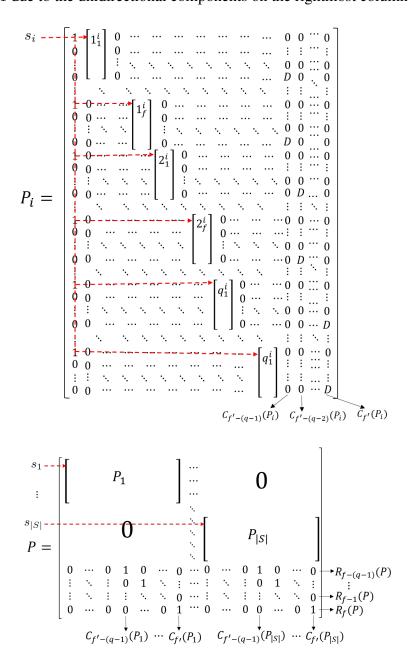

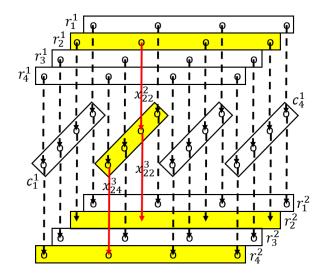

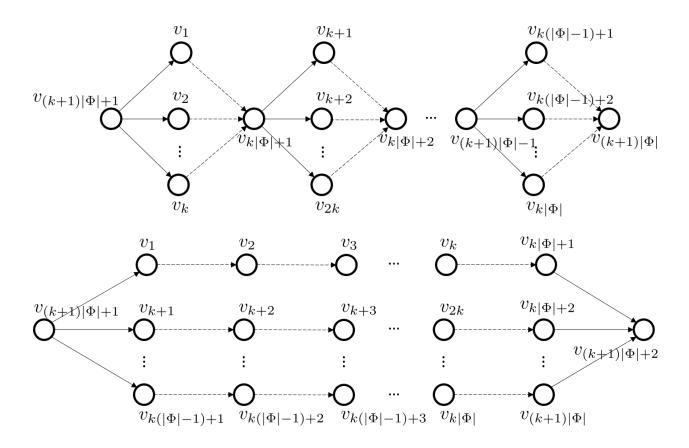

- 6.1 Modular representation of the construction in Theorem 6. The well-formed design  $k_j^i$  computes  $(\phi_j^k | s_i)$  for a given *i* and is used in  $P_i$  to compute  $(\phi^k | s_i)$ for all *i*.  $P_i$  is then used in the final design *P* to compute  $\phi^1, \ldots, \phi^q, \ldots, 56$

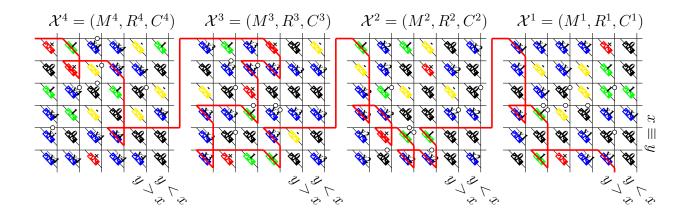

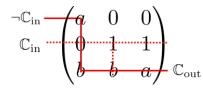

6.3 4-bit ripple-carry adder as a cascade of crossbars with mapping matrix (6.8).

61

| 7.1 | State transitions for a memristor $m$ given the voltage on its input wire $w$ and the state of the common wire $u$ .                                                                                                                                   | 71 |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

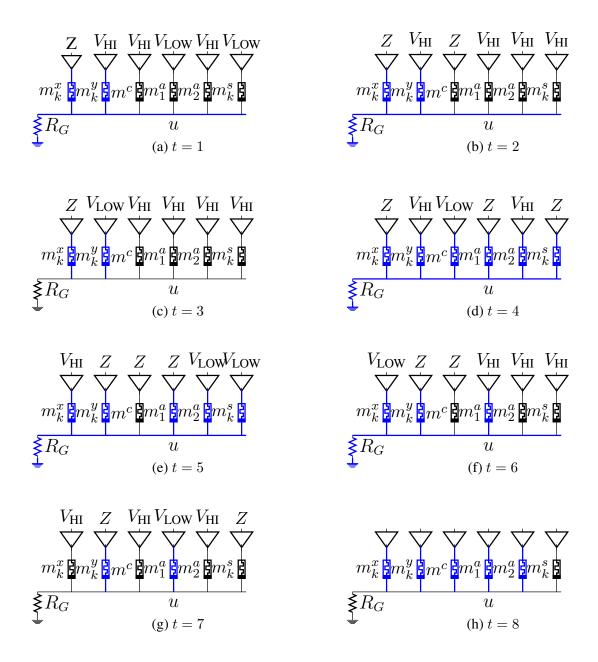

| 7.2 | Memory state at each stage of a 1-bit full adder procedure for non-destructive (ND)<br>addition with inputs $x_k = y_k = 1$ and $c_{in} = 0$ . The blue wire (memristor) denotes<br>$u = 1 \ (m = 1)$                                                  | 77 |

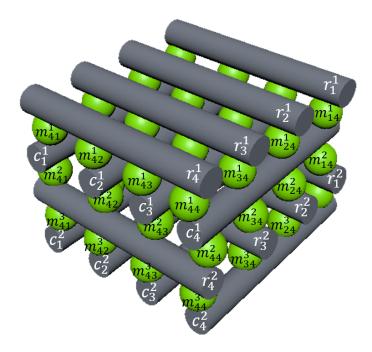

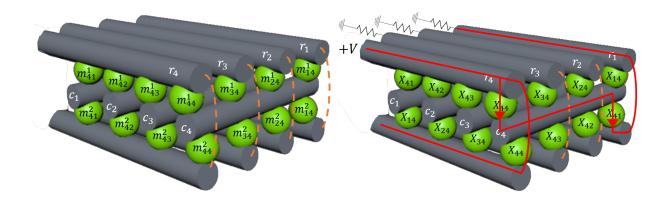

| 8.1 | $4 \times 4 \times 3$ 3D crossbar. There are two sets of row and column wires and three layers of interconnects.                                                                                                                                       | 79 |

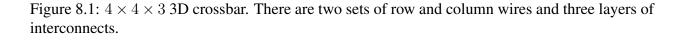

| 8.2 | $4 \times 4 \times 3$ crossbar illustrating the configuration proposed in order to compute<br>the product of Boolean matrices.                                                                                                                         | 82 |

| 8.3 | Dashed lines represent interconnections between row and column wires. Yel-<br>low bars denote a wire with a truth value of 1 and solid red lines are due to<br>Axiom 4; they correspond to interconnects redirecting flow from one wire to<br>another. | 85 |

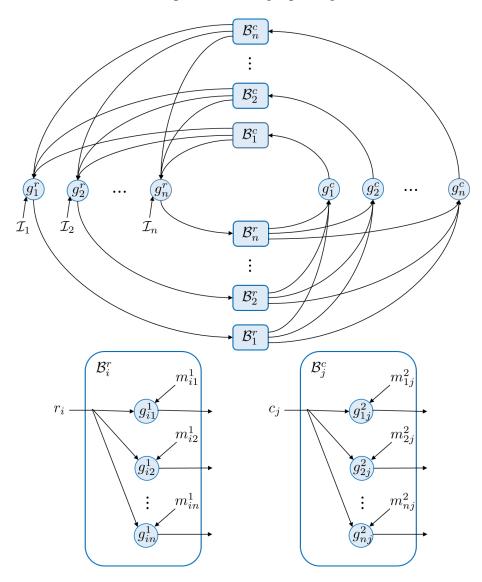

| 9.1 | ( <i>Left</i> ) A graphical illustration of a 3D crossbar $\mathcal{X} = (M^1, M^2, R, C)$ with<br>two layers of interconnects and external feedback loops. The dashed arcs                                                                            |    |

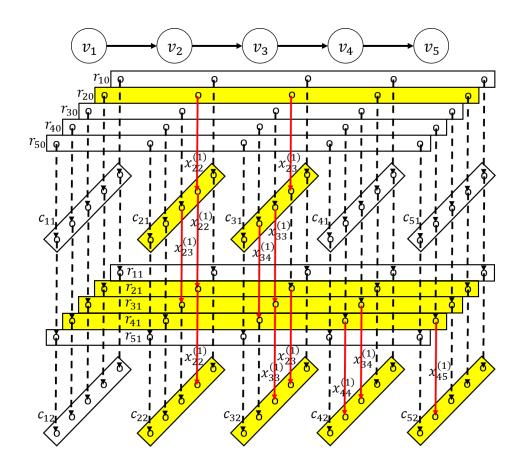

- 9.2 Cyclic Boolean circuit for a given  $n \times n$  crossbar  $\mathcal{X} = (M^1, M^2, R, C)$ . In this circuit, each wire value  $r_i, c_j$  has a corresponding Boolean function  $g_i^r : \{0, 1\}^{n+1} \mapsto \{0, 1\}, g_j^c : \{0, 1\}^n \mapsto \{0, 1\}$  which is a logical disjunction of its inputs. Similarly,  $g_{ij}^1, g_{ij}^2 : \{0, 1\}^2 \mapsto \{0, 1\}$  are 2-bit conjunctions corresponding to the logical output of each  $m_{ij}^1$  and  $m_{ij}^2$ , respectively. . . . . 93

- Procedure for computing the transitive closure  $X^*$  of directed graph G =9.3  $(\{v_1, v_2, v_3, v_4, v_5\}, E)$  (top). The two-layer crossbar with feedback loop  $\mathcal{X} = (M^1, M^2, \{R_1, R_2, R_3, R_4, R_5\}, \{C_1, C_2, C_3, C_4, C_5\})$  (bottom) is unrolled in order to help visualize the computation. Dashed lines represent interconnections between row and column wires, yellow bars denote a wire with a value of 1 (i.e. current flows through it), and solid red lines correspond to interconnects redirecting the flow of current from one wire to another. In this case, we are computing the second row vector  $(X_{21}^*, \ldots, X_{25}^*)$  of  $X^*$  by setting  $(r_{10}, r_{20}, r_{30}, r_{40}, r_{50}) = (0, 1, 0, 0, 0)$ . Note that  $(c_{12}, c_{22}, c_{32}, c_{42}, c_{52}) = (0, 1, 0, 0, 0)$ . 99 9.4 Boolean circuit corresponding to the example in Fig. 9.3. Boolean gates  $g_{ij}^1$ and  $g_{ij}^2$  have inputs  $X_{ij}^{(1)}$  and  $X_{ji}^{(1)}$  in accordance with Theorem 8. Each  $g_i^r$

9.6

xvi

# LIST OF TABLES

| 5.1 | Comparison of design performance, where time is defined as the number of                                                        |    |

|-----|---------------------------------------------------------------------------------------------------------------------------------|----|

|     | steps required to configure the crossbar and compute the formula of interest                                                    | 44 |

| 5.2 | Output voltages for wires $R_1$ and $R_2$ in the full adder design in Figure 5.4                                                |    |

|     | under all possible evaluations.                                                                                                 | 47 |

| 5.3 | Comparison between the proposed full adder architecture and the traditional                                                     |    |

|     | 28-transistor CMOS full adder                                                                                                   | 47 |

| 6.1 | Comparison of our crossbar ripple-carry adder (XRCA) against other cross-                                                       |    |

|     | bar $n$ -bit adder designs proposed in the literature. Our design is state-of-the-                                              |    |

|     | art in terms of execution steps required to compute $n$ -bit addition                                                           | 62 |

| 6.2 | HSPICE simulation results for the full adder design in (6.8). Each column                                                       |    |

|     | entry denotes values under an evaluation vector $\alpha = (x_i, y_i, \mathbb{C}_{i-1})$ . Wires                                 |    |

|     | $C_5, R_5, R_6$ are grounded and a 5V voltage pulse is applied to $R_1$ if $\mathbb{C}_{i-1} = 0$                               |    |

|     | or to $R_2$ if $\mathbb{C}_{i-1} = 1$ . The voltage values read correspond to $\mathbb{S}_i, \neg \mathbb{C}_i, \mathbb{C}_i$ , |    |

|     | respectively. Each entry denotes the voltage reading obtained from grounded                                                     |    |

|     | wires $C_5, R_5, R_6$                                                                                                           | 65 |

| 6.3 | Power comparison between the proposed crossbar ripple-carry adder archi-              |    |

|-----|---------------------------------------------------------------------------------------|----|

|     | tecture (XRCA) and adders presented in the survey [4] using traditional CMOS.         |    |

|     | These are ripple-carry (RCA), increment (INCA), triangle (TRIA), uniform              |    |

|     | and progressive carry-select (CSELA-UNIF, CSELA-PROG), conditional                    |    |

|     | (COND), uniform and progressive-carry bypass (CBYPASS-UNIF, CBYPASS-                  |    |

|     | PROG), and ripple-carry and hierarchical-carry lookahead (CLA-RIPPLE,                 |    |

|     | CLA-HIER) adders. All architectures are simulated using 180 nm technol-               |    |

|     | ogy with a $1.8$ V pulse and $10$ MHz frequency. NVSIM files can be found in          |    |

|     | eecs.ucf.edu/~velasquez/Table6.3                                                      | 66 |

|     |                                                                                       |    |

| 7.1 | Comparison of our adder designs against other $n$ -bit in-memory adder designs pro-   |    |

|     | posed in the literature                                                               | 68 |

| 7.2 | Voltage sequences for implementing the non-destructive, semi-destructive, and fully-  |    |

|     |                                                                                       | 74 |

|     |                                                                                       |    |

| 7.3 | Generalized memristor states at each stage of a non-destructive 1-bit full adder with |    |

|     | respect to arbitrary inputs                                                           | 74 |

|     |                                                                                       |    |

| 8.1 | DESTINY [5] simulations of different memory architectures using 22 nm                 |    |

|     | technology, including the 3D ReRAM used in this paper. In order to avoid              |    |

|     | bias, we utilize the default parameters included in the simulator. Simulation         |    |

|     | files can be found in eecs.ucf.edu/~velasquez/Table7.1                                | 87 |

| 9.4 | Computation time and energy usage metrics for various benchmark circuits      |

|-----|-------------------------------------------------------------------------------|

|     | taken from the Stanford Large Network Data Collection. These networks         |

|     | are mapped to the memories presented in Table 9.3 and the aforementioned      |

|     | metrics are reported. In the (Read) columns, we report values that correspond |

|     | to memories whose cells contain the contents of the network. The (Write +     |

|     | Read) columns assume that the memories must first be configured to contain    |

|     | the contents of the network                                                   |

# **CHAPTER 1: INTRODUCTION**

Computing on current high-performance machines is exacerbated by three issues that arise from challenges in the processing and storage of data. First, the era of sustained transistor scaling per Moore's law is now believed to be coming to an end. In the past, such predictions have been made and the obstacles have been overcome by the ingenuity and collaboration of engineers and scientists. However, the lithographic processes required to fabricate ever-smaller transistors result in higher process variations and more unpredictable structures when working at the atomic scale [8]. Furthermore, the alignment of these devices poses an even greater challenge as we traverse deeper into the nanoscale [9].

In response to these difficulties, substantial research has been devoted to novel patterning methods that can extend traditional optical lithography. This research effort has produced methods such as extreme ultra-violet (EUV) lithography, nanoimprint lithography (NIL), maskless lithography (ML2), and bottom-up directed self-assembly (DSA). The last of these methods shows promise as a potential successor to top-down lithography [10]. DSA synthesizes relatively basic primitives with precise shapes that may be used for computation. However, it is not suitable for fabricating complex device topologies that frequently occur in modern circuits [8]. The use of these basic primitive structures necessitates a paradigm shift in our circuit model. Motivated by the success of assembling aligned nanowires [11] and the ease of reconfiguration, attention has shifted to the use of crossbars [12], which consist of perpendicular sets of parallel wires with two-terminal components at each wire junction. These can be easily assembled using DSA [13]. However, the fabrication of crossbars using this approach suffers from high defect rates [8]. These defects occur in the form of stuck-off and stuck-on devices as well as broken wires. The high defect rates make it uneconomical to simply reject defective nanoscale crossbars [14]. Hence, there is a pressing need to develop fault-tolerant computing approaches [15, 16, 17] that can ensure the fruitful use of even

defective nanoscale crossbars. To this end, we propose a new methodology for mapping logical and arithmetic operations onto a defective crossbar that exploits the occurrence of faults.

The second limitation in high-performance computing stems from today's popular DRAM and SRAM memories, which are volatile in that their stored data is lost when the power source is removed from the system. Consequently, these architectures require a constant supply of power to refresh the stored data, resulting in poor energy efficiency. In order to meet the energy demands of the future, we must move away from volatile memory. Fortunately, much work is being done in this area. HP has announced their plans of building *the Machine* with non-volatile memory. An overhaul of the traditional processor-centric computing model to a memory-driven one has also been proposed [18]. Intel and Micron recently unveiled their groundbreaking 3D XPoint<sup>TM</sup> memory architecture [19] – a 3-dimensional crossbar architecture with two layers of non-volatile memory cells which is orders of magnitude faster than traditional solid-state drives [20]. This technology can already be found on the market in the form of Intel's Optane<sup>TM</sup> drives [21]. HP and Sandisk have also announced a partnership for investigating the area of memory-driven computing [22] in the hopes of leveraging their memristor and non-volatile resistive RAM technologies.

Though a useful step in the right direction, the adoption of non-volatile technology may not be enough on its own. This brings us to our third problem in high-performance computing: the infamous memory wall [23] that arises in traditional von Neumann architectures where the memory and processing units are segregated. This separation poses serious restrictions on performance. Under a 45 nm process at 0.9 V, it has been reported [24] that 32-bit floating-point multiplication consumes approximately 4 pJ of energy whereas accessing DRAM requires 1.3 - 2.6 nJ. There is a difference of three orders of magnitude in power consumption between computation and memory access in this case. A study by NVIDIA yielded similar results [25]. Namely, that a 64-bit arithmetic operation consumes 20 pJ of energy as opposed to the 16 nJ consumed during DRAM read/write operations. The aforementioned problems motivate the need for a non-volatile in-memory computing architecture that uses post-CMOS devices. Such architectures have been studied in the domain of memristor crossbar computing. This powerful alternative to traditional computing uses crossbars to perform both memory and logic operations, thereby eliminating the separation of memory and processing units that is characteristic of traditional architectures and offering a potential solution to the second and third problems mentioned. This topic has garnered significant attention in the past few years due to the reasons mentioned earlier, as well as the breakthrough discovery of memristors [26], which are two-terminal non-volatile memory components that are regarded as potential successors to the transistor. It is worth noting that these memristors have been successfully assembled into crossbars through non-lithographic methods [8, 13]. Thus, in-memory memristor-based computing helps to address the three problems mentioned. It is worth noting that the results presented in this document apply to other memory architectures as well. In particular, any memory whose components store values and act as open or closed switches depending on these values. One such example is phase-change memory (PCM).

The remainder of this thesis is organized as follows.

**Chapter 2**: A detailed exposition of the three main facets of crossbar architectures is presented. These are the interconnects, their arrangement into crossbar designs, and the sneak paths constraint that arises therein.

**Chapter 3**: Related work is presented. Namely, we present popular methods for computing Boolean functions using crossbar memories. These include procedures based on logic synthesis, formula-dependent placement of interconnects, and crossbar networks, among others.

**Chapter 4**: The theory of paths-based logic is presented. This theory provides a framework for arguing about the number of trajectories, or paths, that electric current can flow through between two wires in a crossbar. The notion of irreducible paths is introduced and is used to prove that only

a small subset of paths need to be considered in order to perform computations. The universality of paths-based logic is also established by proposing a general design methodology for any given Boolean formula.

**Chapter 5**: We leverage the results in Chapter 4 and advances in model checking to propose a framework that generates compact crossbar designs to compute a given Boolean formula. This framework is then extended to handle common crossbar faults such as stuck-on and stuck-off defects as well as broken wires.

**Chapter 6**: The limitations of using traditional crossbars and paths-based logic to compute functions are proven rigorously. We then demonstrate how such limitations can be overcome by using heterogeneous crossbars. These crossbars augment the traditional model by allowing interconnects to route the flow of current in some particular direction as opposed to restricting ourselves to interconnects that allow bidirectional flow of current across them. A fault-tolerant design automation approach using these heterogeneous crossbars is proposed in a similar fashion to the one in Chapter 5.

**Chapter 7**: An alternative design automation approach using bounded model checking is presented. As opposed to searching through the space of possible memory configurations, we now search the space of voltage inputs that can be applied on the wires of the memory. Namely, we synthesize the shortest sequence of voltage pulses that will store the result of some desired formula. By allowing the synthesis procedure to perform destructive operations wherein input data can be overwritten, we achieve designs that are state-of-the-art in terms of space.

**Chapter 8**: We focus our attention on crossbars consisting of 1-diode 1-resistor (1D1R) interconnects and how they can be used to compute the product of Boolean matrices, a fundamental problem in computer science. This problem is of interest for various reasons. It is an integral part of group testing [27] and its applications in genetics, data forensics, fault diagnosis, and on-chip sensing. Boolean matrix multiplication has also been studied in the context of matrix decomposition [28], cryptography [29], and CFG parsing [30, 31].

**Chapter 9**: We present a new in-memory computing architecture that can compute the transitive closure of graphs within non-volatile 3D resistive memory (3D RRAM) with external feedback loops. We demonstrate that our approach has a runtime complexity of  $O(n^2)$  operations using  $O(n^2)$  devices. In practice, we argue that our method is both fast and energy-efficient (see Table 9.4 and Section VI).

**Chapter 10**: We briefly outline the contributions made, suggest potential avenues of research in the area, and allude to future work.

### **CHAPTER 2: BACKGROUND**

#### Memristors

The idea of a memristor was first theorized by Leon Chua in 1971 based on a fundamental symmetry argument. Chua argued that there were existing relationships between all of the different electromagnetic elements, except for magnetic flux and charge. Hence, he postulated that a relationship between charge and magnetic flux must exist; he defined the component that establishes this relationship as a *memristor*. Memristance, as defined by a nonlinear relationship between voltage and current, has been serendipitously observed in circuits for decades. It was normally considered an anomaly until 2008, when the quantum science research group at Hewlett Packard laboratories developed the first working memristor and theoretical models explaining its behavior.

Since their discovery by HP Labs in 2008, memristors have been a topic of active research due to several desirable properties, including (i) their small size (< 10 nm), (ii) the ability of a memristor to maintain its state for years after bias has been removed, and (iii) their low power footprint compared to traditional transistors.

The memristor, as detailed in [32], is a two-terminal passive component acting as two variable-state resistors in series – one acting as a semiconductor doped with ion vacancies and the other acting as an insulator. The doped region drifts as the result of electric fields generated by the voltage bias. The properties of the memristor are dictated by its material composition. While the TiO<sub>2</sub> film has been well-studied in memristive and resistance-switching devices, HfO<sub>2</sub> [33], a-Si [34], TaO<sub>x</sub> [35], a-LSMO [36], and a-SrTiO3[37] have also been studied, among others. These differing electrochemical compositions give rise to varying degrees of nonlinearity in the voltage-current relationship of the memristor. They also determine the endurance and power consumption of the

devices and can even cause interesting effects, such as producing unipolar rectifying memristors that act similarly to diodes [38].

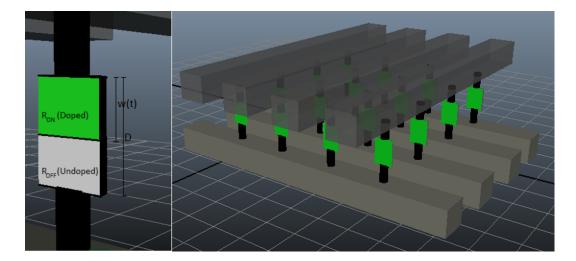

The state of the memristor is uniquely identified by the width w of the doped region of the memristor, as can be seen in Figure 2.1. Here, D is the entire width of the memristor. A positive current causes the doped region to grow, thus increasing w and reducing the overall resistance (memristance) of the memristor. Conversely, a negative current will decrease w and make the resistance of the memristor higher. We denote the low resistance of the doped region by  $R_{on}$  and the high resistance of the undoped region by  $R_{off}$ .

It is worth noting that a voltage threshold which must be exceeded in order to change the state of a memristor, and therefore its resistance, is apparent when there exists a strong nonlinearity in the I-V relationship of the memristor [6]. This allows us to use voltages smaller than said threshold in order to read values from memristors or memristor crossbars without destroying data by erroneously changing the state of the memristors involved.

Figure 2.1: A memristor can be modeled as a pair of resistances in series – a low-resistance resistor of width w and a high-resistance resistor of width D - w (left).  $4 \times 4$  Memristor crossbar (right).

The focus of this thesis is on memristors acting as switches. To this end, we only deal with memristors in one of the extreme states such that their resistance is  $R_{on}$  or  $R_{off}$ . A memristor M in its lowest (highest) resistance state acts similarly to a closed (open) switch and is said to the in the LRS (HRS) state. Here, LRS and HRS stand for low-resistance and high-resistance state. The state m of memristor M is given by m = 1 (m = 0) to denote the LRS (HRS) state.

#### Crossbar Computing

A crossbar consists of two sets of mutually perpendicular wires. Each wire from one set is connected to every wire from the other set through an electronic component. This interconnection can be a two-terminal device such as a diode or memristor, or a three-terminal device such as the CMOS transistor. In the remainder of this section, we will briefly discuss a few popular crossbar computing architectures.

The NanoFabric [39] consists of an array of interconnected and reprogrammable nano-crossbars, called nanoBlocks, with corresponding switch blocks. The NanoFabric is similar to an FPGA *sans* the look-up tables. A number of NanoFabric designs have been proposed that include AND, OR, XOR, and a half-adder. The NanoPLA [40] uses reconfigurable diodes or rectifying diode-like elements in tandem with NOR-NOR logic in order to perform logical operations. The Nanoscale Application-Specific Integrated Circuit (NASIC) architecture [41] is an ASIC that utilizes field-effect transistors and crossbars. An extension of this framework that interfaces with a 3D CMOS stack has also been explored [42].

Crossbar-computing frameworks using traditional CMOS-like logics have been proposed as well. In one such methodology [43], crossbars of p- and n-type FETs and programmable switches are used to evaluate logical conjunctions, disjunctions, and inversions. A hybrid approach, referred to as CMOL [44], utilizes CMOS and molecular computing in the form of crossbars. The crossbars are fabricated on top of the CMOS die and the two architectures interface via a set of pins that connects the CMOS die to the top and bottom nanowires. Bottom-up self-assembly is perfectly suited for this by allowing the crossbars to grow regardless of substrate used, thus not requiring the high temperatures that restrict the fabrication of CMOS circuitry on top of another CMOS stack [9]. The crossbars could function as memory or as reconfigurable computing fabrics. A variation of CMOL [45] uses a field programmable nanowire interconnect (FPNI) to facilitate communication between the crossbar and the CMOS stack. Some additional constraints are enforced, such as confining logic to the CMOS stack and restricting routing to the crossbar. The resulting architecture trades off speed and fault-tolerance for ease of fabrication when compared to traditional CMOS. A 3D extension of CMOL was introduced in [46]. In this architecture, two CMOS stacks are used and the crossbar is sandwiched between the two stacks. This allows each stack to communicate with only one set of wires, thereby mitigating the pin interfacing difficulties of traditional CMOL.

Promising emerging technologies, such as the memristor [26] and spin-transfer-torque (STT) devices, have also been introduced to the crossbar-computing domain both as memory and as computation nodes. A 3-D crossbar architecture [47] uses memristors together with an interfacing methodology similar to field programmable nanowire interconnect (FPNI). The use of Null Convention Logic (NCL) [48] has also been explored to develop an asynchronous lookup table using a memristor crossbar. Sneak paths [49] pose a problem in these architectures by causing HRS nodes to be read as LRS nodes due to the flow of current through sequences of LRS nodes that run in parallel to the current being used to measure the HRS node. This problem is analogous to the crosstalk problem in RRAM memories. Solutions have been proposed via the use of 1M1D memristor-diode structures or diode-like rectifying memristors [50] [2]. In this thesis, we explore the application of formal methods to the problem of designing crossbars that can exploit these sneak paths as a means for evaluating Boolean formula [51] rather than suppress them.

One omission often made in the literature lies in addressing the robustness of crossbar computing designs in the presence of stuck-off and stuck-on nodes as well as broken wires, which are common defects resulting from self-assembly [8]. Given a faulty  $n \times n$  crossbar, one solution [52] determines the  $k \times k$  (k < n) maximum defect-free subset of the crossbar which can then be used in the application-mapping stage of the fabrication process. However, the computational power of the resulting crossbar can be diminished due to loss of significantly many computation nodes. Another algorithm for finding defect-free subcrossbars from a defective crossbar is proposed in [53]. Other methods include simply avoiding the defective devices altogether by providing redundancy in the form of spare parts [54].

In light of the high defect rates associated with self-assembled crossbars, we propose a new approach to fault-tolerant crossbar computing that exploits the stuck-at interconnects and broken wires to design nanoscale crossbars for computing Boolean formula. As our method does not try to identify a sub-crossbar of defect-free interconnects and instead leverages defects during the design phase, it is capable of performing useful computations even on highly defective crossbars. Our approach is independent of the underlying architecture and only requires the use of a crossbar consisting of digital switches. As such, this framework can be easily implemented using memristor crossbars, CMOL, and phase-change memories (PCMs).

### Sneak Paths

One problem that arises in crossbar computing is that of sneak paths. That is, the paths of current that flow through the crossbar which may cause wrong values to be read from memristors. These sneak paths are formally defined in [55] for an |R|-by-|C| binary matrix representation of the memristor states in the crossbar. A path of length 2k + 1 affecting the cell at position (i, j) is said to be a sneak path if  $m_{ij} = 0$  (i.e. the memristor connecting wires *i* and *j* is in the HRS state) and

there exist 2k positive integers  $1 \le r'_1, \ldots, r'_k \le |R|$  and  $1 \le c'_1, \ldots, c'_k \le |C|$  for some  $k \ge 1$ such that the following 2k + 1 memristor states satisfy

$$m_{ic_1'} = m_{r_1'c_1'} = m_{r_1'c_2'} = \dots = m_{r_{k-1}'c_k'} = m_{r_k'c_k'} = m_{r_k'j} = 1$$

(2.1)

Thus, a path of LRS memristors can cause an HRS memristor's interconnected wires to have a significant flow of current across them. This is normally seen as a problem in the literature, especially in individually-addressable memory designs where a current is applied to read the state of a particular memristor. This same current can create a sneak path as mentioned above and cause a wrong state to be read (i.e. an HRS memristor might be read as if it were an LRS memristor). For example, suppose we wish to read the state of the blue memristor in the crossbar in Fig. 2.2, where green and black nodes represent LRS and HRS memristors, respectively. Naturally, a voltage bias is applied at one terminal of the blue memristor while the other terminal is grounded. It follows that, if the blue memristor is in the HRS state, then the voltage drop across the resistor-to-ground should be small. This basic principle can be violated by the sneak paths constraint, which can cause the blue memristor to be read as if it were in the LRS state regardless of its true state.

Numerous solutions and alleviations to the sneak paths problem have been proposed [56, 57, 58, 59, 60, 61, 62, 63, 64]. We briefly present some of these works.

In [59], a multistage method is proposed to accurately read the state of some memristor in a crossbar via a sequence of read and write operations. A total of three read, three write, and one comparison operation is required. The method in [56] also utilizes multiple readings to accurately determine the state of a memristor in the presence of sneak paths. This work improves upon [59] by introducing multipoint access along with the multiple readings in order to reduce the number of read/write operations from six to three. Unfortunately, both of these methods require additional complex hardware and, perhaps more obtrusively, multiple operations are required for what would ideally be a single operation.

Traditionally, transistors and diodes have been deployed in computer architectures to prevent the propagation of undesired current. Thus, it is sensible to attempt such a deployment in memristor crossbars. [60] proposes such a framework by positing a hybrid memristor-crossbar architecture that utilizes the 1D1M and 1T1M structures, where each memristor requires a diode or a transistor, respectively. The diodes in the 1D1M structure cause the flow of current to travel in only one direction, thereby eliminating the sneak paths constraint. This does, however, introduce a significant problem to the crossbar's writing process, which requires dual polarities for effective writes and erases. The 1T1M structure also has pervasive side effects in the form of significantly decreased crossbar density and increased power consumption [58].

In order to preserve the outstanding fabrication density intrinsic to memristive devices, it is desirable to mitigate the sneak paths constraint without complex added circuitry. We propose a crossbar computing framework that mitigates the sneak paths problem without added circuitry or timeconsuming multistage read and write operations. The designs proposed herein exploit sneak paths as first-class design primitives and employ them to perform the proposed computations.

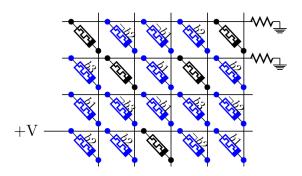

Figure 2.2: Flow behavior of sneak paths, where green nodes denote LRS memristors and black nodes represent HRS memristors. The red bars represent flow of current and we wish to read the value of the blue memristor by applying a voltage at one terminal and grounding the other. It can be seen that a high voltage value will be read at the grounded terminal due to sneak paths regardless of the state of the blue memristor.

### **CHAPTER 3: LITERATURE REVIEW**

Since the discovery of the memristor in 2008, significant effort has been devoted to the development of design methods that allow for memristor-based computation. While there are numerous studies in the area of digital logic computations using individual memristors [65, 66, 67, 68, 2, 69, 3], the literature is scarce when it comes to digital memristor-crossbar computing. This is because developing efficient memristor-crossbar computing frameworks is difficult due to the challenge posed by sneak paths. In this section, we present four memristor-crossbar computing methodologies proposed in the literature and demonstrate how the novel architectures proposed therein overcome the sneak paths constraint and at what cost.

#### Logic Synthesis Methods

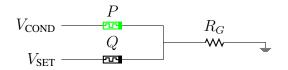

In-memory crossbar computing is largely based on the implication-falsity logic presented in [70]. We briefly present an outline of this procedure. Let P and Q denote two memristors with corresponding states  $p, q \in \{0, 1\}$ , where 0 and 1 denote high-resistance and low-resistance states (HRS, LRS), respectively. Both devices are connected to the same load resistor  $R_G$  and let  $V_{\text{COND}}, V_{\text{TH}}, V_{\text{SET}}$  denote voltages such that  $V_{\text{SET}}$  is sufficient to switch a memristor to the LRS state,  $V_{\text{TH}}$  is the threshold voltage value that must be exceeded in order to switch said memristor, and  $V_{\text{SET}} - V_{\text{COND}} < V_{\text{TH}}$ . Apply voltage bias  $V_{\text{COND}}$  to P and  $V_{\text{SET}}$  to Q. This will cause Q to switch to or remain in the LRS state if  $p \implies q$ . See Fig. 3.1 for a visualization of the case when p = 1 and q = 0. It is easy to see that Q will be switched to or remain in the LRS state under the other 3 evaluations of p and q because the voltage drop across Q will be  $V_{\text{SET}} > V_{\text{TH}}$ . A voltage  $V_{\text{CLEAR}}$  can be used to set the memristor to the HRS state corresponding to a binary value of 0, or *false*. This combination of implication and falsity is functionally complete for Boolean operations.

This result catalyzed a host of design methodologies [71, 69, 67, 68] based on minimizing the number of implication operations required to compute a formula of interest.

Figure 3.1: Memristor implication logic. The green memristor P is in the LRS state (p = 1) and the black memristor Q is in the HRS state (q = 0). The voltage drop across Q will be approximately  $V_{\text{SET}} - V_{\text{COND}} < V_{\text{TH}}$ , so Q will remain in the HRS state, meaning that  $q = 0 = (p \implies q)$ .

In [72] and [73], each interconnect is a complementary resistive switch consisting of two memristors of opposite polarity. The basic logical operation on these interconnects follows the equation  $Z^t = (w \iff b) \land Z^{t-1} \lor (w \implies b) \land \neg Z^{t-1}$ , where  $Z^t$  is the state of the device at time t, w(b) is the wordline (bitline) such that w = 1 (b = 1) in the presence of a high voltage potential and 0 otherwise. This allows greater control over the flows of current throughout the crossbar and it is demonstrated how under this approach an *n*-bit NAND operation can be computed in a constant number of steps as opposed to the linear amount demonstrated in previous works. The results in [73] apply specifically to the design of adders while the contribution in [72] is a general design methodology using NOR-OR and NAND-AND logic.

In [74], a method for computing is proposed that deviates from the omnipresent implication-falsity logic. Each gate consists of a set of input memristors programmed to the HRS or LRS state and an output memristor that will be programmed to the LRS (HRS) state if the gate operation evaluates to 1 (0). Each input memristor is configured to the LRS (HRS) state if its corresponding variable is 1 (0). A programming voltage is then applied so that the output memristor will reach the LRS (HRS) state if the underlying operation evaluates to 1 (0). For example, to perform an *n*-bit disjunction (OR), *n* input memristors are placed in parallel and connected to the output memristor. It follows that if any of the input memristors is in the LRS state, then the output memristor connected to it

will be switched to the LRS state, denoting a value of 1 as intended. Logical conjunction (AND) is performed by placing the input memristors in series so that all of them must be in the LRS state in order to switch the output memristor. Similar procedures are used to compute NAND, NOR, and NOT. It is worth noting, however, that only the NOR operation is amenable to integration within a traditional crossbar array. As such, a computing paradigm using this approach would necessitate additional structural complexities.

The methods referenced in this section are used as benchmarks against which we compare the complexity of some of our proposed designs (See Table 6.1). In particular, we demonstrate that our design is state-of-the-art in terms of execution steps required to compute addition. Our approach is fundamentally different from the methods mentioned in that the components in the crossbar are programmed only once in such a way that the induced trajectories of current can be used to compute.

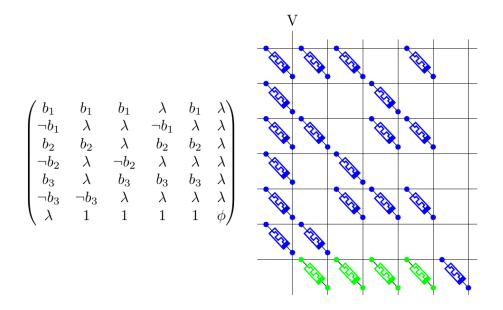

### Formula-Dependent Memristor Placement

In [1], a crossbar construction for evaluating Sum-of-Minterms form Boolean formulas is proposed. The method consists of mapping each clause in the formula to a separate column in the crossbar and mapping all of the literals to the first column. Every column, except the first, contains an LRS memristor at the bottommost row in order to redirect current during the computation step. To perform the actual computation, a read-out voltage is applied on the first column and the formula evaluates to true if one of the columns redirects current to its corresponding LRS memristor, which in turn would use this current to determine and save the state of the result memristor. The design manages sneak paths by removing memristors from locations that are uniquely determined by the formula being evaluated. As an example, we construct the 3-bit parity function  $(b_1 \wedge b_2 \wedge \neg b_3) \vee (b_1 \wedge \neg b_2 \wedge b_3) \vee (\neg b_1 \wedge b_2 \wedge b_3) \vee (b_1 \wedge b_2 \wedge b_3)$  using this method in Figure 3.2.

Figure 3.2: Matrix (left) and crossbar (right) representations of a 3-bit parity construction using the design proposed in [1], where green memristors are in the LRS state,  $\lambda$  values specify a location in which there is no memristor, and the states of blue memristors are determined by variables  $b_i$  and their negations  $\neg b_i$  in the Boolean formula  $\phi$  which we wish to evaluate. The resulting value of  $\phi$  will be stored in the bottom right memristor of the crossbar when the computation is finished.

While this approach benefits from fast computation time, it overcomes the sneak paths issue by adding significant complexity to the design, where only certain junctions may contain memristors and the locations of said junctions vary from formula to formula. This can lead to prohibitively expensive fabrication costs as well as difficulty in reconfiguring such crossbars.

### **Rectifying-Memristor Crossbars**

Another crossbar computing method is introduced in [2]. This method leverages the diode-like capabilities of rectifying memristors [50] to suppress the interference from sneak currents. Unlike

the previous design, there is no added complexity to the crossbar beyond the use of rectifying memristors.

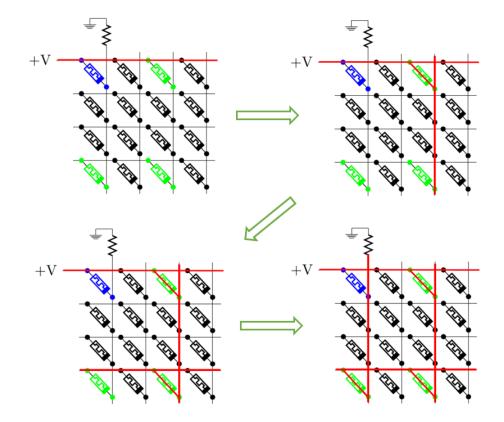

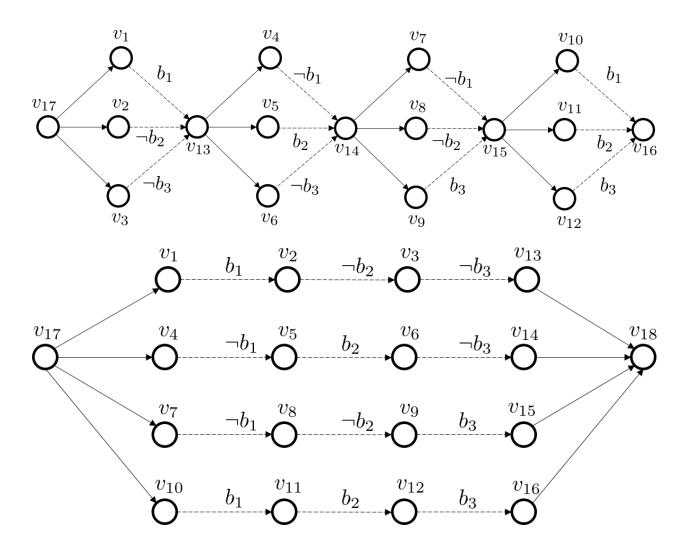

A new operation is introduced based on a procedure similar to the implication logic process described in [66]. This operation is called converse nonimplication, and it provides a method for configuring a crossbar of rectifying, diode-like memristors as well as for performing logical functions. This memristive converse nonimplication logic is used in tandem with the multi-input implication logic introduced in [68] to configure the crossbar and compute the Boolean formula of interest. In the case of a 3-bit parity function  $\phi$ , we can map the formula to a 5-by-4 crossbar as follows:

Figure 3.3: States of the 3-bit parity function over inputs  $b_1, b_2, b_3 \in \{0, 1\}$  mapped to a crossbar using the method in [2].

In Figure 3.3, we assume that the crossbar is initialized to state (1) in a constant number of steps. State (2) is obtained in 2n steps via converse nonimplication, where n is the number of literals in  $\phi$ . State (3) can then be achieved in a single time step by performing a multi-input implication operation on rows 1 through 4 in parallel. This operation is possible thanks to the unidirectional sneak current flow provided by the rectifying memristors. Note that the resulting literal values in column 4 are the negation of the literals in columns 1 through 3; this is because the implication operation  $M_{i4} = ((b_1 \lor b_2 \lor b_3) \implies 0) = (\neg b_1 \land \neg b_2 \land \neg b_3)$ . Similarly, applying a multi-input implication step on column 4 yields state (4), where  $\phi = (\neg b_1 \lor \neg b_2 \lor b_3) \land (\neg b_1 \lor b_2 \lor \neg b_3) \land (b_1 \lor \cdots b_2 \lor b_3) \land (b_1 \lor b_2 \lor b_3)$  is stored in  $m_{5,4}$ . This method benefits from the use of a simple crossbar layout and its intuitive use of rectifying memristors to mitigate the sneak paths problem. However, having to reduce any formula to a sometimes complex sequence of implication logic operations can lead to considerable overhead. For example, a 3-bit parity function requires 30 computational steps to be evaluated using elementary implication logic [75].

### Networks of Interconnected Crossbars

Finally, we have the framework proposed in [3]. This method can be seen as an extension of [76] using a network of interconnected crossbars in order to improve the space complexity of the resulting designs. Any individual crossbar in the network can be used to evaluate a conjunction or disjunction of Boolean variables. By connecting multiple crossbars together, disjunctions (conjunctions) of conjunctions (disjunctions) can be evaluated. Thus, the universal disjunctive and conjunctive normal forms (DNF, CNF) can be computed. See Figure 3.4 for the DNF and CNF designs and Figure 3.5 for an example.

The methods presented in this section succeed in computing Boolean formula using memristor crossbars. These methods are diverse and have different benefits and drawbacks; however, none of them meet all of the following three fundamental tenets of computing architectures: space efficiency, fast computation time, and cost-effectiveness due to structural simplicity.

$$T_{DNF} = \left( \left( \begin{array}{c} \mathbb{M}_{\Lambda}(\phi^{(1)}) \\ \mathbb{M}_{\Lambda}(\phi^{(2)}) \\ 1 \end{array} \right)^{0} \left( \begin{array}{c} \mathbb{M}_{\Lambda}(\phi^{(2)}) \\ \mathbb{M}_{\Lambda}(\phi^{(2)}) \\ 1 \end{array} \right)^{0} \left( \begin{array}{c} \mathbb{M}_{\Lambda}(\phi^{(1)}) \\ \mathbb{M}_{\nu_{\nu}}(\phi^{(2)}) \\ 1 \end{array} \right)^{1} \left( \begin{array}{c} \mathbb{M}_{\nu_{\mu}}(\phi^{(1)}) \\ \mathbb{M}_{\nu_{\mu}}(\phi^{(1)}) \\ 0 \end{array} \right)^{0} \left( \begin{array}{c} \mathbb{M}_{\nu_{\nu}}(\phi^{(2)}) \\ \mathbb{M}_{\nu_{\mu}}(\phi^{(1)}) \\ 0 \end{array} \right)^{0} \left( \begin{array}{c} \mathbb{M}_{\nu_{\mu}}(\phi^{(1)}) \\ \mathbb{M}_{\nu_{\mu}}(\phi^{(1)}) \\ 0 \end{array} \right)^{0} \left( \begin{array}{c} \mathbb{M}_{\nu_{\mu}}(\phi^{(1)}) \\ \mathbb{M}_{\nu_{\mu}}(\phi^{(1)}) \\ \mathbb{M}_{\nu_{\mu}}(\phi^{(1)}) \end{array} \right)^{0} \left( \begin{array}{c} \mathbb{M}_{\nu_{\mu}}(\phi^{(1)}) \\ \mathbb{M}_{\nu_{\mu}}(\phi^{(1)}) \\ \mathbb{M}_{\nu_{\mu}}(\phi^{(1)}) \\ \mathbb{M}_{\nu_{\mu}}(\phi^{(1)}) \end{array} \right)^{0} \left( \begin{array}{c} \mathbb{M}_{\nu_{\mu}}(\phi^{(1)}) \\ \mathbb{M}_{\nu_{\mu}}(\phi^{(1)}) \\ \mathbb{M}_{\nu_{\mu}}(\phi^{(1)}) \\ \mathbb{M}_{\nu_{\mu}}(\phi^{(1)}) \\ \mathbb{M}_{\nu_{\mu}}(\phi^{(1)}) \end{array} \right)^{0} \left( \begin{array}{c} \mathbb{M}_{\nu_{\mu}}(\phi^{(1)}) \\ \mathbb{M}_{\nu}(\phi^{(1)}) \\$$

Figure 3.4: Red dashed lines denote the flow of current and  $\mathbb{M}_*(\phi^{(i)})$  represents the crossbar that computes the  $i^{th}$  clause of the Boolean formula  $\phi$ , which must be in either disjunctive normal form (top) or conjunctive normal form (bottom).

Figure 3.5: Network of crossbars method described in [3]. Here,  $S = (A \land \neg B \land \neg C) \lor (\neg A \land B \land \neg C) \lor (\neg A \land \neg B \land C) \lor (A \land B \land C)$  and  $C_{out} = (A \land B) \lor (A \land C) \lor (B \land C)$  are the sum and carry-out bits over inputs  $A, B, C \in \{0, 1\}$ , and  $f_4$  is a 4-bit parity function over inputs  $x_1, x_2, x_3, x_4 \in \{0, 1\}$ .

## **CHAPTER 4: PATHS-BASED LOGIC**

We begin by formalizing the rather intuitive notion of a crossbar. A pictorial representation of the definition below can be seen in Figure 4.1.

**Definition 1.** CROSSBAR An  $|R| \times |C|$  crossbar is a 3-tuple  $\mathcal{X} = (M, R, C)$  where

•  $M = \begin{pmatrix} M_{11} & M_{12} & \dots & M_{1|C|} \\ \vdots & \vdots & \ddots & \vdots \\ M_{|R|1} & M_{|R|2} & \dots & M_{|R||C|} \end{pmatrix}$  represents a matrix of interconnects with |R| rows and |C| columns.  $m_{ij} \in \{0, 1\}$  denotes the state of device  $M_{ij}$  connecting row i with column j.  $m_{ij} = 0$  ( $m_{ij} = 1$ ) denotes a device in the HRS (LRS) state.

- $R = \{R_1, \ldots, R_{|R|}\}$  is the set of row wires, where  $r_i \in \{0, 1\}$  provides the same input voltage to every interconnect in row  $R_i$ .  $r_i = 0$  ( $r_i = 1$ ) denotes the absence (presence) of electric current in wire  $R_i$ .

- $C = \{C_1, \ldots, C_{|C|}\}$  is the set of column wires, where  $c_j \in \{0, 1\}$  provides the same input voltage to every interconnect in column  $C_j$ .  $c_j = 0$  ( $c_j = 1$ ) denotes the absence (presence) of electric current in wire  $C_j$ .

For the remainder of this thesis, we utilize capital letters to signify wires and components and lowercase letters to denote their value. For example, we say that a wire  $W \in R \cup C$  has value w = 0 if there is negligible current on the wire and w = 1 if there is a significant amount.

### Irreducible Paths in Crossbars

It is clear that if there is an electric potential difference between two wires  $R_{\alpha}$  and  $R_{\beta}$ , then there must exist a sequence of interconnects that, when in the LRS state, would generate a current from  $R_{\alpha}$  to  $R_{\beta}$ . We refer to this sequence of nodes as a path. Any such path is represented by the ordered set  $\Pi^{R_{\alpha} \to R_{\beta}} = \{M_{\alpha j_1}, M_{i_1 j_1}, M_{i_1 j_2}, \dots, M_{i_k j_l}, M_{\beta j_l}\}$ , where each  $M \in \Pi^{R_{\alpha} \to R_{\beta}}$  is a constituent component in the path. It is obvious that the first node resides on wire  $R_{\alpha}$  and the last node must reside on  $R_{\beta}$ . For the sake of simplicity, we will assume that the source and destination of a path are both row wires.

**Definition 2** (Path). A path  $\Pi^{R_{\alpha} \to R_{\beta}} = \{M_{\alpha j_1}, M_{i_1 j_1}, M_{i_1 j_2}, \dots, M_{i_k j_l}, M_{\beta j_l}\}$  is an ordered set of nodes containing a source node  $M_{\alpha j_1}$  and a destination node  $M_{\beta j_l}$ .

**Axiom 1** (Flow Axioms). Let  $\mathcal{X} = (M, R, C)$  be an  $|R| \times |C|$  crossbar. Then the following always hold:

- $\forall i \leq |R|, j \leq |C|, (r_i \wedge m_{ij}) \implies c_j.$

- $\forall i \leq |R|, j \leq |C|, (c_j \wedge m_{ij}) \implies r_i.$

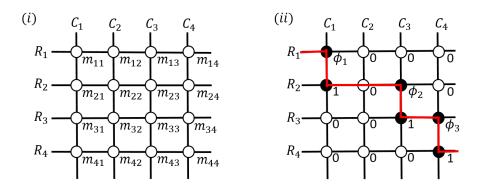

The basis of our approach lies in computing Boolean formula in a crossbar by mapping the variables of the formula to individual interconnects in the crossbar such that there will be a path of electric current between two wires if and only if the formula we wish to compute evaluates to 1. In Figure 4.1, bits  $\phi_1$ ,  $\phi_2$ , and  $\phi_3$  are mapped to  $M_{11}$ ,  $M_{23}$ , and  $M_{34}$ , respectively, while  $M_{21}$ ,  $M_{33}$ , and  $M_{44}$  are in the LRS state (i.e.  $m_{21} = m_{33} = m_{44} = 1$ ). Note that this mapping creates the path  $\Pi^{R_1 \to R_4} = \{M_{11}, M_{21}, M_{23}, M_{33}, M_{34}, M_{44}\}$  which directs flow from wire  $R_1$  to wire  $R_4$  iff  $\phi = (\phi_1 \land \phi_2 \land \phi_3) = 1$  given  $r_1 = 1$ , i.e. an initial flow of current on  $R_1$ .

Figure 4.1: (i)  $4 \times 4$  crossbar  $\mathcal{X} = (M, R, C)$ . (ii) Mapping of the formula  $\phi = (\phi_1 \wedge \phi_2 \wedge \phi_3)$  onto M, where  $R_1$  and  $R_4$  are the source and destination wires, respectively.

**Definition 3** (Irreducible Path). Let  $\tilde{\Pi}^{R_{\alpha} \to R_{\beta}}$  denote the set of all paths from  $R_{\alpha}$  to  $R_{\beta}$  in a crossbar.  $\Pi \in \tilde{\Pi}^{R_{\alpha} \to R_{\beta}}$  is an irreducible path if and only if  $\forall \Pi' \in \tilde{\Pi}^{R_{\alpha} \to R_{\beta}}, \Pi' \not\subset \Pi$ .

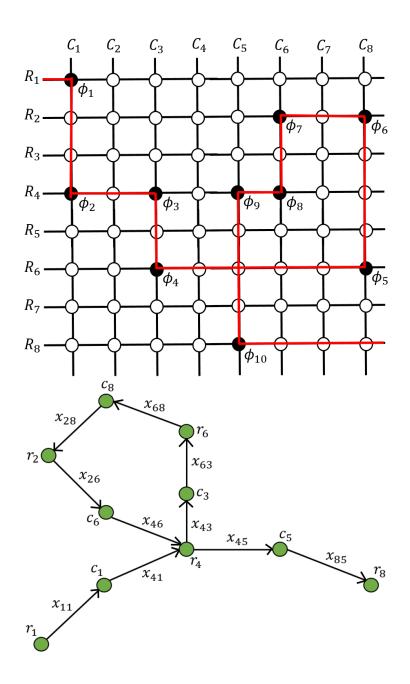

According to Definition 3, a path is irreducible if no other path with the same source and destination nodes is contained within it. See Fig. 4.2 for an example. Path  $\Pi^{R_1 \to R_8} = \{M_{11}, M_{41}, M_{43}, M_{63}, M_{68}, M_{28}, M_{26}, M_{46}, M_{45}, M_{85}\}$  is not an irreducible path because path  $\Pi' = \{M_{11}, M_{41}, M_{41}, M_{45}, M_{85}\}$  is contained within it. That is,  $\Pi' \subset \Pi^{R_1 \to R_8}$ .

Graphs can be used to represent paths in crossbars. The vertices in this graph represent the row and column wires while the edges correspond to the interconnects connecting these wires. The unweighted connected digraph G = (V, E) corresponding to  $\Pi^{R_1 \to R_8}$  is shown in Fig. 4.2b. We define  $\Pi_G^{R_1 \to R_8} = \{(R_1, C_1), (C_1, R_4), (R_4, C_3), (C_3, R_6), (R_6, C_8), (C_8, R_2), (R_2, C_6), (C_6, R_4),$  $(R_4, C_5), (C_5, R_8)\}$  as a path in the graph. Note that  $\Pi_G^{R_1 \to R_8}$  and  $\Pi^{R_1 \to R_8}$  are equivalent representations of the same path. We distinguish between the interconnect and edge representations  $\Pi = \{M_{ij}\}_{i,j}$  and  $\Pi_G = \{(R_i, C_j), (C_j, R_k)\}_{i,j,k}$  of a path  $\Pi$  by adding the subscript G. Note that the graph formed by  $\Pi_G^{R_1 \to R_8}$  has a cycle consisting of the edges in  $\Pi_G^{R_1 \to R_8} \setminus \Pi'_G$ . Furthermore, the irreducible path  $\Pi'_G = \{(R_1, C_1), (C_1, R_4), (R_4, C_5), (C_5, R_8)\}$  contains no cycles.

Figure 4.2: (top)  $8 \times 8$  crossbar mapping the formula  $\phi = (\phi_1 \wedge \phi_2 \wedge \phi_9 \wedge \phi_{10})$ . The red bars represent the path  $\Pi^{R_1 \to R_8} = \{M_{11}, M_{41}, M_{43}, M_{63}, M_{68}, M_{28}, M_{26}, M_{46}, M_{45}, M_{85}\}$  corresponding to  $\bigwedge_{i=1}^{10} \phi_i$ . (bottom) Equivalent representation of  $\Pi^{R_1 \to R_8}$  as a graph given by  $\Pi^{R_1 \to R_8}_{G} = \{(R_1, C_1), (C_1, R_4), (R_4, C_3), (C_3, R_6), (R_6, C_8), (C_8, R_2), (R_2, C_6), (C_6, R_4), (R_4, C_5), (C_5, R_8)\}$ , where  $(R_i, C_j) \in \Pi^{R_1 \to R_8}_{G}$  denotes a directed edge from  $R_i$  to  $C_j$ .

**Theorem 1.** A path  $\Pi^{R_{\alpha} \to R_{\beta}}$  in an  $|R| \times |C|$  crossbar  $\mathcal{X} = \{M, R, C\}$  is reducible if and only if  $\Pi_{G}^{R_{\alpha} \to R_{\beta}}$  contains a cycle.

*Proof.* ( $\implies$ ) We argue the contrapositive. Let  $\Pi_G^{R_\alpha \to R_\beta} = \{(R_\alpha, C_{j_1}), (C_{j_1}, R_{i_1}), \dots, (R_{i_k}, C_{j_l}), (C_{j_l}, R_\beta)\}$ . Since there are no cycles,  $\Pi_G^{R_\alpha \to R_\beta}$  is a minimally connected graph i.e. the out- and in-degrees of all nodes are at most 1. Thus, by definition of minimally connected graphs, there is only one path between any two nodes. It follows that there is only one path from  $R_\alpha$  to  $R_\beta$  in the graph formed by  $\Pi_G^{R_\alpha \to R_\beta}$ . Therefore, the path is irreducible.

(  $\Leftarrow$  ) Suppose, without loss of generality, that  $\Pi = \{M_{i_1j_1}, M_{i_2j_1}, M_{i_2j_2}, \dots, M_{i\alpha_1}, M_{i\alpha_2}, \dots, M_{i\alpha_3}, M_{i\alpha_4}, \dots, M_{i\alpha_{2k-1}}, M_{i\alpha_{2k}}, \dots\}$  is an irreducible path containing a cycle(s). We can construct  $\Pi' = \Pi \setminus \{M_{i\alpha_2}, \dots, M_{i\alpha_{2k-1}}\} \subset \Pi$ . Thus, since  $\Pi' \subset \Pi$ ,  $\Pi$  violates the irreducible paths property, a contradiction. Thus, paths that contain cycles are reducible.  $\Box$

A reducible path will carry a flow of current from its source to its destination wire whenever the irreducible path contained in it can carry a flow of current from the source to the destination. Thus, the presence of reducible paths in crossbar designs does not permit the crossbar to compute new Boolean formula.

**Corollary 1.** A crossbar design using only irreducible paths and a crossbar design using all paths can evaluate the same set of Boolean formula.

*Proof.* It follows from *Theorem 1* that reducible paths have cycles and irreducible paths do not. Suppose we are given an *n*-ary Boolean formula  $\phi(\phi_1, \ldots, \phi_n)$  and paths  $\Pi^{R_\alpha \to R_\beta}$  and  $\Pi'^{R_\alpha \to R_\beta}$ , such that  $\Pi'^{R_\alpha \to R_\beta} \subset \Pi^{R_\alpha \to R_\beta}$ . In the context of our framework, we say that  $\phi$  evaluates to true if and only if there is a path  $\Pi^{R_\alpha \to R_\beta}$  from  $R_\alpha$  to  $R_\beta$  or, equivalently, if  $\Pi^{R_\alpha \to R_\beta}_G$  contains a connected walk from  $R_\alpha$  to  $R_\beta$ . Since the inclusion or exclusion of edges in a cycle does not affect the connectedness of the walk in the graph, it follows that  $\Pi^{R_{\alpha} \to R_{\beta}}$  is a connected walk if  $\Pi'^{R_{\alpha} \to R_{\beta}}$ is a connected walk from  $R_{\alpha}$  to  $R_{\beta}$ .

Since reducible paths do not add to the expressive power of crossbars, our synthesis technique relies on searching through the space of irreducible paths only. This allows us to prune the search space of our approach substantially by ignoring the redundant reducible paths.

**Theorem 2.** A path  $\Pi^{R_{\alpha} \to R_{\beta}}$  forms a cycle if and only if there are more than two nodes in the path that reside on the same wire in the crossbar.

*Proof.* ( $\implies$ ) Assume that  $\Pi_G^{R_\alpha \to R_\beta} = \{(R_i, C_j), (C_j, R_k)\}_{i,j,k}$  contains a cycle. It follows from *Definition 1* that  $(R_\alpha, C_{i_1})$  is the only outgoing edge from  $R_\alpha$  and  $(C_{i_k}, R_\beta)$  is the only incoming edge to  $R_\beta$ . Since  $\Pi_G^{R_\alpha \to R_\beta}$  forms a cyclic connected digraph, and  $R_\alpha$  and  $R_\beta$  cannot be nodes in a cycle, there must exist some node  $R_i$  that belongs to a cycle as well as to a simple walk from  $R_\alpha$  to  $R_\beta$ . It follows that there exist edges  $(C_{j_1}, R_i)$  and  $(R_i, C_{j_2})$  connecting  $R_i$  to the simple walk from  $R_\alpha$  to  $R_\beta$  and edges  $(C_{j_3}, R_i)$  and  $(R_i, C_{j_4})$  connecting  $R_i$  to the cycle. See node  $R_4$  in Figure 4.2b for an example. These edges correspond to interconnects  $M_{ij_1}$ ,  $M_{ij_2}$ ,  $M_{ij_3}$ , and  $M_{ij_4}$  in  $\Pi^{R_\alpha \to R_\beta}$ , leading to more than two nodes on the same wire.

(  $\Leftarrow$  ) Without loss of generality, assume that  $\Pi^{R_{\alpha} \to R_{\beta}} = \{M_{\alpha j_1}, M_{i_1 j_1}, M_{i_2 j_1}, M_{i_2 j_2}, \dots, M_{i' p_1}, M_{i' p_2}, \dots, M_{i' p_2}, \dots, M_{j' p_2}, \dots, M_{\beta c_l}\}$  has more than two nodes on  $R_{i'}$ . Note that for all  $R_i \neq R_{i'}$ , the out- and in-degrees are 1, while the out- and in-degrees of  $R_{i'}$  are greater than or equal to 2. Since  $R_{\alpha}$  is the only node with no incoming edges,  $R_{\beta}$  is the only node with no outgoing edges, and all paths form connected digraphs, it follows that node  $R_{i'}$  must be in a cycle.

**Corollary 2.** A path  $\Pi$  is irreducible if and only if there are no more than two nodes on any wire.

We now have the foundations necessary to enumerate irreducible paths in a crossbar. The length and number of such paths is discussed below.

**Lemma 1.** The maximum length  $|\Pi^{R_{\alpha} \to R_{\beta}}|_{max}$  of an irreducible path  $\Pi^{R_{\alpha} \to R_{\beta}} = \{M_{\alpha j_1}, M_{i_1 j_1}, M_{i_1 j_2}, \dots, M_{i_k j_l}, M_{\beta j_l}\}$  in an  $|R| \times |C|$  crossbar  $\mathcal{X} = (M, R, C)$  is  $2(\min\{|R| - 1, |C|\})$ .

*Proof.* It follows from *Definition 1* that  $M_{\alpha j_1}$  and  $M_{\beta j_l}$  are in the path and are the only nodes on  $R_{\alpha}$  and  $R_{\beta}$ , respectively. Let  $R' = R \setminus \{R_{\alpha}, R_{\beta}\}$  denote the set of remaining rows, where nodes of  $\Pi^{R_{\alpha} \to R_{\beta}}$  reside. Note that |R'| = |R| - 2. It follows from *Corollary 1* that there can only be up to two nodes per wire. Two cases arise:

- Case 1 ( $|C| \ge |R| 1$ ): Each row in R' can have two nodes. Thus,  $|\Pi^{R_{\alpha} \to R_{\beta}}|_{\max} = 2|R'| + 2 = 2(|R| 2) + 2 = 2(|R| 1).$

- Case 2 (|C| < |R|-1): Assigning two nodes to each column yields |Π<sup>R<sub>α</sub>→R<sub>β</sub></sup>|<sub>max</sub> = 2|C| and it follows from *case 1* that assigning two nodes to each row yields |Π<sup>R<sub>α</sub>→R<sub>β</sub></sup>|<sub>max</sub> = 2(|R|-1). However, since |C| < |R|-1, it is not possible to have an irreducible path of length 2(|R|-1) as this would require some column to contain more than two nodes, thereby violating the irreducible paths property. Thus, |Π<sup>R<sub>α</sub>→R<sub>β</sub></sup>|<sub>max</sub> = 2|C|.

**Theorem 3.** There are  $\frac{|C|!(|R|-2)!}{(|C|-k/2)!(|R|-1-k/2)!}$  irreducible paths of length k from  $R_{\alpha}$  to  $R_{\beta}$  in an  $|R| \times |C|$  crossbar.

*Proof.* Let  $f^{(k)}$  denote the number of k-length paths and  $\tilde{\Pi}^{(k)}$  denote the set of said paths. For k = 2,  $\tilde{\Pi}^{(k)} = \{(M_{\alpha j}, M_{\beta j})\}_{j=1}^{|C|}$  for source  $R_{\alpha}$  and destination  $R_{\beta}$ . Thus,  $f^{(2)} = |C|$ . For  $k = 4, 6, \ldots, |\Pi^{R_{\alpha} \to R_{\beta}}|_{\text{max}}$ , there are k - 1 possibilities for choosing row and column coordinates of the nodes in the path. Since our initial and final choices of row coordinate are fixed to the source and destination wires  $R_{\alpha}$  and  $R_{\beta}$ , there will be one more choice of column coordinate than

row coordinate. There are  $\left\{ {|R|-2 \atop k/2-1} \right\}$  ways to choose row coordinates and  $\left\{ {|C| \atop k/2} \right\}$  ways to choose column coordinates, where  $\left\{ {|C| \atop k} \right\}$  denotes the permutation of k elements from a |C|-element set. Thus, we have  $f^{(k)} = \left\{ {|C| \atop k/2} \right\} \left\{ {|R|-2 \atop k/2-1} \right\} = \frac{|C|!(|R|-2)!}{(|C|-k/2)!(|R|-1-k/2)!}$ .

Base case: Paths of length 2.

$$f^{(2)} = \frac{|C|!(|R|-2)!}{(|C|-1)!(|R|-2)!} = |C|$$

Inductive hypothesis: Paths of length k.

$$f^{(k)} = \frac{|C|!(|R|-2)!}{(|C|-k/2)!(|R|-1-k/2)!}$$

*Inductive step*: Note that, given the value of  $f^{(k)}$  for any k, there will be (|R| - 2) - (k/2 - 1) = |R| - 1 - k/2 possible row choices and |C| - k/2 possible column choices for a (k + 2)-length path. Therefore,

$$f^{(k+2)} = f^{(k)}(|C| - k/2)(|R| - 1 - k/2)$$

=

$$\frac{|C|!(|R| - 2)!}{(|C| - k/2)!(|R| - 1 - k/2)!}(|C| - k/2)(|R| - 1 - k/2)$$

=

$$\frac{|C|!(|R| - 2)!}{(|C| - k/2 - 1)!(|R| - k/2 - 2)!}$$

=

$$\frac{|C|!(|R| - 2)!}{(|C| - \frac{k+2}{2})!(|R| - 1 - \frac{k+2}{2})!}$$

Hence, proved by mathematical induction.

**Corollary 3.** The number of irreducible paths from  $R_{\alpha}$  to  $R_{\beta}$  in an  $|R| \times |C|$  crossbar is  $T(|R|, |C|) = \sum_{k=1}^{\min\{|R|-1,|C|\}} {|C| \atop k} {|C| \atop k-1}$ , where  ${|C| \atop k}$  denotes the permutation of k elements from an |C|-element set.

*Proof.* Recall that  $|\Pi^{R_{\alpha} \to R_{\beta}}|_{\text{max}}$  denotes the maximum length of a path from  $R_{\alpha}$  to  $R_{\beta}$ . It follows directly from *Theorem 3* and *Lemma 1* that the total number of irreducible paths is

$$\sum_{k=2, k \text{ even}}^{|\Pi^{R_{\alpha} \to R_{\beta}}|_{\text{max}}} f^{(k)} = \sum_{k=2, k \text{ even}}^{|\Pi^{R_{\alpha} \to R_{\beta}}|_{\text{max}}} \frac{|C|!(|R|-2)!}{(|C|-k/2)!(|R|-1-k/2)!}$$

$$= \sum_{k=1}^{|\Pi^{R_{\alpha} \to R_{\beta}}|_{\text{max}/2}} \frac{|C|!(|R|-2)!}{(|C|-k)!(|R|-1-k)!} \cdot$$

$$= \sum_{k=1}^{\min\{|R|-1,|C|\}} \left\{ |C| \atop k \right\} \left\{ |R|-2 \atop k-1 \right\} = T(|R|,|C|)$$

The number of paths established in the preceding corollary grows rapidly in tandem with the size of the crossbar. While this enormous number of potential paths of current through the crossbar presents a great opportunity for the design of compact computing crossbars, it also poses a considerable obstacle to the invention of spatially-efficient designs via human reasoning. Hence, we suggest the use of automated synthesis techniques for designing nanoscale crossbars for computing Boolean formula.

## Universality of Paths-Based Logic

An *n*-ary Boolean function maps an *n*-tuple of Boolean values to a Boolean value. It can be defined by a truth table of  $2^n$  rows, one for each possible value an *n*-tuple may take. Alternatively and more concisely, it can be defined in terms of a few Boolean operators or connectives. A set of Boolean connectives is complete if every Boolean function can be defined by an expression that uses only the connectives in that set. The set consisting of the  $\neg$  (negation),  $\land$  (conjunction), and  $\lor$  (disjunction) connectives is complete. So any Boolean function can be defined by a well-formed

formula (wff) constructed as follows: (i) a Boolean (propositional) variable p is a wff; (ii) if  $\phi$  is a wff,  $\neg \phi$  is a wff; (iii) if  $\phi_1$  and  $\phi_2$  are wffs,  $\phi_1 \land \phi_2$  is a wff, and (iv) if  $\phi_1$  and  $\phi_2$  are wffs,  $\phi_1 \lor \phi_2$  a wff.

Our method to prove the universality of paths-based logic requires the formulas to be in negation normal form (NFF), which is defined by a slight change to these rules. The negation connective may not be applied to an arbitrary wff, but only to a propositional variable. A formula is in negation normal form if it is constructed as follows: (*i*) a literal, that is, a propositional variable p or  $\neg p$ , is in NNF, (*ii*) if  $\phi_1$  and  $\phi_2$  are in NNF,  $\phi_1 \land \phi_2$  is in NNF, and (*iii*) if  $\phi_1$  and  $\phi_2$  are in NNF,  $\phi_1 \lor \phi_2$ is in NNF.

Any wff constructed using only connectives  $\neg$ ,  $\wedge$  and  $\vee$  can be transformed into an equivalent formula in negation normal form by repeatedly applying the De Morgan Laws:  $\neg(p \wedge q) \equiv \neg p \vee \neg q$ , and  $\neg(p \vee q) \equiv \neg p \wedge \neg q$ , and simplifying  $\neg \neg p$  to p. Thus, the method presented below can be used to evaluate any Boolean function.

Let  $\phi$  be a Boolean formula in negation normal form. We define the state of an  $|R| \times |C|$  memristor crossbar  $M_{\phi}$  as follows, where  $R^i, C^i$  denote row/column wires of  $M_{\phi_i}$  when there are two formulas  $\phi_1, \phi_2$ .

• Literal: For  $\phi = a$ , a literal, we have

$$M_a = \left(\begin{array}{c} a\\ 1 \end{array}\right)$$

. .

Conjunction: For φ = φ<sub>1</sub> ∧ φ<sub>2</sub>, the array has |R<sup>1</sup>| + |R<sup>2</sup>| - 1 rows, where M<sub>φ1</sub> and M<sub>φ2</sub> share row R<sub>|R<sup>1</sup>|</sub>, and |C<sup>1</sup>| + |C<sup>2</sup>| columns. It is defined by:

$$\mathbb{M}_{\phi_1 \land \phi_2} = \begin{pmatrix} \begin{pmatrix} & & & \\ & M_{\phi_1} & \\ & & \end{pmatrix} & \begin{array}{cccc} 0 & \cdots & 0 \\ & & \ddots & \vdots \\ 0 & \cdots & 0 & \\ \vdots & \ddots & \vdots \\ 0 & \cdots & 0 & \begin{pmatrix} & & & \\ & M_{\phi_2} & \\ & & & \end{pmatrix} \end{pmatrix}$$

Disjunction: For φ = φ₁ ∨ φ₂, the array has |R<sup>1</sup>| + |R<sup>2</sup>| rows and |C<sup>1</sup>| + |C<sup>2</sup>| + 2 columns, and is defined by:

$$\mathbb{M}_{\phi_1 \vee \phi_2} = \begin{pmatrix} 1 & & & \\ 0 & & & \\ \vdots & & M_{\phi_1} & \\ 0 & & & 0 & 0 & \\ 0 & 0 & \cdots & 0 & \\ 1 & 0 & \cdots & 0 & \\ \vdots & \vdots & \ddots & \vdots & \\ 0 & 0 & \cdots & 0 & \\ \vdots & \vdots & \ddots & \vdots & \\ 0 & 0 & \cdots & 0 & \\ \end{pmatrix} \begin{pmatrix} 0 & \cdots & 0 & 0 \\ 0 & \cdots & 0 & 1 \\ M_{\phi_2} & & 0 \\ 0 & 1 \end{pmatrix}$$

The array  $M_{\phi}$  is an operator on the wires it intersects. To compute the value of  $\phi$ , it must be applied to a set of wires in which only the first (or top) row  $R_1$  is in state  $r_1 = 1$ . That is, there is a flow of current along that wire.

We prove that given a crossbar in the state just described, which is induced by the formula  $\phi$ , there exists a path that takes current from the first (or top) row  $R_1$  to the last (or bottom) row  $R_{|R|}$  if and only if  $\phi = 1$ .

**Theorem 4.** CROSSBAR COMPUTATION OF NNFS Let  $\mathcal{X} = (M, R, C)$  be a crossbar mapping  $\phi \in NNF$ . If  $r_1 = 1$ , then a sneak current will reach  $R_{|R|} \in R$  iff  $\phi = 1$ .

*Proof.* The proof is by structural induction on the negation normal form  $\phi$ . We prove that given a

crossbar state where  $r_1 = 1$ , a crossbar configuration  $M_{\phi}$  creates a path that takes the wire  $R_{|R|}$  to have flow if and only if  $\phi = 1$ .

Base case: literal.  $\phi \equiv a$ . Note that  $((r_1 \wedge m_{11}) \implies c_1) \wedge (c_1 \wedge m_{21} \implies r_2)$ . Thus, for  $m_{11} = a = 1$ , we have  $a \implies r_2$ . If  $m_{11} = a = 0$ , there is no path from  $R_1$  to  $R_2$  s.t.  $r_2 = 1$ .

Inductive step: conjunction.  $\phi \equiv \phi_1 \wedge \phi_2$ . We want to prove that  $\phi_1 \wedge \phi_2 \iff r_{|R^1|+|R^2|-1}$ . Note that  $M_{\phi_1}$  and  $M_{\phi_2}$  share wire  $R_{|R^1|}$ , which is the output wire of  $M_{\phi_1}$ . Thus, from the inductive hypothesis we have  $r_{|R^1|} \iff \phi_1$ .  $R_{|R^1|}$  is also the input wire to  $M_{\phi_2}$ . It follows that  $r_{|R^1|+|R^2|-1} \iff r_{|R^1|} \wedge \phi_2 \iff \phi_1 \wedge \phi_2$ .

Inductive step: disjunction.  $\phi \equiv \phi_1 \lor \phi_2$ . We want to prove that  $\phi_1 \lor \phi_2 \iff r_{|R^1|+|R^2|}$ .

$(\implies)$ : Suppose  $\phi_1 = 1$ . From the inductive hypothesis, we have  $r_{|R^1|} = 1$ . The implications  $(r_{|R^1|} \land m_{|R^1|,|C^1|+|C^2|+2} \implies c_{|C^1|+|C^2|+2}), (c_{|C^1|+|C^2|+2} \land m_{|R^1|+|R^2|,|C^1|+|C^2|+2} \implies r_{|R^1|+|R^2|})$ hold. Therefore,  $\phi_1 \implies r_{|R^1|+|R^2|}$ . Now, suppose  $\phi_2 = 1$ . A similar chain of implications holds. Namely, it follows that  $(r_1 \land m_{11} \implies c_1) \land (c_1 \land m_{|R^1|+1} \implies r_{|R^1|+1})$ . Since  $R_{|R^1|+1}$  is the input wire to  $M_{\phi_2}$ , it follows that  $\phi_2 \implies r_{|R^1|+|R^2|}$ .

( $\Leftarrow$ ): We prove the contrapositive. That is, we prove that  $\neg \phi_1 \land \neg \phi_2 \implies \neg r_{|R^1|+|R^2|}$ . We know from the preceding argument and the inductive hypothesis that  $r_{|R^1|} \iff \phi_1$  and  $\phi_2 \implies r_{|R^1|+|R^2|}$ . Therefore, we must show that  $r_{|R^1|+|R^2|} \implies \phi_2$  when  $\phi_1 = 0$ , which follows from the inductive hypothesis. Thus, we have  $r_{|R^1|+|R^2|} = 0$ .

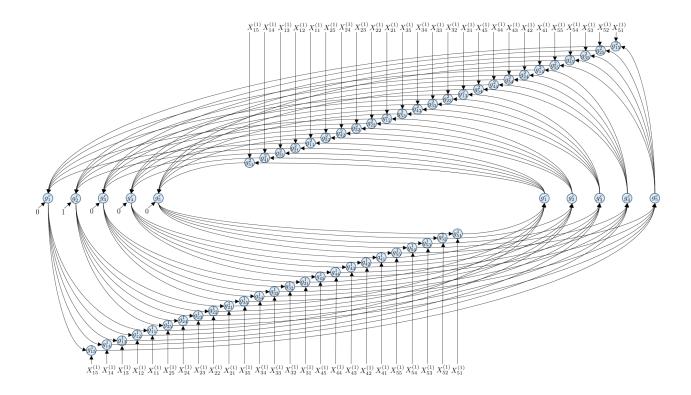

Some examples of Boolean formulas mapped using this inductive design can be seen in Figure 4.3. For the case of a 1-bit adder, the sum bit S can be expressed by the formula  $S = (A \land \neg B \land \neg C) \lor$  $(\neg A \land B \land \neg C) \lor (\neg A \land \neg B \land C) \lor (A \land B \land C)$ . Its crossbar design can be seen in Figure 4.4.

This construction suffices to evaluate Boolean formula. However, in the spirit of parsimony, we

Figure 4.3: Memristor crossbars using our NNF construction for Boolean formulas  $(A \land B)$  (left),  $(A \lor B)$  (center),  $A \oplus B \equiv (A \lor B) \land (\neg A \lor \neg B)$  (right), where A = B = 1 and the source and destination wires are  $R_1$  and  $R_{|R|}$ , respectively.