# Scholars' Mine

**Doctoral Dissertations**

Student Theses and Dissertations

Spring 2014

# Hardware integration of ultracapacitor based energy storage to provide grid support and to improve power quality of the distribution grid

Deepak Somayajula

Follow this and additional works at: https://scholarsmine.mst.edu/doctoral\_dissertations

Part of the Electrical and Computer Engineering Commons

**Department: Electrical and Computer Engineering**

### **Recommended Citation**

Somayajula, Deepak, "Hardware integration of ultracapacitor based energy storage to provide grid support and to improve power quality of the distribution grid" (2014). Doctoral Dissertations. 2184. https://scholarsmine.mst.edu/doctoral\_dissertations/2184

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# HARDWARE INTEGRATION OF ULTRACAPACITOR BASED ENERGY STORAGE TO PROVIDE GRID SUPPORT AND TO IMPROVE POWER QUALITY OF THE DISTRIBUTION GRID

by

### **DEEPAK SOMAYAJULA**

### **A DISSERTATION**

Presented to the Faculty of the Graduate School of the

MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

DOCTOR OF PHILOSOPHY

in

**ELECTRICAL ENGINEERING**

2014

Approved by

Mariesa L. Crow, Advisor Badrul H. Chowdhury Bruce M. McMillin Mehdi Ferdowsi Jonathan W. Kimball

### PUBLICATION DISSERTATION OPTION

This dissertation has been prepared in the form of three papers for publication. The first paper consisting of pages 4 to 39 has been submitted to *IEEE Transactions on Sustainable Energy*. The second paper consisting of pages 40 to 65 has been submitted to *IEEE Transactions on Power Delivery*. The third paper consisting of pages 66 to 91 has been submitted to *IEEE Transactions on Sustainable Energy*.

### **ABSTRACT**

Grid integration of distributed energy resources (DERs) is increasing rapidly. Integration of various types of energy storage technologies like batteries, ultracapacitors (UCAPs), superconducting magnets and flywheels to support intermittent DERs, such as solar and wind, in order to improve their reliability is becoming necessary. Of all the energy storage technologies UCAPs have low energy density, high power density and fast charge/discharge characteristics. They also have more charge/discharge cycles and higher terminal voltage per module when compared to batteries. All these characteristics make UCAPs ideal choice for providing support to events on the distribution grid which require high power for short spans of time. UCAPs have traditionally been limited to regenerative braking and wind power smoothing applications.

The major contribution of this dissertation is in integrating UCAPs for a broader range of applications like active/reactive power support, renewable intermittency smoothing, voltage sag/swell compensation and power quality conditioning to the distribution grid. Renewable intermittency smoothing is an application which requires bidirectional transfer of power from the grid to the UCAPs and vice-versa by charging and discharging the UCAPs. This application requires high active power support in the 10s-3min time scale which can be achieved by integrating UCAPs through a shunt active power filter (APF) which can also be used to provide active/reactive power support. Temporary voltage sag/swell compensation is another application which requires high active power support in the 3s-1min time scale which can be provided integrating UCAPs into the grid through series dynamic voltage restorer (DVR). All the above functionalities can also be provided by integrating the UCAPs into a power conditioner topology.

### **ACKNOWLEDGEMENTS**

Firstly I thank my advisor, Dr. Mariesa Crow for giving me the opportunity to work on the project, and for allowing me to pursue research with complete freedom. Her support was instrumental in changing my thought process and her style of working helped me inculcate a new style of thinking in terms of research in particular and life in general. I would also like to thank my committee members Dr. Badrul Chowdhury, Dr. Mehdi Ferdowsi, Dr. Jonathan Kimball, Dr. Bruce McMillin for taking their time to review the dissertation and Dr. Stan Atcitty for his valuable inputs on the topic. I sincerely thank all my teachers from all walks of life for imparting their knowledge.

I would like to thank the academic and non-academic staff of Missouri S&T and Department of Electrical Engineering for their support. I would like to thank my various lab mates for maintaining a cordial working relationship. Thanks to all my friends who have been like my family while away from family. A special thanks to few of my close friends Raghu, Pramod, Brijesh, Madhu, Ramesh, Neelanjana, Ravi, Praneeth, Srikanth, Hossein, Mostafa, Andrew, Anand and Darshith for all the friendly gestures.

I'm deeply indebted to Hariharananda Gurukulam for giving me an opportunity to learn and practice an ancient scientific meditation technique and for shaping my philosophical outlook. Both of which were extremely useful while I pursued my doctoral studies. My love goes to my mother Mrs. Lakshmi Somayajula and my father Mr. Rama Rao Somayajula for all the sacrifices they had to make so that I could pursue my dreams with complete freedom. I'm deeply indebted to my loving sister Anusha and my brotherin law Rohit for their encouragement. Lastly, I bow and dedicate this effort to all the great minds who have contributed to the welfare of humanity throughout history.

# TABLE OF CONTENTS

|      |      | F                                                                                                                                      | age   |

|------|------|----------------------------------------------------------------------------------------------------------------------------------------|-------|

| PUBI | LIC  | ATION DISSERTATION OPTION                                                                                                              | iii   |

| ABS  | ΓRA  | ACT                                                                                                                                    | iv    |

| ACK  | NO   | WLEDGEMENTS                                                                                                                            | v     |

| LIST | OF   | ILLUSTRATIONS                                                                                                                          | ix    |

| LIST | OF   | TABLES                                                                                                                                 | . xii |

| NOM  | EN   | CLATURE                                                                                                                                | xiii  |

| SECT | [OI  | N                                                                                                                                      |       |

| 1.   |      | INTRODUCTION                                                                                                                           | 1     |

| PAPE | ER   |                                                                                                                                        |       |

|      |      | ntegrated Active Power Filter–Ultracapacitor Design to Provide Intemittency othing and Reactive Power Support to the Distribution Grid |       |

| A    | Abst | ract                                                                                                                                   |       |

| I.   |      | INTRODUCTION                                                                                                                           | 4     |

| II.  |      | THREE-PHASE GRID CONNECTED INVERTER                                                                                                    | 7     |

|      | A.   | Power Stage                                                                                                                            | 8     |

|      | B.   | Controller Implementation                                                                                                              | 9     |

| III. | •    | UCAP AND BIDIRECTIONAL DC-DC CONVERTER                                                                                                 | . 12  |

|      | A.   | UCAP Bank Hardware Setup                                                                                                               | . 12  |

|      | B.   | Bi-directional Dc-dc Converter Hardware Setup                                                                                          | . 14  |

|      | C.   | Controller Implementation                                                                                                              | . 15  |

|      | D.   | Higher Level Integrated Controller                                                                                                     | . 20  |

| IV   |      | SIMULATION RESULTS                                                                                                                     | . 22  |

| V.   |      | EXPERIMENTAL RESULTS                                                                                                                   | . 27  |

| VI   |      | CONCLUSION                                                                                                                             | . 36  |

| RE   | EFE  | RENCES                                                                                                                                 | 37    |

| PAPE | ER   |                                                                                                                                        |       |

|      |      | ntegrated Dynamic Voltage Restorer–Ultracapacitor Design for Improving Power Quality of the Distribution Grid                          | 40    |

| A    | Abst | ract                                                                                                                                   | 40    |

| I    | •          | INTRODUCTION                                                                                                         | 40 |

|------|------------|----------------------------------------------------------------------------------------------------------------------|----|

| Ι    | I.         | THREE-PHASE SERIES INVERTER                                                                                          | 43 |

|      | A.         | Power Stage                                                                                                          | 43 |

|      | B.         | Controller Implementation                                                                                            | 45 |

| I    | II.        | UCAP AND BI-DIRECTIONAL DC-DC CONVERTER                                                                              | 47 |

|      | A.         | UCAP Bank Hardware Setup                                                                                             | 47 |

|      | B.         | Bi-directional Dc-dc Converter and Controller                                                                        | 47 |

| Ι    | V.         | SIMULATION RESULTS                                                                                                   | 49 |

| 7    | <i>J</i> . | EXPERIMENTAL RESULTS                                                                                                 | 56 |

| 7    | /I.        | CONCLUSION                                                                                                           | 62 |

| F    | REFE       | RENCES                                                                                                               | 63 |

| PAI  | PER        |                                                                                                                      |    |

| III. |            | UltracapacitorIntegrated Power Conditioner for Reducing Intermittencies Improving Power Quality of Distribution Grid | 66 |

|      | Abst       | ract                                                                                                                 | 66 |

| I    |            | INTRODUCTION                                                                                                         | 66 |

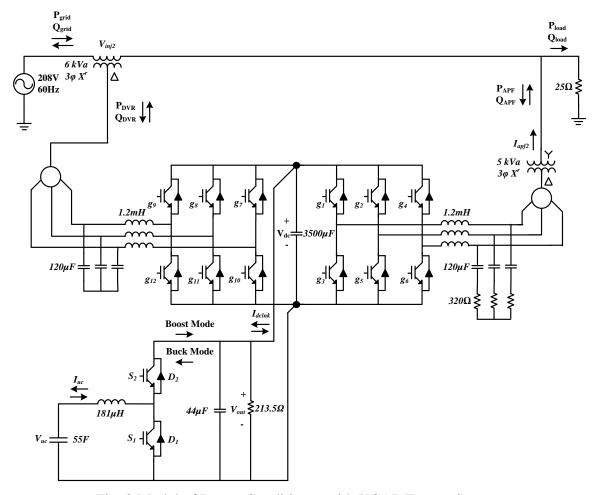

| I    | I.         | THREE-PHASE INVERTERS                                                                                                | 69 |

|      | A.         | Power Stage                                                                                                          | 69 |

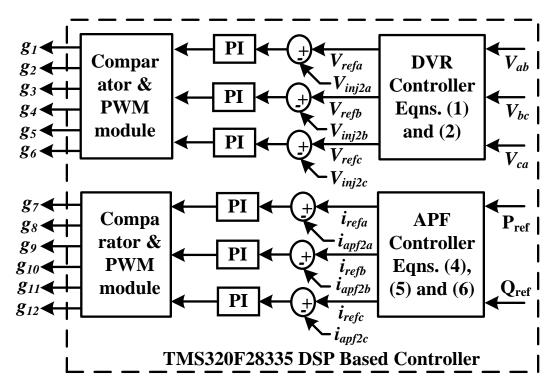

|      | B.         | Controller Implementation                                                                                            | 71 |

| I    | II.        | UCAP AND BI-DIRECTIONAL DC-DC CONVERTER                                                                              | 73 |

|      | A.         | UCAP Bank Hardware Setup                                                                                             | 73 |

|      | B.         | Bi-directional Dc-dc Converter and Controller                                                                        | 74 |

| Ι    | V.         | SIMULATION RESULTS                                                                                                   | 75 |

| 7    | <i>I</i> . | EXPERIMENTAL RESULTS                                                                                                 | 81 |

| 7    | /I.        | CONCLUSION                                                                                                           | 88 |

| F    | REFE       | RENCES                                                                                                               | 89 |

| S    | SECT       | ION                                                                                                                  |    |

| 2    | 2.         | CONCLUSION                                                                                                           | 92 |

| 3    | 3.         | FUTURE WORK                                                                                                          | 94 |

| A    | APPE       | NDICES                                                                                                               |    |

| A    | Α.         | THREE-PHASE PLL IMPLEMENTATION                                                                                       | 95 |

| F    | 3          | EMBEDDED C CONTROLLER CODE FOR DSP                                                                                   | 98 |

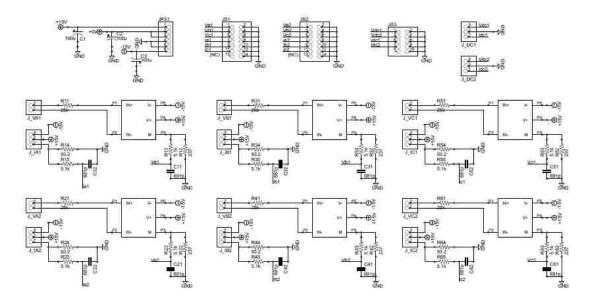

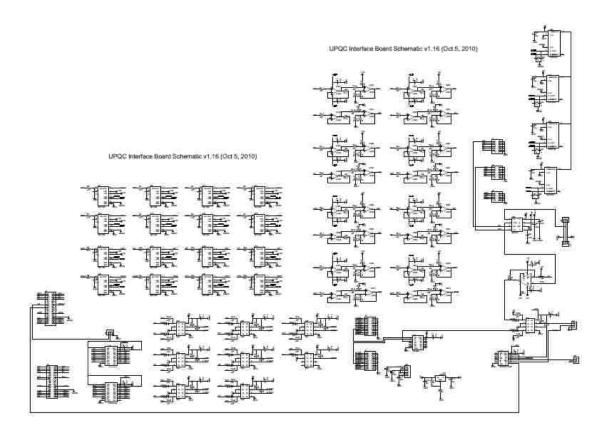

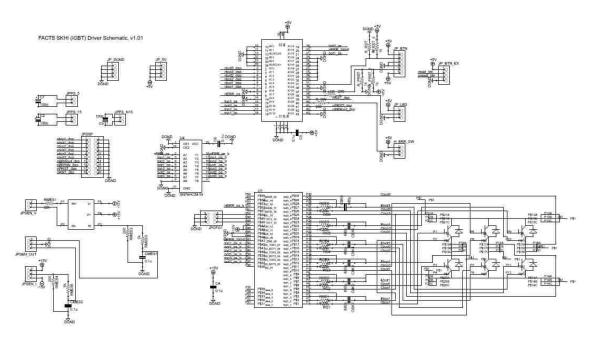

|   | C.    | SCHEMATICS FOR PCB BOARD DESIGN | 109 |

|---|-------|---------------------------------|-----|

|   | REFEI | RENCES                          | 113 |

| V | ITA   |                                 | 114 |

# LIST OF ILLUSTRATIONS

| Page                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Paper I                                                                                                                                                                                   |

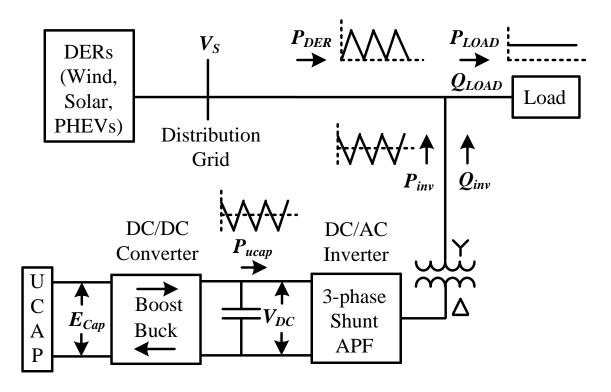

| Fig. 1 One line diagram of the APF-UCAP system                                                                                                                                            |

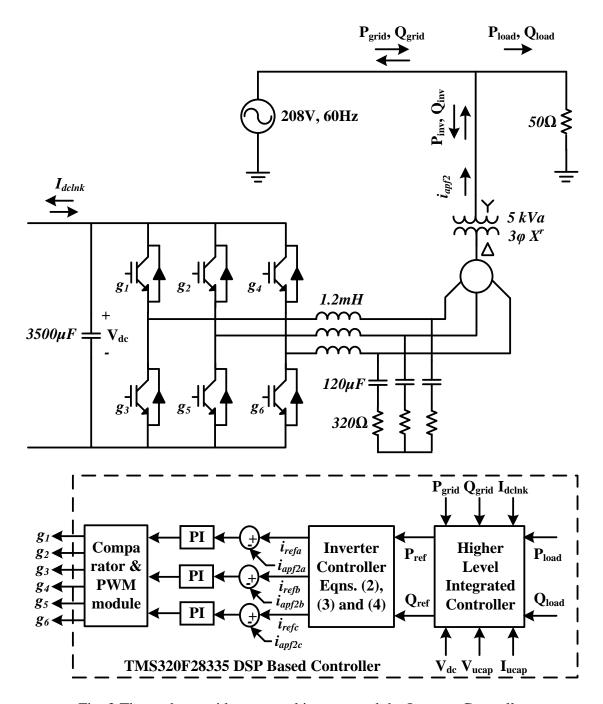

| Fig. 2 Three-phase grid-connected inverter and the Inverter Controller 10                                                                                                                 |

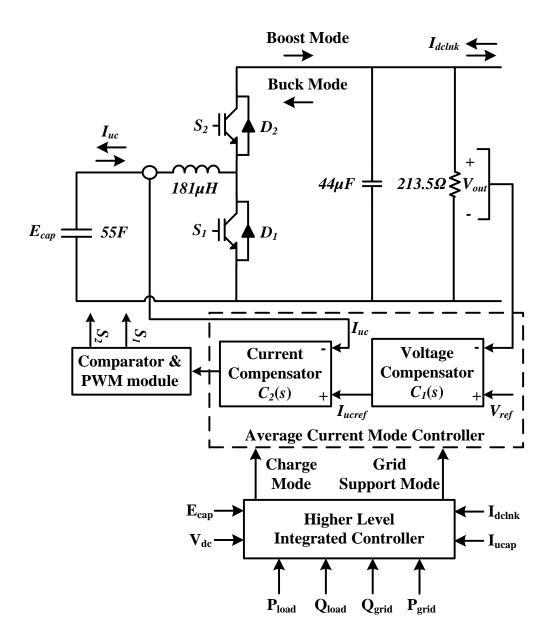

| Fig. 3 (a) Model of the bi-directional dc-dc converter and its controller                                                                                                                 |

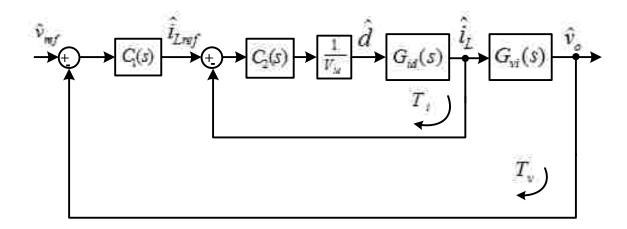

| Fig. 3 (b) Block diagram of closed-loop converter in Average Current Mode Control 19                                                                                                      |

| Fig. 3 (c) Model of the bi-directional dc-dc converter and its controller 20                                                                                                              |

| Fig. 4 (a) Currents and voltages of bi-directional dc-dc converter for $i_{dref}$ = -15.0A (reactive power support)                                                                       |

| Fig. 4 (b) Grid, load and inverter active and reactive power curves for $i_{dref}$ = -15.0A (reactive power support)                                                                      |

| Fig. 4 (c) Currents and voltages of the inverter, grid and load for $i_{dref}$ = -15.0A (reactive power support)                                                                          |

| Fig. 5 (a) Currents and voltages of bi-directional dc-dc converter for $i_{qref}$ = -12.0A (active power support)                                                                         |

| Fig. 5 (b) Grid, load and inverter active and reactive power curves for $i_{qref}$ = -12.0A (active power support)                                                                        |

| Fig. 6 (a) Currents of bi-directional dc-dc converter for $i_{qref}$ = 7.0A (renewable intermittency smoothing; absorbing active power)                                                   |

| Fig. 6 (b) Grid, load and inverter active power curves for $i_{qref}$ = 7.0A (renewable intermittency smoothing; absorbing active power)                                                  |

| Fig. 7 (a) Sensor, Interface and DSP boards (1 <sup>st</sup> ), Dc-link capacitor and Inverter (2 <sup>nd</sup> ), LC filter (3 <sup>rd</sup> ), Isolation Transformer (4 <sup>th</sup> ) |

| Fig. 7 (b) Bi-directional dc-dc converter and MSO4034B oscilloscope (top shelf), UCAP and 213.5 $\Omega$ load (bottom shelf)                                                              |

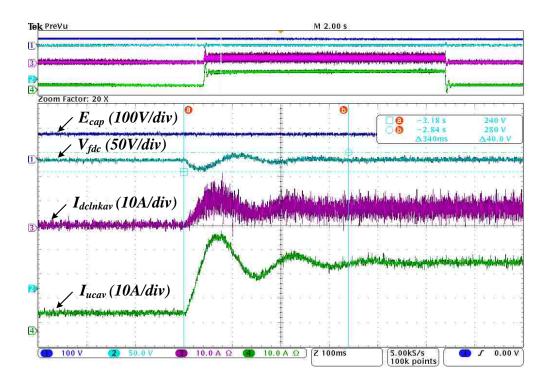

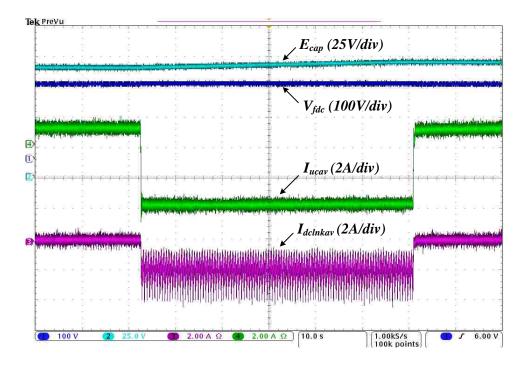

| Fig. 8 (a) Bi-directional dc-dc converter waveforms $V_{fdc}$ (CH1), $E_{cap}$ (CH2), $I_{dclnkav}$ (CH3) and $I_{ucav}$ (CH4)                                                            |

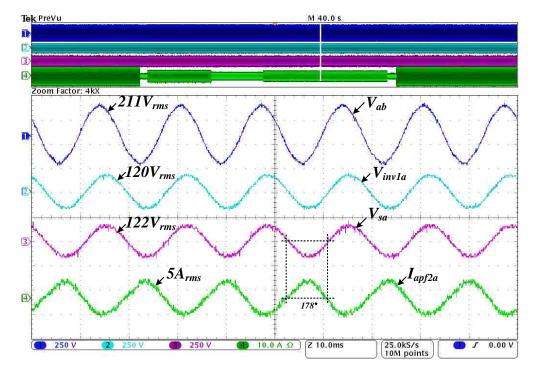

| Fig. 8 (b) Inverter experimental waveforms $V_{ab}$ (CH1), $V_{inv1a}$ (CH2), $V_{sa}$ (CH3) and $I_{apf2a}$ (CH4) for zone 3 (active power support $i_{qref}$ =-12.0A)                   |

| Fig. 8 (c) Inverter experimental waveforms $V_{ab}$ (CH1), $V_{inv1a}$ (CH2), $V_{sa}$ (CH3) and $I_{apf2a}$ (CH4) for zone 7 (reactive power support $i_{dref}$ =-15.0A)                 |

| Fig. 8 (d) Inverter experimental waveforms $V_{ab}$ (CH1), $V_{inv1a}$ (CH2), $V_{sa}$ (CH3) and $I_{apf2a}$ (CH4) for zone 5 (absorbing power from grid $i_{qref}$ =7.0A)                |

| Fig. 8 (e) Bi-directional dc-dc converter waveforms showing transient response during mode transition to active power support mode                                                        |

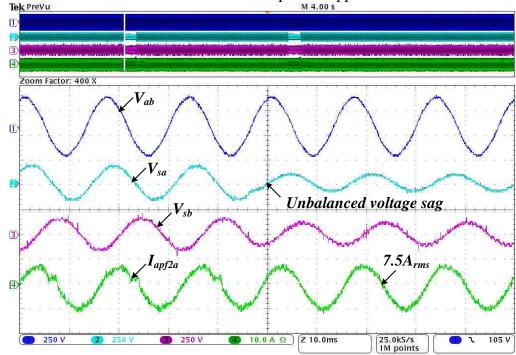

| Fig. 9 (a) Inverter experimental waveforms $V_{ab}$ (CH1), $V_{sb}$ (CH2), $V_{sa}$ (CH3) and $I_{apf2a}$ (CH4) for active power support $i_{qref}$ =-12.0A during an unbalanced sag in phases $a$ and $b$ |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

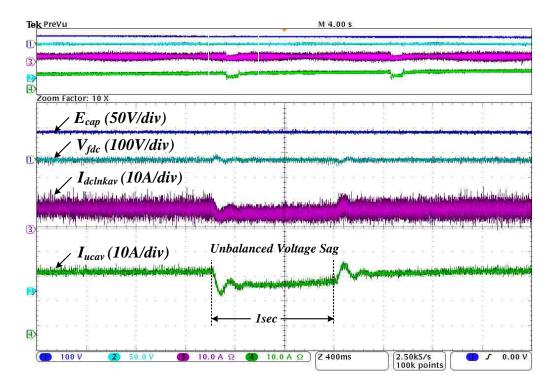

| Fig. 9 (b) Bi-directional dc-dc converter waveforms showing transient response in active power support mode during an unbalanced sag in phases <i>a</i> and <i>b</i> 36                                    |

| Paper II                                                                                                                                                                                                   |

| Fig. 1 One line diagram of DVR with UCAP Energy Storage                                                                                                                                                    |

| Fig. 2 Model of three-phase Series inverter (DVR) and its controller                                                                                                                                       |

| Fig. 3 Model of the bi-directional dc-dc converter and its controller                                                                                                                                      |

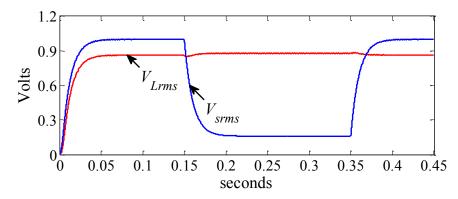

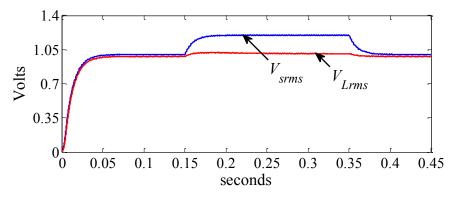

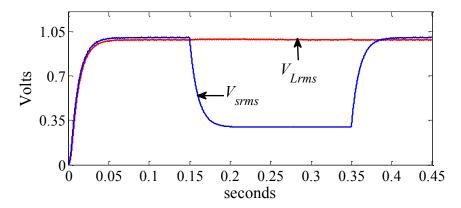

| Fig. 4 (a) Source and load RMS voltages $V_{srms}$ and $V_{Lrms}$ during sag                                                                                                                               |

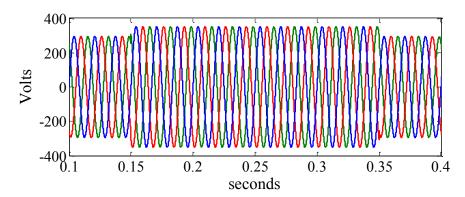

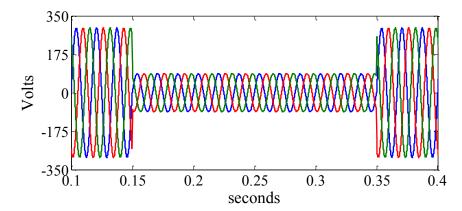

| Fig. 4 (b) Source voltages $V_{sab}$ (blue), $V_{sbc}$ (red), $V_{sca}$ (green) during sag                                                                                                                 |

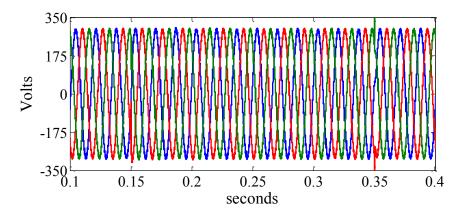

| Fig. 4 (c) Load voltages $V_{Lab}$ (blue), $V_{Lbc}$ (red), $V_{Lca}$ (green) during sag                                                                                                                   |

| Fig. 4 (d) Injected voltages $V_{inj2a}$ (blue), $V_{inj2b}$ (red), $V_{inj2c}$ (green) during sag                                                                                                         |

| Fig. 4 (e) $V_{inj2a}$ (green) and $V_{sab}$ (blue) waveforms during sag                                                                                                                                   |

| Fig. 5 (a) Currents and voltages of dc-dc converter                                                                                                                                                        |

| Fig. 5 (b) Active power of grid, load and inverter during voltage sag                                                                                                                                      |

| Fig. 6 (a) Source and load RMS voltages $V_{srms}$ and $V_{Lrms}$ during swell                                                                                                                             |

| Fig. 6 (b) Source voltages $V_{sab}$ (blue), $V_{sbc}$ (red), $V_{sca}$ (green) during swell                                                                                                               |

| Fig. 6 (c) Load voltages $V_{Lab}$ (blue), $V_{Lbc}$ (red), $V_{Lca}$ (green) during swell                                                                                                                 |

| Fig. 6 (d) Injected voltages $V_{inj2a}$ (blue), $V_{inj2b}$ (red), $V_{inj2c}$ (green) during swell                                                                                                       |

| Fig. 6 (e) $V_{inj2a}$ (green) and $V_{sab}$ (blue) waveforms during swell                                                                                                                                 |

| Fig. 7 (a) Currents and voltages of dc-dc converter during swell                                                                                                                                           |

| Fig. 7 (b) Active and Reactive power of grid, load and inverter during a voltage swell 56                                                                                                                  |

| Fig. 8 (a) Sensor, Interface and DSP boards (1st), Dc-link capacitor and Inverter (2nd), LC filter (3rd), Isolation Transformer (4th)                                                                      |

| Fig. 8 (b) Dc-dc converter and MSO4034B oscilloscope (top shelf), UCAP bank with 3 UCAPs (bottom shelf) and the Industrial Power Corruptor                                                                 |

| Fig. 9 (a) UCAP and bi-directional dc-dc converter experimental waveforms $E_{cap}$ (CH1), $V_{fdc}$ (CH2), $I_{dclnk}$ (CH3) and $I_{ucav}$ (CH4) during voltage sag                                      |

| Fig. 9 (b) UCAP and bi-directional dc-dc converter experimental waveforms $E_{cap}$ (CH1), $V_{fdc}$ (CH2), $I_{dclnk}$ (CH3) and $I_{ucav}$ (CH4) during voltage sag                                      |

| Fig. 10 (a) UCAP and dc-dc converter experimental waveforms $E_{cap}$ (CH1), $V_{fdc}$ (CH2), $I_{dclnk}$ (CH3) and $I_{ucav}$ (CH4) during voltage swell                                                  |

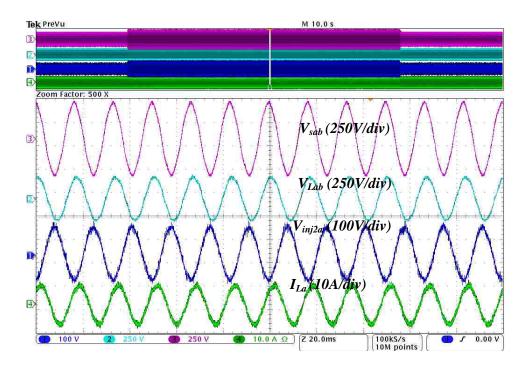

| Fig. 10 (b) Inverter experimental waveforms $V_{sab}$ (CH1), $V_{Lab}$ (CH2) and $V_{inj2a}$ (CH3) and $I_{La}$ (CH4) during the voltage swell                                                             |

| Pape | er III                                                                                                                                                                               |      |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Fig. | 1 One line diagram of Power Conditioner with UCAP Energy Storage                                                                                                                     | . 70 |

| Fig. | 2 Model of Power Conditioner with UCAP Energy Storage                                                                                                                                | . 71 |

| Fig. | 3 Controller block diagram for DVR and APF                                                                                                                                           | . 73 |

| Fig. | 4 Model of the bi-directional dc-dc converter and its controller                                                                                                                     | . 75 |

| Fig. | 5 (a) Source and load RMS voltages $V_{srms}$ and $V_{Lrms}$ during sag                                                                                                              | . 77 |

| Fig. | 5 (b) Source voltages $V_{sab}$ (blue), $V_{sbc}$ (red), $V_{sca}$ (green) during sag                                                                                                | . 77 |

| Fig. | 5 (c) Injected voltages $V_{inj2a}$ (blue), $V_{inj2b}$ (red), $V_{inj2c}$ (green) during sag                                                                                        | . 77 |

| Fig. | 5 (d) Load voltages $V_{Lab}$ (blue), $V_{Lbc}$ (red), $V_{Lca}$ (green) during sag                                                                                                  | . 78 |

| Fig. | 6 (a) Currents and voltages of dc-dc converter                                                                                                                                       | . 78 |

| Fig. | 6 (b) Active power of grid, load and inverter during voltage sag                                                                                                                     | . 79 |

| Fig. | 7 (a) Currents and voltages of bi-directional dc-dc converter for $i_{dref}$ = -15.0A (reactive power support) and $i_{qref}$ =-12.0A (active power support)                         | . 80 |

| Fig. | 7 (b) Grid, load and inverter active and reactive power curves for $i_{dref}$ = -15.0A (reactive power support) and $i_{qref}$ =-12.0A (active power support)                        | . 81 |

| Fig. | 8 (a) Sensor, Interface and DSP boards (1 <sup>st</sup> ), Dc-link capacitor and Inverter (2 <sup>nd</sup> ), LC filter (3 <sup>rd</sup> ), Isolation Transformer (4 <sup>th</sup> ) | . 83 |

| Fig. | 8 (b) Dc-dc converter and MSO4034B oscilloscope (top shelf), UCAP bank with 3 UCAPs (bottom shelf) and the Industrial Power Corruptor                                                | . 83 |

| Fig. | 9 (a) UCAP and bi-directional dc-dc converter experimental waveforms $E_{cap}$ (CH1), $V_{fdc}$ (CH2), $I_{dclnk}$ (CH3) and $I_{ucav}$ (CH4) during voltage sag                     | . 85 |

| Fig. | 9 (b) UCAP and bi-directional dc-dc converter experimental waveforms $E_{cap}$ (CH1), $V_{fdc}$ (CH2), $I_{dclnk}$ (CH3) and $I_{ucav}$ (CH4) during voltage sag                     | . 86 |

| Fig. | 10 (a) UCAP and dc-dc converter experimental waveforms $E_{cap}$ (CH1), $V_{fdc}$ (CH2), $I_{dclnk}$ (CH3) and $I_{ucav}$ (CH4) during voltage swell                                 | . 86 |

| Fig. | 10 (b) Inverter experimental waveforms $V_{ab}$ (CH1), $V_{inv1a}$ (CH2), $V_{sa}$ (CH3) and $I_{apf2a}$ (CH4) for zone 1 (reactive power support $i_{dref}$ =-10.0A)                | . 87 |

| Fig. | 10 (c) Inverter experimental waveforms $V_{sab}$ (CH1), $V_{Lab}$ (CH2), $V_{sa}$ (CH3) and $I_{apf2a}$ (CH4) for zone 3 (active power support $i_{qref}$ =-8.0A)                    | . 87 |

| Fig. | 10 (d) Inverter experimental waveforms $V_{ab}$ (CH1), $V_{inv1a}$ (CH2), $V_{sa}$ (CH3) and $I_{apf2a}$ (CH4) for zone 6 (UCAP charging $i_{aref}$ =8.0A)                           | . 88 |

# LIST OF TABLES

|                                                                  | Page |

|------------------------------------------------------------------|------|

| Paper I                                                          |      |

| TABLE I Shunt Inverter and Dc-dc converter Results               | 31   |

| Paper II                                                         |      |

| TABLE I Series Inverter and Dc-dc converter Experimental Results | 59   |

### **NOMENCLATURE**

Symbol Description

DER Distributed Energy Resource

UCAP Ultracapacitor

APF Active power filter

DVR Dynamic Voltage Restorer

UPQC Unified Power Quality Conditioner

PC Power Conditioner

PLL Phase Locked Loop

$P_{DER}$  Active power output from DER

$P_{UCAP}$  Active power output from UCAP

$P_{ref}$ ,  $Q_{ref}$  Active and Reactive power commanded references

$P_{grid}$ ,  $P_{load}$ ,  $P_{inv}$  Grid, Load and Inverter Active Powers

$Q_{grid}$ ,  $Q_{load}$ ,  $Q_{inv}$  Grid, Load and Inverter Reactive Powers

$E_{cap}$  UCAP bank terminal voltage

$I_{ucav}$  Average current out of the UCAP bank

$V_{fdc}$ ,  $V_{dc}$  Dc-link voltage

$I_{dclnk}$ ,  $I_{dclnkav}$  Dc-link current and average dc-link current

$\theta$  PLL tracking of the system frequency

$\varphi$  Phase difference between inverter current and voltage

$v_{sd}$ ,  $v_{sq}$  D-q components of the system voltage

$i_{dref}$ ,  $i_{qref}$  D-q components of the commanded reference currents

$I_{refa}$ ,  $I_{refb}$ ,  $I_{refc}$  Commanded reference currents of a, b, c phases

$I_{apf2a}$ ,  $I_{apf2b}$ ,  $I_{apf2c}$  Active power filter currents of a, b, c phases

$I_{sa}$ ,  $I_{sb}$ ,  $I_{sc}$  Source or grid currents of a, b, c phases

$I_{La}$ ,  $I_{Lb}$ ,  $I_{Lc}$  Load currents of a, b, c phases

$E_{UCAP}$  Energy stored in the UCAP in W-min

$V_{uc,ini}$ ,  $V_{uc,fin}$  UCAP initial and final voltages while discharging power

$P_{dcin}$  Power flowing into the dc-link

$V_{sa}$ ,  $V_{sb}$ ,  $V_{sc}$  Line-neutral source voltages of a, b, c phases

$V_{sab}$ ,  $V_{sbc}$ ,  $V_{sca}$  Line-line source voltages

$V_{Lab}$ ,  $V_{Lbc}$ ,  $V_{Lca}$  Line-line load voltages

$V_{inj2a}$ ,  $V_{inj2b}$ ,  $V_{inj2c}$  Line-neutral injected voltages of a, b, c phase

$V_{srms}$ ,  $V_{Lrms}$  RMS values of source and load voltages

$C_1(s)$ ,  $C_2(s)$  Voltage and current compensator transfer functions

### 1. INTRODUCTION

Most of the appliances today are powered by electricity and electrical power is transmitted over long distances to power the appliances. During the initial days of commercialization and mass-production of electricity, Nikola Tesla proved to the world that electrical power can be transmitted over long distances in a much more efficient way if polyphase alternating current transmission is used instead of direct current transmission. Since then most of the electrical energy is transmitted over long distances using 3-phase alternating current. One of the major drawbacks of electrical energy in an alternating current system is that it cannot be stored electrically. However, it can be converted to electrochemical energy (batteries), electromagnetic energy (super conducting magnets), electrostatic energy (ultracapacitors), kinetic energy (flywheels) and potential energy (pumped hydro). The concept of integrating energy storage at the transmission level for advanced power applications has been explored and in this regard efforts have been made to integrate energy storage into flexible AC transmission (FACTS) power flow controllers. With the integration of energy storage the FACTS power flow controller will have active power capability which enhances its power transfer capability. However, the energy storage integration at the distribution grid level has been rare and the concept of integrating distributed energy storage (DESs) and distributed energy resources (DERs) into the distributed grid is slowly becoming a reality.

Renewable energy generation is growing fast and ideas such as smart grid are trying to change the role of a consumer from being a passive consumer to an active contributor who can supply stored excess power in various DERs, such as solar, wind and

PHEVs back to the distribution grid or the micro-grid. Most of the DERs are intermittent and integrating them with energy storage not only improves the reliability of the DERs but also gives an opportunity to provide additional functionalities such as active and reactive power support and voltage sag/swell compensation to distribution grid. Of all the energy storage technologies UCAPs have low energy density and high power density and fast charge/discharge characteristics. Therefore, they are ideally suited for providing support to events on the distribution grid which require high power and low energy for short spans of time. UCAPs also have higher number of charge-discharge cycles and higher terminal voltage per module when compared to batteries which again make them ideal choice for providing grid support for short time.

The main contribution of this dissertation is in the hardware integration of UCAP-based energy storage into the distribution grid. UCAP based energy storage can be integrated into the distribution grid through a bi-directional dc-dc converter and a dc-ac inverter and this integration can be carried out by connecting the dc-ac inverter in series as a dynamic voltage restorer (DVR) or in shunt as an active power filter (APF) with the grid. The first paper focuses on integrated UCAP and APF design and the integrated system will have active power capability and it will be able to provide active power support, reactive power support and renewable intermittency smoothing to the distribution grid. The integrated APF-UCAP system with active power capability was simulated in PSCAD and hardware integration of the complete system was performed. Designs of major components in the power stage and the control strategy of the bi-directional dc-dc converter are discussed. The simulation of UCAP-APF system which consists of the UCAP, bi-directional dc-dc converter, and the grid-tied inverter is

performed using PSCAD. A hardware experimental setup of the same integrated system is presented and the ability to provide active power support, reactive power support and renewable intermittency smoothing to the distribution grid is dynamically tested. The second paper focuses on integrated UCAP and DVR design and the integrated system will again have active power capability which gives UCAP-DVR system ability to independently compensate voltage sags and voltage swells. The simulation of the UCAP-DVR system which consists of the UCAP, dc-dc converter, and the inverter connected in series with grid is performed using PSCAD. Hardware experimental setup of the integrated system is presented and the ability to provide temporary voltage sag and swell compensation to the distribution grid is dynamically is tested.

Both the APF and the DVR inverters can be integrated at the dc-link of the inverter to form a power quality conditioner and the UCAP bank can be integrated into the dc-link as well through a bi-directional dc-dc converter and the system will have active power capability. With this integration the power conditioner will be able to provide the combined functionalities of APF and DVR systems with energy storage. Therefore, the power conditioner and UCAP based energy storage can improve the power quality of the distribution grid by providing active, reactive power support, intermittency smoothing as well as voltage sag and swell compensation. The power stage and control strategy of the dc-dc converter, the series DVR and the shunt APF are discussed. Hardware integration of the UCAP based energy storage with the power conditioner systems is performed and hardware experimental results are presented. It is observed that experimental results match very well with PSCAD simulations.

### **PAPER**

# I. An Integrated Active Power Filter–Ultracapacitor Design to Provide Intermittency Smoothing and Reactive Power Support to the Distribution Grid

D. Somayajula, Student Member, IEEE, M. L. Crow, Fellow, IEEE

Abstract—Grid integration of distributed energy resources (DERs) is increasing rapidly. Furthermore, smart grid technologies are making the grid more bi-directional providing opportunities to consumers to supply power back to the grid. Energy storage technologies like battery and ultracapacitor (UCAP) can be integrated through grid tied-inverters to support variable DERs such as solar and wind. In these cases, the energy storage with active power capability can improve grid performance by providing active and reactive power support. In this paper, the concept of providing active/reactive power support to the distribution grid by UCAPs is presented. UCAPs have higher number of charge-discharge cycles and higher terminal voltage per module when compared to batteries which make them ideal for providing grid support. The UCAP is integrated into the dc-link of the active power filter (APF) through a dc-dc converter. The dc-dc converter provides a stiff dc-link voltage which improves the performance of the grid-tied inverter. Design and control of both the dc-ac inverter and the dc-dc converter are very important in this regard and presented. The simulation model of the overall system is developed and compared to the experimental hardware setup.

Index Terms-UCAP, grid-tied inverter, distribution grid, dc-dc converter, APF, d-q control, average current mode control

### I. INTRODUCTION

The integration of distributed energy storage (DES) and distributed energy resources (DER) into the grid is slowly becoming a reality [1]. Renewable energy

generation is growing rapidly and concepts such as the smart grid are changing the role of consumers from passive customer to an active contributor who can supply excess power back to the grid. Most of the DERs are variable and combining them with energy storage technologies like batteries, flywheels, superconducting magnets and ultracapacitors (UCAPs) [2] gives an opportunity to provide active and reactive power support to the distribution grid. Renewable intermittency smoothing of the distribution grid is another application where energy storage integration is needed in the seconds to minutes time Various rechargeable energy storage technologies like batteries, superconducting magnets, flywheels and UCAPs have active power capability. Among these UCAPs are ideally suited for applications like renewable intermittency smoothing which need active power support in the seconds to minutes time scale [2], [4]. UCAPs also have higher number of charge/discharge cycles and higher terminal voltage per module when compared to batteries and the cost of UCAPs has been declining rapidly in the last few years [5] making them a better choice when compared to batteries. UCAPs are currently being used mainly in wind power smoothing applications [6] or for regenerative braking applications in hybrid electric vehicles [7]. The concept of providing active and reactive power support to the distribution grid through UCAP energy storage has not been explored. The main contribution of this paper is the development and hardware integration of active power filter (APF) with UCAP energy storage which gives the integrated APF-UCAP system active power capability which aids in providing renewable intermittency smoothing, active and reactive power support to the distribution grid. This cannot be achieved by a conventional APF with dc-link capacitor which does not have active power capability.

In this paper, the UCAP integration with an APF through a bi-directional dc-dc converter is proposed. Similar integration methods for other DERs have been proposed in the literature, but mostly for PV and wind applications [8]-[9]. In [8], the control of a three-phase grid connected inverter is modified such that the PV system can be connected to the inverter directly without the need for a dc-dc converter for maximum power point tracking. In [9], the active and reactive power limits of a grid-connected inverter connected to a wind energy system are calculated. Integrating battery energy storage at the dc-link of a grid-tied inverter to provide real and reactive power support is proposed in [10]. However, the discussion in [10] is centered on the design of the high-power voltage source converter/inverter for the transmission grid and not the distribution grid. Integration of a UCAP through a dc-dc converter into a power conditioning system is proposed in [11], but the focus is again only on the voltage-source inverter and experimental results for the UCAP and dc-dc converter are not provided. A voltage source multilevel converter-based shunt APF with UCAP at the dc-link is explored in [12]. However, the dc-link capacitor is replaced by an UCAP to improve the performance during voltage dips. Integration of a UCAP bank into a unified power quality conditioner (UPQC) system through dc-dc converter is proposed in [13], but providing active and reactive power support for the grid through the shunt APF is not fully explored. In this paper, UCAP energy storage integration into the grid that extends these earlier developments and addresses the following missing application areas is proposed.

• Integration of UCAP with the APF system gives the system active power capability which is necessary for providing active power support and renewable intermittency smoothing

- Experimental validation of the UCAP, dc-dc converter, inverter their interface and control

- Development of inverter and dc-dc converter controls to provide Renewable

Intermittency Smoothing as well as Active and Reactive power support to the distribution grid

- Hardware integration and performance validation of the integrated APF-UCAP system

Most DERs are connected to the grid through a three-phase grid-tied inverter which can be controlled to meet various control objectives such as supplying active power, reactive power, harmonic compensation, and frequency regulation etc. A three-phase shunt active power filter (APF) can be controlled in such a way that it meets all the same control objectives. Furthermore, a three-phase grid-tied inverter is similar in topology to a three-phase shunt APF which opens up the possibility of exploring the vast amount of literature available for shunt APFs (see [14]-[17] as representative articles) and modifying the control strategies to suit the present control objectives of the grid-tied inverter.

### II. THREE-PHASE GRID CONNECTED INVERTER

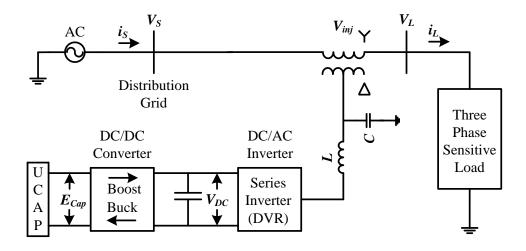

A system diagram of the proposed system is shown in Fig. 1. The APF-UCAP system is shunt connected between the system source and the load. The system consists of a UCAP on the input side of the bi-directional dc-dc converter which acts as an interface between the UCAP and the 3-phase grid connected inverter. The major advantage of integrating the UCAP and the APF system is that the system now has the capability to supply and absorb *Active Power* from the grid. And a bi-directional dc-dc

converter interface is necessary since the UCAP voltage profile changes as it charges/discharges energy while the inverter dc-link voltage has to stay constant for accurate control of inverter. Therefore, it acts as a boost converter while the UCAP is discharging energy into the grid and as a buck converter while charging the UCAP from the grid.

Fig. 1 One line diagram of the APF-UCAP system

## A. Power Stage

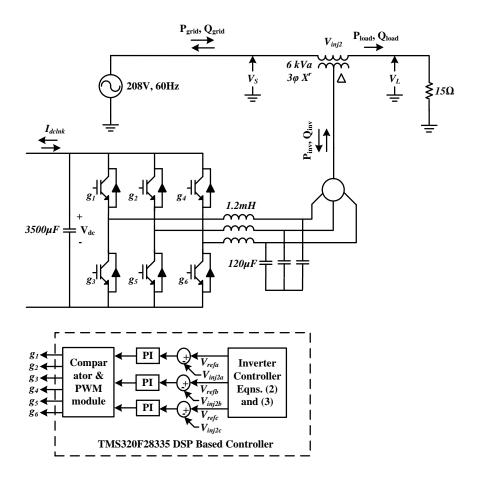

The power stage which consists of a 3-phase inverter and its controller is shown in Fig. 2. The inverter system consists of an IGBT module, its gate-driver, LC filter and an isolation transformer. The dc-link capacitor voltage has to be regulated for optimum performance of the converter such that:

$$V_{dc} = \frac{2\sqrt{2}}{\sqrt{3}m * n} v_{ab(rms)} \tag{1}$$

where m is the modulation index and n is the turns ratio of the isolation transformer. In this application for low voltage distribution grids, the line-line rms voltage is 208V, m is 0.75, and n is  $\sqrt{3}$  for the delta-wye transformer which yields the required dc-link voltage  $V_{dc}$  of 260V.

### B. Controller Implementation

There are various methods to control the 3-phase shunt APF to provide harmonic and reactive power compensation of which the most common approaches are the p-q method [14]-[15] and the  $i_d$ - $i_q$  method [16]. In [16], the authors state that the  $i_d$ - $i_q$  control performs better in non-sinusoidal and unbalanced conditions when compared to the p-q method, while both methods perform in a similar manner in balanced sinusoidal conditions. In this system, the  $i_d$ - $i_q$  method is modified to provide active and reactive power compensation instead of the reactive and harmonic compensation described in [16] such that  $i_d$  controls the reactive power and  $i_q$  controls the active power [9]. Therefore, based on the references for active and reactive powers  $P_{ref}$  and  $Q_{ref}$  the reference currents  $i_{qref}$  and  $i_{dref}$  in d-q domain can be calculated using (2) and (3) where  $v_{sq}$  is the system voltage in q-domain. Ideally a higher level integrated controller will be determining the values of  $P_{ref}$ ,  $Q_{ref}$  based on various system inputs like  $P_{grid}$ ,  $Q_{grid}$ ,  $P_{load}$ ,  $Q_{load}$ ,  $V_{dc}$ ,  $V_{ucap}$ ,  $I_{dclnk}$  as shown in Fig. 2

$$P_{ref} = -\frac{3}{2}(v_{sq}i_{qref} + v_{sd}i_{dref}) \tag{2}$$

If  $v_{sd}=0$ , then  $P_{ref}=-\frac{3}{2}v_{sq}i_{qref}$ . Similarly,

$$Q_{ref} = \frac{3}{2} (v_{sd} i_{qref} - v_{sq} i_{dref}) \tag{3}$$

and if  $v_{sd} = 0$ , then  $Q_{ref} = -\frac{3}{2}v_{sq}i_{dref}$ .

Fig. 2 Three-phase grid-connected inverter and the Inverter Controller

The reference currents in the d-q domain can be transformed into the reference currents  $i_{refa}$ ,  $i_{refb}$  and  $i_{refc}$  in the a-b-c domain using:

$$\begin{bmatrix}

i_{refa} \\

i_{refb} \\

i_{refc}

\end{bmatrix} = \begin{bmatrix}

1 & 0 \\

-\frac{1}{2} & \frac{\sqrt{3}}{2} \\

-\frac{1}{2} & -\frac{\sqrt{3}}{2}

\end{bmatrix} \begin{bmatrix}

\cos \theta & \sin \theta \\

-\sin \theta & \cos \theta

\end{bmatrix} \begin{bmatrix}

i_{dref} \\

i_{qref}

\end{bmatrix}$$

(4)

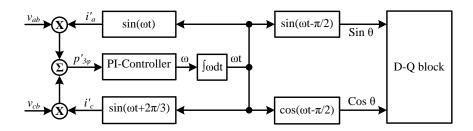

Eqn. (4) requires a PLL to estimate the value of  $\theta$  and the PLL used in this paper is based on the fictitious power method proposed in [15]. The main advantage of the fictitious power method is it tracks the positive sequence voltage  $V_{+I}$  instead of the actual system voltage which is very useful in unbalanced systems. Once the reference currents  $i_{refa}$ ,  $i_{refb}$  and  $i_{refc}$  are calculated they are compared with the actual inverter currents  $i_{apf2a}$ ,  $i_{apf2b}$  and  $i_{apf2c}$  and the error is passed through a PI controller. There are various methods for current control like hysteresis, sigma-delta and PI control. Among these PI control is the most stable however; it requires the tuning of PI gains based on the system parameters. For the present system the  $K_p$  and  $K_i$  values were found out to be 0.2 and 50 respectively. Therefore, the transfer function of PI controller is given by:

$$T(s) = 0.2 + \frac{50}{s} \tag{5}$$

Then the PI controller output is passed through a comparator and Pulse width modulator (PWM) which will generate the gate signals for the inverter and this will allow the inverter to supply the commanded active power  $P_{ref}$  or reactive power  $Q_{ref}$ . In the present scenario for the sake of demonstration and proof of concept validation the system is operated in open loop and  $P_{ref}$  and  $Q_{ref}$  are commanded directly in the controller instead of these values coming from a higher level integrated controller as proposed in the

control block diagram. Therefore, the actual active power  $P_{inv}$  and reactive power  $Q_{inv}$  supplied by the inverter may not be the same as the commanded  $P_{ref}$  and  $Q_{ref}$ . They are estimated as:

$$P_{inv} = 3V_{sa(rms)}I_{apf2a(rms)}\cos\varphi$$

$$Q_{inv} = 3V_{sa(rms)}I_{apf2a(rms)}\sin\varphi$$

(6)

In (6),  $V_{sa}$  is line-neutral voltage of the grid,  $I_{apf2a}$  is the inverter current on the secondary side of the isolation transformer and  $\varphi$  is the phase difference between the  $V_{sa}$  and  $I_{apf2a}$  waveforms. The complete inverter control algorithm is implemented in a DSP TMS320F28335 which has a clock frequency of 150MHz, an inbuilt A/D module, PWM module and real-time emulation, which are all well-suited for this application. The sampling frequency in the inbuilt A/D module was set at 60 kHz and the switching frequency in the PWM module is set at 12 kHz for the present application.

### III. UCAP AND BIDIRECTIONAL DC-DC CONVERTER

### A. UCAP Bank Hardware Setup

UCAPs can deliver very high power in a short time span; they have higher power density and lower energy density when compared to Li-ion batteries [18], [19]. The major advantage UCAPs have over batteries is their power density characteristics, high number of charge-discharge cycles over their lifetime and higher terminal voltage per module [5], [18]. These are ideal characteristics for providing active/reactive power support and intermittency smoothing to the distribution grid on a *short term* basis. In [20], it is proposed that UCAPs are currently viable as short term energy storage for bridging power in kW range in the *seconds* to *few minutes* timescale. The choice of the number of

UCAPs necessary for providing grid support depends on the amount of support needed, terminal voltage of the UCAP, dc-link voltage and distribution grid voltages. In the present case the choice was made based on the following parameters. From (1) it is clear that the dc-link voltage needs to be 260V for the 208V distribution grid for optimal performance of the inverter. The terminal voltage of each BMOD0165P048 module is 48V which means connecting three modules in series would bring the initial voltage of the UCAP bank to 144V and connecting four modules in series would bring the initial voltage of the UCAP bank to 192V. For a 260V dc-link voltage these two options are ideal for integrating the UCAP bank through the dc-dc converter since the duty ratio of the converter would be either too low or too high for other cases. It is cost effective as well to use 3 modules in the UCAP bank when compared to 4 modules. In this paper, the experimental setup consists of three 48V, 165F UCAPs (BMOD0165P048) manufactured by Maxwell Technologies which are connected in series. Assuming that the UCAP bank can be discharged to 50% of its initial voltage  $(V_{uc,ini})$  to final voltage  $(V_{uc,fin})$  from 144V to 72V which translates to depth of discharge of 75%, the energy in the UCAP bank available for discharge is given by:

$$E_{UCAP} = \frac{1}{2} * C * \frac{(V_{uc,ini}^2 - V_{uc,fin}^2)}{60} W - min$$

$$E_{UCAP} = \frac{1}{2} * \frac{165}{3} * \frac{(144^2 - 72^2)}{60}$$

$$= 7128 \text{ W-min}$$

(7)

A bi-directional dc-dc converter is required as an interface between the UCAP and the dc-link since the UCAP voltage varies with the amount of energy discharged while the dc-link voltage has to be stiff. Therefore, bi-directional dc-dc converter is designed to

operate in boost mode when the UCAP bank voltage is between 72V to 144V and the output voltage is regulated at 260V. And when the UCAP bank voltage is below 72V the bi-directional dc-dc converter is operated in Buck mode and draws energy from the grid to charge the UCAPs and the output voltage is again regulated at 260V.

### B. Bi-directional Dc-dc Converter Hardware Setup

Various topologies have been proposed for the dc-dc converter for integrating UCAP based energy storage into the grid. A drive system and an auxiliary energy storage system with UCAPs have been proposed in [21]-[22]. In the present paper, a non-isolated bi-directional dc-dc converter which acts as a boost converter while discharging energy from the UCAP and as a buck converter while charging energy from the grid is used. The integrated UCAP and APF system is supposed to respond dynamically to provide *active* and *reactive power support* to the grid as well as provide *renewable intermittency smoothing*. In the case of renewable intermittency smoothing application the bi-directional dc-dc converter should be able to withstand fluctuations in the power outputs of the DERs by absorbing excess power from DERs into UCAP and discharging power from UCAP when the power output from DERs is lower than load requirement.

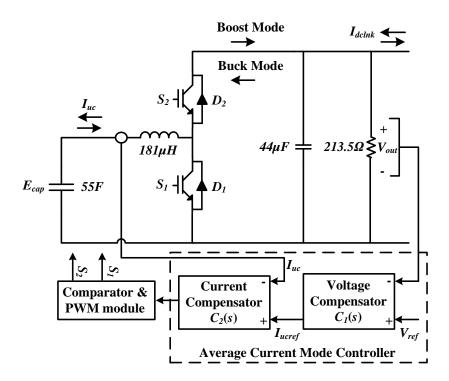

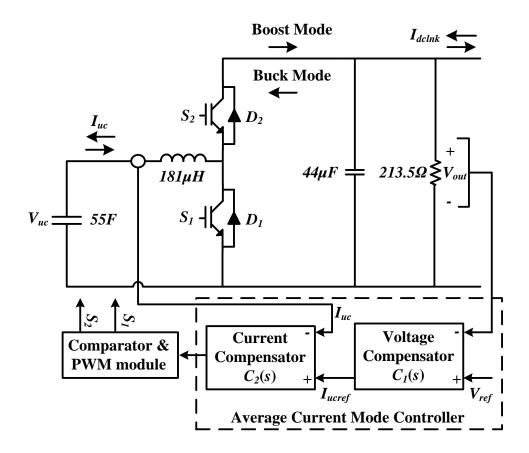

The model of the bi-directional dc-dc converter and its controller is shown in Fig. 3 (a) where the output of the dc-dc converter is connected to the dc-link of the inverter. The input consists of three 48V 165F UCAPs with a total ESR of 21.3  $m\Omega$ . The inductance of 181  $\mu$ H is chosen for operating the converter in continuous conduction mode (CCM) for heavy load cases and in discontinuous conduction mode (DCM) for light load case. The size of the inductor is an important factor in the dc-dc converter design and as the inductor size increases, the amount of ripple in the inductor current also decreases [17]. Generally it is preferred to operate the converter in CCM with low ripple,

but operating the converter in CCM at light load requires a large inductor. Therefore, in this system the ripple in the inductor current is kept constant at 9A and the converter is allowed to operate in both CCM and DCM for optimum sizing of the inductor over a wide operating range.

Switching frequency also impacts the size of the inductor and is set to 31.25 kHz which also produces a good transient response. The input filter capacitor of 88  $\mu$ F is used to reduce the high frequency inductor ripple current which if drawn from the UCAP bank may reduce its cycle life. Note that as the size of the inductor decreases, the amount of ripple current increases, which has to be supplied by the input filter capacitor. Thus the size of the inductor and the input filter capacitor are interdependent and their design must be optimized accordingly. An output capacitor of  $44\mu$ F is used to filter out the high frequency ripple in the output current which is discontinuous and therefore, has higher ripple when compared to the input current. However, the dc-link capacitor provides a portion of the ripple current and the input is more sensitive to high frequency ripple so it has a larger capacitor compared to output. A nominal resistive load of 213.5 $\Omega$  is used to prevent the converter from operating on no-load.

### C. Controller Implementation

Average current mode control is used to regulate the output voltage of the bidirectional dc-dc converter in both Buck and Boost modes while Charging and Discharging the UCAP bank. While the UCAP-APF system is Discharging power the dc-link voltage  $V_{out}$  tends to be less than  $V_{ref}$  which causes the reference current  $I_{ucref}$  to be positive thereby operating the dc-dc converter in  $Boost\ Mode$ . Along similar lines when the UCAP-APF system is absorbing power from the grid the dc-link voltage  $V_{out}$  tends to be greater than  $V_{ref}$  which causes the reference current  $I_{ucref}$  to be negative and thereby operating the dc-dc converter in *Buck mode*. Average current mode control technique is widely explored in the literature [17] and it was found as the ideal method for UCAP-APF integration as it tends to be more stable when compared to other methods like voltage mode control and peak current mode control. Average current mode controller and the higher level integrated controller are shown in Fig. 3 (a) where the actual output voltage  $V_{out}$  is compared with the reference voltage  $V_{ref}$  and the error is passed through the voltage compensator  $C_I(s)$  which generates the average reference current  $I_{ucref}$ . This is then compared to the actual UCAP current (which is also the inductor current)  $I_{uc}$  and the error is then passed through the current compensator  $C_2(s)$ .

Fig. 3 (a) Model of the bi-directional dc-dc converter and its controller

The converter model for average current mode control is based on the following transfer functions developed in [23]:

$$G_{id}(s) = \frac{V_{out}\left(sC + \frac{2}{R}\right)}{s^2LC + s\frac{L}{R} + (1-D)^2}$$

(8)

$$G_{vi}(s) = \frac{(1-D)\left[1 - \frac{sL}{R(1-D)^2}\right]}{\left(sC + \frac{2}{R}\right)}$$

(9)

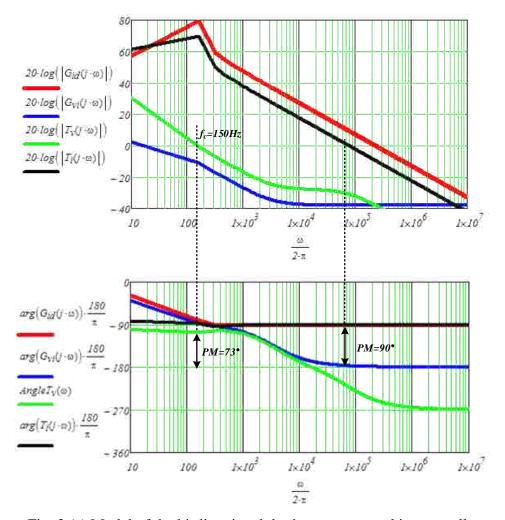

The model of the dc-dc converter in Average current mode control is shown in Fig. 3 (b) which has two loops. The inner current loop  $T_i(s)$  which has the current compensator  $C_2(s)$ , voltage modulator gain  $V_M$  and the transfer function  $G_{id}(s)$ . The outer voltage loop  $T_v(s)$  constitutes the voltage compensator  $C_1(s)$ , current loop  $T_i(s)$  and the transfer function  $G_{vi}(s)$ . The current compensator design  $C_2(s)$  must be carried out initially and the voltage compensator  $C_1(s)$  design is based on the design of the current compensator due to the dependency of  $C_1(s)$  on  $C_2(s)$ . The current compensator  $C_2(s)$  must be designed in such a way that at the cross-over frequency of the current loop there is enough phase-margin to make the current loop  $T_i(s)$  stable and it should have a higher bandwidth when compared to the voltage loop  $T_v(s)$ . Based on these criteria the transfer functions of the current loop  $T_i(s)$  and the current compensator  $C_2(s)$  are given by:

$$T_i(s) = G_{id}(s).\frac{C_2(s)}{V_M} \tag{10}$$

$$C_2(s) = 1.67 + \frac{231.81}{s} \tag{11}$$

Fig. 3 (b) Block diagram of closed-loop converter in Average Current Mode Control

The closed loop transfer function of the current loop is then given by:

$$T_1(s) = \frac{T_i(s)}{1 + T_i(s)} \tag{12}$$

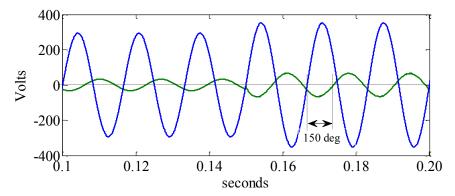

It can be observed from Fig. 3 (c) that the phase margin is around 90° at the cross-over frequency of the current loop  $T_i(s)$  and it has higher bandwidth when compared to the voltage loop  $T_v(s)$ . The voltage loop compensator  $C_I(s)$  design is dependent on the design of  $T_I(s)$  and it is a PI compensator whose gain is adjusted to have the desired cross-over frequency. Based on these criterion the transfer functions of the voltage loop  $T_v(s)$  and compensator  $C_I(s)$  is given by:

$$T_{\nu}(s) = G_{\nu i}(s)C_1(s)T_1(s) \tag{13}$$

$$C_1(s) = 3.15 + \frac{1000}{s} \tag{14}$$

The transfer function of the plant  $G_{vi}(s)$  along with the transfer function of  $C_I(s)$  of the voltage compensator and the overall voltage loop transfer function  $T_v(s)$  are shown in Fig. 3 (c). It can be observed that the voltage loop  $T_v(s)$  has a cross-over frequency of around

150 Hz with a phase margin of 73° which provides a stable dynamic response. The stability and dynamic performance of the voltage loop  $T_{\nu}(s)$  determine the stability and dynamic response of the overall system.

Fig. 3 (c) Model of the bi-directional dc-dc converter and its controller

### D. Higher Level Integrated Controller

The higher level integrated controller is designed to make system level decisions on the inverter and dc-dc converter controllers. Based on various system parameters like  $P_{load}$ ,  $Q_{load}$ ,  $P_{grid}$ ,  $Q_{grid}$ ,  $V_{ucap}$ ,  $V_{dc}$ ,  $I_{dclnk}$ ,  $I_{ucap}$  the higher level integrated controller will

decide on operating in one of the following modes *Active Power Support mode*, *Reactive Power Support Mode*, *Renewable Intermittency Smoothing Mode* and *Charge Mode*.

In Active power support mode and Renewable intermittency smoothing mode the UCAP-APF system must provide active power to the grid. Therefore, the active power capability of the UCAP-APF system must be assessed by the higher level integrated controller. Based on the  $P_{grid}$  and  $P_{load}$  values the reference  $P_{ref}$  is calculated in the higher level integrated controller and it will decide if the UCAP has enough energy to respond to the  $P_{ref}$  command based on the UCAP state of charge. If the UCAP has enough capacity to respond to the request then the dc-dc converter controller is operated in *Grid Support Mode* otherwise it is operated in *Charge Mode* where the UCAP is recharged and the power request is met at a later time. In Grid Support Mode the dc-dc converter will operate in a bi-directional fashion in both Buck and Boost modes to respond to the active power requests and regulate the dc-link voltage in a stable fashion while the inverter controller should respond such that the commanded  $P_{ref}$  is supplied by the inverter through current control.

In Reactive power support mode the UCAP-APF system must provide reactive power to the grid. In this mode the UCAP-APF does not provide any active power to the grid and even the APF losses are supplied by the grid. Based on the  $Q_{grid}$  and  $Q_{load}$  values the reference  $Q_{ref}$  is calculated in the higher level integrated controller. In this mode the dc-dc converter controller can be programmed to operate in Grid Support Mode directly since the active power requirement for operating in this mode is minimal. Therefore, the goal of the dc-dc converter controller is to regulate the dc-link voltage in a stable fashion

while the inverter controller should respond such that the commanded  $Q_{ref}$  is supplied by the inverter through current control.

In *Charge Mode* the UCAP is recharged by absorbing active power from the grid when the UCAP state of charge falls below 50%. The rate at which the UCAP can be charged is assessed by the higher level integrated controller based on the  $P_{grid}$  and  $P_{load}$  values and the reference  $P_{ref}$  is calculated. Then the dc-dc converter controller is commanded to operate in *Charge Mode* wherein the dc-dc converter will operate in Buck Mode to absorb the power from the grid and the inverter controller must respond to supply commanded  $P_{ref}$ .

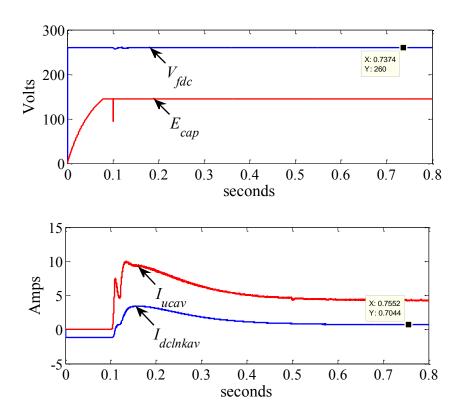

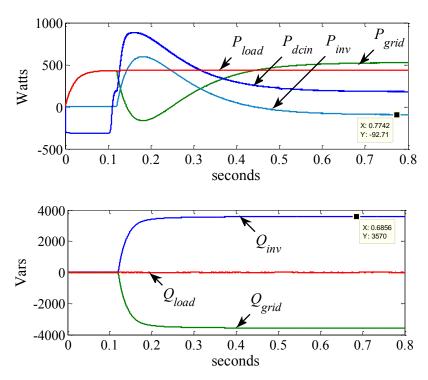

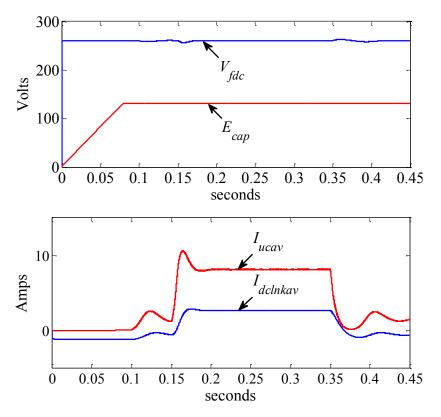

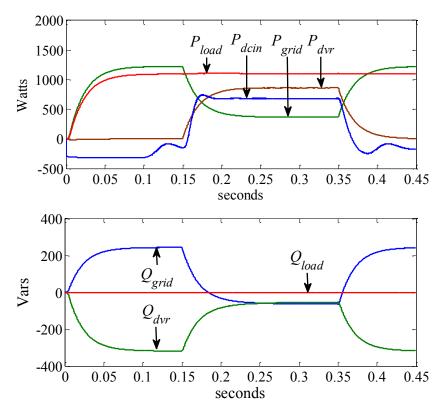

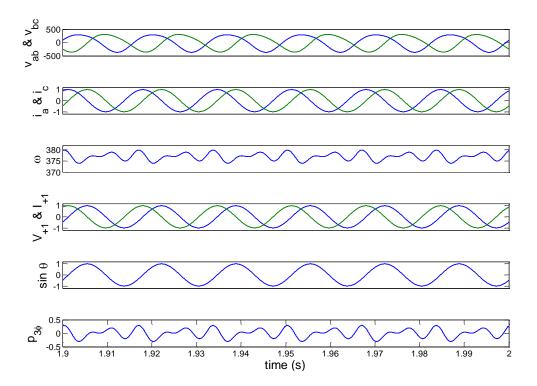

#### IV. SIMULATION RESULTS

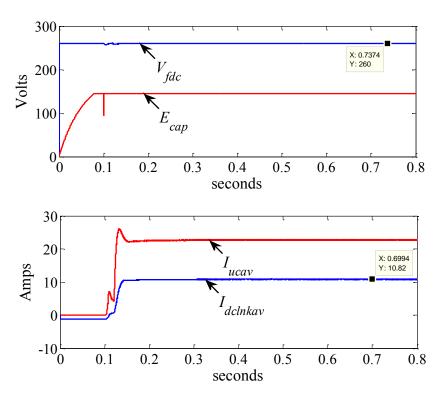

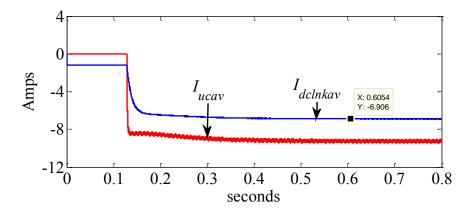

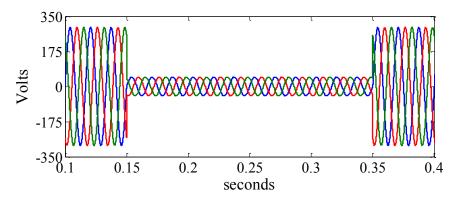

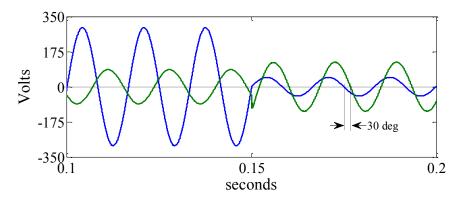

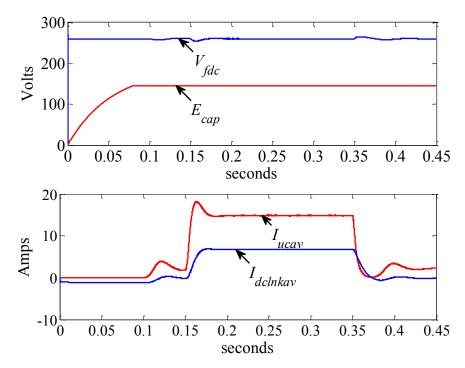

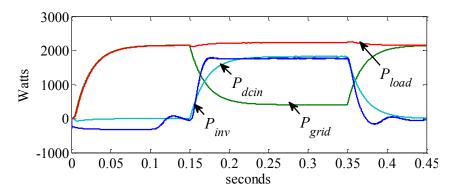

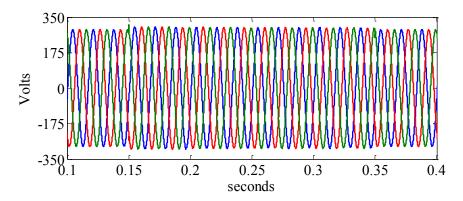

The simulation of the complete system which includes the 3-phase grid tied inverter and the dc-dc converter is performed using PSCAD. The ability of the system to supply the commanded reactive power is simulated with  $i_{dref} = -15$ A which translates to a  $Q_{ref}$  of 3819Var from (3). The simulation results are shown in Fig. 4 (a) and (b) where the UCAP is charged until 0.08s, at which point the UCAP voltage  $E_{cap}$  reaches a value of 144V. The UCAP is connected to the dc-dc converter at t = 0.10s. At t = 0.12s the inverter is synchronized to the grid. It can be observed from Figs. 4 (a) and 4 (b) that  $P_{inv}$ ,  $Q_{inv}$  and  $V_{fdc}$  have converged to the steady state values of -92W, 3570Var and 260V, respectively closely tracking the commanded  $Q_{ref}$ .

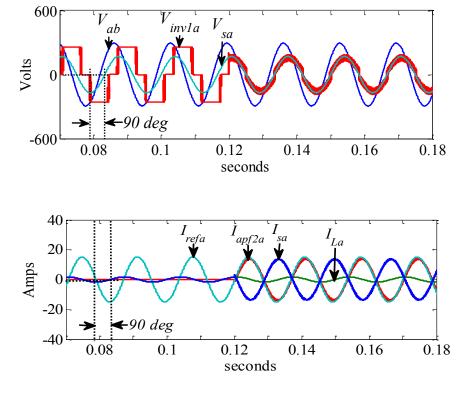

The inverter current and voltage waveforms when the system provides reactive power support are shown in Fig. 4 (c) where it can be observed that  $I_{apf2a}$  tracks the reference current  $I_{refa}$  accurately after synchronization with the grid. And  $I_{refa}$  and hence  $I_{apf2a}$  lags  $V_{sa}$  by approximately 90° which is required for reactive power compensation. It

can also be observed from voltage waveforms that the inverter voltage  $V_{inv1a}$  is almost sinusoidal after synchronization. The ability of the system to supply commanded active power is then simulated with  $i_{qref}$  =-12.0A which translates to  $P_{ref}$  of 3054W from (2). The simulation setup is the same as in the previous case and the simulation results are shown in Figs. 5 (a) and 5 (b) where it can be observed that  $P_{inv}$ ,  $Q_{inv}$ ,  $V_{fdc}$  and  $I_{dclnkav}$  have converged to steady state values of 2701W, 466Var, 260V and 10.82A closely tracking the commanded  $P_{ref}$ .

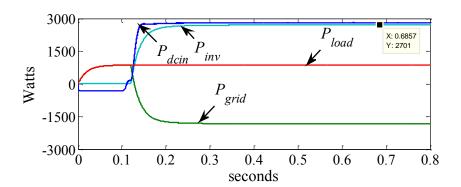

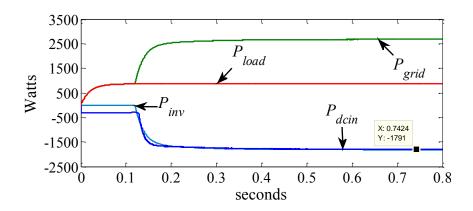

Similarly, the simulation results for the renewable intermittency smoothing applications where the UCAP must be capable of both supplying and absorbing active power are shown in Figs. 6 (a) and (b). Since the results for the case where the UCAP and the inverter system supply active power to the grid are already presented in Figs. 5 (a) and (b) so in Figs. 6 (a) and (b) similar results are presented for the case where the UCAP and inverter system absorb active power from the grid which is achieved by commanding a positive  $i_{qref}$  of 7A which corresponds to a  $P_{ref}$  of -1782W. It can be observed from Figs. 6 (a) and (b) that  $P_{inv}$ ,  $V_{fdc}$  and  $I_{dclnkav}$  have converged to steady state values of -1791W, 260V and -6.906A again tracking the commanded  $P_{ref}$  closely. The slight difference between the reference values and actual values in all three modes is due to the operation of the system in open loop configuration as explained previously. It should also be noted that simulation results are presented for shorter time span when compared to hardware results due to limitations in PSCAD software. Therefore, it is evident from the simulations that the UCAP and APF system can together respond to changes in  $i_{qref}$  and  $i_{dref}$  commands and accordingly provide active and reactive power support to the grid. It is also evident that both the dc-dc converter and inverter can operate in a bi-directional

fashion which is necessary when the system is used in renewable intermittency smoothing applications. Active power support, reactive power support and renewable intermittency smoothing are the primary functionalities the UCAP integrated APF system will be providing to the distribution grid. These functionalities of energy storage with user defined or higher level controls will be playing a major role with penetration of distributed energy resources (DERs) on the distribution grid.

Fig. 4 (a) Currents and voltages of bi-directional dc-dc converter for  $i_{dref}$ = -15.0A (reactive power support)

Fig. 4 (b) Grid, load and inverter active and reactive power curves for  $i_{dref}$ = -15.0A (reactive power support)

Fig. 4 (c) Currents and voltages of the inverter, grid and load for  $i_{dref}$ = -15.0A (reactive power support)

Fig. 5 (a) Currents and voltages of bi-directional dc-dc converter for  $i_{qref}$ = -12.0A (active power support)

Fig. 5 (b) Grid, load and inverter active and reactive power curves for  $i_{qref}$ = -12.0A (active power support)

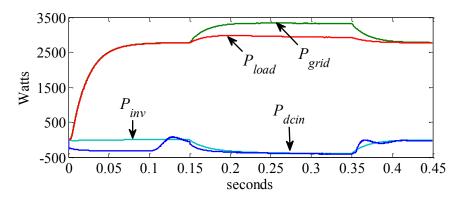

Fig. 6 (a) Currents of bi-directional dc-dc converter for  $i_{qref}$ = 7.0A (renewable intermittency smoothing; absorbing active power)

Fig. 6 (b) Grid, load and inverter active power curves for  $i_{qref}$  = 7.0A (renewable intermittency smoothing; absorbing active power)

# V. EXPERIMENTAL RESULTS

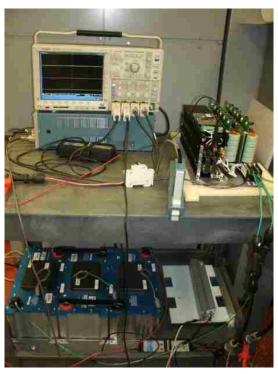

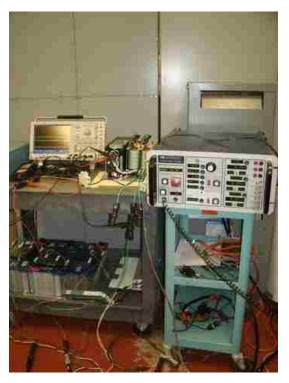

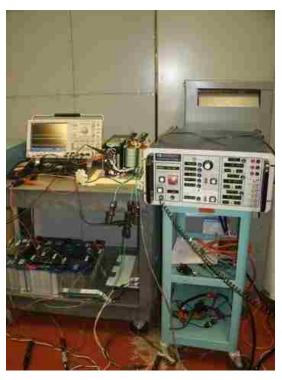

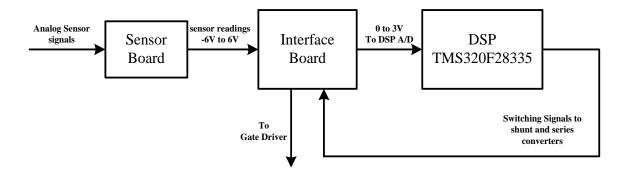

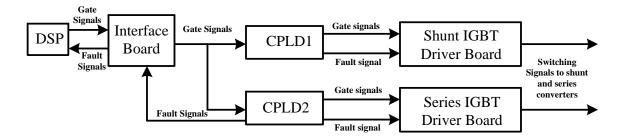

To validate the UCAP-APF performance, a hardware prototype of the system was constructed and is shown in Figs. 7 (a) and 7 (b). In Fig. 7 (a), the complete inverter system is shown. It consists of a sensor board, an interface board, TMS320F28335 DSP controller and their power supply circuit in the top ( $1^{st}$ ) shelf. The  $2^{nd}$  shelf contains the inverter IGBT module (BSM100GD60DLC) which is a 600V, 100A six-pack module from Infineon, its gate driver SKHI 61R manufactured by SEMIKRON, and the 3500  $\mu$ F 450Vdc dc-link capacitor; the  $3^{rd}$  shelf has the LC-filter which consists of a 1.2 mH, 45A

3-phase inductor and three  $120\mu F$  240Vac capacitors connected in wye configuration through damping resistors of  $320~\Omega$  in each phase. The  $4^{th}$  shelf consists of the  $5kVA~\Delta$ -Y (120V/208V) isolation transformer and a protection circuit breaker before the inverter system is connected to the grid. In Fig. 7 (b) the UCAP and the dc-dc converter system is shown with the dc-dc converter and the oscilloscope (MSO4034B used for recording the data) in the top shelf. The bottom shelf has 3 UCAPs connected in series and nominal load of  $213.5\Omega$ .

Fig. 7 (a) Sensor, Interface and DSP boards (1<sup>st</sup>), Dc-link capacitor and Inverter (2<sup>nd</sup>), LC filter (3<sup>rd</sup>), Isolation Transformer (4<sup>th</sup>)

Fig. 7 (b) Bi-directional dc-dc converter and MSO4034B oscilloscope (top shelf), UCAP and  $213.5\Omega$  load (bottom shelf)

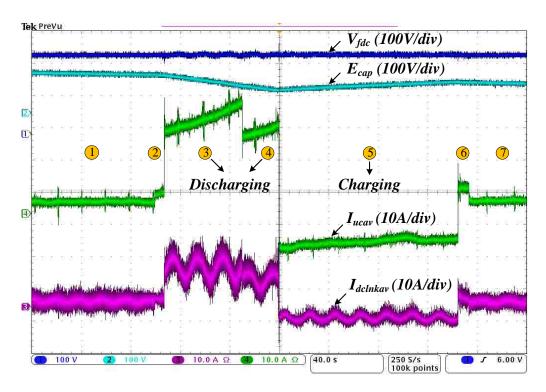

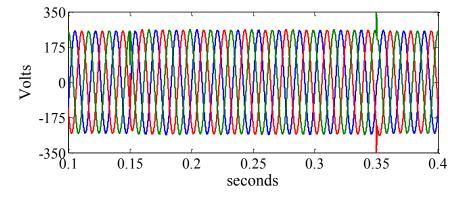

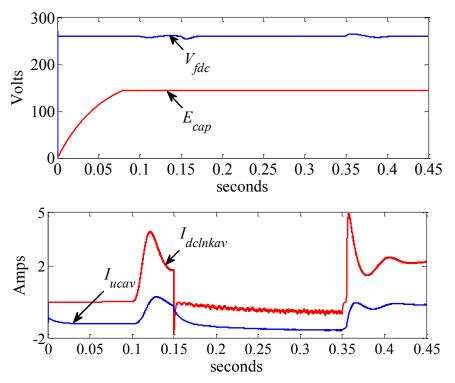

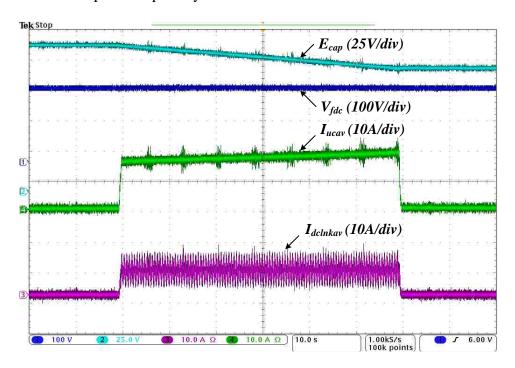

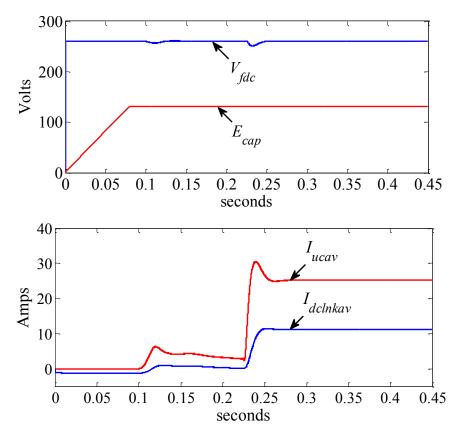

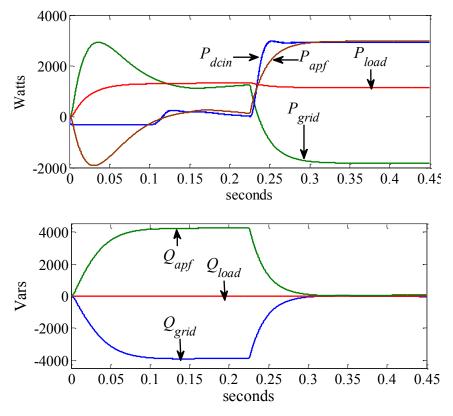

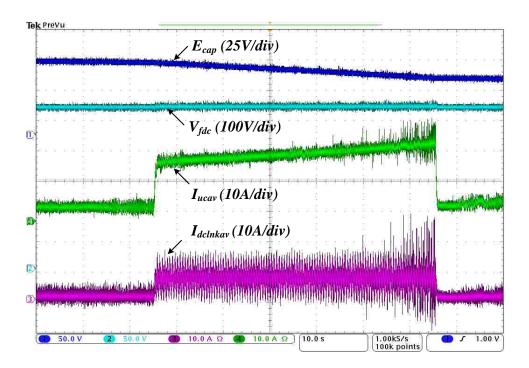

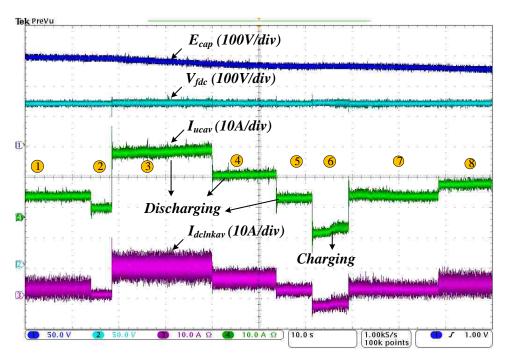

In Fig. 8 (a) the experimental waveforms of the bi-directional dc-dc converter are shown with the UCAP voltage  $E_{cap}$  (CH1), the dc-link voltage  $V_{fdc}$  (CH2), the average UCAP current  $I_{ucav}$  (CH3) and the dc-link current  $I_{dclnk}$  (CH4). Fig. 8 (a) is divided into 7 zones which are labeled from 1 through 7 in the plots. In zone 1 the inverter is supplying

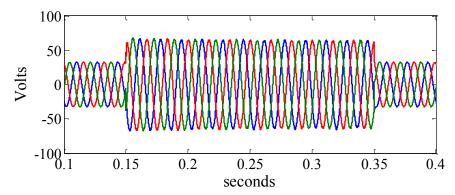

only reactive power and the dc-dc converter is maintaining a stiff dc-link voltage. Zone 2 is a transition mode in which the inverter is changing from supplying reactive power to active power. In Zone 3 the inverter is supplying only active power to the grid which is being discharged from the UCAP. In Zone 4 again the inverter is supplying only active power to the grid however; the amount of active power supplied to the grid in Zone 4 is less than that in Zone 3 which can be observed from  $I_{dclnk}$  trace. In Zone 5 inverter is absorbing active power from the grid which is used for charging the UCAP through the bi-directional dc-dc converter. Zone 6 is again a transition mode in which the inverter is changing from supplying active power to supplying reactive power to the grid. In Zone 7 again the inverter is supplying only reactive power to the grid and the dc-dc converter is maintaining a stiff dc-link voltage.

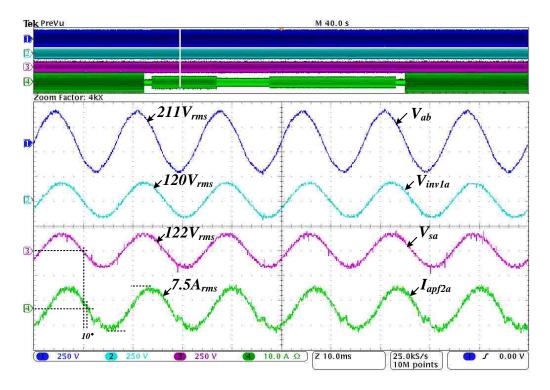

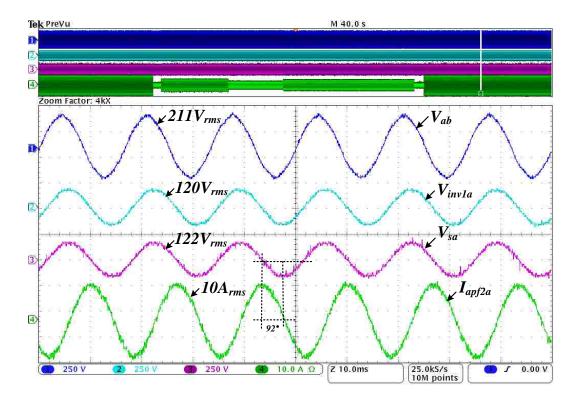

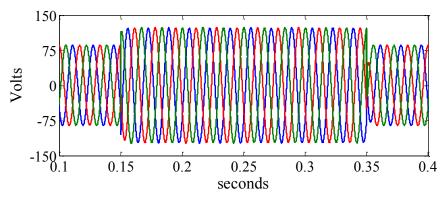

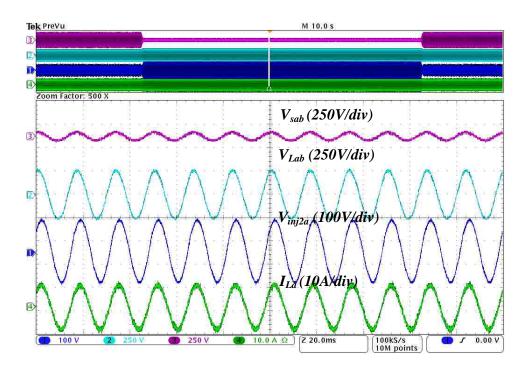

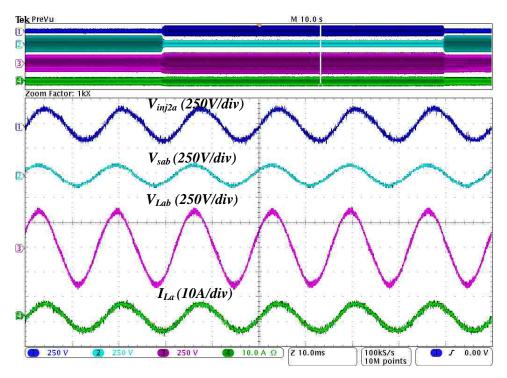

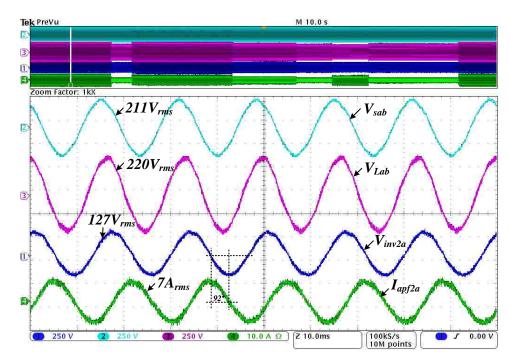

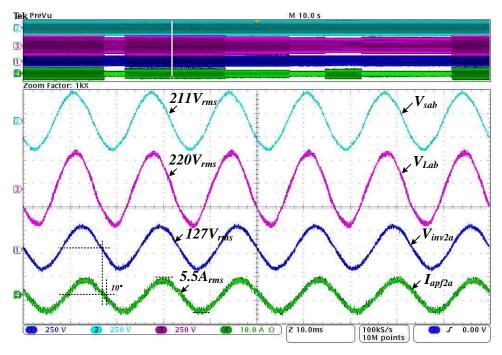

In Fig. 8 (b) the zoomed in view of zone 3 is shown from which it can be observed that the inverter current  $I_{apf2a}$  and voltage  $V_{sa}$  are almost in phase with little phase difference which clearly shows that the inverter is providing active power support to the grid. The RMS values of  $V_{sa}$  and  $I_{apf2a}$  are 7.5A and 122V respectively which translates to  $P_{inv}$  of 2703.3W and  $Q_{inv}$  of 476.6Var from (7) as the phase difference of  $10^{\circ}$  between  $V_{sa}$  and  $I_{apf2a}$ ; the results are similar for zone 4 where the commanded active power is comparatively less than that in zone 4. It is important to notice zones 3 and 4 of Fig. 8 (a) from which it can be seen that UCAP is discharging power rapidly in these zones therefore,  $E_{cap}$  is decreasing rapidly while  $V_{fdc}$  remains constant at 260V and  $I_{ucav}$  is increasing rapidly while average of  $I_{dclnkav}$  remains almost constant. In Fig. 8 (c) the zoomed in view of zone 7 is presented where the inverter is only supplying reactive power to the grid. It can be observed that  $I_{apf2a}$  is lagging  $V_{sa}$  by nearly  $90^{\circ}$  and their RMS

values are 10A and 122V respectively which translates to  $Q_{inv}$  of 3660Var from (7). Similarly, it can be noticed from zones 1 and 7 in Fig. 8 (a) that  $E_{cap}$  is almost constant while  $I_{ucav}$  and  $I_{dclnkav}$  are almost zero which proves that the active power discharged from the UCAP while providing reactive power support to the grid is minimal.

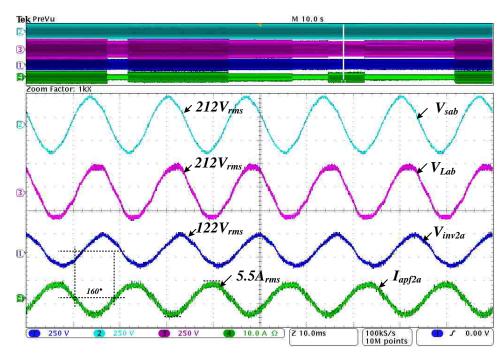

The bi-directional capability of the dc-dc converter which is necessary for absorbing excess power from DERs in renewable intermittency smoothing applications is shown in Fig. 8 (d) which is the zoomed in view of zone 5. To fully utilize the bi-directional capability of the inverter it must be controlled in such a way that it absorbs active power from the grid. In order to achieve this objective  $i_{qref}$  is set to positive 7A and it can be observed that  $I_{apf2a}$  and  $V_{sa}$  are 180° apart and their RMS values are 5A and 122V respectively which translates to  $P_{inv}$  of -1830W. The bi-directional dc-dc converter shifts its operation from Boost mode to Buck mode to absorb the power from the grid. Therefore, in zone 5 of Fig. 8 (a) it can be observed that both  $I_{ucav}$  and  $I_{dclnkav}$  are negative while the  $V_{fdc}$  is still constant at 260V and  $E_{cap}$  is increasing slowly while the UCAP is being charged from the power absorbed from the grid.

The differences between the simulation and experimental results for the inverter and the dc-dc converter during active power support (zones 3 and 4), reactive power support (zones 1 and 7) and renewable intermittency smoothing (zone 7) modes are compared in Table I. It can be seen from  $P_{inv}$  and  $Q_{inv}$  values obtained from simulation and experiment that there is a very close match between the two sets of results in all the four zones. The active power input to the inverter  $P_{dc}$  is also listed in Table I which was obtained from the product of the  $V_{fdc}$  and  $I_{dclnkav}$  which are available from Fig. 8 (a). Based on the experimental values of  $P_{dc}$  and  $P_{inv}$  the efficiency of the inverter can be

computed and it can be observed that the inverter is around 95% efficient in zone 3 and 93% efficient in zones 4 and 5. In zone 7 while providing reactive power support to the grid; the inverter consumes minimal active power from the grid which is for the dc-link capacitor losses which are not provided by the dc-dc converter therefore, inverter efficiency is not computed for this zone and it is not a performance measurement criterion when the system is in reactive power support mode.

TABLE I Shunt Inverter and Dc-dc converter Results

| INVERTER SIMULATION AND EXPERIMENTAL RESULTS |                |                |                 |                      |                                  |       |

|----------------------------------------------|----------------|----------------|-----------------|----------------------|----------------------------------|-------|

| Zone                                         | $P_{inv}(sim)$ | $Q_{inv}(sim)$ | $P_{inv}(\exp)$ | $Q_{inv}$ (exp)      | $P_{dc}\left(\mathbf{W}\right)$  | η (%) |

| $3 (i_{qref} = -12)$                         | 2701           | 466            | 2703.3          | 476.66               | 2885.8                           | 94.66 |

| $4 (i_{qref} = -10)$                         | 1731.6         | 277.3          | 1712.1          | 301.88               | 1781.6                           | 92.79 |

| $5 (i_{qref} = +6)$                          | -1791          | 75             | -1828           | 63                   | -1675.4                          | 92.97 |

| $7 (i_{dref} = -15)$                         | -92            | 3570           | -127            | 3657                 | -                                | -     |

| DC-DC CONVERTER EXPERIMENTAL RESULTS         |                |                |                 |                      |                                  |       |

| Zone                                         | $E_{cap}(V)$   | $I_{ucav}(A)$  | $I_{dclnk}(A)$  | $P_{in}(\mathbf{W})$ | $P_{out}\left(\mathbf{W}\right)$ | η (%) |

| 3                                            | 126.0          | 28.0           | 10.9            | 3528                 | 3193                             | 89.92 |

| 4                                            | 94.0           | 25.0           | 6.8             | 2350                 | 2098                             | 89.28 |

| 5                                            | 110.0          | -10.8          | -5.2            | -1288                | -1358                            | 87.48 |

The bi-directional dc-dc converter experimental results for zones 3, 4 and 5 where the converter provides active power support to the grid and absorbs active power from the grid are also presented in Table I. The voltage and current values listed in the table are the average for the given zone. It is important to note that the converter is around 90% efficient in zones 3, 4 and around 88% in zone 5 which indicates that the UCAP and bi-directional dc-dc converter operate efficiently while supplying active power to the grid and even while absorbing active power from the grid. It must be noted that the dc-dc converter efficiency can be further improved as these products become more prevalent on the distribution grid by reducing the switching losses using soft-switching schemes or

through the use of resonant topologies where the converter impedance and switching frequency vary to provide zero voltage switching thereby reducing the switching losses.