# Scholars' Mine

**Doctoral Dissertations**

Student Theses and Dissertations

Fall 2015

# On the deployment of on-chip noise sensors

Tao Wang

Follow this and additional works at: https://scholarsmine.mst.edu/doctoral\_dissertations

Part of the Computer Engineering Commons Department: Electrical and Computer Engineering

## **Recommended Citation**

Wang, Tao, "On the deployment of on-chip noise sensors" (2015). *Doctoral Dissertations*. 2462. https://scholarsmine.mst.edu/doctoral\_dissertations/2462

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

## ON THE DEPLOYMENT OF ON-CHIP NOISE SENSORS

by

# TAO WANG

# A DISSERTATION

Presented to the Faculty of the Graduate School of the

# MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

## DOCTOR OF PHILOSOPHY

in

## COMPUTER ENGINEERING

2015

Approved by

Dr. Yiyu Shi, Advisor Dr. Daryl Beetner Dr. Jun Fan Dr. Minsu Choi Dr. Maggie Cheng

Copyright 2015 TAO WANG All Rights Reserved

### ABSTRACT

The relentless technology scaling has led to significantly reduced noise margin and complicated functionalities. As such, design time techniques per se are less likely to ensure power integrity, resulting in runtime voltage emergencies. To alleviate the issue, recently several works have shed light on the possibilities of dynamic noise management systems. Most of these works rely on on-chip noise sensors to accurately capture voltage emergencies. However, they all assume that the placement of the sensors is given. It remains an open problem in the literature how to optimally place a given number of noise sensors for best voltage emergency detection. In the first chapter, the problem of noise sensor placement is defined along with a novel sensing quality metric (SQM) to be maximized.

The threshold voltage for noise sensors to report emergencies serves as a critical tuning knob between the system failure rate and false alarms. In the second chapter, the problem of minimizing the system alarm rate subject to a given system failure rate constraint is first formulated. It is further shown that with the help of  $I_{ddq}$  measurements during testing which reveal process variation information, it is possible and efficient to compute a per-chip optimal threshold voltage threshold.

In the third chapter, a novel framework to predict the resonance frequency using existing on-chip noise sensors, based on the theory of 1-bit compressed sensing is proposed. The proposed framework can help to achieve the resonance frequency of individual chips so as to effectively avoid resonance noise at runtime.

### ACKNOWLEDGMENTS

I would like to thank my PhD advisor, Professor Yiyu Shi, for supporting me during these past five years. Prof. Shi is the funniest advisor and one of the smartest people I know. I hope that I could be as lively, enthusiastic, and energetic as Prof. Shi. Prof. Shi has been supportive and has given me the freedom to pursue various projects without objection. He has also provided insightful discussions about the research. I also have to thank the members of my PhD committee, Professors Daryl Beetner, Jun Fan, Minsu Choi and Maggie Cheng for their helpful career advice and suggestions in general.

I thank all the members in Prof. Shi's group, you gave me lots of help during my PhD. I am so happy to have you in my life. I also thank my friends in Rolla for providing support and friendship that I needed.

I especially thank my family. My hard-working parents have sacrificed their lives for me and provided unconditional love and care. I love them so much, and I would not have made it this far without them. Special thanks to the best gifts in my life, my two daughters, who filled my life up with love and warmth.

# TABLE OF CONTENTS

v

# Page

| ABSTRACT ii                                                                                 | ii |

|---------------------------------------------------------------------------------------------|----|

| ACKNOWLEDGMENTS ir                                                                          | v  |

| LIST OF ILLUSTRATIONS vii                                                                   | ii |

| LIST OF TABLES                                                                              | х  |

| SECTION                                                                                     |    |

| 1. EAGLE-EYE: A NEAR-OPTIMAL STATISTICAL FRAMEWORK FOR<br>NOISE SENSOR PLACEMENT            | 1  |

| 1.1. INTRODUCTION                                                                           | 1  |

| 1.2. PRELIMINARIES                                                                          | 3  |

| 1.2.1. Microarchitecture-level Runtime Noise Management                                     | 3  |

| 1.2.2. Noise Sensor Placement                                                               | 4  |

| 1.3. PROBLEM FORMULATION                                                                    | 5  |

| 1.3.1. Problem Statement                                                                    | 5  |

| 1.3.2. Sensing Quality Metric (SQM)                                                         | 6  |

| 1.4. ALGORITHM                                                                              | 8  |

| 1.4.1. Overview                                                                             | 8  |

| 1.4.2. Proof of Optimality                                                                  | 8  |

| 1.5. EXPERIMENTAL RESULTS                                                                   | 2  |

| 1.6. CONCLUSION $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $1$ | 7  |

| 2. ON THE OPTIMAL THRESHOLD VOLTAGE COMPUTATION OF ON-<br>CHIP NOISE SENSORS                | 8  |

| 2.1. ABSTRACT                                                                               | 8  |

|    | 2.2. | INTRO  | ODUCTION                                                                                          | 18 |

|----|------|--------|---------------------------------------------------------------------------------------------------|----|

|    | 2.3. | PREL   | IMINARIES                                                                                         | 21 |

|    |      | 2.3.1. | Runtime Noise Management Systems                                                                  | 21 |

|    |      | 2.3.2. | Impact of Soft Threshold Voltage                                                                  | 22 |

|    | 2.4. | PROB   | LEM FORMULATION                                                                                   | 24 |

|    | 2.5. | UNIF   | ORM SOFT THRESHOLD COMPUTATION                                                                    | 26 |

|    |      | 2.5.1. | An Intuitive Approach                                                                             | 26 |

|    |      | 2.5.2. | An Exact Approach                                                                                 | 27 |

|    | 2.6. | PER-0  | CHIP SOFT THRESHOLD COMPUTATION                                                                   | 30 |

|    |      | 2.6.1. | Per-Chip Optimal Threshold Computation with Fixed Hard<br>Threshold                               | 30 |

|    |      | 2.6.2. | Per-Chip Soft Threshold Computation with Varying Hard Threshold                                   | 35 |

|    | 2.7. | EXPE   | RIMENTAL RESULTS                                                                                  | 37 |

|    | 2.8. | CONC   | CLUSIONS                                                                                          | 41 |

| 3. | RES  | ONAN   | APRESSED SENSING BASED FRAMEWORK FOR BUILT-IN<br>CE FREQUENCY PREDICTION USING ON-CHIP NOISE SEN- | 44 |

|    | 3.1. | ABST   | RACT                                                                                              | 44 |

|    | 3.2. | INTRO  | ODUCTION                                                                                          | 44 |

|    | 3.3. | PREL   | IMINARIES AND MOTIVATION                                                                          | 47 |

|    |      | 3.3.1. | On-Die Capacitance Breakdown and Its Impact on Power Supply Noise                                 | 47 |

|    |      | 3.3.2. | Resonance Frequency Variation                                                                     | 48 |

|    |      | 3.3.3. | On-Chip Noise Sensors                                                                             | 49 |

|    | 3.4. | PROP   | OSED FRAMEWORK                                                                                    | 51 |

|    |      | 3.4.1. | Overview                                                                                          | 51 |

|    |      | 3.4.2. | Load Generator                                                                                    | 53 |

|    |      | 3.4.3. | Measurement Matrix Calculation                                                                    | 54 |

| 3.4.4. Resonance Frequency Prediction | 56     |

|---------------------------------------|--------|

| 3.5. EXPERIMENTAL RESULTS             | 58     |

| 3.6. CONCLUSIONS                      | 62     |

| BIBLIOGRAPHY                          | <br>65 |

| VITA                                  | <br>69 |

# LIST OF ILLUSTRATIONS

# Figure

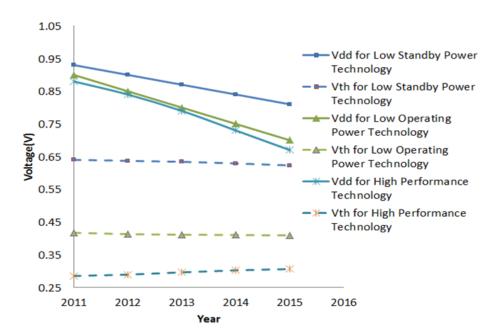

| 1.1. | Supply voltage and threshold voltage scaling trends in International Technology Roadmap for Semiconductors[1]. By 2015 the voltage margin for Low Standby Power (LSP) technology will drop below $0.2 \text{ V}$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1  |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

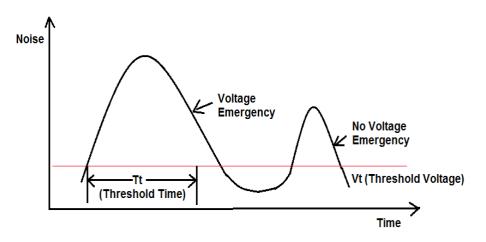

| 1.2. | Definition of voltage emergency                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 2  |

| 1.3. | Proposed algorithm for noise sensor placement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 9  |

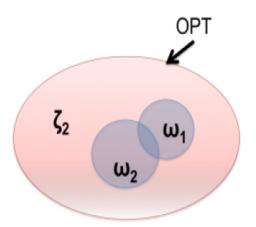

| 1.4. | Variation space coverage of SQM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11 |

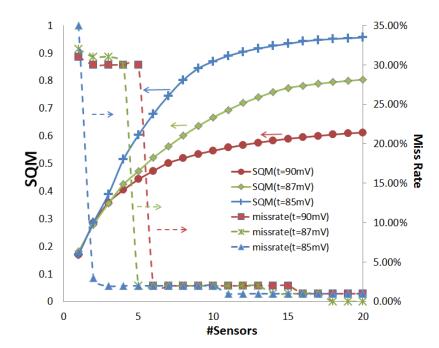

| 1.5. | SQM and miss rate vs. the number of sensors of N2 $\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\hfill\h$ | 15 |

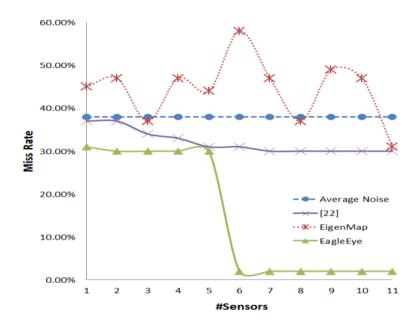

| 1.6. | Miss rate vs. the number of sensors for different approaches (threshold $= 90 \text{ mV}, \text{ N2}$ )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 16 |

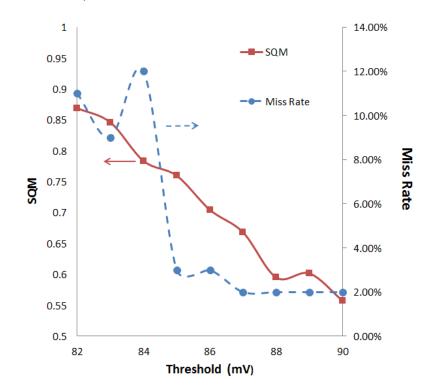

| 1.7. | SQM and miss rate vs. threshold (number of sensors = 10, N2) $~~.~.~$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 16 |

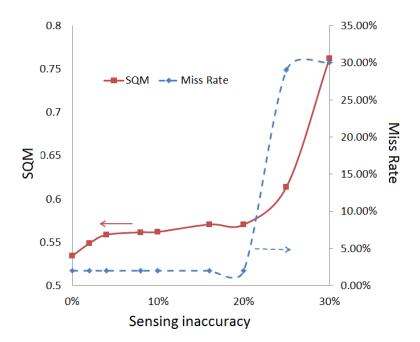

| 1.8. | SQM and miss rate vs. sensing inaccuracy (threshold = 90 mV, $\#$ of sensors = 10, N2) $\dots \dots \dots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 17 |

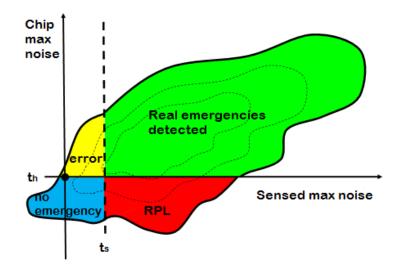

| 2.1. | Joint distribution of the chip maximum noise and sensed maximum noise                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 23 |

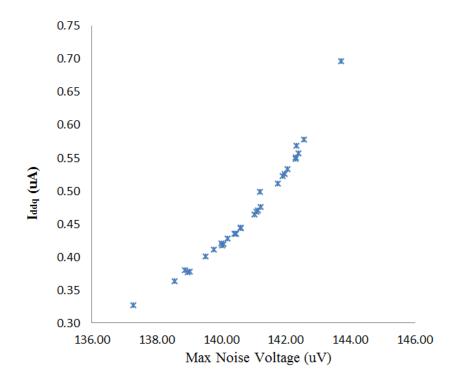

| 2.2. | Relation between $I_{ddq}$ and max noise. The experiment is done by<br>HSPICE simulation of a NAND gate in 45nm node $\ldots \ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 31 |

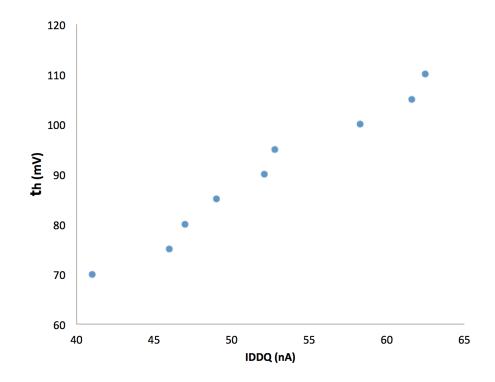

| 2.3. | Relation between $I_{ddq}$ and hard threshold $t_h$ . The experiment is done<br>by HSPICE simulation of a NAND Gate in 45nm node $\ldots \ldots \ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 35 |

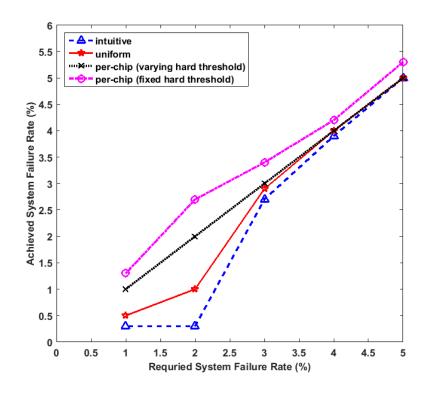

| 2.4. | Achieved system failure rate vs. required system failure rate for different soft threshold computation methods using design N1 $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 39 |

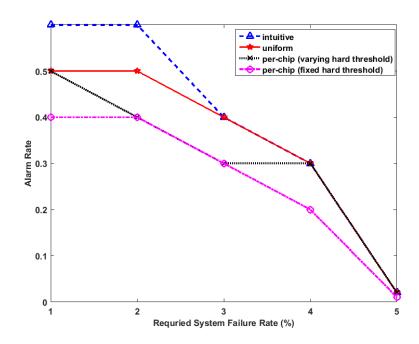

| 2.5. | Alarm rate vs. required system failure rate for different soft threshold computation methods using design N1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 40 |

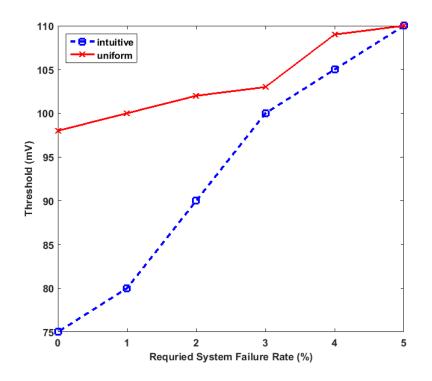

| 2.6. | Intuitive and exact uniform thresholds vs. required system failure rate using design N1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 41 |

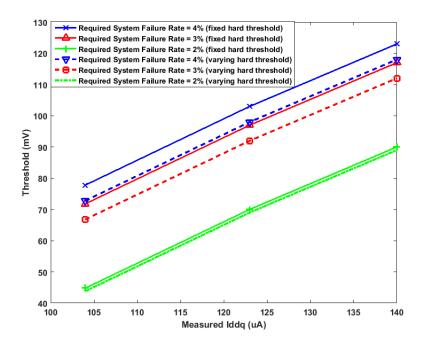

| 2.7. | Per-chip threshold vs. measured $I_{ddq}$ at different required system failure rate using design N1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 42 |

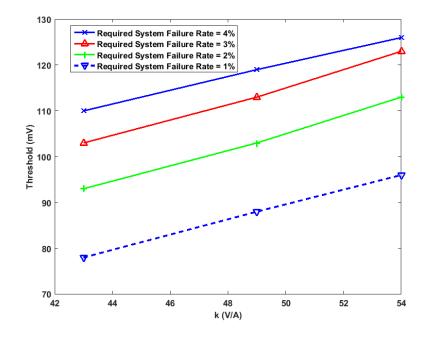

| 2.8. | Per-chip (varying hard threshold) threshold vs. $\kappa$ at different required system failure rate using design N1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 42 |

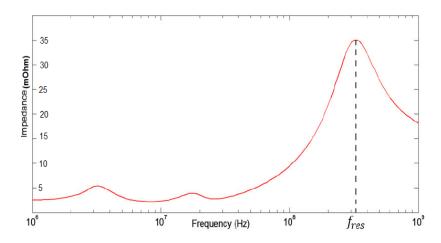

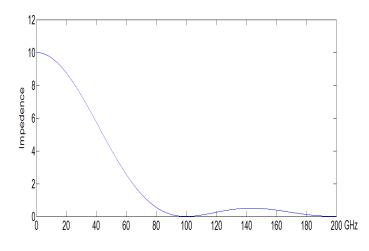

| 3.1. | A representative PDN impedance from an in-house 45 nm industrial design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 46 |

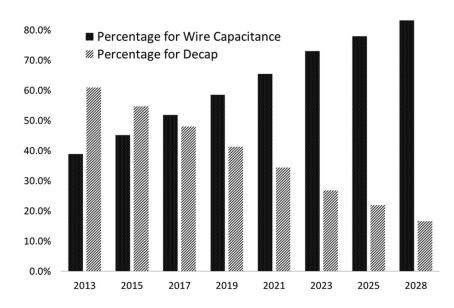

| 3.2.  | Percentage of decap and wire capacitance in on-die PDN capacitance [1].<br>Wire capacitance will dominate in the near future                                                                                                  | 49 |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

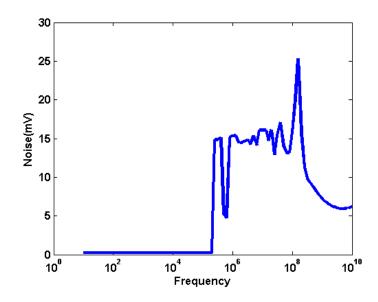

| 3.3.  | Resonance noise in PDN for load patterns with different frequencies .                                                                                                                                                         | 50 |

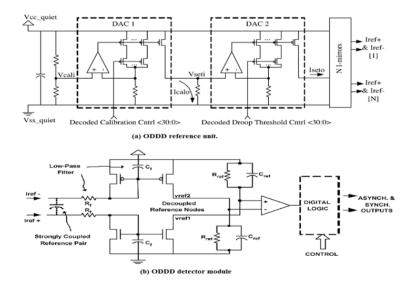

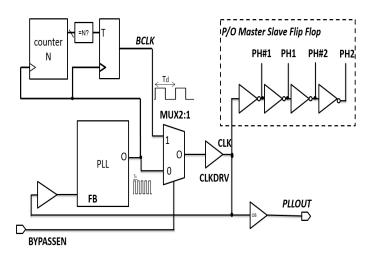

| 3.4.  | On-Die Droop Detector (ODDD) proposed in [23] $\ldots \ldots \ldots$                                                                                                                                                          | 51 |

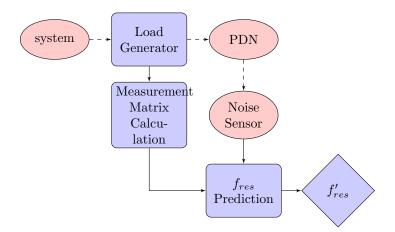

| 3.5.  | Per-chip resonance frequency prediction framework $\ldots \ldots \ldots$                                                                                                                                                      | 52 |

| 3.6.  | Load generation scheme                                                                                                                                                                                                        | 53 |

| 3.7.  | Spectrum of a single triangular waveform with 10 ps rise and fall time                                                                                                                                                        | 54 |

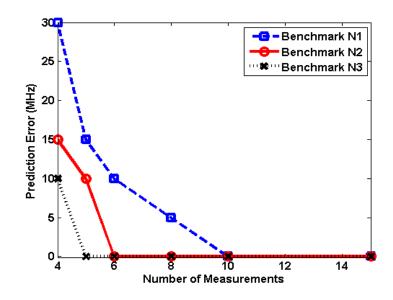

| 3.8.  | Prediction error vs. number of measurements. Sensor threshold = $20$ mV                                                                                                                                                       | 61 |

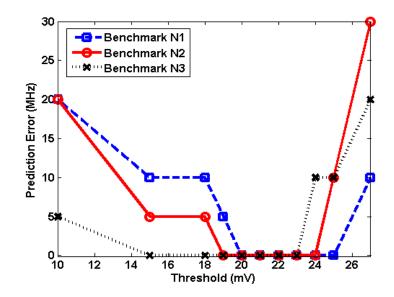

| 3.9.  | Prediction error vs. sensor threshold. Number of measurements $= 10$                                                                                                                                                          | 63 |

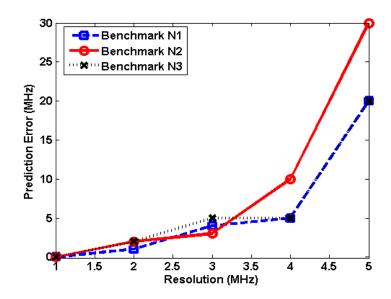

| 3.10. | Prediction error vs. minimum resolution. Number of measurements = $10$ , sensor threshold = $20 \text{ mV} \dots \dots$ | 63 |

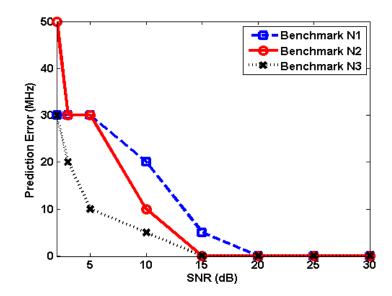

| 3.11. | Prediction error vs. noise in sensor measurements. Number of measurements = $10$ , sensor threshold = $20 \text{ mV} \dots \dots \dots \dots \dots \dots$                                                                     | 64 |

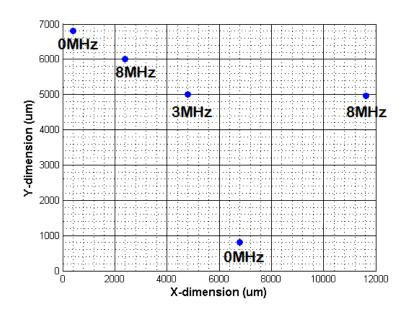

| 3.12. | Prediction error with sensors in different locations for Benchmark N1.<br>Number of measurements = 10, sensor threshold = $20 \text{ mV} \dots \dots$                                                                         | 64 |

# LIST OF TABLES

| 7 | $\Gamma a$ | bl  | le  |

|---|------------|-----|-----|

| _ |            | ~ - | - ~ |

| 1.1. | Benchmark information                                                                                                                                                                                          | 12 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2. | Miss rate comparisons (#sensor = 10, t = 90mV) $\ldots \ldots \ldots$                                                                                                                                          | 13 |

| 1.3. | Runtime comparisons (#sensor = 10, t = 90mV) $\dots \dots \dots \dots$                                                                                                                                         | 14 |

| 2.1. | Benchmark information. #i, #n, #r stand for the number of current sources, nodes and resistance, respectively.                                                                                                 | 38 |

| 2.2. | Comparison of different soft threshold computation methods $\ldots$ .                                                                                                                                          | 43 |

| 3.1. | On-die capacitance breakdown of a 32 nm DDR I/O test chip $~\ldots~$                                                                                                                                           | 48 |

| 3.2. | Benchmark information. $\#n$ , $\#r$ , $\#c$ , $\#l$ stand for the number of nodes, resistance, capacitance and inductance respectively                                                                        | 60 |

| 3.3. | Impedance information for each design. The resonance frequency $f_{res}$ , peak width at half maximum $\Delta f$ , peak impedance $Z_p$ and DC impedance $Z_0$ are reported.                                   | 60 |

| 3.4. | Comparison of the number of measurements needed (#N) between the proposed method and the frequency sweeping based methods to achieve 1 MHz maximum error. The MATLAB runtime of Algorithm 3.1 is also reported | 60 |

## 1. EAGLE-EYE: A NEAR-OPTIMAL STATISTICAL FRAMEWORK FOR NOISE SENSOR PLACEMENT

## **1.1. INTRODUCTION**

The continuous increase in power density brought by the CMOS scaling has resulted in a monotonic decrease of the supply voltage. On the other hand, to avoid excessive leakage power, the threshold voltage cannot be scaled at the same pace, as illustrated in Figure 1.1 [1]. The reduced noise margin, along with the boost in functional complexity, has posed severe threat to the power integrity of the chips. Noise margin violation, which is also known as voltage emergency, leads to undesired effects such as delay degradation, timing violation, etc. which may finally cause system malfunctioning [11, 33].

Figure 1.1: Supply voltage and threshold voltage scaling trends in International Technology Roadmap for Semiconductors[1]. By 2015 the voltage margin for Low Standby Power (LSP) technology will drop below 0.2 V

The strict definition of voltage emergency is the situation when the amplitude of the noise exceeds a given threshold voltage Vt for a minimum duration (threshold time) of  $T_t$  [24]. In other words, the definition captures not just the amplitude of noise, but also the temporal span. An example is shown in Figure 1.2, the duration of the first peak is longer than the threshold time to cause voltage emergency. On the other hand, the second peak is too short to cause it. The rationale behind this is that the impact of power supply noise on timing is more of an accumulative effect, and a very narrow voltage droop is unlikely to cause any timing issues. Conventionally,

Figure 1.2: Definition of voltage emergency

on-chip power integrity is ensured through design time approaches such as decap insertion [5, 35] or metal wire sizing [20] [15]. However, increasingly stringent design constraints with narrowed noise margins and complicated functionalities make such practices expensive, if not impossible, to address all power integrity issues at design time. As such, a recent trend of research innovation [11, 16, 27, 33] is to employ runtime noise management systems at the microarchitecture level to address the power integrity issue. Most of them adopted a centralized control system with distributed noise sensors, and were based on the detection of voltage emergencies. Obviously, the quality of such a microarchitecture level solution with runtime noise management greatly depends on the locations of those distributed noise sensors. Such a problem is, however, largely not addressed in literature.

How to place a limited number of noise sensors is important in order to minimize the hardware overhead and, at the same time, minimize the miss rate of voltage emergency detections, where the miss rate is defined as the probability of noise sensors not detecting any voltage emergencies, while a voltage emergency in fact occurring somewhere on the chip. Failure to detect voltage emergencies may lead to severe performance penalties. For example, the study in [11] showed that undetected voltage emergencies can induce as much as 17% delay degradation. The runtime noise management systems and the associated noise sensor placement problem will become increasingly important in the near future with even tighter noise margin and higher computing demand. Hence a rigorous study in this area is warranted.

In this chapter, the noise sensor placement problem for microarchitecturelevel runtime noise management is formally formulated, and a statistical near-optimal framework is devised to solve it while considering the correlated noise distributions. The main contents of this chapter are as follows: 1) A formal formulation of the noise sensor placement problem for micro-architecture level runtime noise management; 2) A novel metric called sensing quality metric (SQM) to quantitatively evaluate the quality of any noise sensor placement; 3) An efficient approximation algorithm with O(sn) complexity, where n is the number of candidate nodes for sensor placement and s is the number of sensors placed; 4) A proof that the proposed algorithm can achieve the best-possible approximation to the optimal solution among all polynomialcomplexity algorithms.

The remainder of this chapter is organized as follows. Related background information is reviewed in Section 1.2, and the noise sensor placement problem is formulated in Section 1.3. Proposed algorithm is presented in Section 1.4. Concluding remarks are given in Section 1.6.

### **1.2. PRELIMINARIES**

**1.2.1.** Microarchitecture-level Runtime Noise Management. Most existing microarchitecture-level runtime noise management systems adopt a structure with distributed noise sensors and a centralized control system where the voltage emergencies are determined by comparing the sensed noise with a threshold. There are two different types of thresholds. Following the same conventions as [11], in this chapter the hard threshold as the strict constraint beyond which the system will malfunction (e.g. timing violation) are defined. On the other hand, the soft threshold is less strict, beyond which the system becomes less reliable due to effects such as delay degradation. Noise emergency is defined as the time when the noise surpasses/violates either the soft or the hard threshold, depending on the application. Depending on the way voltage emergencies are handled, microarchitecture-level runtime noise management can be divided into three different categories: retroactive system with soft threshold [16, 27], retroactive system with hard threshold [33], and proactive system with soft threshold [11].

Retroactive systems with soft threshold voltage use noise sensors to monitor the supply voltage for specific soft threshold crossings, which indicates potential system reliability reduction. When this occurs, the instruction execution will then be throttled at the microarchitecture-level to prevent potential system failures. However, significant overhead is induced by over-protecting the systems to ensure correctness. Retroactive systems with hard threshold improve such scheme by allowing the errors to occur, but system states need to be rolled back to restore the correct values once the noise emergency is detected. Proactive systems with soft threshold, on the other hand, try to recognize and track the patterns of activities that may lead to voltage emergencies, and hence invoke the throttling mechanism based on the prediction to prevent voltage emergencies from actually happening.

In either of these approaches, the optimal deployment of noise sensors (e.g., sensor design, placement, etc.) plays a central role to accurately capture voltage emergencies with lowest overhead.

**1.2.2.** Noise Sensor Placement. For dynamic noise management such as throttling (e.g.[11, 33]), it is only needed to know whether noise emergencies have

occurred rather than the detailed noise map, which requires significantly less information. Consider a motivational design with only one single (and fixed) noise hot spot that is uncorrelated to other parts on the chip. In this case, only one noise sensor right at the hot spot is sufficient to detect all emergencies.

For noise sensor placement, the goal is to provide a binary decision on whether a voltage emergency has occurred somewhere on chip. The goal of the noise sensor placement is to accurately monitor and report the voltage emergency (where the chip max noise larger than a given threshold t) with a limited number of noise sensors and the binary information provided by the noise sensors.

### **1.3. PROBLEM FORMULATION**

In this section, it is formally formulated the noise sensor placement problem, and the target metric to be optimized.

**1.3.1.** Problem Statement. It is assumed that the following information is given as input: 1) n candidate nodes in the power grid for noise sensor placement;2) threshold voltage t for the voltage emergencies, which is specified by the designer and is the same for all the sensors; 3) the total number of noise sensors t to be placed.

The objective is to identify s nodes  $r_i (1 \le i \le s)$  out of the n candidates to be sensed, so that the miss rate of the voltage emergency detection is minimized. The candidate nodes are those which allow noise sensor placement. Again, the miss rate is defined as the probability that the placed noise sensors do not detect any voltage emergencies while a voltage emergency does occur somewhere on chip, including those places that are not allowed to place a noise sensor. Note that the actual locations of the sensors can be anywhere in the area adjacent to  $r_i$ . However, for the simplicity of presentation, in this chapter it is said a sensor is being placed at  $r_i$  if the sensor is used to sense the voltage at  $r_i$ . In the formulation, one challenging problem is to quantitatively evaluate the miss rate with given noise sensor placements. As it is impossible to obtain all possible voltage drop (noise) waveforms through transient simulation, same as [37] it is proposed to model the noise  $\Delta V_i$ , including the fluctuations in the reference voltage, noise sensor process variation, etc., at any node i of the power grid as a random variable. Those random variables have different means and variances, and are correlated spatially. Specifically, the noise of i-th node, either Gaussian or non-Gaussian, can be represented as [37].

$$\Delta V_i = F_i(\Delta X) = H_i(G) + \Delta R_i \tag{1.1}$$

where  $\Delta X$  is a set of common correlated factors that result the variation of voltage noise through function  $F_i$ . Through modelling techniques, the noise can be represented by function  $H_i(G)$ , where G is an m-dimensional uncorrelated random variable that models the global variation sources (common for all nodes) which can be extracted from  $\Delta X$  through either principle component analysis (PCA) for Gaussian or independent component analysis (ICA) for non-Gaussian distributions of  $\Delta X$ . The dimension of m decides the approximation accuracy. In addition,  $\Delta R_i$  models the independent source of noise variation specific to node *i* which comes from model error, noise sensor process variation, fluctuations in reference voltage. In addition, the functional forms of  $F_i$  and  $H_i$  can be either linear or nonlinear [7]. In the context of such statistical formulation, it is ready to put forward a novel sensing quality metric that can be computed without involving Monte Carlo simulations.

**1.3.2.** Sensing Quality Metric (SQM). Mathematically, the miss rate can be cast as

Miss Rate =

$$P(\Delta V_{max} \le t | \max(\Delta V_{r_i} (1 \le i \le s)))$$

(1.2)

where  $\Delta V_{max}$  is the maximum noise among all the nodes in the power grid,  $\Delta V_{r_i} (1 \le i \le s)$  are the noise at the *s* nodes where the sensors are connected, and *t* is the threshold voltage.

Equation (1.2) still provides little insight into the optimization problem. It can further simplified by using the Bayes law as follows.

$$P(\Delta V_{max} \ge t | \max(\Delta V_{r_i}(1 \le i \le s)) \le t)$$

$$=1 - P(\Delta V_{max} \le t | \max(\Delta V_{r_i}(1 \le i \le s)) \le t)$$

$$=1 - \frac{P(\Delta V_{max} \le t, \max(\Delta V_{r_i}(1 \le i \le s)) \le t)}{P(\max(\Delta V_{r_i}(1 \le i \le s)) \le t)}$$

$$=1 - \frac{P(\Delta V_{max} \le t)}{P(\max(\Delta V_{r_i}(1 \le i \le s)) \le t)}$$

(1.3)

where the last equality utilizes the fact that if the maximum on-chip nois  $\Delta V_{max}$  is below threshold t, then the noise at any node must be below it.

Since for a given design,  $P(\Delta V_{max} \leq t)$  is a constant independent of the sensor placement, it becomes clear that, in order to minimize the miss rate, it is equivalent to minimizing the following metric

$$P(\max(\Delta V_{r_i}(1 \le i \le s)) \le t) \tag{1.4}$$

Or alternatively, it is equivalent to maximize

$$P(\max(\Delta V_{r_i}(1 \le i \le s)) \ge t)$$

(1.5)

Accordingly, the following definition can be derived for the Sensing Quality Metric (SQM).

Definition 1: The Sensing Quality Metric (SQM) for a set of nodes to be sensed is defined as the probability of the maximum noise among them goes beyond the threshold voltage as in Equation (1.5). Intuitively, the SQM can be interpreted as the probability that a voltage emergency can be detected for the given sensor placement. In order to compute SQM, it is needed to evaluate the statistical max of a set of correlated random variables. Such techniques have been developed in the recent statistical timing analysis and power analysis research, for example, [37] for Gaussian random variables and [7] for non-Gaussian ones. The essence of those techniques is to represent the random variables as a function of the underlying common sources of process variations such as in (1.1).

### 1.4. ALGORITHM

**1.4.1. Overview.** Considering SQM, the objective turns to find s nodes among n candidates so that SQM of the set S of all selected nodes is maximized. A nave approach would be to enumerate all the possible combinations, which results in a complexity of  $\binom{n}{s}$ , which is exponential to s. Apparently, this is not a feasible method for large n and relatively large s in the problem.

To balance the complexity and quality of the solution, it is resorted to a compact greedy method, as shown in Figure 1.3. Basically, during each iteration, it always selects a node that could maximally increase the SQM of the set of selected nodes so far. By propagating the canonical form as shown in Equation (1.1),  $SQM(S \cup k)$  could be easily calculated with the statistical max operation [7]. Since there are totally *s* iterations and the maximum number of SQM to be calculated is n, the algorithm complexity could be easily analysed as O(sn). The simplicity of this algorithm prompts us to ask the following question: how good is the resulted solution? Will it be far from the optimal solution? In Section 1.4.2, the proof of optimality will be presented.

**1.4.2. Proof of Optimality.** In this section, the greedy method shown in Figure 1.3 is fomally proved to be the best-possible polynomial complexity approximation algorithm for maximizing the SQM.

Input: Set of the candidate node set  $N = \{1, ..., n\}$ ; the number of sensors to be placed *s*; threshold voltage *t*; Output: Set of selected nodes to be sensed  $S=\{r_1, r_2, ..., r_s\}$ ; Set  $S = \emptyset$ , with SQM(S) = 0; FOR  $\underline{i} = 1:s$ Choose  $k \in N$ , such that  $SQM(S \cup k)$  is maximized; N = N/k;  $S = S \cup k$ ; END FOR

Figure 1.3: Proposed algorithm for noise sensor placement

The proof is inspired by a different interpretation of the SQM. Represented by the function form such as in Equation (1.1), the statistical noise of each node can be seen to lie in the variation space  $\Omega(\delta Y)$ , which is spanned by the random variables corresponding to global and local variation as defined in (1.1).

As such, the SQM of node *i* actually defines the mapping from  $\Delta v_i$  to the subspace  $\omega_i \subseteq \Omega$  as

$$\omega_i = \{\Delta Y | \Delta v_i = H(\Delta G) + \Delta R_i \le t\}$$

(1.6)

In other works, the SQM of a single node covers a subspace in  $\Omega$ , and the SQM of a set of nodes  $T = (n_i (1 \le i \le s))$  is the union of subspaces occupied by each of there nodes.

$$\omega_{SQM} = \bigcup \omega_{n_i} (1 \le i \le s) \tag{1.7}$$

Thus, SQM can also be quantitatively evaluated as the portion of the entire variation space occupied by selected nodes

$$SQM(T) = \frac{|\omega_{SQM}|}{|\Omega|}$$

(1.8)

where  $|\bullet|$  is the Lebesgure measure (i.e., probability-weighted volume of the variation space).

From (1.7) and (1.8), it is clear that maximizing SQM(T) is equivalent to solving the max variation space cover (MVSC) problem, where it is needed to find a set of subspaces whose union covers the maximum volume in the variation space. The algorithm in Figure 1.3 can then be interpreted as to select a subspace for maximum incremental coverage at each iteration.

A related problem, the max set cover (MSC) problem [10], has been extensively studied and proven to be NP-hard. The MSC problem can be stated as follows: Given a set  $M = a_i$ ,  $a_n$ , a collection H composed of subsets  $l_i \subseteq M$  and an integer k, the MSC problem tries to select k elements from H such that they cover the maximum number of elements in M. However, the proofs and conclusions in the MSC problem do not directly apply to the MVSC problem, as the former is defined in discrete space, while the latter works in continuous space. Similar to MSC problem, the MVSC problem is also NP-Hard. It will be showed in the following that that the proposed algorithm in Figure 1.3 can achieve the best polynomial approximation bound.

Corollary 1: The best polynomial-complexity approximation of MVSC is at most  $1 - \frac{1}{e}$ .

Proof: It comes from that the MVSC problem is the super-set of the MSC problem, and the MSC problem has best polynomial-complexity approximation  $1 - \frac{1}{e}$  [10].

Next, the optimality of the greedy algorithm in Figure 1.3 will be proved using the variation space interpretation. As shown in Figure 1.4, OPT can be defined as the maximally covered variation space by the optimally placed s noise sensors through a black-box algorithm.  $\omega_i$  is the space covered by the sensor placed in the i-th iteration of the algorithm in Figure 1.3, and  $\xi_i$  is the space that has not been covered after the i-th iteration, i.e.,

$$|\xi_i| = |OPT| - \sum_{j=1}^{i} |\omega_j|$$

(1.9)

Figure 1.4: Variation space coverage of SQM

The algorithm in Figure 1.3 has the following properties.

Lemma 1:  $|\omega_{i+1}| \ge \frac{|\xi_i|}{s}$ .

Proof: Since the optimal solution uses s subspaces to cover OPT, after i-th iteration, there must exist an unselected subspace  $\omega_{i+1}'$  covering at least  $\frac{1}{s}$  fraction of  $\xi_i$  (otherwise  $\xi_i$  and thus OPT cannot be covered by the union of any s subspaces). Since in the (i + 1)-th iteration the algorithm selects the subspace which maximally reduces the uncovered space, the selected subspace  $\omega_{i+1}$  should reduce as much uncovered subspace as  $\omega_{i+1}'$  does. Thus, it can be concluded that  $\omega_{i+1}$  should have a volume of at least  $\frac{|\xi_i|}{s}$ .

Lemma 2 :  $|\xi_{i+1}| \le (1 - \frac{1}{s})^{i+1} |OPT|$

Proof: By induction. For i = 0, Lemma 2 is true; Assume Lemma 2 is true for i, i.e.,

$$|\xi_i| \le (1 - \frac{1}{s})^i |OPT|$$

(1.10)

Thus from Lemma 1,

$$|\xi_{i+1}| = |OPT| - \sum_{j=1}^{i+1} |\omega_j| = |\xi_i| - |\omega_{i+1}| \le |\xi_i| - \frac{|\xi_i|}{s} \le (1 - \frac{1}{s})^{i+1} |OPT| \quad (1.11)$$

From Lemma 1 and Lemma 2, the following theorem can be proved.

Theorem 2: The algorithm in Figure 1.3 is  $(1 - \frac{1}{e})$  approximation of OPT. Proof: Replace s with i + 1 in Lemma 2,

$$|\xi_s| \le (1 - \frac{1}{s})^s |OPT| \le \frac{|OPT|}{s}$$

(1.12)

From Corollary 1 and Theorem 2, it is straightforward to get the following corollary.

Corollary 2: The proposed greedy algorithm in Figure 1.3 is the best-possible polynomial time algorithm for maximizing SQM.

#### 1.5. EXPERIMENTAL RESULTS

The proposed greedy algorithm in Figure 1.3 is implemented in C++ on a machine with two quad-core 2.4 GHz Intel Xeon E5620 CPUs and 96 GB memories. A similar method as [37] is adopted to obtain the statistical noise model  $Z_i$  for Vdd nets N1, N2 and N3, which are extracted from real industrial power grid designs. As summarized in Table 1.1, the #i, #n and #r stand for the number of current sources, the number of nodes and the number of resistors of each net, respectively. In addition, it is assumed that all the noises are Gaussian, and apply PCA to get the linear canonical form [37]. A zero-mean Gaussian random variable  $\Delta R_i$  is further added to model the independent noise variation of each node which may come from PCA model error, noise sensor process variation, fluctuations in reference voltage, etc. In the experiments, threshold time  $T_t$  is set to 1ns. To compare the quality

Table 1.1: Benchmark information

| Benchmark | #i        | #n      | #r      |

|-----------|-----------|---------|---------|

| N1        | $5,\!387$ | 5,387   | 4,720   |

| N2        | 18,419    | 19,240  | 38,366  |

| N3        | 100,527   | 102,178 | 197,470 |

of the sensor placement result, three alternative noise sensor placement techniques are implemented. The first method simply selects the top-s nodes with maximum average noise for sensor placement (denoted as Ave-noise), while the second and third methods map noise to temperature and employ the state-of-the-art temperature sensor allocation techniques Eigenmap [31] and [32], respectively. Note that the former targets at recovering the whole noise map, while the later targets at capturing the hot spots at all times.

Table 1.2 compares the miss rate of the three methods. The miss rate is directly calculated as p/q, where q is the total number of time steps in the transient noise waveforms and p is the number of time steps in which a voltage emergency is missed (i.e., the placed sensors fail to detect the voltage emergency). The 90 mV threshold is set as 5% of the nominal Vdd (1.8V) according to the reported hard threshold value in literature [11]. The results in Table 1.2 indicate that compared with Ave-noise, the method in [32] and EigenMap [31], Eagle-Eye on average reduces the miss rate of voltage emergency detections by 7.4x, 6.2x and 15x, respectively. The drastic improvement should mainly be credited to the difference in optimization objectives between these methods. The runtime comparison in Table 1.3 also shows that Eagle-Eye is on average 96x faster than EigenMap and 3.2x faster than [32]. Such runtime reduction comes from the fact that the statistical max operations used in Eagle-Eye is much faster than the complex matrix operations needed in EigenMap and [32]. Figure 1.5 shows how the SQM changes with the number of placed sensors

| Benchmark | Miss Rate   |             |            |           |

|-----------|-------------|-------------|------------|-----------|

| Dentimark | Ave-noise   | Reda, S     | EigenMap   | Eagle-Eye |

| N1        | 17%(8.5x)   | 19%(9.5x)   | 75%(38x)   | 2%(1x)    |

| N2        | 38%(19x)    | 30%(15x)    | 47%(24x)   | 2%(1x)    |

| N3        | 18%(3.0x)   | 13%(2.2x)   | 29%(4.8x)  | 6%(1x)    |

| Average   | 24.3%(7.4x) | 20.6%(6.2x) | 50.3%(15x) | 3.3%(1x)  |

Table 1.2: Miss rate comparisons (#sensor = 10, t = 90mV)

under different threshold voltages. In addition to the hard threshold (5%Vdd, 90mV), two soft thresholds 87 mV and 85 mV are also used. Based on the observation in (1.5), it is natural to see that, under all thresholds, SQM increases with the number

| Benchmark | Runtime(sec) |             |              |           |  |

|-----------|--------------|-------------|--------------|-----------|--|

| Dencimark | Ave-noise    | Reda, S     | EigenMap     | Eagle-Eye |  |

| N1        | 0.01 (1/14x) | 0.25 (1.8x) | 1.68 (12x)   | 0.14(1x)  |  |

| N2        | 0.01 (1/20x) | 0.67 (3.4x) | 27.12(136x)  | 0.20(1x)  |  |

| N3        | 0.03 (1/10x) | 1.03 (3.4x) | 31.65 (106x) | 0.30(1x)  |  |

| Average   | 0.02 (1/11x) | 0.65 (3.2x) | 20.15 (96x)  | 0.21 (1x) |  |

Table 1.3: Runtime comparisons (#sensor = 10, t = 90mV)

of sensors. In all test cases, with fewer than 10 sensors, SQM reaches 90% of its maximum. This suggests that only a small number of sensors are indeed necessary, which means the framework will induce very little hardware overhead. The miss rate also drops with the number of sensors as expected. Interestingly, it is observed a rapid drop of miss rate at certain knee points of the number of noise sensors. This suggests the existence of a few nodes in the given power grid design, the union of which can be used as a good statistical indicator for the full-chip voltage emergencies. The number of nodes needed to form such a representative noise indicator increases as the threshold decreases. It is also found from this experiment that there is no overlap between those groups of nodes being selected at different thresholds.

Figure 1.6 compares the miss rate of different approaches with different number of noise sensors at 90 mV threshold on N2. Apparently, with the increase of the sensor number, the miss rate of Eagle-Eye quickly drops below 2%, while those of the Ave-noise and [32] are much slower. This is because [32] focuses on capturing the maximum noise locations at all times. When the number of sensors is limited, it may not select the nodes that have less noise but are better indicators of full-chip voltage emergencies. Even worse, the miss rate of EigenMap fluctuates extensively. This is because EigenMap emphasizes more on recovering the entire noise map. As such, it fails to capture the representative nodes as they are relatively uncorrelated to the other power grid nodes in the design.

It is further studied how SQM and miss rate change as the threshold voltage increases, and the result is shown in Figure 1.7 for N2 with 10 sensors. It is interesting

Figure 1.5: SQM and miss rate vs. the number of sensors of N2

that although SQM decreases in general with the increase of threshold voltage, which is intuitive from (1.5), the miss rate fluctuates with the overall trend of decreasing. The sudden drop of miss rate can be noted, again due to the existence of a few nodes whose union form a good statistical indicator for full-chip voltage emergencies for 85 mV threshold voltage and above.

Finally, for the same benchmark N2, sensor number 10 and threshold voltage 90 mV, Figure 1.8 studies the impact of sensing inaccuracy (i.e.,  $\Delta R_i$  in (1.1) induced by factors such as measurement error and process variations of the sensors) on the final sensor placement result. Here  $\Delta R_i$  is represented as a zero-mean Gaussian random variable. Obviously, when the sensing inaccuracy is small ( $\leq 20\%$ ), the miss rate and SQM remain flat, which shows the Eagle-Eye has strong resistance against small sensing inaccuracy. However, as the sensing inaccuracy increases, the chip noises become largely randomized. As such, it is harder to select a good statistical indicator for full-chip voltage emergencies, which translates into a rapid increase in the miss rate. The increase in SQM comes from the increased noise variations. Although not

Figure 1.6: Miss rate vs. the number of sensors for different approaches (threshold = 90 mV, N2)

Figure 1.7: SQM and miss rate vs. threshold (number of sensors = 10, N2)