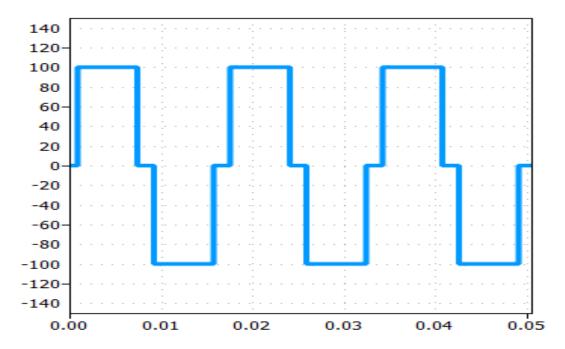

# Scholars' Mine

**Masters Theses**

Student Theses and Dissertations

Summer 2015

# Comparative study of three types of inverters based on the output total harmonic distortion

Paterrson Thomas

Follow this and additional works at: https://scholarsmine.mst.edu/masters\_theses

Part of the Electrical and Computer Engineering Commons

# Department:

#### **Recommended Citation**

Thomas, Paterrson, "Comparative study of three types of inverters based on the output total harmonic distortion" (2015). Masters Theses. 7438.

https://scholarsmine.mst.edu/masters\_theses/7438

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# COMPARATIVE STUDY OF THREE TYPES OF INVERTERS BASED ON THE OUTPUT TOTAL HARMONIC DISTORTION

by

# **PATERRSON THOMAS**

### A THESIS

Presented to the Faculty of the Graduate School of the

MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

# MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

2015

Approved by

Dr. Mehdi Ferdowsi

Dr. Pourya Shamsi

Dr. Jhi-Young Joo

© 2015

Paterrson Thomas

All Rights Reserved

#### **ABSTRACT**

In this thesis, three cases of power electronic inverters are taken into consideration to analyze their performance in terms of total harmonic distortion in their output voltage and output current. Firstly, a single H-bridge inverter is simulated. Staircase switching technique is used to generate the gating pulses for the switches. Only one switch is made to toggle for every half cycle. The fundamental harmonic component of the desired output voltage is considered to be 120 V. Secondly, the same topology is used with a Bipolar PWM gating technique. The switching frequency of the carrier wave is 33\*60 Hz. Thirdly, a multilevel H-bridge inverter is designed by connecting two H-bridge cells in series - one H-bridge cell with a DC source (main H-bridge inverter) and other with a capacitor (auxiliary inverter). The capacitor voltage regulation method is also proposed to control the voltage of the capacitor. Finally, FFT analysis is performed to understand the total harmonic distortion of output current and output voltage of all the three cases. A comparison study is made between all the three inverters' total harmonic distortion of their output current by keeping the load inductor value as constant and vice versa. Cost, size, no. of components used and design level factors are also taken into consideration to compare the inverters.

#### **ACKNOWLEDGEMENTS**

I would like to take this opportunity to show my sincere gratitude to my advisor Dr. Mehdi Ferdowsi for giving me this wonderful opportunity to work on this research topic. His continuous feedback and suggestions helped me a lot to complete this thesis. I would also like to extend my thanks to Dr. Pourya Shamsi and Dr. Jhi-Young Joo for serving on my thesis committee and spending their valuable time in reviewing my work.

I am much obliged to my mom, dad and brother who encouraged me in all possible ways in my life. I am also grateful to my other family members and friends. Last but not the least, I would like to owe my thanks to Almighty who showered me with his blessing to achieve success.

# TABLE OF CONTENTS

|                                  | Page |

|----------------------------------|------|

| ABSTRACT                         | iii  |

| ACKNOWLEDGEMENTS                 | iv   |

| LIST OF ILLUSTRATIONS            | vii  |

| LIST OF TABLES                   | ix   |

| SECTION                          |      |

| 1. INTRODUCTION                  | 1    |

| 1.1 THREE CASES OF INVERTERS     | 2    |

| 1.2.1 Case (i)                   | 2    |

| 1.2.2 Case (ii)                  | 2    |

| 1.2.3 Case (iii)                 | 2    |

| 2. SINGLE H-BRIDGE INVERTER      | 4    |

| 2.1 INVERTER TOPOLOGY            | 4    |

| 2.2 GATING TECHNIQUES            | 5    |

| 2.3 SIMULATION                   | 6    |

| 2.4 ANALYSIS OF OUTPUT WAVEFORMS | 9    |

| 3. BIPOLAR PWM INVERTER          | 11   |

| 3.1 INVERTER TOPOLOLOGY          | 11   |

| 3.2 GATING TECHNIQUE             | 11   |

| 3.3 SIMULATION                   | 13   |

| 3.4 ANALYSIS OF OUTPUT WAVEFORMS | 14   |

| 4.  | HYBRID MULTILEVEL H-BRIDGE INVERTER                 | 16 |

|-----|-----------------------------------------------------|----|

|     | 4.1 INVERTER TOPOLOGY                               | 16 |

|     | 4.2 GATING TECHNIQUE OF MAIN H-BRIDGE INVERTER      | 18 |

|     | 4.3 GATING TECHNIQUE OF AUXILIARY H-BRIDGE INVERTER | 19 |

|     | 4.3.1 Carrier Waveform                              | 20 |

|     | 4.3.2 Reference Waveform                            | 20 |

|     | 4.4 CAPACITOR VOLTAGE REGULATION                    | 22 |

|     | 4.5 SIMULATION                                      | 26 |

|     | 4.6 ANALYSIS OF OUTPUT WAVEFORMS                    | 30 |

| 5.  | COMPARISON BETWEEN THREE INVERTERS                  | 32 |

| 6.  | CONCLUSION                                          | 35 |

| BIB | BLIOGRAPHY                                          | 36 |

| VIT | ΓΑ                                                  | 40 |

# LIST OF ILLUSTRATIONS

|                                                                             | Page |

|-----------------------------------------------------------------------------|------|

| Figure 2.1 Topology of single H-bridge inverter                             | 4    |

| Figure 2.2 Desired output waveform of single H-bridge inverter              | 5    |

| Figure 2.3 Simulink model for gating pulse generator for switches           | 7    |

| Figure 2.4 Output voltage waveform of single H-bridge inverter              | 8    |

| Figure 2.5 Output current waveform of single H-bridge inverter              | 9    |

| Figure 2.6 FFT Analysis of output voltage of single H-bridge inverter       | 10   |

| Figure 2.7 FFT Analysis of output current of single H-bridge inverter       | 10   |

| Figure 3.1 Comparison between waves for BPWM                                | 11   |

| Figure 3.2 Generation of gating pulses for switches                         | 12   |

| Figure 3.3 Output voltage waveform of BPWM inverter                         | 13   |

| Figure 3.4 Output current waveform of BPWM inverter                         | 14   |

| Figure 3.5 FFT Analysis of output voltage of BPWM inverter                  | 15   |

| Figure 3.6 FFT Analysis of output current of BPWM inverter                  | 15   |

| Figure 4.1 Topology of multilevel hybrid H-bridge inverter                  | 17   |

| Figure 4.2 Gating pulse logic for main H-bridge inverter [4]                | 19   |

| Figure 4.3 Gating pulse logic for auxiliary H-bridge inverter               | 20   |

| Figure 4.4 Subtracting output of main inverter from desired output waveform | 21   |

| Figure 4.5 Resultant first part of the reference waveform                   | 21   |

| Figure 4.6 Comparison of final reference waveform with carrier waveform     | 22   |

| Figure 4.7 Canacitor voltage regulation method [4]                          | 23   |

| Figure 4.8 PI controller                                                | 24 |

|-------------------------------------------------------------------------|----|

| Figure 4.9 Capacitor voltage waveform                                   | 27 |

| Figure 4.10 Output voltage waveform of auxiliary H-bridge inverter      | 28 |

| Figure 4.11 Output voltage waveform of cascaded H-bridge inverter       | 29 |

| Figure 4.12 Output current waveform of cascaded H-bridge inverter       | 29 |

| Figure 4.13 FFT Analysis of cascaded H-bridge inverter output voltage   | 30 |

| Figure 4.14 FFT Analysis of cascaded H-bridge inverter output voltage   | 31 |

| Figure 5.1 Comparison of three inverters based on load inductor value   | 32 |

| Figure 5.2 Comparison of three inverters based on THD of output current | 33 |

# LIST OF TABLES

|                                         | Page |

|-----------------------------------------|------|

| Table 5.1 Comparison of three inverters | 34   |

#### 1. INTRODUCTION

Recent developments in the field of power electronics have paved a way to use inverters in an efficient way. There are many different kinds of inverters, which are being used in various fields. Among them, the cascaded H-bridge structured inverter, diode clamped inverter and flying capacitor inverter are the most common types of multi-level inverters. In this thesis, H-bridge structured inverter is taken into consideration to analyze Total Harmonic Distortion (THD) in various circumstances.

Inverters are widely used in different fields like Uninterruptible Power Supplies (UPS), power grid, renewable energy resources, controlling speed of the electric motor, induction heating and many other fields related to power.

#### 1.1 EFFECTS OF THD

Calculation of the Total Harmonic Distortion is important in the field of power in order to maintain the desired operation. Undesired harmonics cause eddy current losses in transformers, which create a serious problem in the operating temperature of the transformer. They also affect the capacitors by heating the dielectric medium [30].

Due to increase in harmonics in the current, the conductor will be overheated owing to skin effect. They also cause failure of circuit breaker, fuses and generator. Meters used in the utility purpose will show improper measurements due to harmonics present in the supply [28]. Harmonics multiplies the losses in the core of the motor resulting in the temperature increase of the motor windings. Undesired harmonics do not cause immediate

problems in the equipment. However, they slowly overheat the equipment and reduce the overall life span of them.

#### 1.2 THREE CASES OF INVERTERS

In this thesis, three cases of inverters are simulated and analyzed to reduce the Total Harmonic Distortion in the output current. They are:

- (i) Single H-bridge Inverter

- (ii) Bipolar Pulse Width Modulation (BPWM) Inverter

- (iii) Hybrid Multilevel H-Bridge Inverter

- **1.2.1 Case (i)**. For the first case, single phase H-Bridge inverter with four switches was considered. Staircase switching pattern is used in this case [3]. The gating pulses for the switches of the inverter are generated based upon the desired output of the single H-bridge inverter. Only one switch is made to toggle for every half cycle. RL load is connected across the output of the inverter.

- **1.2.2** Case (ii). The topology of the inverter is going to be same as the previous case (with the single phase H-bridge inverter being used in this case also). There is a difference in generating the gating pulse for the inverter in this case. Bipolar Pulse Width Modulation technique is used to control the switches. The triangular waveform is compared with the sinusoidal waveform to create the gating pulses.

- **1.2.3** Case (iii). In this case, two single H-bridge inverters are connected in series to form a multilevel inverter. Generally, if two H-bridge inverters are used, there will be two independent isolated dc voltage sources [29]. This will increase the cost of the inverter.

This drawback can be resolved by replacing one of the independent dc sources by the capacitor [1,2,4,5]. By this way, the cost of the inverter can be reduced.

If the individual dc source is replaced by the capacitor, the voltage across the capacitor has to be controlled. There are many methods to control the voltage across the capacitor. One of the capacitor voltage regulation methods is discussed in this thesis in section 4.4.

### 2. SINGLE H-BRIDGE INVERTER

# 2.1 INVERTER TOPOLOGY

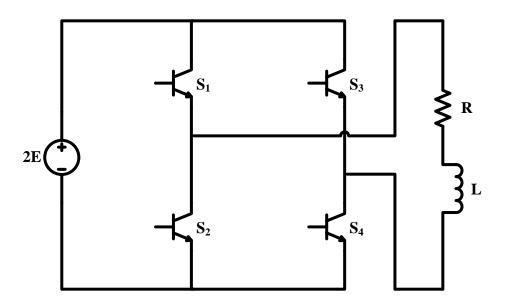

A single H-Bridge inverter consists of four switches with the DC source. A three level AC output is obtained from the single H-Bridge inverter. Figure 2.1 shows the topology of the single H-Bridge inverter. The value of the DC source of the single H-Bridge inverter is assumed to be 2E. The reason for this assumption will be discussed in the chapter 4. The RL load is connected to the output of this inverter.

Figure 2.1 Topology of Single H-Bridge Inverter

# 2.2 GATING TECHNIQUES

The gating signal of this inverter is designed based upon the desired output of this inverter. The firing angle of the inverter [18] is determined by

$$\alpha = \cos^{-1}(\pi V_{\rm m}/8E) \tag{1}$$

The respective switches are triggered based upon their contribution in generating the desired output. The involvement of the switches in developing the output can be understood from the Figure 2.2.

Figure 2.2 Desired output waveform of single H-Bridge inverter

The switch  $S_1$  should be ON in the interval of 0 to  $\pi$ - $\alpha$  and also from  $2\pi$ - $\alpha$  to  $2\pi$ . In the interval of 0 to  $\alpha$  and from  $\pi$ + $\alpha$  to  $2\pi$ - $\alpha$  switch  $S_3$  must be ON. Similarly switches  $S_2$  and  $S_4$  should be triggered at the intervals of  $\pi$ - $\alpha$  to  $2\pi$ - $\alpha$  and from  $\alpha$  to  $\pi$ + $\alpha$  respectively. These intervals are repeated in the same order after  $2\pi$ . From the Figure 2.2, it is clear that

switches  $S_1$  and  $S_4$  are responsible for the positive cycle of the inverter output voltage. Similarly, negative half cycle of the inverter output voltage is created by the switches  $S_2$  and  $S_3$ . It is made sure that switches  $S_1$  and  $S_2$  or the switches  $S_3$  and  $S_4$  are not triggered at the same interval in order to avoid short circuit in the inverter. The switching pattern explained above is as follows:

$$\begin{aligned} \mathbf{S_1} &= \{ -\alpha < \omega t < \pi\text{-}\alpha \text{ and } \\ 2\pi\text{-}\alpha < \omega t < 2\pi \text{ } \} \end{aligned}$$

$$\mathbf{S_2} &= \pi\text{-}\alpha < \omega t < 2\pi\text{-}\alpha$$

$$\mathbf{S_3} &= \{ -\alpha < \omega t < \alpha \text{ and } \\ \pi\text{+}\alpha < \omega t < 2\pi \text{ } \}$$

$S_4 = \alpha < \omega t < \pi + \alpha$

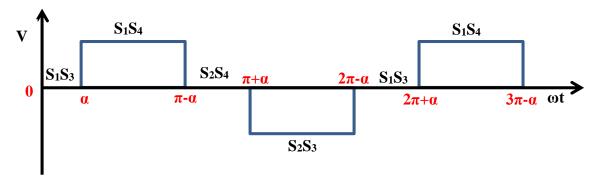

#### 2.3 SIMULATION

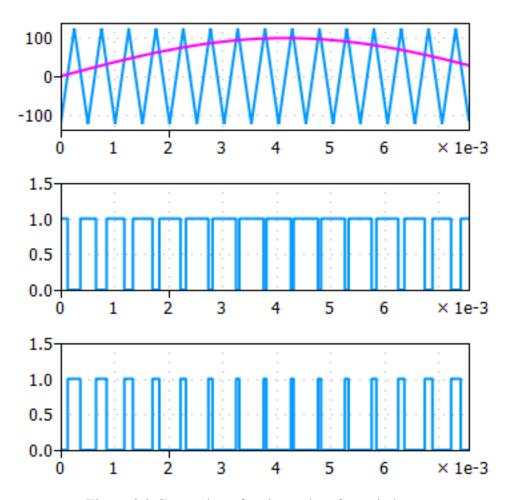

The DC source voltage (i.e. 2E) is chosen to be 100 V. The fundamental harmonic component of the desired AC output voltage is 120. According to these values, using equation (1), the firing angle is calculated. Then the gating pulses for all the switches are generated based upon the technique which is discussed in section 2.2. Figure 2.3 shows the generation of gating pulses for the switches  $S_1$ ,  $S_2$ ,  $S_3$  and  $S_4$ .

Figure 2.3 Simulink model for gating pulse generator for switches

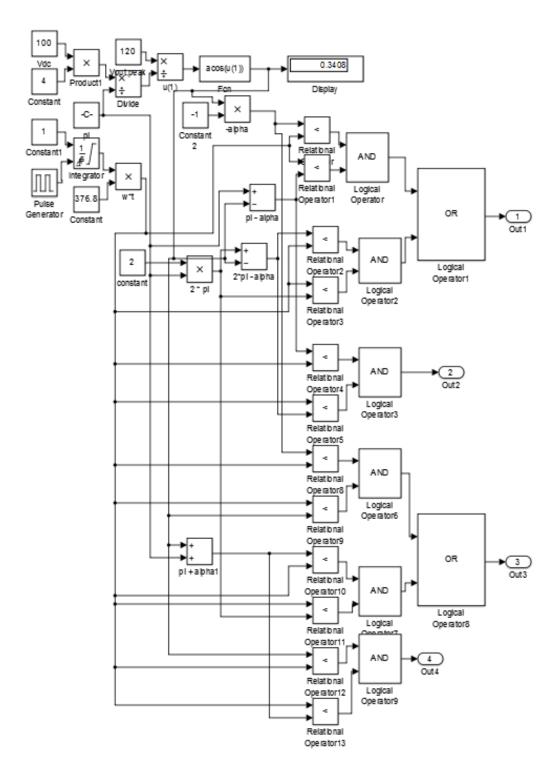

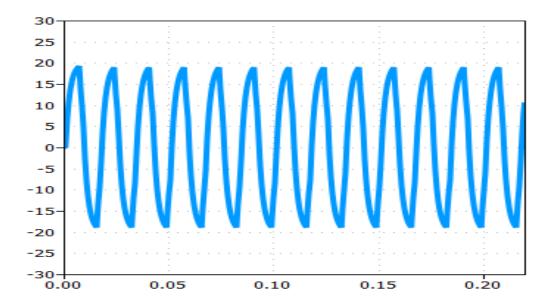

The values of the load for the inverter is chosen as  $R=5\Omega$  and L=0.01H. The waveforms of the output voltage and output current of the inverter are obtained as shown in Figure 2.4 and Figure 2.5 respectively.

Figure 2.4 Output voltage waveform of single H-bridge inverter

The fundamental harmonic component of the output voltage of the inverter is found to be 120 V as expected.

Figure 2.5 Output current waveform of single H-bridge inverter

The fundamental harmonic component of the output current of the inverter is found to be 19.16 A.

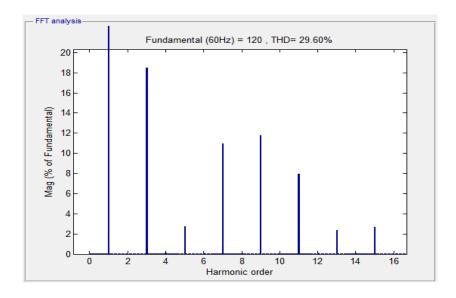

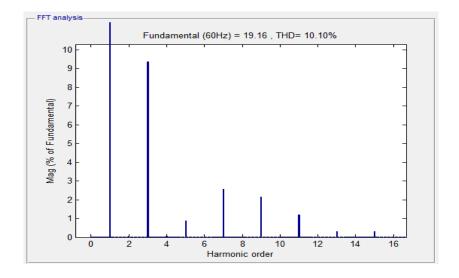

# 2.4 ANALYSIS OF OUTPUT WAVEFORMS

Fast Fourier Transform (FFT) analysis is done in the waveforms of output voltage and current of the inverter in order to know about the Total Harmonic Distortion of the respective waveforms. The results show that THD of the output voltage of the inverter is 29.6% and for the output current of the inverter the THD is 10.10%. These results are shown in the Figure 2.6 and Figure 2.7.

Figure 2.6 FFT Analysis of output voltage of single H-bridge inverter

Figure 2.7 FFT Analysis of output current of single H-bridge inverter

#### 3. BIPOLAR PWM INVERTER

### 3.1 INVERTER TOPOLOGY

The topology of the Bipolar PWM inverter remains same as the single H-bridge inverter discussed in the section 2.1.

# 3.2 GATING TECHNIQUE

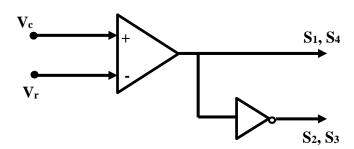

Bipolar Pulse Width Modulation (BPWM) technique is used to generate the gating pulses for the switches in the inverter. This technique is shown is Figure 3.1 [26, 27]. The triangular wave is chosen as the carrier wave. The sinusoidal wave with the same frequency as the desired output waveform is chosen as the reference wave. The sine wave is compared with the triangular wave to generate the gating pulses.

Figure 3.1 Comparison between waves for BPWM

When the value of the triangular wave is greater than the value of the sinusoidal wave, the switches  $S_1$  and  $S_4$  will be ON. Similarly, when the value of the triangular wave is less than the value of the sinusoidal wave,  $S_2$  and  $S_3$  switches will become ON. With the help of these switches, the output voltage waveform is generated. The generation of gating pulses is shown in Figure 3.2.

Figure 3.2 Generation of gating pulses for switches

# 3.3 SIMULATION

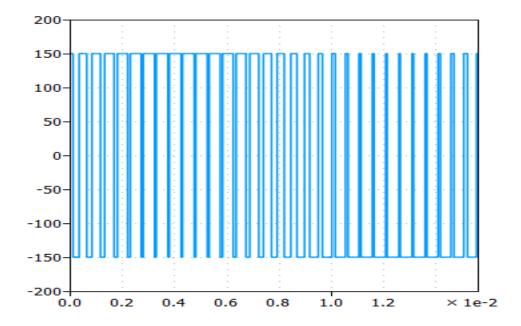

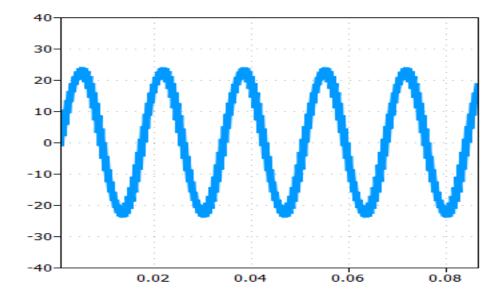

The input DC source value of the inverter is taken as 150 V. The desired fundamental harmonic component value of the output voltage is 120 V. Therefore, the chosen value of the modulation index is 0.8. The gating pulses are generated as per section 4.2. The values of the load for the inverter are chosen as  $R=5\Omega$  and L=0.01H. The waveforms of the output voltage and output current of the inverter are obtained as shown in Figure 3.3 and Figure 3.4 respectively. The fundamental harmonic component of the output voltage and current of the inverter is found to be 119.8 V and 22.45 A respectively.

Figure 3.3 Output voltage waveform of BPWM inverter

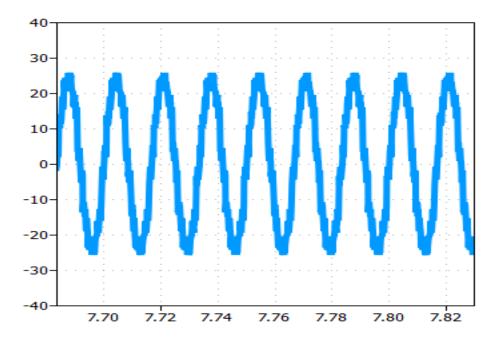

Figure 3.4 Output current waveform of BPWM inverter

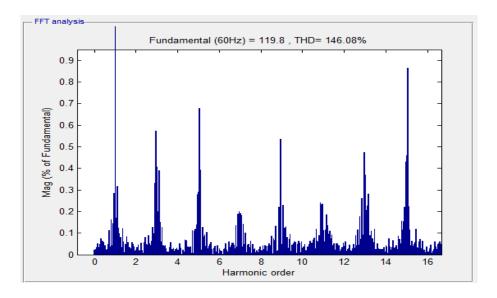

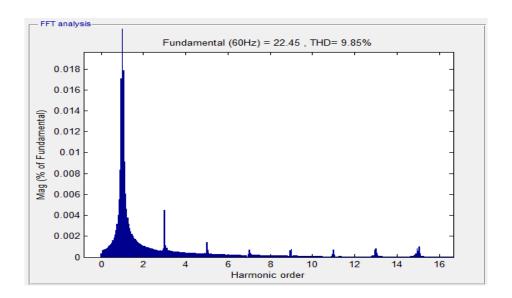

# 3.4 ANALYSIS OF OUTPUT WAVEFORMS

FFT analysis is done in the waveforms of output voltage and current of the inverter; in order to know about the Total Harmonic Distortion (THD) of the respective waveforms. The results show that the THD of the output voltage and output current of the inverter are 146.08% and 9.85% respectively. These results are shown in Figure 3.5 and Figure 3.6.

Figure 3.5 FFT Analysis of output voltage of BPWM inverter

Figure 3.6 FFT Analysis of output current of BPWM inverter

#### 4. HYBRID MULTILEVEL H-BRIDGE INVERTER

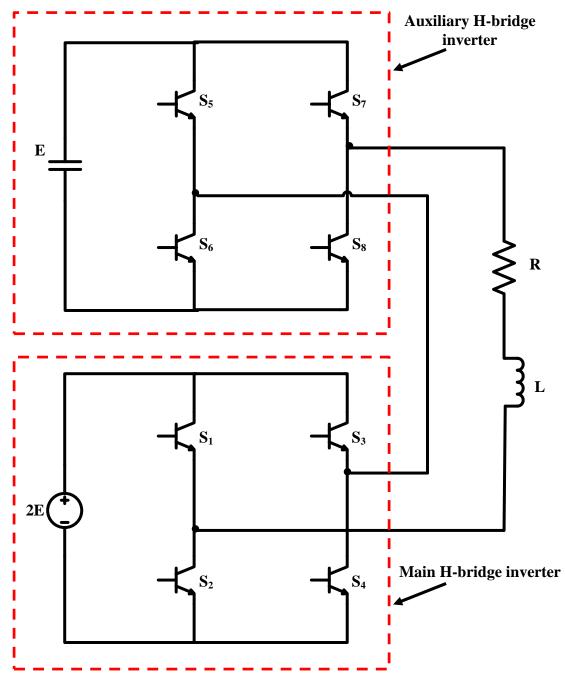

#### **4.1 INVERTER TOPOLOGY**

This multilevel single phase inverter has two H-Bridge inverters, which are cascaded in series [8,15,17]. One of the inverters would be referred to as the 'main H-Bridge inverter' and the other one as the 'auxiliary H-Bridge inverter' for easy reference [1]. The topology of the main inverter remains the same as the single H-bridge inverter, which was discussed in chapter 2. The topology of the auxiliary H-bridge inverter is similar to the main inverter; except the DC source. The auxiliary H-bridge inverter is supplied by a capacitor instead of a separate DC source.

Therefore, the overall cascaded H-bridge inverter has eight semi-conductor switches, single DC source and a capacitor. The gating techniques for both main and auxiliary inverters will be different. These techniques will be discussed in detail in section 4.2. The RL load is connected to the cascaded hybrid H-bridge multilevel inverter. The entire topology of the hybrid multilevel H-bridge inverter is shown in Figure 4.1.

Figure 4.1 Topology of multilevel hybrid H-bridge inverter

As it is discussed in the previous section, the DC voltage source of the main H-bridge inverter is denoted as 2E. The voltage across the capacitor of the auxiliary H-bridge inverter is shown as E, which will be exactly half the value of the main H-bridge inverter DC source. If the DC source is replaced by the capacitor, it is necessary to control the voltage across the capacitor to the desired value [7,22-25]. The capacitor voltage regulation method for controlling the voltage of this inverter is discussed in detail in section 4.4.

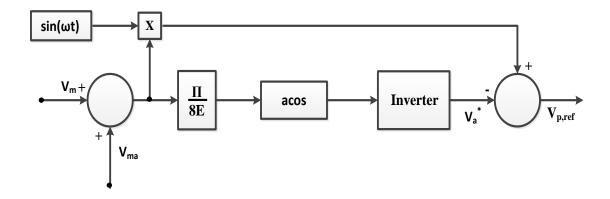

#### 4.2 GATING TECHNIQUE OF MAIN H-BRIDGE INVERTER

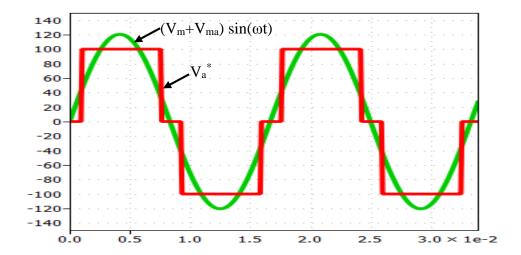

The gating pulse logic for the main inverter is going to remain the same as the logic followed for the case (i): single H-bridge inverter. But an extra compensation term is involved in calculating the firing angle. The extra compensation term is represented as  $V_{ma}$ . This  $V_{ma}$  term is added to the desired amplitude of the fundamental harmonic of the inverter output voltage  $V_m$ . Due to the operation of the capacitor, there will be a fluctuation in the amplitude of the output voltage waveform. To avoid this,  $V_{ma}$  term is added to  $V_m$  while calculating the firing angle. This compensation term will be discussed in detail at the end of section 4.4.

Therefore the equation of the firing angle becomes

$$\alpha = \cos^{-1}[\pi(V_m + V_{ma})/8E] \tag{2}$$

The gating pulse logic of the main H-bridge inverter is shown in Figure 4.2.

Figure 4.2. Gating pulse logic for main H-bridge inverter [4]

where,

$V_m$  = Amplitude of the desired sinusoidal output waveform

$V_{ma}$  = Extra compensation term

V<sub>a</sub>\* = Output of the main inverter

$V_{p,ref}$  = First part of the reference waveform

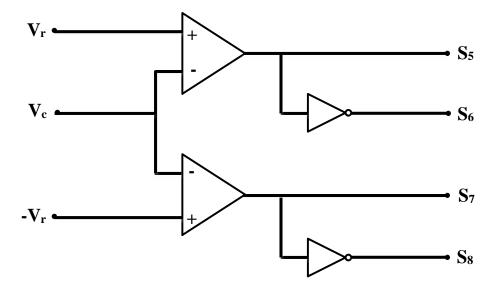

# 4.3 GATING TECHNIQUE OF AUXILIARY H-BRIDGE INVERTER

Pulse Width Modulation (PWM) technique is used to generate gating pulses for the auxiliary H-bridge inverter[21]. The reference wave is compared with the carrier wave in order to produce the gating pulses for the switches. This technique is decribed in the Figure 4.3 [26].

Figure 4.3 Gating pulse logic for auxiliary H-bridge inverter

**4.3.1 Carrier Waveform.** In this Pulse Width Modulation technique, triangular wave is used as the carrier waveform to be compared with the reference waveform.

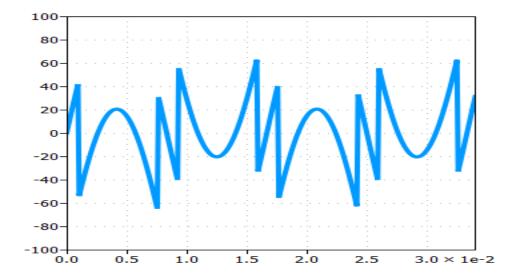

**4.3.2 Reference Waveform.** The generation of reference waveform is splitted into two parts. The first part of the waveform is denoted as  $V_{p,ref}$ . The output waveform of the main H-bridge inverter ( $V_a^*$ ) is subtracted from the desired sinusoidal output waveform to generate the first part of the reference waveform [6]. This is shown in Figure 4.4 and Figure 4.5. In Figure 4.5, an inequality in the peak magnitude of the waveform is clearly visible. This is mainly due to the operation of capacitor. The equation of the first part of the reference waveform is derived as:

$$V_{p,ref} = [(V_m + V_{ma}) \sin(\omega t)] - V_a^*$$

(3)

Figure 4.4 Subracting output of main inverter from desired output waveform

Figure 4.5 Resultant first part of the refernce waveform

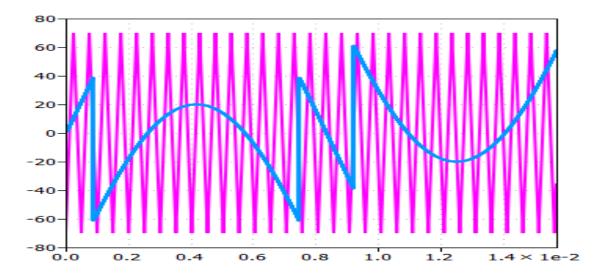

The second part of the reference waveform  $(V_r)$  is generated by subtracting the output of the PI controller from the first part of the reference waveform  $(V_{p,ref})$ . This will be discussed in detail in later part of the section 4.4. The final reference waveform is

compared with the triangular waveform to synthesize the gating pulses for switches  $S_5$ ,  $S_6$ ,  $S_7$  and  $S_8$ . These are depicted in the Figure 4.6.

Figure 4.6 Comparing final reference waveform with carier waveform

Whenever the value of reference waveform is greater than the carier waveform, switch  $S_5$  will be triggered and vice versa for the switch  $S_6$ . Similarly, if the negative value of the reference waveform is greater than the triangular waveform, the gating pulse will be ON for the switch  $S_7$  and vice versa for  $S_8$  switch.

## 4.4 CAPACITOR VOLTAGE REGULATION

The voltage across the capacitor has to be maintained at the desired value for the proper functioning of the cascaded H-bridge inverter. There are many methods available

already to control the voltage of the capacitor [9-16,19,20]. One of those methods is discussed in this section.

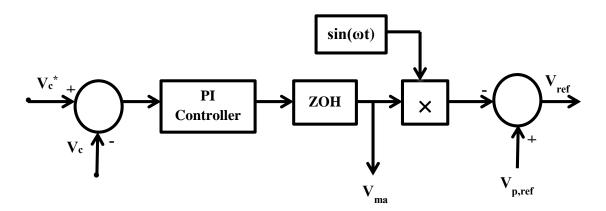

The main H-bridge inverter involves in generating fundamental harmonic component of the output voltage of the entire cascaded H-bridge inverter. The auxiliary H-bridge inverter does not involve in producing fundamental harmonic component. This is the main principle used in voltage regulation method [4]. During the fundamental line frequency period, auxiliary H-bridge inverter should not supply the average active power. The capacitor voltage regulation method is depicted in Figure 4.7.

The desired value across the capacitor is denoted as E. The voltage value of the capacitor of the auxiliary H-bridge inverter has to be maintained at half the value of the DC source of the main H-bridge inverter [1,4]. This is the reason for naming the DC voltage source as 2E as per the convenience.

In the reference waveform of the auxiliary H-bridge inverter, a small amount of the fundamental harmonic component is added or subtracted based upon the measured voltage across the capacitor.

Figure 4.7 Capacitor voltage regulation method [4]

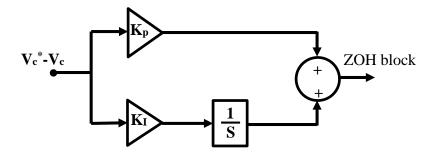

The measured voltage across the capacitor is subtracted from the desired voltage of the capacitor (i.e. E). The resultant value is given to the PI controller. The PI controller design is shown in the Figure 4.8.

Figure 4.8. PI Controller

Then zero-order hold (ZOH) block is used to sample the output of the PI controller at every period cycle. With the help of this, the fundamental harmonic component added to the reference waveform of the auxialiary H-bridge is kept constant during each line period. This is done to overcome the distortion due to the capacitor voltage regulation in the cascaded H-bridge inverter output voltage. The output of the ZOH block (i.e.  $V_{ma}$ ) is fedback and added to the desired amplitude of the output sinusoidal waveform (i.e.  $V_{m}$ ). The resultant value is used to calculate the firing angle of the main H-bridge inverter. Additionally, it is also used to compare it with the output of the main H-bridge inverter after multiplying it with the sinusoidal waveform of same frequency to create the first part of the reference waveform. This is shown in detail in the Figure 4.2. This feedback is done

to avoid any increase or decrease in the amplitude of the fundamental harmonic companent of the cascaded H-Bridge inverter. The output value of the ZOH block is mulitplied with the sinusoidal waveform and then it is subtracted from the first part of the reference waveform. The resultant will be the final reference waveform which will be used to companre with the carier wave in Pulse Width Modulation technique to generate the gating pulse for the auxiliary H-bridge inverter. The final reference voltage waveform is given in the equation 4.

$$V_{ref} = V_{p,ref} - [(V_c^* - V_c)^* (K_p + K_i/s)^* \sin(\omega t)]$$

(4)

where,

$V_c^*$  = Desired voltage across the capacitor

V<sub>c</sub> = Measured voltage across the capacitor

$V_{ma}$  = Extra compensation term

$V_{p,ref}$  = First part of reference waveform

$V_{ref}$  = Final reference waveform

$K_p$  = Proportional gain of PI controller

K<sub>I</sub> = Integral gain of PI controller

This entire method depends upon the power supplied by the auxiliary H-bridge inverter. Whenever the value of the measured voltage across the capacitor is greater than

the desired voltage value of the capacitor, a small sinusoidal waveform which has the same fundamental frequency is added to the first part of the reference waveform. This indicates the involvement of auxiliary H-bridge inverter in generating the fundamental harmonic component of the output waveform of the cascaded H-bridge inverter and also produce active power. As the auxiliary H-bridge inverter involves in generating power, the charge of the capacitor decreases automatically. Therefore, the measured voltage across the capacitor will come down to the desired voltage value E.

Similarly, if the voltage measured across the capacitor is less than the desired value, a small sinusoidal waveform, which has the same fundamental frequency, is subtracted from the first part of the reference waveform. This makes the auxiliary H-bridge inverter to absorb the power. So, the capacitor gets charged and the measured voltage across the capacitor increases and reaches the desired value. By this way, the voltage across the capacitor is maintained at the desired value.

Under the normal operating condition, auxiliary H-bridge inverter does not involve in generating or absorbing power. But a small amount of active power is supplied or absorbed in order to regulate the capacitor voltage.

#### 4.5 SIMULATION

The DC source voltage (i.e. 2E) of the main inverter H-bridge inverter is chosen to be 100 V. The fundamental harmonic component of the desired AC output voltage is 120 V. According to these values, using equation (2), the firing angle is calculated. Then the gating pulses for all the switches in the main H-bridge inverter are generated based upon the technique which is discussed in 2.2.

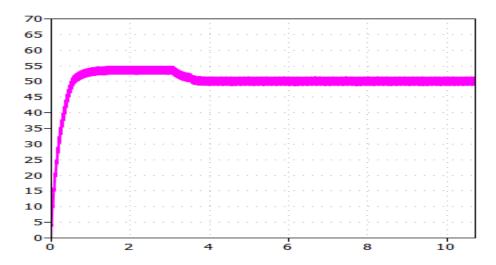

Then PWM technique is used to synthesize gating pulses for the auxiliary H-bridge inverter switches as discussed in the section 4.3. The voltage across the capacitor is maintained at 50 V, which is half of the value of DC source of the main H-bridge inverter, with the help of capacitor voltage regulation method discussed in section 4.4. The voltage waveform across the capacitor is depicted in the Figure 4.9.

Figure 4.9. Capacitor voltage waveform

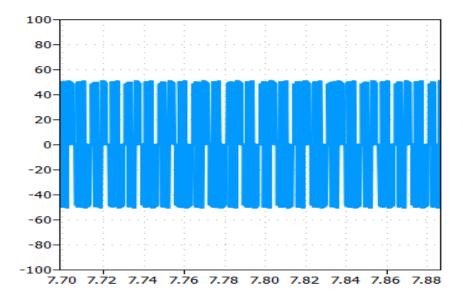

The value of the load for the cascaded H-bridge inverter is chosen as  $R=5\Omega$  and L=0.01H. The waveforms of the output voltage of the auxiliary H-bridge inverter and the waveforms of output voltage and output current of the cascaded inverter are obtained as shown in Figure 4.9, Figure 4.10 and Figure 4.11 respectively.

Figure 4.10 Output voltage waveform of auxiliary H-bridge inverter

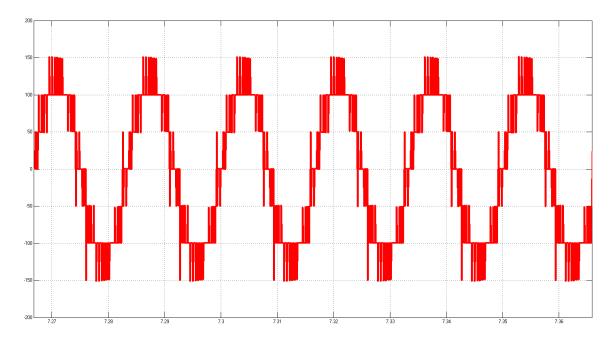

In the Figure 4.11, there are some spikes in the output voltage waveform of the cascaded H-bridge inverter. It is due to the increase in output voltage of the main inverter and the decrease in output voltage of the auxiliary inverter at the same instant.

Figure 4.11 Output voltage waveform of cascaded H-bridge inverter

Figure 4.12 Output current waveform of cascaded H-bridge inverter

The fundamental harmonic component of the output voltage and output current of the inverter is found to be 121.3 V and 24.19 A respectively.

## 4.6. ANALYSIS OF OUTPUT WAVEFORMS

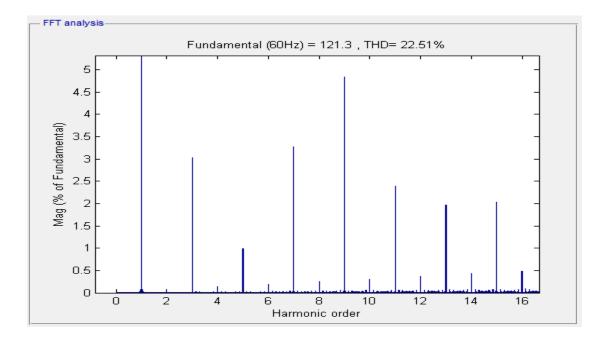

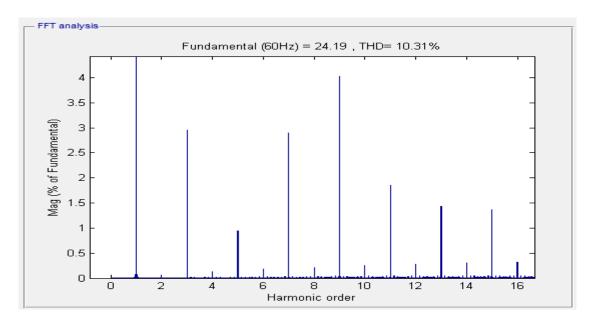

FFT analysis is done in the waveforms of output voltage and current of the cascaded H-bridge inverter to determine about the Total Harmonic Distortion (THD) of the respective waveforms. The results show that THD of the output voltage of the inverter is 22.51% and for the output current of the inverter the THD is 10.31%. These results are shown in the Figure 4.13 and Figure 4.14 respectively.

Figure 4.13 FFT Analysis of cascaded H-bridge inverter output voltage

Figure 4.14 FFT Analysis of cascaded H-bridge inverter output current

## 5. COMPARISON BETWEEN THREE INVERTERS

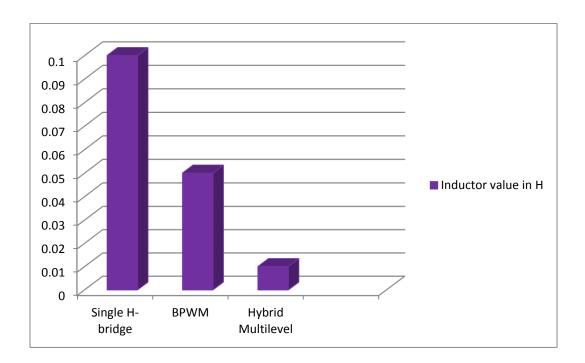

Here, these three inverters are compared based on the obtained THD values. Firstly, the inductor load which is connected to these inverters is varied in order to get around 10% of THD in the output current. Based upon the chosen inductor values, these three inverters are compared as shown in Figure 5.1.

Figure 5.1 Comparison of three inverters based on load inductor value

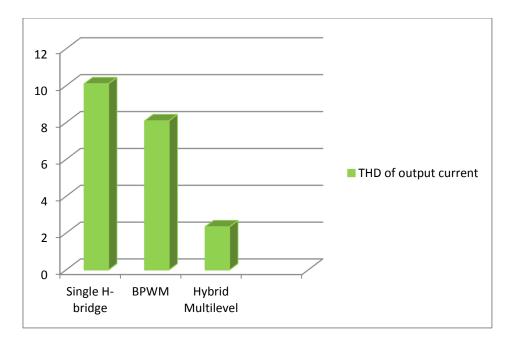

Then, the load value of all the inverters is kept constant to compare the THD of the output current of the three inverters. The chosen value of the load is  $R=5\Omega$  and L=10mH. This comparison is depicted in the Figure 5.2.

Figure 5.2 Comparison of three inverters based on THD of output current

There are many other considerations, which will be taken in account while choosing an inverter. Based on those constraints, these three inverters are compared and tabulated as in Table 5.1

Table 5.1 Comparison of three inverters

|                   |       |      | No. of components |           |

|-------------------|-------|------|-------------------|-----------|

| Inverter type     | Size  | Cost | used              | Design    |

| Single H-bridge   | Large | High | Less              | Easy      |

| BPWM              | Large | High | Less              | Easy      |

| Hybrid Multilevel | Small | Low  | High              | Difficult |

Hybrid multilevel inverter shows better performance in THD but the size and cost of the inverter are high; when compared to the other inverters. Therefore, choosing the particular inverter is completely dependent on the user requirements. If the user requires an inverter with less THD and has low cost and size then hybrid multilevel inverter should be an ideal choice. If the no. of components used and the design level are the major constraint of the user, then either a single H-bridge or BPWM inverter can serve better.

### 6. CONCLUSION

In this thesis, three types of inverters are simulated and analyzed based upon their performance. A single H-bridge inverter is simulated using PLECS software and gating pulses for the switches are generated based on the desired output waveform of the inverter. Then, with the same inverter topology, Bipolar Pulse Width Modulation (BPWM) technique is used to control the operation of the switches in the inverter. A hybrid multilevel cascaded H-bridge inverter is also designed by connecting two H-bridge inverters in series. One of them has a DC source and the other one has a capacitor as its source. PWM technique is used to create the gating pulses for the auxiliary inverter. The capacitor voltage regulation method is proposed to control the voltage across the capacitor at the desired value. The FFT Analysis is performed to calculate the Total Harmonic Distortion (THD) of the inverters' output voltage and current. While analyzing the performance of all the three inverters, hybrid multilevel cascaded H-bridge inverter shows better performance in terms of THD, cost and size of the inverter. In terms of no. of components used and design level, hybrid multilevel inverter is not better than the other two inverters. Therefore, based upon the requirements of the user, the respective inverter is selected.

#### **BIBLIOGRAPHY**

- 1. H. Sepahvand, M. Khazraei, M. Ferdowsi and K.A. Corzine, "Feasibility of capacitor voltage regulation and output voltage harmonic minimization in cascaded H-bridge converters," in *Proc. IEEE Appl. Power Ectron. Conf. and Expo.*, 2010, pp. 452-457.

- 2. M. H. Ameri and S. Farhangi, "A new simple method for capacitors voltage balancing in cascaded H-bridge SSSC," in *Proc. Power Electron. And Drive Syst. And Technologies Conf.*, 2010, pp. 147-151.

- 3. J. Rodriguez, J. S. Lai and F. Z. Peng, "Multilevel inverter; a survey of topologies, controls, and applications," *IEEE Trans. Ind. Electron.*, vol. 49, no. 4, pp. 724-738, Aug. 2002.

- 4. H. Sepahvand, M. Ferdowsi and K.A. Corzine, "Fault recovery strategy for hybrid cascaded H-bridge multi-level inverters," *Proc. IEEE Appl. Power Electron. Conf. Expo.*, 2011, pp. 1629-1633.

- 5. H. Sepahvand, J. Liao, M. Ferdowsi and K.A. Corzine, "Capacitor voltage regulation in single DC source cascaded H-bridge multilevel converters using phase-shift modulation," *IEEE Trans. Ind. Electron.*, vol. 60, no. 9, pp. 3619-3626, Sep. 2013.

- 6. H. Sepahvand, M. Khazraei, M. Ferdowsi and K.A. Corzine, "A hybrid multilevel inverter with both staircase and PWM switching schemes," in *Proc. IEEE Energy Conversion Congr. And Expo.*, 2010, pp. 4364-4367.

- 7. J. A. Ulrich and A. R. Bendre, "Floating capacitor voltage regulation in diode clamped hybrid multilevel converters," in *Proc. IEEE electric Ship Technologies Symp.*, 2009, pp. 197-202.

- 8. K. A. Corzine and Y. Familiant, "A new cascaded multilevel H-bridge drive," *IEEE Trans. Power Electron.*, vol. 17, no. 1, pp. 125-131, Jan. 2002.

- 9. K. A. Corzine, M. W. wielebski, F. Z. Peng and J. Wang, "Control of cascaded multilevel inverters," *IEEE Trans. Power Electron.*, vol.19, no. 3, pp. 732-738, May 2004.

- 10. Z. du, L. M. Tolbert, B. Ozpineci and J. N. Chiasson, "Fundamental frequency switching strategies of a seven-level hybrid cascaded H-bridge multilevel inverter," *IEEE Trans. Power Electron.*, vol. 24, no. 1, pp. 25-33, Jan. 2009.

- 11. J. Pereda and J. Dixon, "High-frequency link: a solution for using only one dc source in asymmetric cascaded multilevel inverters," *IEEE Trans. Ind. Electron.*, vol. 58, no. 9, pp. 3884-3892, Sep. 2011.

- 12. K. Iwaya and I. Takahashi, "Novel multilevel PWM wave control method using series connected full bridge inverters," in *Proc. IEEE Int. Electric Machines and Drives Conf.*, vol. 3, pp. 1543-1548, 2003.

- 13. C. A. silve, L. A. Cordova, P. Lezana and L. Empringham, "Implementation and control of a hybrid multilevel converter with floating dc links for current waveform improvement," *IEEE Trans. Ind. Electron.*, vol. 58, no. 6, pp. 2304-2312, Jun. 2011.

- 14. P. Roshankumar, P. P. Rajeevan, K. Mathew, K. Gopakumar, J. I. Leon and L. G. Franquelo, "A five-level inverter topology with single dc supply by cascading a flying capacitor inverter and an H-bridge," *IEEE Trans. Power Electron.*, vol. 27, no. 8, pp. 3505-3512, Aug. 2012.

- 15. C. Rech, H. Pinheiro, H. A. Griindling, H. L. Hey and J. R. Pinheiro, "Analysis and comparison of hybrid multilevel voltage source inverters," *IEEE Power Electron. Spec. Conf.*, vol. 2, pp. 491-492, 2002.

- 16. F. Khoucha, A. Ales, A. Khoudiri, K. Marouani, M.E.H. Benbouzid and A. Kheloui, "A 7-level single DC source cascaded H-bridge multilevel inverters control using hybrid modulation," *Electrical Machines XIX Intl. Conf.*, pp. 1-5, Sept. 2010.

- 17. S. J. Lee, H. S. Bae, B. H. Cho, "Modeling and control of the single phase photovoltaic grid connected cascaded H-bridge multilevel inverter," in *Proc. IEEE Energy Convers. Congr. Exp. Conf.*, pp. 43-47, Sep. 2009.

- 18. D. W. Hart, "Introduction to power electronics," 1st edition, 1996.

- 19. H. Sepahvand, "Addressing control and capacitor voltage regulation challenges in multilevel power electronic converters," PhD, Missouri University of Science and Technology, Rolla, MO, Fall 2012.

- 20. J. S. Choi and F. S. Kang, "Modification of cascaded H-bridge multilevel inverter to increase output voltage level with a single DC voltage source," *IEEE Energy Conver. Congr. And Exp.*, pp. 5757-5760, Sept. 2014.

- 21. M. Singh, A. Agarwal and N. Kaira, "Performance evaluation of multilevel inverter with advance PWM control techniques," *IICPE*, pp. 1-6, Dec. 2012.

- 22. B. M. Roodsari, A. A. Judi and E. Nowicki, "Modified nearest three virtual space-vector modulation method for improved dc capacitor voltage control in N-level diode clamped inverters," *CCECE, IEEE Canadian Conf.*, pp. 1-4, May 2012.

- 23. C. Yuanhua, L. Wenhua, Y. Gangui and S. Qiang, "Research of capacitor voltage balance control method for H-bridge inverter of hybrid 9-level inverter," *Proc. IEEE Appl. Power Electron. Conf. Expo.*, vol. 3, pp. 1714-1719, 2004.

- 24. Y. Chen, W. Liu, Q. Song and Q. Yu, "PWM and capacitor voltage balance control strategies for hybrid 9-level inverter," *IEEE Power Electron. Spec. Conf.*, vol. 5, pp. 3465-3470, Jun. 2004.

- 25. E. Barcenas, S. Ramirez, V. Cardenas and R. Echavarria, "Cascaded multilevel inverter with only one DC source," *Proc. Power Electron Congr. CIEP*, pp. 171-176, Oct. 2002.

- 26. P. H. Zope, P. G. Bhangale, P. Sonare and S. R. Suralkar, "Design and implementation of carrier based sinusoidal PWM inverter," *IJAREEIE*, vol. 1, no. 4, Oct. 2012.

- 27. A. Namboodiri and H. S. Wani, "Unipolar and Bipolar PWM Inverter," *IJIRST* vol. 1, no. 7, Dec. 2014.

- 28. APT Associated Power Technologies, "Total Harmonic Distortion and effects in electrical power systems."

- 29. J. Kumar, "THD analysis for different levels of cascaded multilevel inverters for industrial applications," *IJETAE*, vol. 2, no. 10, Oct. 2012.

- 30. Power Quality Centre, "Harmonic distortion in the electric supply system," Technical note no. 3, University of Wollongong, March 2000.

# **VITA**

Paterrson Thomas was born in Puducherry, India. He received his Bachelor of Engineering degree in Electrical and Electronics Engineering from Anna University, Chennai in 2013. He was a graduate student in Electrical Engineering department at Missouri University of Science and Technology since 2013 and worked as a Graduate Research Assistant under Dr. Mehdi Ferdowsi and as a Graduate Teaching Assistant under Dr. Jonathan W. Kimball from August 2014 to May 2015. He received his Master's in Electrical Engineering at Missouri University of Science and Technology in August 2015.