# Scholars' Mine

## Masters Theses

Student Theses and Dissertations

Spring 2008

# Via transition modeling and charge replenishment of the power delivery network in multilayer PCBs

Matteo Cocchini

Follow this and additional works at: https://scholarsmine.mst.edu/masters\_theses

Part of the Electrical and Computer Engineering Commons Department:

## **Recommended Citation**

Cocchini, Matteo, "Via transition modeling and charge replenishment of the power delivery network in multilayer PCBs" (2008). *Masters Theses*. 4616. https://scholarsmine.mst.edu/masters\_theses/4616

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# VIA TRANSITION MODELING AND CHARGE REPLENISHMENT OF THE POWER DELIVERY NETWORK IN MULTILAYER PCBs

by

## MATTEO COCCHINI

## A THESIS

Presented to the Faculty of the Graduate School of the

## MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

2008

Approved by

James L. Drewniak, Advisor David Pommerenke Daryl Beetner

© 2008

Matteo Cocchini All Rights Reserved

## **PUBLICATION THESIS OPTION**

This thesis consists of the following five articles that have been published or submitted for publication as follows:

Pages 1-16 have been published in the IEEE International Symposium on EMC, pp. 1–6, Honolulu, Hawaii, July 2007

Pages 17-29 have been accepted for publication to the 2008 IEEE EMC Detroit Symposium

Pages 30-40 have been submitted for presentation to EMC Europe 2008, Hamburg, Germany

Pages 41-71 have been published in the Proceedings of Design Conference East, Santa Clara, CA, Feb 2007

Pages 72-85 are intended for submission to the 2008 IEEE EMC Detroit Symposium

## ABSTRACT

In the first article of this thesis, the charge delivery in the power distribution network for printed circuit board has been analyzed in the time-domain. Performing all the simulations and analyzing the PDN physics and modeling, I contributed to a better understanding of the time-domain decoupling mechanism.

The second paper studies the noise coupling sing a segmentation approach combined with a via-to-antipad capacitance model and a plane-pair cavity model. Building equivalent circuit models as well as analyzing design strategies, I contributed to a new approach for the PDN analysis in multilayer PCBs.

The third article discusses how to estimate the amount of current needed for large ICs and how to evaluate the amount of noise voltage due to this current draw. After accurate discussion of the design strategies, I modeled and simulated the free evolution of a charged PCB with and without decoupling capacitors.

The depletion of charges stored between the power buses in time and frequency-domain has been investigated as a function of the plane thickness, SMT decoupling closeness in the fourth paper. With my contribution, the time and frequency-domain in the PDN have been related using circuit approach.

In the fifth paper, I analyzed a 26-layer printed circuit board performing milling, measurements and building circuit models. It is the first time that the segmentation approach has been used for differential geometry. In addition, Debye materials have been implemented in the cavity model.

## ACKNOWLEDGMENTS

I would like to express my sincere gratitude to Dr. James Drewniak, my research advisor, for his instruction and direction during the pursuit of my Master Degree. I would like to appreciate Dr. David Pommerenke and Dr. D. Beetner for their advisement and direction for my research and engineering work. I would like to thank Dr. Jun Fan, Dr. T. P. Van Doren, Dr. R. Dubroff and Dr. Marina Koledintseva for their beneficial discussions and suggestions related to my research. I am grateful to Dr. Bruce Archambeault, Dr. James Knighten and Dr. Wheling Chang for their help with my research during our cooperation. I would like to thank all my colleagues in the MST/UMR EMC Laboratory for their help and cooperation during my study and research, in particular a former student, Dr. Giuseppe Selli who guided and helped me when I joined the EMC Lab.

Most of all, I am very grateful to my fiancée Mariaelena, who resisted two years without me, my parents and my sisters for their love and supports during my study and pursuit of my Master.

## **TABLE OF CONTENTS**

|                                                                                                                               | Page |

|-------------------------------------------------------------------------------------------------------------------------------|------|

| PUBLICATION THESIS OPTION                                                                                                     | iii  |

| ABSTRACT                                                                                                                      | iv   |

| ACKNOWLEDGMENTS                                                                                                               | v    |

| LIST OF ILLUSTRATIONS                                                                                                         | ix   |

| LIST OF TABLES                                                                                                                | xiii |

| 1. EARLY TIME CHARGE REPLENISHMENT OF THE POWER DELIVER<br>NETWORK IN MULTI-LAYER PCBS                                        |      |

| 1.1. ABSTRACT                                                                                                                 | 1    |

| 1.2. INTRODUCTION                                                                                                             | 1    |

| 1.3. MODELING ISSUES AND IMPLEMENTATION                                                                                       | 2    |

| 1.4. TIME DOMAIN BEHAVIOR – EARLY TIME                                                                                        | 5    |

| 1.5. CONCLUSIONS                                                                                                              | 14   |

| 1.6. REFERENCES                                                                                                               | 14   |

| 2. NOISE COUPLING BETWEEN SIGNAL AND POWER/GROUND NETS<br>DUE TO SIGNAL VIAS TRANSITIONING THROUGH POWER/GROUND<br>PLANE PAIR | 17   |

| 2.1. ABSTRACT                                                                                                                 |      |

| 2.2. INTRODUCTION                                                                                                             | 17   |

| 2.3. MODELING APPROACH                                                                                                        |      |

| 2.4. NOISE COUPLING FROM SIGNAL TO POWER/GROUND                                                                               |      |

| 2.5. NOISE COUPLING FROM POWER/GROUND TO SIGNAL                                                                               |      |

| 2.6. CONCLUSIONS                                                                                                              |      |

| 2.7. REFERENCES                                                                                                               |      |

| 3. DESIGN METHODOLOGY FOR PDN SYNTHESIS ON MULTI-LAYER PCBS                                                                   | 30   |

| 3.1. ABSTRACT                                                                                                                 |      |

| 3.2. INTRODUCTION                                                                                                             |      |

| 3.3. HOW MUCH CURRENT IS REQUIRED BY THE IC?                                                                                  |      |

| 3.4. PURPOSE OF LOCAL DECOUPLING CAPACITORS                                                                                   |      |

vi

| 3.5. INITIAL PULSE VOLTAGE DROOP                                                                                                                              | 35 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.6. TIME FOR CHARGE RESTORATION TO THE PLANES                                                                                                                | 35 |

| 3.7. SIMULATION CONFIGURATION                                                                                                                                 | 36 |

| 3.8. EFFECTS WITHIN A CYCLE                                                                                                                                   | 36 |

| 3.9. EFFECTS OVER MANY CYCLES                                                                                                                                 | 37 |

| 3.10. SUMMARY                                                                                                                                                 | 39 |

| 3.11. REFERENCES                                                                                                                                              | 39 |

| 4. COMPARING TIME-DOMAIN AND FREQUENCY DOMAIN<br>TECHNIQUES FOR INVESTIGATION ON CHARGE DELIVERY AND<br>POWER-BUS NOISE FOR HIGH-SPEED PRINTED CIRCUIT BOARDS | 41 |

| 4.1. ABSTRACT                                                                                                                                                 | 41 |

| 4.2. INTRODUCTION                                                                                                                                             | 41 |

| 4.3. THE POWER DELIVERYNETWORK                                                                                                                                | 43 |

| 4.3.1. THE DECOUPLING CAPACITORS                                                                                                                              | 44 |

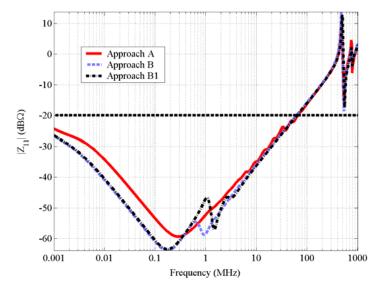

| 4.3.2. DETERMINING INDIVIDUAL DECOUPLING CAPACITORS<br>VALUES – DIFFERING APPROACH                                                                            | 47 |

| 4.3.3. THE IMPORTANCE OF CAPACITORS LOCATION                                                                                                                  | 49 |

| 4.3.4. LOCAL DECOUPLING AS SEEN IN THE FREQUENCY<br>DOMAIN                                                                                                    | 52 |

| 4.3.5. LOCAL DECOUPLING AS SEEN IN THE TIME DOMAIN                                                                                                            | 54 |

| 4.4. CHARGE DEPLETION AS SEEN IN THE TIME DOMAIN                                                                                                              | 60 |

| 4.5. CONCLUSION                                                                                                                                               | 68 |

| 4.6. REFERENCES                                                                                                                                               | 68 |

| 5. DIFFERENTIAL VIAS TRANSITION MODELING IN A MULTILAYER<br>PRINTED CIRCUIT BOARD                                                                             | 72 |

| 5.1. ABSTRACT                                                                                                                                                 | 72 |

| 5.2. INTRODUCTION                                                                                                                                             | 72 |

| 5.3. PCB TEST GEOMETRY AND MEASUREMENT SETUP                                                                                                                  | 73 |

| 5.4. MODELING APPROACH                                                                                                                                        | 75 |

| 5.5. MEASUREMENTS AND SIMULATIONS COMPARISON                                                                                                                  | 77 |

| 5.6. EFFECTS OF TOLERANCES ON MODELING                                                                                                                        | 82 |

| 5.7. CONCLUSIONS                                                                                                                                              | 83 |

| 5.8. REFERENCES                                                                                                                                               | 84 |

| VITA | . 86 |

|------|------|

|------|------|

# viii

## LIST OF ILLUSTRATIONS

| Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.1. Equivalent circuit model corresponding to (1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 1.2. Geometry under test and triangular current waveform source connected at Port 25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Figure 1.3. Configuration with 35 mils plane separation and decoupling capacitor 400 mils away from the driver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| Figure 1.4. Configuration with 10 mils plane separation and decoupling capacitor 400 mils away from the driver7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Figure 1.5. Plane separation 35 mils and 1nH decoupling capacitor interconnect inductance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 1.6. Plane separation 10 mils and 1nH decoupling capacitor interconnect inductance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Figure 1.7. Early instants of time comparison between a ring of eight 0.1 $\mu$ F decoupling capacitor 400 mils away from the driver <i>vs.</i> a single 0.8 $\mu$ F decoupling capacitor at 400 mils away from the driver (L <sub>3</sub> = 0.5 nH and ESR 30 mΩ) and a ring of eight 1 $\mu$ F decoupling capacitor 400 mils away from the driver <i>vs.</i> single 8 $\mu$ F decoupling capacitor at 400 mils away from the driver <i>vs.</i> single 8 $\mu$ F decoupling capacitor at 400 mils away from the driver <i>vs.</i> 11                                                                    |

| Figure 1.8. Early instants of time comparison between a ring of eight 0.1 $\mu$ F decoupling capacitor 400 mils away from the driver <i>vs.</i> a single 0.8 $\mu$ F decoupling capacitor at 400 mils away from the driver (L <sub>3</sub> = 0.5 nH and ESR 30 m $\Omega$ ) and a ring of eight 1 $\mu$ F decoupling capacitor 400 mils away from the driver <i>vs.</i> a single 8 $\mu$ F decoupling capacitor at 400 mils away from the driver for 10 mils plane separation (L <sub>3</sub> = 0.5 nH and ESR 30m $\Omega$ )                                                                            |

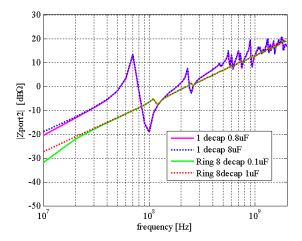

| Figure 1.9. Frequency domain comparison between a ring of eight 0.1 $\mu$ F decoupling capacitor 400 mils away from the driver <i>vs.</i> a single 0.8 $\mu$ F decoupling capacitor at 400 mils away from the driver (L <sub>3</sub> = 0.5 nH and ESR 30 mΩ) and a ring of eight 1 $\mu$ F decoupling capacitor 400 mils away from the driver <i>vs.</i> single 8 $\mu$ F decoupling capacitor at 400 mils away from the driver for a 35 mils plane separation (L <sub>3</sub> = 0.5 nH and ESR 30mΩ)13                                                                                                  |

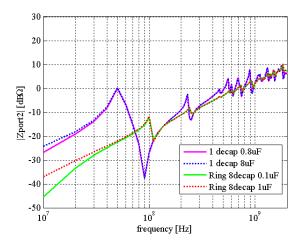

| Figure 1.10. Frequency domain comparison between a ring of eight 0.1 $\mu$ F decoupling capacitor 400 mils away from the driver <i>vs.</i> a single 0.8 $\mu$ F decoupling capacitor at 400 mils away from the driver (L <sub>3</sub> = 0.5 nH and ESR 30 m $\Omega$ ) and a ring of eight 1 $\mu$ F decoupling capacitor 400 mils away from the driver <i>vs.</i> a single 8 $\mu$ F decoupling capacitor at 400 mils away from the driver <i>vs.</i> a single 8 $\mu$ F decoupling capacitor at 400 mils away from the driver 10 mils plane separation (L <sub>3</sub> = 0.5 nH and ESR 30m $\Omega$ ) |

| Figure 2.1. A typical building block19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Figure 2.2. Test geometry to study noise coupling from signal to power/ground nets.                                                                        | 21      |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| Figure 2.3. Equivalent circuit model for the test geometry shown in Figure 2.2                                                                             | 22      |

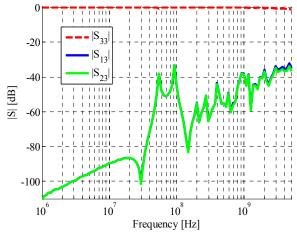

| Figure 2.4. Frequency-domain transfer functions including the noise transfer functions from signal to power/ground.                                        | 22      |

| Figure 2.5. Time-domain transfer functions including the noise transfer functions from signal to power/ground.                                             | 23      |

| Figure 2.6. Noise voltages generated in the power/ground plane pair due to the signal transition.                                                          | 23      |

| Figure 2.8. Test geometry to study noise coupling from power/ground to signal nets.                                                                        | 24      |

| Figure 2.9. Equivalent circuit model for the test geometry shown in Figure 2                                                                               | 25      |

| Figure 2.9. Frequency-domain transfer functions including the noise transfer functions from power/ground to signal.                                        | 26      |

| Figure 2.10. Noise voltages generated in the signal trace caused by power bus noise due to the signal transition.                                          | e<br>26 |

| Figure 2.11. Signal via is further away from the power/ground vias, compared to the test geometry shown in Figure 2.7                                      | 27      |

| Figure 2.12. Frequency-domain transfer functions including the noise transfer functions from power/ground to signal, for the geometry shown in Figure 2.11 | 28      |

| Figure 2.13. Noise voltages generated in the signal trace caused by power bus noise due to the signal transition, for the geometry shown in Figure 2.11.   |         |

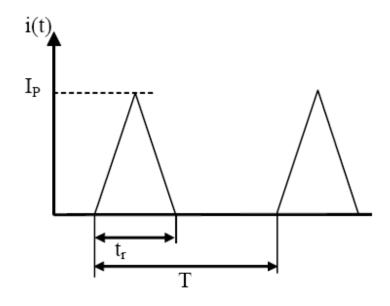

| Figure 3.1. Simple triangle current waveform                                                                                                               | .33     |

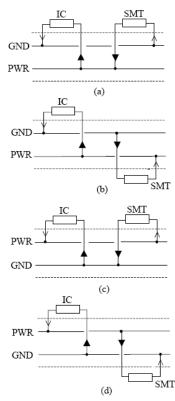

| Figure 3.2a. Low connection inductance configurations                                                                                                      | 34      |

| Figure 3.2b. High connection inductance configuration                                                                                                      | 34      |

| Figure 3.3. Equivalent circuit                                                                                                                             | 36      |

| Figure 3.4. Within cycle noise voltage from IC current draw                                                                                                | 37      |

| Figure 3.5. Noise voltage across many cycles                                                                                                               | 38      |

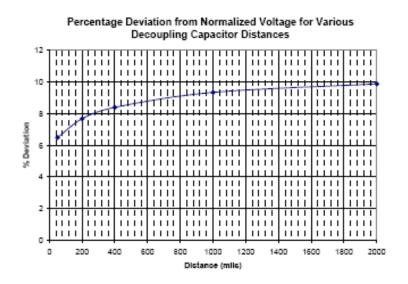

| Figure 3.6. Deviation Vs. decoupling capacitor distance                                                                                                    | 39      |

| Figure 4.1. Typical Impedance Profile for PDN.                                                                                                             | .45     |

| Figure 4.2. Connection Inductance Associated with Capacitor Mounting on PCB                                                                                | .46     |

| Figure 4.3. PDN Impedance from Comparison of Decoupling Approaches.                                                                                        | 49      |

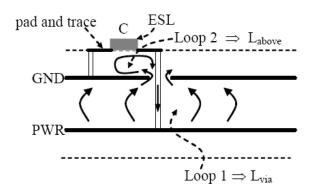

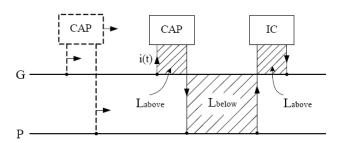

| Figure 4.4. Inductance "Above" and "Below" for connection to PDN                                                                                           | 50      |

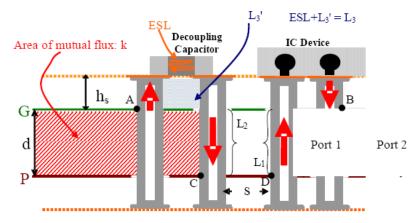

| Figure 4.5. Local Decoupling Inductance and Mutual Inductance.                                                                                             | 52      |

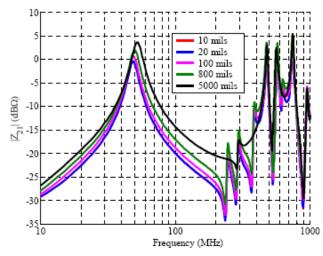

| Figure 4.7. Transfer Impedance for Dielectric Thickness = 10 mils                                                                                          | .53     |

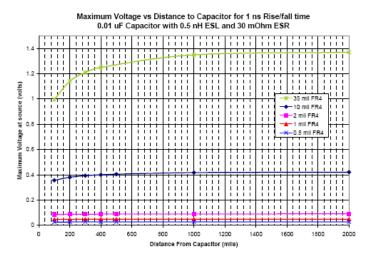

| Figure 4.9. Time Domain Noise Pulse for Different Decoupling Capacitor Distances.                                                                                           | 56 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.10. Comparison of Maximum Time Domain Voltage for Different<br>Decoupling Capacitor Distances and Dielectric Thicknesses.                                          | 57 |

| Figure 4.11. Capacitor Mounting on Top/Bottom of PCB                                                                                                                        | 58 |

| Figure 4.12. Proper Capacitor Mounting Configurations.                                                                                                                      | 59 |

| Figure 4.13. Incorrect Capacitor Mounting Configurations                                                                                                                    | 60 |

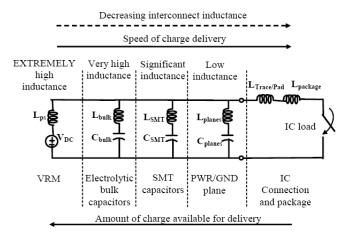

| Figure 4.14. Charging hierarchy of a power delivery network                                                                                                                 | 61 |

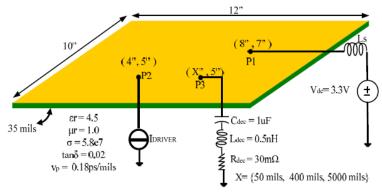

| Figure 4.15. Board model under investigation.                                                                                                                               | 61 |

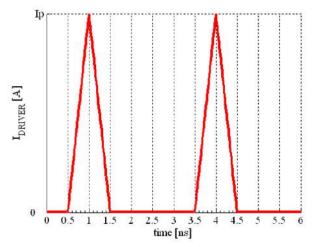

| Figure 4.16. Current waveform sunk at Port 2. The peak current is chosen accordingly to the required time domain simulation settings                                        | 62 |

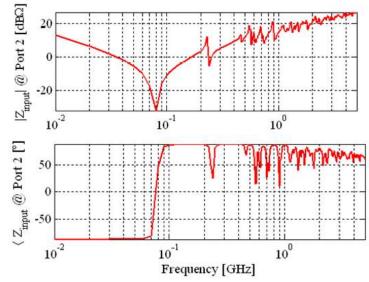

| Figure 4.17. Self-impedance, magnitude and phase, looking into Port 2 of Figure 4.15.                                                                                       | 63 |

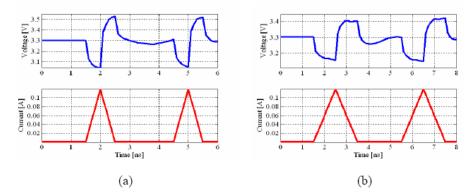

| Figure 4.18. Triangular current at Port 2 for (a) 1 ns base; (b) 2 ns base. The corresponding inductive voltage drop is observed at the terminals of Port 2                 | 64 |

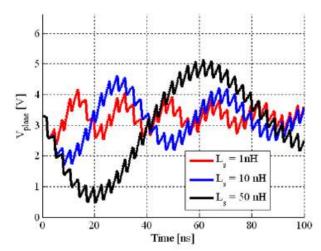

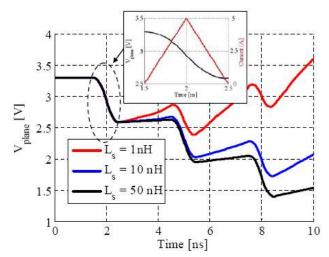

| Figure 4.19: Voltage observed across the plane pair of the board model given in Figure 4.15 for different voltage supply series inductance.                                 | 65 |

| Figure 4.20. Close up of the voltage given in Figure 4.19.                                                                                                                  | 65 |

| Figure 4.21. Voltage observed across the plane pair of the board model given in Figure 4.15 for different locations of the decoupling capacitor or no decoupling capacitor. |    |

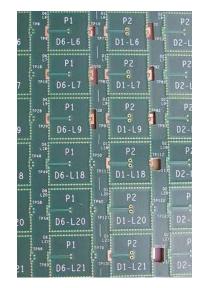

| Figure 5.1. Top view of P2-D1 series of test sites                                                                                                                          |    |

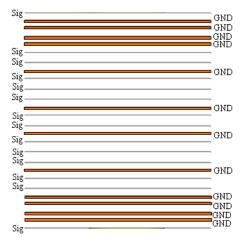

| Figure 5.2. Board Stack-up                                                                                                                                                  | 74 |

| Figure 5.3. P2-D1 test sites for different stub lengths                                                                                                                     | 75 |

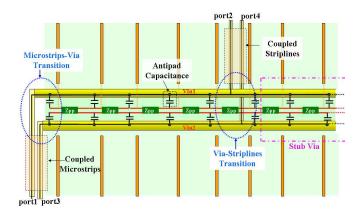

| Figure 5.4. Detail of test site P2-D1-L21and cross-section on launching structure                                                                                           | 75 |

| Figure 5.5. Geometry and equivalent circuit model                                                                                                                           | 76 |

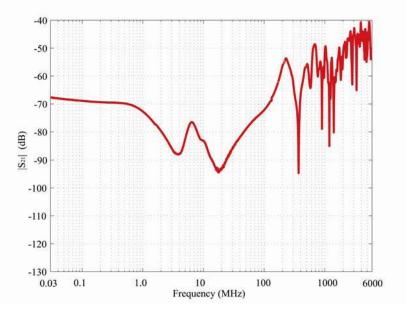

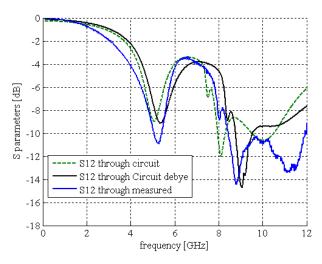

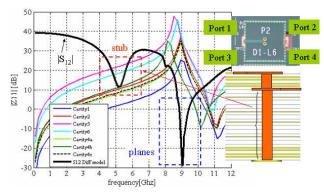

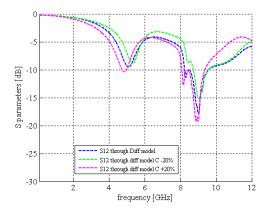

| Figure 5.6.  S <sub>12</sub>   including Debye materials                                                                                                                    | 77 |

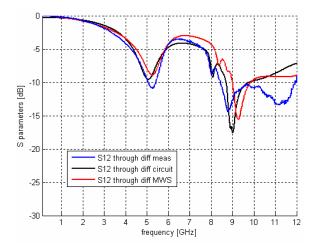

| Figure 5.7.  S <sub>12</sub>   Measurements vs. simulations                                                                                                                 | 78 |

| Figure 5.8. $ S_{12} $ overlapped with all the plane impedances $ Z_{11} $                                                                                                  | 78 |

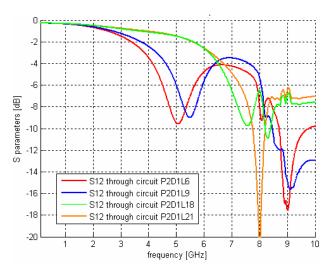

| Figure 5.9. $ S_{12} $ simulations varying stub length                                                                                                                      | 79 |

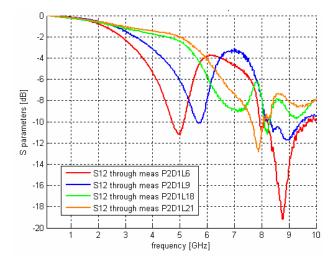

| Figure 5.10.  S <sub>12</sub>   measurements varying stub length                                                                                                            | 80 |

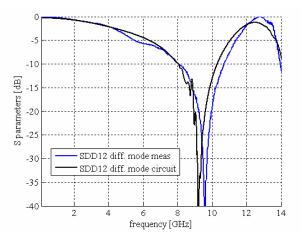

| Figure 5.11.  S <sub>DD12</sub>   measurements vs. equivalent circuit model                                                                                                 | 80 |

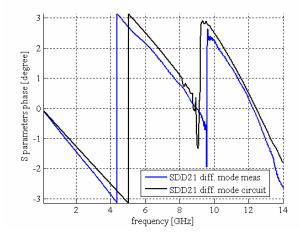

| Figure 5.12. Phase of SDD <sub>12</sub> measurements vs. equivalent circuit                                                                                                 | 81 |

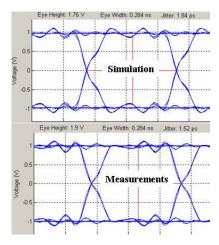

| Figure 5.13. Eye diagram for a 3.5Gbit/s pattern based on simulated and measured S-parameters                                                                               | 81 |

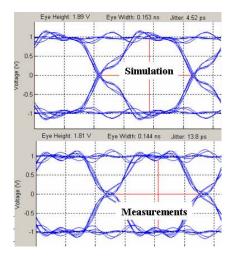

| Figure 5.14. Eye diagram for a 6.3Gbit/s pattern based on simulated and measured          |    |

|-------------------------------------------------------------------------------------------|----|

| S-parameters                                                                              | 82 |

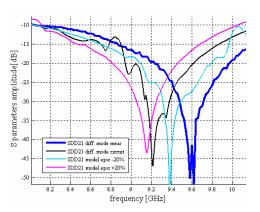

| Figure 5.15.  S <sub>DD12</sub>   measurement vs. model varying dielectric constant value | 83 |

| Figure 5.16.  S <sub>12</sub>   model varying via-to-antipad capacitance                  | 84 |

## LIST OF TABLES

## Page

| Table 1.1. k, $L_3/L_2$ and $ Z_{decrease(dB)} $ factor for the curves in Figure 1.3  | 9   |

|---------------------------------------------------------------------------------------|-----|

| Table 1.2. k, $L_3/L_2$ and $ Z_{decrease(dB)} $ factor for the curves in Figure 1.4. | .10 |

| Table 1.3. k, $L_3/L_2$ and $ Z_{decrease(dB)} $ factor for the curves in Figure 1.5. | .10 |

| Table 1.4. k, $L_3/L_2$ and $ Z_{decrease(dB)} $ factor for the curves in Figure 1.6. | .10 |

| Table 3.1 Calculated Connection Inductance for various dimensions                     | .34 |

| Table 4.1 Inductance from Capacitor Mounting on Top/Bottom of PCB                     | .58 |

| Table 4.2. Resonant frequencies associated to oscillations observed in Figure 4.19    | .64 |

## 1. EARLY TIME CHARGE REPLENISHMENT OF THE POWER DELIVERY NETWORK IN MULTI-LAYER PCBS

Giuseppe Selli, Matteo Cocchini, James Knighten, Bruce Archambeault, Jun Fan, Samuel Connor, Antonio Orlandi, James L. Drewniak Electrical Engineering University of Missouri – Rolla, Missouri, U.S.A 65401 Email: gs5xd@mst.edu, mcfk9@mst.edu, jim.knighten@ncr.com, barch@us.ibm.com, jfan@mst.edu, sconnor@us.ibm.com, orlandi@ing.univaq.it, drewniak@mst.edu

#### **1.1. ABSTRACT**

The investigation of decoupling issues has been extensively treated in the literature in both the frequency and the time domain [1-9]. The two domains describe from different perspectives the same physical phenomenon, being related by a Fourier transform. In this article, well known decoupling issues usually addressed in the frequency domain [1,2] are discussed in the time domain. Moreover, some modeling issues related to the cavity model approach are discussed and, in particular, the circuit extraction feature associated with this methodology is utilized throughout the article to carry out the time domain simulations within a SPICE based-tool. The depletion of charges stored between the power bus is investigated in the time domain as a function of the plane thickness, SMT decoupling closeness and interconnect inductance values.

#### Keywords

Decoupling Issues, Power Delivery Network, Charge Depletion, Cavity Model

## **1.2. INTRODUCTION**

Understanding decoupling issues in both the frequency and the time domain is important for effective design of the power distribution network for printed circuit boards (PCB) for high-speed signaling. Many contributions can be found in the literature [1-9] dealing with PDN decoupling aspects to ensure the functionality of PCB systems. Different schools of thoughts exist regarding the utilization of decoupling capacitors, typically in terms of a target impedance of the power/ground plane pair (power bus). The ability to perform circuit extraction when describing the power bus in terms of cavity modes [10-17] is used in this paper to investigate these issues mainly in the time domain by means of SPICE-based tools. Firstly, a couple of modeling problems are discussed in order to explain some intricacies associated with the circuit models and the choice of the observation points. Then, well known decoupling, issues that are usually addressed in the frequency domain, are investigated in the time domain. Design tips and conclusions drawn are consistent regardless of whether frequency or time domains are examined [1,2].

## **1.3. MODELING ISSUES AND IMPLEMENTATION**

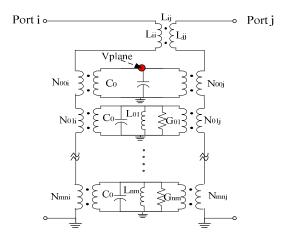

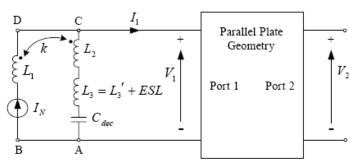

The circuit extraction feature of the cavity model approach [10-17] can be utilized to model the power delivery network. The circuit models extracted are run in a SPICEbased tool allowing for the possibility to investigate the same issues from a time domain prospective. The circuit interpretation of the cavity model approach is given below:

$$Z_{ij} = \frac{1}{j\omega C_p} + \sum_{n=0}^{N} \sum_{m=0}^{M} \frac{N_{nmi} N_{nmj}}{j\omega C_p} + \frac{1}{j\omega L_{nm}} + G_{nm} + j\omega L_{ij}^{HM}$$

(1)

is divided into three terms. The first term corresponds to the interplane capacitance of the plane pair. It represents the impedance of the board at low frequencies, i.e., when the impedance declines at -20 dB/dec. The third term is the higher order interconnect inductance. This term comprises all the contributions of the modes, whose resonant frequencies fall above the maximum frequency of interest. It is well- known that each resonant mode can described in terms of an equivalent R-L-C parallel circuit [11-14]. Hence, all the inductive contributions of those higher order modes are grouped together to create the inductive behavior. Also, this inductance resonates with the interplane capacitance creating the characteristic first dip seen in any self-impedance profile. If no additional terms were to be considered in the impedance formula, a characteristic

impedance rise of 20 dB/dec would be observed in the self-impedance profile at higher frequencies. The second term of the summation consists of a double summation of all the resonant modes considered for the board geometry. The maximum number of those modes for each propagating direction is chosen according to the formulas provided in [12-13]. All these modes superimpose their characteristic R-L-C behavior on top of the underlying  $j\omega L_{ij}$  behavior as the frequency is increased. Figure 1.1 illustrates the equivalent circuit realized by equation (1).

Figure 1.1. Equivalent circuit model corresponding to (1).

The original summation of equation (1) consists of a double infinite summation, which is replaced by two finite N by M summations and the inductive term. The inductive term is obtained as the number which the double infinite summations converges, once the N by M terms - still explicitly present in the formulation (1) - are subtracted from it.

Further considerations need to be added regarding the investigation of decoupling issues in the time domain and in particular the charge depletion of the planes. As a repetitive triangular current waveform is drawn from a given location on the board, the sagging of the voltage is observed at the node specified in Figure 1.1 as Vplane. By placing a current source at Port i and leaving Port j open, the voltage observed at the driver port, or Port i, corresponds to the summation of all the voltage drops observed across the higher order mode inductance  $L_{ii}$ , the capacitance of the plane  $C_0$  and all the R-L-C circuits associated with the resonant modes, coupled to the driver Port i by means of

the ideal transformers  $N_{mni}$ . The quantity of interest is the voltage sag as a function of the charge depleted from the planes by the current drawn at the driver location, or Port i. Hence, the voltage, which is monitored and correlated to the amount of charge associated with the triangular current pulse, is the one specified in Figure 1.1 as Vplane.

An alternative representation of the power delivery network, other than the equivalent circuit model shown in Figure 1.1, would not allow monitoring the voltage Vplane and relate its decrease the amount of charge depleted from the planes themselves.

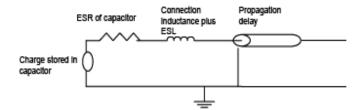

The effectiveness of a decoupling capacitor is an important issue when designing a decoupled power bus. Often, effectiveness is defined as the ability to lower the power bus impedance. From studies in the frequency domain, this effectiveness is determined as a function of two frequency independent parameters [2,6], the coefficient of mutual coupling k and the ratio of the interconnect inductance above the plane over the interconnect inductance below the planes  $L_3/L_2$ . The coefficient of mutual coupling quantifies the amount of magnetic energy coupled between an IC-pin via and the connection via of a decoupling capacitor [2,6,8]. The farther away the capacitor via from the IC via, the lower the local decoupling effectiveness, the closer the k to zero. It is also desirable to have the ratio of the inductance above the plane over the inductance below the plane to be smaller than one when the mutual coupling coefficient is much larger than zero, in order to benefit from local decoupling effects [2,6]. This is usually achievable when the plane pair is thick, i.e., 35 mils plane spacing, and the interconnect inductance above the planes is minimized by choosing the decoupling capacitors with low ESL and properly designing the decoupling capacitor pads on the top or bottom sides of the PCB.

Finally, the two frequency independent quantities can be grouped into the formula (2) [6], which quantifies the reduction, namely  $|Z_{\text{deacrease}(dB)}|$ , of the impedance.

$$\left|Z_{decrease(dB)}\right| = \left|20\log_{10}\left(\frac{\left(1-k\right)+\left(\frac{L_3}{L_2}\right)}{1+\left(\frac{L_3}{L_2}\right)}\right)\right|$$

(2)

#### **1.4. TIME DOMAIN BEHAVIOR – EARLY TIME**

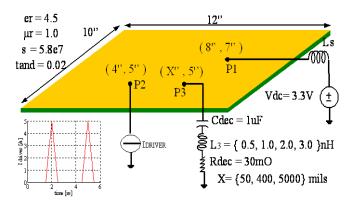

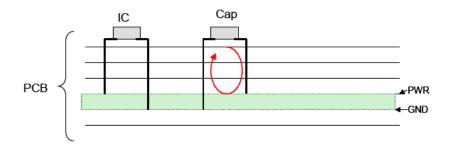

The equivalent circuit models extracted by means of the cavity model approach are used in this article to perform the investigation of power delivery issues as a function of various parameters such as decoupling capacitor distance and inductance above the planes. The inductance above the plane is varied in a range between 0.5 nH and 3 nH to observe the variations in the voltage noise excited between the power planes. On the other hand, the decoupling capacitor distance form Port 2, i.e., the point at which the current is drawn, is varied in a range between 50 mils to 5000 mils in order to observe the effects of the distance in reducing or increasing the power bus noise voltage. The two layer board of interest is shown in Figure 1.2.

Figure 1.2. Geometry under test and triangular current waveform source connected at Port 2

A constant DC voltage is connected at Port 1 through a interconnect inductance  $L_s$  of 50nH, a periodic triangular current waveform of 500 ps rise time and 3 ns repetition , also shown in Figure 1.2, is hooked up at Port 2 in order to draw charges at a given rate and observe the PDN reaction to this disturbance. Also, a 1  $\mu$ F decoupling capacitor with 30 $\Omega$  ESR and a variable  $L_3$  is connected to Port 3, whose location is at a variable distance along the x direction from the driver, i.e., 50, 400, and 5000 mils. The peak value of the current waveform is chosen to be 5 A so that every cycle approximately 20% of the overall plane charge is drawn from the driver. Finally, two values of plane separation are chosen, i.e., 35 and 10 mils.

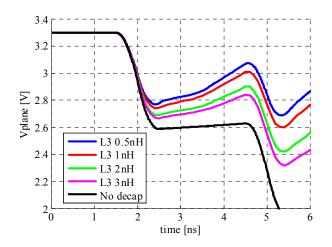

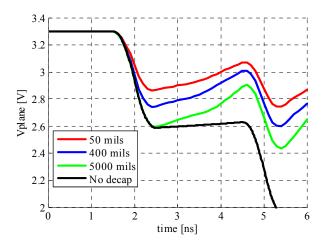

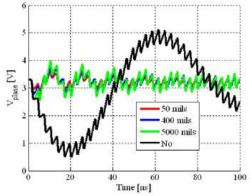

A first comparison between the two aforementioned configurations is shown in Figure 1.3 and Figure 1.4. The current waveform of Figure 1.2 is applied at Port 2 and the interconnect inductance of the decoupling capacitor, located 400 mils away from the driver, is varied in the following range, i.e., 0.5 nH, 1 nH, 2 nH, and 3 nH.

Figure 1.3. Configuration with 35 mils plane separation and decoupling capacitor 400 mils away from the driver.

It is important to observe that the time domain results agree with the frequency domain expectations [2,6] associated with the two configurations considered. The plane voltage reported in Figure 1.3 and Figure 1.4 is associated with the voltage across the plane capacitance, as indicated in Figure 1.1. By relating circuit models to the geometry, each point on the board would experience this voltage sag and each point would also have additional voltage terms associated with their positions with respect to the spatial variation of the resonant modes. Hence, the Vplane is the first order approximation of the voltage variation observed at any location. The reduction in the voltage sag observed in Figure 1.3 as a function of the decoupling capacitor interconnect inductance can be explained in terms of the impedance decrease formula given in equation (2) [2,6,8]. Since the distance between the decoupling capacitor and the driver is constant for all the four different cases, the only variable in equation (2) is the ratio between the inductance above the plane  $L_3$  and  $L_2$  which is constant for all the cases. As the  $L_3$  is increased becoming

the dominant factor, the  $L_3/L_2$  ratio also increases. Hence, the impedance-decrease factor is reduced or, the voltage swing is increased. This is true when examining results in the frequency domain, or in the time domain. The plane voltage sag lowers the plane voltage during the time when the current draw is increasing. During the time in which the current draw decreases, the plane voltage increases, but it doesn't return to the level at which it started, i.e., 3.3 V. Hence, when the second current pulse begins, the plane voltage sags again and later in the current cycle, when the current draw decreases, again, the voltage rises, but it cannot reach the value it had achieved after the first triangular pulse. This phenomenon reflects the physics of charge replenishment, or lack thereof in this case. The decoupling capacitor is not able to respond quick enough to meet the charge demand from the driver.

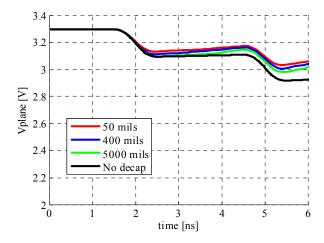

The negligible reduction in the voltage sag associated with the 10 mils configuration as a function of the decoupling interconnect inductance can also be explained in terms of equation (2). The mutual coupling coefficient k is the same as the 35 mils case. However, the value of  $L_2$  is 3.5 time smaller, hence the ratio of  $L_3/L_2$  is 3.5 time larger, making this term the dominant one in equation (2).

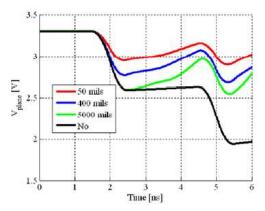

Figure 1.4. Configuration with 10 mils plane separation and decoupling capacitor 400 mils away from the driver.

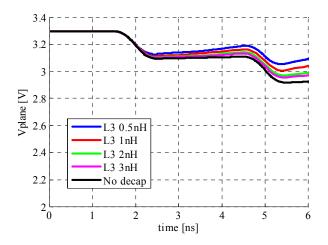

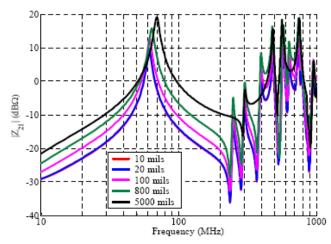

The overall difference in the voltage swing observed when comparing the curves in Figure 1.3 and Figure 1.4 is also explained by considering that the interplane capacitance of the 10 mils case is also 3.5 larger than the interplane capacitance of the 35 mils case. Hence, the thin configuration is more effective in terms of decoupling by supporting the same amount of charge draw with a smaller voltage sag. Two additional comparisons of the decoupling capacitor effectiveness, as a function of the distance of the decoupling capacitor itself to the driver, are given in Figure 1.5 and Figure 1.6, for the 35 mils case and the 10 mils case, respectively. The reduction in the voltage sag in Figure 1.5 can be again explained in terms of equation (2) [2,6,8]. As the decoupling capacitor is moved far away from the driver, the coupling coefficient k decreases, making equation (2) in value close to one.

Figure 1.5. Plane separation 35 mils and 1nH decoupling capacitor interconnect inductance

This effect is less important, hence the location of the decoupling capacitors with respect to the driver, is less important when considering thin parallel plane pair, as shown in Figure 1.6. As already mentioned in the previous paragraph, when reducing the plane separation from 35 mils down to 10 mils, the coupling coefficient is reduced of about 3.5 times and the plane capacitance is increased accordingly. Hence, the voltage swing is not significantly affected by the physics described in equation (2) and the overall voltage

level is higher since the plane can provide the same amount of charges with a smaller voltage sag.

Figure 1.6. Plane separation 10 mils and 1nH decoupling capacitor interconnect inductance

The values associated with the two frequency independent quantities constituting equation (2), i.e., the coupling coefficient k and the ratio of inductances  $L_3/L_2$  are reported in Table 1.1, Table 1.2, Table 1.3 and Table 1.4 and for all the curves shown in Figure 1.3, Figure 1.4, Figure 1.5 and Figure 1.6. The value of the  $|Z_{decrease}|$  is also shown in the two tables and it is possible to devise the correlation described in the previous paragraphs between the curves in the aforementioned plots and the values obtained from equation (2) [6].

| 35 mils $L_2 = 1.0$ nH & k = 0.38 @ 400 mil |                 |                                           |  |  |

|---------------------------------------------|-----------------|-------------------------------------------|--|--|

| $L_3 = 0.5 nH$                              | $L_3/L_2 = 0.5$ | $ Z_{\text{decrease}(\text{dB})}  = 2.62$ |  |  |

| $L_3 = 1.0 nH$                              | $L_3/L_2 = 1.0$ | $ Z_{\text{decrease}(\text{dB})}  = 1.83$ |  |  |

| $L_3 = 2.0 nH$                              | $L_3/L_2 = 2.0$ | $ Z_{\text{decrease}(\text{dB})}  = 1.21$ |  |  |

| $L_3 = 3.0 nH$                              | $L_3/L_2 = 3.0$ | $ Z_{\text{decrease}(\text{dB})}  = 0.92$ |  |  |

Table 1.1. k,  $L_3/L_2$  and  $|Z_{decrease(dB)}|$  factor for the curves in Figure 1.3

| 10 mils $L_2 = 0.28$ nH & k = 0.38 @ 400 mil |                  |                                           |  |

|----------------------------------------------|------------------|-------------------------------------------|--|

| $L_3 = 0.5 nH$                               | $L_3/L_2 = 1.78$ | $ Z_{\text{decrease}(\text{dB})}  = 1.31$ |  |

| $L_3 = 1.0 nH$                               | $L_3/L_2 = 3.5$  | $ Z_{\text{decrease}(\text{dB})}  = 0.82$ |  |

| $L_3 = 2.0 nH$                               | $L_3/L_2 = 7.1$  | $ Z_{\text{decrease}(\text{dB})}  = 0.45$ |  |

| $L_3 = 3.0 nH$                               | $L_3/L_2 = 10$   | $ Z_{\text{decrease}(\text{dB})}  = 0.25$ |  |

Table 1.2. k,  $L_3/L_2$  and  $|Z_{decrease(dB)}|$  factor for the curves in Figure 1.4.

Table 1.3. k,  $L_3/L_2$  and  $|Z_{decrease(dB)}|$  factor for the curves in Figure 1.5.

| 35 mils - $L_3 = 1.0$ nH & $L_2 = 1.0$ nH (~ same for all cases) |                 |          |                                           |

|------------------------------------------------------------------|-----------------|----------|-------------------------------------------|

| 50 mils                                                          | $L_3/L_2 = 1.0$ | k = 0.74 | $ Z_{decrease(dB)}  = 4.00$               |

| 400 mils                                                         | $L_3/L_2 = 1.0$ | k = 0.38 | $ Z_{\text{decrease}(\text{dB})}  = 1.83$ |

| 5000 mils                                                        | $L_3/L_2 = 1.0$ | k = 0.09 | $ Z_{\text{decrease}(\text{dB})}  = 0.45$ |

Table 1.4. k,  $L_3/L_2$  and  $|Z_{decrease(dB)}|$  factor for the curves in Figure 1.6.

| 10 mils - $L_3 = 1.0$ nH & $L_2 = 0.28$ nH (~ same for all cases) |                 |          |                                           |

|-------------------------------------------------------------------|-----------------|----------|-------------------------------------------|

| 50 mils                                                           | $L_3/L_2 = 3.5$ | k = 0.74 | $ Z_{\text{decrease}(\text{dB})}  = 1.51$ |

| 400 mils                                                          | $L_3/L_2 = 3.5$ | k = 0.38 | $ Z_{\text{decrease}(\text{dB})}  = 0.82$ |

| 5000 mils                                                         | $L_3/L_2 = 3.5$ | k = 0.09 | $ Z_{\text{decrease}(\text{dB})}  = 0.18$ |

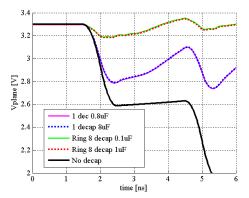

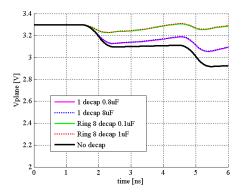

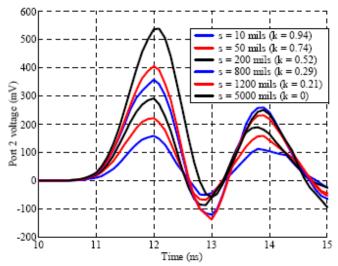

Four additional comparisons are finally presented in Figure 1.7 and Figure 1.8 in the timed domain and in Figure 1.9 and Figure 1.10 and in the frequency domain. A 400 mils radius ring of eight capacitors centered around the driver is compared against a single capacitor, 8 times larger also 400 mils away from the driver along one direction.

The conclusions to be drawn when comparing each set of curves within each plot is that the ring of decoupling capacitor acts by improving the speed of charge delivery from the capacitors themselves to the plane, where the voltage across the plane starts sagging. It is also seen, by comparing Figure 1.7 and Figure 1.8, that the value of decoupling capacitor is not important in the very early instants of time during the plane charge depletion. An array of decoupling capacitors, presenting a lower interconnect inductance, is superior to a single capacitor of much greater value.

Figure 1.7. Early instants of time comparison between a ring of eight 0.1  $\mu$ F decoupling capacitor 400 mils away from the driver *vs.* a single 0.8  $\mu$ F decoupling capacitor at 400 mils away from the driver (L<sub>3</sub> = 0.5 nH and ESR 30 mΩ) and a ring of eight 1 $\mu$ F decoupling capacitor 400 mils away from the driver *vs.* single 8 $\mu$ F decoupling capacitor at 400 mils away from the driver for a 35 mils plane separation (L<sub>3</sub> = 0.5 nH and ESR 30mΩ)

There is a definitive improvement when compared with the case of no decoupling, but also the improvement with respect to the single capacitor is remarkable and it amount to approximately 400mV in the case of 35 mils. The smaller voltage swing associated with the 10 mils cases is again explained by considering that the interplane capacitance is 3.5 times higher.

Figure 1.8. Early instants of time comparison between a ring of eight 0.1  $\mu$ F decoupling capacitor 400 mils away from the driver *vs.* a single 0.8  $\mu$ F decoupling capacitor at 400 mils away from the driver (L<sub>3</sub> = 0.5 nH and ESR 30 mΩ) and a ring of eight 1  $\mu$ F decoupling capacitor 400 mils away from the driver *vs.* a single 8  $\mu$ F decoupling capacitor at 400 mils away from the driver for 10 mils plane separation (L<sub>3</sub> = 0.5 nH and ESR 30mΩ).

This rationale is also confirmed by looking at the frequency domain plots given Figure 1.9 and Figure 1.10 corresponding to the time domain graphs of Figure 1.7 and Figure 1.8, respectively. First of all, the self-impedance observed across the driver port, when the plane separation is 35 mils, is approximately 10 dB higher with respect to the 10 mils case above approximately 50 MHz. This improvement is well documented in the literature [1-9] and also confirmed by the timed domain simulations presented in the previous paragraph. Also, above 20-30 MHz, both graphs confirm the greater importance of the interconnect inductance over the values of the decoupling capacitance utilized. The two ring configurations as well as the single decoupling configurations exhibit the same frequency domain behavior, respectively, in both the 35 mils case and the 10 mils case.

It is important to note that different nodes are monitored when the pair of curves given in Figure 1.7 and Figure 1.8 and the pair of curves shown in Figure 1.9 and Figure 1.10 are obtained. In fact, the time domain curves were observed at the node Vplane shown in Figure 1.1. This node provides a first order approximation of the plane voltage noise and it is not affected by the  $L_{ii}$ di/dt voltage drop, which is large compared to the one across the plane in the configuration of Figure 1.2. On the other hand, the input impedance plots were both observed from Port 2, or the driver port, hence the port inductance is considered and it prevails at higher frequencies. This is the reason why the self impedance in both the cases of the ring of decoupling capacitors and the single decoupling capacitor exhibits the same impedance behavior above 100 MHz, while the plots of early instants of time show significant differences. The difference between the ring and the single capacitors is more visible in the range between 10 MHz and approximately 100 MHz, where the effect of the interconnect inductance of the decoupling capacitors play a role in reducing the plane impedance.

Figure 1.9. Frequency domain comparison between a ring of eight 0.1  $\mu$ F decoupling capacitor 400 mils away from the driver *vs.* a single 0.8  $\mu$ F decoupling capacitor at 400 mils away from the driver (L<sub>3</sub> = 0.5 nH and ESR 30 mΩ) and a ring of eight 1  $\mu$ F decoupling capacitor 400 mils away from the driver *vs.* single 8  $\mu$ F decoupling capacitor at 400 mils away from the driver for a 35 mils plane separation (L<sub>3</sub> = 0.5 nH and ESR 30mΩ).

Figure 1.10. Frequency domain comparison between a ring of eight 0.1  $\mu$ F decoupling capacitor 400 mils away from the driver *vs.* a single 0.8  $\mu$ F decoupling capacitor at 400 mils away from the driver (L<sub>3</sub> = 0.5 nH and ESR 30 mΩ) and a ring of eight 1  $\mu$ F decoupling capacitor 400 mils away from the driver *vs.* a single 8  $\mu$ F decoupling capacitor at 400 mils away from the driver for 10 mils plane separation (L<sub>3</sub> = 0.5 nH and ESR 30mΩ).

## **1.5. CONCLUSIONS**

Modeling problems issues, as well as, some important design issues are in this paper. In particular, it is been shown the importance of the higher order mode self and mutual inductances, which are crucial parameters to represent correctly when dealing with decoupling issues. A reduction in the impedance, in the frequency domain, or a reduction in the voltage swing, in the time domain can be achieved for some PDN designs by placing the decoupling capacitors close to the drivers and minimizing their interconnect inductance. The PDN associated with thin power planes, i.e., 10 mil and below, are not significantly affected by the decoupling placement as shown in the time domain plots given in the previous paragraph. It is very interesting to note that the value of the decoupling capacitors themselves do not make a difference in the early instants of time. In this time frame, it is of more importance achieving a configuration with a low parasitic interconnect inductance rather than increasing the value of decoupling capacitors.

#### **1.6. REFERENCES**

- Knighten, James L., Bruce Archambeault, Jun Fan, Samuel Connor, James L. Drewniak, "PDN design strategies: I. Ceramic SMT decoupling capacitors – what values should I choose?," IEEE EMC Society Newsletter, Issue No. 207, Fall 2005, pp. 34-41.

- Knighten, James L., Bruce Archambeault, Jun Fan, Giuseppe Selli, Liang Xue, Samuel Connor, and James L. Drewniak, "PDN design strategies : I. Ceramic SMT decoupling capacitors – does location matter ?," IEEE EMC Society Newsletter, Issue No. 208, Winter 2006, pp. 56-67.

- L. Smith, R.E. Anderson, D.W. Forehand, T.J. Pelc, and T. Roy, "Power distribution system design methodology and capacitor selection for modern CMOS technology," IEEE Transaction on Advanced Packaging, Vol. 22, No. 3, August 1999, pp. 284-291.

- L. Smith, "Decoupling capacitor calculations for CMOS circuits," Proceedings of Electrical Performance of Electronic Packages (EPEP), Monterey, CA, November 1994.

- J.L.Drewniak, B.Archambeault, J.L.Knighten, G.Selli, J.Fan, M.Cocchini, S. Connor, and L.Xue, "Comparing Time-Domain and Frequency Domain Techniques for Investigation on Charge Delivery and Power-Bus Noise for High-Speed Printed Circuit Boards," Accepted for Publication on Proceedings of Design Conference East, CA, Feb. 2007.

- Fan, Jun, James L. Drewniak, James. L. Knighten, Norman W. Smith, and Antonio Orlandi, Thomas P. Van Doren, Todd H. Hubing, and Richard E. DuBroff "Quantifying SMT Decoupling Capacitor Placement in DC Power-Bus Design for Multi-Layer PCBs," IEEE Trans. of Electromagnetic Compatibility, Vol. 43, No. 4, November 2001, pp. 588-599.

- Fan, Jun, Wei Cui, James L. Drewniak, Thomas Van Doren, and James L. Knighten, "Estimating the Noise Mitigating Effect of Local Decoupling in Printed Circuit Boards," IEEE Transactions on Advanced Packaging, Vol. 25, No. 2, May 2002, pp. 154-165.

- 8. Jun Fan, James L. Knighten, Lin Zhang, Giuseppe Selli, Jingkun Mao, Bruce Archambeault, Richard E. DuBroff, and James L. Drewniak, "An investigation of the importance of decoupling capacitor values in high-speed digital PCBs," IMAPS Advanced Technology Workshop on High-Speed Interconnect, EMC and Power Aspects of System Packaging for High-Performance Computing, Telecom and Semiconductor Capital Equipment, Palo Alto, CA, October 2003.

- Archambeault, B., Juan Wang, and Samuel Connor, "Power and Ground-Reference Plane Impedance Determination As Decoupling Capacitor Distance Increases," IEEE International Symposium on Electromagnetic Compatibility, August 2003, pp. 875-880.

- Y. Lo, D. Solomon, W. Richards, "Theory and experiment on microstrip antennas," IEEE Trans. Antennas and Propagation, vol. 27, pp. 137-145, March 1979.

- T. Okoshi, Planar Circuits for Microwaves and Lightwaves, Springer-Verlag Berlin Heidelberg, 1985.

- G.T. Lei, R.W. Techentin, R.P. Hayes, D.J. Schwab, and B.K.Gilbert," Wave model to the Ground/Power Plane Noise Problem," IEEE Transactions on Instrumentations and Measurements, Vol.44, No.2, April 1995, pp. 300-303.

- G.T. Lei, R.W. Techentin, and B.K.Gilbert, "High-frequency characterization of power/ground-planes structures" IEEE Transactions on microwave Theory and Technique, Vol.47, No.5, May 1999, pp. 562-569.

- 14. C. Wang, J. Mao, G. Selli, S. Luan, L. Zhang, J. Fan, D.J. Pommerenke, R.E. Dubroff, and J.L. Drewniak, "An efficient approach for power delivery network design with closed-form expressions for parasitic interconnect inductance,", IEEE Transactions on Advanced Packaging, Vol. 29, No.2.

- 15. G. Selli, J.L. Drewniak, L. Xue, J.L. Knighten, J. Fan, B. Archambeault, S. Connor, and C. Wang, "Modeling and design of embedded capacitances for power distribution networks on multilayer printed circuit board," Proceedings of Design Conference East, CA, Feb. 2006.

- 16. G. Selli, L. Xue, J.L. Drewniak, B. Archambeault, J.Fan, S. Connor and J.L. Knighten "Power delivery effectiveness of multiple power plane pair configuration printed circuit board" IMAPS Advanced Technology Workshop on High-Speed Interconnect, EMC and Power Aspects of System Packaging for High-Performance Computing, Telecom and Semiconductor Capital Equipment, San Diego, CA, October 2006

- J. Knighten, J., B. Archambeault, J. Fan, G. Selli, L. Xue, S. Connor, J. Drewniak, "PDN Design Strategies: III. Planes and Materials – Are they Important Factors in Power Bus Design?," IEEE EMC Society Newsletter, Issue No. 208, Winter 2006, pp. 56-67.

## 2. NOISE COUPLING BETWEEN SIGNAL AND POWER/GROUND NETS DUE TO SIGNAL VIAS TRANSITIONING THROUGH POWER/GROUND PLANE PAIR

Jun Fan, Matteo Cocchini, Bruce Archambeault, James L. Knighten, James L. Drewniak, Samuel Connor Electrical Engineering University of Missouri – Rolla, Missouri, USA 65401 Email: jfan@mst.edu, mcfk9@mst.edu, barch@us.ibm.com, jim.knighten@ncr.com, drewniak@mst.edu, sconnor@us.ibm.com

## 2.1. ABSTRACT

Signal vias are often used to move a signal from one PCB layer to another. As a result, these vias can penetrate power/ground plane pair and cause noise coupling (crosstalk) between signal and power/ground nets. This paper studies the noise coupling mechanism using a segmentation approach combined with a via capacitance model and a plane-pair cavity model. Noise coupling from signal to power/ground, and vice versa, is demonstrated in the modeling results.

*Keywords:* Differential signal, noise coupling, signal and power/ground nets, signal via transition, via capacitance, cavity model, ground vias.

#### **2.2. INTRODUCTION**

In modern multi-layer printed circuit boards (PCBs), signal vias are extensively used to route signals from one layer to another. The high density and small package size of today's high-speed integrate circuits (ICs) force signal nets to be routed on multiple layers to facilitate access to all the pins/balls in the device's dense pin field. Further, the number of layers can be a big factor in PCB cost. By transitioning signals among multiple layers PCB real estate may be used more efficiently, possibly reducing the number of signal layers required in the PCB. Vias used for signal layer transitions are likely to penetrate one or more power and/or ground planes, Power/ground plane pair are commonly used in multi-layer highspeed PCB designs as a power distribution network. Previous work found the signal penetration through power and ground plane pair was a mechanism that can result in power bus noise, in addition to the more commonly understood simultaneous switching noise (SSN)[1-2].

This noise coupling phenomenon can be explained using the return current for the signal penetrating the power and ground plane pair. Even if there are many decoupling capacitors placed between the power and ground plane pair, not all the return current will take the capacitor paths because of the interconnect inductance associated with these decoupling capacitors. A portion of the return current will jump between the planes in the form of a displacement current, and hence excite the power and ground plane pair. The same phenomenon can occur between two power planes with different logic levels.

The noise coupling mechanism described above works in the reverse as well. A signal via transitioning through a power and ground plane pair can pick up the noise in the power and ground planes that may be caused by other mechanisms such as SSN. The noise from the power and ground planes may affect the integrity (quality) of the high-speed signal that propagates through the via.

This paper studies the noise coupling problems between the signal and power/ground nets due to via transition, using a segmentation method combined with a via capacitance model and a plane-pair cavity model. Section 2 introduces the modeling approach, while two typical coupling cases are modeled and discussed in Sections 3 and 4.

## 2.3. MODELING APPROACH

The modeling approach used in this paper is based on the segmentation method [3]. First, the entire geometry is divided into multiple blocks. Then, each block is modeled using an equivalent circuit model. All the blocks are finally connected together by enforcing the current and voltage continuity conditions. This approach has many advantages over the traditional full-wave modeling approaches. It extracts an equivalent circuit model that is physics-based, so that geometry features are linked with circuit

parameters for meaningful engineering design and optimization. The equivalent circuit allows the further integration of the model with other circuit components such as decoupling capacitors and IC devices, and it can be run in both the frequency and time domains. Compared to the full-wave methods, this approach is very fast and efficient. It can handle tens of plane pair and hundreds of vias, which can be the case in practical PCB designs.

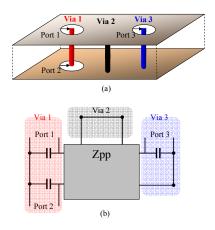

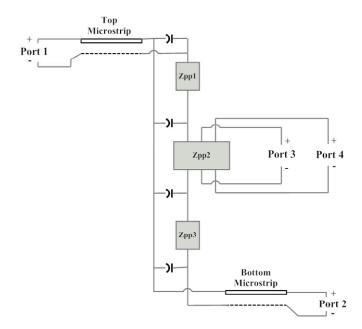

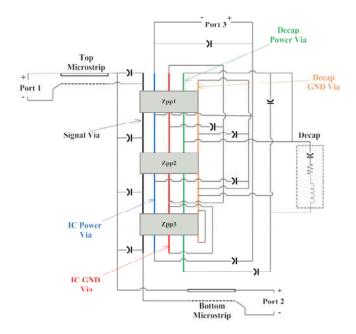

The entire PCB geometry is divided at the middle of every power or ground plane. The underlying reasoning for this is that only the TEM mode exists in the anti-pad regions that are coaxial structures in the frequency range of interest. Thus well-defined voltages and currents exist at every interface between the blocks. Figure 2.1 illustrates a typical block except the top and bottom ones that are often microstrip structures. As clearly shown in Figure 2.1(a), the geometry of every block includes a pair of planes and multiple via portions that may or may not be connected to the planes. The corresponding equivalent circuit model is shown in Figure 2.1(b), where a capacitor exists between a via portion and a plane if the via portion is not connected to the plane. The capacitance values can be calculated using a quasi-static EM tool or a closed-form expression [4]. The pair of the planes is modeled as a multi-port impedance matrix that is obtained using a cavity method [5]. The inductances associated with the via portions including the mutual ones are accounted for in the impedance matrix, as well as the dimensiondependent distributed behaviors of the plane pair.

Figure 2.1. A typical building block.

Trace/via transitions, including both microstrip/via and stripline/via transitions, can be combined with the fundamental blocks, as well as other circuit components such as decoupling capacitors and IC devices. This segmentation approach combined with the via capacitance model and the plane-pair cavity model has been validated to be effective and efficient for common PCB structures [4, 6].

#### 2.4. NOISE COUPLING FROM SIGNAL TO POWER/GROUND

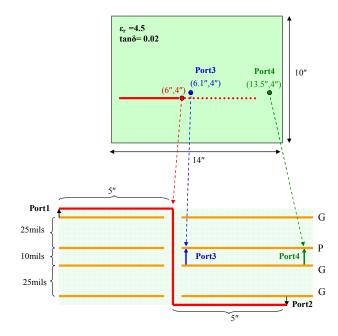

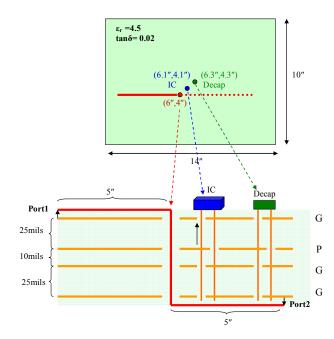

The approach was first applied to study the noise coupling from signal to power/ground nets. The test geometry is shown in Figure 2.2. It includes a multi-layer printed circuit board and a signal via transitioning a signal from the microstrip line on the top to another microstrip line on the bottom of the board. The printed circuit board has four solid planes for power supply and current return (ground planes). The signal via penetrates all the four planes.

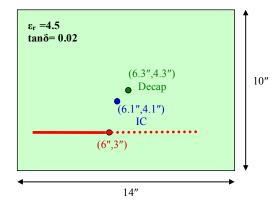

The dimensions of the printed circuit board are  $14'' \times 10''$ , and the two 50  $\Omega$  microstrip lines are both 5'' long. All the dielectric layers are assumed to have a dielectric constant of 4.5, and a loss tangent of 0.02. The signal via is located at (6'', 4'') from the left bottom corner of the board, and the via radius is 11 mils. Two ports (Ports 3 and 4) between the two middle planes are chosen to monitor the noise coupled from the signal via. Ports 1 and 2 are located at the end of the top and bottom microstrip traces, respectively.

The equivalent circuit model for the test geometry was extracted using the previously introduced segmentation approach, and is shown in Figure 2.3. Notice that the middle plane pair is modeled as a three port impedance matrix, where one port is at the signal via and the other two are at the two observation ports.

Figure 2.2. Test geometry to study noise coupling from signal to power/ground nets.

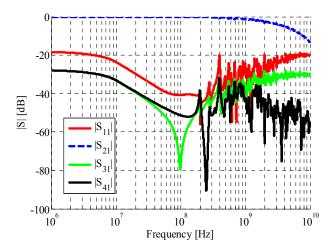

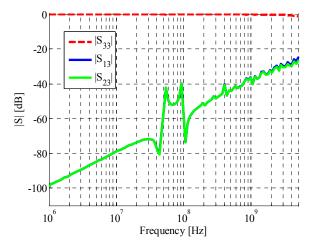

The circuit model is first investigated in the frequency domain, and the modeled S-parameters among Ports 1, 2, 3, and 4 are shown in Figure 2.4. The  $|S_{21}|$ , which indicates the transmission of the signal from the top microstrip line to the bottom one, is close to 0 dB up to approximately 1 GHz. The signal can be effectively transmitted with a very small loss. The  $|S_{21}|$  starts to decrease rapidly from 1 GHz due to both the dielectric and skin-effect losses.

The  $|S_{31}|$  and  $|S_{41}|$  reflect the noise coupling at Ports 3 and 4 from Port 1, respectively. At most of the frequencies, the magnitude of these two transfer functions ranges from -60 to -30 dB. If the signal voltage at Port 1 is strong enough, a relatively high noise voltage at Ports 3 and 4 due to the signal via transition could be generated. This is consistent with the previous work reported in [1-2].

Figure 2.3. Equivalent circuit model for the test geometry shown in Figure 2.2.

Figure 2.4. Frequency-domain transfer functions including the noise transfer functions from signal to power/ground.

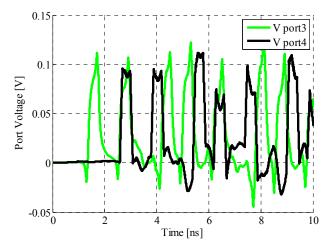

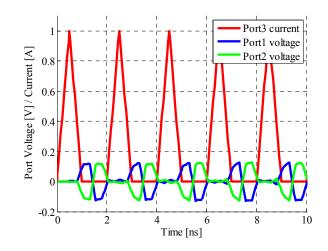

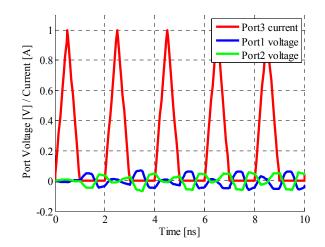

Figure 2.5 shows the time-domain waveforms when Port 1 is exited with a 5V voltage source with a 50  $\Omega$  matching source impedance. The source data rate is 2.5 Gb/s, and the rise/fall time is 100 ps. The data pattern is "010010001" in repetition. Port 2 is terminated with a 50  $\Omega$  load impedance. As clearly seen in Figure 2.5, the voltage at Port 2 has a magnitude close to 5 V, indicating the signal transmission loss is relatively small

at the fundamental frequency. However, the waveform at Port 2 is significantly rounded due to the high-frequency loss, consistent to the frequency-domain result discussed before. The noise voltages at Ports 3 and 4 are much smaller, compared to the Port 2 signal voltage. However, if they are examined more carefully in the zoomed-in plots as shown in Figure 2.6, their magnitude gets as high as 120 mV. Obviously these noise voltages cannot be neglected.

Figure 2.5. Time-domain transfer functions including the noise transfer functions from signal to power/ground.

Figure 2.6. Noise voltages generated in the power/ground plane pair due to the signal transition.

#### 2.5. NOISE COUPLING FROM POWER/GROUND TO SIGNAL

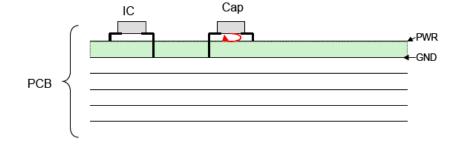

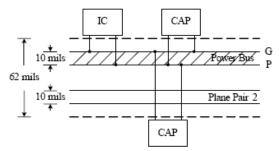

The signal via can also pick up power bus noise when it penetrates a power and ground plane pair. Figure 2.7 shows a test geometry used to study this noise coupling mechanism. Similar to the previous example, it includes a multi-layer printed circuit board and a signal via transitioning a signal from the top microstrip line to the bottom one. The PCB stackup, dimensions, the microstrip lines, and the signal via location are the same as in the previous example. Additionally, an IC and a decoupling capacitor are added in the geometry. The coordinates shown in the figure are the power via locations for these two components. Their ground vias are placed 50 mils away from the corresponding power vias. Ports 1 and 2 are located at the end of the top and bottom microstrip traces, respectively. Port 3 is set at the IC, looking into its power and ground vias. The equivalent circuit model for this test geometry is shown in Figure 2.8. The decoupling capacitor is modeled as a series RLC circuit.

Figure 2.8. Test geometry to study noise coupling from power/ground to signal nets.

Figure 2.9. Equivalent circuit model for the test geometry shown in Figure 2..

Figure 2.9 shows the frequency-domain transfer functions. As illustrated by the  $|S_{13}|$  and  $|S_{23}|$ , noise voltage can be generated at the end of the microstrip traces when the power bus noise is coupled to the signal via that penetrates the power and ground plane pair. Since the geometry is symmetric, the magnitudes of the noise voltages at Ports 1 and 2 are the same.

The corresponding time-domain results are shown in Figure 2.10. When the IC (Port 3) draws current (triangular pulses) from the power and ground plane pair, noise voltage pulses are observed at Ports 1 and 2. Notice that these two noise voltages are outof-phase. In other words, the dominant coupling is inductive coupling between the signal and power vias.

Figure 2.9. Frequency-domain transfer functions including the noise transfer functions from power/ground to signal.

Figure 2.10. Noise voltages generated in the signal trace caused by power bus noise due to the signal transition.

If the signal via location is further away from the IC and the decoupling capacitor, as illustrated in Figure 2.11, the noise coupling from the power and ground plane pair to the signal traces is weakened, as shown in both Figure 2.12 and Figure 2.13. In the frequency domain, the  $|S_{13}|$  and  $|S_{23}|$  magnitudes, generally speaking, are a few dB lower than those in Figure 2.9, except close at the two resonant frequencies of 55 MHz and 90 MHz. Due to nature of the transfer functions, this indicates a lower noise coupling from the power and ground plane to the signal traces. The trend is more intuitive in the time

domain. As shown in Figure 2.13, the magnitude of the noise voltage at Ports 1 and 2 is much lower than in Figure 2.10.

#### 2.6. CONCLUSIONS

This paper studies the noise coupling between signal and power/ground nets due to signal vias penetrating power and ground plane pair. A segmentation approach combined with a via capacitance model and a plane-pair cavity model is used. The modeled results demonstrate that noise can be coupled from the signal to the power and ground plane pair, and vice versa, with a magnitude of as high as -30 dB in the frequency-domain transfer functions. Therefore, the noise magnitude can be significant enough and careful design is required to achieve the noise mitigation and signal integrity objectives in high-speed digital circuits. The segmentation approach provides a suitable tool for effective and efficient engineering designs and optimization.

Figure 2.11. Signal via is further away from the power/ground vias, compared to the test geometry shown in Figure 2.7.

Figure 2.12. Frequency-domain transfer functions including the noise transfer functions from power/ground to signal, for the geometry shown in Figure 2.11.

Figure 2.13. Noise voltages generated in the signal trace caused by power bus noise due to the signal transition, for the geometry shown in Figure 2.11.

# **2.7. REFERENCES**

- W. Cui, X. Ye, B. Archambeault, D. White, M. Li, and J. L. Drewniak, "EMI resulting from signal via transitions through the DC power bus," IEEE International Symposium on Electromagnetic Compatibility, August 2000, pp. 821-826.

- J. L. Knighten, B. Archambeault, J. Fan, G. Selli, A. Rajagopal, S. Connor, and J. L. Drewniak, "PDN design strategies: IV. Sources of PDN noise," IEEE EMC Society Newsletter, Issue No. 212, Winter 2007, pp 54-64.

- T. Okoshi, Y. Uehara, and T. Takeuchi, "The segmentation method an approach to the analysis of microwave planar circuits," IEEE Transactions on Microwave Theory and Techniques, vol. MTT-24, no. 10, pp. 662-668, Oct. 1976.

- 4. C. Schuster, Y. Kwark, G. Selli, and P. Muthana, "Developing a 'physical' model for vias," DesignCon 2006, February 6-9, 2006, Santa Clara, CA.

- C. Wang, J. Mao, G. Selli, S. Luan, L. Zhang, J. Fan, D. Pommerenke, R. E. DuBroff, and J. L. Drewniak, "An efficient approach for power delivery network design with closed-form expressions for parasitic interconnect inductances," IEEE Transactions on Advanced Packaging, vol. 29, no. 2, pp. 320-334, May 2006.

- G. Selli, C. Schuster, Y. H. Kwark, M. B. Ritter, and J. L. Drewniak, "Developing a physical model for vias – part II: coupled and grounded return vias," Designcon 2007, Santa Clara, 2007.

#### **3. DESIGN METHODOLOGY FOR PDN SYNTHESIS ON MULTI-LAYER PCBS**

Bruce Archambeault Matteo Cocchini, Giuseppe Selli, Jun Fan, James L. Knighten, Samuel Connor, Antonio Orlandi, James L. Drewniak University of Missouri – Rolla, Missouri, USA 65401 Email: barch@us.ibm.com, mcfk9@mst.edu, gs5xd@mst.edu, jfan@mst.edu, jim.knighten@ncr.com, sconnor@us.ibm.com, orlandi@ing.univaq.it, drewniak@mst.edu

#### **3.1. ABSTRACT**

This paper discusses a fast and accurate design methodology for real world design of power distribution networks on printed circuit boards. The designer is shown how to estimate the amount of current needed for large ICs, how to estimate the amount of noise voltage due to this current draw, and the effect of decoupling capacitor distance from the IC's power/ground pins.

Keywords: EMI, Power Integrity, Signal integrity, PDN, decoupling, cavity resonance.

## **3.2. INTRODUCTION**

Proper decoupling of printed circuit board (PCB) power distribution networks (PDN) is very important for proper operation of the PCB. Decoupling of the PDN is important in (a) reducing radiated and conducted noise levels from the PCB (EMI), (b) reducing the noise level on the PCB that active components tolerate (EMC), and, (c) providing current (charge) to ICs that is timely and sufficient (usually an issue with large digital ICs). Because these three areas are broad in scope, yet distinct, there are many published design rules, but because of the breadth of decoupling requirements and the distinct character is each of the three requirements, these published design rules can contradict each other. The designer can be faced with evaluating a plethora of design rules often without the benefit of a sound understanding of the physics involved with a well designed decoupling strategy. The common result is an over design where a larger number of decoupling capacitors are used than may be required. This paper focuses on the third area of importance in decoupling, i.e., ensuring timely and sufficient charge supply to major ICs on the PCB.

The designer faces three basic questions:

(1) what is the maximum amount of noise between the power and ground-reference plane desired,

(2) how much current is needed by the IC, and

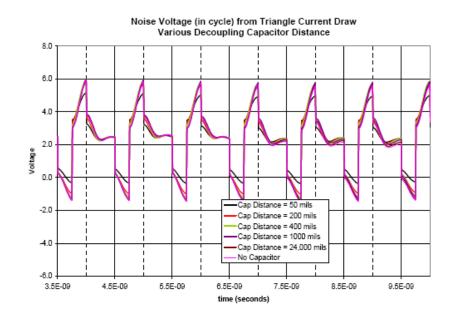

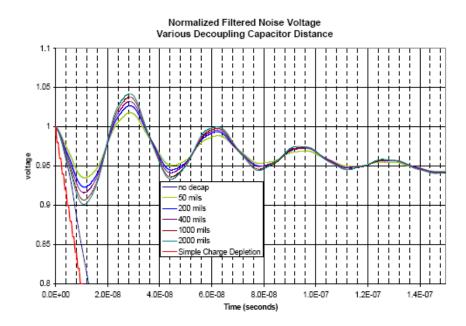

(3) how many capacitors are required to meet the goal with the variation in distance to the capacitor and capacitor connection inductance.