# Scholars' Mine

**Masters Theses**

Student Theses and Dissertations

Fall 2012

Computation of power plane pair inductance, measurement of multiple switching current components and switching current measurement for multiple ICs with an island structure

Liang Li

Follow this and additional works at: https://scholarsmine.mst.edu/masters\_theses

Part of the Electrical and Computer Engineering Commons

Department:

#### **Recommended Citation**

Li, Liang, "Computation of power plane pair inductance, measurement of multiple switching current components and switching current measurement for multiple ICs with an island structure" (2012). Masters Theses. 5322.

https://scholarsmine.mst.edu/masters\_theses/5322

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# COMPUTATION OF POWER PLANE PAIR INDUCTANCE, MEASUREMENT OF MULTIPLE SWITCHING CURRENT COMPONENTS AND SWITCHING CURRENT MEASUREMENT FOR MULTIPLE ICs WITH AN ISLAND STRUCTURE

by

#### LIANG LI

#### A THESIS

Presented to the Faculty of the Graduate School of the

MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

2012

Approved by

Jun Fan, Advisor Albert E. Ruehli Daryl Beetner

© 2012 LIANG LI All Rights Reserved

#### **PUBLICATION THESIS OPTION**

This thesis consists of the following three articles that have been formatted according to the university's spec of thesis, and published as follows:

- Pages 3 62 have been accepted to be published in 2012 Electrical Performance of Electronic Packaging and Systems (EPEPS), Tempe, AZ.

- Pages 63 76 have been published in 2011 IEEE International Symposium on Electromagnetic Compatibility, Long Beach, CA.

- Pages 77 92 have been published in 2012 IEEE International Symposium on Electromagnetic Compatibility, Pittsburgh, PA.

#### **ABSTRACT**

The first part of the thesis presents the computation of power / ground plane pair inductance based on Partial Element Equivalent Circuit (PEEC) method in power distribution network (PDN) design. An efficient approach for the inductance computation is investigated. Speed-up techniques are employed include using the faster decay of mutual coupling due to the "differential" currents (same magnitude but opposite directions) in the two planes. Also, an approximate rectangular mesh reduction method is introduced which allows a local increase in mesh density.

The second part presents a measurement-based data-processing approach to obtain parameters of multiple current components through a bulk decoupling capacitor for power integrity studies. A lab-made low-cost current probe is developed to measure the induced voltage due to the time-varying switching current. Then, a post data-processing procedure is introduced to separate and obtain the parameters of multiple current components.

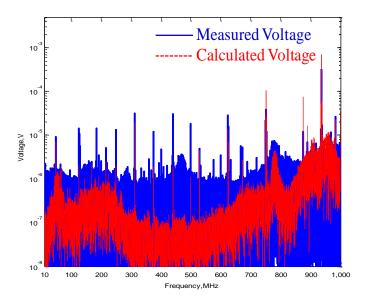

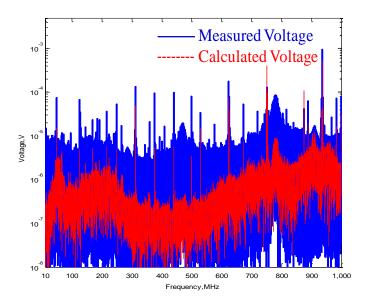

The third part proposes a measurement methodology, when IC information is not available, to obtain the equivalent switching current of each IC in the case where multiple ICs are connected to a common power island structure. Time-domain oscilloscope measurements are used to capture the noise-voltage waveforms at a few locations in the power island. Combining with the multi-port frequency-domain S-parameter measurement among the same locations, an equivalent switching current for each IC is calculated. The proposed method is validated at a different location in the power island by comparing the calculated noise voltage using the equivalent switching currents as excitations with the actual measured noise voltage.

#### ACKNOWLEDGMENTS

I would like to express my sincere gratitude to my advisor, Dr. Jun Fan, for his constant encouragement, support and guidance throughout my master degree program. I want to thank Dr. Albert Ruehli, Dr. James Drewniak, Dr. David Pommerenke and Dr. Daryl Beetner for their guidance on my research work. I also want to thank all the EMC Lab students for their help.

I would like to thank my wife, Lei Hua, for her love and support throughout these years. I would also like to thank my family for their endless love and unconditional support during my study in US.

# TABLE OF CONTENTS

|                                                                   | Page |

|-------------------------------------------------------------------|------|

| PUBLICATION THESIS OPTION                                         | iii  |

| ABSTRACT                                                          | iv   |

| ACKNOWLEDGMENTS                                                   | v    |

| LIST OF ILLUSTRATIONS                                             | viii |

| SECTION                                                           |      |

| 1. INTRODUCTION                                                   | 1    |

| PAPER                                                             |      |

| I. ACCURATE AND EFFICIENT COMPUTATION OF POWER PLANE PAINDUCTANCE |      |

| ABSTRACT                                                          | 3    |

| 1. INTRODUCTION                                                   | 4    |

| 2. THEORY AND FORMULATION                                         | 6    |

| 2.1. CONCEPTS OF PARTIAL INDUCTANCE                               | 6    |

| 2.2. PEEC METHOD                                                  | 8    |

| 2.3. MODIFIED NODAL ANALYSIS (MNA)                                | 9    |

| 2.4. THE PPP APPROACH                                             | 11   |

| 3. UNIFORM AND NON-UNIFORM MESH                                   | 23   |

| 3.1. ASSEMBLY OF MNA                                              | 23   |

| 3.2. BOOKKEEPING OF NODES                                         | 27   |

| 3.3. COMPUTATION SPEED-UP.                                        | 28   |

| 3.4. COMPUTE TIME ANALYSIS                                        | 30   |

| 3.5. NUMERICAL EXPERIMENT                                         | 32   |

| 3.6. MULTIPLE CONTACTS                                            | 34   |

| 3.7. NON-UNIFORM MESH                                             | 38   |

| 3.8. NUMERICAL EXPERIMENT FOR NON-UNIFORM MESH                    | 41   |

| 3.9. CLOSE VIAS                                                   | 42   |

| 3.10. DETERMINE SUB-MESH REGION                                   | 43   |

| 3.11. VALIDATION OF SUB-MESH METHOD                               | 45   |

|      |      | 3.12. CURRENT DISTRIBUTION ANALYSIS                                                | . 46 |

|------|------|------------------------------------------------------------------------------------|------|

|      |      | 3.13. EFFICIENCY OF SUB-MESH METHOD                                                | . 51 |

|      |      | 3.14. VIA INDUCTANCE                                                               | . 52 |

|      |      | 3.15. PLANE INDUCTANCE WITH DIFFERENT SHORT LOCATIONS .                            | . 55 |

|      |      | 3.16. APPLICATION IN PDN DESIGN                                                    | . 58 |

|      | 4.   | CONCLUSION                                                                         | 60   |

|      | BIB  | LIOGRAPHY                                                                          | . 61 |

| II.  |      | SUREMENT OF MULTIPLE SWITCHING CURRENT COMPONENTS DUGH A BULK DECOUPLING CAPACITOR | .63  |

|      | AB   | STRACT                                                                             | 63   |

|      | 1.   | INTRODUCTION                                                                       | 64   |

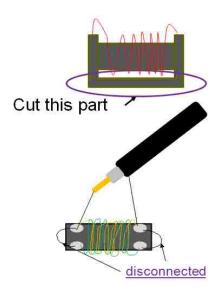

|      | 2.   | PROPOSED CURRENT PROBE                                                             | 66   |

|      | 3.   | SEPARATION AND CHARACTERIZATION OF MULTIPLE CURRENT COMPONENTS                     |      |

|      | 4.   | CONCLUSION                                                                         | . 75 |

|      | BIB  | LIOGRAPHY                                                                          | . 76 |

| III. |      | TCHING – CURRENT MEASUREMENT FOR MULTIPLE ICs SHARING MMON POWER ISLAND STRUCTURE  |      |

|      | AB   | STRACT                                                                             | . 77 |

|      | 1.   | INTRODUCTION                                                                       | . 78 |

|      | 2.   | THEORY AND MEASUREMENT SETUPS                                                      | . 80 |

|      | 3.   | RESULTS AND DISCUSSIONS                                                            | . 85 |

|      | 4.   | CONCLUSION                                                                         | . 91 |

|      | BIB  | LIOGRAPHY                                                                          | . 92 |

| SE   | CTIO | V                                                                                  |      |

|      | 2.   | CONCLUSIONS.                                                                       | .93  |

| AP   | ENDE | X                                                                                  | .95  |

| Vľ   | ТА   |                                                                                    | .97  |

# LIST OF ILLUSTRATIONS

|             |                                                                                                                  | Page |

|-------------|------------------------------------------------------------------------------------------------------------------|------|

| Paper I     |                                                                                                                  |      |

| Figure 2.1  | Division of conductors into segments.                                                                            | 8    |

| Figure 2.2  | Power/Ground plane pair with IC and decoupling capacitors                                                        | 11   |

| Figure 2.3  | Current distribution on power and ground planes.                                                                 | 12   |

| Figure 2.4  | Plane subdivision                                                                                                | 13   |

| Figure 2.5  | Partial inductance evaluation.                                                                                   | 13   |

| Figure 2.6  | Two parallel thin conductors                                                                                     | 14   |

| Figure 2.7  | i-th and j-th section                                                                                            | 15   |

| Figure 2.8  | The corresponding equivalent circuit of <i>i-th</i> and <i>j-th</i> section                                      | 15   |

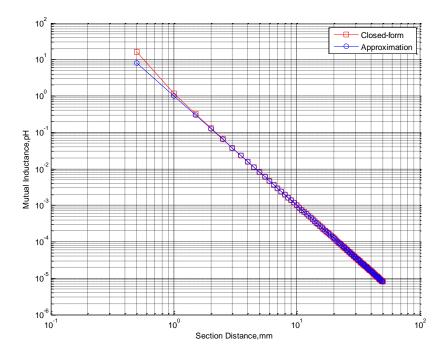

| Figure 2.9  | Partial-mutual inductance between two sections calculated by the closed-form formula and approximated method     | 18   |

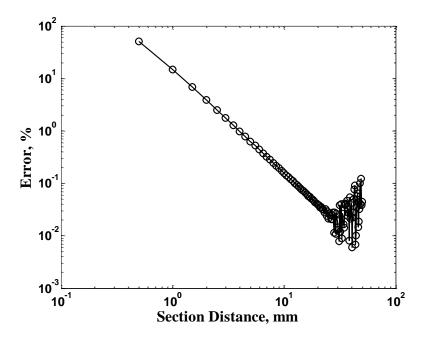

| Figure 2.10 | Relative error between the closed-form formula and approximation                                                 | 19   |

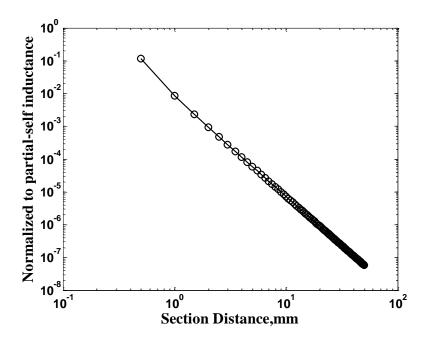

| Figure 2.11 | Normalized to partial-self inductance.                                                                           | 20   |

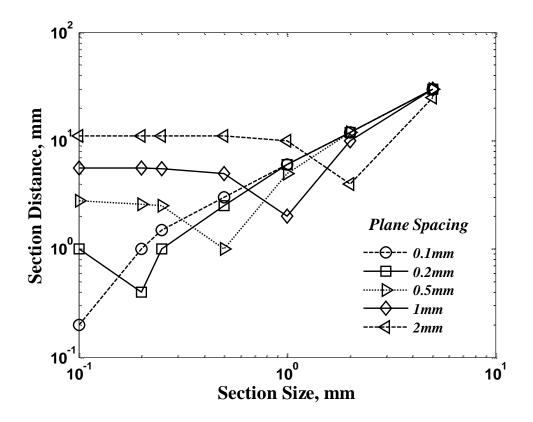

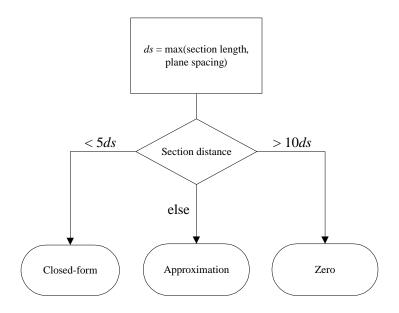

| Figure 2.12 | Criteria to apply the approximation formula                                                                      | 22   |

| Figure 2.13 | Schematic of criteria determination when <i>err</i> = 3%                                                         | 22   |

| Figure 3.1  | Example with the smallest structure. (a) Mesh in x and y direction. (b) Partial inductance in x and y direction. | 23   |

| Figure 3.2  | Equivalent circuit of the example with the smallest structure                                                    | 24   |

| Figure 3.3  | Bookkeeping of the nodes.                                                                                        | 27   |

| Figure 3.4  | Example for partial-self and partial-mutual inductance calculation                                               | 29   |

| Figure 3.5  | Total compute time vs. unknowns                                                                                  | 31   |

| Figure 3.6  | Time for stamping MNA matrix vs. unknowns                                                                        | 31   |

| Figure 3.7  | Time for solving MNA matrix vs. unknowns                                                                         | 32   |

| Figure 3.8  | Test geometry                                                                                                    | 33   |

| Figure 3.9  | PWR/GND pair with multiple vias                                                                                  | 34   |

| Figure 3.10 | Test geometry with 10 contacts.                                                                                  | 34   |

| Figure 3.11 | Test geometry for multiple shorts                                                                                | 35   |

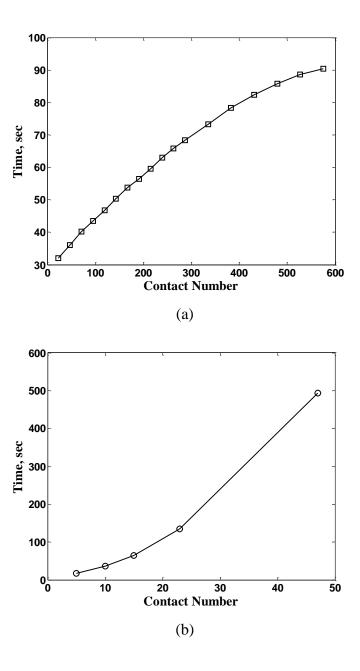

| Figure 3.12 | Compute time comparison for multiple contacts. (a) PPP approach. (b) Cavity model.                               | 37   |

| Figure 3.13 | of the interface in x direction. (c) Zoom-in of the interface in y direction.                                                                                                                                                                   | . 38 |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 3.14 | Transition between mesh density.                                                                                                                                                                                                                | . 39 |

| Figure 3.15 | Sub-mesh around the vias.                                                                                                                                                                                                                       | . 41 |

| Figure 3.16 | Close vias covered by one sub-mesh region                                                                                                                                                                                                       | . 42 |

| Figure 3.17 | Define the sub-mesh region around the vias.                                                                                                                                                                                                     | . 43 |

| Figure 3.18 | Current distribution on the plane. (a) x direction; (b) y direction                                                                                                                                                                             | . 44 |

| Figure 3.19 | Test geometry for the inductance calculation [8]. (a) Variables are spacing between two vias, $l$ , and separation between two planes, $d$ . (b) Port condition.                                                                                | . 45 |

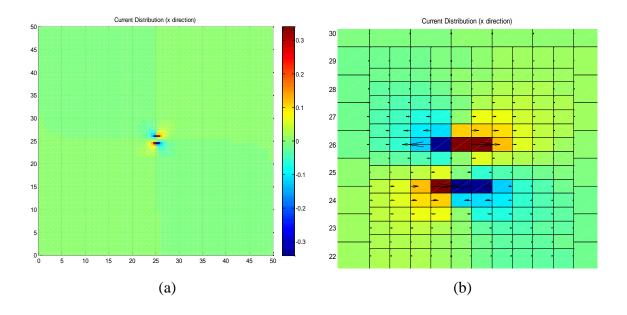

| Figure 3.20 | Current distribution in $x$ direction on the plane with $d = 1$ mm and $l = 1.5$ mm. (a) Total current distribution in $x$ direction. (b) Current vector in $x$ direction at the source and short.                                              | . 46 |

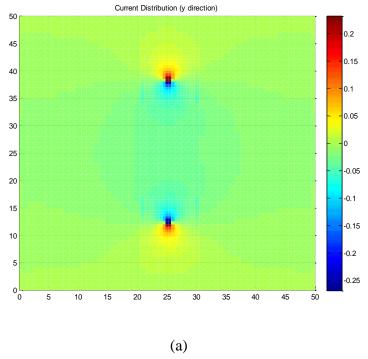

| Figure 3.21 | Current distribution in $y$ direction on the plane with $d=1$ mm and $l=1.5$ mm. (a) Total current distribution in $y$ direction. (b) Current vector in $y$ direction at the source and short.                                                  | . 47 |

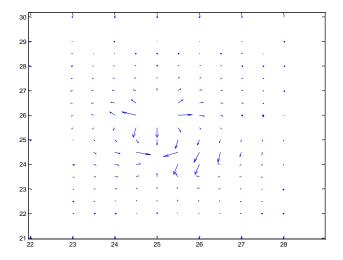

| Figure 3.22 | Zoom-in of current vector at source and short on the plane with $d = 1 \text{mm}$ and $l = 1.5 \text{mm}$                                                                                                                                       | . 47 |

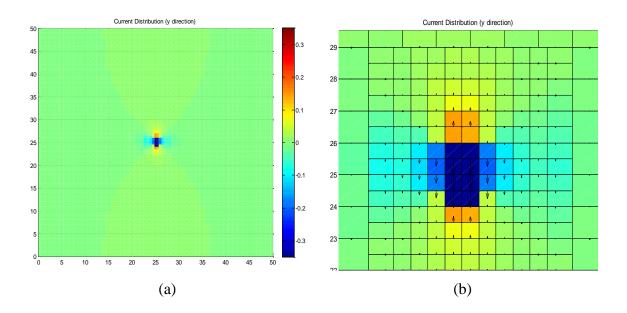

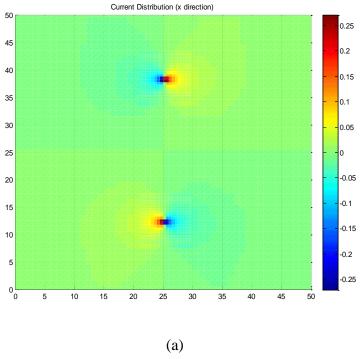

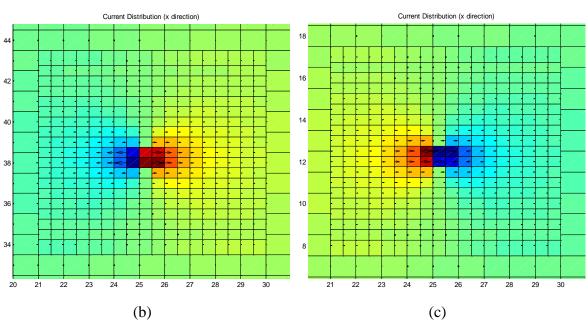

| Figure 3.23 | Current distribution in $x$ direction on the plane with $d = 1$ mm and $l = 25.5$ mm. (a) Total current distribution in $x$ direction. (b) Current vector in $x$ direction at the source port. (c) Current vector in $x$ direction at the short | . 48 |

| Figure 3.24 | Current distribution in y direction on the plane with $d = 1$ mm and $l = 25.5$ mm. (a) Total current distribution in y direction. (b) Current vector in y direction at the source. (c) Current vector in y direction at the short.             | . 49 |

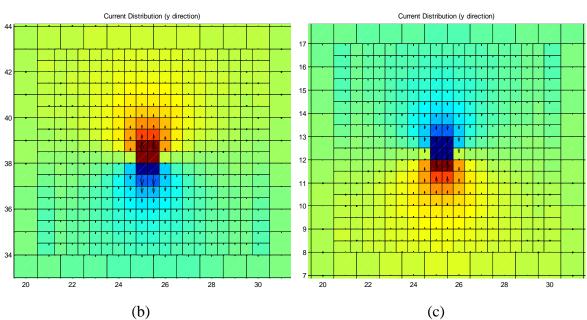

| Figure 3.25 | Current vector on the plane with $d = 1$ mm and $l = 25.5$ mm. (a) Zoom-in of the current vector between source and short. (b) Current vector at the source port. (c) Current vector at the short.                                              | . 50 |

| Figure 3.26 | Via constructed with 4 metal sheets.                                                                                                                                                                                                            | . 52 |

| Figure 3.27 | Zero thickness conductors at 90 deg angle.                                                                                                                                                                                                      | . 52 |

| Figure 3.28 | Source via and short via                                                                                                                                                                                                                        | . 53 |

| Figure 3.29 | Geometry for board inductance test. (a) Source fed at center. (b) Source fed at a corner.                                                                                                                                                       | . 55 |

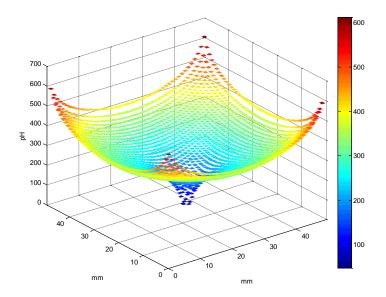

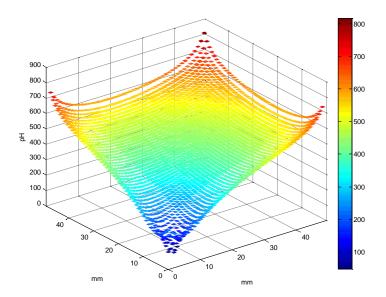

| Figure 3.30 | 3D plot for inductance with the source fed at center and the short placed at different locations on the board.                                                                                                                                  | . 56 |

| Figure 3.31 | 2D plot for inductance (pH) with the source fed at center and the short placed at different locations on the board.                                                                                                                             | . 56 |

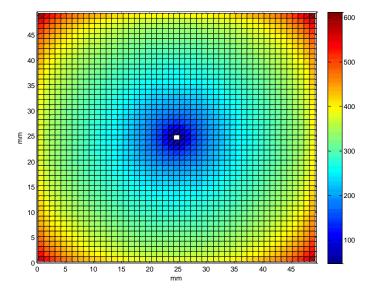

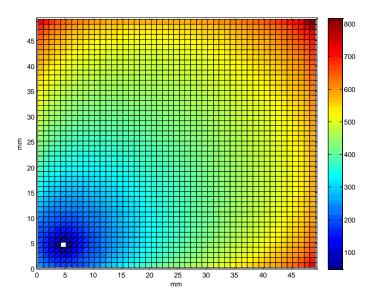

| Figure 3.32 | 2 3D plot for inductance (pH) with the source fed at corner and the short placed at different locations on the board                                                         |            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| Figure 3.33 | 2D plot for inductance (pH) with the source fed at corner and the short placed at different locations on the board.                                                          | 7          |

| Paper II    |                                                                                                                                                                              |            |

| Figure 2.1  | Structure of the proposed low-cost probe                                                                                                                                     | 6          |

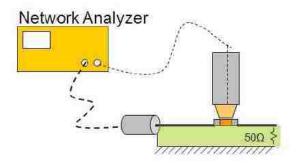

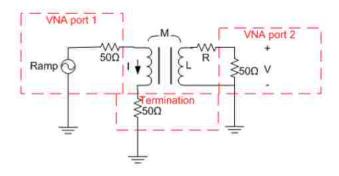

| Figure 2.2  | Measurement setup for current probe calibration                                                                                                                              | 7          |

| Figure 2.3  | Equivalent circuit of the measurement setup shown in Figure 2.2 6                                                                                                            | 7          |

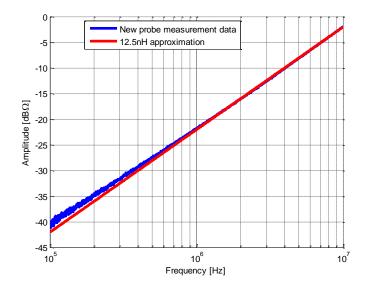

| Figure 2.4  | Transfer coefficient of the lab-made current probe for a specific bulk capacitor package                                                                                     | i8         |

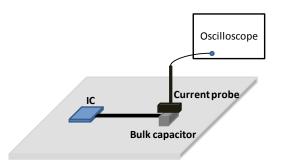

| Figure 3.1  | Experimental setup of the bulk capacitor current measurement using the lab-made current probe.                                                                               | <u>5</u> 9 |

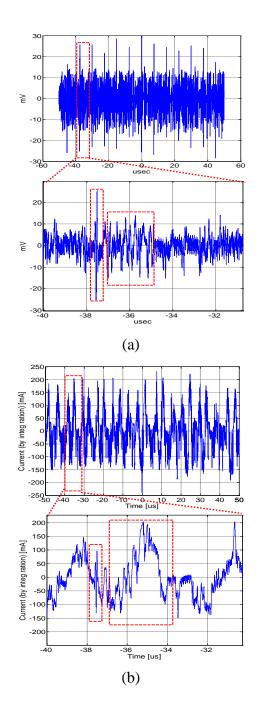

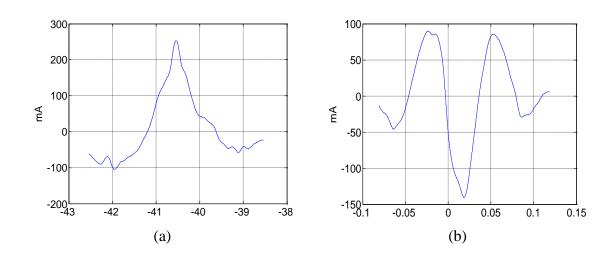

| Figure 3.2  | Induced voltage and corresponding current. (a) Measured induced voltage in the current probe; (b) Current calculated from Eq. (1)                                            | 0'         |

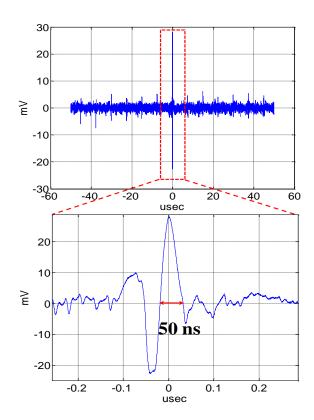

| Figure 3.3  | Measured current component that results in the induced voltage peaks using the triggered averaging technique                                                                 | 1          |

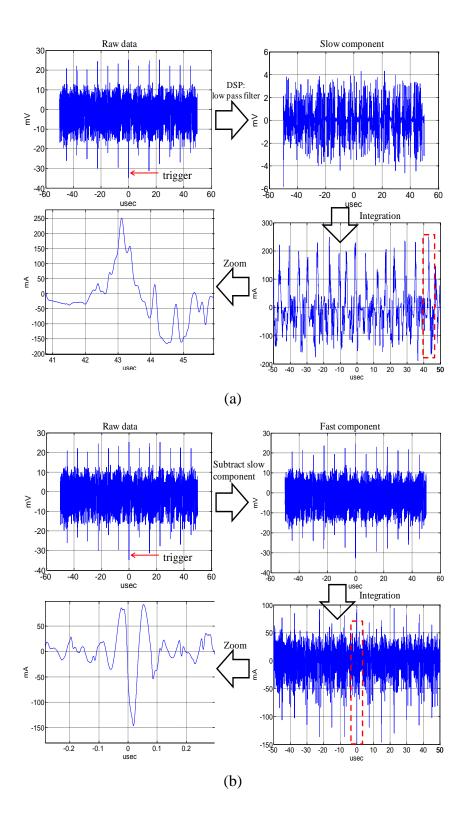

| Figure 3.4  | The proposed post data-processing procedure                                                                                                                                  | 2          |

| Figure 3.5  | Post data processing to obtain the highest peak for current components with slow (a) and fast (b) transient time                                                             | '3         |

| Figure 3.6  | Averaged current waveforms for (a) slower and (b) faster current components when the bulk capacitor value is $10~\mu F$                                                      | '4         |

| Paper III   |                                                                                                                                                                              |            |

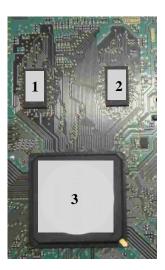

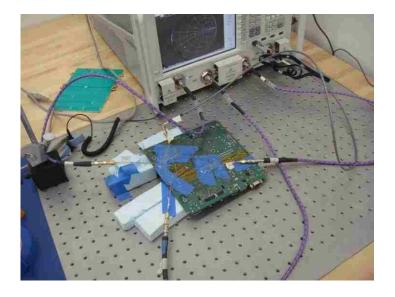

| Figure 2.1  | A picture of the functioning board under study: three ICs sharing a common power island structure                                                                            | 80         |

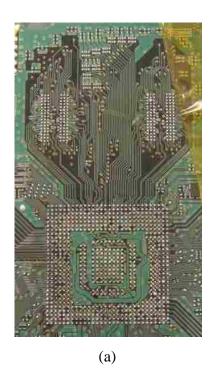

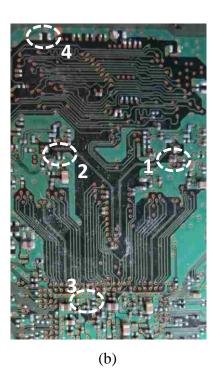

| Figure 2.2  | Same board with (a) three ICs removed (top layer) and (b) port locations (bottom layer)                                                                                      | 31         |

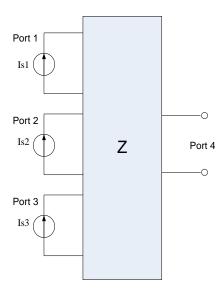

| Figure 2.3  | A simple four-port network describing the behaviour of the power island 8                                                                                                    | 2          |

| Figure 2.4  | Setup of multiport S-parameter measurement                                                                                                                                   | 2          |

| Figure 2.5  | Setup of oscilloscope measurement                                                                                                                                            | 4          |

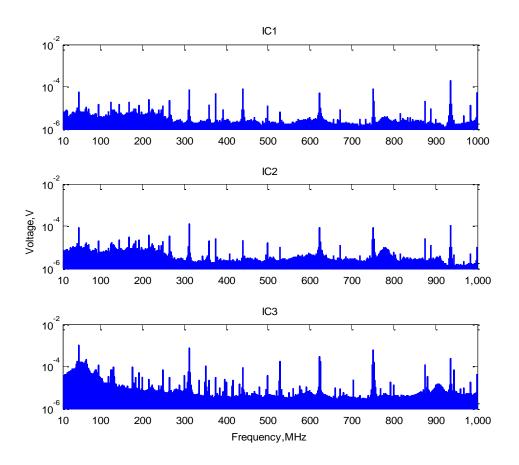

| Figure 3.1  | Magnitude spectra of the noise voltages at the IC ports (Ports 1-3) in the frequency range of 10 MHz to 1 GHz: without the 10 $\mu$ F decoupling capacitor placed at Port 4. | 35         |

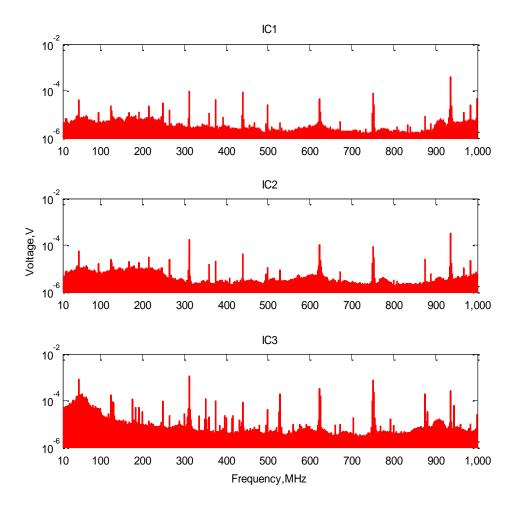

| Figure 3.2  | Magnitude spectra of the noise voltages at the IC ports (Ports 1-3) in the frequency range of 10 MHz to 1 GHz: with the 10 µF decoupling capacitor placed at Port 4          | 36         |

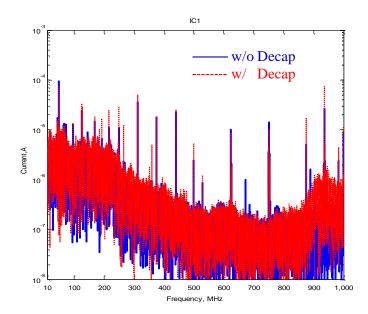

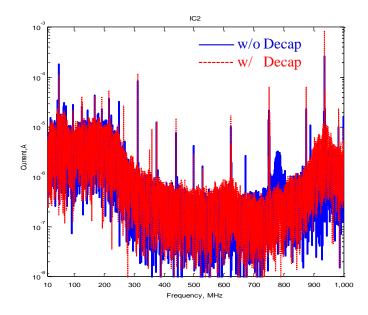

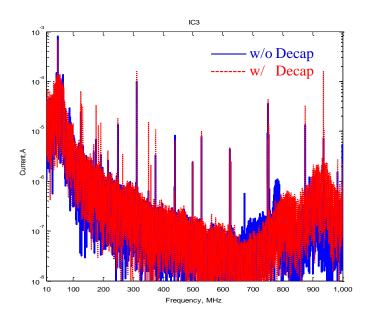

| Figure 3.3 | Magnitudes of the calculated equivalent switching current drawn by IC 1 for both cases of with and without the decoupling capacitor at Port 4 | . 87 |

|------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 3.4 | Magnitudes of the calculated equivalent switching current drawn by IC 2 for both cases of with and without the decoupling capacitor at Port 4 | . 88 |

| Figure 3.5 | Magnitudes of the calculated equivalent switching current drawn by IC 3 for both cases of with and without the decoupling capacitor at Port 4 | . 88 |

| Figure 3.6 | Magnitude comparison between the calculated and the measured noise voltages at Port 4, without the decoupling capacitor placed at Port 4      | . 90 |

| Figure 3.7 | Magnitude comparison between the calculated and the measured noise voltages at Port 4, with the decoupling capacitor placed at Port 4         | . 90 |

# LIST OF TABLES

|            | Pag                                                                           | ge             |

|------------|-------------------------------------------------------------------------------|----------------|

| Paper I    |                                                                               |                |

| Table 2.1  | Minimum section distance to satisfy 3 % <i>err</i> , plane spacing = 0.5 mm 2 | 21             |

| Table 3.1  | Branch number and corresponding nodes at the ends                             | 24             |

| Table 3.2  | Branch voltage                                                                | 24             |

| Table 3.3  | Node current                                                                  | 25             |

| Table 3.4  | Bookkeeping of the nodes                                                      | 28             |

| Table 3.5  | Compute time with different plane sizes                                       | 30             |

| Table 3.6  | Calculation results with different methods                                    | 33             |

| Table 3.7  | Plane pair inductance with 10 shorts                                          | 35             |

| Table 3.8  | Multiple shorts                                                               | 36             |

| Table 3.9  | Weighted KCL matrix                                                           | <del>1</del> 0 |

| Table 3.10 | Inductance calculated using uniform mesh and sub-mesh methods                 | 12             |

| Table 3.11 | Plane net inductances from the hybrid, PEEC solver and PPP methods            | 16             |

| Table 3.12 | Comparison between sub- and uniform mesh methods                              | 51             |

| Table 3.13 | Partial inductance of the source via, pH, $d = 0.2$ mm, $l = 1.5$ mm          | 54             |

| Table 3.14 | Comparison of partial inductance of via and total inductance                  | 55             |

| Table 3.15 | Code performance for large geometry                                           | 58             |

#### 1. INTRODUCTION

A power distribution network (PDN) is used to deliver power to the core logic and input / output (I / O) circuits on multilayer printed circuit boards (PCBs). Nowadays, the internal clock frequency of modern electronic devices has been more than several GHz, and the switching current is up to tens of amperes. With silicon technology going to nanometer feature dimension, the increasing number of I/Os in simultaneous transmission demand significant amount of transient current in PDN. With faster switching speed, higher circuit density, lower supply voltages and smaller feature size in integrated circuits (ICs) design, the voltage noise become a serious issue, affecting power and signal integrity (PI & SI) as well as causing electromagnetic interference (EMI) problems in high – speed electronic devices.

It is well known that the power / ground (PWR / GND) noise should be sufficiently suppressed, such as simultaneous switching noise (SSN) which is one of the main sources for many SI, PI and EMI issues. Decoupling capacitors in PWR and GND planes are widely used to stabilize the supply voltage levels in multilayer packages and PCB structures by supplying the charge needed for the switching current. However, the parasitic inductances due to the current loop in the power delivery and return path impede the current supplied to the chip, limiting the effectiveness of the decoupling capacitors to rapidly provide charge. Therefore, quantifying the parasitic inductance of PWR and GND planes is critical for problems associated with PDN design. Full-wave simulation methods have been used to model the PWR / GND layer pair to determine the impedance of the PDN, including the parasitic inductance. However, the full-wave methods may require long compute time and huge memory resources. An efficient approach based on partial element equivalent circuit (PEEC) is proposed for fast impedance calculation of parallel planes.

To evaluate the performance of a PDN, target impedance is a widely used guideline for PDN design. It is a reverse problem of PDN noise analysis to establish the target impedance specification for PDN design. In PDN noise analysis, the maximum noise voltage induced by IC switching currents can be simulated or calculated using an appropriate PDN model and switching currents. Conversely, target impedance for PDN design is obtained from the knowledge of switching currents and the maximum PDN

noise tolerance. Therefore, the waveform of IC switching currents in time domain is necessary to develop the target impedance. In some real-world hardware measurements, it is found that multiple current components could exist in the time-varying current flowing through a decoupling capacitor. Further, when the current through a bulk decoupling capacitor is of interest, it needs to be measured at the frequencies as low as a few hundred KHz. A lab-made low-cost current probe is developed with very small in size, suitable for dense-PCB applications and sensitive enough for low-frequency measurements. A post data-processing procedure is developed to separate the effects of different current components, and to obtain the parameters important for target impedance.

In some PDN designs, there are multiple ICs sharing a common power island structure. When detailed IC information is available, chip-level modeling is an effective way to obtain the switching current information. However, IC information is proprietary and usually unavailable for most PCB designers. A measurement-based method is developed to handle the situation where multiple ICs share a common power island and IC information is not available. The measured time-domain noise-voltage waveforms are converted into the frequency domain through the Fourier transform. Together with the S-parameter measurement of the multi-port power-island structure, equivalent switching currents including both magnitude and phase are obtained, which is important for optimized PDN design (such as target impedance).

#### **PAPER**

# I ACCURATE AND EFFICIENT COMPUTATION OF POWER PLANE PAIR INDUCTANCE

Liang Li, Albert E. Ruehli, Jun Fan

Missouri University of Science and Technology, Rolla, MO, 65401, USA <a href="mailto:llh9b@mst.edu">llh9b@mst.edu</a>, albert.ruehli@gmail.com, jfan@mst.edu

#### **ABSTRACT**

Computation of power-plane inductance for multiple ports is an important part of power distribution network (PDN) design. In this paper, we present an efficient approach for the inductance computation. Since this PEEC approach is based on partial inductance computations, vias and other discontinuities can be accurately taken into account. Speed-up techniques are employed like the faster decay of mutual coupling due to the "differential" currents (same magnitude but opposite directions) in the two planes. Also, an approximate rectangular mesh reduction method is introduced which allows a local increase in mesh density.

#### 1. INTRODUCTION

The internal clock frequency and input-output (IO) speed in modern high speed digital devices increase dramatically, and the current density becomes higher, which results in increased current demand from the PDN of the board. When numerous logic gates and buffers inside integrated circuits (ICs) switch simultaneously, they induce significant voltage drops or ripples in the PDN, resulting in critical power integrity issues and electromagnetic (EM) interference problems [1]. The power noise in the supply voltage can further couple to the signal traces transitioning through the power and reference (often denoted as "ground") planes and result in signal integrity problems [2]. On-chip and off-chip decoupling capacitors are used to provide the needed charge for the switching current. Within the frequency range from megahertz to hundreds of megahertz, the off-chip decoupling capacitors in the power and ground planes are widely used to make the supply voltage stable in the printed circuit board (PCB) by achieving low power supply impedance [3]. However, the parasitic inductances due to the current loop in the power delivery and return path impede the current supplied to the chip, limiting the effectiveness of the decoupling capacitors to rapidly provide charge. Therefore, quantifying the parasitic inductance of the power and ground planes is critical for the problems associated with PDN design.

Many techniques are available today to determine the PDN impedance, including the parasitic inductance between power and ground planes. Full-wave electromagnetic modeling methods have been widely used to model the power/ground layer pair problem, such as finite-difference time domain (FDTD) [4], the finite-element method (FEM) [5] and the method of moments (MOM) [6]. However, full-wave methods require significant computing time and resources for complicated hierarchical PDN structures. Other approaches such as transmission-line methods [7] and the resonant cavity model [8] are usually much faster than full-wave numerical methods and can be easily included into circuit simulations, but the accurate computation of the inductances for power/ground plane pair with multiple decoupling capacitor placements can still be very time consuming.

In this paper, an efficient Plane Pair PEEC (PPP) approach is proposed. The decoupling capacitors can be modeled by single-lumped inductance macromodels assuming that the capacitive impedance is small at the frequencies of interest. The portions of the inductances associated with the parallel planes are calculated using the proposed PPP approach, and the remaining portions associated with the package of the capacitors, bonding pads and vias can be easily added with very little extra computation time.

In the PPP approach, the inductive coupling between different cells decays very fast, which is used to obtain a sparsification of the partial mutual inductance evaluation. Speed-up techniques are employed to save the computational time and memory usage. Both uniform and non-uniform mesh methods were investigated and validated. Our model is flexible to choose ports and change decoupling capacitor locations. Change of the plane pair inductance due to the change of decoupling capacitor locations can be easily calculated which provides useful guidelines for PDN designs.

#### 2. THEORY AND FORMULATION

#### 2.1. CONCEPTS OF PARTIAL INDUCTANCE

The definition of the inductance for a system of *N* loops is given as,

$$L_{ij} = \frac{\psi_{ij}}{I_i} \text{ for } I_k = 0 \text{ if } k \neq j$$

(1)

where  $\psi_{ij}$  is the magnetic flux in loop i due to the current  $I_j$  in loop j. The magnetic vector potential  $\vec{A}$  at any observation point  $\vec{r}$  generated by the current  $I_j$  is [9],

$$\vec{A} = \frac{\mu}{4\pi} \frac{I_j}{a_i} \oint_j \int_{a_j} d\vec{l_j} da_j \tag{2}$$

where  $r = |\vec{r} - \vec{r_j}|$ ,  $d\vec{l_j}$  is the element of conductor j with the direction along the axis of the conductor and  $a_j$  is the conductor cross section perpendicular to the current flow. A uniform current density is assumed in conductor j with a constant cross section  $a_j$  along the loop. The average magnetic flux  $\psi_{ij}$  in loop i can be related to the vector potential  $\overline{A_j}$  as,

$$\psi_{ij} = \frac{1}{a_i} \oint_i \int_{a_i} \overline{A_j} \cdot d\vec{l_i} da_i \tag{3}$$

where  $a_i$  represents the constant cross section of conductor i. The mutual inductance for the loops i and j can be expressed as [9].

$$L_{ij} = \frac{1}{a_i a_j} \frac{\mu}{4\pi} \oint_i \int_{a_i} \oint_j \int_{a_j} \frac{d\vec{l_i} \cdot d\vec{l_j}}{r_{ij}} da_i da_j$$

(4)

Relations for the inductance between the parts of circuits can be further developed from Eq. (4). The integrations over the lengths can be expressed as summations over the straight loop segments and all segments are allowed to have a different cross section as show in Eq. (5) [9],

$$L_{ij} = \sum_{k=1}^{K} \sum_{m=1}^{M} \frac{\mu}{4\pi} \frac{1}{a_k a_m} \int_{a_k} \int_{a_m} \int_{b_k}^{c_k} \int_{b_m}^{c_m} \frac{d\vec{l}_k \cdot d\vec{l}_m}{r_{km}} da_k da_m$$

(5)

where the *i*th loop is divided into K segments while *j*th loop is consist of M segments. The starting points  $b_k$ ,  $b_m$  and the ending points  $c_k$ ,  $c_m$  are the limits in the integrals.

Partial inductance is defined as the argument of the double summation in Eq. (6) for the conductor segments as [9],

$$Lp_{km} = \frac{\mu}{4\pi} \frac{1}{a_k a_m} \int_{a_k} \int_{a_m} \int_{b_k}^{c_k} \int_{b_m}^{c_m} \frac{|d\vec{l_k} \cdot d\vec{l_m}|}{r_{km}} da_k da_m.$$

(6)

The sign of  $Lp_{km}$  is accounted for by a factor  $S_{km}$  as Eq. (7),

$$Lp_{ij} = \sum_{k=1}^{K} \sum_{m=1}^{M} S_{km} Lp_{km} . (7)$$

$S_{km}$  represents the sign (±1) associated with the particular partial inductance, which is positive by definition.  $S_{km}$  depends on the direction of current flow in the conductors.

Partial self-inductance is evaluated from the definition of partial inductance in Eq. (6), where integration i and integration j are both over the same conductor,

$$Lp_{ii} = \frac{\mu}{4\pi} \frac{1}{a_i a_{i'}} \int_{a_i} \int_{a_{i'}} \int_0^l \int_0^{l'} \left| d\vec{l}_i \cdot d\vec{l}_{i'} \right| da_i da_{i'}.$$

(8)

#### 2.2. PEEC METHOD

The Partial Element Equivalent Circuit (PEEC) was developed by A. Ruehli in the 1970s and 1980s [10]. The PEEC method is used for numerical modeling of electromagnetic (EM) problems. It models electric-field interactions as capacitances and magnetic-field interactions as inductances. Using the PEEC method, problem under study is transferred from the EM domain to the circuit domain where the conventional SPICE-like circuit solvers can be employed to analyze the equivalent circuit. By applying the PEEC method, all electrical components e.g. passive components, sources, non-linear elements, ground, etc. can be easily integrated together. Moreover, by using the PEEC method it is easy to separate the resistive, capacitive or inductive effects.

To apply the PEEC method, all of the conductors in the problem must first be subdivided into N canonical primitive structures, such as rectangular bars, for which formulas for resistance, partial self-inductances, and partial mutual-inductances are known. For example, Figure 2.1 shows an interconnect with two signal traces and a plane return path. The conductors are subdivided to rectangular bars. The small, generically shaped conductors in Figure 2.1 are called branches. The resistances and inductances are then assembled into a complete circuit and solved with a circuit simulator. The accuracy improves with finer-grained subdivision of the original geometry [11].

Figure 2.1. Division of conductors into segments.

Assume the current is uniform across the cross section of the branches. Then relatively simple DC resistance and static inductance formulas are applicable. The resistance and partial self-inductance of each branch is computed along with the partial

mutual-inductance between each pair of branches. Assemble the results into a diagonal  $N \times N$  resistance matrix and an  $N \times N$  partial inductance matrix. The voltage drops across the branches are,

$$\overline{V}_b = (R + j\omega L)\overline{I}_b = \overline{Z}_p\overline{I}_b \tag{9}$$

where  $\overline{I}_b$  are the branch currents.

### 2.3. MODIFIED NODAL ANALYSIS (MNA)

The branches are connected together at a number of nodes. The number of the nodes, *M*, depends on the subdivision used. By satisfying Kirchhoff's voltage (KVL) and current laws (KCL), a dedicated solver for the PEEC method can be constructed.

Each branch voltage is defined by the difference of the two node voltages at the ends of the branch. It can be shown,

$$\overline{V}_b = \overline{AV}_n \tag{10}$$

where  $\overline{A}$  is the incident matrix, and stores all of the connection information in an  $N \times M$  matrix, where N is the number of the branches.  $\overline{A}$  is constructed by setting  $A_{bi} = 1$  and  $A_{bj} = -1$  when the current flows from node i to node j through branch b.

The total currents into the nodes are given by,

$$\bar{I}_n = \bar{A} \bar{I}_b \tag{11}$$

where  $\overline{I}_n$  are the currents driven into the nodes by external sources, and  $\overline{I}_b$  are the branch currents. In general, most of the  $\overline{I}_n$  are zero since current is externally supplied only at the ports.

The Modified Nodal Analysis (MNA) is easy to implement algorithmically on a computer which is a substantial advantage for automated solution. There are two main aspects to be considered when choosing algorithms: accuracy and speed. The MNA has been proved to accomplish these.

The MNA applied to a circuit with passive elements, independent current and voltage sources and active elements results in a matrix equation of the form,

$$[A][x] = [z] \tag{12}$$

For a circuit with M nodes and N independent voltage sources (branches), the A matrix is  $(N+M) \times (N+M)$  in size, and consists only of known quantities. The A matrix is developed as the combination of 4 smaller matrices, B, C, D and G,

$$A = \begin{bmatrix} B & D \\ C & G \end{bmatrix} \tag{13}$$

The B matrix is  $N \times N$  in size and is zero if only independent sources are considered. The C matrix is  $N \times M$  in size with only 0, 1 and -1 elements and is determined by the connection of the voltage sources (branches). The D matrix is  $M \times N$  in size and is equal to the transposed C matrix. The G matrix is  $M \times M$  in size and is determined by the interconnections between the circuit elements.

The x vector is  $(N + M) \times 1$  in size, which holds the unknown quantities and is developed as the combination of two smaller vectors, v and i,

$$x = \begin{bmatrix} v \\ i \end{bmatrix} \tag{14}$$

The v vector is  $M \times 1$  in size and holds the unknown voltages. The i vector is  $N \times 1$  in size and holds the unknown currents through the voltage sources (branches).

The z vector is also  $(N + M) \times 1$  in size, which is developed as the combination of two smaller vectors p and q,

$$z = \begin{bmatrix} p \\ q \end{bmatrix} \tag{15}$$

The p vector is  $M \times 1$  in size with each element of the vector corresponding to a particular node. The value of each element of p is determined by the sum of current sources into the corresponding node. If there are no current sources connected to the node, the value is zero. The q vector is  $N \times 1$  in size with each element of the vector equal to the corresponding independent voltage source. If there is no independent voltage source, the value is zero.

#### 2.4. THE PPP APPROACH

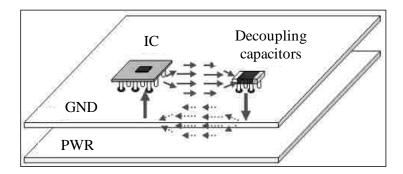

In the power distribution network of a multilayer printed circuit board, the inductance formed by two parallel planes and IC/decoupling capacitor vias (Figure 2.2) can be separated into two parts: the vertical via barrel inductance and plane pair inductance due to the changes of the horizontal plane current distribution adjacent to the vias (Figure 2.3).

Figure 2.2. Power/Ground plane pair with IC and decoupling capacitors.

Figure 2.3. Current distribution on power and ground planes.

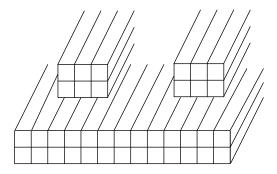

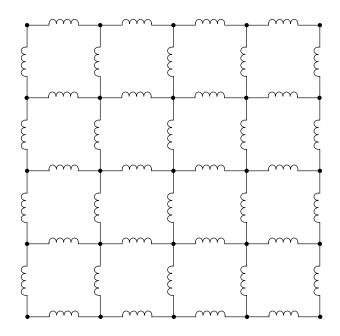

The power and ground planes are subdivided into commensurate cells using conventional PEEC meshing method [12] as shown in Figure 2.4. Non-orthogonal cells are avoided with rectangular mesh size, which makes coupling terms minimal. For example, Figure 2.4 shows a  $4 \times 4$  plane subdivided into 16 squares with  $1 \times 1$  size. The currents flowing on the plane are divided into the x and y directions. Thus, the plane is also subdivided into cells in the x and y directions, respectively. The width of the cells on the edges is half of the cells inside so that by connecting the nodes in Figure 2.4, the equivalent circuit using partial inductances can be created as shown in Figure 2.5. This allows the subdivided plane sections to be connected in a systematic way. The same subdivisions are applied for both power and ground planes to make them symmetric.

Figure 2.4. Plane subdivision

Figure 2.5. Partial inductance evaluation.

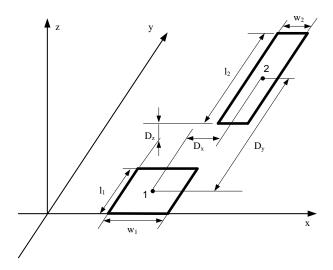

The closed-form formulation for mutual inductance between two parallel thin conductors as shown in Figure 2.6 is given in Eq. (16), which is called the thin tape – tape (TT) algorithm [9].

Figure 2.6. Two parallel thin conductors

$$L_{p12} = \frac{\mu}{4\pi} \frac{1}{w_1 w_2} \sum_{i=1}^{4} \sum_{j=1}^{4} (-1)^{i+j} \left[ \frac{b_j^2 - D_z^2}{2} a_i \ln(a_i + \rho) + \frac{a_i^2 - D_z^2}{2} b_j \ln(b_j + \rho) \right]$$

$$- \frac{1}{6} (b_j^2 - 2D_z^2 + a_i^2) \rho - b_j D_z a_i \tan^{-1} \frac{a_i b_j}{\rho D_z}$$

$$\rho = (a_i^2 + b_j^2 + D_z^2)^{\frac{1}{2}}$$

$$a_1 = D_x - \frac{l_1}{2} - \frac{l_2}{2}, \ a_2 = D_x + \frac{l_1}{2} - \frac{l_2}{2}$$

$$a_3 = D_x + \frac{l_1}{2} + \frac{l_2}{2}, \ a_4 = D_x - \frac{l_1}{2} + \frac{l_2}{2}$$

$$b_1 = D_y - \frac{w_1}{2} - \frac{w_2}{2}, \ b_2 = D_y + \frac{w_1}{2} - \frac{w_2}{2}$$

$$b_3 = D_y + \frac{w_1}{2} + \frac{w_2}{2}, \ b_4 = D_y - \frac{w_1}{2} + \frac{w_2}{2}$$

$$(16)$$

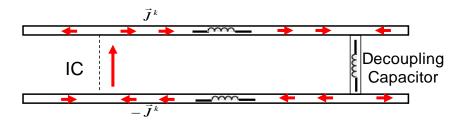

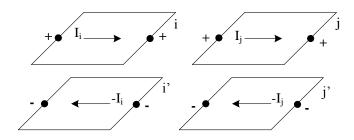

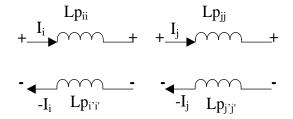

For power/ground plane pair with opposing currents, two cells located on the top and bottom planes with the same x and y coordinates can be united to a cell pair called "section" [12] as shown in Figure 2.7. Due to the cancelling effect of the opposing currents in a cell pair (Figure 2.8), the inductive coupling between sections decays much faster with increasing distance [13].

Figure 2.7. *i-th* and *j-th* section

Figure 2.8. The corresponding equivalent circuit of *i-th* and *j-th* section

It has been shown that the mutual inductance between the i-th section and j-th section,  $Ls_{ij}$  can be expressed with the partial-mutual inductances of the cells, in which symmetry of the cells is applied to reduce by a factor of two in the number of the partial inductance evaluations [12]. Briefly, the voltage drop in the i-th section caused by the current in the j-th section can be expressed as,

$$Vs_{i} = sI_{j}(Lp_{ij} - Lp_{ij'} + Lp_{i'j'} - Lp_{i'j})$$

(17)

Because of the symmetry of the cells, we have  $Lp_{ij} = Lp_{i'j'}$  and  $Lp_{ij'} = Lp_{i'j}$ . The partial-mutual inductance between the *i-th* section and the *j-th* section can be expressed as,

$$Ls_{ij} = \frac{Vs_{i}}{sI_{j}} = 2(Lp_{ij} - Lp_{ij'})$$

(18)

Similarly, the partial-self inductance of the *i-th* section can be expressed as,

$$Ls_{ii} = 2(Lp_{ii} - Lp_{ii}) (19)$$

The orthogonal cells are used in the PPP approach, which reduces the coupling a lot since only the coupling in the x direction or the y direction will be calculated. Non-orthogonal mesh can result in the mutual coupling between the x and y directed cells which is costly in computation.

A special case for the inductance of thin filamentary circuits i and j is given by the Neumann formula [9],

$$Lp_{ij} = \frac{\mu}{4\pi} \int_{i} \int_{j} \frac{d\vec{l}_{i} \cdot d\vec{l}_{j}}{r_{ij}}.$$

(20)

When the distance between two cells,  $r_{ij}$  is sufficiently large, the partial-mutual inductance between two cells can be approximated as,

$$Lp_{ij} = \frac{\mu}{4\pi} \frac{l_i l_j}{r_{ij}} \tag{21}$$

Define  $q = h/r_{ij}$ , where h is the plane to plane spacing, and  $r_{ij}$  is the distance between two sections. When the distance  $r_{ij}$  between two sections >> the size of the sections, the partial-mutual inductance between the sections shown in Figure 2.7 can be approximated as,

$$Ls_{ij} = 2(Lp_{ij} - Lp_{ij'}) = 0.2\Delta x \Delta x (1/r_{ij} - 1/r_{ij'}), \ \mu H$$

(22)

where  $r_{ij} = \sqrt{r_{ij}^2 + h^2} = r_{ij}\sqrt{1 + q^2}$ . The square root can be expanded in a Taylor series as,

$$\frac{1}{\sqrt{1+q^2}} = 1 - \frac{q^2}{2} + \frac{q^4}{8} - \dots$$

(23)

When  $q \ll 1$ ,  $\frac{1}{\sqrt{1+q^2}} \cong 1 - \frac{q^2}{2}$ . Eq. (22) can be expressed as,

$$Ls_{ij} = 0.1\Delta x \Delta x q^2 / r_{ij}, \ \mu H \tag{24}$$

where  $r_{ij} = \sqrt{(i\Delta x)^2 + (j\Delta y)^2}$  (Figure 2.4). For uniform mesh subdivision, the cell is square with  $\Delta x = \Delta y$ , and Eq. (24) can be written as Eq. (25). Thus, the coupling between sections decays very fast, which is proportional to  $(1/r_{ij})^2$ .

$$Ls_{ij} = 0.1\Delta x q^2 / \sqrt{i^2 + j^2}, \ \mu H$$

(25)

Applying the approximation formula can speed up calculation of the mutual inductance coupling between sections, which is related to the section length, distance between sections and the plane pair spacing only. The relative error of the mutual inductance between sections obtained by the original closed-form expression and the approximation formula is given by Eq. (26).

$$err = \frac{|Ls_{ij} - Ls_{ij(apprx)}|}{Ls_{ij}} \times 100\%$$

(26)

To find out the criteria for the application of the approximation formula, the defined error was set as 3% to achieve enough accuracy. Different plane pair spacing was applied. Here we show an example of  $0.5 \, \mathrm{mm} \times 0.5 \, \mathrm{mm}$  cell size and  $0.2 \, \mathrm{mm}$  plane spacing. The partial-mutual inductance between two sections with various distances is calculated using the closed-form expression and the approximation formula, and the results are shown in Figure 2.9. The relative error calculated by Eq. (26) is shown in Figure 2.10.

Figure 2.9. Partial-mutual inductance between two sections calculated by the closed-form formula and the approximated method.

Figure 2.10. Relative error between the closed-form formula and approximation.

The relative – error criteria is set as 3 %. It can be seen that when the section distance is larger than 2.5mm, which is 5 times of the cell size, the relative error is already less than 3 %.

Normalize the partial-mutual inductance between two sections to the partial-self inductance of the section,  $Ls_{ij}/Ls_{ii}$  as shown in Figure 2.11. It is obviously that the partial-mutual inductance decays very fast. When the distance between two sections is 5mm, which is 10 times of the cell size, the coupling is already less than  $10^{-4}$  of the partial-self inductance. Therefore, the coupling can be approximated as zero when the distance between two sections is large enough.

Figure 2.11. Normalized to partial-self inductance.

Vary the plane pair spacing from 0.1mm to 2mm. For each spacing value, the section length was changed from 0.1mm to 2mm, and the minimum section distance at which the relative error is no more than 3% was recorded as shown in Figure 2.12. The minimum section distance to satisfy the relative – error criteria requirement can be related to either section size or plane spacing, whichever is larger, by multiplying a factor.

Here we use the section with 0.5mm plane pair spacing as an example. Table 2.1 shows the section size, and the corresponding minimum section distance at which the relative error is less than 3 %. If section size is smaller than the plane spacing, the minimum section distance is roughly 5 times of the plane spacing. If section size is larger than the plane spacing, similar relationship can be found between the minimum section distance and section size. When section size is equal to the plane spacing, the minimum section distance is only 2 times of section size or the plane spacing. However, we can still set the minimum section distance equal to 5 times of section size or plane spacing. We will show that this estimated relationship gives high enough accuracy later.

Table 2.1 Minimum section distance to satisfy 3 % err, plane spacing = 0.5 mm

| Section Size, mm | Minimum Section Distance, mm |

|------------------|------------------------------|

| 0.1              | 2.8                          |

| 0.2              | 2.6                          |

| 0.25             | 2.5                          |

| 0.5              | 1                            |

| 1                | 5                            |

| 2                | 12                           |

| 5                | 30                           |

It has been found that if the distance between sections is less than 5 times of the larger value of section length and plane spacing, called ds, the relative error is higher than 3 % and the closed-form expression needs to be applied to calculate the mutual inductance between two sections. If the distance between sections is larger than ds, the approximation formula can be applied with the relative error less than 3 %. If the distance between sections is larger than 2ds, the mutual inductance can be estimated as zero. Figure 2.13 shows the schematic of how to determine the calculation formulation for the mutual coupling. Applying the approximation criteria can speed up computations [12], which will be shown in an example later, and make the partial inductance matrix sparse due to the zero terms.

Figure 2.12. Criteria to apply the approximation formula

Figure 2.13. Schematic of criteria determination when err = 3%.

#### 3. UNIFORM AND NON-UNIFORM MESH

## 3.1. ASSEMBLY OF MNA

By stamping in the appropriate contribution circuit element in a conventional Modified Nodal Analysis (MNA) method, the circuit matrix can be set up to model the plane pair [12]. Briefly, the MNA matrix is composed by KVL, KCL and partial inductance matrices. By solving the matrix, the voltage at each node and the current in each branch can be obtained. Thus, all desired inductances like the inductance of the plane pair can be calculated.

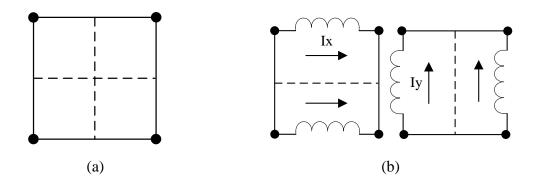

Figure 3.1 shows an example with the smallest structure. Subdividing the example with the conventional PEEC mesh (Figure 3.1 (a)), the corresponding partial inductance evaluation in x and y direction is shown in Figure 3.1 (b). Since the geometry shown here is subdivided with the least amount of mesh, the cells in both x and y directions are cells on the edge. It is worth to note that the currents we are talking here, x and y are differential currents as shown in Figure 2.8.

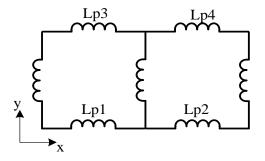

Figure 3.1. Example with the smallest structure. (a) Mesh in x and y direction. (b) Partial inductance in x and y direction.

The corresponding equivalent circuit for the example in Figure 3.1 is shown in Figure 3.2. Node 1 is defined as the current source with the current, *Is* injected into. Node 4 is defined as the short connected to ground, which is the datum node with the voltage of zero. The branch number and corresponding nodes at two ends are listed in Table 3.1.

Figure 3.2. Equivalent circuit of the example with the smallest structure.

Table 3.1 Branch number and corresponding nodes at the ends

| Branch No. | Beginning Node | End Node |

|------------|----------------|----------|

| 1          | 1              | 2        |

| 2          | 3              | 4        |

| 3          | 1              | 3        |

| 4          | 2              | 4        |

Table 3.2 Branch voltage

| Branch Voltage |          | Node Voltage |          |          |  |  |

|----------------|----------|--------------|----------|----------|--|--|

| Branen voltage | $V_{N1}$ | $V_{N2}$     | $V_{N3}$ | $V_{N4}$ |  |  |

| $V_1$          | 1        | -1           | 0        | 0        |  |  |

| $V_2$          | 0        | 0            | 1        | -1       |  |  |

| $V_3$          | 1        | 0            | -1       | 0        |  |  |

| $V_4$          | 0        | 1            | 0        | -1       |  |  |

According to Eq. (10), the voltage drop on the branch is determined by the voltage of the nodes at the ends as shown in Table 3.2. The incident matrix of voltage,  $\overline{V}$  can be expressed as,

$$\frac{=}{V} = \begin{bmatrix} 1 & -1 & 0 & 0 \\ 0 & 0 & 1 & -1 \\ 1 & 0 & -1 & 0 \\ 0 & 1 & 0 & -1 \end{bmatrix}$$

(27)

Table 3.3 Node current

|        | Branch Current  |                 |        |                 |  |

|--------|-----------------|-----------------|--------|-----------------|--|

|        | Ix <sub>1</sub> | Ix <sub>2</sub> | $Iy_1$ | Iy <sub>2</sub> |  |

| Node 1 | 1               | 0               | 1      | 0               |  |

| Node 2 | -1              | 0               | 0      | 1               |  |

| Node 3 | 0               | 1               | -1     | 0               |  |

| Node 4 | 0               | -1              | 0      | -1              |  |

The current flowing through each node is calculated by KCL as shown in Table 3.3. Define the current flowing out of the node as "+" and the current flowing into the node as "-". The incident matrix of current is,

$$\vec{I} = \begin{bmatrix}

1 & 0 & 1 & 0 \\

-1 & 0 & 0 & 1 \\

0 & 1 & -1 & 0 \\

0 & -1 & 0 & -1

\end{bmatrix}.$$

(28)

Same as Eq. (11), we have  $\overline{I} = \overline{V}^T$ . The source current injected into node 1 and the short current at node 4 are not included in  $\overline{I}$ , and they will be included in the final assembled MNA matrix.

Since the cell is orthogonal, the coupling is only in x or y direction. The partial inductance matrix,  $\overset{=}{L}$  is expressed as,

$$\frac{1}{L} = \begin{bmatrix}

Lpx_{11} & Lpx_{12} & 0 & 0 \\

Lpx_{21} & Lpx_{22} & 0 & 0 \\

0 & 0 & Lpy_{33} & Lpy_{34} \\

0 & 0 & Lpy_{43} & Lpy_{44}

\end{bmatrix}$$

(29)

Assemble  $\overline{V}$ ,  $\overline{I}$  and  $\overline{L}$  with an all-zero  $4 \times 4$  matrix to form A matrix as shown in Eq. (12). The circuit equation for the smallest structure is shown in Eq. (30). A column and a row are added into A matrix as the last column and row, which are used for the stamping of short current and voltage, respectively. Is in the right-hand-side of Eq. (30) represents the source current injected into node 1. By solving Eq. (30), the voltage of each node and the current on each branch can be obtained. Therefore, the impedance of the smallest structure is give by  $L_{11} = V_{N1} / sIs$ . All other inductance like  $L_{21}$ ,  $L_{31}$  can also be calculated.

$$\begin{bmatrix} 0 & 0 & 0 & 0 & 1 & 0 & 1 & 0 & 0 \\ 0 & 0 & 0 & 0 & -1 & 0 & 0 & 1 & 0 \\ 0 & 0 & 0 & 0 & 0 & 1 & -1 & 0 & 0 \\ 0 & 0 & 0 & 0 & 0 & 0 & -1 & 0 & -1 & 1 \\ 1 & -1 & 0 & 0 & Lpx_{11} & Lpx_{12} & 0 & 0 & 0 \\ 0 & 0 & 1 & -1 & Lpx_{21} & Lpx_{22} & 0 & 0 & 0 \\ 1 & 0 & -1 & 0 & 0 & Lpy_{33} & Lpy_{34} & 0 \\ 1 & 0 & -1 & 0 & 0 & Lpy_{43} & Lpy_{44} & 0 \\ 0 & 0 & 0 & 1 & 0 & 0 & 0 \end{bmatrix} \begin{bmatrix} V_{N1} \\ V_{N2} \\ V_{N3} \\ SIx_1 \\ SIx_2 \\ SIy_1 \\ SIy_2 \\ SI_{sh} \end{bmatrix} = \begin{bmatrix} SIS \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \\ 0 \end{bmatrix}$$

$$(30)$$

It is important that for much larger and more realistic geometry, the structure of the MNA matrix is similar as that in Eq. (30). The source current can be injected into any node(s) we want to calculate the inductance at, and the short(s) can be placed at any node(s) where the capacitors are located.

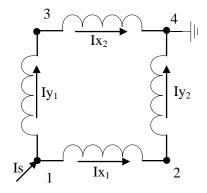

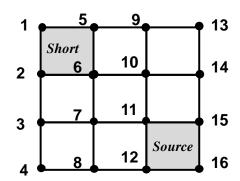

#### 3.2. BOOKKEEPING OF NODES

In the previous work, the port was represented with a single node in the model [12]. Here, we included the port dimension into the model to make it more general for the real case. Firstly, subdivide the plane to commensurate cells as shown in Figure 2.4, and label each node with a global number. The nodes in the corresponding port region are treated as one node. Then use bookkeeping to assign a local number for each node. An example is shown in Figure 3.3. Nodes with the global number of 1,2,5 and 6 form the port of short, and nodes with the global number of 11,12,15 and 16 form the port of source. Assign the local number of 1 to the nodes on the port of short and the local number of 2 to the nodes on the port of source. Then assign a local number to other nodes in sequence to build the node system. Table 3.4 shows the global number and the local number of each node.

Figure 3.3. Bookkeeping of the nodes.

Table 3.4 Bookkeeping of the nodes

| Global Node No. | Local Node No. | Node Property |

|-----------------|----------------|---------------|

| 1               | 1              | short         |

| 2               | 1              | short         |

| 3               | 3              | -             |

| 4               | 4              | -             |

| 5               | 1              | short         |

| 6               | 1              | short         |

| 7               | 5              | -             |

| 8               | 6              | -             |

| 9               | 7              | -             |

| 10              | 8              | -             |

| 11              | 2              | source        |

| 12              | 2              | source        |

| 13              | 9              | -             |

| 14              | 10             | -             |

| 15              | 2              | source        |

| 16              | 2              | source        |

## 3.3. COMPUTATION SPEED-UP.

Although the approximated formulation is helpful to speed up computation, the model may still be time consuming since a huge number of partial-self and partial-mutual inductance need to be calculated if the plane size is large or the mesh is very dense. Due to the symmetry of the uniform mesh subdivision, we can only calculate the partial-self and partial-mutual inductance of one section, and the partial-self and partial-mutual inductance of other sections can be obtained directly from the results of the section we calculate. Figure 3.4 shows an example of the smallest circuit to calculate the partial-self and partial-mutual inductance in x direction.

Figure 3.4. Example for partial-self and partial-mutual inductance calculation.

The partial-self inductance of section 1,  $Lp_{11}$  and the partial-mutual inductance  $Lp_{12}$ ,  $Lp_{13}$  and  $Lpx_{14}$  can be calculated using the formulations in Eq. (16) and Eq. (25). It's noticed that for section 2, we have  $Lp_{21}=Lp_{12}$ ,  $Lp_{22}=Lp_{11}$ ,  $Lp_{23}=Lp_{14}$  and  $Lp_{24}=Lp_{13}$ . The partial-self and partial-mutual inductance of section 2 can be obtained from the results of section 1 by building a transfer matrix shown in Eq. (31). For more realistic case with many partial inductance components, the transfer matrix can be built with similar structure.

$$\begin{bmatrix} Lp_{21} \\ Lp_{22} \\ Lp_{23} \\ Lp_{24} \end{bmatrix} = \begin{bmatrix} Lp_{11} & Lp_{12} & Lp_{13} & Lp_{14} \end{bmatrix} \begin{bmatrix} 0 & 1 & 0 & 0 \\ 1 & 0 & 0 & 0 \\ 0 & 0 & 0 & 1 \\ 0 & 0 & 1 & 0 \end{bmatrix}$$

(31)

# 3.4. COMPUTE TIME ANALYSIS

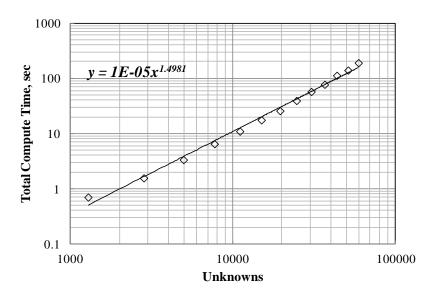

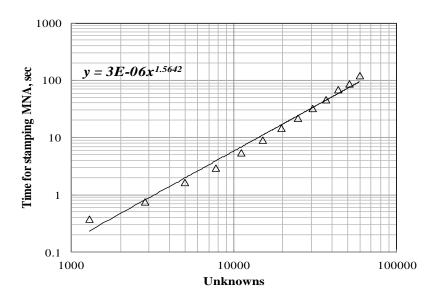

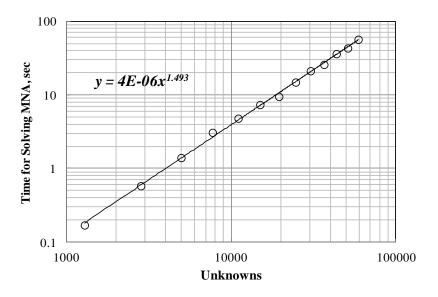

The total compute time to solve the MNA matrix is determined by the number of unknowns in Eq. (30), which are  $V_{Ni}$ ,  $Ix_i$  and  $Iy_i$ . To find the relationship between the number of unknowns and compute time, we can increase the problem size by keeping the same mesh size while increasing the geometry size. The plane size is changed from  $20\text{mm} \times 20\text{mm}$  to  $140\text{mm} \times 140\text{mm}$  with the plane spacing of 0.2mm while the mesh size is kept as  $1\text{mm} \times 1\text{mm}$ . The total compute time, time for stamping MNA matrix and time for solving MNA matrix are recorded and listed in Table 3.5. It is obviously that the total compute time is determined by the time for stamping and solving MNA matrix, and most time is spent on stamping MNA matrix.

Table 3.5 Compute time with different plane sizes

| Plane size,    |          | Total Time, | Stamp MNA, | Solve MNA, |

|----------------|----------|-------------|------------|------------|

| $mm \times mm$ | Unknowns | sec         | sec        | sec        |

| 20             | 1282     | 0.7         | 0.38       | 0.17       |

| 30             | 2822     | 1.56        | 0.76       | 0.58       |

| 40             | 4962     | 3.34        | 1.66       | 1.4        |

| 50             | 7702     | 6.48        | 2.96       | 3.08       |

| 60             | 11042    | 10.95       | 5.47       | 4.8        |

| 70             | 14982    | 17.53       | 9.11       | 7.36       |

| 80             | 19522    | 25.73       | 14.68      | 9.48       |

| 90             | 24662    | 39.32       | 21.98      | 14.87      |

| 100            | 30402    | 57.25       | 32.59      | 21.18      |

| 110            | 36742    | 77.28       | 46.29      | 25.83      |

| 120            | 43682    | 112.41      | 69.38      | 36.18      |

| 130            | 51222    | 139.87      | 87.4       | 43.18      |

| 140            | 59362    | 190.62      | 122        | 56.76      |

Figure 3.5, Figure 3.6 and Figure 3.7 show the total compute time, time for stamping MNA matrix and time for solving MNA matrix vs. the number of unknowns,

respectively. In all three figures, the exponential is around 1.5, which agrees with our expectation.

Figure 3.5. Total compute time vs. unknowns

Figure 3.6. Time for stamping MNA matrix vs. unknowns

Figure 3.7. Time for solving MNA matrix vs. unknowns

## 3.5. NUMERICAL EXPERIMENT

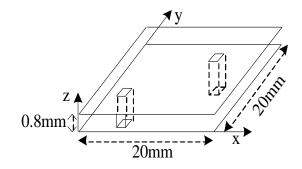

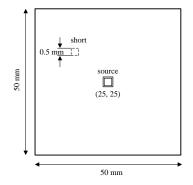

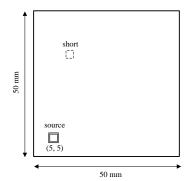

Here we give the results for a plane pair with  $20\text{mm} \times 20\text{mm}$  plane size and 0.8mm plane spacing as shown in Figure 3.8. The short center is located at (x=5mm, y=5mm), and the source center is located at (x=13mm, y=13mm). The port size for both short and source is  $2\text{mm} \times 2\text{mm}$ . The mesh size is set as  $0.5\text{mm} \times 0.5\text{mm}$ . The software of PowerPEEC from IBM [14] is used to validate the results. The calculated results are listed in Table 3.6. The results from PPP approach agree well with the result using PowerPEEC, and the relative error is less than 0.5 %.

Figure 3.8. Test geometry

Table 3.6 Calculation results with different methods

|            | Unknowns | Inductance | Time     |

|------------|----------|------------|----------|

| w/o Apporx | 4834     | 729.97 pH  | 31.3 sec |

| w/ Approx  | 4834     | 727.95 pH  | 7.5 sec  |

| PowerPEEC  | -        | 727.15 pH  | 85.4 sec |

The calculated plane pair inductance using the PPP approach matches well with PowerPEEC. The result obtained with the approximation criteria applied is very close to that calculated using closed-form expression, and *err* is less than 0.5 %. The total compute time with approximation applied is reduced to about a quarter of the total time using closed-form expression with losing the accuracy, which is very helpful when plane size is large.

# 3.6. MULTIPLE CONTACTS

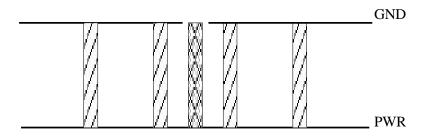

In real PDN design, multiple decoupling capacitors are placed between power and ground plane (Figure 3.9). In PPP approach, these decoupling capacitors are represented using short vias. Here, we show an example with 10 shorts shown in Figure 3.10. The plane pair is  $50 \text{mm} \times 50 \text{mm}$  with the plane spacing of 0.2mm. The via size is  $2 \text{mm} \times 2 \text{mm}$ , and mesh size is  $1 \text{mm} \times 1 \text{mm}$ . The locations of the source and 10 shorts are shown in Figure 3.10.

Figure 3.9. PWR/GND pair with multiple vias.

Figure 3.10. Test geometry with 10 contacts.

The inductance of the plane pair structure shown in Figure 3.10 is calculated using the PPP approach and compared to PowerPEEC (Table 3.7). The PPP approach shows enough accuracy, and the relative error between two methods is only 2.4 %.

Table 3.7 Plane pair inductance with 10 shorts

| Plane Pair   | Relative error |       |

|--------------|----------------|-------|

| PPP Approach | Relative eller |       |

| 165.75 pH    | 161.89 pH      | 2.4 % |

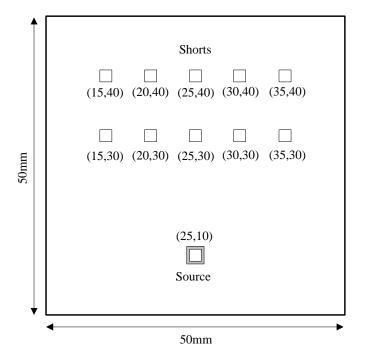

Next, we show that the PPP approach is very efficient taking multiple vias into account compared to other methods, like cavity model [8]. We use the test geometry shown in Figure 3.11 to test the compute time of PPP approach and the cavity model. The plane pair is  $50 \text{mm} \times 50 \text{mm}$  with plane spacing 0.2mm. The source port is fixed at a location, and multiple shorts are spread on the board around the port.

Figure 3.11. Test geometry for multiple shorts

The number of increased unknowns due to the increasing of vias is a small portion compared to the total amount of unknowns in the MNA matrix, which determines the total computational time. For example, when the number of shorts is increased from 10 to 20, the number of unknowns increases 10 which is only 0.13 % of the total amount of unknowns (Table 3.8). Thus, the total compute time of the PPP approach will not increase much by increasing the number of shorts.

Table 3.8 Multiple shorts

| Contact No. | Unknowns | Increased portion |

|-------------|----------|-------------------|

| 10          | 7711     | -                 |

| 20          | 7721     | 0.13 %            |

As shown in Figure 3.12, for the same geometry, the running time for the PPP approach is almost linear to the contact number. However, the running time for cavity model is exponential to the contact number. It is apparently that the PPP approach is more efficient to handle the case with multiple contacts.

Figure 3.12. Compute time comparison for multiple contacts. (a) PPP approach. (b) Cavity model.

# 3.7. NON-UNIFORM MESH

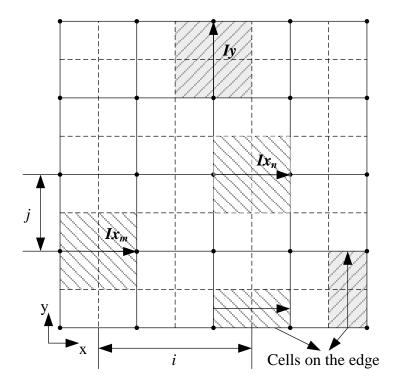

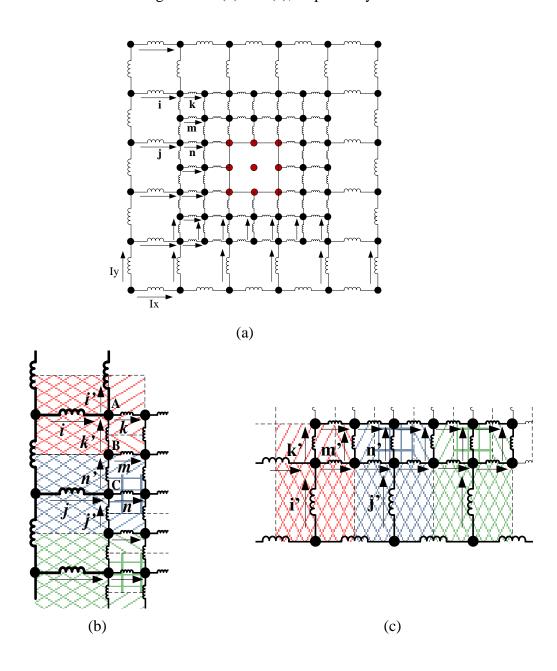

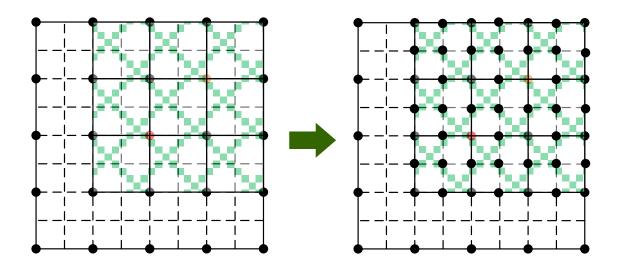

Since the current distribution is concentrated near the port region, non-uniform mesh may be applied to reduce the size of MNA matrix and increase calculation speed. Sub-mesh is applied to the region near the ports. For the region away from the ports, sparse mesh is used (Figure 3.13 (a)). The zoom-in of the interface currents in both x and y directions is also shown in Figure 3.13 (b) and (c), respectively.

Figure 3.13. Non-uniform mesh. (a) Sub-mesh near the port region. (b) Zoom-in of the interface in *x* direction. (c) Zoom-in of the interface in *y* direction.

The size of the dense mesh is set as half of the size of the sparse mesh (Figure 3.13). The incident matrix of the voltage is similar as that of the uniform mesh. The incident matrix of the current is changed due to the re-distribution of the current at the interface between sparse mesh region and sub-mesh region. To generate incident matrix of current,  $\bar{I}$  for the interface, we assume that the current flows uniformly through the cell.

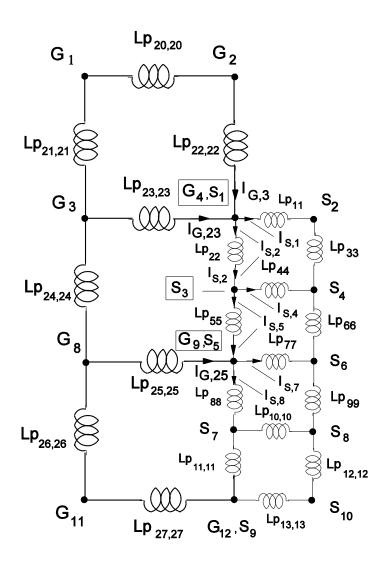

Figure 3.14. Transition between mesh density.

Figure 3.14 shows the equivalent circuit for the transition between mesh density as shown in Figure 3.13. There are three types of nodes that are of importance for the transition between the two regions. Type I node is the corner node between the transition regions, i.e., node A in Figure 3.13 or node ( $[G_4, S_1]$ ) in Figure 3.14. Type II node is the nodes next to the corner nodes occur only in the reduced size mesh, i.e., node B in Figure 3.13 or node  $S_3$  in Figure 3.14. Type III node is different from the side node and there is a direct connection to the coarse mesh, i.e., node C in Figure 3.13 or node ( $[G_9, S_5]$ ) in Figure 3.14.

Based on the ratio of the corresponding cross section length, the weighted KCL equations for the three types of nodes can be obtained. For node A, the cross section that current  $Ix_k$  flows out is 75% of that current  $Ix_i$  flows in. For node B, the cross section  $Ix_m$  flows out is 25% of the cross sections  $Ix_i$  and  $Ix_j$  flows in. For node C, the cross section  $Ix_n$  flows out is 50% of that  $Ix_j$  flows in. All coarse-fine mesh nodes are handled same way. Eq. (32) shows the weighted KCL equations for the three types of nodes in the equivalent circuit shown in Figure 3.14. Stamping the coefficients in Eq. (32) into to  $\overline{I}$  generate a new weighted KCL matrix as shown in Table 3.9. Again, the current we talk about here is the differential current as shown in Figure 2.8.

Type I Node:

$$-0.75I_{G,23} + I_{S,1} + I_{S,2} - 0.75I_{G,3} = 0$$

Type II Node:

$$-0.25I_{G,23} - 0.25I_{G,25} + I_{S,4} + I_{S,5} - I_{S,2} = 0$$

(32)

Type III Node:

$$-0.5I_{G.25} + I_{S.7} + I_{S.8} - I_{S.5} = 0$$

Table 3.9 Weighted KCL matrix

|             | $I_{G,23}$ | $I_{G,25}$ | $I_{S,1}$ | $I_{S,4}$ | $I_{S,7}$ | $I_{G,3}$ | $I_{S,2}$ | $I_{S,5}$ | $I_{S,8}$ |

|-------------|------------|------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| $[G_4,S_1]$ | -0.75      | 0          | 1         | 0         | 0         | -0.75     | 1         | 0         | 0         |

| $S_3$       | -0.25      | -0.25      | 0         | 1         | 0         | 0         | -1        | 1         | 0         |

| $[G_9,S_5]$ | 0          | -0.5       | 0         | 0         | 1         | 0         | 0         | -1        | 1         |

# 3.8. NUMERICAL EXPERIMENT FOR NON-UNIFORM MESH

A test geometry of  $20\text{mm} \times 20\text{mm}$  plane size with 0.2mm plane pair distance is used to check the performance of the non-uniform mesh approach. The source center is located at (14.5mm, 14.5mm), and the short center is located at (5.5mm, 5.5mm). The via size is  $1\text{mm} \times 1\text{mm}$ . Two uniform mesh sizes, 1mm and 0.5mm, are applied in uniform mesh method, respectively. For non-uniform mesh approach, the sub-mesh size is 0.5mm and the sparse mesh size is 1mm. The convergence of the sub-mesh method is tested by increasing the sub-mesh area around the source via and short via as shown in Figure 3.15.

Figure 3.15. Sub-mesh around the vias.

The inductance obtained using both uniform mesh and sub-mesh methods are shown in Table 3.10. The sub-mesh method shows enough accuracy compared to the uniform mesh method. The amount of unknowns of sub-mesh method is much less than the unknowns of uniform mesh approach without losing the accuracy, which leads to much smaller MNA matrix size and benefits total compute time. By increasing the area of sub-mesh region, the result is convergent.

Table 3.10 Inductance calculated using uniform mesh and sub-mesh methods

|            | Uniform Mesh Size |                    | Sub-mesh Size |               |           |

|------------|-------------------|--------------------|---------------|---------------|-----------|

|            |                   |                    | 0.5mm         |               |           |

|            | 1mm               | 0.5mm Sub-mesh are |               | Sub-mesh area |           |

|            | 111111            |                    | 3mm×3mm       | 5mm×5mm       | 7mm×7mm   |

| Unknowns   | 1268              | 4922               | 1428          | 1732          | 2180      |

| Inductance | 268.95 pH         | 276.15 pH          | 275.05 pH     | 275.86 pH     | 276.06 pH |

# 3.9. CLOSE VIAS

When the vias are very close, we can use only one sub-mesh region to cover all the vias (Figure 3.16), so that there are enough meshes between the vias to increase the accuracy.

Figure 3.16. Close vias covered by one sub-mesh region.

Figure 3.17. Define the sub-mesh region around the vias.

Define  $X = m\Delta x$  and  $Y = n\Delta y$ , where X and Y are the distance between two vias in x and y direction, respectively, and  $\Delta x$  and  $\Delta y$  are the uniform cell length in x and y direction, respectively. Usually we have  $\Delta x = \Delta y$ . The sub-mesh area for close vias is defined as  $(m + k)(n + k)\Delta x\Delta y$ , k = 2, 4, 6, ... (Figure 3.17).

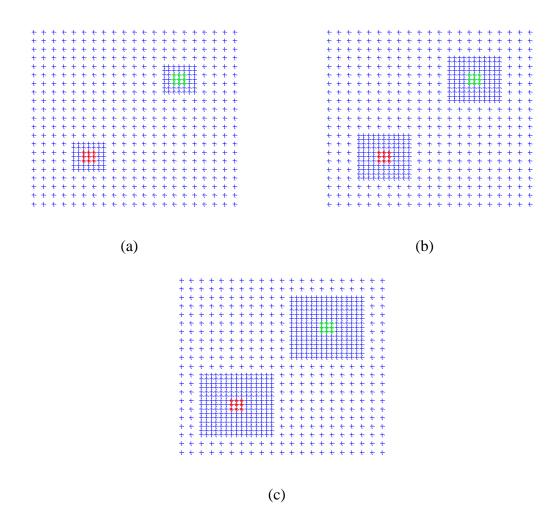

## 3.10. DETERMINE SUB-MESH REGION

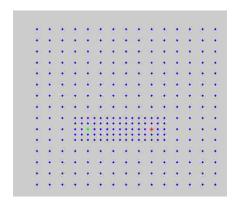

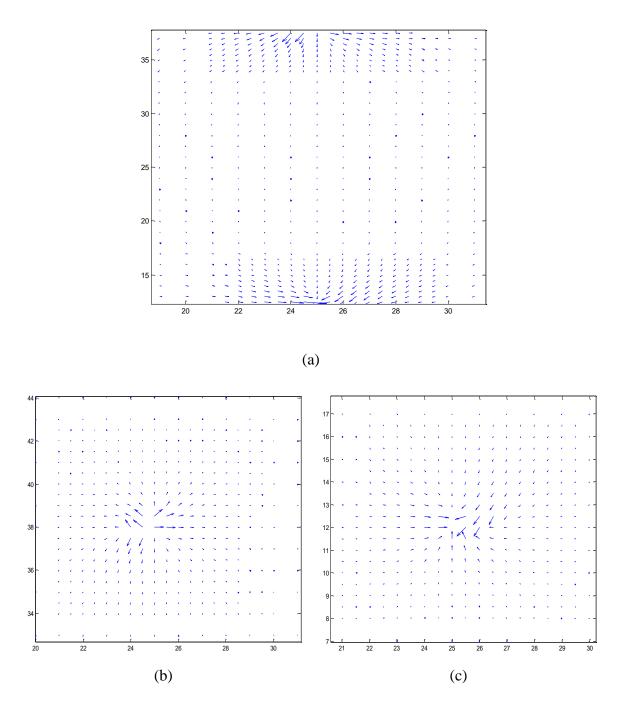

To apply sub-mesh method, we need to know how large the sub-mesh region we should use. Figure 3.18 shows the current distribution on the plane where uniform mesh is applied. It is clearly that the current distribution is concentrated in the region close to the source via and short via in both x and y directions. The current decays very fast in the region away from the vias.

From Figure 3.18, it can be seen that most of the current in x direction is concentrated within 6 uniform cells around the via, 3 cells on the left side and 3 cells on the right side (Figure 3.18 (a)). Same phenomena can be observed for the current distribution in y direction. Since the decay of the coupling between the sections is proportional to  $1/r^2$  from Eq. (25). For the  $4^{th}$  section away from the via, the coupling to the via decays to 1/16 of the coupling between the via and the  $1^{st}$  section next to the via.

Thus, the area of the sub-mesh region should be  $6\Delta x \times 6\Delta y$ , which will give enough accuracy.

Figure 3.18. Current distribution on the plane. (a) *x* direction; (b) *y* direction.

## 3.11. VALIDATION OF SUB-MESH METHOD

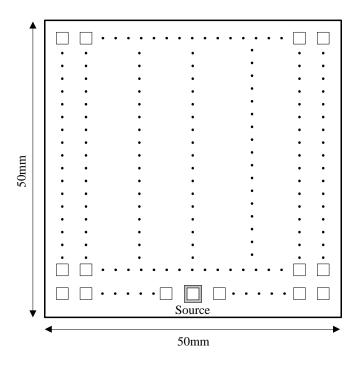

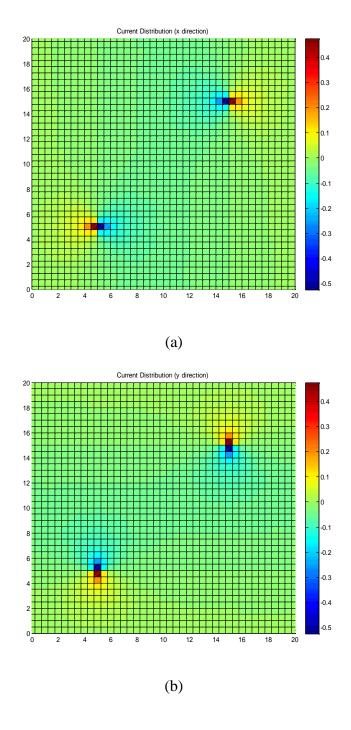

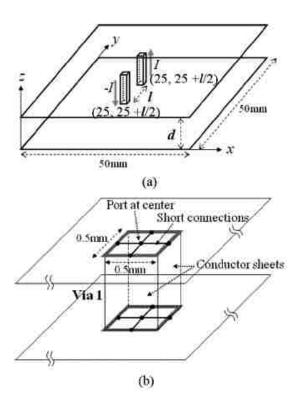

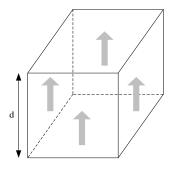

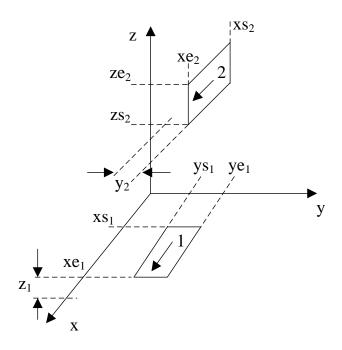

A test geometry in reference [8] is used for the inductance calculation with submesh method and changing several geometrical factors is shown in Figure 3.19 (a). The square parallel planes with the size of  $50 \text{mm} \times 50 \text{mm}$  and two rectangular vias with the size of  $0.5 \text{mm} \times 0.5 \text{mm}$  are shown in Figure 3.19. Two values for the spacing between two planes, d, 0.2mm and 1mm, are tested. Two values for the spacing between two vias, d, 1.5mm and 25.5mm are tested as two extreme cases. The locations of two vias are symmetrical along the y-axis in the test geometry, i.e., (25, 25-l/2) mm and (25, 25+l/2) mm. The calculated plane net inductances (Table 3.11) are compared to the values obtained using hybrid method and PEEC solver (PowerPEEC) in reference [8]. The comparison in Table 3.11 shows that the results obtained using PPP approach agrees with hybrid method and PowerPEEC.