### Scholars' Mine

**Masters Theses**

Student Theses and Dissertations

Spring 2014

# Improved phase shedding technique in a multiphase converter system

Anagha Rayachoti

Follow this and additional works at: https://scholarsmine.mst.edu/masters\_theses

Part of the Electrical and Computer Engineering Commons

Department:

#### **Recommended Citation**

Rayachoti, Anagha, "Improved phase shedding technique in a multiphase converter system" (2014). Masters Theses. 7272.

https://scholarsmine.mst.edu/masters\_theses/7272

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# IMPROVED PHASE SHEDDING TECHNIQUE IN A MULTIPHASE CONVERTER SYSTEM

by

#### ANAGHA RAYACHOTI

#### A THESIS

Presented to the Faculty of the Graduate School of the

MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

2014

Approved by

Mehdi Ferdowsi, Advisor Jonathan W. Kimball Mareisa L. Crow

# © 2014 ANAGHA RAYACHOTI All Rights Reserved

#### **ABSTRACT**

Multiphase converters are increasingly gaining prominence in the field of power electronics. The main advantage of a multiphase converter is its increased efficiency in comparison to a single phase converter. The one major drawback of a multiphase converter is its light load efficiency. Light load efficiency in multiphase converters is very poor when compared to single phase converters. Phase shedding is one of the approaches used to improve this light load efficiency but the transient output voltage response of the system shows large deviations during the process of phase change. This thesis proposes a new technique, called the ramp control technique, to improve this transient behavior. Ramp control technique, proposes to gradually shed a phase or phases of the converter at light loads, instead of abruptly shutting it down. This is done by decreasing the duty cycle of the phase gradually to zero. In this thesis, a moving average model of the ramp control technique is constructed and the slope required for this technique is calculated on the basis of different parameters. The performance of the ramp control technique is also compared with the various conventional methods proposed in literature and it has been proved analytically and through simulation results that the ramp control technique has better dynamic performance when compared to the conventional methods.

#### **ACKNOWLEDGEMENTS**

I owe a debt of gratitude to all those who have helped me with this thesis. First of all, I would like to thank my advisor Dr. Mehdi Ferdowsi, who gave me an opportunity to work on this research. His suggestions and encouragement carried me through difficult times. His valuable feedback contributed greatly to this thesis. Secondly, I would also like to express my gratitude to Dr. Jonathan W. Kimball and Dr. Mareisa L. Crow for serving on my thesis committee and for taking time to review this work.

I am grateful to my loving dad Sasidhar Rayachoti for his professional help and inputs. This project is partially funded by the Intelligent Systems Center (ISC) and I express my gratitude to them as well.

# TABLE OF CONTENTS

|                                                              | Page |

|--------------------------------------------------------------|------|

| ABSTRACT                                                     | iii  |

| ACKNOWLEDGEMENTS                                             | iv   |

| LIST OF ILLUSTRATIONS                                        | vii  |

| LIST OF TABLES                                               | xii  |

| SECTION                                                      |      |

| 1. INTRODUCTION                                              | 1    |

| 1.1 MULTIPHASE CONVERTERS                                    | 1    |

| 1.2 ADVANTAGES OF MULTIPHASE CONVERTERS                      | 2    |

| 1.2.1 Compact Size.                                          | 2    |

| 1.2.2 Reduction in Ripple Current.                           | 3    |

| 1.2.3 Increase in Efficiency.                                | 3    |

| 1.2.4 Increased Current Carrying Capacity                    | 3    |

| 1.3 CHALLENGES OF A MULTIPHASE CONVERTER                     | 3    |

| 2. MATHEMATICAL MODEL OF A MULTIPHASE BUCK CONVERTER $\dots$ | 4    |

| 2.1 INTRODUCTION                                             | 4    |

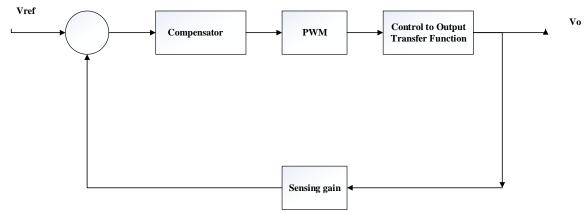

| 2.2 CLOSED LOOP MODEL OF MULTIPHASE CONVERTER                | 5    |

| 2.2.1 Output to Control Transfer Function.                   | 7    |

| 2.2.2 Compensator Design.                                    | 9    |

| 2.2.3 PWM Control Circuit                                    | 14   |

| 2.3 CURRENT SHARING IN MULTIPHASE CONVERTERS                 | 15   |

| 3. PHASE SHEDDING IN MULTIPHASE CONVERTERS                   | 18   |

| 3.1 INTRODUCTION TO PHASE SHEDDING                           | 18   |

| 3.2 PHASE SHEDDING MODEL                                     | 19   |

| 3.2.1 Converter-1                                            | 20   |

| 3.2.2 Converter-2.                                           | 25   |

| 3.3 CONVENTIONAL PHASE SHEDDING TECHNIQUES                   | 30   |

| 3.3.1 Converter-1                                            | 31   |

| 3.3.2 Converter-2.                                           | 35 |

|--------------------------------------------------------------|----|

| 4. RAMP CONTROLLED PHASE SHEDDING                            | 41 |

| 4.1 RAMP CONTROL TECHNIQUE                                   | 41 |

| 4.2 STATE DIAGRAM IMPLEMENTATION                             | 44 |

| 4.3 RAMP CONTROL MODEL OF A MULTIPHASE CONVERTER             | 50 |

| 4.4 RAMP CONTROLLED PHASE SHEDDING IN A MULTIPHASE CONVERTER | 53 |

| 4.4.1 Converter 1                                            | 53 |

| 4.4.2 Converter-2                                            | 61 |

| 4.5 RAMP CONTROLLED PHASE ADDING IN A MULTIPHASE             |    |

| CONVERTER                                                    | 68 |

| 4.5.1 Converter 1                                            | 68 |

| 4.5.2 Converter-2                                            | 73 |

| 5. CONCLUSION                                                | 80 |

| BIBLIOGRAPHY                                                 | 81 |

| VITA                                                         | 85 |

# LIST OF ILLUSTRATIONS

|                                                                                       | Page |

|---------------------------------------------------------------------------------------|------|

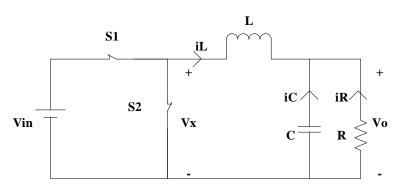

| Figure 1.1 Buck converter schematic                                                   | 1    |

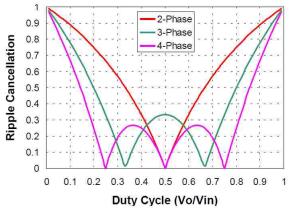

| Figure 1.2 Ripple cancellations in a multiphase converter for different number of pha | ases |

| as a function of the duty cycle [4]                                                   | 2    |

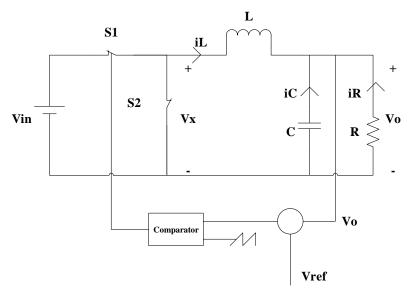

| Figure 2.1 Closed loop control schematic of a Buck converter                          | 6    |

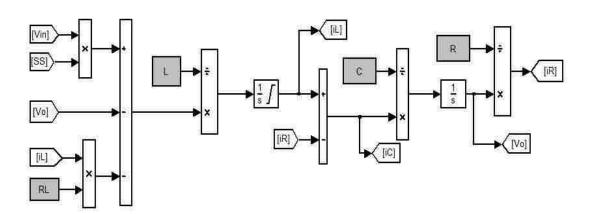

| Figure 2.2 Single-phase Buck converter model                                          | 7    |

| Figure 2.3 Two phase Buck converter model                                             | 8    |

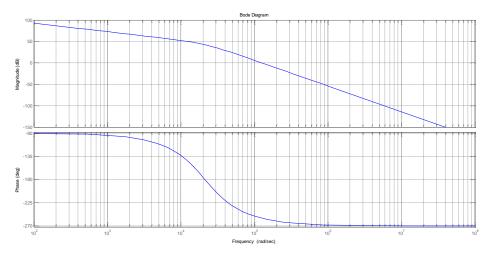

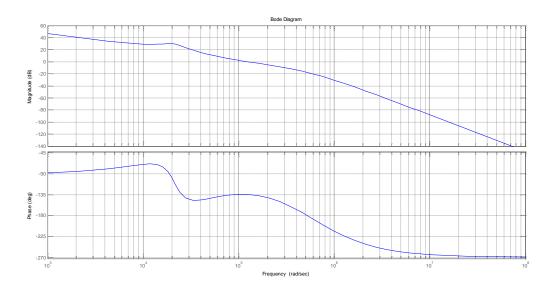

| Figure 2.4 Bode plot of the system for BW of 20 kHz (Converter 1)                     | 11   |

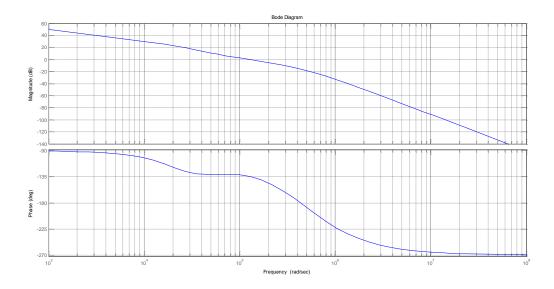

| Figure 2.5 Bode plot of the compensated system (Converter 1)                          | 12   |

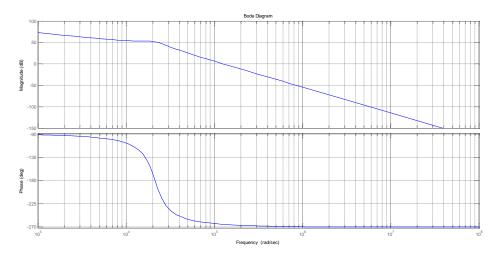

| Figure 2.6 Bode plot of the system for BW of 20 kHz (Converter 2)                     | 13   |

| Figure 2.7 Bode plot of the compensated system (Converter 2)                          | 13   |

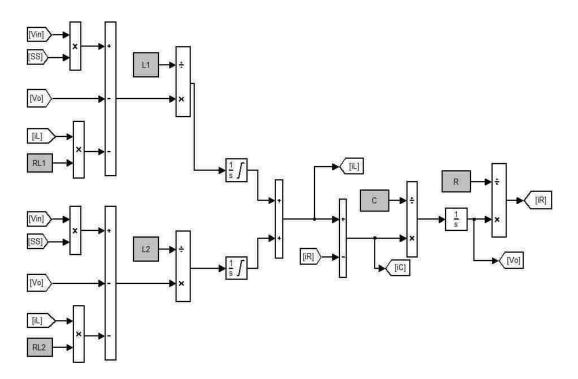

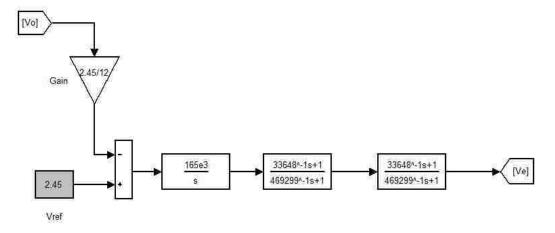

| Figure 2.8 Closed loop system implementation in Simulink (Converter 1)                | 14   |

| Figure 2.9 Voltage mode control schematic of the Buck converter                       | 14   |

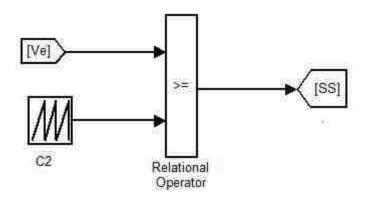

| Figure 2.10 VMC control implementation in Simulink                                    | 15   |

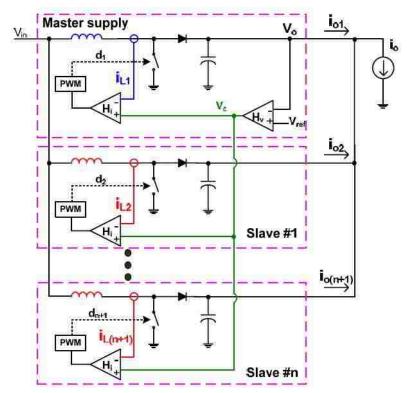

| Figure 2.11 Master-slave control of the Buck converter [4]                            | 16   |

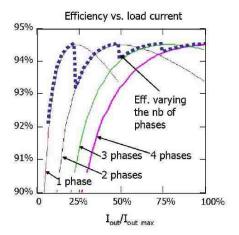

| Figure 3.1 Efficiency graphs of a multiphase converter for different phases [8]       | 19   |

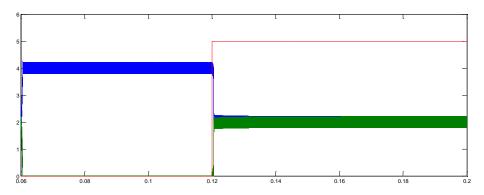

| Figure 3.2 Phase shedding PWM control implementation in Simulink                      | 20   |

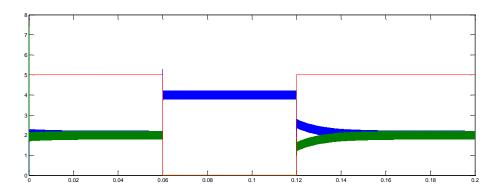

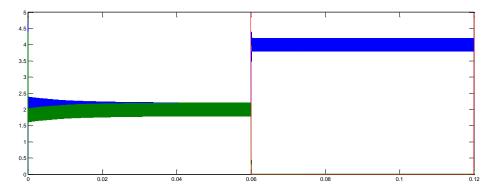

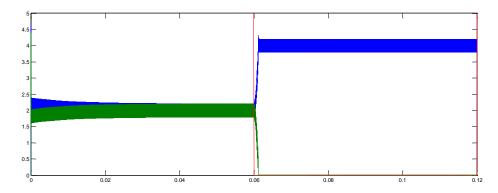

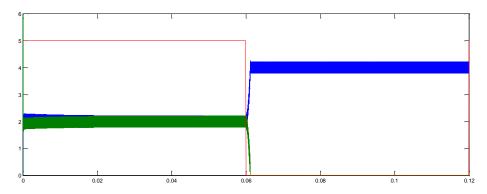

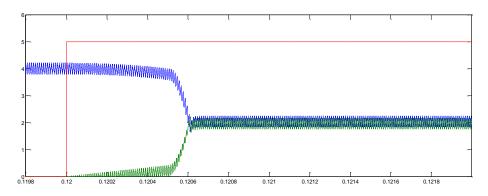

| Figure 3.3 Phase currents in converter-1                                              | 21   |

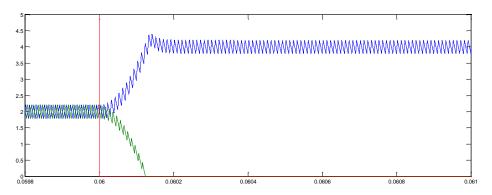

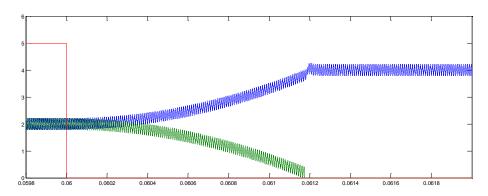

| Figure 3.4 Zoomed in phase currents in converter-1 at the point of phase shedding     | 21   |

| Figure 3.5 Zoomed in phase currents in converter-1 at the point of phase adding       | 22   |

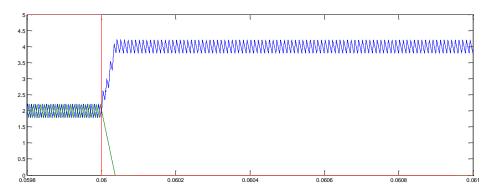

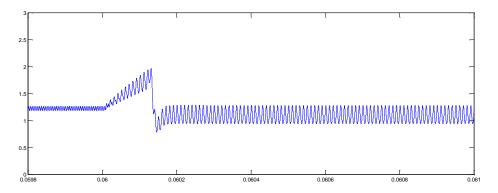

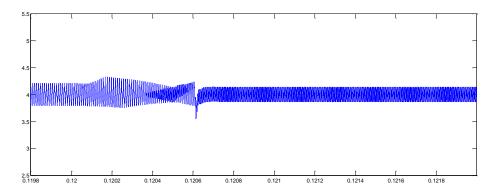

| Figure 3.6 Total current in converter-1 at the point of phase shedding                | 22   |

| Figure 3.7 Total current in converter-1 at the point of phase adding                  | 22   |

| Figure 3.8 Phase-1's error voltage in converter-1 at the point of phase shedding      | 23   |

| Figure 3.9 Phase-1's error voltage in converter-1 at the point of phase adding        | 23   |

| Figure 3.10 Phase-2's error voltage in converter-1 at the point of phase shedding     | 23   |

| Figure 3.11 Phase-2's error voltage in converter-1 at the point of phase adding       | 24   |

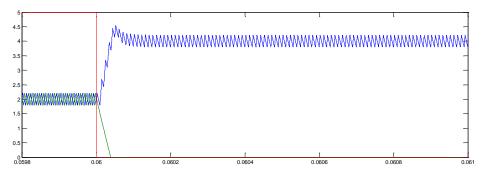

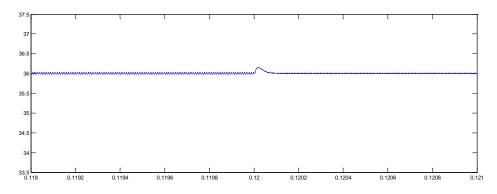

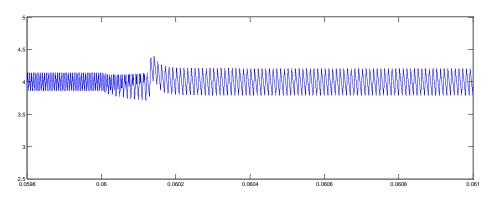

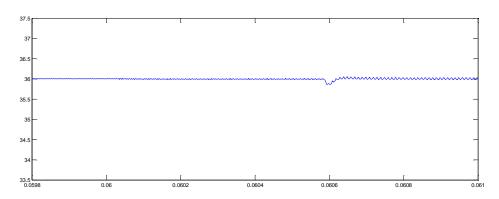

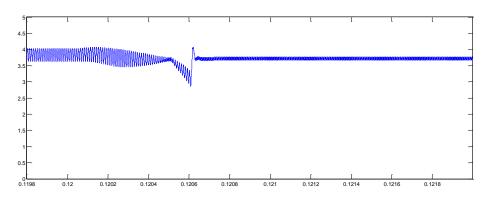

| Figure 3.12 Output voltage of converter-1 at the point of phase shedding              | 24   |

| Figure 3.13 Output voltage of converter-1 at the point of phase adding                | 24   |

| Figure 3.14 | Phase currents in converter-2                                               | 5 |

|-------------|-----------------------------------------------------------------------------|---|

| Figure 3.15 | Zoomed in phase currents in converter-2 at the point of phase shedding 2    | 6 |

| Figure 3.16 | Zoomed in phase currents in converter-2 at the point of phase adding 2      | 6 |

| Figure 3.17 | Total current in converter-2 at the point of phase shedding                 | 6 |

| Figure 3.18 | Total current in converter-2 at the point of phase adding                   | 7 |

| Figure 3.19 | Phase-1's error voltage in converter-2 at the point of phase shedding 2     | 7 |

| Figure 3.20 | Phase-1's error voltage in converter-2 at the point of phase adding         | 7 |

| Figure 3.21 | Phase-2's error voltage in converter-2 at the point of phase shedding 2     | 8 |

| Figure 3.22 | Phase-2's error voltage in converter-2 at the point of phase adding         | 8 |

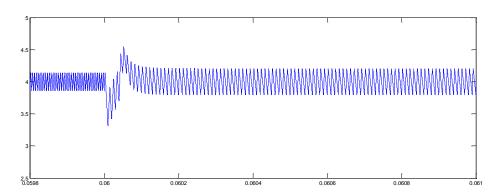

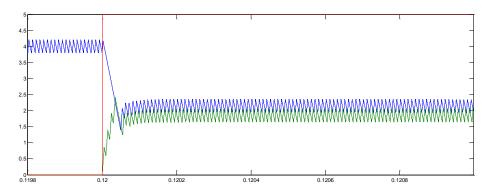

| Figure 3.23 | Output voltage of converter-2 at the point of phase shedding                | 8 |

| Figure 3.24 | Output voltage of converter-2 at the point of phase adding                  | 9 |

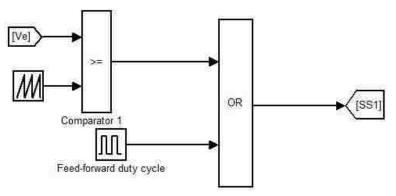

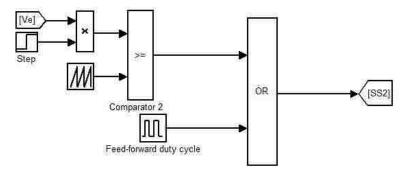

| Figure 3.25 | Feed-forward control implementation for phase-1 in Simulink                 | 1 |

| Figure 3.26 | Feed-forward control implementation for phase-2 in Simulink                 | 1 |

| Figure 3.27 | Phase currents of converter-1 in a feed-forward control system 3            | 2 |

| Figure 3.28 | Zoomed in phase currents of converter-1 in a feed-forward control system. 3 | 3 |

| Figure 3.29 | Zoomed in phase currents of converter-1 during phase adding in a feed-      |   |

|             | forward control system                                                      | 3 |

| Figure 3.30 | Total current of converter-1 during phase shedding in a feed-forward        |   |

|             | control system                                                              | 3 |

| Figure 3.31 | Total current of converter-1 during phase adding in a feed-forward control  |   |

|             | system                                                                      | 4 |

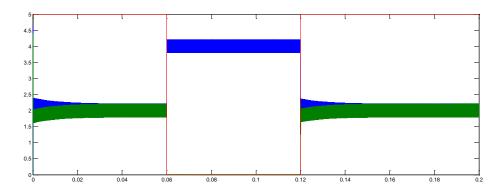

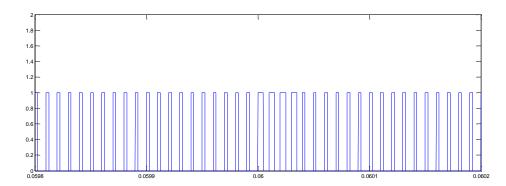

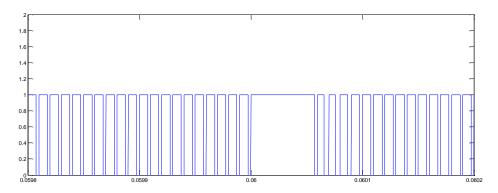

| Figure 3.32 | Zoomed in view of the switching state of phase-1 in converter-1 during      |   |

|             | phase shedding for feed-forward control                                     | 4 |

| Figure 3.33 | Zoomed in view of the switching state of phase-2 in converter-1 during      |   |

|             | phase adding for feed-forward control                                       | 4 |

| Figure 3.34 | Output voltage of converter-1 during phase shedding in a feed forward       |   |

|             | control system                                                              | 5 |

| Figure 3.35 | Output voltage of converter-1 during phase adding in a feed forward         |   |

|             | control system                                                              | 5 |

| Figure 3.36 | Phase currents of converter-2 in a feed-forward control system              | 6 |

| Figure 3.37 Zoomed in phase currents of converter-2 during phase shedding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | in a feed- |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| forward control system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 36         |

| Figure 3.38 Zoomed in phase currents of converter-2 during phase adding in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | a feed-    |

| forward control system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 37         |

| Figure 3.39 Total current of converter-2 during phase shedding in a feed-forward for the converter of the co | ward       |

| control system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 37         |

| Figure 3.40 Total current of converter-2 during phase adding in a feed-forward                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | rd         |

| control system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 37         |

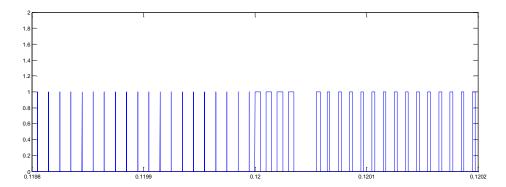

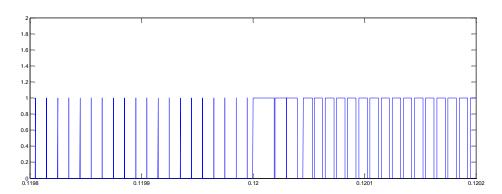

| Figure 3.41 Zoomed in view of the switching state of phase-1 in converter-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | during     |

| phase shedding for feed-forward control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 38         |

| Figure 3.42 Zoomed in view of the switching state of phase-2 in converter-2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | during     |

| phase adding for feed-forward control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 38         |

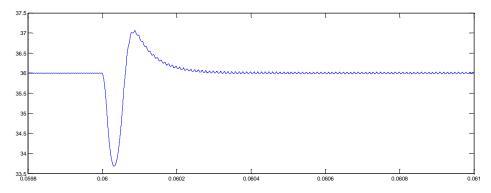

| Figure 3.43 Output voltage of converter-2 during phase adding in a feed forw                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | vard       |

| control system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 38         |

| Figure 3.44 Output voltage of converter-2 during phase adding in a feed forw                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | vard       |

| control system                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 39         |

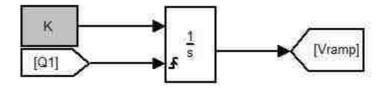

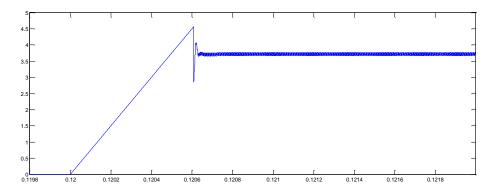

| Figure 4.1 Implementation of the state V <sub>RAMP</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 44         |

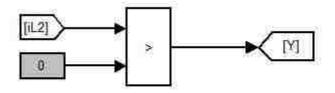

| Figure 4.2 Implementation of the transition condition Y                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 45         |

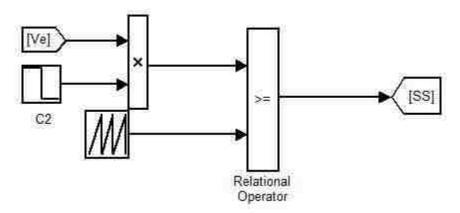

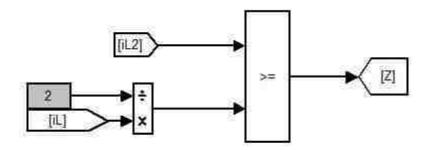

| Figure 4.3 Implementation of the transition condition Z                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 45         |

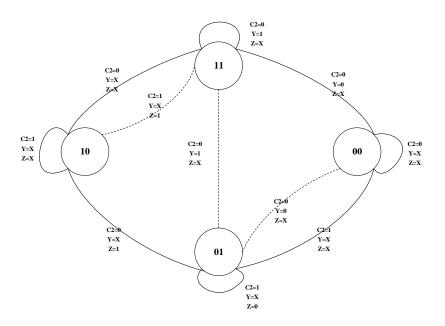

| Figure 4.4 State diagrams for a ramp controlled phase change process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 46         |

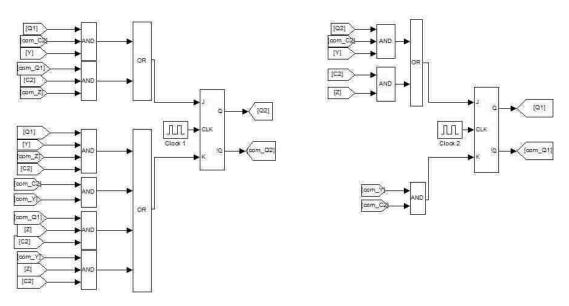

| Figure 4.5 Flip-flop implementation of the state diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 50         |

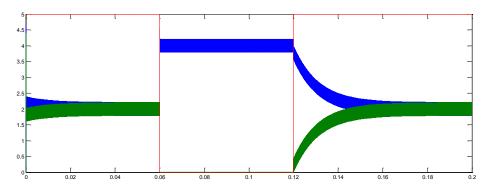

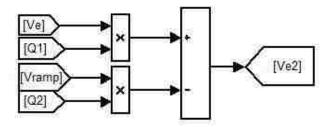

| Figure 4.6 Error voltage of phase-2 in ramp control technique                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 52         |

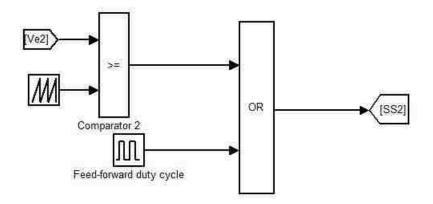

| Figure 4.7 Ramp control implementation for phase-2 in Simulink                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 52         |

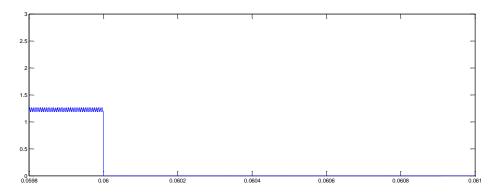

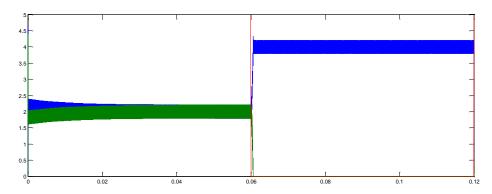

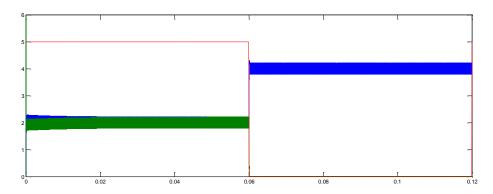

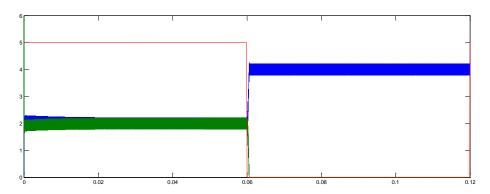

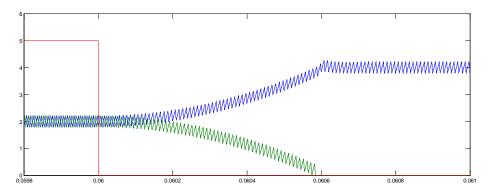

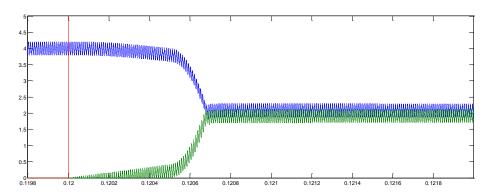

| Figure 4.8 Phase current in converter-1 for T <sub>d</sub> =100 μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 53         |

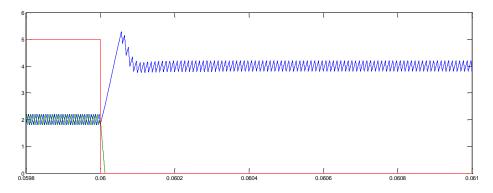

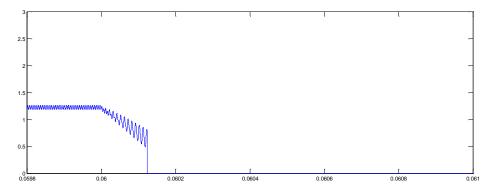

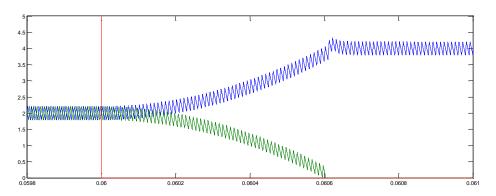

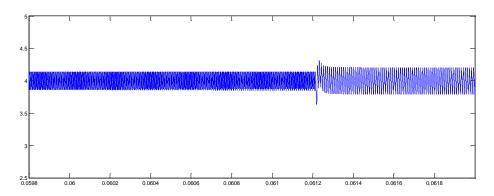

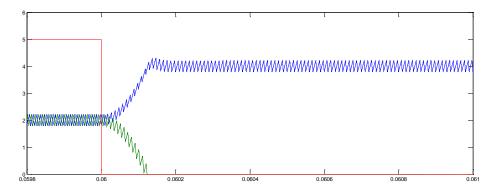

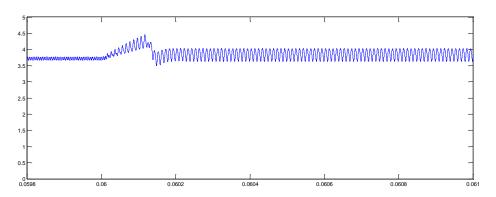

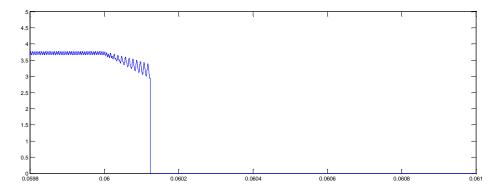

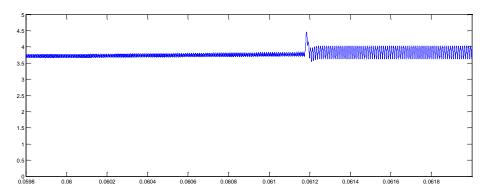

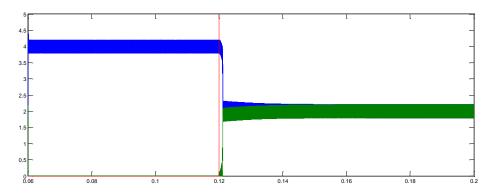

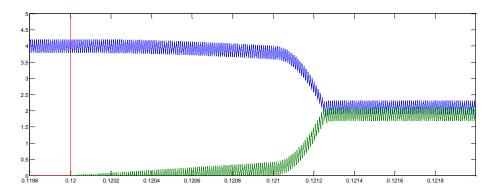

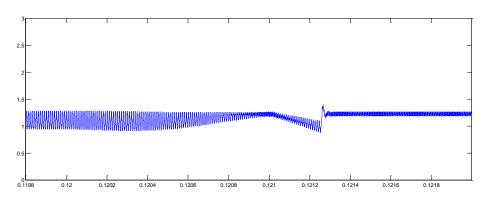

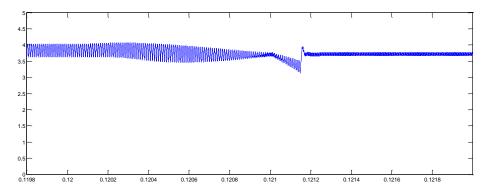

| Figure 4.9 Zoomed in phase currents in converter-1 for $T_d$ =100 $\mu$ s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 54         |

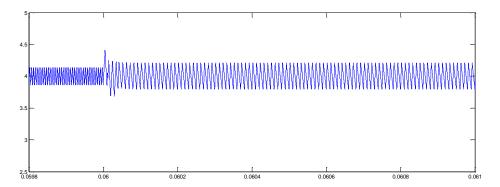

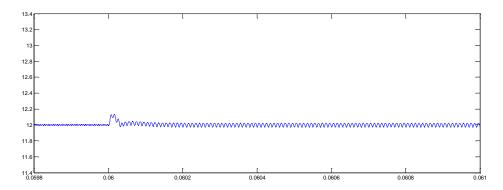

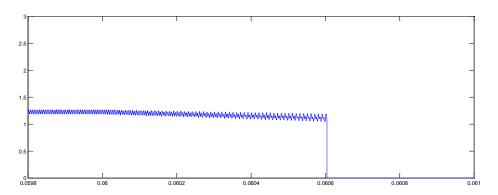

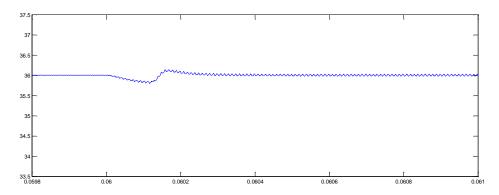

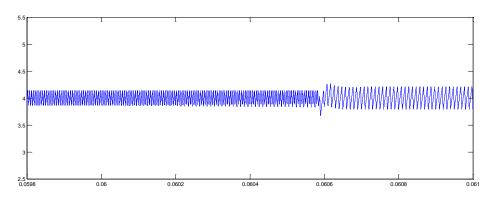

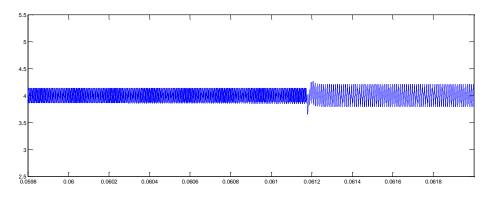

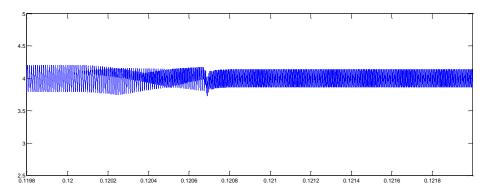

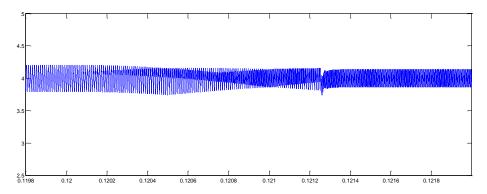

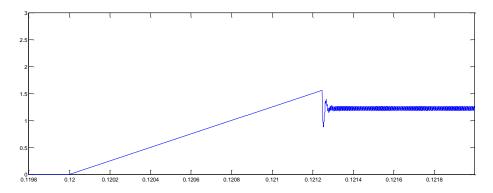

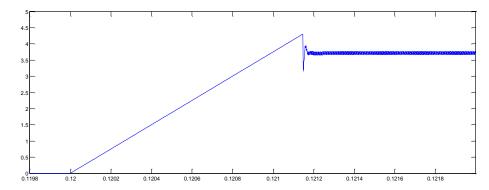

| Figure 4.10 Total current in converter-1 for T <sub>d</sub> =100 μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 54         |

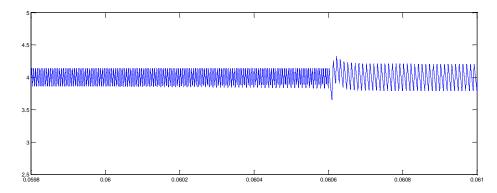

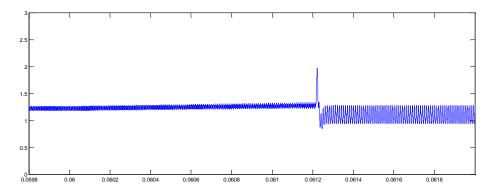

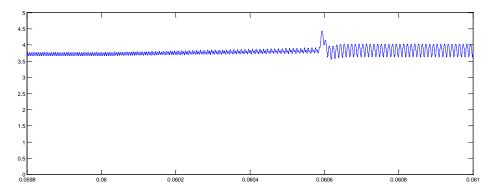

| Figure 4.11 Phase-1's error voltage in converter-1 for $T_d$ =100 $\mu$ s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 54         |

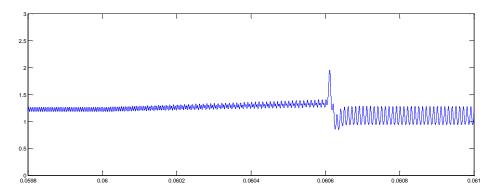

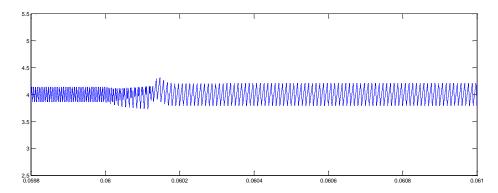

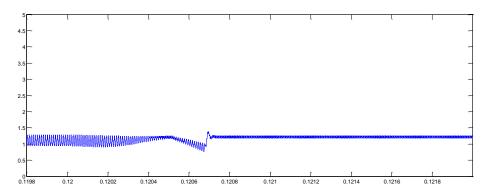

| Figure 4.12 Phase-2's error voltage in converter-1 for $T_d$ =100 $\mu$ s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 55         |

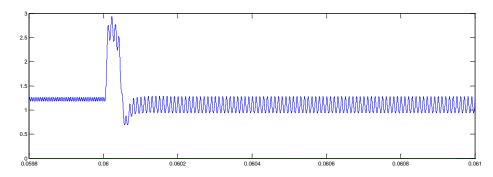

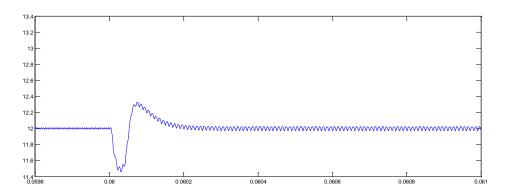

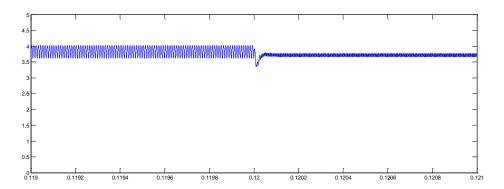

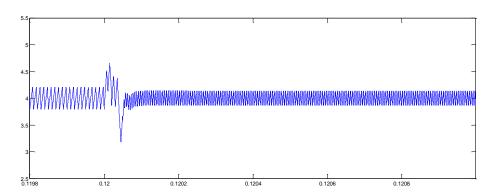

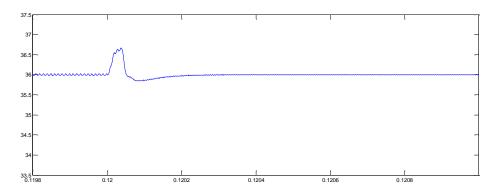

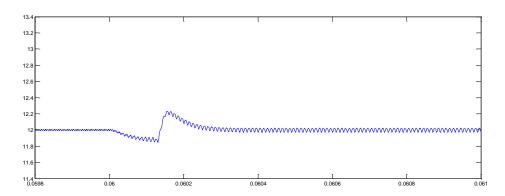

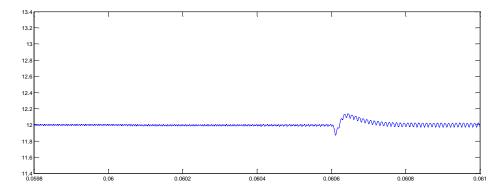

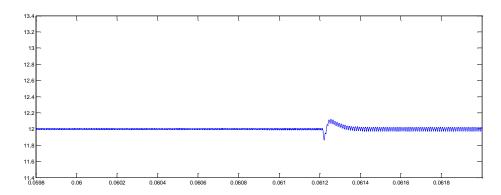

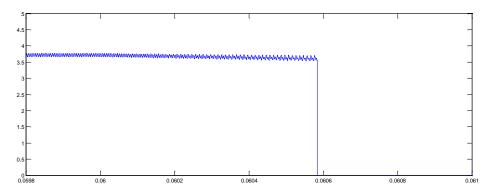

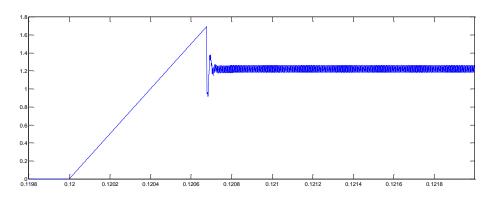

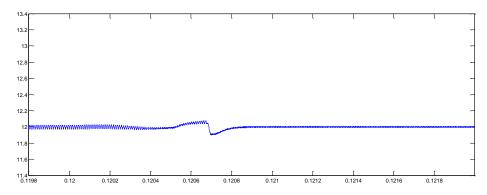

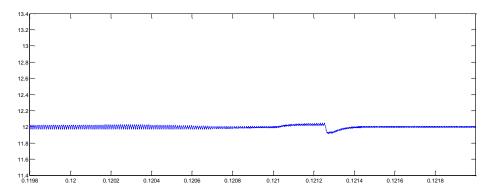

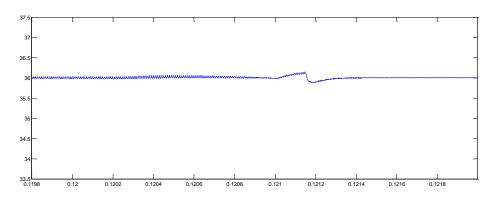

| Figure 4.13 Output voltage of converter-1 for T <sub>d</sub> =100 μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 55         |

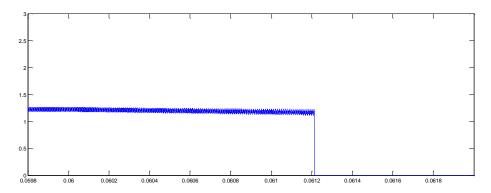

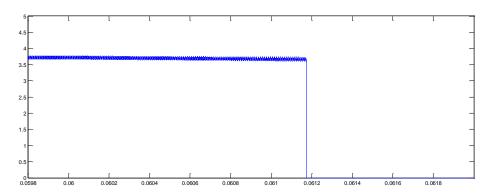

| Figure 4.14 Phase current in converter-1 for T <sub>d</sub> =500 μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 56         |

| Figure 4.15 Zoomed in phase currents in converter-1 for T <sub>d</sub> =500 μs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 56         |

| Figure 4.16 Total current in converter-1 for T <sub>d</sub> =500 μs            | 56 |

|--------------------------------------------------------------------------------|----|

| Figure 4.17 Phase-1's error voltage in converter-1 for $T_d$ =500 $\mu s$      | 57 |

| Figure 4.18 Phase-2's error voltage in converter-1 for $T_d$ =500 $\mu s$      | 57 |

| Figure 4.19 Output voltage of converter-1 for $T_d$ =500 $\mu s$               | 57 |

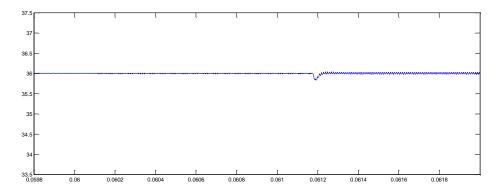

| Figure 4.20 Phase current in converter-1 for $T_d$ =1000 $\mu s$               | 58 |

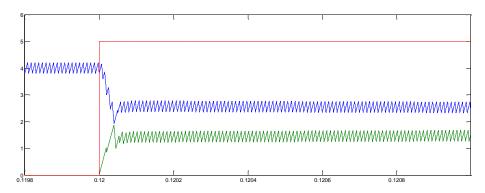

| Figure 4.21 Zoomed in phase currents in converter-1 for $T_d$ =1000 $\mu s$    | 59 |

| Figure 4.22 Total current in converter-1 for $T_d$ =1000 $\mu s$               | 59 |

| Figure 4.23 Phase-1's error voltage in converter-1 for $T_d$ =1000 $\mu s$     | 59 |

| Figure 4.24 Phase-2's error voltage in converter-1 for $T_d$ =1000 $\mu s$     | 60 |

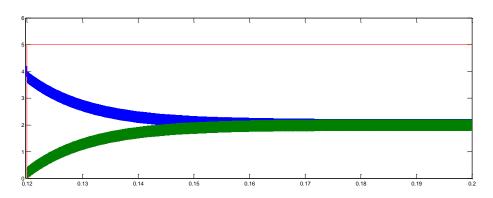

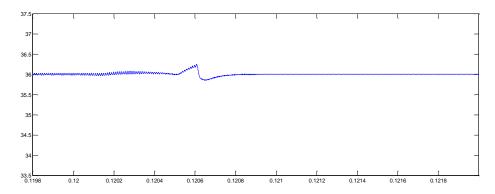

| Figure 4.25 Output voltage of converter-1 for $T_d$ =1000 $\mu s$              | 60 |

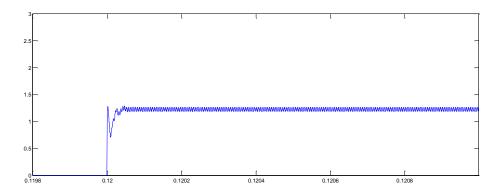

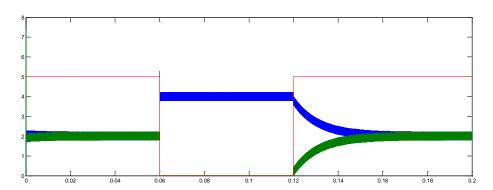

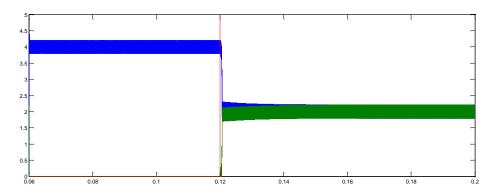

| Figure 4.26 Phase current in converter-2 for $T_d$ =100 $\mu s$                | 61 |

| Figure 4.27 Zoomed in phase currents in converter-2 for $T_d$ =100 $\mu s$     | 61 |

| Figure 4.28 Total current in converter-2 for $T_d$ =100 $\mu s$                | 62 |

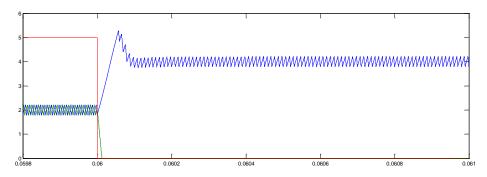

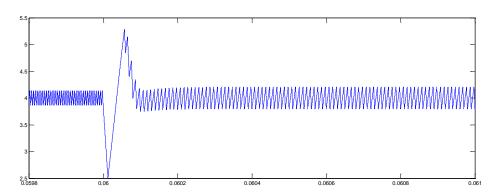

| Figure 4.29 Phase-1's error voltage in converter-2 for $T_d$ =100 $\mu s$      | 62 |

| Figure 4.30 Phase-2's error voltage in converter-2 for $T_d$ =100 $\mu s$      | 62 |

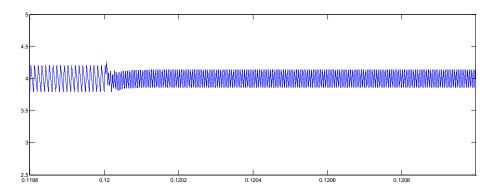

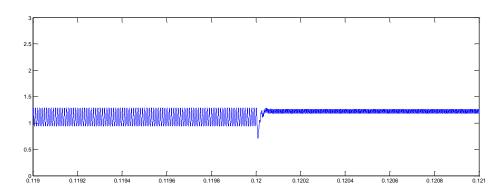

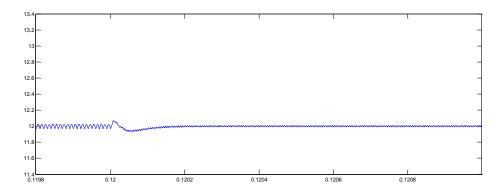

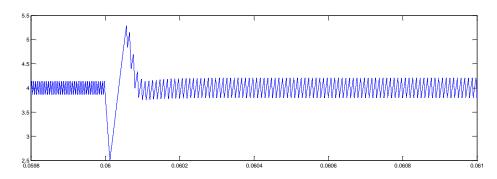

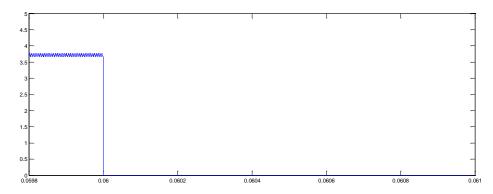

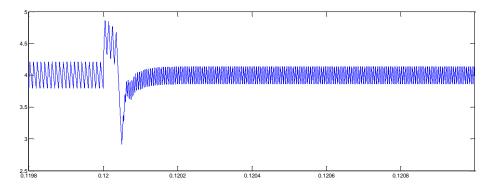

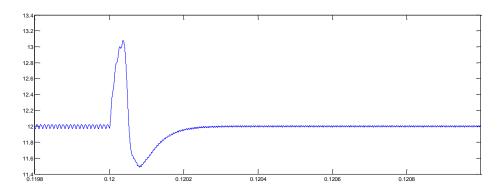

| Figure 4.31 Output voltage of converter-2 for $T_d$ =100 $\mu s$               | 63 |

| Figure 4.32 Phase current in converter-2 for $T_d$ =500 $\mu s$                | 63 |

| Figure 4.33 Zoomed in phase currents in converter-2 for $T_d$ =500 $\mu$ s     | 64 |

| Figure 4.34 Total current in converter-2 for $T_d$ =500 $\mu s$                | 64 |

| Figure 4.35 Phase-1's error voltage in converter-2 for $T_d$ =500 $\mu s$      | 64 |

| Figure 4.36 Phase-2's error voltage in converter-2 for $T_d$ =500 $\mu s$      | 65 |

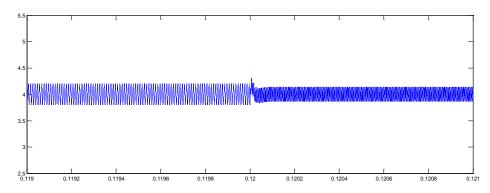

| Figure 4.37 Output voltage of converter-2 for $T_d$ =500 $\mu s$               | 65 |

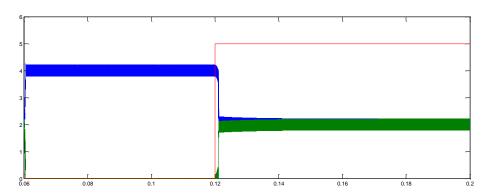

| Figure 4.38 Phase current in converter-2 for $T_d$ =1000 $\mu s$               | 66 |

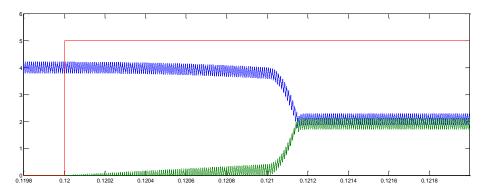

| Figure 4.39 Zoomed in phase currents in converter-2 for $T_d$ =1000 $\mu s$    | 66 |

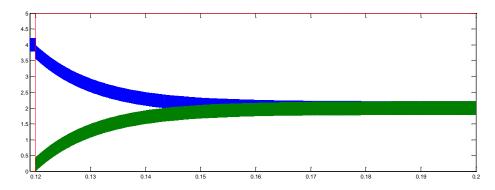

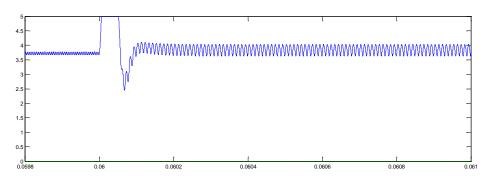

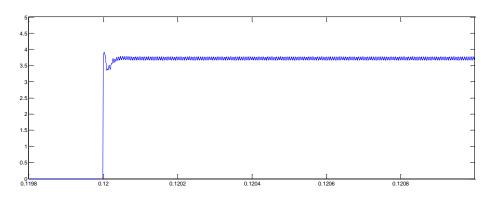

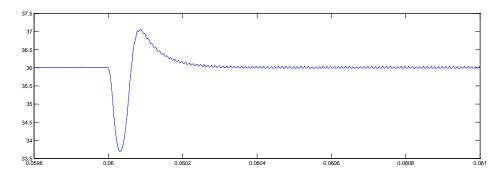

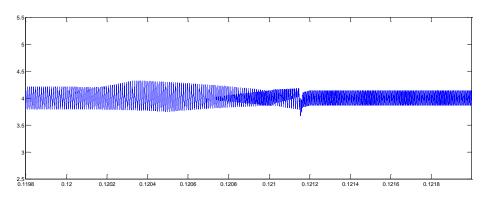

| Figure 4.40 Total current in converter-2 for $T_d$ =1000 $\mu s$               | 66 |