## Scholars' Mine

**Masters Theses**

Student Theses and Dissertations

Spring 2010

# FPGA implementation of PSO algorithm and neural networks

Parviz Palangpour

Follow this and additional works at: https://scholarsmine.mst.edu/masters\_theses

Part of the Computer Engineering Commons

Department:

#### **Recommended Citation**

Palangpour, Parviz, "FPGA implementation of PSO algorithm and neural networks" (2010). Masters Theses. 4759.

https://scholarsmine.mst.edu/masters\_theses/4759

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

## FPGA IMPLEMENTATION OF PSO ALGORITHM AND NEURAL NETWORKS

by

## PARVIZ MICHAEL PALANGPOUR

#### A THESIS

Presented to the Faculty of the Graduate School of the

## MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

MASTER OF SCIENCE IN COMPUTER ENGINEERING

2010

Approved by

Ganesh Kumar Venayagamoorthy, Advisor Waleed Al-Assadi Maciej Zawodniok

# $\ \$ © 2010 $\label{eq:parviz michael palangeour All Rights Reserved}$ All Rights Reserved

#### ABSTRACT

This thesis describes the Field Programmable Gate Array (FPGA) implementations of two powerful techniques of Computational Intelligence (CI), the Particle Swarm Optimization algorithm (PSO) and the Neural Network (NN).

Particle Swarm Optimization (PSO) is a popular population-based optimization algorithm. While PSO has been shown to perform well in a large variety of problems, PSO is typically implemented in software. Population-based optimization algorithms such as PSO are well suited for execution in parallel stages. This allows PSO to be implemented directly in hardware and achieve much faster execution times than possible in software. In this thesis, a pipelined architecture for hardware PSO implementation is presented. Benchmark functions solved by software and FPGA hardware PSO implementations are compared.

NNs are inherently parallel, with each layer of neurons processing incoming data independently of each other. While general purpose processors have reached impressive processing speeds, they still cannot fully exploit this inherent parallelism due to their sequential architecture. In order to achieve the high neural network throughput needed for real-time applications, a custom hardware design is needed. In this thesis, a digital implementation of an NN is developed for FPGA implementation.

The hardware PSO implementation is designed using only VHDL, while the NN hardware implementation is designed using Xilinx System Generator. Both designs are synthesized using Xilinx ISE and implemented on the Xilinx Virtex-II Pro FPGA Development Kit.

#### ACKNOWLEDGMENT

I am deeply grateful to my advisor Dr. Ganesh Kumar Venayagamoorthy, who has provided me with guidance, knowledge and financial support throughout the research and preparation of this thesis.

I would also like to thank Dr. Waleed Al-Assadi and Dr. Maciej Zawodniok for their assistance and serving on my committee. I would also like to thank Dr. Scott C. Smith for his advice and comments towards my work.

I would like acknowledge funding from the following grants:

- 1. GAANN: Advanced Computational Techniques and Real-Time Simulation Studies for the Next Generation Energy Systems

- 2. NSF CAREER: Scalable Learning and Adaption with Intelligent Techniques and Neural Networks for Reconfiguration and Survivability of Complex Systems (ECCS # 0348221)

- 3. EFRI-COPN: Neuroscience and Neural Networks for Engineering the Future Intelligent Electric Power Grid (EFRI #0836017)

Most importantly, I would like to thank my parents for their unconditional support and encouragement towards reaching my goals.

## TABLE OF CONTENTS

|                                    | Page    |

|------------------------------------|---------|

| ABSTRACT                           | <br>iii |

| ACKNOWLEDGMENT                     | <br>iv  |

| LIST OF ILLUSTRATIONS              | <br>vii |

| LIST OF TABLES                     | <br>ix  |

| SECTION                            |         |

| 1 INTRODUCTION                     | <br>1   |

| 1.1 BACKGROUND                     | <br>1   |

| 1.2 THESIS OBJECTIVE               | <br>4   |

| 1.3 THESIS OVERVIEW                | <br>4   |

| 1.4 CONTRIBUTIONS OF THIS THESIS   | <br>5   |

| 1.5 RESEARCH PUBLICATIONS          | <br>5   |

| 1.6 SUMMARY                        | <br>5   |

| 2 IMPLEMENTATIONS OF PSO ALGORITHM | <br>6   |

| 2.1 INTRODUCTION                   | <br>6   |

| 2.2 PARTICLE SWARM OPTIMIZATION    | <br>7   |

| 2.3 PSO HARDWARE IMPLEMENTATION    | <br>9   |

| 2.3.1 The Hardware Velocity Update | <br>10  |

| 2.3.2 Random Number Generation     | <br>11  |

| 2.3.3 Control Module               | <br>12  |

| 2.4 RESULTS                        | <br>13  |

| 3 IMPLEMENTATION OF NEURAL NETWORK | <br>19  |

| 3.1 INTRODUCTION                   | <br>19  |

| 3.2 DESIGN APPROACH                | <br>20  |

| 3.3 NN HARDWARE IMPLEMENTATION     | <br>21  |

| 3.3.1 Implementing the Neuron MAC               | 21 |

|-------------------------------------------------|----|

| 3.3.2 Implementing the Activation Function LUT  | 23 |

| 3.3.3 Implementing the Complete Hardware Neuron | 24 |

| 3.3.4 Implementing the NN Layer Control Block   | 26 |

| 3.3.5 Implementing a Three-Layer NN             | 27 |

| 3.4 RESULTS                                     | 30 |

| 4 CONCLUSIONS AND FUTURE WORK                   | 35 |

| APPENDICES                                      |    |

| A HARDWARE PSO SOURCE CODE                      | 36 |

| B HARDWARE NN SOURCE CODE                       | 67 |

| BIBLIOGRAPHY                                    | 76 |

| VITA                                            | 79 |

## LIST OF ILLUSTRATIONS

| Figur | re                                                                                         | Page |

|-------|--------------------------------------------------------------------------------------------|------|

| 2.1   | PSO hardware implementation with 6-stage pipeline                                          | 10   |

| 2.2   | An example of a linear-feedback shift register                                             | 11   |

| 2.3   | The structure of the neighborhood-of-four PRNG                                             | 12   |

| 2.4   | The hardware PSO execution flowchart                                                       | 14   |

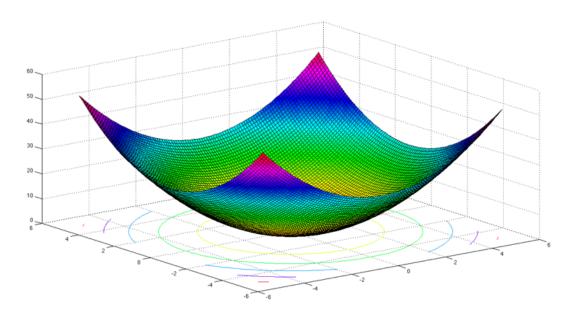

| 2.5   | A two-dimensional view of the sphere benchmark problem fitness surface                     | . 15 |

| 2.6   | A two-dimensional view of the Rosenbrock benchmark problem fitness surface                 | 16   |

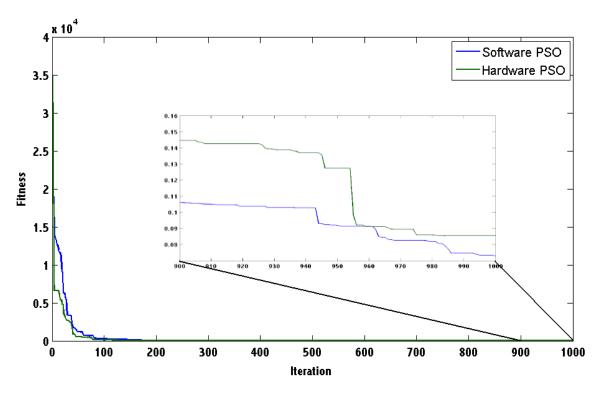

| 2.7   | The hardware PSO compared with a software PSO for the sphere function of 10 dimensions     | 17   |

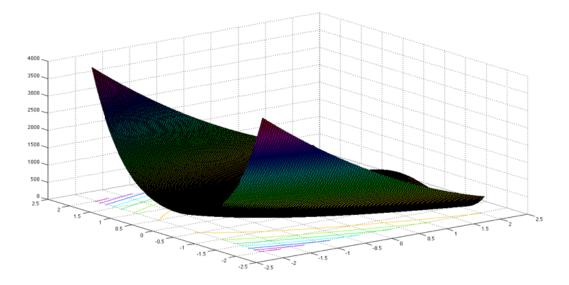

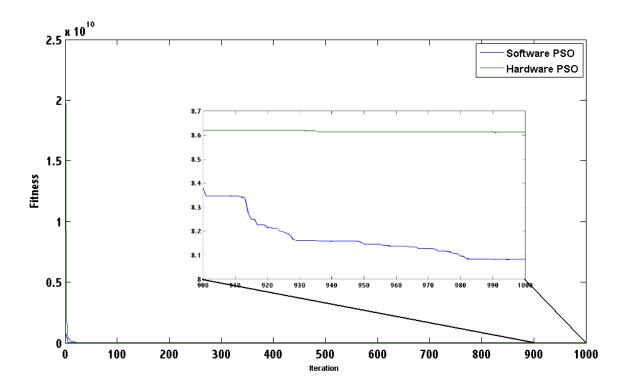

| 2.8   | The hardware PSO compared with a software PSO for the Rosenbrock function of 10 dimensions | 18   |

| 3.1   | An NN with an input, hidden and output layer                                               | 19   |

| 3.2   | A diagram of the neuron model                                                              | 22   |

| 3.3   | MAC hardware subsystem                                                                     | 22   |

| 3.4   | LUTAF approximation                                                                        | 25   |

| 3.5   | LUTAF approximation subsystem                                                              | 25   |

| 3.6   | The complete hardware neuron                                                               | 26   |

| 3.7   | The LCB finite state machine $(2 \times 3 \text{ Layer})$                                  | 27   |

| 3.8   | A LCB controlling three hardware neurons (2 $\times$ 3 Layer)                              | 28   |

| 3.9   | A hardware neuron being controlled by a LCB                                                | 29   |

| 3.10  | A FPGA-based NN (of size $1 \times 3 \times 1$ )                                           | 29   |

| 3.11  | The trained NN for approximating a sin function                                            | 30   |

| 3.12  | The output of the Simulink simulation of the FPGA-based NN                                 | 32   |

| 3.13  | Comparing the output of hidden neurons of the FPGA-based NN and Matlab-based NN            | 33   |

| 3.14  | Comparing the output of the FPGA-based NN and Matlab-based NN                              | 34   |

| 3.15 | The hardware resources used for the $1 \times 10 \times 1$ NN on the Xilinx Virtex-II |    |

|------|---------------------------------------------------------------------------------------|----|

|      | Pro FPGA                                                                              | 34 |

## LIST OF TABLES

| Table |                                                                                    | Page |

|-------|------------------------------------------------------------------------------------|------|

| 2.1   | The values for the LUT in each PRNG cell                                           | 13   |

| 2.2   | Achieved fitness after 1000 iterations for benchmark problems                      | 17   |

| 2.3   | Execution time for software and hardware PSO implementations                       | 17   |

| 2.4   | Hardware PSO logic requirements for the benchmark problems                         | 18   |

| 3.1   | The values for the hyperbolic tangent activation Function LUT where $x \in [L, U]$ |      |

#### 1 INTRODUCTION

#### 1.1 BACKGROUND

Computational Intelligence (CI) is a sub-branch of artificial intelligence. CI is the study of adaptive mechanisms to enable or facilitate intelligent behavior in complex and changing environments [1]. Many of the CI paradigms have mechanisms that exhibit the ability to adapt to new situations, to generalize, abstract, discover and associate. The main CI paradigms are artificial Neural Networks (NNs), evolutionary computing, Swarm Intelligence (SI) and fuzzy systems. Each of these paradigms has origins in some biological system. For instance, NNs are models of biological neural systems while SI models the social behavior of organisms that live in swarms or colonies.

The most common way to implement CI techniques is to write software that can be executed on a standard digital processor. One reason why this approach is the most common is because of the ease of development as developers can take advantage of the enormous number of existing software libraries. By building applications on top of existing software libraries and operating systems, the developer can implement the application without having to be concerned with the operation of the underlying digital hardware. Furthermore, there are a large number of software programming languages available, C, C++, Java, etc; for each of these languages exists multiple mature tools exist that make implementing, simulating and optimizing software applications much easier.

There are also a variety of digital processors that can be used to execute CI software, microcontrollers, digital signal processors (DSPs) and general purpose microprocessors. Microcontrollers offer the least amount of processing power but are available at very low prices and consume very little power. DSPs are designed specifically for digital signal processing applications while general purpose microprocessors offer the highest performance and flexibility. When software is compiled for execution on a specific processor, the compiler essentially converts the software into series of small instructions. These instructions are then executed in a sequential nature on the processor. However, only the simplest of processors execute instructions in a

strictly sequential manner, more advanced processors utilize different techniques to achieve instruction-level parallelism that allow the execution of multiple instructions simultaneously.

While the trend in high-performance microprocessor and DSP design is to incorporate techniques to achieve instruction-level parallelism, the processor and software compiler are left to interpret and exploit any such opportunities for parallelism. As processors are designed for general purpose computing, they cannot be designed to take advantage of the underlying parallelism in each application. Instead of executing the software on a processor, a custom digital system can be designed specifically for a given application. This custom digital system can be designed take advantage of any level of parallelism that exists in the application being implemented. Since the custom digital system can perform a much higher degree of parallelism, a custom digital system can outperform any software-based implementation in terms of execution time. However, it is much more difficult to design a complete digital system to implement an algorithm rather than simply implement the algorithm in software.

Field-Programmable Gate Arrays (FPGAs) are essentially programmable integrated circuits. FPGAs can be reprogrammed to implement arbitrary logic functionality without having to endure the long and expensive design process required for Application Specific Integrated Circuits (ASICs). While FPGAs don't incur the high setup costs of ASIC production, FPGAs are slower, consume more power and consume more area than their ASIC counterparts. However, the flexible architecture and lower cost of entry makes FPGAs ideal for prototyping new designs; this makes FPGAs a popular platform for research.

Specific FPGA design details vary from vendor to vendor, but generally each FPGA contains a large number of Lookup Tables (LUTs) and interconnecting logic that can be programmed. The LUTs are programmed to reflect the specific logic functions they need to perform and the interconnecting logic is programmed to properly implement the connections between the LUTs. It should be noted that this is only an abstract view of an FPGAs internals; most FPGAs contain not only LUTs, but registers, multiplexers, distributed and block memory, and dedicated circuitry for fast adders and multipliers. Recently, FPGAs have become essential components in implementing high performance digital signal processing (DSP) systems. The memory

bandwidth of a modern FPGA far exceeds that of a microprocessor or DSP processor running at clock rates two to ten times that of the FPGA. Coupled with the capability of implementing highly parallel arithmetic architectures, FPGAs are ideally suited for high-performance custom data path processors.

FPGAs have two main types of resources that are used to implement the logic for the intended application, generic programmable logic blocks and dedicated (or "embedded") circuitry that perform fixed functions. The generic logic blocks can be used to build any arbitrary logic function. The embedded hardware blocks are essentially fixed logic functions that are available to the designer at no cost of logic blocks. The embedded hardware operations are ASIC implementations, so they are faster and require less area than the equivalent function built using logic blocks. One common embedded hardware operation is the multiply operation, which typically requires a large number of logic blocks to implement. By selecting a specific FPGA product with the proper embedded resources for the given application, some of the performance disadvantages of FPGA implementations can be reduced.

Several hardware implementations of one SI-based algorithm, Particle Swarm Optimization (PSO), has been reported in literature. Reynolds et al. have implemented a hardware version of PSO for inverting a very large neural network [2]. One Xilinx XC2V6000 was used to execute the PSO algorithm while another was used for computing the fitness. The details of the hardware PSO architecture are not reported. A multi-swarm PSO architecture for blind adaption of array antennas was proposed by Kokai et al. [3]. Each swarm optimizes a single architecture and executes in parallel with the other swarms. The authors have not described the hardware architecture in detail or provided any performance measurements.

Farmahini-Farahani et al. have implemented PSO within a system on a programmable chip framework [4]. The authors utilized a hardware implementation of the discrete version of PSO. A soft-core Altera NIOS II embedded processor was used to compute the fitness function and implemented on a Altera Stratix 1S10ES Development Kit. Performance was sacrificed in exchange for flexibility by implementing the fitness function in software.

There has been a lot of interest in hardware implementations of NNs and many different approaches have been reported in literature [5] [6] [7] [8] [9]. Several authors

One large area of interest in hardware NN implementations is how to implement the activation function efficiently. This is a difficult problem because the non-linear activation functions cannot be efficiently implemented directly in hardware. As a result, hardware NN implementations rely on circuits that approximate the activation functions. One of the most common methods is to implement a piece-wise approximation of the activation function using LUTs. This allows the designer to easily select the desired balance between precision and circuit size. Recently, authors have shown that a genetic algorithm, another component of CI, can be used to generate an optimal spline-based approximation function [12].

#### 1.2 THESIS OBJECTIVE

The PSO algorithm is a SI technique that has been used in a number of optimization problems. NNs are another important CI paradigm which can be used to approximate arbitrary functions. Both of these techniques are primarily implemented in software because developing hardware implementations is more difficult. However, to achieve the highest performance hardware implementations of the techniques are required. The focus of this thesis is to present the high-performance hardware implementations of these techniques on a FPGA platform.

#### 1.3 THESIS OVERVIEW

This thesis is organized into four sections. Section 2 introduces the PSO algorithm and the developed FPGA hardware implementation. Simulation results are provided for two benchmark problems and the hardware PSO is compared to a software implementation of PSO. Section 3 introduces NNs and the developed FPGA hardware implementation. Simulation results are provided and the FPGA NN is

compared to a software NN. Section 4 concludes the thesis and provides possible directions for improvement and future research.

#### 1.4 CONTRIBUTIONS OF THIS THESIS

In this thesis, the follow contributions have been made:

- The PSO algorithm has been implemented directly as a digital hardware design

- The hardware PSO design does not require a processor and can execute independently of any other digital hardware

- The hardware PSO design is implemented on the Xilinx Virtex-II Pro FPGA

- A high-level model that can be used to build hardware NNs in has been developed.

- The hardware NN model is implemented on the Xilinx Virtex-II Pro FPGA

#### 1.5 RESEARCH PUBLICATIONS

A Computer DESign (CDES) conference paper has been published based on the hardware PSO implementation presented in this thesis [13]. In addition, a submission to the International Joint Conference on Neural Networks (IJCNN) 2010 will be prepared based on the hardware NN implementation presented [14].

#### 1.6 SUMMARY

In this Section an introduction to CI and FPGAs has been presented. Also, the objectives of this work and an overview of the thesis has be presented.

#### 2 IMPLEMENTATIONS OF PSO ALGORITHM

#### 2.1 INTRODUCTION

Adaptive systems have become a large area of interest since many systems operate in changing, unpredictable environments. Evolutionary Algorithms (EAs) are well suited for adapting the behavior of many adaptive systems because of their simplicity; EAs only require a fitness function to provide a measure of the systems behavior. Many different variations of EAs for adapting system behavior have been extensively explored. In principle, all EAs are population-based optimization algorithms. The population consists of candidate solutions to the problem being studied and during each iteration of the algorithm a series of operators are applied to the population. After the population has been passed through the operators, the candidate solutions are evaluated and given a level of fitness that represents their degree of performance for the problem being studied. Each of the operators are based on evolution and play a role in combining and randomly modifying portions of the population. As the fitness of candidate solutions play a role in what solutions are selected to combine and modify, the population as a whole improves over time. PSO is another populationbased algorithm which begins with a population of potential solutions and continually evolves the solutions until they reach a desired level of fitness [15]. While EAs and PSO are similar, PSO requires fewer operations. This is important for real-time applications where speed is critical.

PSO is a swarm intelligence based optimization algorithm that has been shown to perform very well for a large number of applications. While PSO has been applied in a large number of applications, PSO is typically executed in software. Recently, there has been interest in using PSO for real-time applications [16] [17]. However, in order to meet the time constraints of some real-time applications, PSO must be executed directly in hardware.

#### 2.2 PARTICLE SWARM OPTIMIZATION

The PSO algorithm was developed by Kennedy and Eberhart and is based on the social behavior of bird flocking [15]. Each particle in the population has a position vector which represents a potential solution to the problem. The particles are initialized to random positions throughout the search space and for each iteration of the algorithm a velocity vector is computed and used to update each particles position. Each particles velocity is in influenced by the particles own experience as well as the experience of its neighbors. There are two basic variants of PSO, local and global. In this study the more common global version of the PSO algorithm is applied.

The population consists of N particles. For each iteration, a cost function f is used to measure the fitness of each particle i in the population. The position of each particle i is then updated, which is influenced by three terms, the particles velocity from the last iteration, the difference between the particles known best position and the particles current position, and the difference between the swarms best known position and the particles current position. The latter two terms are each multiplied by a uniform random number in [0,1] to randomly vary the in influence of each term, as well as an acceleration coefficient to scale and balance the in influence of each term. The best position each particle attained is stored in the vector  $p_i$ , also known as pbest, while the best position attained by any particle in the population is stored in the vector  $p_g$ , also known as gbest. The velocity vector  $v_i$  for each particle is then updated:

$$v_i^{t+1} = w \cdot v_i^t + c_1 r_1 \cdot (p_i^t - x_i^t) + c_2 r_2 \cdot (p_g^t - x_i^t)$$

(2.1)

where w,  $c_1$  and  $c_2$  are positive and  $r_1$  and  $r_2$  are uniformly distributed random numbers in [0,1]. The inertia coefficient, w is used to keep the particles moving in the same direction they have been traveling. The value for w is typically in [0,1]. The term  $c_1$  is called the cognitive acceleration term and  $c_2$  is called the social acceleration term. These two values balance the influence between the particles own best performance and that of the population. The velocity is constrained between the parameters  $V_{min}$  and  $V_{max}$  to limit the maximum change in position in Equation 2.2.

$$v_i^{t+1} = \begin{cases} v_{Max} & \text{if } v_i^{t+1} > V_{max} \\ v_{Min} & \text{if } v_i^{t+1} < V_{min} \\ v_i^{t+1} & \text{else} \end{cases}$$

(2.2)

The position of each particle is then updated using the new velocities in Equation 2.3.

$$x_i^{t+1} = x_i^t + v_i^{t+1} (2.3)$$

The position in each dimension is limited between the parameters  $X_{min}$  and  $X_{max}$  in Equation 2.4.

$$x_i^{t+1} = \begin{cases} x_{Max} & \text{if } x_i^{t+1} > X_{max} \\ x_{Min} & \text{if } x_i^{t+1} < X_{min} \\ x_i^{t+1} & \text{else} \end{cases}$$

(2.4)

The psuedocode for PSO is listed in Algorithm 1.

#### Algorithm 1 PSO

```

Initialize the positions, velocities, pbest and gbest values repeat

for i=1 to NUM_PARTICLES do

if f(x_i) \leq f(p_i) then

p_i \leftarrow x_i

if f(x_i) \leq f(p_g) then

p_g \leftarrow x_i

end if

for j=1 to NUM_DIMENSIONS do

v_{ij}^{t+1} \leftarrow w \cdot v_{ij}^t + c_1 r_1 \cdot (x_{ij}^t - p_{ij}^t) + c_2 r_2 \cdot (x_{ij}^t - p_{gj}^t)

v_{ij}^{t+1} \in (V_{min}, V_{max})

x_{ij}^{t+1} \leftarrow x_{ij}^t + v_{ij}^{t+1}

x_{ij}^{t+1} \in (X_{min}, X_{max})

end for

end for

until maximum iterations reached

```

#### 2.3 PSO HARDWARE IMPLEMENTATION

Software implementations of PSO often use floating point values. However, floating-point operations typically require several times the number of logic resources for a similar fixed-point operation. In addition, it is common for FPGAs to include a number of embedded multipliers which can be used to perform fixed-point multiplications without using any of the FPGAs programmable logic. For these reasons, the hardware PSO implementation uses the fixed-point representation for all values.

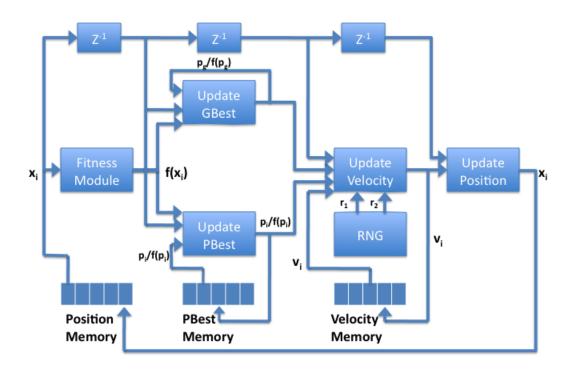

For hardware implementation, the PSO algorithm is decomposed into five operations that are performed on each particle: evaluate the fitness, update the particle's best position, update the global best position, update the velocity and update the position. Each of these five operations are implemented in a separate hardware module. It should be noted that the constraints in Equations 2.2 and 2.4 are not directly implemented; the results of the fixed-point arithmetic operations for Equations 2.1 and 2.3 are set to saturate which will indirectly constrain the values based on their width. Since updating the *pbest* and *gbest* can be performed in parallel, the five operations can be organized in a 6-stage pipeline, including the initial fetch and final write stages. The flow for an execution of a single particle is described as follows.

In the first stage, the position for particle i,  $x_i$  is fetched from memory. Then in the second stage, the fitness module computes the fitness,  $f(x_i)$  based on the position of particle i. The current pbest values,  $p_i$  and  $f(p_i)$  are also fetched from pbest memory. In the third stage, the gbest and pbest are updated. Both the update gbest and pbest modules are passed  $x_i$  and  $f(x_i)$ . In addition, the update pbest module is passed  $p_g$  and  $f(p_g)$ . Each module selects the lowest fitness and associated positions for their output, which are the now updated gbest and pbest. In addition, the old velocity,  $v_i$  is fetched from the velocity memory. Now in the fourth stage of the pipeline, the new  $p_i$  and  $f(p_i)$  are stored in the pbest memory. The update velocity module uses  $v_i$ ,  $v_i$ ,

are simply represented as 5-element registers; the hardware which stores the values could as simple as registers or as large as dynamic RAM.

Figure 2.1. PSO hardware implementation with 6-stage pipeline.

2.3.1 The Hardware Velocity Update. In PSO, the velocity update equation involves the largest number of arithmetic operations. As shown in Equation 2.1, there are five multiplications, two additions and two subtractions. In hardware, multiplications require a large amount of logic and are usually to be avoided. Since the inertia, w is typically set to 0.8, the first term of the velocity update can be simplified in two different ways. The first is to replace the term with an arithmetic shift to the right of  $v_i^t$ . This effectively changes the inertia to 0.5 and eliminates the multiplication needed. An alternative is to remove the inertia entirely and substitute  $v_i^t$  for the first term.

The cognitive and social acceleration coefficients,  $c_1$  and  $c_2$  are typically set to 2.0. Performing arithmetic left shifts on  $r_1$  and  $r_2$  would effectively multiply each value by 2. However, since the values for  $c_1r_1$  and  $c_2r_2$  are just uniform random numbers in [0,2], the fixed-point pseudo random numbers can just be extended to fulfill the range by incorporating an additional random bit.

2.3.2 Random Number Generation. Two random numbers are needed for each velocity update. This means  $2 \times p \times i$  random numbers are required for a PSO run of p particles and i iterations. In addition, some variants of PSO require an additional random value to vary the inertia [18]. While PSO is still able to find solutions in the absence of the random influence, it is not guaranteed PSO will converge as fast or with as high quality of solutions [2] [19]. Pseudo random numbers are generated in hardware using Pseudo Random Number Generators (PRNGs). Typically, linear feedback shift registers (LFSR) and cellular automata (CA) based PRNGs are used [20]. LFSRs are simpler to implement and are used in most hardware implementations. A LFSR is shown in Figure 2.2, the left-most bit is computed based

Figure 2.2. An example of a linear-feedback shift register.

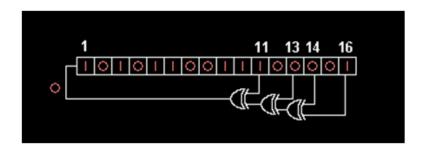

on the previous value generated and the bits in the register are shifted to the right. However, CA-based PRNGS have been shown to offer better statistical properties. In this work, a neighborhood-of-four CA-based PRNG is used [21]. The neighborhood-of-four CA-based PRNG is selected for this work because it offers efficiency in FPGA hardware implementation as well as good statistical properties. The PRNG is organized into a grid of 8x8 cells, where each cell represents a register storing one bit and each cell receives the value from the cell above, to the left, to the right and below.

The 8x8 PRNG structure is shown in Figure 2.3. The new value of each cell is found using a 4-input LUT, which is shown in Table 2.1. This implementation is efficient for FPGA implementation because the FPGA utilized in this work, the Xilinx Virtex-II Pro, uses 4-input LUTs to implement logic functions. Therefore, implementing the neighborhood-of-four CA-based PRNG only requires one LUT and D-type flip-flop per PRNG bit. To extract the generated number from the PRNG, the bit of each cell is concatenated together into a bit-string. As there are 64 cells, the PRNG produces a pseudorandom 64-bit string each cycle.

Figure 2.3. The structure of the neighborhood-of-four PRNG.

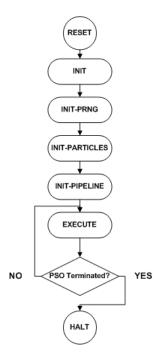

2.3.3 Control Module. The control module is used to initialize the memory and generate the control signals for the modules. Upon reset the control module enters an *Init* state which is used to initialize the counters to their respective starting states. The control module then enters an *Init-PRNG* state to initialize the

Table 2.1. The values for the LUT in each PRNG cell.

| $x_0x_1x_2x_3$ | f |

|----------------|---|

| 0000           | 0 |

| 0001           | 1 |

| 0010           | 1 |

| 0011           | 1 |

| 0100           | 0 |

| 0101           | 0 |

| 0110           | 1 |

| 0111           | 0 |

| 1000           | 1 |

| 1001           | 1 |

| 1010           | 0 |

| 1011           | 1 |

| 1100           | 1 |

| 1101           | 0 |

| 1110           | 0 |

| 1111           | 0 |

|                |   |

PRNG. The *Init-Particles* state cycles through the particles and sets each particles initial position, velocity and *pbest* position to a random value from the PRNG. The *gbest* position is initialized in the same manner. The next state, *Init-Pipeline* is used to prepare the module inputs. The *Execute* state is responsible for shifting each particle through the pipeline and properly passing the modules the correct particles information from memory while storing each particles new values as they are updated. Upon either reaching a defined fitness or number of iterations, the *Halt* state is entered and execution halts. The hardware PSO flowchart is shown in Figure 2.4.

#### 2.4 RESULTS

All of the modules in the hardware PSO design have been designed in VHDL. The hardware PSO design has been simulated and implemented on the Xilinx Virtex-II Pro development platform [22]. In order to assess the performance of the hardware PSO implementation, the hardware implementation is compared to a software implementation developed in Matlab. The Matlab PSO implementation is executed on

Figure 2.4. The hardware PSO execution flowchart.

a 2.16 GHz Intel Core 2 Duo-based PC with 4 GB RAM. First, the performance of the two implementations is compared with respect to the lowest fitness that the implementation of able to achieve for the benchmark problems. Then the execution speed of the two implementations is compared. Finally, the logic requirements for the hardware implementation are discussed.

Two well-known benchmark optimization problems [23] have been selected for comparing the two implementations. The first benchmark problem is the sphere function:

$$f(x) = \sum_{i=1}^{n} x_i^2 \tag{2.5}$$

The second benchmark problem is the Rosenbrock function:

$$f(x) = \sum_{i=1}^{n-1} 100(x_{i+1} - x_i^2)^2 + (x_i - 1)^2$$

(2.6)

The surface of the sphere and Rosenbrock fitness functions are shown in Figures 2.5 and 2.6, respectively. The sphere function is a simple unimodal function that is

typically used to test local optimizers. The Rosenbrock function is multimodal for n of 4 and higher and is more difficult to optimize. These functions are often used to assess the performance of EAs.

Figure 2.5. A two-dimensional view of the sphere benchmark problem fitness surface.

Both the hardware and software PSO implementations are executed for 1000 iterations, with 20 particles. The achieved fitness for the hardware and software implementations of PSO on the benchmark problems is listed in Table 2.2. The execution time for the software and hardware PSO implementations iterations is listed in Table 2.3. A comparison of the fitness with respect to iteration, between the hardware and software PSO for the 10-dimensional sphere function is shown in Figure 2.7. In addition, a comparison of the fitness with respect to iteration, between the hardware and software PSO for the 10-dimensional Rosenbrock function is shown in Figure 2.8 The total execution time for the hardware PSO design can be computed as follows. After the sixth clock cycle the first particle has finished its first iteration of PSO. All particles must pass through the hardware PSO pipeline for each full iteration of PSO to be completed. Therefore, in an additional nineteen clock cycles, the 20th particle has finished, completing the first iteration of PSO. As the throughput is one

Figure 2.6. A two-dimensional view of the Rosenbrock benchmark problem fitness surface.

particle per clock cycle and each particle must pass through 1000 times, the execution time is computed as:

$$T_{total} = \frac{1}{f_{clk}} (5 + 20 \times 1000) \tag{2.7}$$

where  $f_{clk}$  is the clock frequency of the PSO hardware. However, two factors can restrict the maximum clock frequency. The more mathematical operations the fitness function requires, the more time is required for the fitness module to compute the fitness. This means it will require more time to compute the fitness for the Rosenbrock function than the sphere function. In addition, as the number of dimensions increase, the number of mathematical operations required to compute the fitness increases. The utilization for Xilinx Virtex-II Pro FPGA and maximum clock frequencies are shown in Table 2.4. Since the fitness function is implemented in hardware, as the complexity of the fitness function increases, so does the number of LUTs required to implement the function in the FPGA.

| Table 2.2    | Achievred | fitness | ofter | 1000 | itorations | $f_{Or}$ | benchmark | problems  |

|--------------|-----------|---------|-------|------|------------|----------|-----------|-----------|

| rable $z.z.$ | Acmeved   | nuness  | anter | TOOU | neramons   | 101      | Dencimark | problems. |

| Problem    | n  | Software PSO Fitness | Hardware PSO Fitness |

|------------|----|----------------------|----------------------|

|            | 1  | 0.00                 | 0.00                 |

| Sphere     | 5  | 0.00                 | 0.00                 |

|            | 10 | 0.073                | 0.001                |

|            | 2  | 0.00                 | 0.00                 |

| Rosenbrock | 5  | 0.044                | 0.085                |

|            | 10 | 8.081                | 8.615                |

Table 2.3. Execution time for software and hardware PSO implementations.

| Problem    | n  | Software PSO Time      | Hardware PSO Time    |

|------------|----|------------------------|----------------------|

|            | 1  | 2.07  sec.             | $200~\mu s$          |

| Sphere     | 5  | 5.79  sec.             | $338~\mu \mathrm{s}$ |

|            | 10 | $10.99  \mathrm{sec.}$ | $392~\mu \mathrm{s}$ |

|            | 2  | 2.14 sec.              | $344~\mu s$          |

| Rosenbrock | 5  | 5.95  sec.             | $444~\mu \mathrm{s}$ |

|            | 10 | $10.91  \mathrm{sec.}$ | $800~\mu \mathrm{s}$ |

Figure 2.7. The hardware PSO compared with a software PSO for the sphere function of 10 dimensions.

Figure 2.8. The hardware PSO compared with a software PSO for the Rosenbrock function of 10 dimensions.

Table 2.4. Hardware PSO logic requirements for the benchmark problems.

| Problem    | n  | Logic Utilization | LUTs  | Clock   |

|------------|----|-------------------|-------|---------|

|            | 1  | 1118              | 1523  | 100 MHz |

| Sphere     | 5  | 4744              | 10631 | 59 MHz  |

|            | 10 | 9249              | 20873 | 51 MHz  |

|            | 2  | 2244              | 5332  | 58 MHz  |

| Rosenbrock | 5  | 5228              | 12513 | 45 MHz  |

|            | 10 | 9940              | 25750 | 25 MHz  |

#### 3 IMPLEMENTATION OF NEURAL NETWORK

#### 3.1 INTRODUCTION

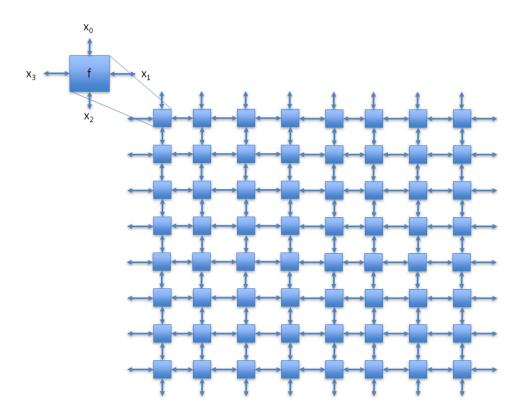

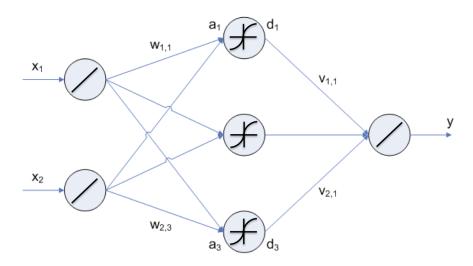

NNs are universal function approximators. The structure of a multilayer perceptron, which is used in this thesis work, is given in Figure 3.1. This network has two inputs, three hidden neurons, and one output. The input and output layers are linear, while the hidden layer uses the hyperbolic tangent function. The vector w contains the weights for the input layer while the vector v contains the weights for the hidden layer. The output of the network is computed as follows:

$$a_{i} = \sum_{j=1}^{nI} w_{i,j} x_{j,i}, i = 1, ..., nH$$

$$d_{i} = \frac{e^{a_{i}} - e^{-a_{i}}}{e^{a_{i}} + e^{-a_{i}}}, i = 1, ..., nH$$

$$y = \sum_{i=1}^{nH} v_{i} d_{i}$$

(3.1)

where nH and nI are the number of hidden neurons and inputs, respectively.

Figure 3.1. An NN with an input, hidden and output layer.

NNs are inherently parallel, with each layer of neurons processing incoming data independently of each other. While general purpose processors have reached impressive processing speeds, they still cannot fully exploit this inherent parallelism due to their sequential architecture [24]. In order to achieve the high neural network throughput need for real-time applications, a custom hardware design is needed.

There are different ways to exploit the parallelism of NNs in hardware. For instance, each neuron in a given layer can be processed in parallel; this results in one layer being processed at a given movement. As an alternative, each of the layers could be processed simultaneously. In this design each of the neurons would be processed simultaneously. In terms of performance, the latter would yield the greatest throughput, however, logic resources on the FPGAs is limited. The most costly operation in computing an NN output is multiplication, for an NN with I inputs, H hidden neurons and O outputs,  $I \times H + H \times O$  multiplications are required. The FPGA resources required for a single multiplication operation are dependent on the width of the multiplication, i.e. a 8-bit by 8-bit multiplication or a 12-bit by 12-bit multiplication. In addition to the resources required for the multiplications, the activation function must be implemented on the FPGA. The activation function is typically a non-linear function such as the hyperbolic tangent:

$$f(x) = \frac{e^x - e^{-x}}{e^x + e^{-x}} \tag{3.2}$$

which requires two exponentials,  $e^x$  and  $e^{-x}$  to be computed. These operations would also require a large amount of FPGA resources and computing them directly is usually avoided as a result. An alternative is to compute a linear piece-wise approximation and program it into the LUTs on the FPGA. Although the approximations will lose some precision the LUTs can be accessed in a single clock cycle which is far faster than computing the real solution, in addition to consuming far less FPGA resources.

#### 3.2 DESIGN APPROACH

Although hardware implementations of NNs offer the best performance, software implementations are far more common. As stated in Section 1, the hardware implementations are more difficult to design. More importantly, its more difficult for engineers without digital system design backgrounds to learn how to quickly develop digital systems. Typically designing a digital system requires experience with a hardware description language (HDL) such as VHDL or Verilog.

Xilinx System Generator is a software tool for modeling and designing FPGA-based systems in MathWorks Simulink [25]. This tool presents a high level abstract view of the whole system, yet automatically maps the system to a faithful hardware implementation. System Generator allows hardware designers to design high-performance, high-level DSP systems using custom Simulink blocks. Designers can use the System Generator blocks to build a hardware system, simulate the system using Simulink and produce a bit file which can then be programmed onto a FPGA. Since Simulink is tightly integrated with MathWorks MATLAB, it becomes easier to implement complex algorithms in hardware than purely using a HDL. Furthermore, System Generator allows blocks designed using an HDL to be imported and simulated within a system designed using System Generator.

As stated in Section 3.1, NNs require a large number of multiplications and the multiplication operation is very resource consuming when implemented on a FPGA. This places a constraint on the size of the neural network; even if LUTs are used for activation computation, the FPGA must be able to provide two multipliers per neuron. Due to this constraint, a multiplier-rich FPGA platform has been selected, the Xilinx Virtex-II Pro Development System. The Virtex-II Pro boasts 136 18-bit embedded multipliers, two embedded PowerPC processors and 30,000 programmable logic cells [22]. The Virtex-II is targeted at high-performance DSP and research applications and is well suited for a FPGA-based NN implementation.

#### 3.3 NN HARDWARE IMPLEMENTATION

The following sections discuss the design of the FPGA-based NN.

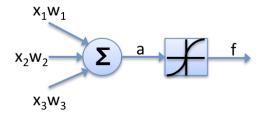

**3.3.1 Implementing the Neuron MAC.** The neurons are the essential components of NNs. In a feedforward NN, each neuron receives the output of each neuron in the preceding layer. The neuron model is shown in Figure 3.2. The *activatation* of a neuron is the sum of the neurons inputs multiplied by their corresponding

weights:

$$a = \sum_{i=0}^{N} x_i \cdot w_i \tag{3.3}$$

where  $x_i$  is the output of the *i*th neuron in the preceding layer and  $w_i$  is the corresponding weight. This is known as performing a Multiply ACcumulate (MAC) operation. Each neuron has an *activation function*, such as the hyperbolic tangent function. The output of the neuron is found by applying the activation function to the activation of the neuron.

Figure 3.2. A diagram of the neuron model.

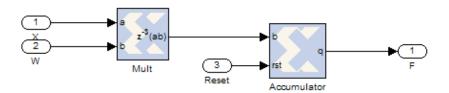

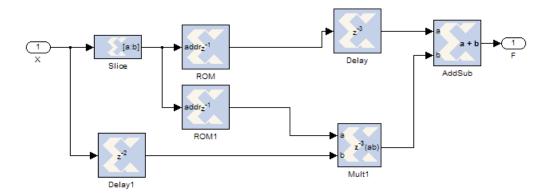

The MAC operation is modeled using a multiply and accumulate block. The MAC subsystem is provided an input x, the corresponding weight w and a reset signal. The reset signal is used to reset the accumulator to 0 when all the pairs of inputs and weights have been processed. The MAC subsystem is illustrated in Figure 3.3.

Figure 3.3. MAC hardware subsystem.

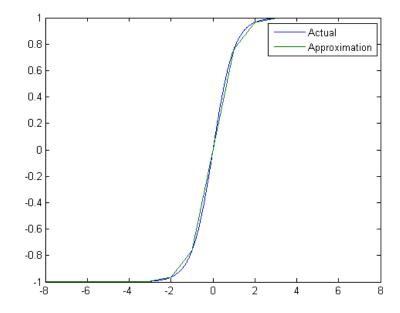

**3.3.2** Implementing the Activation Function LUT. As discussed in Section 3.1, the activation function is approximated using a LUT-Based Activation Function (LUTAF) module. The activation functions need to be approximated, using a simple linear function:

$$f(x) = \alpha_2 + c_2 * x \tag{3.4}$$

where x is the activation of the neuron and  $\alpha_1$  and  $\alpha_2$  are LUT constants. To solve for the constants, the interval over which the approximations will hold must be determined. In this thesis, the interval was selected to be  $x \in [-8, 7]$ . The number of linearized intervals also needs to be determined (as a power of two). In this thesis, the number of subintervals was selected to be  $2^4 = 16$ . The linearized regions can be found in Table 3.1. Now, the values for  $\alpha_1$  and  $\alpha_2$  must be computed for the given activation function, the approximated interval and the respective number of subintervals. In this thesis the hyperbolic tangent activation function was used. Therefore, to compute  $\alpha_1$  and  $\alpha_2$  for a given region the following system must be solved:

$$\alpha_1 + \alpha_2 * L = \frac{e^U - e^{-U}}{e^U + e^{-U}} \tag{3.5}$$

$$\alpha_1 + \alpha_2 * U = \frac{e^L - e^{-L}}{e^L + e^{-L}} \tag{3.6}$$

where L is lower boundary in the subinterval and U is the upper boundary in the subinterval. Solving for  $\alpha_1$  and  $\alpha_2$  using Matlab's Symbolic Math toolbox results in:

$$\alpha_1 = \frac{L * e_U - U * e_U * e_L + L * e_U * e_L + U + e_L * L - L + U * e_L}{-U - U * e_U - U * e_L - U * e_U * e_L + L + L * e_U * e_L * L + L * e_U * e_L}$$

(3.7)

$$\alpha_2 = \frac{2 * (e_U - e_L)}{-U - U * e_U - U * e_L - U * e_U * e_L + L + L * e_U + e_L * L + L * e_U * e_L}$$

(3.8)

where  $e_U$  and  $e_L$  are constants which equal  $e^{-2*U}$  and  $e^{-2*L}$ , respectively. The values for  $\alpha_1$  and  $\alpha_2$  are now computed for each subinterval using these solutions. The resulting values for this work can be found in Table 3.1. The resulting approximation is shown in Figure 3.4.

Table 3.1. The values for the hyperbolic tangent activation Function LUT where  $x \in [L, U]$ .

| L  | U  | $\alpha_1$   | $lpha_2$    |

|----|----|--------------|-------------|

| 6  | 7  | 0.99992      | 1.0625e-005 |

| 5  | 6  | 0.99952      | 7.8507e-005 |

| 4  | 5  | 0.99701      | 0.0005799   |

| 3  | 4  | 0.98223      | 0.0042745   |

| 2  | 3  | 0.90197      | 0.031027    |

| 1  | 2  | 0.55916      | 0.20243     |

| 0  | 1  | -2.2204e-016 | 0.76159     |

| -1 | 0  | 0            | 0.76159     |

| -2 | -1 | -0.55916     | 0.20243     |

| -3 | -2 | -0.90197     | 0.031027    |

| -4 | -3 | -0.98223     | 0.0042745   |

| -5 | -4 | -0.99701     | 0.0005799   |

| -6 | -5 | -0.99952     | 7.8507e-005 |

| -7 | -6 | -0.99992     | 1.0625e-005 |

| -8 | -7 | -0.99999     | 1.438e-006  |

The hardware implementation of the LUTAF is constructed from three main elements, the memory element which contains the linearized constants  $\alpha_1$  and  $\alpha_2$ , a multiplier and an addition unit. The LUTAF subsystem can be found in Figure 3.5. The proper subinterval is determined by selecting the upper k most significant bits of the input, x, where  $2^k$  is the number of subintervals. The upper k bits are used to index the corresponding values of  $\alpha_1$  and  $\alpha_2$  by using the k bits as the address to the memory elements. The values for  $\alpha_2$  and x are passed to a multiplier while  $\alpha_1$  is latched (delayed to match the propagation of the signal  $(\alpha_2 \times x)$ ). Finally, the terms  $(\alpha_2)$  and  $(\alpha_2 \times x)$  are added to produce the activation function approximation.

3.3.3 Implementing the Complete Hardware Neuron. The hardware neuron is a combination of the Neuron MAC (Section 3.3.1) and the LUTAF (Section 3.3.2) and a memory element to store the weights. The complete hardware neuron

Figure 3.4. LUTAF approximation.

Figure 3.5. LUTAF approximation subsystem.

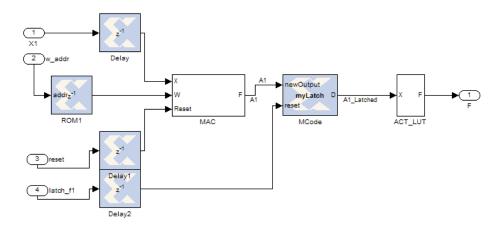

subsystem can be seen in Figure 3.6. The hardware neuron receives the values x,  $w\_addr$ , reset and  $latch\_f$ . The input x is the value of the current input being processed (i.e. from the preceding neuron i). The value of  $w\_addr$  is the index of the current input being processed, i. This signal is used to index the value of the corresponding weight in the memory element. The reset signal is used to reset the MAC as explained

in Section 3.3.1. The latch\_f signal is used to indicate when the output of the MAC is valid and should be latched (since the MAC sequentially accumulates values, the values other than the last are incomplete sums). The latch  $my\_latch$  is responsible for latching the result of the MAC when its valid, based on the latch\_f signal. The latched output from the MAC is connected to the input to the LUTAF subsystem which computes the approximated activation function output.

Figure 3.6. The complete hardware neuron.

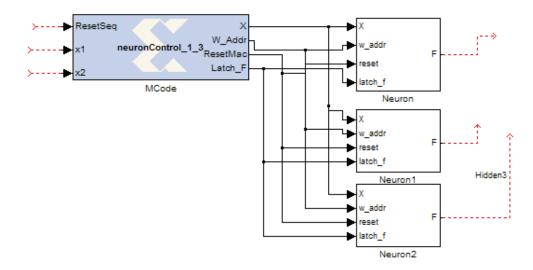

3.3.4 Implementing the NN Layer Control Block. As the hardware neurons process the input/weight pairs sequentially, a mechanism is needed to cycle through each of the outputs from the previous layer and provide them to the hardware neurons in the respective current layer. The LCB (Layer Control Block) receives the outputs from the neurons in the previous layer as well as a global reset signal. The LCB is responsible for providing the value of the current input being processed, the index of the current input, the MAC reset and latch signals to the hardware neurons. Since the hardware neurons process each input/weight pair in parallel, each hardware neuron receives the same signals. The LCB is implemented as a finite state machine. The finite state machine for a layer receiving two inputs with three neurons is illustrated in Figure 3.7, while the LCB and hardware neurons are shown in Figure 3.8. The operation of a hardware neuron being controlled by a LCB can be seen in Figure 3.9.

```

function [X, W Addr, ResetMac, Latch F] = neuronContro 1 3 (ResetSeq, x1, x2)

init = 0;

persistent state, state = x1_state(init, {xlUnsigned, 3, 0});

W Addr Width = 2;

switch double(state)

case 0

X = xfix(\{xlSigned, 18, 14\}, 0);

W_Addr = xfix({xlUnsigned, W_Addr_Width, 0}, 2);

ResetMac = xfix((xlBoolean),0);

Latch F = xfix({xlBoolean},0);

case 1

X = x1;

W_Addr = xfix({xlUnsigned,W_Addr_Width,0},0);

ResetMac = xfix({xlBoolean},1);

Latch F = xfix({xlBoolean},1);

case 2

X = x2;

W_Addr = xfix({xlUnsigned,W_Addr_Width,0},1);

ResetMac = xfix({xlBoolean},0);

Latch_F = xfix({xlBoolean},0);

case 3

X = 0;

W Addr = xfix((xlUnsigned, W Addr Width, 0), 2);

ResetMac = xfix({xlBoolean},0);

Latch F = xfix({xlBoolean},0);

case 4

x = 0;

W_Addr = xfix({xlUnsigned, W_Addr_Width, 0}, 2);

ResetMac = xfix((xlBoolean),0);

Latch F = xfix({xlBoolean},0);

otherwise

x = 0;

W_Addr = xfix({xlUnsigned, W_Addr_Width, 0}, 2);

ResetMac = xfix({xlBoolean},1);

Latch F = xfix({xlBoolean},0);

end

if(state == 4)

state = 0;

else

state = state + 1;

end

```

Figure 3.7. The LCB finite state machine  $(2 \times 3 \text{ Layer})$ .

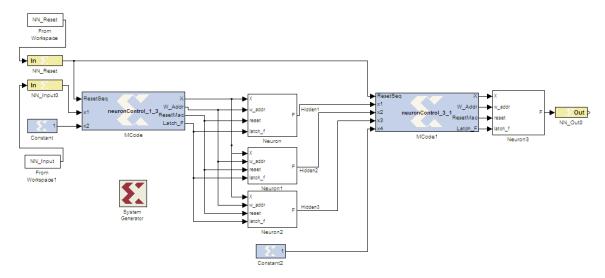

3.3.5 Implementing a Three-Layer NN. Using the components developed in Sections 3.3.3 and 3.3.4, an NN of arbitrary size can be constructed. The LCB finite state machines must have the corresponding states for the layers inputs and outputs. For a NN of size  $1 \times 3 \times 1$  (a bias is included in each layer), the hardware NN is illustrated in Figure 3.10. The inputs to the FPGA-Based NN are the global reset signal, ResetSeq which synchronize the two LCBs and the x1 signal which is the input the NN. The FPGA-Based NN produces the signal F which is the output of the NN. The Gate In and Gateway Out blocks indicate ports on the FPGA where external

Figure 3.8. A LCB controlling three hardware neurons  $(2 \times 3 \text{ Layer})$ .

signals are presented to the FPGA and received from the FPGA, respectively. The Gateway blocks are configured to specify specific I/O pins on the FPGA.

To construct a n-layer NN, (n-1) LCBs are required; the input layer does not require a LCB, only layers which contain neurons that receive input from multiple sources require a LCB. The number of neurons in each layer impact the number of the hardware resources consumed as well as the throughput of the NN. Layers that do not require a non-linear transfer function (linear layers) require less hardware resources to implement because there is no need for each neuron to have a LUTAF module. Therefore, a non-linear n-neuron hidden layer would require more hardware resources than a n-neuron linear output layer. The number of input patterns processed in a given time is strictly a function of the largest layer in the NN. In other words, a  $1 \times 10 \times 1$  NN will process the same number of input patterns as a  $5 \times 10 \times 5$  NN in a given amount of time. This is due to the fact that the LCBs must operate together, each must process the first input at the same time, one cannot begin processing a new input pattern before the other LCBs are finished for all other layers.

Figure 3.9. A hardware neuron being controlled by a LCB.

Figure 3.10. A FPGA-based NN (of size  $1\times3\times1).$

# 3.4 RESULTS

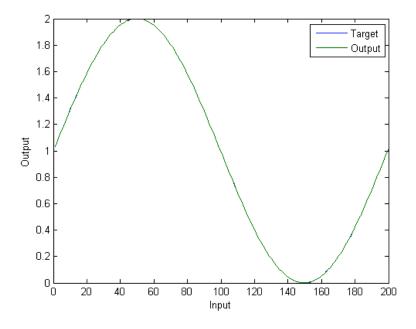

To test the FPGA-Based NN, a simple NN has been implemented to verify its operation. A NN of size  $1 \times 10 \times 1$  has been selected, utilizing the hyperbolic tangent activation function for neurons in the hidden layer and a linear activation function for the output neuron. A NN of the same architecture must first be trained in software. As an example, the following function has been selected to be approximated by the NN:

$$f(x) = \sin(5 * x) \tag{3.9}$$

In this thesis the MATLAB Neural Network is used to implement the training algorithm, however any other method could be used. The "train\_nn.m" script containing the training procedure is found in Appendix B. The results of the NN training are shown in Figure 3.11. After the weights for the NN have been determined using the training algorithm some processing needs to take place before the hardware NN can be used. First the weights need to be organized into the matrices w and v which con-

Figure 3.11. The trained NN for approximating a sin function.

tain the weights for the hidden and output layers, respectively. The Xilinx System Generator Single Port Read-Only Memory (ROM) is used in each hardware neuron to store its respective weights. The ROM in each neuron is configured to select the correct weight indices from the trained weights in the MATLAB workspace (from matrices w and v), each neuron only stores the weights it needs to compute its own output. Here the weights are converted into 18.12 fixed-point<sup>1</sup> representation when they are loaded into the ROMs.

In the second part of this process the values for the LUTAF must be loaded into each Neurons LUTAF ROM. A MATLAB script it used to solve for the values of  $\alpha_1$  and  $\alpha_2$  using the method described in Section 3.4. In order for LUTAF constants  $\alpha_1$  and  $\alpha_2$  to be used by the FPGA-Based NN, the values of the constants found in MATLAB must also be converted into 18.12 fixed-point.

Finally, the input patterns that were used for training are processed using a MATLAB script for presentation to the Xilinx System Generator Gateway In port,  $NN\_Input$ . In addition, a reset signal is prepared in the same manner for the Gateway In port  $NN\_Reset$ . These steps are performed by the script "nn\\_load.m" in Appendix B.

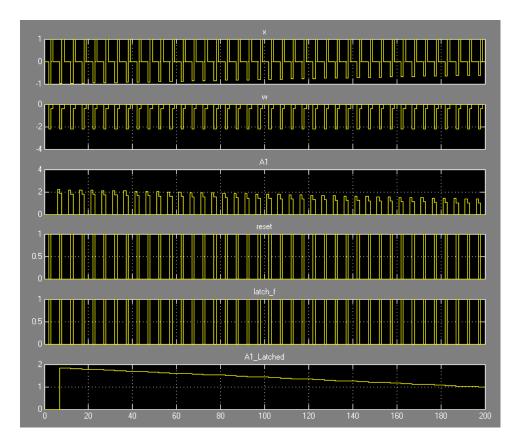

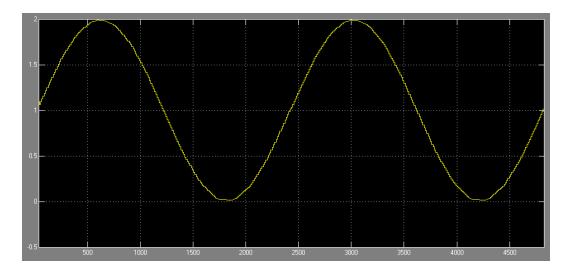

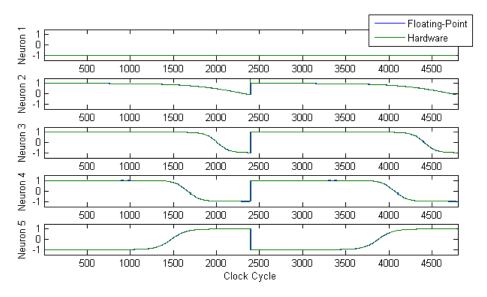

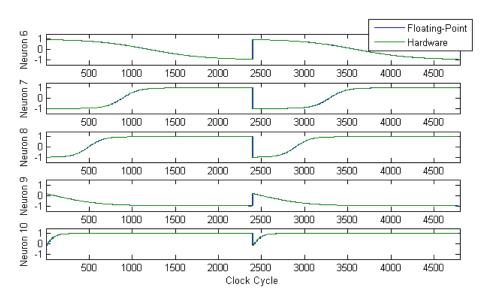

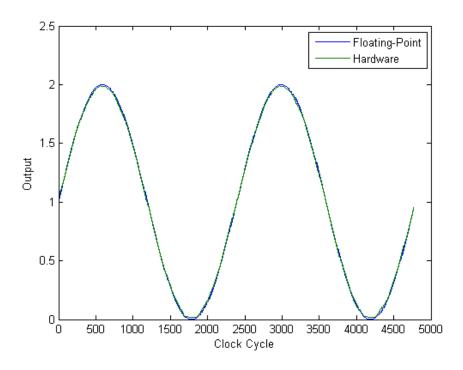

Now that the The FPGA-based NN model has of the necessary values converted and loaded, it can be simulated. The output of the Simulink simulation can be found in Figure 3.12. However, the output is in terms of clock cycles. In order to compare the hardware NN output against the software NN output, the software NN output must be upsampled. This is performed by the script "test\_nn\_model.m", in Appendix B. The output of each hardware hidden neuron is compared with the software hidden neurons in Figure 3.13. The output of the first five hidden neurons are shown in Figure 3.13(a) while the output of the last five hidden neurons are shown in Figure 3.13(b). The output of the hardware NN is compared against the software NN in Figure 3.14. The simulations presented are not high-level simulations, they are cycleaccurate simulations of the synthesized hardware NN design executing on the Xilinx Virtex-II Pro FPGA platform.

<sup>&</sup>lt;sup>1</sup>18.12 fixed-point representation indicates that a total of 18 bits are used and 12 of the bits are dedicated to the fractional portion of the value, leaving 6 bits for the integer portion of the value.

Figure 3.12. The output of the Simulink simulation of the FPGA-based NN.

The design is then synthesized using Xilinx ISE. The FPGA resources used can be found in Figure 3.15. It should be noted that the 1x10x1 hardware NN only requires approximately 6% of the Xilinx Virtex II Pro's logic resources. The critical path has a delay of 15.4 ns, resulting in a maximum clock rate of 64 MHz. Using a newer FPGA, such as the Xilinx Virtex-4 or Xilinx Virtex-5 will result in even higher clock rates. The logic utilization will vary if another FPGA is used, depending on the size of the FPGA being targeted.

(a) The output of hidden neurons 1-5.

(b) The output of hidden neurons 6-10.

Figure 3.13. Comparing the output of hidden neurons of the FPGA-based NN and Matlab-based NN.

Figure 3.14. Comparing the output of the FPGA-based NN and Matlab-based NN.

| Device Utilization Summary                     |       |           |             | Н       |

|------------------------------------------------|-------|-----------|-------------|---------|

| Logic Utilization                              | Used  | Available | Utilization | Note(s) |

| Number of Slice Flip Flops                     | 1,388 | 27,392    | 5%          |         |

| Number of 4 input LUTs                         | 1,701 | 27,392    | 6%          |         |

| Logic Distribution                             |       |           |             |         |

| Number of occupied Slices                      | 1,245 | 13,696    | 9%          |         |

| Number of Slices containing only related logic | 1,245 | 1,245     | 100%        |         |

| Number of Slices containing unrelated logic    | 0     | 1,245     | 0%          |         |

| Total Number of 4 input LUTs                   | 1,701 | 27,392    | 6%          |         |

| Number used as logic                           | 1,312 |           |             |         |

| Number used as Shift registers                 | 389   |           |             |         |

| Number of bonded IOBs                          | 36    | 416       | 8%          |         |

| Number of RAMB16s                              | 20    | 136       | 14%         |         |

| Number of MULT18X18s                           | 21    | 136       | 15%         |         |

| Number of BUFGMUXs                             | 1     | 16        | 6%          |         |

| Number of RPM macros                           | 21    |           |             |         |

Figure 3.15. The hardware resources used for the  $1\times10\times1$  NN on the Xilinx Virtex-II Pro FPGA.

# 4 CONCLUSIONS AND FUTURE WORK

This thesis has presented two independent hardware designs, a hardware implementation of the PSO algorithm and a hardware implementation of an NN.

A pipelined hardware implementation of PSO has been presented. The hardware PSO design implemented on a Xilinx Virtex-II Pro FPGA is shown to perform well on two standard benchmark problems when compared to a common software implementation of PSO in Matlab. When compared to the software implementation, the hardware implementation is between 6,220 - 28,935 times faster. The system is targeted for real-time applications where minimizing PSO execution time is critical. One such application is real-time neural network training.

A high-performance Xilinx Virtex-II Pro FPGA-based NN architecture has been presented. The system allows feed-forward NNs to be implemented on FPGAs resulting in very high throughput. The hardware NN is developed using a model-based methodology which is easier for researchers who are not knowledgeable in a HDL to modify for their specific application.

The PSO hardware design in this thesis did not utilize any explicit memory such as RAM for storing the PSO variables<sup>2</sup>; instead, all of the variables were simply stored in registers. This approach is not the most efficient for problems which have fitness function with a large number of dimensions. Training a large NN would be such a case, where the number of weights could be in the hundreds or thousands. For these applications, the PSO hardware design presented could be augmented with a memory interface that used a RAM module to store PSO variables.

The hardware NN presented in this thesis was of the feed-forward architecture. None of the outputs or outputs from the hidden layer were passed back as inputs to the NN. These recurrent architectures have been shown to offer more capabilities for approximating problems with temporally related data. The hardware NN design presented here could be extended to incorporate recurrent architectures by modifying the LCBs.

<sup>&</sup>lt;sup>2</sup>While FPGAs utilize memory components as LUTs to implement logic functions, they also have a number of block RAMs available that are more area-efficient for storing large amounts of data.

# APPENDIX A HARDWARE PSO SOURCE CODE

The main portions of the VHDL source code developed for the hardware PSO implementation has been selected for inclusion in this appendix for reference. All of the VHDL source code was compiled and simulated using Mentor Graphics ModelSim 6.5. The source code was synthesized using Xilinx ISE 10.1.

### PSO. vhd

```

1 library IEEE;

2 use IEEE.STD_LOGIC_1164.ALL;

3 use IEEE.STD_LOGIC_ARITH.ALL;

4 use IEEE.STD_LOGIC_UNSIGNED.ALL;

6 LIBRARY ieee_proposed;

7 USE ieee_proposed.math_utility_pkg.ALL;

8 USE ieee_proposed.fixed_pkg.ALL;

9

10 USE WORK. pso_package .ALL;

11

12 --- Uncomment the following library declaration if instantiating

13 --- any Xilinx primitives in this code.

14 - library UNISIM;

15 — use UNISIM. VComponents. all;

16

17 entity PSO is

18

PORT(

19

SYSTEM_CLK : in std_logic;

20

SWITCHES: in STD_LOGIC_VECTOR(1 downto 0);

21

LEDS: out STD_LOGIC_VECTOR(1 downto 0);

22

GBEST: out STD_LOGIC_VECTOR(7 downto 0)

23

);

24 end PSO;

25

26 architecture Behavioral of PSO is

27

28

signal DCM_IBUFG_OUT, DCM_CLK0_OUT, DCMLOCKED : std_logic;

29

signal clk : std_logic;

30

signal gbest_position : total_position;

signal gbest_fitness : sfixed (FITNESS_BITS_LEFT downto -

31

FITNESS_BITS_RIGHT);

32

signal PSO_reset , PSO_finished : std_logic;

33

signal iteration : unsigned (ITERATION_COUNT_BITS-1 downto 0);

34

35

signal gbest_fitness_tmp : std_logic_vector(FITNESS_BITS_LEFT +

FITNESS_BITS_RIGHT downto 0);

```

```

36

37

COMPONENT dcm0

38

PORT(

39

CLKIN_IN : IN std_logic;

40

CLKDV_OUT : OUT std_logic;

41

CLKIN_IBUFG_OUT : OUT std_logic;

42

CLK0_OUT : OUT std_logic;

43

LOCKED_OUT : OUT std_logic

44

);

45

END COMPONENT;

46

47

COMPONENT pso_top

48

PORT (

49

clk, reset : in std_logic;

gbest : total_position;

50

51

gbest_e : out sfixed(FITNESS_BITS_LEFT downto -FITNESS_BITS_RIGHT);

52

iteration : out unsigned (ITERATION_COUNT_BITS-1 downto 0);

53

finished : out std_logic);

54

END COMPONENT:

55

56 begin

57

Inst_dcm0: dcm0 PORT MAP(

58

CLKIN_IN \Rightarrow SYSTEM_CLK,

59

60

CLKDV\_OUT \Rightarrow clk,

61

CLKIN_BUFG_OUT \Rightarrow DCM_BUFG_OUT,

CLK0\_OUT \Rightarrow DCM\_CLK0\_OUT,

62

LOCKED_OUT => DCMLOCKED

63

64

);

65

66

Inst_pso_top0: pso_top PORT MAP(

67

clk \implies clk,

68

reset => PSO_reset,

69

gbest => gbest_position,

70

gbest_e => gbest_fitness,

iteration => iteration,

72

finished => PSO_finished

73

);

74

```

```

75

PSO\_reset \le SWITCHES(0);

76

77

LEDS(0) <= NOT PSO_reset;

LEDS(1) \le NOT PSO_finished;

78

79

gbest_fitness_tmp <= to_slv(gbest_fitness);</pre>

80

81

--GBEST <= gbest_position (7 downto 0);

82

83

GBEST \le gbest\_fitness\_tmp(7 downto 0);

84

85 end Behavioral;

```

# pso\_package.vhd

```

--LIBRARY floatfixlib;

-USE floatfixlib. math_utility_pkg. ALL;

3 | -USE float fixlib.fixed_pkg.ALL;

5 LIBRARY ieee_proposed;

6 USE ieee_proposed.math_utility_pkg.ALL;

7 USE ieee_proposed.fixed_pkg.ALL;

9 PACKAGE pso_package is

constant NUM_PARTICLES : natural := 20;

10

11

constant RN_BITS : natural := 64;

constant NUM_DIMENSIONS : natural := 10;

12

13

14

constant POSITION_BITS_LEFT : natural := 7;

15

constant POSITION_BITS_RIGHT : natural := 9;

16

--constant\ FITNESS\_BITS\_LEFT:\ natural:=POSITION\_BITS\_LEFT;

17

18

--constant\ FITNESS\_BITS\_RIGHT:\ natural:=POSITION\_BITS\_RIGHT;

--constant\ FITNESS\_BITS\_LEFT\ :\ natural\ :=\ POSITION\_BITS\_LEFT\ +

19

POSITION\_BITS\_LEFT + NUM\_DIMENSIONS;

--constant\ FITNESS\_BITS\_RIGHT\ :\ natural\ :=\ POSITION\_BITS\_RIGHT\ +

20

POSITION_BITS_RIGHT;

21

constant FITNESS_BITS_LEFT : natural := 43+NUM_DIMENSIONS + 6;

22

constant FITNESS_BITS_RIGHT : natural := 36;

23

constant C_BITS_LEFT : natural := 2;

24

25

constant C_BITS_RIGHT : natural := 2;

26

27

constant R_BITS_LEFT : natural := 0;

constant R_BITS_RIGHT : natural := 9;

28

29

30

constant W_BITS_LEFT : natural := 0;

31

constant W_BITS_RIGHT : natural := 3;

32

--constant\ VELOCITY\_BITS\_LEFT:\ natural:=POSITION\_BITS\_LEFT+1+

33

R_BITS_LEFT+C_BITS_LEFT+2;

```

```

34

--constant\ VELOCITY\_BITS\_RIGHT:\ natural:=POSITION\_BITS\_RIGHT+

R\_BITS\_RIGHT+C\_BITS\_RIGHT;

constant VELOCITY.BITS.LEFT : natural := POSITION.BITS.LEFT;

35

36

constant VELOCITY_BITS_RIGHT: natural := POSITION_BITS_RIGHT+1;

37

38

constant PARTICLE_COUNT_BITS : natural := 5;

39

constant DIMENSION_COUNT_BITS : natural := 4;

40

41

constant ITERATION_COUNT_BITS : natural := 10;

constant MAX_ITERATIONS : natural := 1000;

42

43

type total_position is array (0 to NUM_DIMENSIONS-1) of sfixed(

44

POSITION_BITS_LEFT downto -POSITION_BITS_RIGHT);

type total_velocity is array (0 to NUM_DIMENSIONS-1) of sfixed(

45

VELOCITY_BITS_LEFT downto -VELOCITY_BITS_RIGHT);

46

47 END pso_package;

```

pso\_top.vhd

```

1 USE WORK. pso_package .ALL;

2 LIBRARY IEEE;

3 USE IEEE. std_logic_1164.ALL;

4 USE IEEE. numeric_std.ALL;

5

6 \left| --LIBRARY \right| floatfixlib;

7 \mid --USE \mid floatfixlib \cdot math\_utility\_pkg \cdot ALL;

8 \mid --USE \quad float fix lib. fix ed_pkg.ALL;

10 LIBRARY ieee_proposed;

11 USE ieee_proposed.math_utility_pkg.ALL;

12 USE ieee_proposed.fixed_pkg.ALL;

13

14 ENTITY pso_top IS

15

PORT (clk, reset : in std_logic;

16

gbest : out total_position;

17

gbest_e : out sfixed (FITNESS_BITS_LEFT downto -

FITNESS_BITS_RIGHT);

18

iteration : out unsigned (ITERATION_COUNT_BITS-1 downto 0);

19

finished : out std_logic);

20 END ENTITY pso_top;

22 ARCHITECTURE behavioral OF pso_top IS

23

24

-- Reset Signals

25

signal reset_modules : std_logic;

-- Signals to RNG

26

27

signal reset_rng , rng_enable : std_logic;

-- Signals from RNG

28

29

signal rn : std_logic_vector(RN_BITS-1 downto 0);

30

-- Signals to Fitness module

31

signal position_to_eval : total_position;

32

-- Signals from Fitness module to Best modules

33

signal fitness_from_eval : sfixed (FITNESS_BITS_LEFT downto -

FITNESS_BITS_RIGHT);

34

-- Signals to Best modules

35

signal position_to_best : total_position;

```

```

36

signal pbest_position , gbest_position : total_position;

37

signal pbest_fitness, gbest_fitness: sfixed(FITNESS_BITS_LEFT

downto -FITNESS_BITS_RIGHT);

-- Signals from Best modules

38

39

signal new_pbest_position, new_gbest_position: total_position;

signal new_pbest_fitness , new_gbest_fitness : sfixed(

40

FITNESS_BITS_LEFT downto -FITNESS_BITS_RIGHT);

41

-- Signals to Update Velocity module

42

signal velocity_to_update_velocity : total_velocity;

43

signal position_to_update_velocity : total_position;

44

signal rn1, rn2 : sfixed(R_BITS_LEFT-1 downto -R_BITS_RIGHT);

45

- Signals to Update Position module

46

signal new_velocity : total_velocity;

47

-- Signals from Update Ppsition module

48

49

signal new_position : total_position;

50

51

-- Particle Memory

52

type particle_position_mem is array (0 to NUM_PARTICLES-1) of

total_position;

53

type particle_velocity_mem is array (0 to NUM_PARTICLES-1) of

total_velocity;

54

type particle_fitness_mem is array (0 to NUM_PARTICLES-1) of sfixed(

FITNESS_BITS_LEFT downto -FITNESS_BITS_RIGHT);

55

signal position_mem : particle_position_mem;

56

signal velocity_mem : particle_velocity_mem;

57

58

signal pbest_position_mem : particle_position_mem;

59

signal pbest_fitness_mem : particle_fitness_mem;

60

signal gbest_position_mem : total_position;

61

signal gbest_fitness_mem : sfixed (FITNESS_BITS_LEFT downto -

FITNESS_BITS_RIGHT);

62

signal init_fitness_to : sfixed (FITNESS_BITS_LEFT downto -

FITNESS_BITS_RIGHT);

63

-- PSO Top FSM

64

65

TYPE states IS (idle, init_rng, init_particles1, init_particles2,

init_particles3 , init_pipeline1 , init_pipeline2 , exec , done);

66

signal state : states;

```

```

67

signal dimension_cnt : unsigned(DIMENSION_COUNT_BITS-1 downto 0);

68

signal particle_cnt_init : unsigned(PARTICLE_COUNT_BITS-1 downto 0);

69

signal particle_cnt_stage1 : unsigned(PARTICLE_COUNT_BITS-1 downto

(0):

signal particle_cnt_stage2 : unsigned(PARTICLE_COUNT_BITS-1 downto

70

(0);

signal particle_cnt_stage3 : unsigned(PARTICLE_COUNT_BITS-1 downto

71

0);

72

signal particle_cnt_stage4 : unsigned(PARTICLE_COUNT_BITS-1 downto

73

signal particle_cnt_stage5 : unsigned(PARTICLE_COUNT_BITS-1 downto

0);

74

signal iteration_cnt : unsigned(ITERATION_COUNT_BITS-1 downto 0);

75

signal init_rng_cnt : unsigned(4 downto 0);

76 BEGIN

77

rng: ENTITY work.RandomNumberGenerator(General)

78

PORT MAP (clk, rng_enable, reset_rng, rn);

79

80

delay_positions : for i in 0 to NUM_DIMENSIONS-1 generate

81

delay_position1 : ENTITY work.delay_position(behavioral)

82

PORT MAP (clk, position_to_eval(i), position_to_best(i));

83

delay_position2 : ENTITY work.delay_position(behavioral)

84

PORT MAP (clk, position_to_best(i), position_to_update_velocity(

i));

85

end generate delay_positions;

86

87

--fitness\_eval : ENTITY work.fitness\_dummy(behavioral)

-- PORT MAP (clk, position_to_eval, fitness_from_eval);

88

89

--fitness\_eval: ENTITY work. fitness\_squared (behavioral)

-- PORT MAP (clk, position_to_eval, fitness_from_eval);

90

91

fitness_eval : ENTITY work.fitness_rosenbrock(behavioral)

92

PORT MAP (clk, position_to_eval, fitness_from_eval);

93

94

update_pbest : ENTITY work.update_best(behavioral)

95

PORT MAP (clk, reset_modules, position_to_best, fitness_from_eval,

pbest_position, pbest_fitness,

96

new_pbest_position , new_pbest_fitness);

97

98

update_gbest : ENTITY work.update_best(behavioral)

```

```

99

PORT MAP (clk, reset_modules, position_to_best, fitness_from_eval,

new_gbest_position, new_gbest_fitness,

100

new_gbest_position , new_gbest_fitness);

101

102

pso_dimensions : for i in 0 to NUM_DIMENSIONS-1 generate

103

pso_dimension : ENTITY work.pso_dimension(behavioral)

PORT MAP (clk, reset_modules, position_to_update_velocity(i),

104

velocity_to_update_velocity(i), new_pbest_position(i),

new_gbest_position(i),

105

rn1, rn2, new_velocity(i), new_position(i)

106

);

107

end generate pso_dimensions;

108

109

iteration <= iteration_cnt;</pre>

110

PSO_main : PROCESS(clk, reset)

111

112

BEGIN

-- Go into 'idle' state upon reset

113

114

IF reset = '1' THEN

state <= idle;

115

-- Reset modules

116

117

reset_modules <= '1';

-- Reset RNG

118

reset_rng \ll '1';

119

120

rng_enable <= '0';

121

finished \ll '0';

iteration_cnt <= (others => '0');

122

123

ELSIF (clk 'EVENT AND clk = '1') THEN

124

CASE state IS

WHEN idle =>

-- Was reset

125

state <= init_rng;

126

127

particle_cnt_init <= (others => '0');

128

dimension\_cnt \ll (others \implies '0');

129

iteration_cnt <= (others => '0');

130

finished \ll '0';

-- Maximum (worst) fitness value

131

132

init_fitness_to <= (FITNESS_BITS_LEFT => '0', others => '1')

init_rng_cnt \ll (others \Rightarrow '0');

133

```

```

134

135

particle_cnt_stage1 <= (others => '0');

particle_cnt_stage2 <= to_unsigned(NUM_PARTICLES-2,

136

PARTICLE_COUNT_BITS);

particle_cnt_stage3 <= to_unsigned(NUM_PARTICLES-3,

137

PARTICLE_COUNT_BITS);

138

particle_cnt_stage4 <= to_unsigned (NUM_PARTICLES-4,

PARTICLE_COUNT_BITS);

139

particle_cnt_stage5 <= to_unsigned (NUM_PARTICLES-5,

PARTICLE_COUNT_BITS);

140

141

- Cycle through some RNG values so

WHEN init_rng =>

they are 'more random'

reset_rng \ll '0';

142

rng\_enable \ll '1';

143

144

if(init\_rng\_cnt < "11111") then

145

init_rng_cnt <= init_rng_cnt + 1;</pre>

146

else

147

state <= init_particles1;

148

end if;

149

WHEN init_particles 1 =>

- Initalize all particle

memory to random values

150

position_mem(to_integer(particle_cnt_init))(to_integer(

dimension_cnt)) <= to_sfixed(rn(POSITION_BITS_LEFT +

POSITION_BITS_RIGHT downto 0), POSITION_BITS_LEFT, -

POSITION_BITS_RIGHT);

velocity_mem (to_integer (particle_cnt_init)) (to_integer (

151

dimension_cnt)) <= to_sfixed(0, VELOCITY_BITS_LEFT, -

VELOCITY_BITS_RIGHT);

152

153

if(dimension_cnt < NUM_DIMENSIONS-1) then</pre>

154

dimension_cnt <= dimension_cnt + 1;</pre>

else

155

156

dimension\_cnt \ll (others \implies '0');

157

if(particle_cnt_init < NUM_PARTICLES-1) then</pre>

158

particle_cnt_init <= particle_cnt_init + 1;</pre>

159

else

160

particle_cnt_init <= (others => '0');

state <= init_particles2;</pre>

161

```

```

162

end if:

163

end if;

164

WHEN init_particles 2 =>

165

-- Initalize all particle

memory to random values

166

--pbest\_position\_mem(to\_integer(particle\_cnt\_init))(

to\_integer(dimension\_cnt)) <= to\_sfixed(rn(

POSITION_BITS_LEFT + POSITION_BITS_RIGHT downto 0),