# Scholars' Mine

#### Masters Theses

Student Theses and Dissertations

Fall 2013

# Communication protocols for integrated fiber optic sensor interrogator

Tameem Ahmed Khan

Follow this and additional works at: https://scholarsmine.mst.edu/masters\_theses

Part of the Computer Engineering Commons Department:

#### **Recommended Citation**

Khan, Tameem Ahmed, "Communication protocols for integrated fiber optic sensor interrogator" (2013). *Masters Theses*. 5440. https://scholarsmine.mst.edu/masters\_theses/5440

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

# COMMUNICATION PROTOCOLS FOR INTEGRATED FIBER OPTIC SENSOR INTERROGATOR

by

#### TAMEEM AHMED KHAN

#### A THESIS

Presented to the Faculty of the Graduate School of the

## MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

#### MASTER OF SCIENCE IN COMPUTER ENGINEERING

2013

Approved by

Dr. Hai Xiao (Advisor) Dr. Maciej Zawodniok Dr. Minsu Choi

#### ABSTRACT

Fiber optic sensors have gained rapid recognition in sensing environmental factors such as strain, stress, acoustics, pressure, temperature among emerging other sensing applications. Major advantages of fiber based systems are small size, light weight, multiplex-ability of sensors on a single fiber, and immunity to Radio Frequency (RF) interference. However, single most major disadvantage of such technology is that traditionally the interrogation systems are typically bulky and heavy lab only equipment. Embed-ability of sensors into different structures and environments requires that the whole systems (sensors + interrogator) be small, modular and portable.

This thesis presents such a custom Fiber optic Sensor Interrogator (FSI) based on a Low-power TMS320C6748 applications Processor (DSP) and Virtex®-5 FPGA hardware. Specific objectives for such FSI include; first, to develop a management module that could compare and set FLASH parameters for LASER Controller, second to develop robust code for data collection through a DRP2E Photo Detector, third to establish communication protocols including Serial, USB, Ethernet and Wireless (both on FSI and PC end).

#### ACKNOWLEDGMENTS

I am extremely thankful to my advisor Dr. Hai Xiao for his support and the knowledge imparted by him, which not just helped in my thesis but also in my overall development as a student. I would also like to thank him for supporting my work with graduate research assistantship.

I thank Dr. Maciej Zawodniok and Dr. Minsu Choi in having trust in me for timely completion of this work and serving on my committee.

I am thankful to my team at Photonics Technology Lab who time to time taught me basics and advanced topics in laser physics and extended their support in understanding the existing lab equipment.

I also thank my wife Adviya Saba Khan for her support on the personal end without which it would have been things would have been different for me. I also thank my mother Arifa Begum for support she extended by joining hands with us in our endeavors.

Finally, I would like to thank my fellow graduate students who always gave a helping hand when I needed one.

## TABLE OF CONTENTS

|                                               | Page |

|-----------------------------------------------|------|

| ABSTRACT                                      | iii  |

| ACKNOWLEDGMENTS                               | iv   |

| LIST OF ILLUSTRATIONS                         | viii |

| LIST OF TABLES                                | X    |

| NOMENCLATURE                                  | xi   |

| SECTION                                       |      |

| 1. INTRODUCTION                               | 1    |

| 2. SETUP                                      | 3    |

| 2.1. HARDWARE                                 | 3    |

| 2.2. SOFTWARE                                 | 8    |

| 2.2.1. Device End FPGA Setup                  | 9    |

| 2.2.2. Device End DSP Setup                   | 10   |

| 2.2.3. PC End COM Interrogation               | 11   |

| 2.2.4. PC End USB Interrogation               | 11   |

| 3. SERIAL PORT (COM)                          | 14   |

| 3.1. PURPOSE OF THE PERIPHERAL                | 14   |

| 3.2. OVERVIEW OF FEATURES                     | 14   |

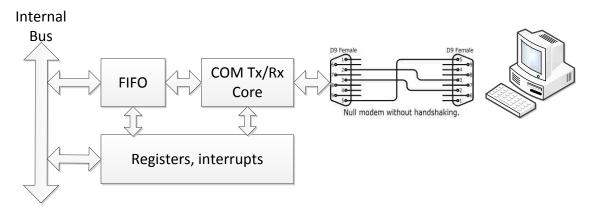

| 3.3. FUNCTIONAL BLOCK DIAGRAM                 | 15   |

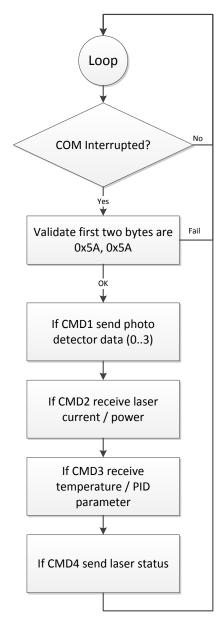

| 3.4. FLOW DIAGRAM FOR COM                     | 16   |

| 4. UNIVERSAL SERIAL BUS (USB)                 | 17   |

| 4.1. PURPOSE OF THE PERIPHERAL                | 17   |

| 4.2. OVERVIEW OF FEATURES                     | 17   |

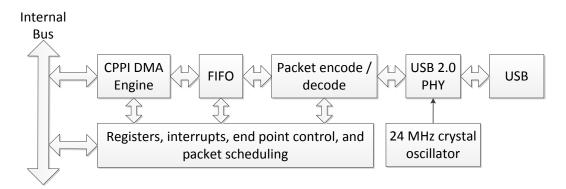

| 4.3. FUNCTIONAL BLOCK DIAGRAM                 | 18   |

| 4.4. USB CONTROLLER PERIPHERAL MODE OPERATION | 18   |

| 4.4.1. Soft Connect                           | 19   |

| 4.4.2. Entry into Suspend Mode                | 19   |

| 4.4.3. Resume Signaling                       | 20   |

| 4.4.4. Initiating a Remote Wakeup             | 20   |

| 4.4.5. Reset Signaling                        | 20   |

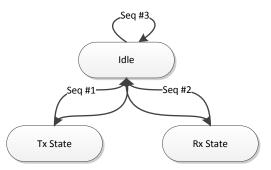

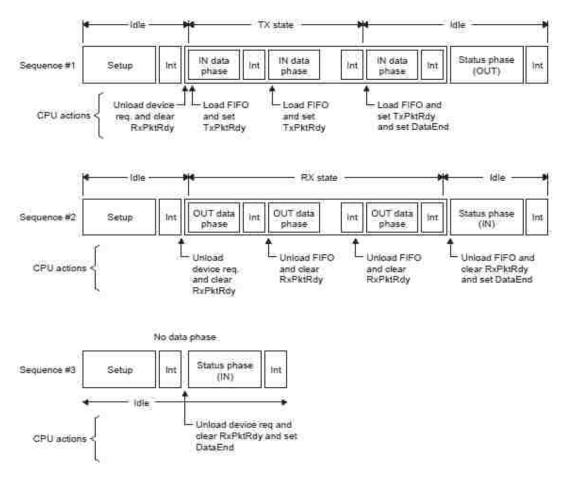

| 4.5. PERIPHERAL MODE: CONTROL TRANSACTIONS           | 21 |

|------------------------------------------------------|----|

| 4.5.1. Zero Data Requests                            | 21 |

| 4.5.2. Write Requests                                | 23 |

| 4.5.3. Read Requests                                 | 24 |

| 4.5.4. Endpoint 0 States                             | 25 |

| 4.5.5. Endpoint 0 Service Routine                    | 27 |

| 4.5.6. IDLE Mode                                     | 30 |

| 4.5.7. TX Mode                                       | 30 |

| 4.5.8. RX Mode                                       | 32 |

| 4.5.9. Error Handling                                |    |

| 5. ETHERNET                                          | 35 |

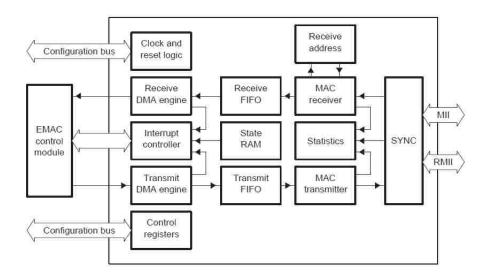

| 5.1. EMAC                                            | 35 |

| 5.1.1. Purpose of the Peripheral                     | 35 |

| 5.1.2. Features                                      |    |

| 5.1.3. Memory Map                                    |    |

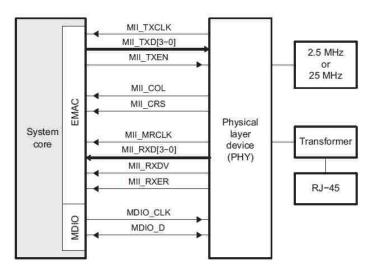

| 5.1.4. Media Independent Interface (MII) Connections | 39 |

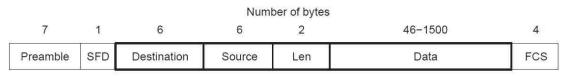

| 5.1.5. Ethernet Frame Format                         |    |

| 5.1.6. Packet Buffer Descriptors                     | 40 |

| 5.1.7. Transmit and Receive Descriptor Queues        | 40 |

| 5.1.8. Transmit and Receive EMAC Interrupts          | 40 |

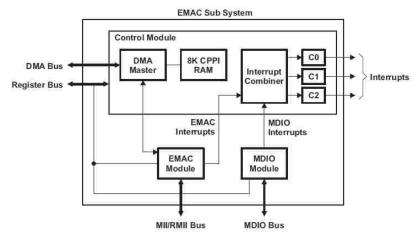

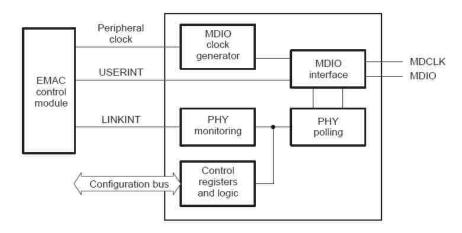

| 5.2. MDIO MODULE                                     | 41 |

| 5.2.1. Initializing the MDIO Module                  | 42 |

| 6. RESULTS                                           | 43 |

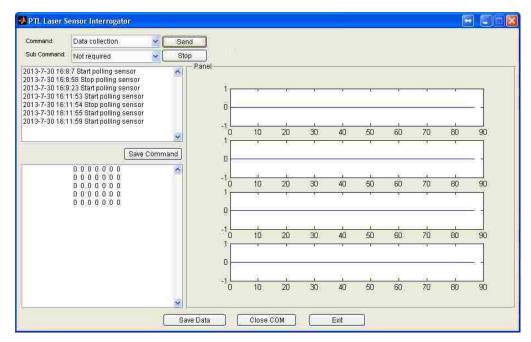

| 6.1. SERIAL PORT / COM                               | 43 |

| 6.1.1. User Interface                                | 43 |

| 6.1.2. Data Transfer                                 | 43 |

| 6.2. UNIVERSAL SERIAL BUS (USB)                      | 44 |

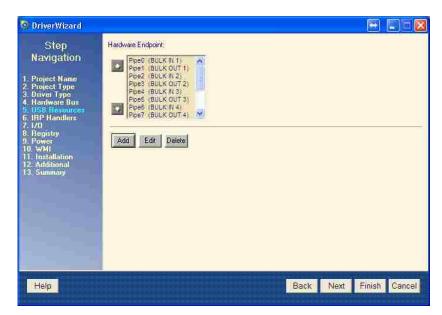

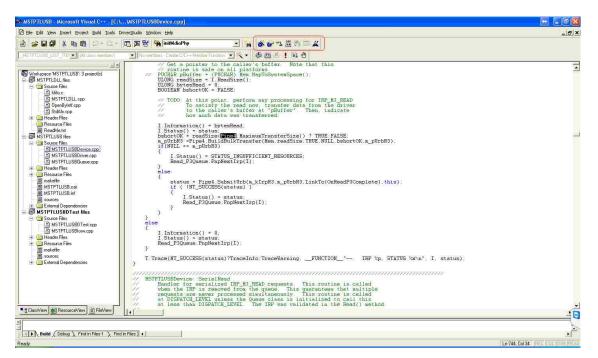

| 6.2.1. USB Driver                                    | 44 |

| 6.2.2. Data Transfer                                 | 45 |

| 6.3. ETHERNET                                        | 46 |

| 6.4. WIRELESS                                        | 46 |

| APPENDIX - CODE OVERVIEW | 47 |

|--------------------------|----|

| BIBLIOGRAPHY             | 54 |

| VITA                     | 56 |

# LIST OF ILLUSTRATIONS

|                                                                 | Page |

|-----------------------------------------------------------------|------|

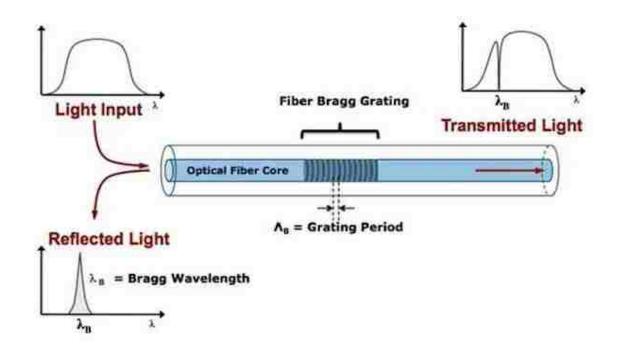

| Figure 1.1 Structure of the fiber optical sensor <sup>[2]</sup> | 1    |

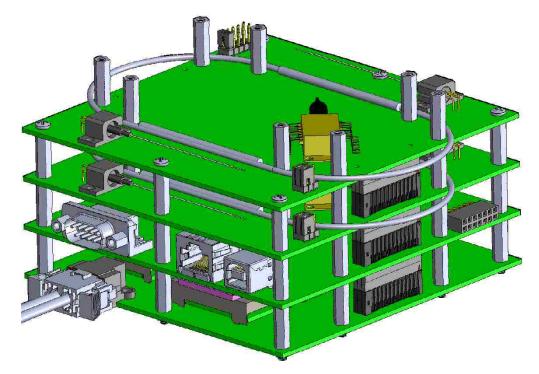

| Figure 2.1 Multi layered board layout                           |      |

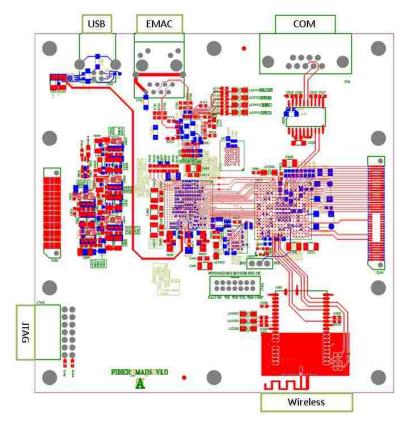

| Figure 2.2 PCB layout of main board                             | 4    |

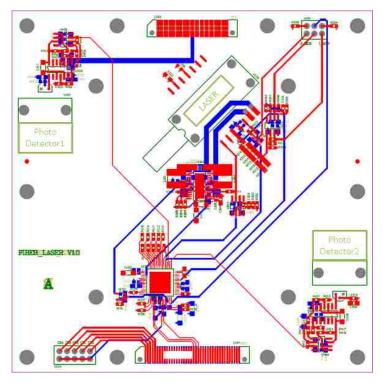

| Figure 2.3 PCB layout of LASER board                            | 5    |

| Figure 2.4 Photo detector schematic                             | 6    |

| Figure 2.5 Hybrid view of proposed FSI                          | 6    |

| Figure 2.6 Modular view of proposed FSI                         | 7    |

| Figure 2.7 Software control flow of proposed FSI                | 8    |

| Figure 2.8 Perform a new boundary scan & assign configuration   | 9    |

| Figure 2.9 Perform FPGA programming                             | 9    |

| Figure 2.10 DSP Configuration                                   | 10   |

| Figure 2.11 FSI connected via COM port                          | 11   |

| Figure 2.12 Configuring hardware endpoints                      | 12   |

| Figure 2.13 Building USB driver project                         | 12   |

| Figure 2.14 Build the DDK                                       | 13   |

| Figure 3.1 COM functional block diagram                         | 15   |

| Figure 3.2 COM Flow Diagram                                     | 16   |

| Figure 4.1 USB Functional Block Diagram                         | 18   |

| Figure 4.2 CPU Actions at USB Transfer Phases                   | 26   |

| Figure 4.3 USB Sequence of Transfer                             | 27   |

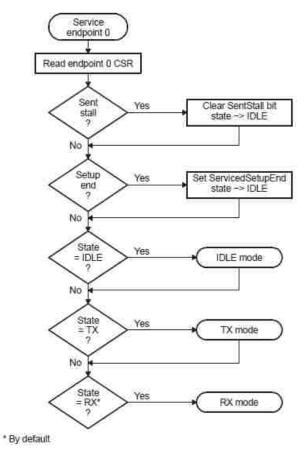

| Figure 4.4 USB Service Endpoint 0 Flow Chart                    | 29   |

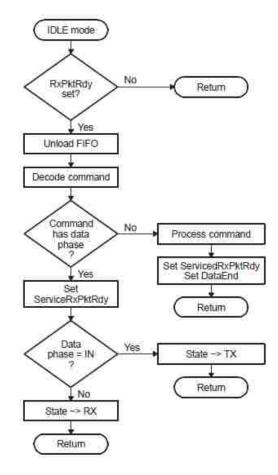

| Figure 4.5 USB IDLE Mode Flow Chart                             | 30   |

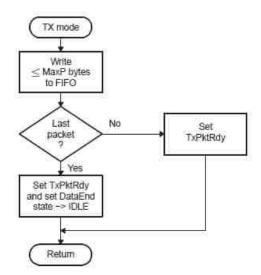

| Figure 4.6 USB TX Mode Flow Chart                               | 31   |

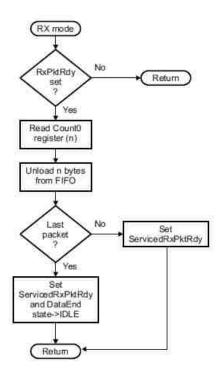

| Figure 4.7 USB RX Mode Flow Chart                               | 33   |

| Figure 5.1 EMAC Module Block Diagram                            | 35   |

| Figure 5.2 EMAC and MDIO Block Diagram                          | 37   |

| Figure 5.3 Ethernet Configuration—MII Connection        | 39 |

|---------------------------------------------------------|----|

| Figure 5.4 Frame Format for Ethernet                    | 39 |

| Figure 5.5 Basic Ethernet Descriptor Format             | 40 |

| Figure 5.6 MDIO Module Block Diagram                    | 41 |

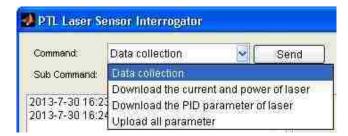

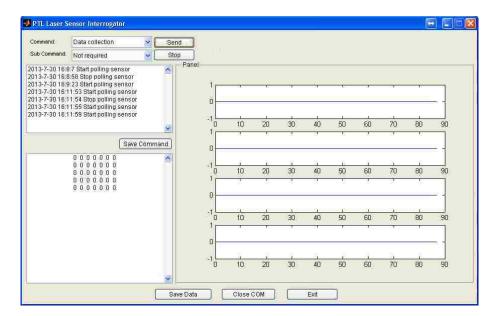

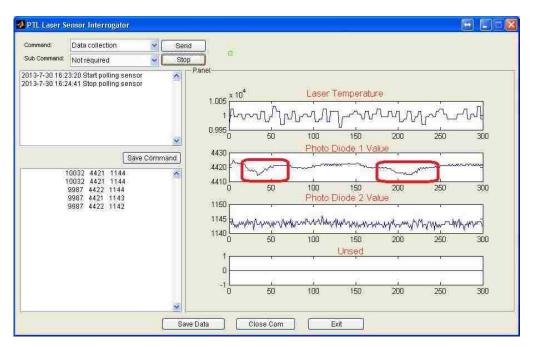

| Figure 6.1 Sample UI Menu                               | 43 |

| Figure 6.2 COM data to PC without Laser board connected | 43 |

| Figure 6.3 COM data to PC when Laser board connected    | 44 |

| Figure 6.4 PC side USB DLL Test                         | 45 |

| Figure 6.5 USB Data Transactions                        | 46 |

|                                                         |    |

# LIST OF TABLES

|                        | Page |

|------------------------|------|

| Table 3.1 COM Features | 14   |

| Table 3.2 COM Protocol |      |

# NOMENCLATURE

# Symbol

# Description

| FBG  |                    | Fiber Bragg Grating        |

|------|--------------------|----------------------------|

| FPGA |                    | -Programmable Gate Array   |

| DSP  |                    | Digital Signal Processor   |

| UART | Universal Asynchro | onous Receiver/Transmitter |

| USB  |                    | Universal Serial Bus       |

| FIFO |                    | First In First Out         |

| IIR  |                    | Infinite Impulse Response  |

#### **1. INTRODUCTION**

With increasing demand on the sensor based monitoring for structural integrity sensing, harsh chemical sensing or any other on-site sensing system, the necessity for a compact modular yet cost / power effective sensor interrogator and communications systems is becoming indispensible.

Electrical sensors have for decades been the default mechanism for measuring various phenomena. Despite their simple structure, these sensors have inherent limitations such as transmission loss, power and susceptibility to electromagnetic interference (EMI) that make their usage challenging or impractical in many applications. Fiber-optic sensing is an excellent solution to these challenges, using light rather than electricity and standard optical fiber in place of copper wire.

Figure 1.1 Structure of the fiber optical sensor<sup>[2]</sup>

Fiber optical sensing overcomes many of the challenges commonly found with electrical sensing by using light (laser light in this project) rather than electricity and standard optical fiber in place of copper wire. Optical fibers and FBG optical sensors are nonconductive, electrically passive, and immune to EMI.

Interrogation with a high-power tunable laser enables measurements that can run over long distances with little or no loss in signal integrity hence making them best suited for remote sensing. Also, unlike electrical sensing systems, each fiber optical channel has the capability to measure multiple FBG sensors, hence reducing the size, weight, and complexity of the measurement system.

Further, lack of flexibility limits the system's ability to meet many structural test and monitoring application needs. This project realizes a solution for FSI which is small in size, robust in communication and to an extent scalable.

#### 2. SETUP

#### **2.1. HARDWARE**

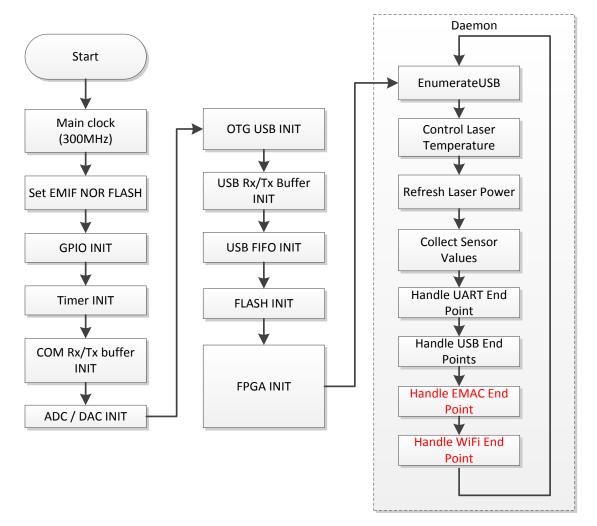

The hardware design includes multi layered board layout. The first level is the DC power distribution board. Second level is the Logic / Signal processing (including FPGA, Flash, PROM, COM, USB, Ethernet and WiFi mega modules). Third level onwards a maximum of four laser driver boards can be connected. Each laser board will have one laser chip and maximum of two photo diodes that can detect the transmitted or reflected light.

Figure 2.1 Multi layered board layout

Below two layouts show details on the parts of the board layout discussed throughout this report that participate in communication.

Figure 2.2 PCB layout of main board

Figure 2.3 PCB layout of LASER board

a. Laser module

The laser module D2570H<sup>[8]</sup> used has following properties:

- ITU wavelengths available from 1528.77 nm —1610.06 nm

- Temperature tunable for precise wavelength selection

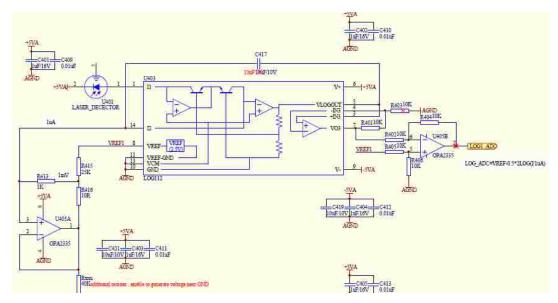

# b. Photo detector

The photo detector DRP2EX - 43T2<sup>[7]</sup> has following properties

- Bias voltage: 5.0 V

- Wavelength: 1520nm 1570nm

Figure 2.4 Photo detector schematic

Figure 2.5 Hybrid view of proposed FSI

Figure 2.6 Modular view of proposed FSI

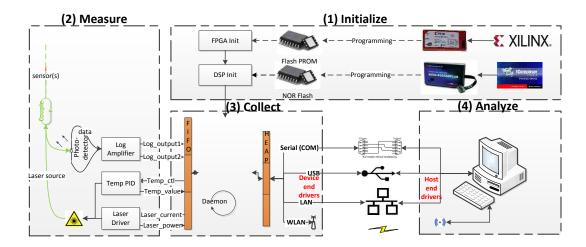

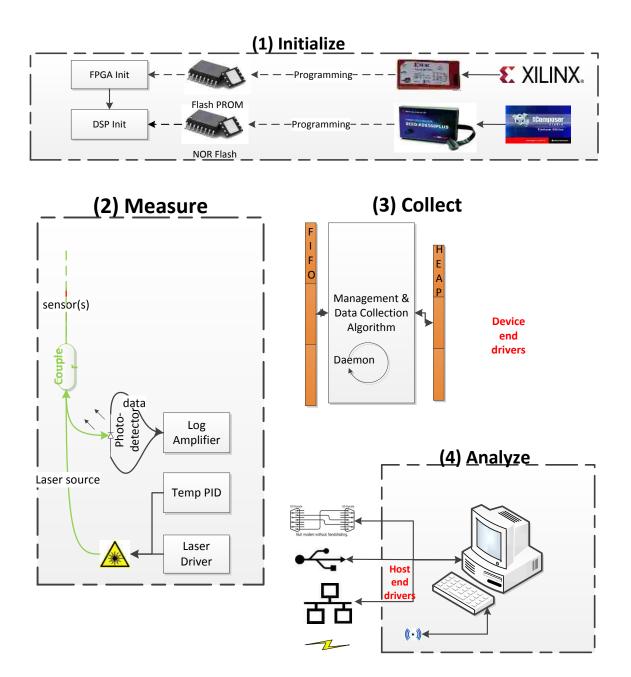

Below figure depicts the communication flow of the FSI which will be the main focus of this thesis. The code is developed using Code Composer Studio v3.3 (for DSP) and Xilinx iMPACT 12.3 (for FPGA).

Figure 2.7 Software control flow of proposed FSI

**2.2.1. Device End FPGA Setup.** Connect Xilinx 12.3 FPGA programmer and start ISE iMPACT (M .70d)

| SISE IMPACT (M. 70d) - [Boundary Scan]                                                |                                                         |                                                                                                                 | +              |

|---------------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------|

| File Edit New Operations Output Debug                                                 | Window Help                                             |                                                                                                                 | _ 8            |

| ■ ★ ● ● × Ⅱ Ⅱ ■ ★                                                                     | 10 33 28                                                |                                                                                                                 |                |

| MPACT Flows ++ 디 라 ×                                                                  |                                                         |                                                                                                                 |                |

| Boundary Scan     SystemACE     Grave ACM File (PROM File Formatter)     WebTalk Data | TDI                                                     | 7                                                                                                               |                |

|                                                                                       | xc108p xc5vlx30<br>bypass bypass<br>TDO                 |                                                                                                                 |                |

|                                                                                       |                                                         |                                                                                                                 |                |

|                                                                                       | Panerties                                               | Device 1 Programming Properties                                                                                 |                |

| MPACT Processes ++                                                                    | Category                                                | - Device 11 rog mining roperies                                                                                 |                |

| Available Operations are:                                                             | B Boundary-Scan                                         |                                                                                                                 | Vakaa 🔊        |

|                                                                                       | Device 1 ( PRCM2 xcf08p )<br>Device 2 ( FPGA xc5vbx30 ) | Property Name<br>Venfy                                                                                          | Value          |

|                                                                                       | 1865-26-25-31 (IC 11-11-11-26-27)                       | General CPLD And PROM Properties                                                                                |                |

|                                                                                       |                                                         | Erase Before Programming                                                                                        | 2              |

|                                                                                       |                                                         | - Read Protect                                                                                                  |                |

|                                                                                       |                                                         | PROM/CoolRunner-II Usercode (8 Hex Dialts)                                                                      |                |

|                                                                                       |                                                         | FROM Specific Properties                                                                                        |                |

|                                                                                       |                                                         | Load FPGA                                                                                                       |                |

|                                                                                       |                                                         | Parallel Mode                                                                                                   |                |

|                                                                                       |                                                         | Advanced PROM Programming Properties                                                                            |                |

|                                                                                       |                                                         | During Configuration: PROM is Configuration Master (chec                                                        |                |

| 19                                                                                    | 6                                                       | [select clock source]                                                                                           | External Clock |

| onsole                                                                                |                                                         | The second se |                |

| CH IDOND                                                                              |                                                         |                                                                                                                 | 100            |

| PROGRESS END - End Operation                                                          |                                                         |                                                                                                                 |                |

| PROGRESS_END - End Operation.<br>Elapsed time = 0 sec.                                |                                                         |                                                                                                                 | (i)            |

|                                                                                       | 4.                                                      | OK Cancel                                                                                                       | Apply Help     |

Figure 2.8 Perform a new boundary scan & assign configuration

| 🛃 IST BAPACT (M. 70d) - [Boundary Scan                                                                                                                                                                                                                         |                                                  |                                   |                           |                            |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----------------------------------|---------------------------|----------------------------|

| Ble Edit Yew Operations Quiput D                                                                                                                                                                                                                               | ebug Window Help                                 |                                   |                           | - # X                      |

|                                                                                                                                                                                                                                                                | X   世田日 🍋 🕺                                      | P N?                              |                           |                            |

| reparct Flows                                                                                                                                                                                                                                                  |                                                  |                                   |                           |                            |

| H TE ROUGHE Son<br>G Swatewick<br>C Search FECH File (RECM File Formation)<br>C Search FECH File (RECM File Formation)<br>K S WebTak Cata                                                                                                                      | 10                                               | Enar<br>Enar<br>xc/m.20<br>bypass |                           |                            |

| PENCT Processes ··· 따 중 ×<br>Available Operations are:                                                                                                                                                                                                         |                                                  |                                   |                           |                            |

| <ul> <li>Hogran</li> <li>Verify</li> <li>Errise</li> <li>Blank Check</li> <li>Reachack</li> </ul>                                                                                                                                                              |                                                  |                                   |                           |                            |

| fee Device D     fee Device D     fee Device SpratureRUsercode     Get Device Cardinatercode     Get Device Cardinatercode     Get Device Cardinatercode     for Device Cardinatercode     for Device Cardinatercode     for Device Staff                      |                                                  |                                   | Program Succeeded         |                            |

| One Step KSVF                                                                                                                                                                                                                                                  | 8                                                | Boundary Scan                     |                           |                            |

| onucle                                                                                                                                                                                                                                                         |                                                  |                                   |                           | +D5>                       |

| 1: Verifying device<br>dom.<br>1: Verification completed.<br>1: Calculated checksum mace<br>1: Putting device the TSP mo<br>dome.<br>1: Pitting device the TSP mo<br>1: Programming completed so<br>PhotoRESS_END - End Operation.<br>Elamped time - 4 de sec. | dedone.<br>dedone.<br>commsfully.<br>commsfully. | 10149235                          |                           |                            |

| 17-4-10-1 - 10-1 - 30 - 200 -                                                                                                                                                                                                                                  |                                                  |                                   |                           |                            |

|                                                                                                                                                                                                                                                                |                                                  |                                   |                           |                            |

| 📱 Console 🧔 Enters 🦺 Warrangs                                                                                                                                                                                                                                  |                                                  |                                   |                           |                            |

|                                                                                                                                                                                                                                                                |                                                  |                                   | Configuration 12 afform 5 | able USB II 6 99-17 Odb be |

Figure 2.9 Perform FPGA programming

# 2.2.2. Device End DSP Setup. Open AISgen for D800K002

and perform below steps

| AlSgen for D800K00                                          | 2                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AlSgen for D800                                               | (002                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| File Help                                                   |                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | File Help                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| General Flash PLLO                                          | PLL1 PSC Pinmux                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | General Flash PL                                              | LO PLL1 PSC Pinmux                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Boot                                                        | ee Type: delicit.002 w DSP v<br>Mode: NOR Flash v                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                             | Source: Coystal 24 MH:<br>onligure PLL0 I Configure PLL1<br>onligure DDR Configure DDR<br>onligure PSC I Configure Pinnux<br>nable CRC<br>peaily Entrypoint. | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                               | Data Width: 16-bit.<br>CS2 Setup: 0x10C445AD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| AIS Output File: C                                          | Documents and Settings\Tameern Ahmed Khan\N<br>Documents and Settings\Tameern Ahmed Khan\N<br>rom file C:\Documents and Settin                               | additional strength ( and ).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | DSP Application File<br>AIS Output File<br>Loaded configurati | C:\Documents and Settings\Tameem Ahmed Kha<br>C:\Documents and Settings\Tameem Ahmed Kha<br>on from file C:\Documents and Settin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | And a second sec |

|                                                             |                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ·/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| AlSgen for D800K00                                          | 2                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | AlSgen for D800                                               | (002                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| File Help                                                   |                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | File Help                                                     | x0022                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |