## Scholars' Mine

#### **Masters Theses**

Student Theses and Dissertations

2015

# Analysis and comparison of two high-gain interleaved coupledinductor boost converters

Venkat Sai Prasad Gouribhatla

Follow this and additional works at: https://scholarsmine.mst.edu/masters\_theses

Part of the Electrical and Computer Engineering Commons Department:

#### **Recommended Citation**

Gouribhatla, Venkat Sai Prasad, "Analysis and comparison of two high-gain interleaved coupled-inductor boost converters" (2015). *Masters Theses*. 7672. https://scholarsmine.mst.edu/masters\_theses/7672

This thesis is brought to you by Scholars' Mine, a service of the Missouri S&T Library and Learning Resources. This work is protected by U. S. Copyright Law. Unauthorized use including reproduction for redistribution requires the permission of the copyright holder. For more information, please contact scholarsmine@mst.edu.

## ANALYSIS AND COMPARISON OF TWO HIGH - GAIN INTERLEAVED COUPLED-INDUCTOR BOOST CONVERTERS

by

### GOURIBHATLA VENKAT SAI PRASAD

### A THESIS

# Presented to the Faculty of the Graduate School of the MISSOURI UNIVERSITY OF SCIENCE AND TECHNOLOGY

In Partial Fulfillment of the Requirements for the Degree

#### MASTER OF SCIENCE IN ELECTRICAL ENGINEERING

2015

Approved by

Mehdi Ferdowsi, Advisor

Jonathan Kimball

Pourya Shamsi

© 2015

Gouribhatla Venkat Sai Prasad All Rights Reserved

#### ABSTRACT

The main objective of this thesis is to compare and analyze two different highgain dc-dc power electronic converters based on coupled inductors and capacitor-diode multiplier cells. The idea of these converters is to integrate the solar energy with a 400V DC microgrid. DC microgrids are more efficient, less expensive, and more reliable compared to AC microgrids. They also favor the integration of renewable energy sources. With the growing need for the utilization of more renewable sources of energy, photovoltaic panels have become one of the trending technologies which convert the energy from the sun to a useable electrical power. But these panels produce a low dc output voltage which cannot directly be connected to the high voltage dc distribution of the grid. They require high-gain dc-dc converters suitable for converting the output voltage of the solar panels to the dc distribution grid voltage. The topologies studied in this thesis provide a high dc voltage gain suitable for this application. The other significant advantage of these topologies is a continuous input current which increases the effective utilization of the source. These converters can also be used in applications involving high gain dc-dc conversion such as fuel cells, and energy storage applications like ultracapacitors. In this thesis, the different operating modes of the two high-gain dcdc converters are explained in detail. Also, the voltage and current stresses seen by the components have been derived and power loss analysis is carried out for both the topologies. Recently, GaN switches have gained popularity for their higher efficiencies at higher switching frequencies, so this thesis also makes an attempt to compare Si to GaN devices in terms of efficiency improvements for the studied converters.

#### ACKNOWLEDGMENTS

I would like to sincerely thank my advisor Dr. Mehdi Ferdowsi for giving me a wonderful opportunity to carry out my graduate research. It would have been impossible without the constant support and guidance of my advisor during the course of my research. He always stood by my side which has given me an immense motivation and support to successfully complete my research. Additionally, I would like to thank my committee members, Dr. Jonathan Kimball and Dr. Pourya Shamsi, for their support and suggestions during my research.

I am also grateful to my colleagues Anand Prabhala, Bhanu Baddipadiga, Stepehen Moerer, Amrita Dabbiru, and Mohammad Jamaluddin for their support and help during the process of my thesis work.

Finally, I would like to thank my parents, brothers and all my friends for their constant support, motivation and encouragement in completing my Graduate thesis.

## **TABLE OF CONTENTS**

| ABSTRACTi<br>ACKNOWLEDGMENTSi<br>LIST OF ILLUSTRATIONSvi<br>LIST OF TABLESvi<br>NOMENCLATUREx<br>SECTION | iv<br>iii<br>xi<br>1<br>1 |

|----------------------------------------------------------------------------------------------------------|---------------------------|

| LIST OF ILLUSTRATIONSvi<br>LIST OF TABLES                                                                | iii<br>xi<br>tii<br>1     |

| LIST OF TABLES                                                                                           | xi<br>tii<br>1            |

| NOMENCLATURE x                                                                                           | cii<br>1<br>1             |

|                                                                                                          | 1<br>1                    |

| SECTION                                                                                                  | 1                         |

|                                                                                                          | 1                         |

| 1. INTRODUCTION                                                                                          |                           |

| 1.1. ROLE OF HIGH GAIN DC-DC CONVERTERS                                                                  | 1                         |

| 1.2. REVIEW OF HIGH GAIN DC-DC CONVERTERS                                                                | 1                         |

| 1.3. INTERLEAVED COUPLED INDUCTOR BASED BOOST<br>CONVERTER WITH TWO SECONDARY WINDINGS<br>(TOPOLOGY 1)   | 7                         |

| 1.4. INTERLEAVED COUPLED INDUCTOR BASED BOOST<br>CONVERTER WITH ONE SECONDARY WINDING<br>(TOPOLOGY 2)    | 8                         |

| 1.5. OPERATING MODES                                                                                     | 9                         |

| 1.5.1. Operating Modes of Topology 1                                                                     | 9                         |

| 1.5.2. Operating Modes of Topology 2 1                                                                   | 0                         |

| 2. COMPONENTS STRESS IN TOPOLOGIES 1 & 2 1                                                               | 4                         |

| 2.1. THEORETICAL ANALYSIS 1                                                                              | 4                         |

| 2.2. VOLTAGE STRESS OF COMPONENTS IN TOPOLOGY 1 1                                                        | 4                         |

| 2.2.1. Voltage Across Capacitor C1 1                                                                     | 5                         |

| 2.2.2. Voltage Across Capacitor C 1                                                                      | 6                         |

| 2.2.3. Voltage Across MOSFET 1                                                                           | 7                         |

| 2.2.4. Voltage Across Diode D2 1                                                                         | 7                         |

| 2.2.5. Voltage Across Diode D1 1                                                                         | 8                         |

| 2.3. VOLTAGE STRESS OF COMPONENTS IN TOPOLOGY 2 1                                                        | 9                         |

| 2.3.1. Voltage Across Capacitor C1 1                                                                     | 9                         |

| 2.3.2. Voltage Across Capacitor C                                                                        | 20                        |

| 2.3.3. Voltage Across MOSFET                                                                              |    |

|-----------------------------------------------------------------------------------------------------------|----|

| 2.3.4. Voltage Across Diode D2                                                                            |    |

| 2.3.5. Voltage Across Diode D1                                                                            | 22 |

| 2.4. COMPARISON OF VOLTAGE STRESS IN BOTH THE<br>TOPOLOGIES 1 AND 2                                       | 22 |

| 2.5. CURRENT STRESS OF COMPONENTS IN TOPOLOGY 1                                                           | 23 |

| 2.5.1. Magnetizing Currents of Inductors                                                                  | 23 |

| 2.5.2. Inductor Coil Currents                                                                             | 24 |

| 2.5.3. Switch Currents                                                                                    | 25 |

| 2.5.4. Diode Currents                                                                                     | 25 |

| 2.5.5. Capacitor C1 Current                                                                               | 25 |

| 2.6. CURRENT STRESS OF COMPONENTS IN TOPOLOGY 2                                                           | 26 |

| 2.6.1. Magnetizing Currents of Inductors                                                                  | 26 |

| 2.6.2. Inductor Coil Currents                                                                             | 26 |

| 2.6.3. Switch Currents                                                                                    | 27 |

| 2.6.4. Diode Currents                                                                                     | 28 |

| 2.6.5. Capacitor C1 Current                                                                               | 28 |

| 2.7. COMPARISON OF CURRENT STRESS IN BOTH THE TOPOLOGIES 1 & 2                                            | 28 |

| 2.8. COMPARISON OF SIMULATION RESULTS WITH<br>THEORETICAL ANALYSIS                                        | 29 |

| 2.9. COMPARISON OF SIMULATION TO PRACTICAL<br>WAVEFORMS IN BOTH THE TOPOLOGIES                            | 34 |

| 2.9.1. Topology 1                                                                                         | 34 |

| 2.9.2. Topology 2                                                                                         | 49 |

| 3. POWER LOSS ANALYSIS IN TOPOLOGIES 1 & 2 & VARIATION OF<br>EFFICIENCY WITH COUPLED INDUCTOR TURNS RATIO | 64 |

| 3.1. POWER LOSS ANALYSIS IN TOPOLOGIES 1 & 2                                                              | 64 |

| 3.2. EFFECT OF N RATIO ON EFFICIENCY                                                                      | 67 |

| 4. EFFICIENCY ANALYSIS OF THE CONVERTER BY USING SILICON<br>TO GALLIUM NITRIDE MOSFETS                    | 71 |

| 4.1. GaN TECHNOLOGY                                                                                       | 71 |

| 4.2. CHALLENGES WITH GaN                                                                                  |    |

| 4.3. HARDWARE COMPARISON | 73 |

|--------------------------|----|

| 5. CONCLUSION            | 76 |

| BIBLIOGAPHY              | 77 |

| VITA                     | 80 |

## LIST OF ILLUSTRATIONS

| Figure                                                                          | Page |

|---------------------------------------------------------------------------------|------|

| 1.1. Parallel diode clamped coupled inductor boost converter                    | 2    |

| 1.2. Boost converter with winding-coupled inductor                              | 2    |

| 1.3. Elementary additional circuit                                              |      |

| 1.4. Hybrid Step up converter switching structure                               | 4    |

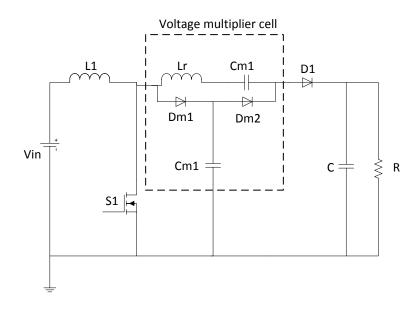

| 1.5. Boost converter with voltage multiplier cell                               | 5    |

| 1.6. Interleaved boost converter with voltage multiplier cell                   | 5    |

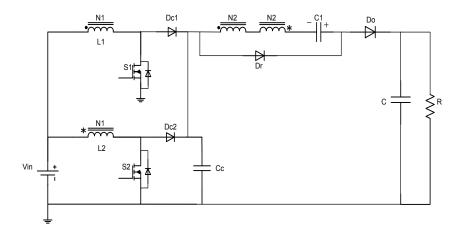

| 1.7. Interleaved coupled inductor boost converter                               | 6    |

| 1.8. Interleaved boost converter with intrinsic voltage-doubler characteristics | 7    |

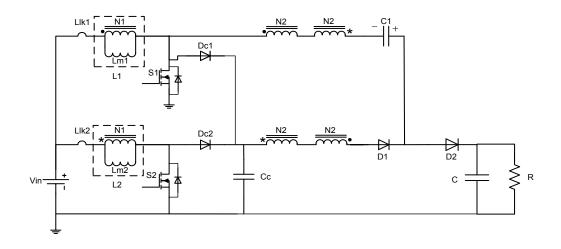

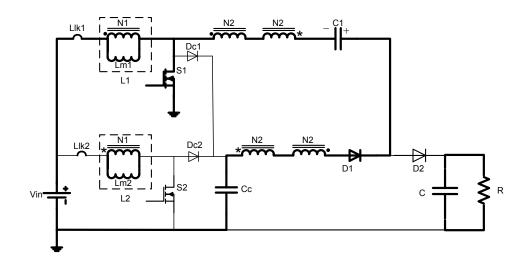

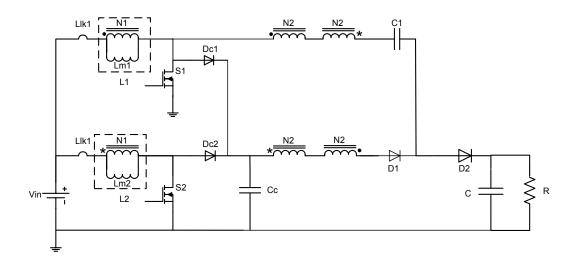

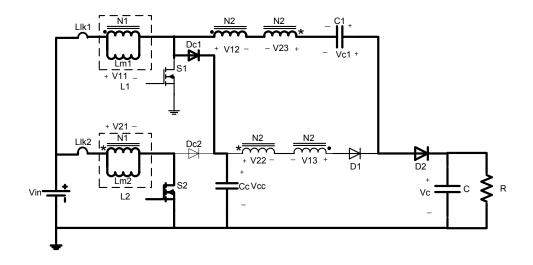

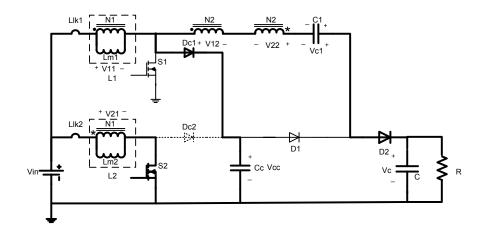

| 1.9. Schematic diagram of topology1                                             |      |

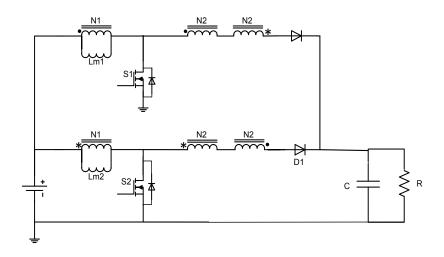

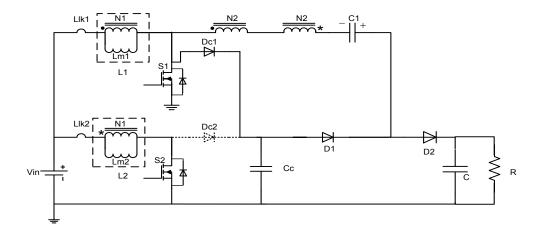

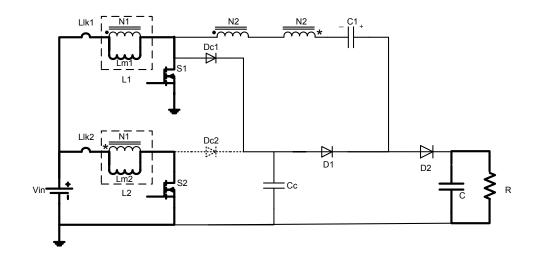

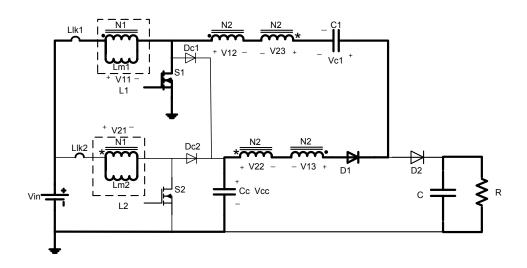

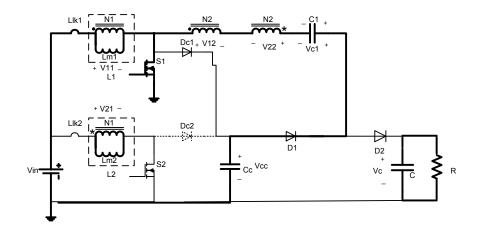

| 1.10. Schematic diagram of topology2                                            | 9    |

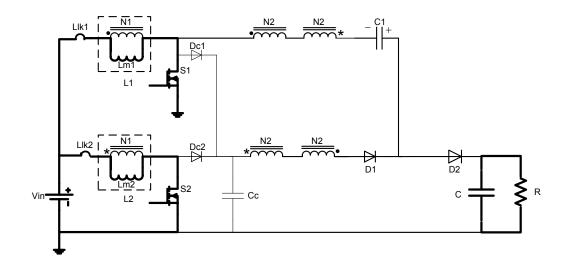

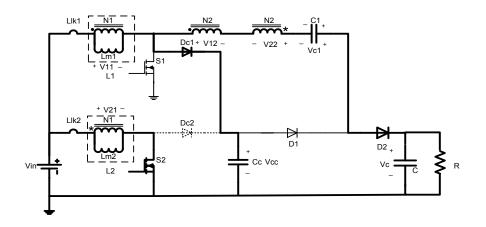

| 1.11. Topology 1 operating mode 1                                               |      |

| 1.12. Topology 1 operating mode 2                                               |      |

| 1.13. Topology 1 operating mode 3                                               |      |

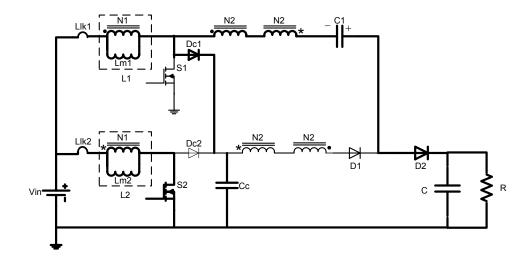

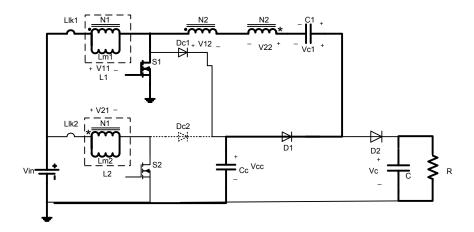

| 1.14. Topology 2 operating mode 1                                               |      |

| 1.15. Topology 2 operating mode 2                                               |      |

| 1.16. Topology 2 operating mode 3                                               |      |

| 2.1. Schematic diagram of topology1                                             |      |

| 2.2. Topology 1 operating mode 3                                                |      |

| 2.3. Topology 1 operating mode 2                                                |      |

| 2.4. Topology 1 operating mode 3                                                | 17   |

| 2.5. Topology 1 operating mode 2                                                |      |

| 2.6. Topology 2 operating mode 3                                                |      |

| 2.7. Topology 2 operating mode 2                                                |      |

| 2.8. Topology 2 operating mode 3                                                |      |

| 2.9. Topology 2 operating mode 2                                                |      |

| 2.10. Practical waveform of Vout for topology 1                                 |      |

| 2.11. Simulated waveform of Vout for topology 1                                 |      |

| 2.12. Practical waveform of V <sub>c1</sub> for topology 1                      |      |

| 2.13. Simulated waveform of $V_{c1}$ for topology 1         |    |

|-------------------------------------------------------------|----|

| 2.14. Practical waveform of $V_{cc}$ for topology 1         |    |

| 2.15. Simulated waveform of Vcc for topology 1              |    |

| 2.16. Practical waveform of $V_{d1}$ for topology 1         |    |

| 2.17. Simulated waveform of $V_{d1}$ for topology 1         |    |

| 2.18. Practical waveform of $V_{d2}$ for topology 1         | 39 |

| 2.19. Simulated waveform of $V_{d2}$ for topology 1         | 39 |

| 2.20. Practical waveform of $V_{ds1}$ for topology 1        | 40 |

| 2.21. Simulated waveform of $V_{ds1}$ for topology 1        | 40 |

| 2.22. Practical waveform of Vds2 for topology 1             |    |

| 2.23. Simulated waveform of $V_{ds2}$ for topology 1        |    |

| 2.24. Practical waveform of Iin for topology 1              |    |

| 2.25. Simulated waveform of Iin for topology 1              |    |

| 2.26. Practical waveform of IL2 for topology 1              |    |

| 2.27. Simulated waveform of IL2 for topology 1              |    |

| 2.28. Practical waveform of IL1 for topology 1              | 44 |

| 2.29. Simulated waveform of IL1 for topology 1              | 44 |

| 2.30. Practical waveform of Is1 for topology 1              |    |

| 2.31. Simulated waveform of Is1 for topology 1              |    |

| 2.32. Practical waveform of Is2 for topology 1              |    |

| 2.33. Simulated waveform of Is2 for topology 1              |    |

| 2.34. Practical waveform of Ic1 for topology 1              |    |

| 2.35. Simulated waveform of Ic1 for topology 1              |    |

| 2.36. Practical waveform of Id1 for topology 1              |    |

| 2.37. Simulated waveform of Id1 for topology 1              |    |

| 2.38. Practical waveform of Vout for topology 2             | 49 |

| 2.39. Simulated waveform of V <sub>out</sub> for topology 2 | 50 |

| 2.40. Practical waveform of V <sub>c1</sub> for topology 2  | 50 |

| 2.41. Simulated waveform of Vc1 for topology 2              |    |

| 2.42. Practical waveform of V <sub>cc</sub> for topology 2  |    |

| 2.43. Simulated waveform of $V_{cc}$ for topology 2         | 52 |

|-------------------------------------------------------------|----|

| 2.44. Practical waveform of V <sub>d2</sub> for topology 2  | 53 |

| 2.45. Simulated waveform of $V_{d2}$ for topology 2         | 53 |

| 2.46. Practical waveform of $V_{d1}$ for topology 2         | 54 |

| 2.47. Simulated waveform of $V_{d1}$ for topology 2         | 54 |

| 2.48. Practical waveform of $V_{ds1}$ for topology 2        | 55 |

| 2.49. Simulated waveform of V <sub>ds1</sub> for topology 2 | 55 |

| 2.50. Practical waveform of $V_{ds2}$ for topology 2        | 56 |

| 2.51. Simulated waveform of $V_{ds2}$ for topology 2        | 56 |

| 2.52. Practical waveform of Iin for topology 2              | 57 |

| 2.53. Simulated waveform of Iin for topology 2              | 57 |

| 2.54. Practical waveform of IL2 for topology 2              | 58 |

| 2.55. Simualted waveform of IL2 for topology 2              | 58 |

| 2.56. Practical waveform of IL1 for topology 2              | 59 |

| 2.57. Simualted waveform of IL1 for topology 2              | 59 |

| 2.58. Practical waveform of Is1 for topology 2              | 60 |

| 2.59. Simualted waveform of Is1 for topology 2              | 60 |

| 2.60. Practical waveform of Is2 for topology 2              | 61 |

| 2.61. Simualted waveform of Is2 for topology 2              | 61 |

| 2.62. Practical waveform of Ic1 for topology 2              |    |

| 2.63. Simualted waveform of Ic1 for topology 2              |    |

| 2.64. Practical waveform of Id1 for topology 2              | 63 |

| 2.65. Simualted waveform of Id1 for topology 2              | 63 |

| 3.1. Power Analysis in topology 1                           | 64 |

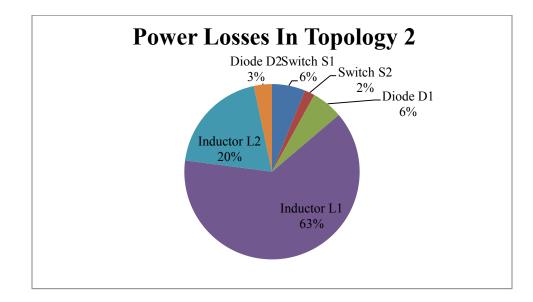

| 3.2. Power Analysis in topology 2                           | 66 |

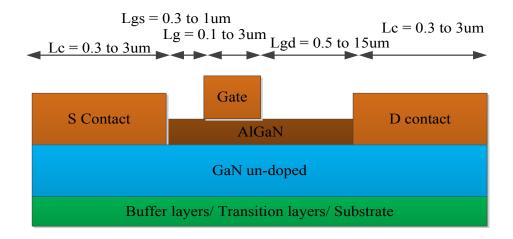

| 4.1. Device structure of GaN                                | 71 |

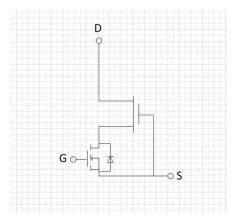

| 4.2. Normally OFF GaN used in the prototype                 |    |

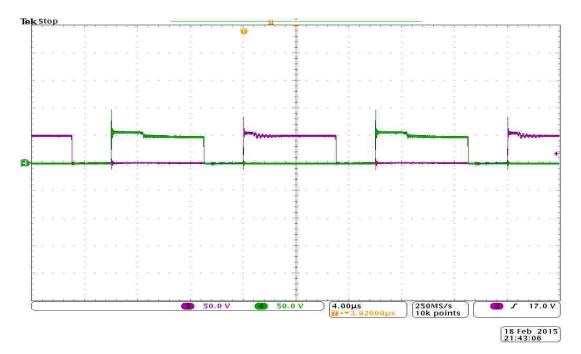

| 4.3. Voltage of drain to source with Si based MOSFET        | 74 |

| 4.4. Voltage of drain to source with GaN based MOSFET       | 75 |

## LIST OF TABLES

| Table                                                                      | Page |

|----------------------------------------------------------------------------|------|

| 2.1 Voltage stress comparison                                              |      |

| 2.2 Current stress comparison                                              |      |

| 2.3 Simulation inputs for output power 400W                                |      |

| 2.4 Voltage stress comparison of theoretical to simulation results at 400W |      |

| 2.5 Current stress comparison of theoretical to simulation results at 400W | 30   |

| 2.6 Simulation inputs for output power 200W                                |      |

| 2.7 Voltage stress comparison of theoretical to simulation results at 200W |      |

| 2.8 Current stress comparison of theoretical to simulation results at 200W |      |

| 2.9.1 Hardware parameters for topology 1                                   |      |

| 2.9.2 Hardware parameters for topology 2                                   | 49   |

| 3.1 Parameters for power loss analysis for topology 1                      | 64   |

| 3.2 Breakdown of losses in Topology 1                                      | 65   |

| 3.3 Parameters for power loss analysis for topology 2                      | 65   |

| 3.4 Breakdown of losses in Topology 2                                      | 66   |

| 3.5 N vs efficiency for topology 1                                         |      |

| 4.1 Material properties comparison                                         |      |

| 4.2 Efficiency with Si based MOSFET                                        |      |

| 4.3 Efficiency with GaN based MOSFET                                       |      |

## NOMENCLATURE

| Description                          |

|--------------------------------------|

| Input Voltage                        |

| Output Voltage                       |

| Duty Cycle                           |

| Turns Ratio of the coupled inductors |

|                                      |

#### **1. INTRODUCTION**

#### **1.1. ROLE OF HIGH GAIN DC-DC CONVERTERS**

With the growing interest in the field of DC microgrids and integration of renewable sources in power generation, the need for high gain DC-DC converters has become one of the most viable options as they would help in integrating solar energy. The main purpose of high gain DC-DC converters is to boost up the low voltage from the solar panel to high voltages which makes it feasible for connecting it to DC micro grids [1-3].

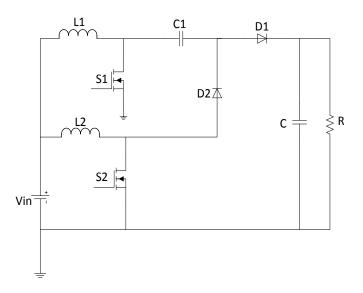

There have been many proposed topologies for high gain DC-DC converters in the literature [4-13]. But topologies with higher efficiency and lesser component stress is the optimal solution. In this regard, this thesis will focus on two high gain DC-DC converter topologies based on a coupled inductor boost converter with multiplier cells. The topologies discussed in this thesis are almost similar in operation except that one of them uses coupled inductors each with a core consisting of one primary winding and two secondary windings and the other with one primary winding and only one secondary winding. This thesis compares, explains various operating modes, and obtains voltage transfer ratio and component's stress for both topologies. It also shows simulation results and hardware results.

#### **1.2. REVIEW OF HIGH-GAIN DC-DC CONVERTERS**

With the growing applications of high gain dc-dc converter, there have been many proposed high gain dc-dc converters in the literature. This section reviews few topologies to achieve high voltage gain. Figure 1.1 shows a a parallel diode clamped coupled inductor based boost converter.

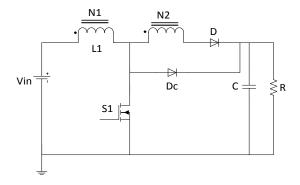

Topology shown in Figure 1.1 uses a center tapped coupled inductor. The primary winding is similar to a filter inductor and secondary winding acts as a voltage source in series with the power branch. Diode  $D_c$  is a clamp diode, which is used to dissipate leakage energy on to the output side.

The output to input voltage gain of this topology is  $\frac{V_0}{V_{in}} = \frac{1 + ND}{1 - D}$ , where N – is

the secondary to primary turns ratio of coupled inductor, D- is the duty ratio of switch.

Figure 1.1 Parallel diode clamped coupled inductor boost converter [14]

The voltage stress across switch in this topology is same as the output voltage which is a major disadvantage for applications involving high voltage gain. Figure 1.2 shows another topology based on winding-coupled inductor.

Figure 1.2 Boost converter with winding-coupled inductor [15]

Topology shown in Figure 1.2 consists of a coupled inductor based interleaved boost converter with three windings on the coupled inductors. The voltage transfer ratio of this topology is  $\frac{V_o}{V_{in}} = \frac{N}{1-D}$ , where N – is the secondary to primary turns ratio of coupled inductor, D- is the duty ratio of switches. Because of interleaving of two boost converters, the input current in this topology is smooth and voltage stress across switches is  $\frac{V_o}{N}$ . High-gain DC-DC converters can also be designed by adding voltage lift cells to a basic boost converter to achieve high output voltage. By using an elementary Luo converter [16] and connecting two such cells in series a higher voltage transfer ratio can be achieved. A two-cells in series circuit is shown in Figure 1.3.

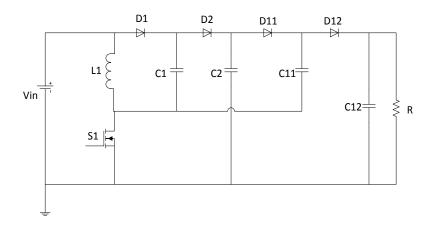

Figure 1.3 Elementary additional circuit

The principle of operation of this topology is charging capacitors in parallel and discharging them in series to achieve a higher voltage gain at the output. The voltage transfer ratio is  $\frac{V_o}{V_{in}} = \frac{3-D}{1-D}$ . As there are lot of capacitors and diodes being used in this topology, it results in high cost and low efficiency. Another similar topology based on voltage lift cell is as depicted in Figure 1.4 [17]. The voltage transfer ratio of this topology is  $\frac{V_o}{V_{in}} = \frac{1+D}{1-D}$ .

One topology of interest based on voltage lift cell is as shown in Figure 1.5 [18]. In this, a voltage multiplier cell used in AC voltage lift applications is introduced. Small  $L_r$  in the multiplier cell helps in zero current switching (ZCS) of the diodes. The voltage transfer ratio of this topology is  $\frac{V_o}{V_{in}} = \frac{1+M}{1-D}$ , where M represents number of voltage multiplier cells. The efficiency of this topology is good according to [18]. But the efficiency is not good for high voltage applications. Other methods used to achieve a high voltage gain are based on a coupled inductor based boost converter interleaving which is reported in [19].

Figure 1.4 Hybrid Step up converter switching structure

Figure 1.6 shows another edition of voltage multipliers for boost converters. This topology has an interleaved coupled inductor based boost converter on the front end and a capacitor diode multiplier cell on rear end which is charged and discharged to achieve high voltage gain at the output. Voltage gain of this topology is  $\frac{V_o}{V_{in}} = \frac{2N+1}{1-D}$ , where N is the secondary to primary turns ratio of the coupled inductor and D is the duty ratio of the switches. The voltage stress across switches in this topology is very less  $\frac{V_{in}}{1-D}$ . This topology has a high potential for applications involving high voltage gain.

Figure 1.5 Boost converter with voltage multiplier cell

Figure 1.6 Interleaved boost converter with voltage multiplier cell

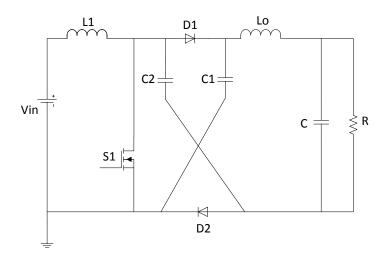

The schematic of an interleaved coupled inductor boost converter [4] is as shown in Figure 1.7. The voltage gain for this topology is  $\frac{V_o}{V_i} = \frac{N+1}{1-D}$ . Because of interleaving of two boost converters, input current of this topology is continuous. The voltage stress across switches is  $\frac{V_{in}}{1-D}$ . The coupled inductor secondary windings on the rear end produce a voltage boost on the output side.

Figure 1.7 Interleaved coupled inductor boost converter

An interleaved boost converter with intrinsic voltage-doubler characteristic [20] topology works on the principle of charging and discharging capacitor C1 as one of the switches is always ON over a switching cycle. There is a 180 degrees phase displacement between the pulses given to active switches. This creates a doubling effect of boost converter output voltage in the system. The voltage gain is of this topology is  $\frac{V_o}{V_i} = \frac{2}{1-D}$ . This voltage gain of the converter is not suitable for high voltage gain applications. The

schematic of this topology is as shown in Figure 1.8.

The focus of application in this thesis is integration of solar energy to a 400V DC microgrid. In this regard, two new topologies were proposed based on a coupled inductor based interleaved boost converter concept. These topologies have higher voltage gain, continuous input current and less voltage stress across switches when compared to other topologies in existing literature as discussed above.

Figure 1.8 Interleaved boost converter with intrinsic voltage-doubler characteristics

Because of these features, they are the best topologies that can be used in the focus of application being discussed in this thesis. So, this thesis performs analysis and comparison of these two proposed topologies.

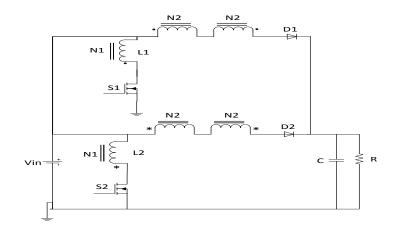

## **1.3. INTERLEAVED COUPLED INDUCTOR BASED BOOST CONVERTER** WITH TWO SECONDARY WINDINGS (TOPOLOGY 1)

Figure 1.9 is an interleaved coupled inductor based boost converter with a multiplier cell. It basically consists of an interleaved boost converter at the front end that boosts up the input voltage with a gain  $\left(\frac{1}{(1-D)}\right)$  and coupled inductor secondary windings that are connected in series with a capacitor. This capacitor is used to charge

and discharge every switching cycle to boost up the interleaved boost converter output further. The other basic principle in switching pattern is that the pulses to switches S1 and S2 has a phase difference of 180 degrees. The voltage transfer ratio of this topology is

$$V_{out} = \left(\frac{3N+2}{1-D}\right) \times V_{in}$$

, where N is the turns ratio of coupled inductors. The operating

modes, component's stress, simulation and hardware results are discussed in the latter part of the thesis.

Figure 1.9. Schematic diagram of topology1

## 1.4. INTERLEAVED COUPLED INDUCTOR BASED BOOST CONVERTER WITH ONE SECONDARY WINDING (TOPOLOGY 2)

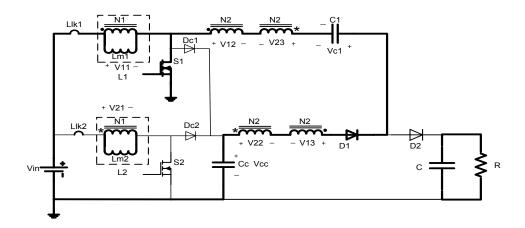

The schematic of topology 2 is almost similar to that of topology 1 except that the coupled inductors have only one secondary winding. Even operating principle of this topology is the same as topology 1 but the transfer ratio of this is less when compared to topology 1 for a particular duty cycle. The voltage transfer ratio of this topology is  $V_{out} = \left(\frac{2N+2}{1-D}\right) \times V_{in}$ , where N is the turns ratio of coupled inductor. Figure 1.10 shows the schematic of topology 2.

In Figures 1.9 and 1.10, a body diode of the MOSFET is shown but it will not be shown in future schematics as there is no participation of this diode in operating modes of the circuit.

Figure 1.10. Schematic diagram of topology 2

#### **1.5. OPERATING MODES**

**1.5.1. Operating modes of Topology 1.** The basic operating modes are explained in this section for topology 1. The other operating modes includes only the transient dissipation of leakage energy in to the clamp circuit. The clamp circuit consists of  $D_{C1}$ ,  $D_{C2}$ ,  $C_c$  components

### Mode 1

In this mode, both switches  $S_1$  and  $S_2$  are ON, this charges inductors  $L_1$  and  $L_2$  respectively. This is similar to the boost converter operation when switch is ON. During this mode, the load is supplied by the output capacitor. Figure 1.11 shows the circuit operation in Mode 1.

#### Mode 2

This mode starts when switch  $S_1$  is turned OFF while  $S_2$  remains ON. The current through  $L_2$  keeps increasing but the current through  $L_1$  starts decreasing and charges the output capacitor through  $C_1$  and  $D_2$ . Figure 1.12 shows the circuit operation in Mode 2.

Mode 3

This mode starts when switch  $S_1$  is ON and  $S_2$  is OFF. During this mode, inductor  $L_1$  charges and  $L_2$  discharges to charge capacitor  $C_1$  through lower and upper secondary windings of coupled inductor. Figure 1.13 shows the circuit operation in Mode 3.

Figure 1.11. Topology 1 operating mode 1

**1.5.2. Operating Modes of topology 2.** Mode 1. This mode is similar to mode 1 of topology 1, both inductors  $L_1 \& L_2$  are charged through  $S_1$ ,  $S_2$  respectively. Figure 1.14 shows the circuit operation in Mode 1.

#### Mode 2

In this mode,  $S_1$  is OFF and  $S_2$  is ON. The current through inductor  $L_2$  increases and the current through  $L_1$  discharges through  $C_1$  and diode  $D_2$  to charge the output capacitor. The stored energy in inductor  $L_1$  and capacitor  $C_1$  is used to boost up the output voltage. Figure 1.15 shows the circuit operation in Mode 2. Capacitor  $C_c$  is charged through input source through  $D_{c1}$ .

Figure 1.12. Topology 1 operating mode 2

Mode 3

This mode starts when  $S_1$  is ON &  $S_2$  is OFF. In this mode, capacitor  $C_c$  discharges through the darkened path and charges capacitor  $C_1$ . During the same, the load is supplied by the output capacitor. Figure 1.16 shows the circuit operation in Mode 3.

Figure 1.13. Topology 1 operating mode 3

Figure 1.14. Topology 2 operating mode 1

Figure 1.15. Topology 2 operating mode 2

Figure 1.16. Topology 2 operating mode 3

#### 2. COMPONENT'S STRESS IN TOPOLOGIES 1 & 2

#### **2.1. THEORETICAL ANALYSIS**

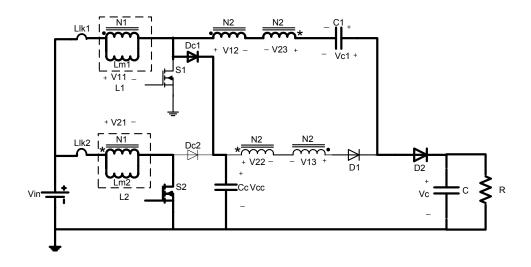

For theoretical analysis of components stress, the analysis is carried out on topology 1 as both the topologies are almost similar except that in topology 2, there is only one secondary winding for coupled inductors. While deducing the equations for topology 2 from topology 1 the windings from  $C_c$  to anode of diode  $D_1$  are considered not to exist. Figure 2.1 shows the schematic of topology 1.

#### 2.2. VOLTAGE STRESS OF COMPONENTS IN TOPOLOGY 1

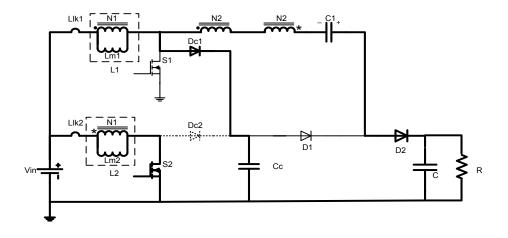

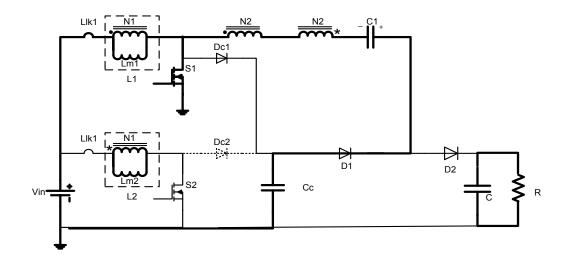

Figure 2.1. Schematic diagram of topology1

Topology above has various components as show in the circuit diagram. In designing a power converter sizing of components is one of the main requirements which require components stress in selecting the optimal device. The stress across components can be found by analysis of topology during various modes of operation.

**2.2.1. Voltage Across Capacitor**  $C_1$ : The voltage across  $C_1$  can be analyzed by using mode 3 of topology. Figure 2.2 shows the operation of topology 1 in mode 3.

Figure 2.2. Topology 1 operating mode 3

In the above loop, by applying KVL,

$$V_{c1} = V_{cc} - V_{22} + V_{13} - V_{23} + V_{12}$$

$$V_{cc} = \left(\frac{V_{in}}{1 - D}\right), \text{ as it is the output of a interleaved boost converter}$$

$$V_{23} = V_{22} = N \times (V_{in} - V_{cc}), N = \frac{N_2}{N_1}$$

$$= N \times \left(V_{in} - \frac{V_{in}}{(1 - D)}\right)$$

$$(2.1)$$

Voltage across the top inductor with dotted representation in the circuit is  $V_{in}$  as inductor  $L_1$  is charging.

$$V_{12} = V_{13} = N \times V_{in} \tag{2.3}$$

Substituting equations (2.2) and (2.3) in (2.1),

$$\begin{aligned} V_{c1} &= \left(\frac{V_{in}}{1-D}\right) - N \times \left(V_{in} - \left(\frac{V_{in}}{1-D}\right)\right) + (N \times V_{in}) - N \times \left(V_{in} - \left(\frac{V_{in}}{1-D}\right)\right) + N \times V_{in} \\ &= 2 \times N \times \left(\frac{V_{in}}{1-D}\right) + \left(\frac{V_{in}}{1-D}\right) \\ V_{c1} &= \left(\frac{(2N+1) \times V_{in}}{1-D}\right) \\ V_{c1} &= \left(\frac{V_{in}}{1-D}\right) - N \times \left(V_{in} - \frac{V_{in}}{1-D}\right) + (N \times V_{in}) - N \times \left(V_{in} - \frac{V_{in}}{1-D}\right) + N \times V_{in} \\ &= 2 \times N \times \left(\frac{V_{in}}{1-D}\right) + \left(\frac{V_{in}}{1-D}\right) \\ V_{c1} &= \left(\frac{(2N+1)V_{in}}{1-D}\right) \quad (2.4) \end{aligned}$$

**2.2.2. Voltage Across Capacitor C.** The voltage across C can be analyzed by using mode 2 of topology 1. This is also the voltage transfer ratio of the converter. Figure 2.3 shows the operation of topology 1 in mode 2.

Figure 2.3. Topology 1 operating mode 2

Applying KVL in the above loop,

$V_c = V_{cc} - V_{12} + V_{23} + V_{c1}$

$$V_{cc} = \frac{V_{in}}{1 - D}$$

$$V_{23} = N \times V_{in}, N = \frac{N^2}{N^1}$$

$$V_{12} = N \times \left(V_{in} - \frac{V_{in}}{1 - D}\right)$$

Substituting above values and (2.4),

$$V_{c} = \left(\frac{V_{in}}{1-D}\right) - N \times \left(V_{in} - \frac{V_{in}}{1-D}\right) + N \times V_{in} + \left(\frac{2N+1}{1-D}\right) \times V_{in}$$

$$V_{c} = \left(\frac{3N+2}{1-D}\right) \times V_{in}$$

Hence, the gain or transfer ratio of the converter is  $V_c = \left(\frac{3N+2}{1-D}\right) \times V_{in}$

**2.2.3. Voltage Across MOSFET.** The voltage across switches when they are OFF will be equal to the boost converter output voltage, i.e.,  $\left(\frac{V_{in}}{1-D}\right)$ .

**2.2.4. Voltage Across Diode D2.** The voltage across diode D2 is maximum in operation mode 3. The voltage stress can be analyzed from Figure 2.4 which shows the operation of topology 1 in mode 3.

Figure 2.4. Topology 1 operating mode 3

$V_{d2}$  = (Voltage at the node where C1, D1 are connected – output voltage)

$$V_{d2} = (V_{c1} + V_{23} - V_{12}) - Vc$$

=  $\left(\frac{(2N+1) \times V_{in}}{1-D}\right) + N \times \left(V_{in} - \frac{V_{in}}{1-D}\right) - N \times V_{in} - \left(\frac{(3N+2) \times V_{in}}{1-D}\right)$

=  $-\left(\frac{(2N+1) \times V_{in}}{1-D}\right)$

**2.2.5. Voltage Across Diode D1**. Diode D1 experiences maximum stress in mode 2. The analysis in mode 2 is as shown in Figure 2.5.

$$V_{d1} = (V_{22} - V_{13} - V_{cc}) - V_c$$

$$V_{d1} = (V_{22} - V_{13} - V_{cc}) - V_c$$

$$= N \times V_{in} - N \times \left( V_{in} - \frac{V_{in}}{1 - D} \right) - \left( \frac{V_{in}}{1 - D} \right) - \left( \frac{(3N + 2) \times V_{in}}{1 - D} \right)$$

$$= -\left( \frac{(4N + 1) \times V_{in}}{1 - D} \right)$$

Figure 2.5. Topology 1 operating mode 2

#### 2.3. VOLTAGE STRESS OF COMPONENTS IN TOPOLOGY 2

Topology 2 is almost similar to topology 1 in analysis. The following section shows the derivation of the voltage stress for various components in the circuit.

**2.3.1. Voltage Across Capacitor C1.** The voltage across capacitor C1 can be analyzed from mode 3 operation of topology 2 as shown in Figure 2.6.

In the below loop, by applying KVL,

$V_{c1} = V_{cc} - V_{22} + V_{12}$

Figure 2.6. Topology 2 operating mode 3

$$V_{cc} = \left(\frac{V_{in}}{1-D}\right), \text{ as it is the output of a interleaved boost converter}$$

$$V_{22} = N \times (V_{in} - V_{cc}), N = \left(\frac{N_2}{N_1}\right) = N \times \left(V_{in} - \frac{V_{in}}{1-D}\right)$$

$$V_{22} = N \times (V_{in} - V_{cc}), N = \left(\frac{1}{N_1}\right) - N \times \left(\frac{V_{in} - 1}{1 + 1}\right)$$

$$V_{12} = N \times V_{in}$$

Substituting the above values in equation

$$V_{c1} = \left(\frac{V_{in}}{1-D}\right) - N \times \left(V_{in} - \frac{V_{in}}{1-D}\right) + N \times V_{in}$$

$$= \left(\frac{(N+1) \times V_{in}}{1-D}\right)$$

**2.3.2.** Voltage Across Capacitor C. Mode 2 of topology 2 is used to analyze voltage across capacitor C as shown in Figure 2.7.

Figure 2.7. Topology 2 operating mode 2

$$V_{c} = V_{cc} - V_{12} + V_{22} + V_{c1}$$

$$V_{cc} = \left(\frac{V_{in}}{1 - D}\right)$$

$$V_{22} = N \times V_{in}, N = \frac{N^{2}}{N1}$$

$$V_{12} = N \times \left(V_{in} - \frac{V_{in}}{1 - D}\right)$$

Substituting the above values in equation for Vc,

$$V_{c} = \left(\frac{V_{in}}{1-D}\right) - N \times \left(V_{in} - \frac{V_{in}}{1-D}\right) + N \times V_{in} + \left(\frac{(N+1) \times V_{in}}{1-D}\right)$$

$$V_{c} = \left(\frac{(2N+2) \times V_{in}}{1-D}\right)$$

Hence, the gain of topology 2 is  $\left(\frac{(2N+2) \times V_{in}}{1-D}\right)$

20

**2.3.3. Voltage Across MOSFET.** The voltage across switches when they are OFF will be equal to the boost converter output voltage, i.e.,  $\left(\frac{V_{in}}{1-D}\right)$ .

**2.3.4. Voltage Across Diode D2.** Mode 3 of topology 2 is used to analyze the voltage across  $D_2$  as shown in Figure 2.8.

Figure 2.8. Topology 2 operating mode 3

$V_{d2} = (\text{Voltage at the node where } C_1, D_1 \text{ are connected} - \text{output voltage})$  $V_{d2} = (V_{c1} + V_{22} - V_{12}) - V_c$  $= \left(\frac{(N+1) \times V_{in}}{1 - D}\right) + N \times \left(V_{in} - \frac{V_{in}}{1 - D}\right) - \left(N \times V_{in} - \frac{(2 \times N + 2) \times V_{in}}{1 - D}\right)$  $= -\left(\frac{(2N+1) \times V_{in}}{1 - D}\right)$

**2.3.5. Voltage Across Diode D1.** Mode 2 of topology 2 is used to analyze voltage across diode  $D_1$  as shown in Figure 2.9.

$$V_{d1} = V_{cc} - V_c$$

=  $\left(\frac{V_{in}}{1-D}\right) - \left(\frac{(2N+2) \times V_{in}}{1-D}\right)$

=  $-\left(\frac{(2N+1) \times V_{in}}{1-D}\right)$

Figure 2.9. Topology 2 operating mode 2

## 2.4. COMPARISON OF VOLTAGE STRESS IN BOTH TOPOLOGIES 1 AND 2

Based on the analysis shown in before sections, a comparison of voltage stress across various components is tabulated as shown below in Table 2.1.

|      | Component | Vo                                              | oltage Stress                       |

|------|-----------|-------------------------------------------------|-------------------------------------|

| S.No | Component | Topology 1                                      | Topology 2                          |

|      | Capacitor | $\left( (2N+1) \times V_{in} \right)$           | $((N+1) \times V_{in})$             |

| 1    | C1        | $\left(\begin{array}{c} 1-D \end{array}\right)$ | $\begin{pmatrix} 1-D \end{pmatrix}$ |

Table 2.1 Voltage stress comparison

| 2 | Output<br>Capacitor C | $\left(\frac{(3N+2)\times V_{in}}{1-D}\right)$ | $\left(\frac{(2N+2)\times V_{in}}{1-D}\right)$ |

|---|-----------------------|------------------------------------------------|------------------------------------------------|

| 3 | Switch                | $\left(\frac{V_{in}}{1-D}\right)$              | $\left(\frac{V_{in}}{1-D}\right)$              |

| 4 | Diode D1              | $\left(\frac{(4N+1)\times V_{in}}{1-D}\right)$ | $\left(\frac{(2N+1)\times V_{in}}{1-D}\right)$ |

| 5 | Diode D2              | $\left(\frac{(2N+1)\times V_{in}}{1-D}\right)$ | $\left(\frac{(2N+1)\times V_{in}}{1-D}\right)$ |

Table 2.1 Voltage stress comparison (Contd.)

#### 2.5. CURRENT STRESS OF COMPONENTS IN TOPOLOGY 1

This section describes some work about current equations of components in topology 1 which is one of the main requirements of component selection. The rms and average current equations are analyzed. In analysis of current equations for both the topologies 1 and 2, it is assumed that there is no leakage inductance (without clamp) and the duty ratios of both the upper and lower switches as the same.

**2.5.1. Magnetizing Currents of Inductors.** (Lm1 and Lm2): Mode 3 is used to explain the derivation of these currents. In this mode of operation, when S1 is ON and S2 is OFF, the value of the current flowing through Imm2 will be  $\frac{\langle I_{d1} \rangle}{(1-D)}$ , because of this current flowing through two secondary windings there is a reflected current of  $\left(\frac{2 \times N \times I_0}{1-D}\right)$ , therefore the average value of inductor 2 magnetizing current is  $I_{Im2} = \left(\frac{I_0}{1-D}\right) + \left(\frac{2 \times N \times I_0}{1-D}\right) = \left(\frac{2N+1}{1-D}\right) \times I_0$ . Based on the power balance equation of the converter,  $I_{Im1} + I_{Im2} = \left(\frac{(3N+2) \times I_0}{1-D}\right)$ . Hence,  $I_{Im1} = \left(\frac{(N+1) \times I_0}{1-D}\right)$ .

On assuming  $L_1 = L_2 = L$  and  $D_1 = D_2 = D$ , in operating mode 1, the voltage across inductors L1 and L2 will be  $V_{in}$ , hence  $\Delta i = \left(\frac{V_{in} \times D}{L \times f_{sw}}\right)$ . The rms values of inductor

magnetizing currents can be found from the equations as under

$$I_{lm1rms} = \sqrt{I_{lm1}^2 + \frac{\Delta i^2}{12}}, I_{lm2rms} = \sqrt{I_{lm2}^2 + \frac{\Delta i^2}{12}}$$

**2.5.2. Inductor Coil Currents.** (L1 and L2) Inductor coil average currents for various periods during the switching cycle is as shown below

$$I_{I1} = \begin{cases} \frac{I_{I1}\min + \left(\frac{(V \times (D - 0.5))}{L \times f_{SW}}\right) + I_{I1}\min}{2} & 0 < t < (D - 0.5)T \\ I_{Im1} + \left(\frac{(2 \times N \times I_0)}{(1 - D)}\right) & (D - 0.5)T < t < T/2 \\ \frac{I_{I1}\min + \left(\frac{(V \times 0.5)}{L \times f_{SW}}\right) + I_{I1}\max}{2} & T/2 < t < DT \\ \frac{I_0}{(1 - D)} & DT < t < T \end{cases}$$

$$I_{l2} = \begin{cases} \frac{I_{l2}\min + \left(\frac{(V \times (D - 0.5))}{L \times f_{sw}}\right) + I_{l2}\min}{2} & 0 < t < (D - 0.5)T \\ I_{ln} - I_o / (1 - D) & (D - 0.5)T < t < T / 2 \\ \frac{I_{l2}\min + \left(\frac{(V \times 0.5)}{L \times f_{sw}}\right) + I_{l2}\max}{2} & T / 2 < t < DT \\ 0 & DT < t < T \end{cases}$$

$I_{l1} = (2 \times D - 1) \times I_{lm1} + (3 \times N + 2) \times I_o$  $I_{l2} = (2 \times D - 1) \times I_{lm2} + (3 \times N + 2) \times I_o$

The rms values of the above currents can be calculated by applying the rms equation in given periods over a switching period.

**2.5.3. Switch Currents.** ( $S_1$  and  $S_2$ ) Switch average currents for various periods during the switching cycle is as shown below

$$I_{s1} = \begin{cases} \frac{I_{l1\min} + \left(\frac{(V \times (D - 0.5))}{L \times f_{sw}}\right) + I_{l1\min}}{2} & 0 < t < (D - 0.5)T \\ I_{ln} & (D - 0.5)T < t < T/2 \\ \frac{I_{l1\min} + \left(\frac{(V \times 0.5)}{L \times f_{sw}}\right) + I_{l1\max}}{2} & T/2 < t < DT \end{cases}$$

$$I_{s2} = \begin{cases} \frac{I_{l2}\min + \left(\frac{(V \times (D - 0.5))}{L \times f_{sw}}\right) + I_{l2}\min}{2} & 0 < t < (D - 0.5)T \\ I_{in} - \frac{I_o}{(1 - D)} & (D - 0.5)T < t < T/2 \\ \frac{I_{l2}\min + \left(\frac{(V \times 0.5)}{L \times f_{sw}}\right) + I_{l2}\max}{2} & T/2 < t < DT \\ I_{s1} = (2 \times D - 1) \times I_{lm1} + (3 \times N + 1) \times I_o \end{cases}$$

$$I_{s2} = (2 \times D - 1) \times I_{lm2} + (3 \times N + 1) \times I_o$$

The rms values of the above currents can be calculated by applying the rms equation in the given periods over a switching period.

**2.5.4. Diode Currents.**  $(D_1 \& D_2)$  The average current values of diodes  $D_1 \& D_2$  is equal to the load current. From above, the peak value of diode current will be

$$\frac{I_o}{(1-D)}$$

, the rms value will be  $\frac{I_o}{\sqrt{1-D}}$ .

**2.5.5. Capacitor C1 Current.** Capacitor current is same as diode  $D_1 \& D_2$  currents while charging and discharging respectively, as capacitor discharges when diode  $D_1$  conducts and charges when  $D_2$  conducts. The rms can be found as shown below

$$I_{c1rms} = \sqrt{\left(\frac{1}{T}\right) \times \left((1-D)T\right) \times \left(\left(\frac{I_o}{(1-D)}\right)^2 + \left(\frac{I_o}{(1-D)}\right)^2\right)}$$

$$= \sqrt{\frac{2}{(1-D)}} \times I_o$$

#### 2.6. CURRENT STRESS OF COMPONENTS IN TOPOLOGY 2

Similar to the work shown in the above section, this section will describe about various current equations of the components in topology 2.

**2.6.1. Magnetizing Currents of Inductors.** ( $L_{m1}$  and  $L_{m2}$ ) Mode 3 is used to explain the derivation of these currents. In this mode of operation when  $S_1$  is ON and

$S_2$  OFF, the average value of current flowing through  $I_{lm2}$  will be  $\frac{\langle I_{dl} \rangle}{(1-D)}$ , because of

this current flowing through the secondary winding there is a reflected current of

$\left(\frac{N \times I_o}{1-D}\right)$ , therefore the average value of inductor 2 magnetizing current is  $I_{lm2} = \left(\frac{N \times I_o}{1-D}\right)$ .

Based on the power balance equation of the converter,

$$I_{lm1} + I_{lm2} = \left(\frac{(2N+2) \times I_o}{1-D}\right)$$

Hence,

$$I_{lm1} = \left(\frac{(N+2) \times I_o}{1-D}\right)$$

On assuming  $L_1 = L_2 = L$  and  $D_1 = D_2 = D$ , in operating mode 1, the voltage across

inductors will be  $V_{in}$ , hence  $\Delta i = \left(\frac{V_{in} \times D}{L \times f_{sw}}\right)$ . The rms values of inductor magnetizing

currents can be found from the equations as under

$$I_{lm1rms} = \sqrt{I_{lm1}^2 + \frac{\Delta i^2}{12}}, I_{lm2rms} = \sqrt{I_{lm2}^2 + \frac{\Delta i^2}{12}}$$

**2.6.2. Inductor Coil Currents.** (L<sub>1</sub> and L<sub>2</sub>) Inductor coil average currents for various periods during the switching cycle is as shown below

$$I_{12} = \begin{cases} \frac{I_{11}\min + \left(\frac{(V \times (D - 0.5))}{L \times f_{sw}}\right) + I_{11}\min}{2} & 0 < t < (D - 0.5)T \\ I_{lm1} + \left(\frac{(2 \times N \times I_0)}{(1 - D)}\right) & (D - 0.5)T < t < T/2 \\ \frac{I_{lm1} + \left(\frac{(V \times 0.5)}{L \times f_{sw}}\right) + I_{l1}\max}{2} & T/2 < t < DT \\ \frac{I_0}{1 - D} & DT < t < T \\ \end{cases}$$

$$I_{12} = \begin{cases} \frac{I_{12}\min + \left(\frac{(V \times (D - 0.5))}{L \times f_{sw}}\right) + I_{l2}\min}{2} & 0 < t < (D - 0.5)T \\ I_{lm} - I_0/(1 - D) & (D - 0.5)T < t < T/2 \\ I_{l2}\min + \left(\frac{(V \times 0.5)}{L \times f_{sw}}\right) + I_{l2}\max}{2} & T/2 < t < DT \\ \end{cases}$$

$$I_{l2} = \begin{cases} \frac{(L \times f_{sw})}{2} & 0 < t < (D - 0.5)T \\ I_{ln} - I_o / (1 - D) & (D - 0.5)T < t < T \\ \frac{I_{l2} \min + \left(\frac{(V \times 0.5)}{L \times f_{sw}}\right) + I_{l2} \max}{2} & T / 2 < t < DT \\ 0 & DT < t < T \\ I_{l1} = (2 \times D - 1) \times I_{lm1} + (2 \times N + 3) \times I_o \end{cases}$$

$$I_{l1} = (2 \times D - 1) \times I_{lm1} + (2 \times N \times I_o)$$

$$I_{l2} = (2 \times D - 1) \times I_{lm2} + (2 \times N \times I_o)$$

The rms values of the above currents can be calculated by applying the rms equation in the given periods over a switching period.

**2.6.3. Switch Currents.** ( $S_1$  and  $S_2$ ) Switch average currents for various periods during the switching cycle is as shown below

$$I_{s1} = \begin{cases} \frac{I_{l1}\min + \left(\frac{(V \times (D - 0.5))}{L \times f_{sw}}\right) + I_{l1}\min}{2} & 0 < t < (D - 0.5)T \\ I_{ln} - \frac{I_o}{(1 - D)} & (D - 0.5)T < t < T/2 \\ \frac{I_{l1}\min + \left(\frac{(V \times 0.5)}{L \times f_{sw}}\right) + I_{l1}\max}{2} & T/2 < t < DT \end{cases}$$

$$I_{s2} = \begin{cases} \frac{I_{l2}\min + \left(\frac{(V \times (D - 0.5))}{L \times f_{sw}}\right) + I_{l2}\min}{2} & 0 < t < (D - 0.5)T \\ I_{ln} - \frac{N \times I_o}{(1 - D)} & (D - 0.5)T < t < T/2 \\ \frac{I_{l2}\min + \left(\frac{(V \times 0.5)}{L \times f_{sw}}\right) + I_{l2}\max}{2} & T/2 < t < DT \end{cases}$$

$I_{s1} = (2 \times D - 1) \times I_{lm1} + (2 \times N + 3) \times I_o$  $I_{s2} = (2 \times D - 1) \times I_{lm2} + (N + 2) \times I_o$

The rms values of the above currents can be calculated by applying the rms equation in the given periods over a switching period.

**2.6.4. Diode Currents.** (D<sub>1</sub> and D<sub>2</sub>) The average current values of diodes D1 & D2 is equal to the load current. From above, the peak value of diode current will be

$$\frac{I_0}{(1-D)}$$

, the rms value will be  $\frac{I_0}{\sqrt{1-D}}$ .

**2.6.5. Capacitor**  $C_1$  **Current**. Capacitor current is same as diode  $D_1 \& D_2$  currents while charging and discharging respectively, as capacitor discharges when diode  $D_1$  conducts and charges when  $D_2$  conducts. The rms can be found as shown below

$$I_{c1rms} = \sqrt{\left(\frac{1}{T}\right) \times \left((1-D)T\right) \times \left(\left(\frac{I_o}{(1-D)}\right)^2 + \left(\frac{I_o}{(1-D)}\right)^2\right)}$$

$$= \sqrt{\frac{2}{(1-D)}} \times I_o$$

#### 2.7. COMPARISON OF CURRENT STRESS IN BOTH THE TOPOLOGIES 1 & 2

Based on the analysis shown in before sections, a comparison of current stress across various components is tabulated as shown below in Table 2.2.

| S.No  | Component | Current Stress |            |  |  |

|-------|-----------|----------------|------------|--|--|

| 5.INO | Component | Topology 1     | Topology 2 |  |  |

Table 2.2 Current stress comparison

|   |                          | rable 2.2 Current stress comparise                              | on (conta.)                                                     |

|---|--------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|

| 1 | $I_{lm1}$                | $\left(\frac{(\mathrm{N+1})\times\mathrm{I_o}}{1-D}\right)$     | $\left(\frac{(N+2)\times I_{o}}{1-D}\right)$                    |

| 2 | Ilm2                     | $\left(\frac{(2N+1)\times I_{o}}{1-D}\right)$                   | $\left(\frac{\mathbf{N}\times\mathbf{I}_{o}}{1-D}\right)$       |

| 3 | Ist                      | $(2 \times D - 1) \times I_{im1} + (3 \times N + 1) \times I_o$ | $(2 \times D - 1) \times I_{lm1} + (2 \times N + 3) \times I_o$ |

| 4 | Is2                      | $(2 \times D - 1) \times I_{im2} + (3 \times N + 1) \times I_o$ | $(2 \times D - 1) \times I_{lm2} + (N + 2) \times I_o$          |

| 5 | <i>I</i> d1, <i>I</i> d2 | Io                                                              | Io                                                              |

| 6 | Id1rms ,<br>Id2rms       | $\frac{I_{o}}{\sqrt{1-D}}$                                      | $\frac{I_{o}}{\sqrt{1-D}}$                                      |

| 7 | <i>Ic</i> 1 <i>rms</i>   | $\sqrt{rac{2}{(1-D)}} 	imes I_o$                               | $\sqrt{rac{2}{(1-D)}} 	imes I_o$                               |

Table 2.2 Current stress comparison (Contd.)

# 2.8. COMPARISON OF SIMULATION RESULTS WITH THEORETICAL ANALYSIS

To validate the theoretically analyzed voltage and current stress equations, a comparison study with simulated values is discussed in this section. The comparison is performed at two different output powers 400W and 200W to focus on derived equations validity for various conditions. The specifications used for output power 400W are as tabulated in Table 2.3. Also Table 2.4, Table 2.5, Table 2.7, and Table 2.8 shows the results of theoretical to simulation results of voltage and current stress of components at 400W and 200W respectively.

Topology 1

Topology 2

Vin

20V

20V

Vout

400V

400V

Rout

400Ω

400Ω

D

0.75

0.75

Table 2.3 Simulation inputs for output power 400W

| fsw | 100kHz | 100kHz |

|-----|--------|--------|

| L   | 50µH   | 50µH   |

| N   | 1      | 1.5    |

| Io  | 1A     | 1A     |

| Iin | 20A    | 20A    |

Table 2.3 Simulation inputs for output power 400W (Contd.)

Table 2.4 Voltage stress comparison of theoretical to simulation results at 400W

|              | Volta       | ge Stress (V) | Voltage Stress (V) |           |  |  |

|--------------|-------------|---------------|--------------------|-----------|--|--|

|              | Т           | opology1      | Topology2          |           |  |  |

|              | Theoretical | Simulated     | Theoretical        | Simulated |  |  |

| Vc1          | 240         | 240           | 200                | 199.9     |  |  |

| Vsw_pk       | 80          | 80            | 80                 | 80        |  |  |

| $V_{D1\_pk}$ | 400         | 400           | 320                | 320       |  |  |

| VD2_pk       | 240         | 240           | 320                | 320       |  |  |

| Vo           | 400         | 400           | 400                | 400       |  |  |

Table 2.5 Current stress comparison of theoretical to simulation results at 400W

|          | Curre | ent Stress (A) | Currer | nt Stress (A) |

|----------|-------|----------------|--------|---------------|

|          | Te    | opology1       | Topolo | ogy2          |

| Ilm1_avg | 8     | 8              | 14     | 13.93         |

| Ilm2_avg | 12    | 12             | 6      | 6.16          |

| Ilm1rms               | 8.05  | 8.05  | 14.03 | 13.95 |

|-----------------------|-------|-------|-------|-------|

| Ilm2rms               | 12.03 | 12.03 | 6.06  | 6.16  |

| Is1_avg               | 9     | 9     | 13    | 13    |

| Is2_avg               | 10    | 10    | 6     | 5.96  |

| Is1rms                | 11.52 | 11.52 | 15.58 | 15.56 |

| Is2rms                | 11.68 | 11.68 | 7.38  | 7.4   |

| Id1_avg               | 1     | 1     | 1     | 1     |

| Id 2 _ avg            | 1     | 1     | 1     | 1.02  |

| Id 1rms               | 2     | 2     | 2     | 2.02  |

| Id 2 rms              | 2     | 2     | 2     | 2.1   |

| Ic1rms                | 2.83  | 2.84  | 2.83  | 2.99  |

| $\Delta i$ l _ ripple | 3     | 3     | 3     | 3     |

| Il1_avg               | 9     | 9     | 13    | 13.98 |

| Il2_avg               | 11    | 11    | 6     | 5.97  |

| Il1rms                | 10.03 | 10.03 | 14.23 | 14.65 |

Table 2.5 Current stress comparison of theoretical to simulation results at 400W (Contd.)

The specifications for the second iteration i.e. at output power 200W is as shown in Table 2.6.

|      | Topology 1 | Topology 2 |

|------|------------|------------|

| Vin  | 20V        | 20V        |

| Vout | 400V       | 400V       |

| Rout | 800Ω       | 800Ω       |

| D    | 0.75       | 0.75       |

| fsw  | 100kHz     | 100kHz     |

| L    | 50μΗ       | 50µH       |

| N    | 1          | 1.5        |

| Io   | 1A         | 1A         |

| Iin  | 10A        | 10A        |

Table 2.6 Simulation inputs for output power 200W

Table 2.7 Voltage comparison of theoretical to simulation results at 200W

|              | Voltage Stres           | ss (V) | Voltage Stress (V) |             |  |

|--------------|-------------------------|--------|--------------------|-------------|--|

|              | Topology                | 1      | Topology2          |             |  |

|              | Theoretical Simulated 7 |        | Theoretical        | Simulated   |  |

| $V_{c1}$     | 240                     | 240    | 200                | 199.9<br>80 |  |

| Vsw_pk       | 80                      | 80     | 80                 |             |  |

| $V_{D1\_pk}$ | 400                     | 400    | 320                | 320         |  |

| VD2_pk       | 240                     | 240    | 320                | 320         |  |

| Vo           | 400                     | 400    | 400                | 400         |  |

|                       | Current S | Stress (A) | Current S |      |

|-----------------------|-----------|------------|-----------|------|

|                       | Торо      | logy1      | Topology  | 2    |

| Iim1_avg              | 4         | 4          | 7         | 6.82 |

| Ilm2_avg              | 6         | 6          | 3         | 2.89 |

| Ilm1rms               | 4.09      | 4.1        | 7.05      | 6.87 |

| Ilm2rms               | 6.06      | 6.06       | 3.12      | 3.03 |

| Is1_avg               | 4.5       | 4.5        | 6.5       | 6.53 |

| Is2_avg               | 5         | 5          | 3         | 2.93 |

| Is1rms                | 5.79      | 5.8        | 7.82      | 7.88 |

| Is2rms                | 5.87      | 5.87       | 3.74      | 3.68 |

| Id1_avg               | 0.5       | 0.5        | 0.5       | 0.49 |

| Id 2 _ avg            | 0.5       | 0.5        | 0.5       | 0.43 |

| Id 1 rms              | 1         | 1          | 1         | 1.04 |

| Id2rms                | 1         | 1          | 1         | 0.98 |

| Ic1rms                | 1.41      | 1.44       | 1.41      | 1.48 |

| $\Delta i_l$ _ ripple | 3         | 3          | 3         | 3    |

| Il1_avg               | 4.5       | 4.5        | 6.5       | 7.15 |

| Il2_avg               | 5.5       | 5.5        | 3         | 2.96 |

| Il1rms                | 5.05      | 5.06       | 7.15      | 7.5  |

| Il2rms                | 5.96      | 5.96       | 3.74      | 3.72 |

Table 2.8 Current stress comparison of theoretical to simulation results at 200W

# 2.9. COMPARISON OF SIMULATION TO PRACTICAL WAVEFORMS IN BOTH THE TOPOLOGIES

This section shows various practical and simulated waveforms for both topologies 1 and 2. In order to perform practical testing, a hardware set up was built and various waveforms are captured.

**2.9.1. Topology 1.** This section shows practical and simulated waveforms for topology 1. The parameters of the hardware prototype to capture practical waveforms are as shown in Table 2.9.1.

| Iin   | Vo    | $R_o$      | Io          | $P_{in}$        | $P_o$                        | Ν                                | $f_{sw}$                |

|-------|-------|------------|-------------|-----------------|------------------------------|----------------------------------|-------------------------|

| (A)   | (V)   | $(\Omega)$ | (A)         | (W)             | (W)                          |                                  | (kHz)                   |

|       |       |            |             |                 |                              |                                  |                         |

|       |       |            |             |                 |                              |                                  |                         |

| 11.36 | 400.7 | 796        | 0.503       | 227.2           | 201.5                        | 1.4                              | 50                      |

|       | (A)   | (A) (V)    | (A) (V) (Ω) | (A) (V) (Ω) (A) | (A) (V) ( $\Omega$ ) (A) (W) | (A) (V) ( $\Omega$ ) (A) (W) (W) | (A) (V) (Ω) (A) (W) (W) |

Table 2.9.1 Hardware parameters for topology 1

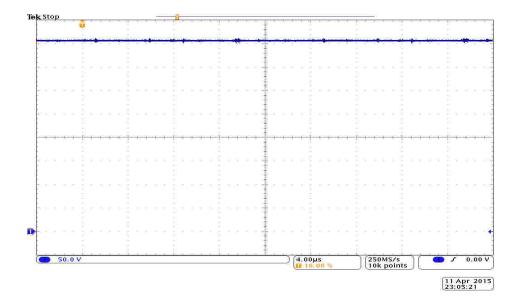

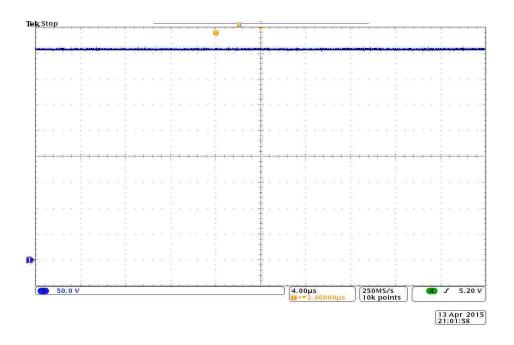

In Figure 2.10, each voltage division is 50V and total number of divisions is 8. So, the output voltage is  $8 \times 50 = 400V$ . Figure 2.10 and Figure 2.11 shows the practical and simulated output voltage waveforms for topology1.

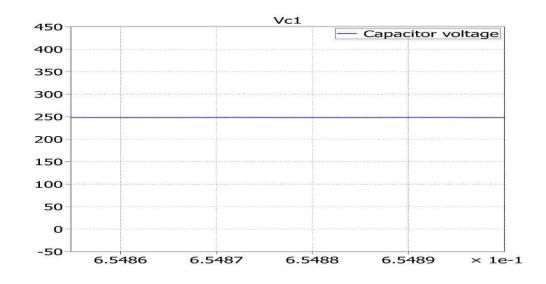

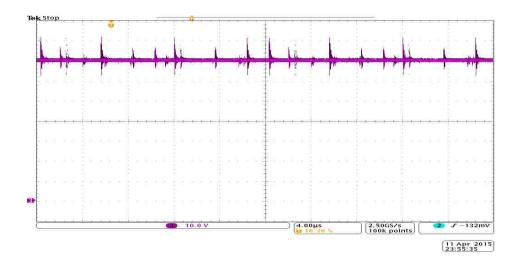

In Figure 2.12, each voltage division is 50V and total number of divisions is around 4.8. So, capacitor  $C_1$  voltage is  $5 \times 50 = 250V$ . Figure 2.12 and Figure 2.13 shows the practical and simulated voltage of capacitor  $C_1$  for topology 1. Practical

Figure 2.10. Practical waveform of Vout for topology 1

Figure 2.11. Simulated waveform of Vout for topology 1

Practical

Figure 2.12. Practical waveform of V<sub>c1</sub> for topology 1

Figure 2.13. Simulated waveform of  $V_{c1}$  for topology 1

In Figure 2.14, each voltage division is 10V and total number of divisions is 7.2. So, capacitor  $C_c$  voltage is  $7.2 \times 10 = 72V$ . Figure 2.14 and Figure 2.15 shows the practical and simulated waveforms of voltage across capacitor  $C_c$  for topology 1.

Figure 2.14. Practical waveform of Vcc for topology 1

Figure 2.15. Practical waveform of Vcc for topology 1

The below waveform across diode  $D_1$  was measured with positive terminal of the probe connected to cathode and negative to anode, hence the waveform above is positive. The ringing in the waveform is because of leakage inductance and parasitics and may also be because of loop inductance while measuring the waveform.

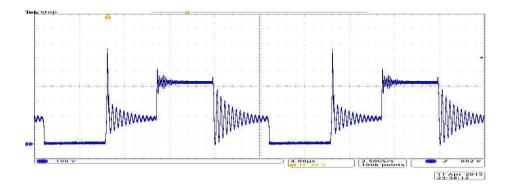

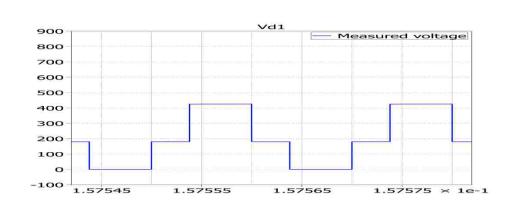

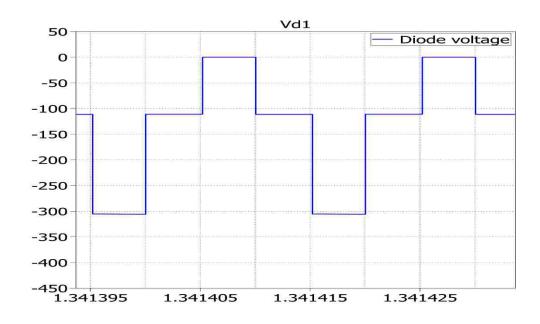

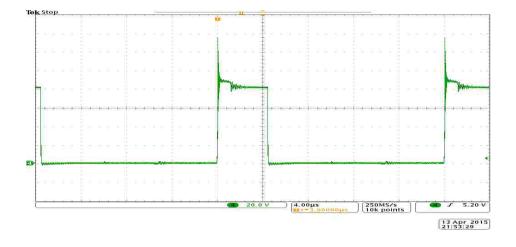

In Figure 2.16, each voltage division is 100V and total number of divisions is 4.5. So, diode  $D_1$  peak voltage is  $4.3 \times 100 = 430V$ . Figure 2.16 and Figure 2.17 shows the practical and simulated waveforms for voltage across diode  $D_1$  for topology 1.

Figure 2.16. Practical waveform of  $V_{d1}$  for topology 1

Simulated waveform

Figure 2.17. Simulated waveform of  $V_{d1}$  for topology 1

The below waveform across diode  $D_2$  was measured with positive terminal of the probe connected to cathode and negative to anode, hence the waveform above is positive. The ringing in the waveform is because of leakage inductance and parasitics and may also be because of loop inductance while measuring the waveform.

In Figure 2.18, each voltage division is 50V and total number of divisions is 4.8. So, diode  $D_2$  peak voltage is  $4.8 \times 50 = 240V$ . Figure 2.18 and Figure 2.19 shows the practical and simulated waveforms for voltage across diode  $D_2$  for topology 1.

Figure 2.18. Practical waveform of V<sub>d2</sub> for topology 1

Simulated waveform

Figure 2.19. Simulated waveform of  $V_{d2}$  for topology 1

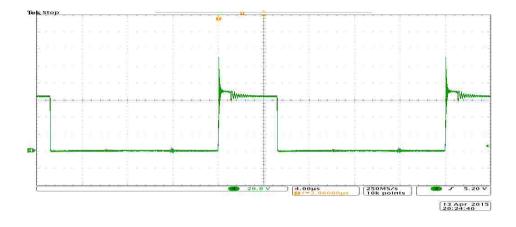

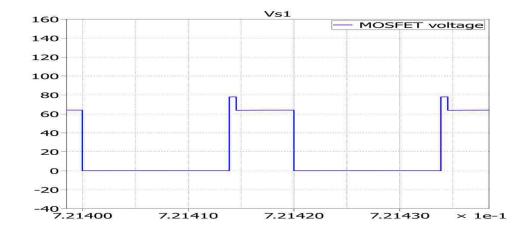

In Figure 2.20, each voltage division is 20V and total number of divisions is 3.2. So, switch peak voltage is  $3.2 \times 20 = 64V$ . The voltage spike is because of leakage inductance in the circuit during turn-off of switch. Figure 2.20 and Figure 2.21 shows the practical and simulated waveforms for voltage across switch S<sub>1</sub> for topology 1.

### Practical

Figure 2.20. Practical waveform of *V*<sub>ds1</sub> for topology 1

Figure 2.21. Simulated waveform of  $V_{ds1}$  for topology 1

In Figure 2.22, each voltage division is 20V and total number of divisions is 3.2. So, switch peak voltage is  $3.2 \times 20 = 64V$ . The voltage spike is because of leakage inductance in the circuit during turn-off of switch. Figure 2.22 and Figure 2.23 shows the practical and simulated waveforms for voltage across switch S<sub>2</sub> for topology 1.

Figure 2.22. Practical waveform of  $V_{ds2}$  for topology 1

Simulated waveform

Figure 2.23. Simulated waveform of Vds2 for topology 1

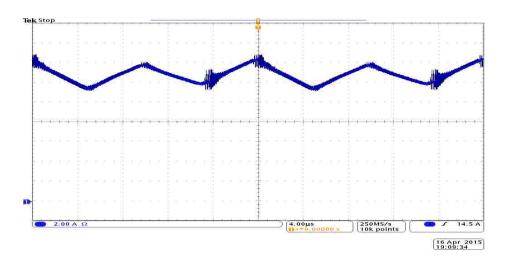

In Figure 2.24, each voltage division is 2A and total number of divisions is 6.4. So, peak input current is  $7 \times 2 = 14A$ . Figure 2.24 and Figure 2.25 shows the practical and simulated waveforms for input current of topology 1.

Practical

Figure 2.24. Practical waveform of *I*<sub>in</sub> for topology 1

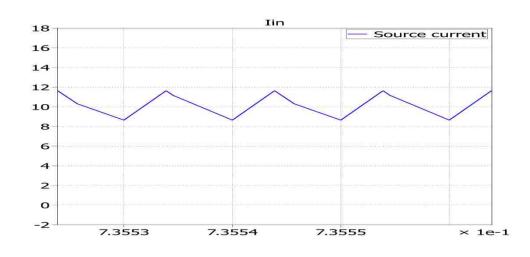

Figure 2.25. Simulated waveform of *I*<sub>in</sub> for topology 1

The ringing in the circuit is mainly because of parasitics. In Figure 2.26, each voltage division is 2A and peak of above current is 5.6 divisions. So,  $L_2$  peak primary inductor current is  $5.6 \times 2 = 11.2A$ . Figure 2.26 and Figure 2.27 shows the practical and simulated waveforms for inductor current  $I_{L_2}$  of topology 1.

### Practical

Figure 2.26. Practical waveform of *I*<sub>L2</sub> for topology 1

Figure 2.27. Simulated waveform of *I*<sub>L2</sub> for topology 1

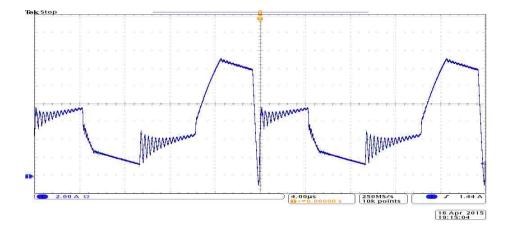

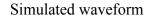

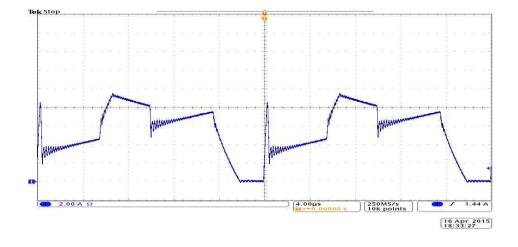

The ringing in the circuit is mainly because of parasitics. In Figure 2.28, each voltage division is 2A and peak of above current is 6.4 divisions. So,  $L_1$  peak primary inductor current is  $6.4 \times 2 = 12.8A$ . Figure 2.28 and Figure 2.29 shows the practical and simulated waveforms for inductor current  $I_{L_1}$  of topology 1.

Figure 2.28. Practical waveform of *I*<sup>L1</sup> for topology 1

Figure 2.29. Simulated waveform of *I*<sub>L1</sub> for topology 1

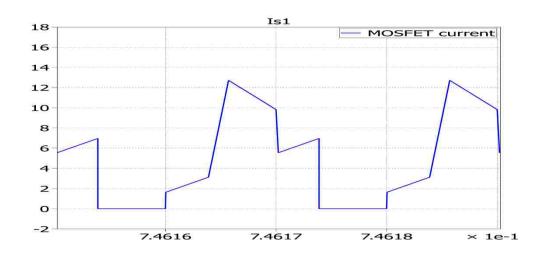

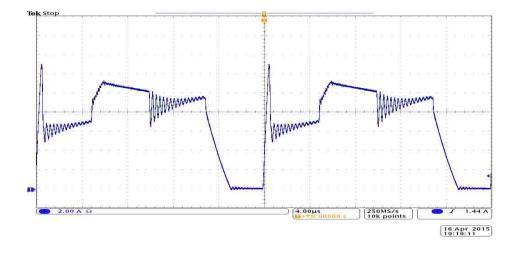

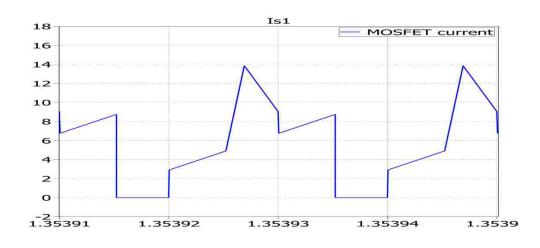

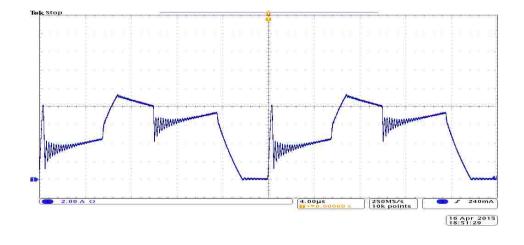

The ringing in the circuit is mainly because of parasitics. In Figure 2.30, each voltage division is 2A and peak of above current is 7.8 divisions. So,  $S_1$  peak current is 7.8×2=15.6*A*. Figure 2.30 and Figure 2.31 shows the practical and simulated waveforms for switch current  $I_{S_1}$  of topology 1.

Figure 2.30. Practical waveform of *I*<sup>s1</sup> for topology 1

Simulated waveform

Figure 2.31. Simulated waveform of  $I_{s1}$  for topology 1

The ringing in the circuit is mainly because of parasitics. In Figure 2.32, each voltage division is 2A and peak of above current is 5.6 divisions. So,  $S_2$  peak current is 5.6×2=11.2*A*. Figure 2.32 and Figure 2.33 shows the practical and simulated waveforms for switch current  $I_{S_2}$  of topology 1.

Figure 2.32. Practical waveform of *Is2* for topology 1

Figure 2.33. Simulated waveform of *I*<sub>s2</sub> for topology 1

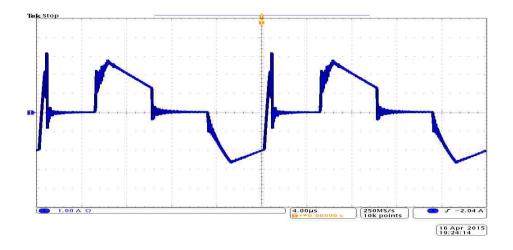

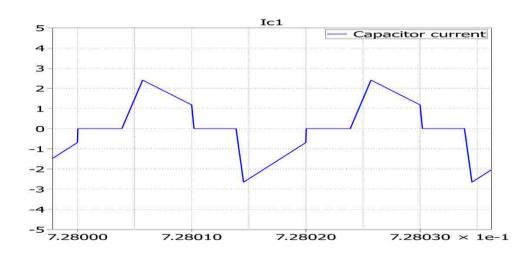

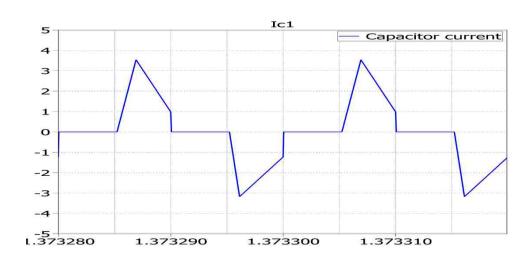

In Figure 2.34, each voltage division is 1A and peak of above current is 2.8 divisions. So,  $C_1$  peak current is  $2.8 \times 1 = 2.8A$ . Figure 2.34 and Figure 2.35 shows the practical and simulated waveforms of capacitor  $C_1$  current for topology 1.

#### Practical

Figure 2.34. Practical waveform of *I*<sub>c1</sub> for topology 1

Figure 2.35. Simulated waveform of  $I_{c1}$  for topology 1

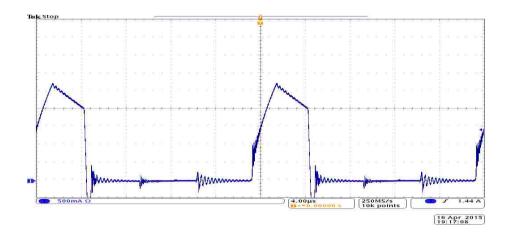

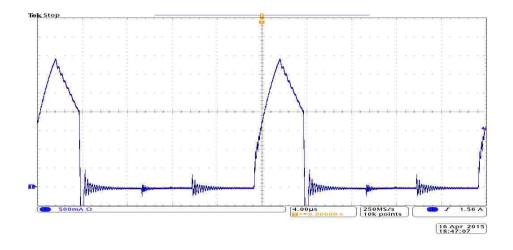

In Figure 2.36, each voltage division is 0.5A and peak of above current is 5.4 divisions. So,  $D_1$  peak current is  $5.4 \times 0.5 = 2.7A$ . Figure 2.36 and Figure 2.37 shows the practical and simulated waveforms of diode D<sub>1</sub> current for topology 1.

### Practical

Figure 2.36. Practical waveform of  $I_{d1}$  for topology 1

#### Simulation waveform

Figure 2.37. Simulated waveform of *I*<sub>d1</sub> for topology 1

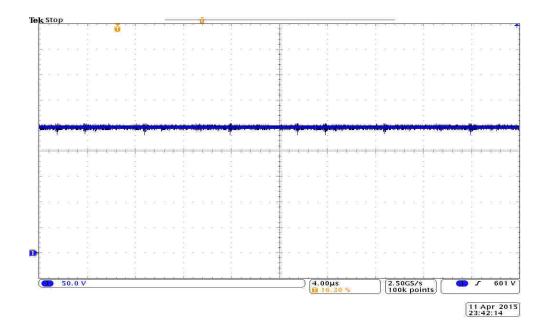

**2.9.2. Topology 2.** This section shows practical and simulated waveforms for topology 2. The parameters of the hardware prototype to capture practical waveforms are as shown in Table 2.9.2.

| $V_{in}$ | Iin   | $V_o$ | Ro  | Io    | Pin   | Po    | N   | $f_{sw}$ |

|----------|-------|-------|-----|-------|-------|-------|-----|----------|

| (V)      | (A)   | (V)   | (Ω) | (A)   | (W)   | (W)   |     | (kHz)    |

|          |       |       |     |       |       |       |     |          |

|          |       |       |     |       |       |       |     |          |

| 20       | 11.52 | 400   | 795 | 0.503 | 230.4 | 201.2 | 1.4 | 50       |

Table 2.9.2 Hardware parameters for topology 2

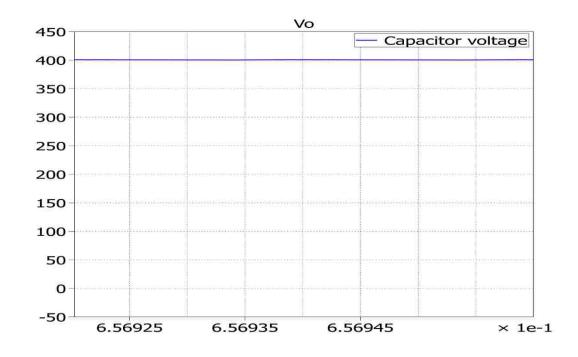

In Figure 2.38, each voltage division is 50V and total number of divisions is 8. So, the output voltage is  $8 \times 50 = 400V$ . Figure 2.38 and Figure 2.39 shows the practical and simulated waveforms of output voltage for topology 2.

Figure 2.38. Practical waveform of Vout for topology 2

### Simulated waveform

Practical

Figure 2.39. Simulated waveform of Vout for topology 2

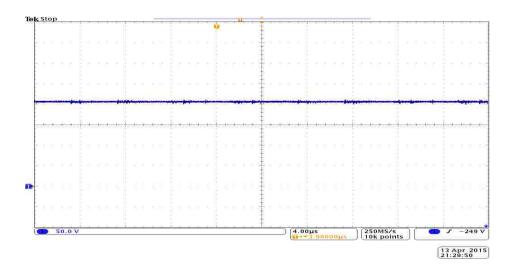

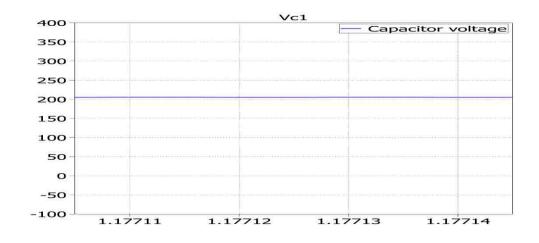

In Figure 2.40, each voltage division is 50V and total number of divisions is around 4. So, capacitor  $C_1$  voltage is  $4 \times 50 = 200V$ . Figure 2.40 and Figure 2.41 shows the practical and simulated waveforms of capacitor  $C_1$  voltage for topology 2.

Figure 2.40. Practical waveform of V<sub>c1</sub> for topology 2

### Simulated waveform

Figure 2.41. Simulated waveform of Vc1 for topology 2

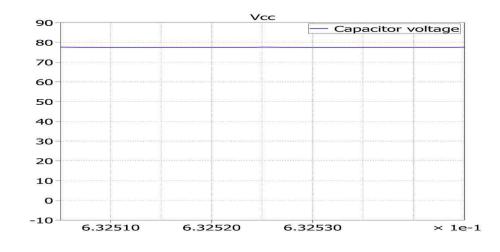

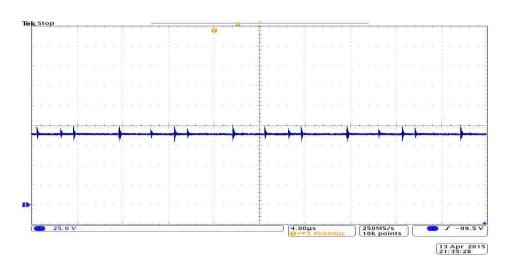

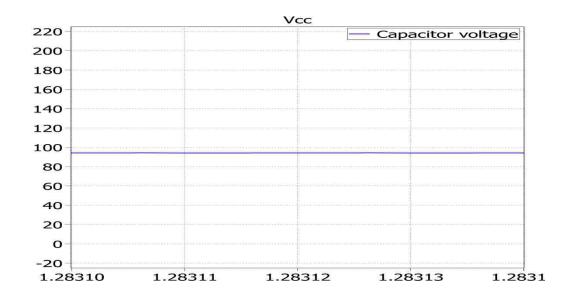

In Figure 2.42, each voltage division is 25V and total number of divisions is 3.6. So, capacitor  $C_c$  voltage is  $3.6 \times 25 = 90V$ . Figure 2.42 and Figure 2.43 shows the practical and simulated waveforms of capacitor  $C_c$  voltage for topology 2.

Figure 2.42. Practical waveform of V<sub>cc</sub> for topology 2

#### Simulated waveform

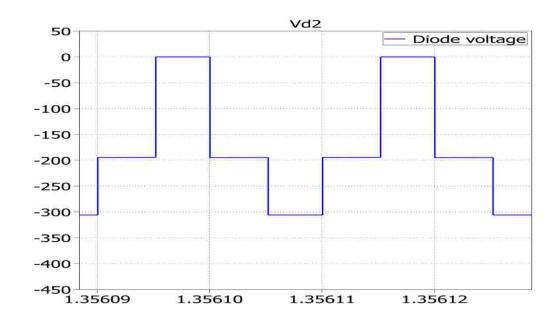

Figure 2.43. Simulated waveform of V<sub>cc</sub> for topology 2

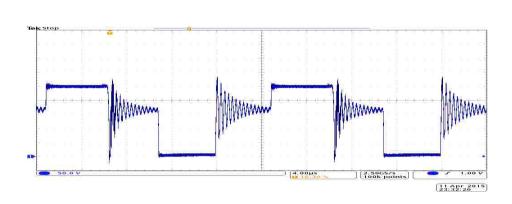

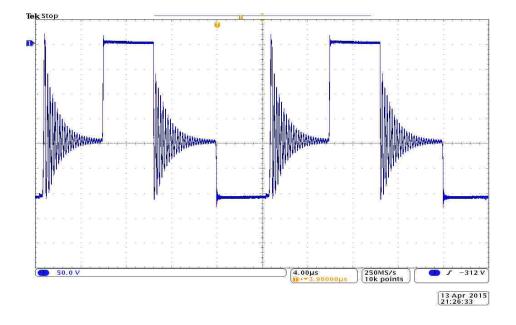

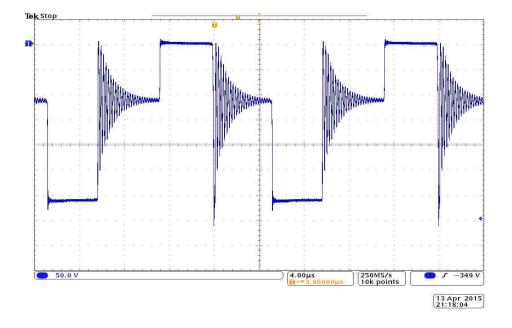

The below waveform across diode  $D_2$  was measured with negative terminal of the probe connected to cathode and positive to anode, hence the waveform above is negative. The ringing in the waveform is because of leakage inductance and parasitics and may also be because of loop inductance while measuring the waveform. In Figure 2.44, each voltage division is 50V and total number of divisions is 6.2. So, diode  $D_2$  peak voltage is  $6.2 \times 50 = 310V$ . Figure 2.44 and Figure 2.45 shows the practical and simulated waveforms of diode  $D_2$  voltage for topology 2.

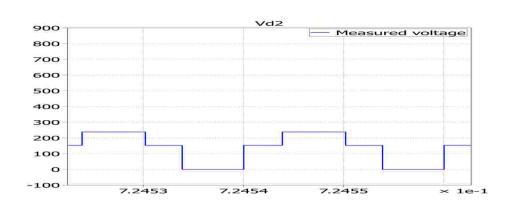

The below waveform across diode  $D_1$  was measured with negative terminal of the probe connected to cathode and positive to anode, hence the waveform above is negative. The ringing in the waveform is because of leakage inductance and parasitics and may also be because of loop inductance while measuring the waveform. In Figure 2.46, each voltage division is 50V and total number of divisions is 6.2. So, diode  $D_1$  peak voltage is  $6.2 \times 50 = 310V$ . Figure 2.46 and Figure 2.47 shows the practical and simulated waveforms of diode  $D_1$  voltage for topology 2.

# Practical

Figure 2.44. Practical waveform of  $V_{d2}$  for topology 2

Figure 2.45. Simulated waveform of  $V_{d2}$  for topology 2

# Practical

Figure 2.46. Practical waveform of  $V_{d1}$  for topology 2

Figure 2.47. Simulated waveform of  $V_{d1}$  for topology 2

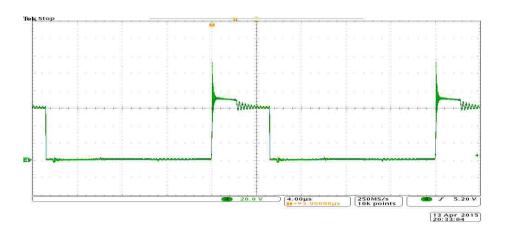

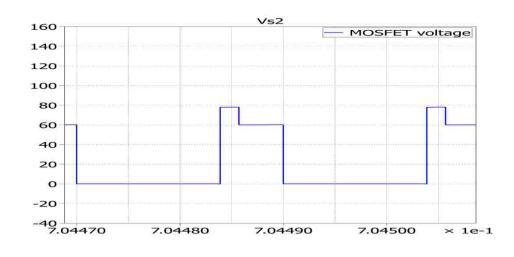

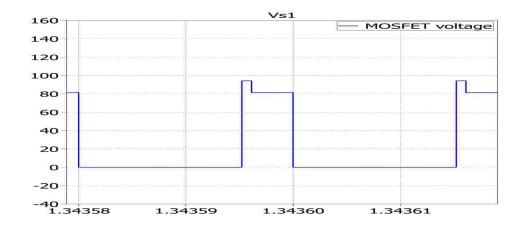

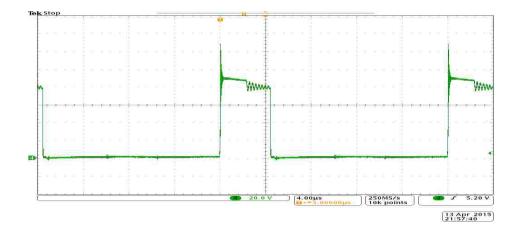

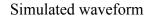

In Figure 2.48, each voltage division is 20V and total number of divisions is 4.2. So, peak switch voltage is  $4.2 \times 20 = 84V$ . The voltage spike is because of leakage inductance in the circuit during turn-off of switch. Figure 2.48 and Figure 2.49 shows the practical and simulated waveforms of switch V<sub>ds1</sub> voltage for topology 2.

### Practical

Figure 2.48. Practical waveform of V<sub>ds1</sub> for topology 2

Figure 2.49. Simulated waveform of Vds1 for topology 2

In Figure 2.50, each voltage division is 20V and total number of divisions is 4.2. So, peak switch voltage is  $4.2 \times 20 = 84V$ . The voltage spike is because of leakage inductance in the circuit during turn-off of switch. Figure 2.50 and Figure 2.51 shows the practical and simulated waveforms of switch V<sub>ds2</sub> voltage for topology 2.

Figure 2.50. Practical waveform of  $V_{ds2}$  for topology 2

Figure 2.51. Simulated waveform of  $V_{ds2}$  for topology 2

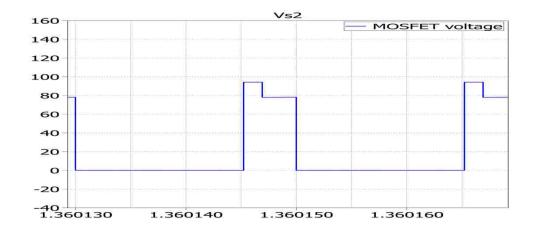

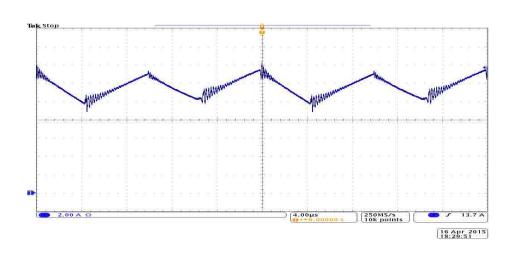

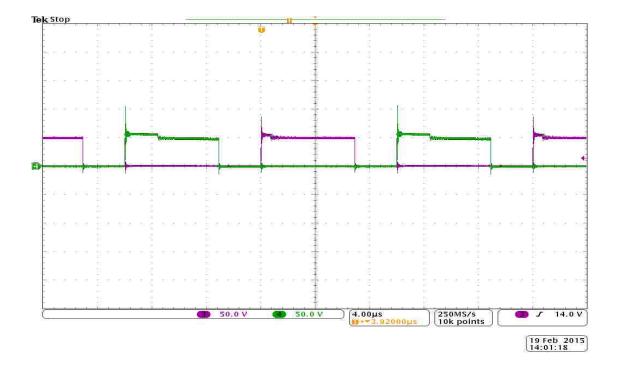

In Figure 2.52, each voltage division is 2A and total number of divisions is 7.6. So, peak input current is  $7 \times 2 = 14A$ . Figure 2.52 and Figure 2.53 shows the practical and simulated waveforms of input current I<sub>in</sub> for topology 2.

Figure 2.52. Practical waveform of Iin for topology 2

Simulated waveform

Figure 2.53. Simulated waveform of Iin for topology 2

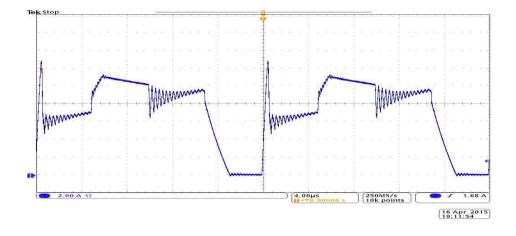

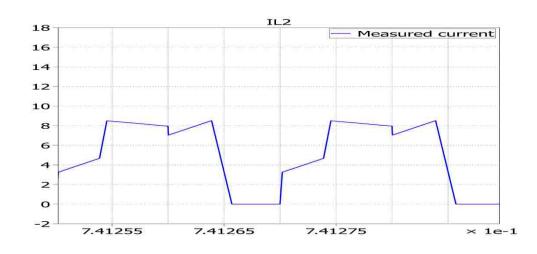

The ringing in the circuit is mainly because of parasitics. In Figure 2.52, each voltage division is 2A and peak of above current is 4.8 divisions. So,  $L_2$  peak primary inductor current is  $4.8 \times 2 = 9.6A$ . Figure 2.54 and Figure 2.55 shows the practical and simulated waveforms of inductor current  $I_{L2}$  for topology 2.

### Practical

Figure 2.54. Practical waveform of *IL*<sup>2</sup> for topology 2

Figure 2.55. Simulated waveform of *I*<sub>L2</sub> for topology 2

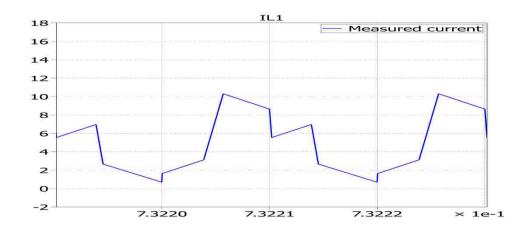

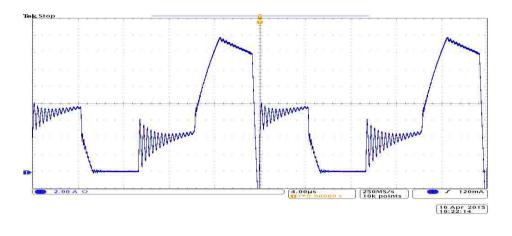

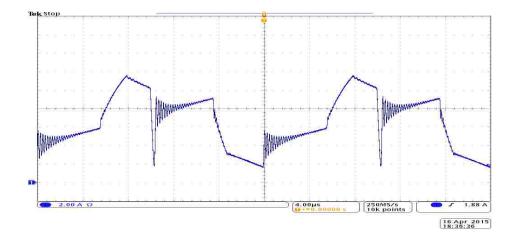

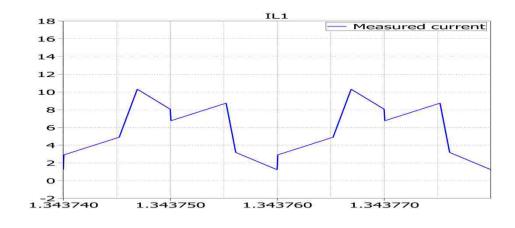

The ringing in the circuit is mainly because of parasitics. In Figure 2.56, each voltage division is 2A and peak of above current is 5.8 divisions. So, peak  $L_1$  primary inductor current is  $5.8 \times 2 = 11.6A$ . Figure 2.56 and Figure 2.57 shows the practical and simulated waveforms of inductor current  $I_{L_1}$  for topology 2.

Practical

Figure 2.56. Practical waveform of *I*<sub>L1</sub> for topology 2

Figure 2.57. Simulated waveform of *I*<sup>L1</sup> for topology 2

The ringing in the circuit is mainly because of parasitics. In Figure 2.58, each voltage division is 2A and peak of above current is 7.6 divisions. So, peak S<sub>1</sub> current is 7.6×2=15.2*A*. Figure 2.58 and Figure 2.59 shows the practical and simulated waveforms of switch current  $I_{s1}$  for topology 2.

Figure 2.58. Practical waveform of Is1 for topology 2

Figure 2.59. Simulated waveform of Is1 for topology 2

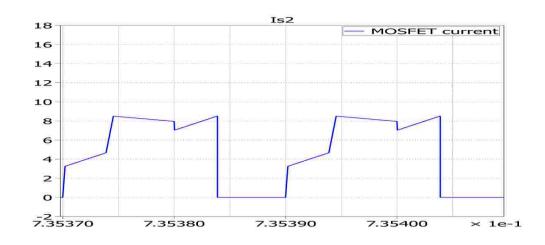

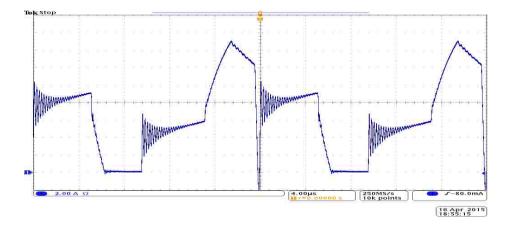

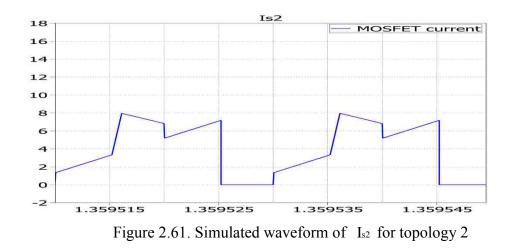

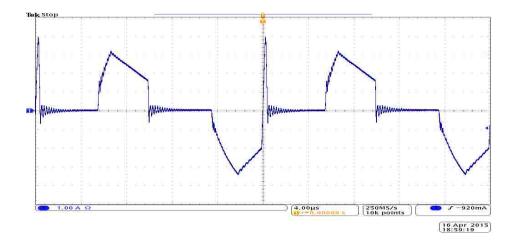

The ringing in the circuit is mainly because of parasitics. In Figure 2.60, each voltage division is 2A and peak of above current is 4.6 divisions. So, peak S<sub>2</sub> current is  $4.6 \times 2 = 9.2A$ . Figure 2.60 and Figure 2.61 shows the practical and simulated waveforms of switch current I<sub>s2</sub> for topology 2.

## Practical

Figure 2.60. Practical waveform of Is2 for topology 2

In Figure 2.62, each voltage division is 1A and peak of above current is 3.2 divisions. So,  $C_1$  peak current is  $3.2 \times 1 = 3.2A$ . Figure 2.62 and Figure 2.63 shows the practical and simulated waveforms of capacitor current  $I_{c1}$  for topology 2.

## Practical

Figure 2.62. Practical waveform of *I*<sub>c1</sub> for topology 2

Figure 2.63. Simulated waveform of *I*<sub>c1</sub> for topology 2

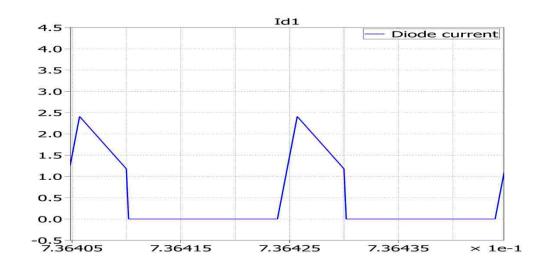

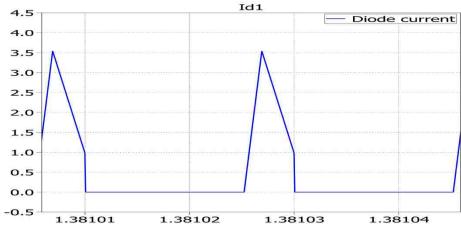

In Figure 2.64, each voltage division is 0.5A and peak of above current is 6.8 divisions. So,  $D_1$  peak current is  $6.8 \times 0.5 = 3.4A$ . Figure 2.64 and Figure 2.65 shows the practical and simulated waveforms of capacitor current  $I_{d_1}$  for topology 2.

## Practical

Figure 2.64. Practical waveform of *I*<sup>*d*1</sup> for topology 2

Figure 2.65. Simulated waveform of *I*<sub>d1</sub> for topology 2

# 3. POWER LOSS ANALYSIS IN TOPOLOGIES 1 AND 2 AND VARIATION OF EFFICIENCY WITH COUPLED INDUCTOR TURNS RATIO

## 3.1. POWER LOSS ANALYSIS IN TOPOLOGIES 1 & 2

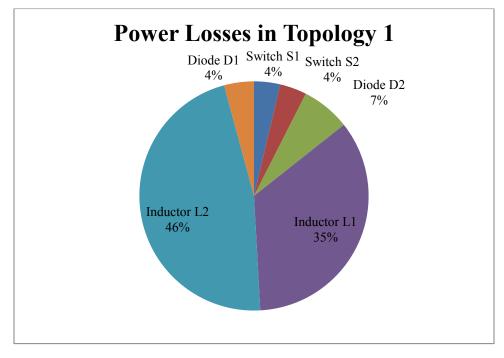

Based on the average and RMS current equations for all the components, a power loss analysis is carried out for both the topologies and the results are discussed in this section. The analysis is carried out with the below mentioned parameters for the converter in topology 1. The percentage and breakdown of losses in topology 1 are as mentioned in Figure 3.1 and Table 3.2 respectively. The parameters used for power loss analysis in topology 1 are as shown in Table 3.1.

| $V_{in}$ | Vo  | Ro         | D    | Io  | $P_o$ | f <sub>sw</sub> | N | Iin | L    |

|----------|-----|------------|------|-----|-------|-----------------|---|-----|------|

| (V)      | (V) | $(\Omega)$ |      | (A) | (W)   | (kHz)           |   | (A) | (µH) |

| 20       | 400 | 400        | 0.75 | 1   | 400   | 100             | 1 | 20  | 50   |

Table 3.1 Parameters for power loss analysis for topology 1

Figure 3.1. Power Loss Analysis in Topology 1

| 1 doie 5.2.Died                | kdown of losses in Topology I        |

|--------------------------------|--------------------------------------|

| Component                      | Power Loss (W)                       |

| MOSFET $(S_1)$                 | Conduction losses – 0.99             |

|                                | Switching losses – 0.204             |

|                                | Total losses – 1.20                  |

| MOSFET (S <sub>2</sub> )       | Conduction losses – 1.023            |

|                                | Switching losses – 0.204             |

|                                | Total losses – 1.23                  |

| Output diode (D <sub>2</sub> ) | Conduction losses – 2.23             |

| Diode (D <sub>1</sub> )        | Conduction losses – 1.37             |

| Inductor (L <sub>1</sub> )     | Conduction losses – 11.3             |

| Inductor (L <sub>2</sub> )     | Conduction losses – 15.17            |

|                                | Total losses in topology 1 are 32.49 |

Table 3.2.Breakdown of losses in Topology 1

The equation used for switching losses of MOSFET is

$P_{sw} = (\frac{1}{2} \times I_{Lavg} \times V_s \times (t_{off} + t_{on})) + (\frac{1}{2} \times f_{sw} \times C_{oss} \times V_s^2), \text{ where } I_{Lavg} \text{ is the new average current}$