#### Louisiana State University LSU Digital Commons

#### LSU Master's Theses

Graduate School

2013

## GPU acceleration of the Variational Monte Carlo Method for Many Body Physics

Kaushik Ragavan Rajagopalan Louisiana State University and Agricultural and Mechanical College, kaushikragavan89@gmail.com

Follow this and additional works at: https://digitalcommons.lsu.edu/gradschool\_theses Part of the <u>Electrical and Computer Engineering Commons</u>

**Recommended** Citation

Rajagopalan, Kaushik Ragavan, "GPU acceleration of the Variational Monte Carlo Method for Many Body Physics" (2013). *LSU Master's Theses*. 3622. https://digitalcommons.lsu.edu/gradschool\_theses/3622

This Thesis is brought to you for free and open access by the Graduate School at LSU Digital Commons. It has been accepted for inclusion in LSU Master's Theses by an authorized graduate school editor of LSU Digital Commons. For more information, please contact gradetd@lsu.edu.

# GPU ACCELERATION OF THE VARIATIONAL MONTE CARLO METHOD FOR MANY BODY PHYSICS

A Thesis

Submitted to the Graduate Faculty of the Louisiana State University and Agricultural and Mechanical College in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

in

The Department of Electrical and Computer Engineering

by Rajagopalan Kaushik Ragavan B.ENG in Electronics and Communication, Anna University, Chennai, May 2010 May 2013

## Acknowledgments

My sincere thanks to Dr. David Koppelman for his valuable teachings on GPU, CPU architecture and on High Performance computing, which motivated me to pick my thesis in this domain. He was a great mentor and guided me on every step of my thesis.

I would like to thank Dr.Mark Jarrell, Dr.Juana Moreno and the LA-Sigma group for funding this research.

I would like to thank Dr.Xin Li and Dr.Juana Moreno for accepting my request to be a part of the thesis committee.

I would also like to thank other colloborators: Dr.Ka Ming Tam, Dr.Zhifeng Yun, Niladri Sengupta and Dr.Sandeep Pathak for their valuable contributions and sharing of thoughts.

Finally, I would like to thank my parents for supporting my education till now. It was their motivation and trust which made my degree possible.

## **Table of Contents**

| ACKNOWLEDGMENTS                                                                                                                                                                                                               | ii                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|

| LIST OF TABLES                                                                                                                                                                                                                | v                                                                                                       |

| LIST OF FIGURES                                                                                                                                                                                                               | vi                                                                                                      |

| ABSTRACT                                                                                                                                                                                                                      | viii                                                                                                    |

| CHAPTER                                                                                                                                                                                                                       |                                                                                                         |

| 1       VARIATIONAL MONTE CARLO (VMC)         1.1       Trial Wavefunction         1.2       The VMC Algorithm         1.2.1       Difficulty of VMC         1.2.2       Faster VMC         1.2.3       Summary of VMC method | $     \begin{array}{c}       1 \\       1 \\       2 \\       3 \\       4 \\       5     \end{array} $ |

| 2 PRIOR WORK<br>2.1 CPU Implementation<br>2.2 MPI Implementation<br>2.3 GPU Implementation                                                                                                                                    | 7<br>7<br>7<br>7                                                                                        |

| <ul> <li>3 GRAPHICS PROCESSING UNITS</li></ul>                                                                                                                                                                                | 9<br>9<br>11                                                                                            |

| <ul> <li>4.1 Pseudocode for the VMC Method</li></ul>                                                                                                                                                                          | 14<br>14<br>19<br>20<br>22<br>24<br>24<br>24<br>25<br>25<br>25                                          |

| <ul><li>4.6 Results</li><li>4.7 Multiple MCs and the system behavior</li></ul>                                                                                                                                                | 26<br>31                                                                                                |

| 5 PORTING VMC TO CUDA                                                                                                                                                                                                         | 33                                                                                                      |

|       | 5.1  | GPU Acceleration of the VMC Method                       | 33  |

|-------|------|----------------------------------------------------------|-----|

|       | 5.2  | Naïve Implementation                                     | 33  |

|       | 5.3  | Execution configuration                                  | 35  |

|       | 5.4  | Memory requirements and cache behaviour                  | 36  |

|       | 5.5  | Memory Access Pattern                                    | 39  |

|       |      | 5.5.1 Function DetPByDet                                 | 39  |

|       |      | 5.5.2 Function UpdateConfig                              | 42  |

|       | 5.6  | Optimization efforts                                     | 44  |

|       |      | 5.6.1 Thread selection in depth                          | 44  |

|       |      | 5.6.2 Elimination of redundant copies of a configuration | 46  |

|       |      | 5.6.3 Optimized memory access pattern                    | 46  |

|       | 5.7  | Merger of Equilibration and Accumulation                 | 51  |

|       | 5.8  | Streamlined function                                     | 53  |

| 6     | RES  | ULTS                                                     | 57  |

|       | 6.1  | Input Parameters                                         | 57  |

|       | 6.2  | Comparison between a CPU and GPU code                    | 57  |

|       | 6.3  | Comparison between MPI-CPU and GPU code                  | 57  |

|       | 6.4  | GPU results in depth                                     | 60  |

| 7     | CON  | ICLUSION                                                 | 64  |

|       | 7.1  | Conclusion                                               | 64  |

|       | 7.2  | Future Work                                              | 64  |

| REFE  | RENC | ZES                                                      | 65  |

| APPEI | NDIX |                                                          |     |

|       | a    |                                                          |     |

| А     |      | DA CODE FOR THE MERGED EQUILIBRATION AND                 | 0.0 |

|       | ACC  | CUMULATION STAGE                                         | 68  |

| В     | DEV  | VICE FUNCTIONS                                           | 74  |

# List of Tables

| 4.1 | Data Structures and Memory requirements             | 19 |

|-----|-----------------------------------------------------|----|

| 4.2 | Classes used in the Implementation of VMC           | 19 |

| 4.3 | FLOPS calculation for the VMC method                | 24 |

| 4.4 | Execution time for $L = 5$                          | 27 |

| 4.5 | Execution time for $L = 9$                          | 28 |

| 4.6 | Execution time for $L = 15$                         | 29 |

| 5.1 | Speculation of a GPU's cache behaviour for $L = 5$  | 37 |

| 5.2 | Speculation of a GPU's cache behaviour for $L = 9$  | 37 |

| 5.3 | Speculation of a GPU's cache behaviour for $L = 15$ | 38 |

| 5.4 | Summary of Memory prediction for $L = 5$            | 38 |

| 5.5 | Threads per MC and Number of MCs per SM             | 46 |

| 5.6 | Occupancy calculation for $L = 5$                   | 46 |

| 6.1 | Input Parameters                                    | 58 |

| 6.2 | Comparison of CPU vs GPU Performance for bfactor=8  | 59 |

| 6.3 | Comparison of CPU vs GPU Performance for bfactor=16 | 59 |

| 6.4 | Nodal architecture of Philip Supercomputer          | 59 |

| 6.5 | Comparison of MPI vs GPU Performance                | 60 |

| 6.6 | GPU execution time in cycles for $L = 5$            | 60 |

| 6.7 | GPU execution time in cycles for $L = 9$            | 61 |

| 6.8 | GPU execution time in cycles for $L = 15$           | 62 |

# List of Figures

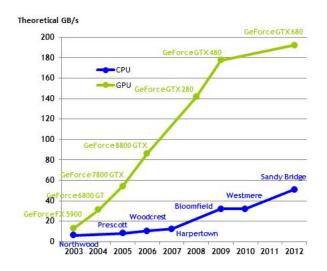

| 3.1 | Floating Point operations per second for CPU vs GPU, Source:<br>CUDA Programming guide                 | 10 |

|-----|--------------------------------------------------------------------------------------------------------|----|

| 3.2 | Memory Bandwidth for CPU vs GPU, Source: CUDA Program-<br>ming guide                                   | 10 |

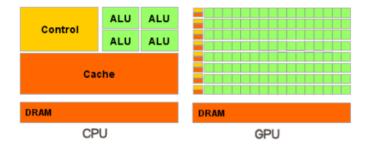

| 3.3 | GPU vs CPU architecture, Source: CUDA Programming guide                                                | 11 |

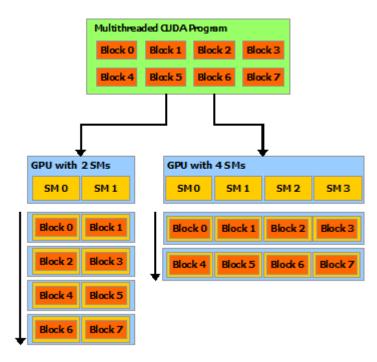

| 3.4 | Automatic Scalability of Applications, Source: CUDA Program-<br>ming guide                             | 12 |

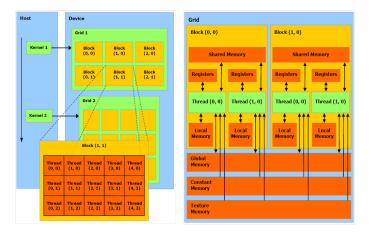

| 3.5 | CUDA Thread hierarchy, Source: Programming Massively Par-<br>allel Processors- A hands-on Approach     | 13 |

| 3.6 | CUDA Memory Hierarchy, Source CUDA Programming guide                                                   | 13 |

| 4.1 | Sequential Memory Access Pattern for the up spin: (a) $\Psi^{-1}$ , (b)<br>Plist, (c) Pairfunction     | 20 |

| 4.2 | Sequential Memory Access Pattern for the down spin: (a) $\Psi^{-1}$ ,<br>(b) Plist, (c) Pairfunction   | 21 |

| 4.3 | Update of a configuration for the up spin                                                              | 22 |

| 4.4 | Update of a configuration for the down spin                                                            | 23 |

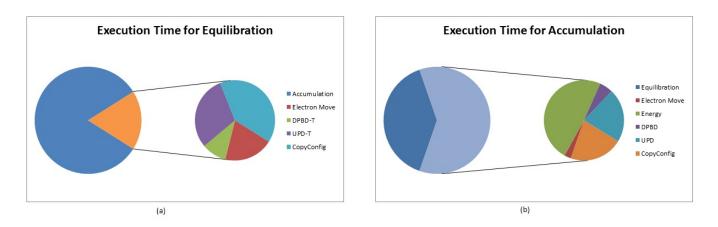

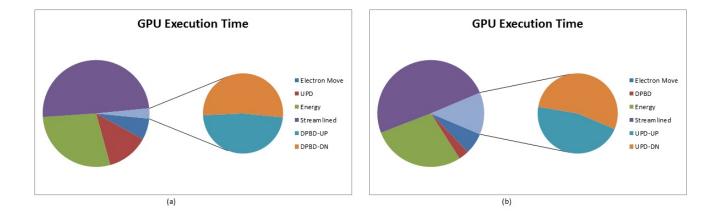

| 4.5 | Pie chart for $L = 5$ :(a) Split of Equilibration, (b) Split of Accumulation                           | 26 |

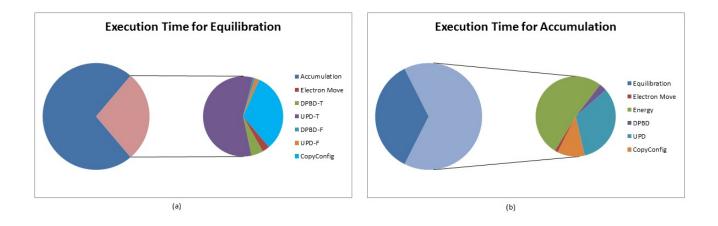

| 4.6 | Pie chart for $L = 9$ :(a) Split of Equilibration, (b) Split of Accumulation                           | 30 |

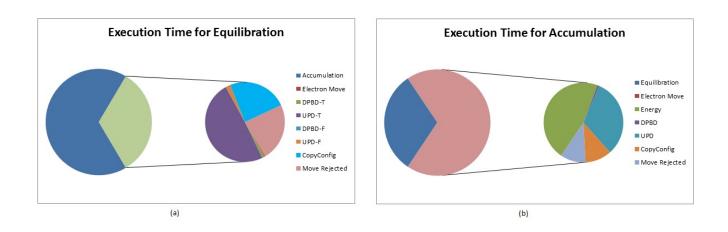

| 4.7 | Pie chart for $L = 15$ :(a) Split of Equilibration, (b) Split of Accumulation                          | 30 |

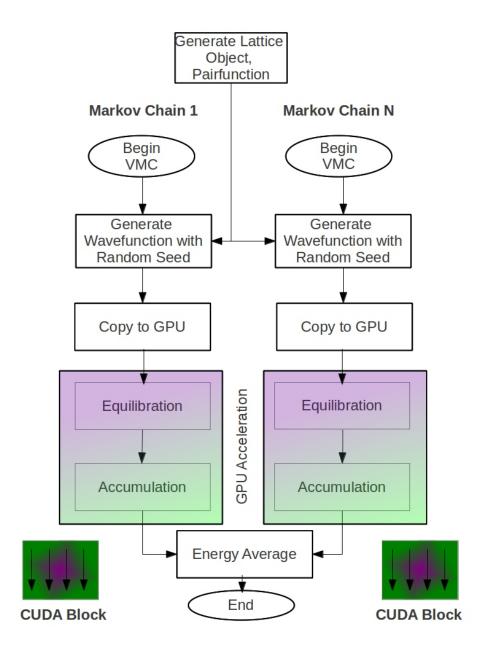

| 5.1 | VMC Workflow for Multiple Markov Chains (MCs)                                                          | 34 |

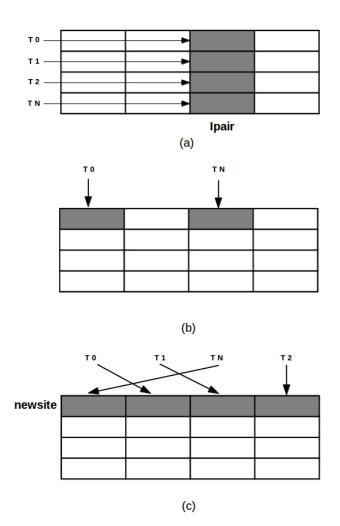

| 5.2 | Memory Access Pattern for up spin: (a) $\Psi^{-1}$ , (b) Picking a site from Plist, (c) Pairfunction   | 40 |

| 5.3 | Memory Access Pattern for down spin: (a) $\Psi^{-1}$ , (b) Picking a site from Plist, (c) Pairfunction | 41 |

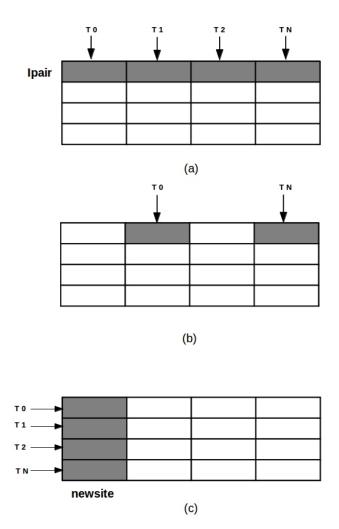

| 5.4  | Memory Access Pattern for up spin: (a) $\Psi^{-1}$ , (b) Picking a site<br>from Plist, (c) Pairfunction                                                                                                                                                                                                                                                                                 | 43 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 5.5  | Memory Access Pattern for down spin: (a) $\Psi^{-1}$ , (b) Picking a site from Plist, (c) Pairfunction                                                                                                                                                                                                                                                                                  | 45 |

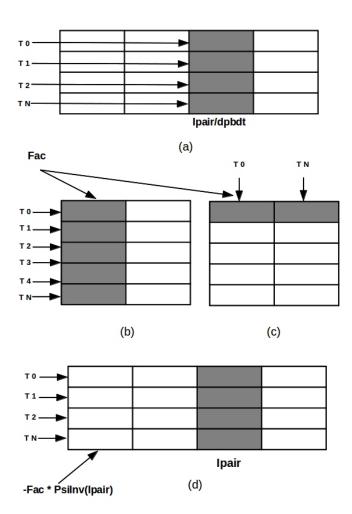

| 5.6  | Optimization for up spin: (a) $\Psi^{-1}$ , (b) Plist, (c) Pairfunction,<br>(d) Reduction on a shared memory                                                                                                                                                                                                                                                                            | 48 |

| 5.7  | Optimization for down spin: (a) $\Psi^{-1}$ , (b) Plist, (c) Transposed<br>Pairfunction, (d) Reduction on a shared memory.                                                                                                                                                                                                                                                              | 49 |

| 5.8  | Optimization for up spin: (a) $\Psi^{-1}$ - update of $Ipair^{th}$ column,<br>(b) $\Psi^{-1}$ with threads-per-col, $T_P$ , (c) Pairfunction, (d) $\Psi^{-1}$ -<br>update of other columns.                                                                                                                                                                                             | 50 |

| 5.9  | Optimization for down spin: (a) $\Psi^{-1}$ - update of $Ipair^{th}$ row, (b) $\Psi^{-1}$ with a blocking factor, $bfactor$ (c) Transposed Pairfunction, (d) $\Psi^{-1}$ - update of other rows.                                                                                                                                                                                        | 52 |

| 5.10 | Optimization for up spin: (a) $\Psi^{-1}$ - with $T_P$ , (b) Pairfunction,<br>(c) Reduction in a shared memory to obtain dpbd1, (d) Calcu-<br>lation of dot product using $Jpair^{th}$ row of $\Psi^{-1}$ , (e) Calculation<br>of dot product using Transposed pairfunction, (f) Reduction in<br>a shared memory to obtain the final $dpbd$ : $dpbd = dpbd1 * Reduction(colval)$        | 55 |

| 5.11 | Optimization for down spin: (a) $\Psi^{-1}$ - with $T_B$ , (b) Pairfunction,<br>(c) Reduction in a shared memory to obtain dpbd1, (d) Calcula-<br>tion of dot product using $Jpair^{th}$ column of $\Psi^{-1}$ , (e) Calculation<br>of dot product using Transposed pairfunction, (f) Reduction in<br>a shared memory to obtain the final $dpbd$ : $dpbd = dpbd1 * Reduction(rowval)$ . | 56 |

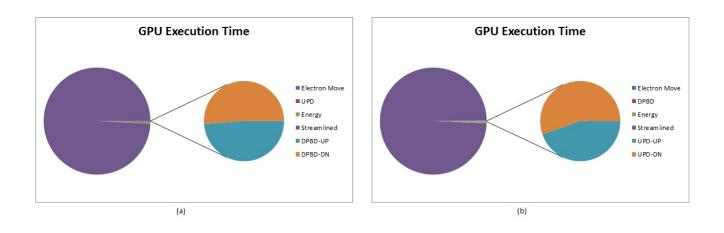

| 6.1  | Pie chart for $L = 5$                                                                                                                                                                                                                                                                                                                                                                   | 61 |

| 6.2  | Pie chart for $L = 9$                                                                                                                                                                                                                                                                                                                                                                   | 62 |

| 6.3  | Pie chart for $L = 15$                                                                                                                                                                                                                                                                                                                                                                  | 63 |

## Abstract

High-Performance computing is one of the major areas making inroads into the future for large-scale simulation. Applications such as 3D nuclear test, Molecular Dynamics, and Quantum Monte Carlo simulations are now developed on supercomputers using the latest computing technologies. As per the TOP500 supercomputers rating, most of today's supercomputers are now *heterogeneous*: with massively parallel Graphics Processing Units (GPU) equipped with Multi-core CPU(s) to increase the computational capacity.

The Variational Monte Carlo(VMC) method is used in the Many Body Physics to study the ground state properties of a system. The wavefunction depends on some variational parameters, which contain the physics for a better prediction. In general, the variational parameters are chosen to realize some sort of order or broken symmetry such as *superconductivity* and *magnetism*.

The variational approach is computationally expensive and requires a large number of trajectories to obtain convergence. The Markov chains (MCs) exhibit abundant *data parallelism* and parallelizing across CPU clusters will prove to be expensive and does not scale in proportion to the system size. Hence, this method will be a suitable candidate on a massively parallel Graphics Processing Unit (GPU).

In this research, we discuss about the various optimization and parallelization strategies adopted to port the VMC method to a NVIDIA GPU using CUDA. We obtained a speedup of nearly 3.85 X compared to the MPI implementation [4] and a speedup of up to 19 X compared to an object-oriented C++ code.

# Chapter 1 Variational Monte Carlo (VMC)

### 1.1 Trial Wavefunction

Variational Monte Carlo (VMC) method is a direct application of Monte Carlo integration to strongly correlated systems. The variational approach has been used widely in different areas of condensed matter physics, in particular the d-wave superconducting state of the high  $T_C$  cuprates at T=0 [1]. In quantum mechanics, variational principle can be derived by expanding a normalized trial wavefunction,  $\Psi_T$ , in terms of the exact normalized eigenstates of the Hamiltonian [9].

$$\Psi_T = \sum_{i=0}^{\infty} c_i \Psi_i, \qquad (1.1)$$

where  $c_i$  is given by,

$$\sum_{i=0}^{\infty} |c_i|^2 = 1 \tag{1.2}$$

The many-body Hamiltonian,  $\hat{H}$ , evaluated by,

$$\left\langle \Psi_T \middle| \hat{H} \middle| \Psi_T \right\rangle = \left\langle \sum_i c_i \Psi_i \middle| \hat{H} \middle| \sum_j c_j \Psi_j \right\rangle = \sum_i |c_i|^2 \epsilon_i, \tag{1.3}$$

where  $\epsilon_i = \left\langle \Psi_i \middle| \hat{H} \middle| \Psi_i \right\rangle$

From the above equations [9], the expectation value of a trial wavefunction with the Hamiltonian must be greater than or equal to the true ground state energy. The variational method depends mostly on the trial wavefunction used. Wavefunctions are normally obtained by Hartree-Fock or similar methods and additional parameters added to build in additional physics such as, known limits and derivatives of the many-body wavefunction. The wavefunction is then further optimized by the variational parameters.

From [4], an example of a trial wavefunction is then taken to be,

$$\Psi(R) = D(R)exp\left[\sum_{i< j}^{N} -u(r_{ij})\right],$$

(1.4)

where D is a determinant of Hartree-Fock or meanfield solutions. The variational parameters for constructing D is used to optimize the trial wavefunction. The extra projection factor u is included in the above wavefunction.

### 1.2 The VMC Algorithm

The VMC algorithm consists of two distinct phases [9, 5]: Equilibration and Accumulation (Measurement). In the first phase, the system is made to equilibrate and sampled for  $|\Psi|^2$ . In the second phase, the energies and other observables are accumulated. Thus we perform random walk across configurations.

#### 1. Equilibration:

- (a) Generate an initial random configuration.

- (b) For each electron in the configuration:

- i. Propose a move from  $m_r$  to  $m'_r$

- ii. Compute the ratio  $R=|\Psi(m_r')/\Psi(m_r)|^2$

- iii. Perform metropolis acceptance comparison min(1, R)

- iv. If the move is accepted, update the configuration.

- v. Else restore the old configuration.

- (c) Repeat the above steps until the system equilibrates.

#### 2. Accumulation:

- (a) Repeat the same procedure from Equilibration.

- (b) Accumulate the local energy and other observable parameters at  $m'_r$  and  $m_r$ ,

- (c) Perform metropolis acceptance comparison min(1, R)

- (d) Repeat the above steps until energies are accumulated

#### 1.2.1 Difficulty of VMC

The energy function [5] is defined as,

$$E(\alpha_i) = \frac{\sum_C \Psi_{\alpha}^*(C) H \Psi_{\alpha}(C)}{\sum_C \Psi_{\alpha}^*(C) \Psi_{\alpha}(C)}$$

(1.5)

In many of these cases, the wavefunction in real space is given by,  $\Psi_{\alpha}(r_{1\uparrow}, \ldots, r_{N\uparrow}, r_{1\downarrow}, \ldots, r_{N\downarrow})$ , where  $r_{i\sigma}$  are the coordinates of the electrons on a lattice and  $C \equiv (r_{1\uparrow}, \ldots, r_{N\uparrow}, r_{1\downarrow}, \ldots, r_{N\downarrow})$ , a configuration of electrons.

To sum over all configurations, for example: a lattice with 100 sites and  $50 \uparrow$  and  $50 \downarrow$  electrons, we need to visit over  $10^{60}$  configurations. To overcome this difficulty, we use Monte Carlo method to perform the sum[2].

$$E(\alpha_i) = \sum_C P(C) \frac{H\Psi_{\alpha}(C)}{\Psi_{\alpha}(C)}$$

(1.6)

where P(C), the probability of the configuration, is given by,

$$P(C) = \frac{|\Psi_{\alpha}(C)|^2}{\sum_C \Psi_{\alpha}^*(C)\Psi_{\alpha}(C)}$$

For any operator O

$$\langle O \rangle = \sum_{C} P(C) \frac{O\Psi_{\alpha}(C)}{\Psi_{\alpha}(C)}$$

(1.7)

where,  $\sum_{C} P(C) = 1$ .

To avoid visiting all the configurations, we will visit the "most important" configurations [5] and add up the corresponding contribution. The configurations with "high probability" are considered to be important. This is called as *importance sampling* [5].

Using the importance sampling, accurate results for various quantites can be obtained by a smaller number of Monte Carlo sweeps,  $N_{MC}$ .

$$E(\alpha_i) = \frac{1}{N_{MC}} \sum_{k=1}^{N_{MC}} \frac{H\Psi_\alpha(m_r)}{\Psi_\alpha(m_r)}$$

(1.8)

For other operators,

$$\langle O \rangle_{\alpha} = \frac{1}{N_{MC}} \sum_{k=1}^{N_{MC}} \frac{O\Psi_{\alpha}(m_r)}{\Psi_{\alpha}(m_r)}$$

(1.9)

For every Monte Carlo (MC) step, we need to evaluate the ratio of  $\frac{|\Psi(m_{r'})|^2}{|\Psi(m_r)|^2}$  which is of complexity  $O(N^3)$ . In order to optimize with respect to  $\alpha_i$ , we need a complexity of O(N).

#### 1.2.2 Faster VMC

Consider the spinless fermions [5, 4] with a configuration k given by a wavefunction  $\Psi$ and a configuration l given by a wavefunction  $\Phi$ . Both the configurations differ only by a position of a electron e,  $e_l$  and  $e'_l$

$$\begin{bmatrix} \psi_{a1}(e_1) & \dots & \psi_{a1}(e_l) & \dots & \psi_{a1}(e_N) \\ \vdots & \dots & \vdots & \dots & \vdots \\ \psi_{aN}(e_1) & \dots & \psi_{aN}(e_l) & \dots & \psi_{aN}(e_N) \end{bmatrix}$$

(1.10)

Since  $\Psi$  and  $\Phi$  differ by only one column, the ratio can be determined as [2],

$$\frac{det[\Phi]}{det[\Psi]} = \sum_{k} \Psi_{kl}^{-1} \Phi_{kl} \tag{1.11}$$

which of O(N)

The calculation of  $\Psi^{-1}$  is reduced to the order of  $O(N^2)$  using Sherman-Morrison-Woodbury (SMH) method.

#### 1.2.3 Summary of VMC method

- 1. Start with a random configuration

- 2. For  $k = 0, N_{MC}$

- (a) Pick an electron at random for the configuration  $m_r$  and move to a random position. Name this configuration  $m'_r$ .

- (b) Check for Probability, accept the configuration if the ratio is greater than a uniform random number:  $min\left\{1, \frac{|\Psi(m'_r)|^2}{|\Psi(m_r)|^2}\right\}$ , set  $m_{r+1} = m'_r$  if accepted, else set  $m_{r+1} = m_r$ .

- (c) Perform the update of  $\Psi^{-1}$  using SMH formula.

- (d) Wait until the system Equilibriates.

- (e) Repeat the above steps (a c).

- (f) Accumulate the energy contributions.

$$\frac{O\Psi_{\alpha}(m_{r+1})}{\Psi_{\alpha}(m_{r+1})}$$

3. Determine necessary averages for  $E(\alpha_i)$ .

- 4. Optimize over  $\alpha_i$  to obtain  $|\Psi_G\rangle$ .

- 5. Study the ground state  $|\Psi_G\rangle$ .

The VMC method is tested on a tilted square lattice [4, 1]. The Resonance Valance Bond model is used to represent the high  $T_C$ . The number of sites,  $N_S$  is given by  $N_S = L^2 + 1$ , where L is odd. The number of electron pairs,  $N_P$  is given by,  $N_P = N_e/2$  where  $N_e$ , is the number of electrons. The number of electrons can be calculated based on a given hole doping (x),  $Nsites \times (1.0 - x)$  [5].

The Hubbard model for this method is given by,

$$-\sum_{ij} t_{ij} c_{i\sigma} c_{j\sigma} + U \sum_{i} n_{i\uparrow} n_{i\downarrow}$$

(1.12)

where U = 0 (free electrons) and  $U = \infty$  (Extremely correlated liquid) and the model is a t - t' - t'' model to study the material dependencies.

## Chapter 2 Prior Work

## 2.1 CPU Implementation

In [1, 4], the VMC method is used to study the competition between Antiferromagnetic and Superconducting states in High- $T_C$  superconductors. A Fortran implementation of VMC was done by [4] by simulating identical systems, called *Markov chains (MCs)*, each initialized randomly. Since the initial implementation was a sequential version and in order to exploit the parallelism involved in the MCs, the programming model was converted to a MPI version [5].

#### 2.2 MPI Implementation

A MPI Fortran implementation was done by [5, 4] to study the d-correlated systems using the variational approach. The programming model designates a MPI rank (or processor) per Markov chain and requires inter-processor and inter-node communication to calculate the average energy and error distribution. This implementation does not utilize cache blocking for regions within the code which require *locality of reference*. Since, designating a CUDA thread per MC will result in a poor performance due to the working set exceeding the device limits, a better MPI implementation can still yield a good performance. However, the MPI version will be computationally expensive and we need to find a cost effective approach for the VMC algorithm.

### 2.3 GPU Implementation

The first step in porting VMC code to CUDA was done by Byron Tasseff, an REU student at our research group. A *naive* GPU implementation was done by [17] which laid the foundation for our research on tuning this algorithm. In his implementation, a CUDA

thread performs a MC and the number of MCs correspond to the number of threads running in parallel. The implementation lacks enough *thread-level parallelism* and does not utilize the fast memory resources on a GPU, such as, shared and constant memory. Functions such as update of a configuration and ratio of determinant of the configurations have different memory access pattern and certain caching techniques can yield a better performance. In our GPU implementation, we address these issues and optimize the memory usage.

A GPU and a FPGA implementation was done by [18]. This implementation compares the performance of Quantum Monte Carlo calculations between a CPU, GPU and a FPGA. Atoms ranging from 256 to 8192 were tested on a Dual-Core-Dual-processor AMD Opteron @ 2.2 GHz, NVIDIA C1060 GPU and a Virtex-4 XC4VLX160 FPGA. Results show a speedup of  $\approx 2$  for the GPU implementation compared to the CPU version. The implementation does not effectively utilize the memory resources on a GPU and we address these issues in our code.

## Chapter 3 Graphics Processing Units

### 3.1 Increasing Trend in Parallel Computing

The semiconductor industry has now settled on two main trajectories for microprocessor design [8]. The *Multicore* trajectory strives to improve the performance of sequential program, while doubling the number of cores with each generation. As an example,  $Intel^{\textcircled{C}}$  $Core^{TM}i7$  microprocessor has four processor cores, each of which is an out-of-order, multiple instruction issue processor. The processor implements the full x86 instruction set and supports hyperthreading with two threads per core [8]. On the contrary, a GPU increases the throughput of parallel applications. As an example, the NVIDIA Tesla  $M2090^{\textcircled{C}}$ supports upto 512 cores, Dual Warp Scheduler, which simultaneously schedules and dispatches instructions from two independent warps and NVIDIA GIGATHREAD for faster application context switching.

Figures 3.1, 3.2 show that NVIDIA GPU(s) have better FLOPS and Memory Bandwidth compared to their CPU counterpart [7]. Data-parallel appplications, when ported to GPU, are observed to get a performance boost compared to the CPU. This discrepancy is maily due to more number of transistors dedicated for data processing rather than data caching and flow control [8].

Figure 3.3 compares the architecture of a Multicore CPU and a GPU model. CPU dedicates more transistors for caching and control, whereas GPU dedicates it for computational units.

| 3250 | GeForce GTX 680                                                     |

|------|---------------------------------------------------------------------|

| 3000 |                                                                     |

| 2750 |                                                                     |

| 2500 | Intel CPU Single Precision                                          |

| 2300 | Intel CPU Double Precision                                          |

| 2250 | /                                                                   |

| 2000 |                                                                     |

| 1750 |                                                                     |

| 1500 | GeForceGTX 580                                                      |

| 1500 | GeForce GTX 480                                                     |

| 1250 |                                                                     |

| 1000 | GeForce GTX 280                                                     |

| 750  |                                                                     |

| 750  | GeForce 8800 GTX Tesla C2050 Sandy Bridge                           |

| 500  |                                                                     |

|      | eForce 6800 Ultra Tesla C1060 Bloomfield                            |

| 0    | tium 4 Jun-04 Mar-07 <sup>Harpertown</sup> Westmere<br>Dec-09 Aug-1 |

Figure 3.1: Floating Point operations per second for CPU vs GPU, Source: CUDA Programming guide

Figure 3.2: Memory Bandwidth for CPU vs GPU, Source: CUDA Programming guide

Figure 3.3: GPU vs CPU architecture, Source: CUDA Programming guide

### 3.2 CUDA Programming model

Introduced by NVIDIA in November 2006,  $CUDA^{TM}$  is a new parallel programming model that leverages the compute engine in NVIDIA GPU(s) to solve complex computational problems efficiently than a traditional CPU [7].

The CUDA programming model is designed for an easy transition from the C code by a minimal set of language extensions, thereby providing a low learning curve for the programmer. The core has three key abstractions [7] - a hierarchy of thread groups, shared memories and barrier synchronization. These abstractions enable the programmer to partition the application to fine-grained data parallelism and thread parallelism, nested within coarse-grained data parallelism and task parallelism.

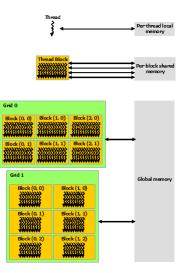

Figure 3.4 shows the scaling model based on the Multiprocessor count (SM) on a GPU. The **threadIdx** can be of one, two or three-dimensions, hence forming a one, two, or three dimensional *thread block*. Each Streaming Multiprocessor (SM) is capable of hosting 1536 CUDA threads, with limited memory resources shared between them. The total number of resident *thread blocks* per SM is given by 8 for a fermi architecture [11]. Blocks are organized into a one, two or a three-dimensional *grid* of thread blocks.

Figure 3.4: Automatic Scalability of Applications, Source: CUDA Programming guide

Each thread has a private local memory, and a thread block has a shared memory with read/write capability for all threads within the block [7]. Finally, all threads have access to the same global memory, two read-only memory spaces, constant and texture. The global, constant and texture memory spaces are optimized for different memory usage [7, 8]. *Global memory coalescing* should be followed to avoid longer memory latency. The fermi architecture offers the flexibility of particining the shared/L1 memory space according to the application. The 64 KB memory space can be participated into 16 KB shared/64 KB L1 or vice-versa. Figure 3.5, 3.6 shows the memory hierarchy and their access pattern.

Figure 3.5: CUDA Thread hierarchy, Source: Programming Massively Parallel Processors-A hands-on Approach

Figure 3.6: CUDA Memory Hierarchy, Source CUDA Programming guide

## Chapter 4 CPU Implementation of VMC

VMC has been implemented targeting a cluster level system by [4, 5], a CPU, GPU and a reconfigurable Field Programmable Gate Array (FPGA) by cite [18]. In this chapter, we present a straightforward implementation of the VMC method using C++ based on an object-oriented approach. The following sections describe the pseudocode for the VMC method and its core components, structure of the CPU code, algorithm analysis and the results obtained for a single-core implementation. Based on our results and taking factors such as computational cost into consideration [17] and [4], we claim a cost-effective and efficient model can be implemented on a GPU.

### 4.1 Pseudocode for the VMC Method

In this section, we show the pseudocodes for the VMC method and its core stages: Equilibration and Accumulation given by Algorithms 4, 3. The VMC method, given by Algorithm 1 has four main stages: Electron move, calculation of ratio of determinants(DetPByDet), update of a configuration (UpdateConfig), and copy of a configuration (Copyconfig), if the move is rejected [5, 9]. The electron move procedure will pick a pair, spin at random and an oldsite from the electron occupancy list (plist). Now, a newsite is picked based on the neighbor probability and an electron is moved to this site. The spinflip is determined and then DetPByDet, UpdateConfig and DetPByDet are called in-order to determine the product of the ratio of determinant of the configurations ( $dpbd1 \times dpbd2$ ). The norm of this product is compared to a real uniform random number and the move is accepted/rejected based on this. [5].

## Algorithm 1 Overview of the VMC Method

| begin vmc        |                                                          |

|------------------|----------------------------------------------------------|

| Initialization() | ▷ Generate lattice object, wavefunction and pairfunction |

| Equilibration()  | ▷ Perform the Equilibration procedure                    |

| Accumulation()   | ▷ Accumulate the energy and study the groundstate        |

| end vmc          |                                                          |

| Algorithm 2 Equilibration        |                                                       |

|----------------------------------|-------------------------------------------------------|

| procedure Equilibration()        |                                                       |

| for $i \leftarrow 0, nsweeps$ do |                                                       |

| Electron move()                  | $\triangleright$ Call the electron move procedure     |

| Perform MonteCarlo Sweep()       | $\triangleright$ Determine the acceptance of the move |

|                                  | and update the Configuration                          |

| end for                          |                                                       |

| end procedure                    |                                                       |

| Algorithm 3 Accumulation                                     |                                                           |

|--------------------------------------------------------------|-----------------------------------------------------------|

| procedure Accumulation()                                     |                                                           |

| for $i \leftarrow 0$ , navesweeps do $\triangleright$ Change | the loop bounds to navesweeps and npsweep                 |

| for $j \leftarrow 0, npsweep$ do                             | $\triangleright$ Repeat the procedures from Equilibration |

| Electron Move()                                              |                                                           |

| Perform MonteCarlo Sweep()                                   |                                                           |

| end for                                                      |                                                           |

| $energy \leftarrow \text{EnergyofConfig}()$                  | $\triangleright$ Call the energy of configuration         |

| $eneloc \leftarrow eneloc + energy$                          | $\triangleright$ Accumulate the energy                    |

| end for                                                      |                                                           |

| end procedure                                                |                                                           |

#### Algorithm 4 Electron Move

```

procedure Electron Move()

ipair \leftarrow rand(Npairs)

\triangleright Pick a pair and spin at random

ispin \leftarrow rand(2)

oldsite \leftarrow plist(ipair, ispin)

while (newsite == 0) do

\triangleright Find a site for the electron move

if neiprob > 0.0 then

newsite \leftarrow rand(Nsites)

else

newsite \leftarrow neiblist()

▷ neiblist maintains the neighbour information

end if

if (latocc(newsite)! = (BT \text{ or } HL)) then \triangleright latocc will determine the spin at the

newsite

spinflip \leftarrow true

jpair \leftarrow which pair(newsite * 2 + 1 - ispin) \triangleright which pair(ilat, spin), "spin" at

lattice site ilat

else

newsite = 0

end if

end while

end procedure

```

```

Algorithm 5 Perform MonteCarlo Sweep

procedure Perform MonteCarlo Sweep()

▷ Determine the spinflip from the electron move stage

if spinflip = true then

▷ Calculate the Ratio of determinants and Update the Configuration

dpbd1 \leftarrow \text{DetPByDet}(ipair, 2 * ispin - 1, newsite)

UpdateConfig(ipair, 2 * ispin - 1, newsite, dpbd1)

dpbd2 \leftarrow \text{DetPByDet}(jpair, 1-2 * ispin, oldsite)

dpbd \leftarrow dpbd1 * dpbd2

else

dpbd \leftarrow \text{DetPByDet}(ipair, 2 * ispin - 1, newsite)

end if

\triangleright Determine \frac{\Psi'^{-1}}{\Psi^{-1}}

norm2 \leftarrow norm(dpbd)

if norm2 \ge uniformrand(0,1) then

\triangleright Move is accepted

if spinflip = true then

UpdateConfig(jpair, 1 - 2 * ispin, oldsite, dpbd2)

else

UpdateConfig(ipair, 2 * ispin - 1, newsite, dpbd)

end if

\triangleright Restore the configuration: Move is not accepted

else

Copyconfig()

end if

end procedure

```

Algorithm 6 Energy of a configuration

```

procedure ENERGYOFCONFIG()

saved = config()

\triangleright Make a copy of the configuration

tempconf = config()

▷ Make a temporary configuration to

calculate dpdbd and update the configuration

for ispin \leftarrow 0, 2 do

\triangleright Calculate the Kinetic energy part of the Hamiltonian

spin \leftarrow 2 * ispin - 1

for ipair \leftarrow 0, Npairs do

isite \leftarrow plist(ipair * 2 + ispin)

for jn \leftarrow 0, nneibs do

jsite \leftarrow neiblist(jn + nneibs * isite)

if latocc(jsite) = HL then

dpbd \leftarrow \text{DetPByDet}(ipair, spin, jsite)

enekloc \leftarrow enekloc + thop(ishell(jn)) * real(dpbd)

spkeloc(ispin) \leftarrow spkeloc(ispin) + thop(ishell(jn)) * real(dpbd)

end if

end for

end for

end for

\triangleright Compute the Exchange term of the Hamiltonian

```

```

otheloc \leftarrow 0

\triangleright To hold the energy from the exchange term

for inn \leftarrow 0, nearnsets do

isite \leftarrow nearnp(inn * 2); jsite \leftarrow nearnp(inn * 2 + 1)

ispin \leftarrow latocc(isite); jspin \leftarrow latocc(jsite)

ipair \leftarrow which pair(isite * 2 + (1 + ispin)/2)

jpair \leftarrow which pair(jsite * 2 + (1 + jspin)/2)

if ispin * jspin < 0 then

tempconf \leftarrow CopyConfig()

dpbd \leftarrow DePByDet(ipair, ispin, jsite); UpdateConfig()

dpbd1 \leftarrow \text{DetPByDet}(jpair, jspin, isite)

otheloc = otheloc - real(dpbd * dpbd1) + 1.0

end if

end for

otheloc \leftarrow (Jij * otheloc)/(2)

▷ Jij represents the Antiferromagnetic exchange

enektot \leftarrow enekloc

othetot \leftarrow otheloc

energy \leftarrow (enektot + othetot)/Nsites

kinenergy \leftarrow (spkeloc(0) + spkeloc(1))/Nsites

othen ergy \leftarrow othetot

return energy

end procedure

```

The programming model follows the object-oriented approach and the major data structures, such as  $\Psi^{-1}$  and pairfunction are members of the classes defined in Table 4.2. By varying the input parameters such as hole doping and the lattice size, data structures such as  $\Psi^{-1}$  and pairfunction become the point of interest due to increasing memory consumption. Table 4.1 shows the memory consumption for different lattice models.

| Data structure | Formula                  | Data Type            | L = 5    | L = 9      | L = 15     |

|----------------|--------------------------|----------------------|----------|------------|------------|

| $Nsites(N_S)$  | $L^2 + 1$                | $\operatorname{int}$ | 26       | 82         | 226        |

| $Nelecs(N_e)$  | Nsites * (1.E0 - x)      | $\operatorname{int}$ | 24       | 74         | 204        |

|                | where $x$ is hole doping |                      |          |            |            |

| Npairs $(N_P)$ | Nelecs/2                 | $\operatorname{int}$ | 12       | 37         | 102        |

| PsiInv         | $(Npairs^2)$             | double               | 1.152 kB | 10.952  kB | 83.232 kB  |

| Pairfunction   | $(Nsites^2)$             | double               | 5.408 kB | 53.792 kB  | 408.608 kB |

| Plist          | (2*N pairs)              | $\operatorname{int}$ | 96 B     | 296 B      | 816 B      |

Table 4.1: Data Structures and Memory requirements

Table 4.2: Classes used in the Implementation of VMC

| S.No | Class        | Functionality                                             |  |

|------|--------------|-----------------------------------------------------------|--|

| 1    | Sqlat        | Holds Lattice parameters such as Nsites, Nelecs,          |  |

|      |              | Npairs and hopping, etc                                   |  |

| 2    | Config       | Contains the energy arrays, and functions for calculating |  |

|      |              | the Ratio of Determinants and Update of $\Psi^{-1}$       |  |

| 3    | Wavefunction | Contains the variational parameters required to           |  |

|      |              | generate the pairfunction or wavefunction                 |  |

| 4    | Montecarlo   | Contains the lattice object, pairfunction and             |  |

|      |              | randomseeds for a corresponding Markov chain              |  |

#### 4.1.1 Structure of the CPU code

The implementation uses an object-oriented approach for the individual functions mentioned in the previous section. Each class is used to create an object and the final executable is obtained by compiling and linking the individual objects. Table 4.2 describes the classes and the corresponding functionality.

## 4.2 Calculation of the Ratio of Determinants using SMH Formula

The SMH formula, as explained in Section 1.2.2, is used to calculate the ratio of determinant of the configurations. This is implemented using a function called DetPByDet.

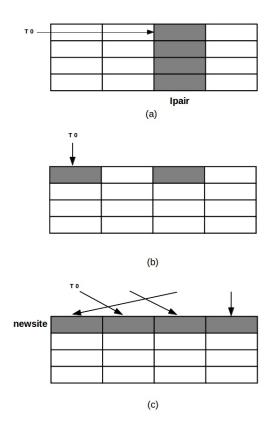

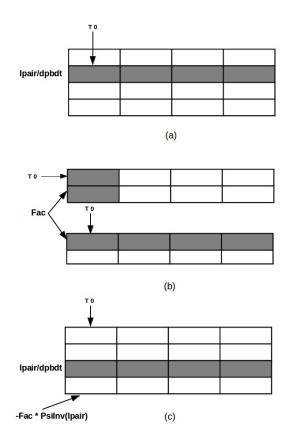

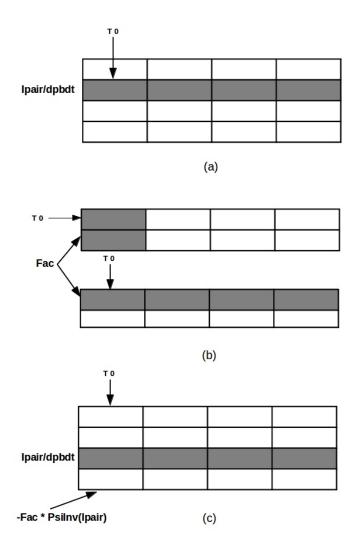

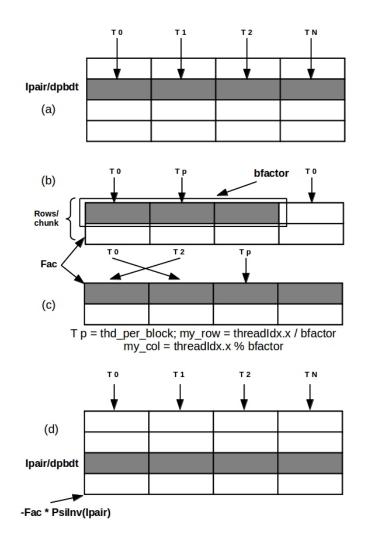

Figure 4.1: Sequential Memory Access Pattern for the up spin: (a)  $\Psi^{-1}$ , (b) Plist, (c) Pairfunction

Figure 4.1 shows the access pattern for the up spin. A site is picked from an electron list and referred to as an oldsite. This site corresponds to the column of pairfunction. A newsite given by an input parameter corresponds to the row of pairfunction. The *Ipair* represents the electron pair and corresponds to the column of  $\Psi^{-1}$ . Thus, a dot product of a row of pairfunction and a column of  $\Psi^{-1}$  is calculated (dpbd). There will be  $N_P$  cache misses for the  $\Psi^{-1}$  array and one cache miss, to load the first pairfunction element on the **L1 cache**. For the given lattice size, L, there will be a total of  $N_P$  fused multiply-add floating point operations (FLOPS) to compute a dot-product.

Figure 4.2: Sequential Memory Access Pattern for the down spin: (a)  $\Psi^{-1}$ , (b) Plist, (c) Pairfunction

Figure 4.2 shows the access pattern for the down spin. In this case, the access pattern is reversed, where a column of the pairfunction and a row of  $\Psi^{-1}$  are accessed. There will be  $N_S$  of cache misses for the pairfunction array and one cache miss for the  $\Psi^{-1}$ . From section 1.2.2, the ratio of determinants can be calculated in the order of  $O(N_P)$  using SMH formula [5].

## 4.3 Update of a configuration

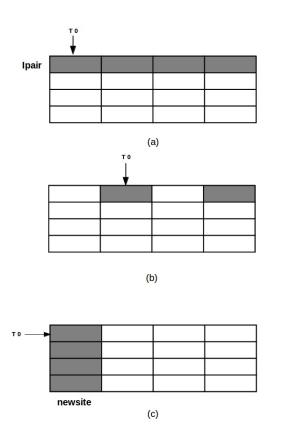

Figure 4.3: Update of a configuration for the up spin

Figure 4.3 shows the update of a configuration for the up spin of an electron. The  $Ipair^{th}$  column of  $\Psi^{-1}$  is first updated using dpbd.

The remaining columns of  $\Psi^{-1}$  are updated using the dot product between  $\Psi^{-1}$  and pairfunction. The update of  $\Psi^{-1}$  is of order  $O(N_P^2)$ .

Figure 4.4: Update of a configuration for the down spin

For the case of a down spin, the access pattern is reversed, where an electron pair represents the  $Ipair^{th}$  row in  $\Psi^{-1}$ . The remaining rows are updated by using the dot product between  $\Psi^{-1}$  and pairfunction. Figure 4.4 shows the update of a configuration for the down spin of an electron.

### 4.4 Algorithm Analysis

The execution time of the individual functions is dependent on parameters such as,  $N_P$ ,  $N_S$ , neqlsweeps, npsweep and navesweeps. Table 4.3 gives the Floating point operations per second (FLOPS) calculation for different functions of the VMC method. The FLOPS are calculated based on a speculation that a spinflip will occur 50% of the time in both the Equilibration and Accumulation stage. Thus, the FLOPS are an estimate to different lattice models based on  $N_P$  and may vary depending on the occurrence of a spinflip.

| Function      | FLOPS                       | Operation                      |

|---------------|-----------------------------|--------------------------------|

| DetPByDet     | N pairs * MUL               | Either case of                 |

|               |                             | spinflip                       |

| UpdateConfig  | N pairs * DIV               | For <i>Ipair</i> <sup>th</sup> |

|               |                             | row or col of $\Psi^{-1}$      |

|               | $+Npairs^2 * (MUL + ADD)$   | For dot product                |

|               |                             | calculation                    |

|               | $+Npairs^2 * (MUL + SUB)$   | For updating other             |

|               |                             | rows or cols of $\Psi^{-1}$    |

| CopyConfig    | NIL                         | NIL                            |

| Energy of a   | 2 * N pairs * N neibs       |                                |

| Configuration | *(DetPByDet + MUL + ADD)    | Kinetic energy                 |

|               |                             | calculation                    |

|               | +Nearnsets*(DetPByDet)      |                                |

|               | +N earns ets* Update config |                                |

|               | +Nearnsets*(DetPByDet)      |                                |

|               | +N earnsets * (ADD + SUB)   | Accumulation                   |

Table 4.3: FLOPS calculation for the VMC method

### 4.5 Cache Behavior

The implementation utilizes a single core of the CPU and further testing and optimization of the code are decided upon the cache behavior. We consider the Intel(R)Core(TM)i7-2600 CPU architecture for determing the cache behavior. From [10], the cache hierarchy is given by: 32 kB data + 32 kB instruction L1 cache, 256 kB L2 cache per core.

#### 4.5.1 Function DetPByDet

Referring to Section 4.1.1, one dot product requires a total of  $N_P$  fused multiply-add floating-point operations. Since a cache line is 64 B wide, we find that for lattice size of L = 5, a row of pairfunction or a column of  $\Psi^{-1}$  does not fit within a cache line. There will be only one miss penalty to load the first element for pairfunction. There will be  $N_P$ cache misses for  $\Psi^{-1}$  since we access a column. The penalties are reversed for the down spin, where there will be  $N_S$  of cache misses for the pairfunction and one miss penalty for  $\Psi^{-1}$ .

#### 4.5.2 Function UpdateConfig

Referring to section 4.3, the update of  $\Psi^{-1}$  is of order  $O(N_P^2)$ . For the case of an up spin, there will be  $N_P$  cache misses for every element of the *Ipair*<sup>th</sup> of  $\Psi^{-1}$ . To perform a dot product, the penalty levels will be the same as mentioned in 4.5.1. To update the remaining columns there will be  $N_P$  cache misses for every element per column. The penalties are reversed for the down spin, where there will be one cache miss per row of  $\Psi^{-1}$ , while  $N_S$ of cache misses per element of pairfunction. The pairfunction access is permuted in either case of the spin and hence the latency will increase if the data falls outside the cache.

#### 4.5.3 Function Pairfunction

For the case of an up spin of an electron, a row of pairfunction is accessed. Though the access pattern within a row is permuted, the data is still cached and will have a lower latency. The case is reversed for the down spin, where there will be several cache misses as explained in Section 4.1.1. From Figures 4.3, 4.4, the pairfunction will suffer a minimum cache miss for the up spin, while there will be several cache misses for the down spin. All these cache misses are viewed from the **L1 cache** level. Since, the pairfunction is accessed more than  $10^4$  in both the Equilibration and Accumulation stage and the size for any lattice model is less than that of **L2 cache**, we can speculate the hardware to move it to the **L2 cache**.

### 4.6 Results

The VMC method has been tested on Intel(R)Core(TM)i7-2600 CPU @ 3.40 GHz. The method performs one MC and from the timing results, we find the *hot spots* for futher parallelism and optimization using GPU. More work on porting VMC to GPU using CUDA are discussed in Chapter 5. Tables 4.4-4.6 give the timing results for individual functions and for the overall VMC method for L = 5, 9, 15.

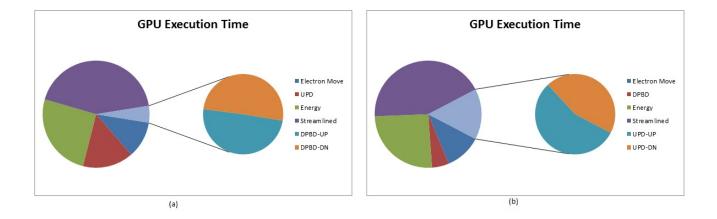

Figure 4.5: Pie chart for L = 5:(a) Split of Equilibration, (b) Split of Accumulation

| Lattice Size | Function              | Execution Time(s) |

|--------------|-----------------------|-------------------|

|              | Equilibration         |                   |

|              | 1.Electron Move       | 0.02              |

|              | 2.Spinflip = true:    |                   |

|              | DetPbyDet             | 0.01              |

|              | UpdateConfig          | 0.03              |

|              | 3.Spinflip = false:   |                   |

|              | DetPbyDet             | 0.00              |

|              | UpdateConfig          | 0.00              |

|              | 4.Copyconfig          | 0.04              |

|              | Move rejected         | 0.02              |

|              | 5.Total               | 0.24              |

| L = 5        | Accumulation          |                   |

|              | 1.Electron Move       | 0.01              |

|              | 2.Spinflip = true:    |                   |

|              | DetPbyDet             | 0.01              |

|              | UpdateConfig          | 0.07              |

|              | 3.Spinflip = false:   |                   |

|              | DetPbyDet             | 0.01              |

|              | UpdateConfig          | 0.02              |

|              | 4. Energy calculation |                   |

|              | DetPbyDet             | 0.02              |

|              | UpdateConfig          | 0.08              |

|              | Total                 | 0.18              |

|              | 5.Copyconfig          | 0.08              |

|              | Move rejected         | 0.03              |

|              | 6.Total               | 0.46              |

|              | Total VMC             | 0.70              |

Table 4.4: Execution time for L = 5

| Lattice Size | Function              | Execution Time(s) |

|--------------|-----------------------|-------------------|

|              | Equilibration         |                   |

|              | 1.Electron Move       | 0.01              |

|              | 2.Spinflip = true:    |                   |

|              | DetPbyDet             | 0.11              |

|              | UpdateConfig          | 1.32              |

|              | 3.Spinflip = false:   |                   |

|              | DetPbyDet             | 0.02              |

|              | UpdateConfig          | 0.04              |

|              | 4.Copyconfig          | 0.74              |

|              | Move rejected         | 0.68              |

|              | 5.Total               | 3.04              |

| L = 9        | Accumulation          |                   |

|              | 1.Electron Move       | 0.07              |

|              | 2.Spinflip = true:    |                   |

|              | DetPbyDet             | 0.07              |

|              | UpdateConfig          | 1.44              |

|              | 3.Spinflip = false:   |                   |

|              | DetPbyDet             | 0.00              |

|              | UpdateConfig          | 0.09              |

|              | 4. Energy calculation |                   |

|              | DetPbyDet             | 0.17              |

|              | UpdateConfig          | 1.85              |

|              | Total                 | 2.91              |

|              | 5.Copyconfig          | 0.62              |

|              | Move rejected         | 0.64              |

|              | 6.Total               | 6.03              |

|              | Total VMC             | 9.07              |

Table 4.5: Execution time for L = 9

| Lattice Size | Function              | Execution Time(s) |

|--------------|-----------------------|-------------------|

|              | Equilibration         |                   |

|              | 1.Electron Move       | 0.19              |

|              | 2.Spinflip = true:    |                   |

|              | DetPbyDet             | 0.51              |

|              | UpdateConfig          | 25.15             |

|              | 3.Spinflip = false:   |                   |

|              | DetPbyDet             | 0.07              |

|              | UpdateConfig          | 0.96              |

|              | 4.Copyconfig          | 12.29             |

|              | Move rejected         | 11.99             |

|              | 5.Total               | 51.74             |

| L = 15       | Accumulation          |                   |

|              | 1.Electron Move       | 0.18              |

|              | 2.Spinflip = true:    |                   |

|              | DetPbyDet             | 0.44              |

|              | UpdateConfig          | 25.17             |

|              | 3.Spinflip = false:   |                   |

|              | DetPbyDet             | 0.03              |

|              | UpdateConfig          | 0.98              |

|              | 4. Energy calculation |                   |

|              | DetPbyDet             | 0.80              |

|              | UpdateConfig          | 36.50             |

|              | Total                 | 52.67             |

|              | 5.Copyconfig          | 12.30             |

|              | Move rejected         | 11.61             |

|              | 6.Total               | 104.05            |

|              | Total VMC             | 156.02            |

Table 4.6: Execution time for L = 15

Figure 4.6: Pie chart for L = 9:(a) Split of Equilibration, (b) Split of Accumulation

Figure 4.7: Pie chart for L = 15:(a) Split of Equilibration, (b) Split of Accumulation

Figure 4.5 gives the execution time for L = 5 using a pie-chart. The upper half represents the execution time taken by the accumulation procedure. From the chart, we determine that accumulation is the most time consuming procedure. On further profiling, we found that the execution time for calculating the energy was higher than other functions. Further breakdown revealed the most time consuming and computationally intensive part to be the update of a configuration. Chapter 5 describes the parallelization efforts on GPU for this procedure. On the lower half of the figure, variables such as, DPBD-T and UPD-T represents the execution time taken for the case when the spinflip is true.

Figures 4.6, 4.7 gives the execution time for L = 9, 15. From the charts, we find that the contribution is more when the spinflip is true. Variables DPBD-F and UPD-F represents the contribution when there is no spin-flip. Based on these charts, we claim that the speedup of the application will be enhanced, if the individual functions are parallelized and optimized for effective memory access.

### 4.7 Multiple MCs and the system behavior

The sequential code can be expanded to a MPI-version performing N MCs in parallel on N CPU cores. Issues such as the total execution time, parallel and sequential regions within the equilibration and accumulation stages need to addressed. Let T(N) be the total execution time to complete N MCs in parallel. Let  $T_e$  be the equilibration time on a serial implementation and let  $T_a$  be the accumulation time on a serial implementation.

If we execute N MCs on N CPUs in parallel, the total time can be theoretically,  $T(N) = (T_e + T_a)(N)^{-1}.$

Practically, we cannot expect this execution time due to the following factors.

• Large equilibration time which will be constant for N MCs.

- Serial regions within a MC such as: Electron move, DetPbyDet and update of a configuration.

- 1. For every MC we start with a random configuration and wait until the system equilibrates and start accumulating the energy.

- 2. Since, certain MCs can finish well ahead, there will be a race around condition in the energy accumulation and average calculation.

- Inter-node communication delays if the number of MCs is of order 100 or more.

Hence, these factors will affect the parallelism approach and we cannot expect a direct speedup of over N for this algorithm on a MPI model.

# Chapter 5 Porting VMC to CUDA

### 5.1 GPU Acceleration of the VMC Method

In the previous chapter, we explained the CPU implementation of the VMC method and determined the hot spots for further parallelization. From Section 4.6, we found that the CPU implementation is time consuming for lattice models L = 9, 15. Functions such as the ratio of determinants, update and energy of a configuration are computationally intensive and exhibit data-level parallelism, thereby becoming the best candidates for parallelization. Hence, in this chapter, we discuss the several strategies adopted to parallelize the VMC method for multiple MCs on a NVIDIA GPU using CUDA.

Figure 5.1 represents the workflow for the GPU implementation. Each MC is independent and can be executed in parallel on a GPU. Every chain has its own copy of a configuration object with members such as,  $\Psi^{-1}$ , neighbor list, energy and whichpair. The pairfunction and lattice object are shared by all MCs. A block of CUDA threads will handle a MC and hence we have N parallel CUDA blocks executing in parallel on a NVIDIA GPU. At the end of each MC, the energy per site is accumulated and the result is written to the energy array corresponding to that chain. The results are copied back to the CPU, where the mean energy and standard deviation are calculated. The groundstate,  $|\Psi_G\rangle$  is then optimized with the variational parameters.

## 5.2 Naïve Implementation

The CUDA implementation described here is based upon a preliminary CUDA port, which will be called the *naïve implementation*, performed by [17], an intern student who worked for the La-Sigma research group at LSU. In this implementation, each MC is han-

Figure 5.1: VMC Workflow for Multiple Markov Chains (MCs)

dled by a single CUDA thread and the total number of CUDA blocks were equal to the number of MCs. This does not utilize the capability of the massively parallel GPU and hence no improvement was found over the CPU code. With only one thread per block, the code cannot exceed using  $\frac{1}{32}$  of the GPU's computing potential per warp (group of 32 threads). The other factors contributing to the slowdown being: Higher memory access latency due to global memory read/write(s) and the lack of usage of shared memory and constant memory, and unoptimized use of the L1 and L2 caches. Hence, in the following sections, we describe in detail, the parallelization and effective memory utilization efforts done to improve this naïve implementation.

### 5.3 Execution configuration

The number of threads required to obtain occupancy and SM utilization was the deciding factor for our implementation. The threads per MC depends upon the  $N_P$  of the given lattice.

On a Fermi device (Architecture model for a NVIDIA GPU) with compute capability 2.X [11], a SM can support 8 resident blocks of threads. However, the total number of threads per SM cannot exceed 1536 and the shared or L1 cache per SM is limited to 48 or 16 kB. More blocks will increase the warp occupancy per SM, while the shared memory usage shrinks to a factor of 48/8 = 6 kB per block. Another factor affecting the performance will be the register usage per SM. On a Fermi device, the total number of registers per thread values to 63 [12]. If a thread exceeds this limit, it will result in a local memory spill, which will move the data to high latency global memory [12]. Hence, to avoid higher access latency and assign enough work for the threads, we pick the number of threads per block based on the complexity of the functions. The order of these functions are given by: DetPByDet -  $O(N_P)$ ; Updateconfig -  $O(N_P^2)$ ; CopyConfig -  $O(2 * N_S)$ . If the number of threads is set to  $N_P^2$ , there will be enough threads to cover the latency for UpdateConfig and CopyConfig. On the contrary, this will reduce the speedup due to sequential zones such as Electron move and wasteful threads in DetPByDet. If we recall from the previous chapter, the memory access pattern is distinct for either case of a spinflip of UpdateConfig. Thus, the number of threads should be in the range of  $(N_P < threads/MC < N_P^2)$  and rounded to the nearest multiple of a warp. We discuss more about this in Section 5.6.1.

### 5.4 Memory requirements and cache behaviour

Though the amount of parallelism in a MC is low, by GPU standards, as this section will show the working set, careful use of the available high-speed memory will make this code efficient.

From Section 4.1, we recall the memory requirements for different lattice models. The total device global memory on a fermi device is approximately  $5 \sim 6$  GB. From the Table 4.1, we find that the total memory requirements for a lattice model of size L = 15 is within the GPU global memory limit. However, global memory has the highest latency compared to other memory resources on a GPU and hence we need to find effective ways to utilize the high-speed memories such as, registers, L1/shared, and constant memory [7]. In this section, we discuss about the caching behaviour on a GPU. Tables 5.1, 5.2 and 5.3 shows whether each major array used by the code fits into three different parts of the memory hierarchy for different lattice sizes.

From Table 5.1, arrays such as  $\Psi^{-1}$ , pairfunction and plist fits within the L1 cache. The repeated access of the pairfunction by different MCs will result in caching at L2 level by the hardware. Consider the lattice model, L = 5: From Table 5.1, we find the size of  $\Psi^{-1}$  to be 1.152 kB. The total number of threads per MC is 64. Therefore, the total number of blocks per SM will be 1536/64 = 24. Fermi device has a limit of 8 resident blocks per

| GPU Memory | $\Psi^{-1}$ | Pairfunction | Plist |

|------------|-------------|--------------|-------|

|            | (double)    | (double)     | (int) |

| L = 5      | 1.152 KB    | 5.408 KB     | 96 B  |

| L1 cache/  | Yes         | Yes          | Yes   |

| shared     |             |              |       |

| L2 cache   | No          | Yes.Due      | No    |

|            |             | to sharing   |       |

|            |             | between MC   |       |

| Constant   | No          | No           | No    |

| Memory     |             |              |       |

Table 5.1: Speculation of a GPU's cache behaviour for L = 5

Table 5.2: Speculation of a GPU's cache behaviour for L = 9

| GPU Memory | $\Psi^{-1}$ | Pairfunction | Plist |

|------------|-------------|--------------|-------|

|            | (double $)$ | (double $)$  | (int) |

| L = 9      | 10.952 KB   | 53.792 KB    | 296 B |

| L1 cache/  | Yes         | No           | Yes   |

| shared     |             |              |       |

| L2 cache   | No          | Yes.Due      | No    |

|            |             | to sharing   |       |

|            |             | between M.C  |       |

| Constant   | No          | No           | No    |

| Memory     |             |              |       |

SM [8]. The memory consumption per SM will be:  $\Psi^{-1} = 1.152 * 8 = 9.216 * 3 = 27.648$  kB, since we have three copies of a configuration. This is still within the limit of 48 KB of L1 cache and hence will be cached by the hardware; The pairfunction will be 5.408 kB and is within the limit of 64 kB of constant memory; The plist array will be 96 \* 3 = 288 B, for three configurations and still can reside in L1 cache. All these speculations are based on the assumption that the pairfunction does not evict lines holding  $\Psi^{-1}$ . Since, there are three copies of a configuration and the cache requirements per MC is close to 27 kB, the

| GPU Memory | $\Psi^{-1}$   | Pairfunction | Plist |

|------------|---------------|--------------|-------|

|            | (double)      | (double)     | (int) |

| L = 15     | 83.232 KB     | 408.608 KB   | 816 B |

| L1 cache/  | Yes, but      | No           | Yes   |

| shared     | partly cached |              |       |

| L2 cache   | Yes. Exceeds  | Yes. Due     | No    |

|            | L1 cache size | to sharing   |       |

|            |               | between M.C  |       |

| Constant   | No            | No           | No    |

| Memory     |               |              |       |

Table 5.3: Speculation of a GPU's cache behaviour for L = 15

Table 5.4: Summary of Memory prediction for L = 5

| Lattice | Threads per | Config  | $\Psi^{-1}$ | Pairfunc        | Plist | $\mathbf{SM}$ |

|---------|-------------|---------|-------------|-----------------|-------|---------------|

|         | MC          |         |             |                 |       | occupancy     |

|         |             | Config1 | L1          | Constant-Common | L1    |               |

| L = 5   | 64          | Config2 | L1          | to all MC       | L1    |               |

|         |             | Config3 | L1          |                 | L1    |               |

|         |             | Total   | 27.648 kB   | 5.408 kB        | 288 B | 1 MC          |

number of MC per SM will be limited to 1. Table 5.4 summarizes this memory prediction for L = 5.

For the case of L = 15, the number of threads per MC will be 416; the number of blocks per SM will be  $1536/416 \approx 3$ ; and the memory consumption for  $\Psi^{-1} = 83.232$  KB. Hence, it does not fit within the L1 cache and it will be cached on L2 level by the hardware. This drawback will be overcome by more threads which will hide the global memory latency due to *coalescing*.

### 5.5 Memory Access Pattern

In this section, we discuss about the memory access pattern and initial parallelization efforts for functions such as: DetPByDet (Ratio of determinants) and UpdateConfig (To update a configuration). Section 5.6 discusses more about the optimization strategies adopted for these functions.

### 5.5.1 Function DetPByDet

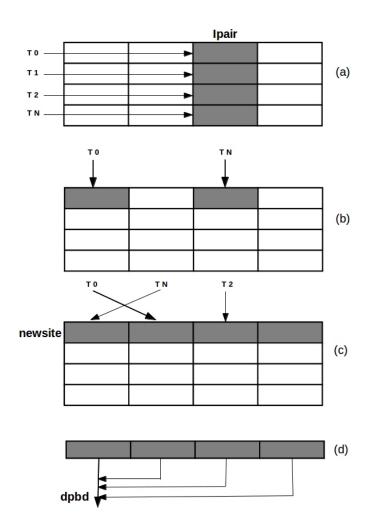

This function is used to calculate the dot product of  $\Psi^{-1}$  and pairfunction. We followed these steps to parallelize this function using CUDA:

- Spinflip = up

- 1. The electron pair, represented by *Ipair*, will correspond to the column of  $\Psi^{-1}$ .

- 2. A *newsite* is picked where the electron will be moved.

- 3. From the lattice occupancy list, given by *plist*, we find the lattice site of the electron, given by *othsite*.

- 4. Now, the *newsite* will correspond to the row and the *othsite* will correspond to the column of pairfunction.

- 5. Thus, we perform a dot product of a column of  $\Psi^{-1}$  and a row of pairfunction using the faster VMC technique given by SMH.

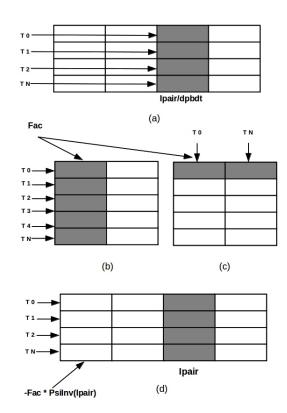

- 6. In this implementation, we use  $N_P$  threads to perform the dot product, whereas [17] uses one thread. Figure 5.2 explains this procedure.

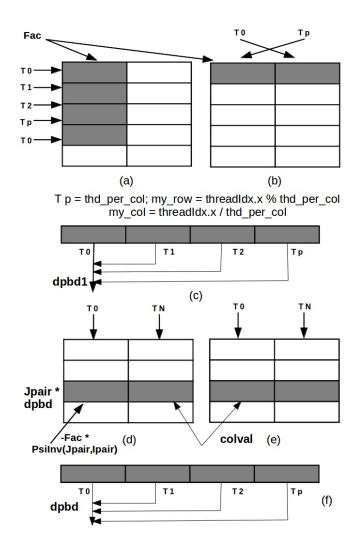

Figure 5.2: Memory Access Pattern for up spin: (a)  $\Psi^{-1}$ , (b) Picking a site from Plist, (c) Pairfunction

Figure 5.3: Memory Access Pattern for down spin: (a)  $\Psi^{-1}$ , (b) Picking a site from Plist, (c) Pairfunction

- Spinflip = down

- 1. The electron pair, represented by *Ipair*, will correspond to the row of  $\Psi^{-1}$ .

- 2. A *newsite* is picked where the electron will be moved.

- 3. From the lattice occupancy list, given by *plist*, we find the lattice site of this electron, given by *othsite*.

- 4. Now the *newsite* will correspond to the column and the *othsite* will correspond to the row of pairfunction.

- 5. Thus, we perform a dot product of a row of  $\Psi^{-1}$  and a column of pairfunction, thereby summing the contribution using the faster VMC technique given by SMH.

- 6. In this implementation, we use  $N_P$  threads to perform the dot product, whereas [17] uses one thread. Figure 5.3 explains this procedure.

### 5.5.2 Function UpdateConfig

- Spinflip = up

- 1. The electron pair, represented by *Ipair*, will correspond to a column of  $\Psi^{-1}$ .

- 2. The *Ipair*<sup>th</sup> column is updated using the dpbd from function DetPByDet.

- 3. Now, a dot product is computed between every column of  $\Psi^{-1}$  and a row of pairfunction.

- 4. The remaining columns of  $\Psi^{-1}$  are now updated with this dot product.

- 5. This implementation utilizes  $N_P$  threads for updating the  $\Psi^{-1}$  and N threadsper-col to perform the dot product. Figure 5.4 describes this procedure.

Figure 5.4: Memory Access Pattern for up spin: (a)  $\Psi^{-1}$ , (b) Picking a site from Plist, (c) Pairfunction

- Spinflip = down

- 1. The electron pair, represented by *Ipair*, will correspond to a row of  $\Psi^{-1}$ .

- 2. The  $Ipair^{th}$  row is updated using the dpbd from function DetPByDet.

- 3. Now, a dot product is computed between every row of  $\Psi^{-1}$  and a column of pairfunction.

- 4. The remaining rows of  $\Psi^{-1}$  are now updated with this dot product.

- 5. This implementation utilizes  $N_P$  threads for updating the  $\Psi^{-1}$  and N threadsper-col to perform the dot product. Figure 5.5 describes this procedure.

### 5.6 Optimization efforts

In the previous Section, we mentioned the preliminary parallelization of functions using CUDA. In this section, we discuss the various memory optimization strategies adopted for these functions.

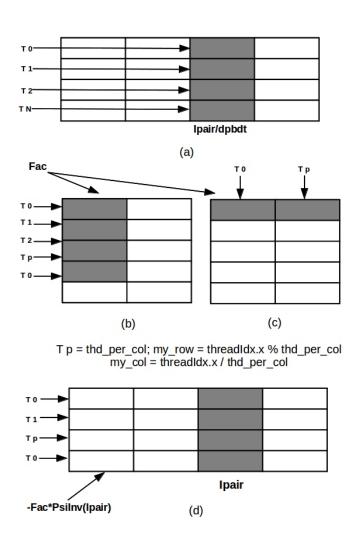

### 5.6.1 Thread selection in depth

Functions such as Updateconfig and Copyconfig have loop bounds on the order of  $O(N_P^2)$  and  $O(2 * N_S)$ . An optimal thread selection range for a MC will be within  $(N_P \leq blocksize \leq N_P^2)$ . Functions such as updateconfig have different access patterns for either case of a spinflip. Hence, we set a parameter called, *threads-per-col*, to determine the number of threads per CUDA block. The number of threads per block is given by: *Blocksize* = Round(*threads-per-col*\*N\_P,nearest multiple of warp). Table 5.5 mentions the threads per block for different lattice models.

Figure 5.5: Memory Access Pattern for down spin: (a)  $\Psi^{-1}$ , (b) Picking a site from Plist, (c) Pairfunction

| Lattice | Npairs | Threads-per-col |        |               |

|---------|--------|-----------------|--------|---------------|

|         |        |                 | per MC | MCs<br>per SM |

| L = 5   | 12     | 4               | 64     | 24            |

| L = 9   | 37     | 4               | 160    | 9             |

| L = 15  | 102    | 4               | 416    | 3             |

Table 5.5: Threads per MC and Number of MCs per SM

### 5.6.2 Elimination of redundant copies of a configuration

We predicted the memory requirements and the SM occupancy for L = 5 on Section 5.4. The prediction was done with three copies of a configuration per MC. In this section, we predict the SM occupancy by eliminating the redundant copies of a configuration.

Table 5.6 calculates the total memory requirements for L = 5 with a single configuration. The SM occupancy (Number of MCs) is given by,  $48/9.312 = 5.15 \approx 5$ .

Table 5.6: Occupancy calculation for L = 5

| Lattice | Threads per   | Config  | $\Psi^{-1}$         | Pairfunc        | $\mathbf{Plist}$ | $\mathbf{SM}$ |

|---------|---------------|---------|---------------------|-----------------|------------------|---------------|

|         | $\mathbf{MC}$ |         |                     |                 |                  | occupancy     |

| L = 5   | 64            | Config1 | L1                  | Constant Memory | L1               |               |

|         |               | Total   | $9.216~\mathrm{kB}$ | 5.408 kB        | 96 B             | 5 MCs         |

### 5.6.3 Optimized memory access pattern

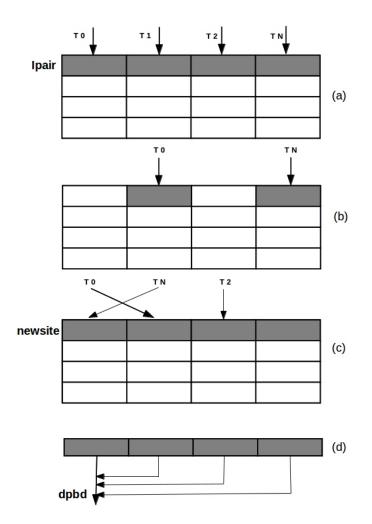

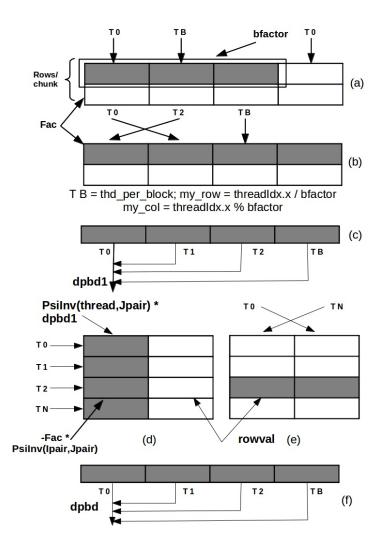

In the previous section, we explained the parallelization efforts for the device functions. For the function Detpbydet, the dot product can be accumulated and reduced in a shared memory. This will result in faster reduction compared to the reduction done on a global memory. For the function Updateconfig, the entire  $\Psi^{-1}$  array is accessed and updated based on the spinflip. Caching effects can be explored if this function is customized with a blocking factor for the L1 cache.

#### • Function DetPByDet

A total of  $N_P$  threads work on this function. The dot product of each element of  $\Psi^{-1}$  and pairfunction is stored in a register for either case of a spinflip. The dot product of all elements are accumulated and reduced in a shared memory. The pairfunction has a permuted access and for the case of a down spinflip, a transposed version of the pairfunction is used. This will result lower cache misses and caching of the pairfunction at L1 level. Figure 5.6 and 5.7 explains the optimization techniques.

#### • Function UpdateConfig