### Louisiana State University LSU Digital Commons

LSU Doctoral Dissertations

**Graduate School**

2014

# Search-based Model-driven Loop Optimizations for Tensor Contractions

Ajay Panyala Louisiana State University and Agricultural and Mechanical College, ajay.panyala@gmail.com

Follow this and additional works at: https://digitalcommons.lsu.edu/gradschool\_dissertations Part of the <u>Computer Sciences Commons</u>

#### **Recommended** Citation

Panyala, Ajay, "Search-based Model-driven Loop Optimizations for Tensor Contractions" (2014). *LSU Doctoral Dissertations*. 3717. https://digitalcommons.lsu.edu/gradschool\_dissertations/3717

This Dissertation is brought to you for free and open access by the Graduate School at LSU Digital Commons. It has been accepted for inclusion in LSU Doctoral Dissertations by an authorized graduate school editor of LSU Digital Commons. For more information, please contactgradetd@lsu.edu.

### SEARCH-BASED MODEL-DRIVEN LOOP OPTIMIZATIONS FOR TENSOR CONTRACTIONS

A Dissertation

Submitted to the Graduate Faculty of the Louisiana State University and Agricultural and Mechanical College in partial fulfillment of the requirements for the degree of Doctor of Philosophy

in

The Department of Electrical Engineering and Computer Science

by Ajay Panyala B.Tech, JNT Univeristy, 2007 August 2014 Dedicated to my parents.

### Acknowledgments

This dissertation would have never been possible without the strong support and guidance of my advisor Dr. Gerald Baumgartner and co-advisor Dr. J. Ramanujam. Gerald gave me the oppurtunity to pursue a doctoral degree regardless of the weak undergraduate background I had. Despite me being very slow with making progress in the first few years, he has always been very patient, even until the end of my doctoral study. I will be grateful to him forever. Dr. Ram has always provided useful advice and valuable insights into the research directions that needed to be pursued.

This research started with the idea of developing a domain-specific compiler for specific computations arising in quantum chemistry. Dr. Chi-Chung Lam was primarily responsible for the intial ideas and algorithms. A lot of other students had contributed to the design and initial implementation which was developed at Ohio State University. I would like to acknowledge all of their efforts which served as a foundation for my dissertation.

I would like to sincerely thank both Dr. Jianhua Chen for serving on my dissertation committee and Dr. James M. Matthews for serving as the dean's representative and for providing valuable feedback. I would also like to express my sincere thanks to Dr. David Tramell for provide systems support promptly whenever I needed anything and Ms. Maggie Edwards for all the administrative support.

# **Table of Contents**

| Acknowledgments                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | iii                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|

| List of Tables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | vi                                                         |

| List of Figures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | iii                                                        |

| Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | X                                                          |

| Chapter 1: Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                          |

| 2.1       Operation Minimization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5<br>5<br>9<br>13<br>14<br>16<br>22<br>4<br>27<br>29<br>29 |

| 3.1       Loop Fusion Optimization       3.2         3.2       Loop Fusion Optimization for Handwritten Code       3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 34<br>34<br>37<br>39                                       |

| 4.1 Data Structures       4.2 Pruning       4.2 Pruning       4.3 Correctness and Complexity of the Loop Fusion Algorithm       4.3 Pruning       4.3 Pruning <td>40<br/>40<br/>41<br/>42<br/>43</td> | 40<br>40<br>41<br>42<br>43                                 |

| 5.1       Algorithm       5.1.1         Solution       5.1.1         Canonicalization       5.1.2         Solution       5.1.2         Region Identification       5.1.3         Subscript Inference       5.1.4         Reaching Definitions Analysis       5.1.5         Loop Fusion for Handwritten Code       5.1.5         Solution       5.1.5 <t< td=""><td>52<br/>54<br/>55<br/>56<br/>56<br/>56<br/>57<br/>59<br/>61</td></t<>                                                                                                                                                                                                                                                                                                                                                                                    | 52<br>54<br>55<br>56<br>56<br>56<br>57<br>59<br>61         |

| Chapter 6: Loop Fusion Optimization for GPGPUs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 53                                                         |

| 6.1     | Algorithms                                                                             | 64  |

|---------|----------------------------------------------------------------------------------------|-----|

|         | 6.1.1 Fusion Algorithm for GPGPUs                                                      | 65  |

|         | 6.1.2 Tiling Algorithm                                                                 | 66  |

|         | 6.1.3 Layout Optimization                                                              | 67  |

| Chapter | 7: The New TCE Infrastructure                                                          | 68  |

| 7.1     | Overview                                                                               | 69  |

| 7.2     | The TCE Front End                                                                      | 69  |

| 7.3     | Porting existing optimizers                                                            | 70  |

| 7.4     | Translating to ROSE Sage Trees                                                         | 70  |

| Chapter | 8: Experimental Evaluation                                                             | 71  |

| 8.1     | Evaluation of the Loop Fusion Algorithm                                                | 71  |

|         | 8.1.1 Memory Usage                                                                     | 71  |

|         | 8.1.2 Experimental Setup                                                               | 73  |

|         | 8.1.3 Effects of Data Structure Choice and Pruning Strategy on Algorithm Performance . | 74  |

| 8.2     | Evaluation of the Performance of the Generated Code                                    | 82  |

|         | 8.2.1 TCE-Generated Sequential Fortran Code                                            | 82  |

|         | 8.2.2 Multi-core and GPGPU code                                                        | 87  |

|         | 8.2.3 Code Versions                                                                    | 89  |

| 8.3     | Evaluation of the Loop Fusion Optimization for GPGPUs                                  | 97  |

| Chapter | r 9: Conclusions and Future Directions                                                 | 100 |

| 9.1     |                                                                                        | 101 |

| Bibliog | raphy                                                                                  | 104 |

| Vita .  |                                                                                        | 114 |

# **List of Tables**

| 2.1  | Trace of the algorithm for the example from Figure 2.1                                     | 25 |

|------|--------------------------------------------------------------------------------------------|----|

| 4.1  | Algorithm trace for the example from Fig. 2.1 with a dynamic memory allocation cost model. | 51 |

| 8.1  | Comparison of memory usage.                                                                | 72 |

| 8.2  | Configuration of the Intel Xeon workstation.                                               | 74 |

| 8.3  | Memory minimization running times without the extension optimization                       | 76 |

| 8.4  | Space-time tradeoff running times without the extension optimization                       | 77 |

| 8.5  | MemMin — the different pruning numbers                                                     | 80 |

| 8.6  | Space-time tradeoffs — the different pruning numbers without any hashing                   | 80 |

| 8.7  | Space-time tradeoffs — the different pruning numbers with hashing                          | 81 |

| 8.8  | Performance of the generated code for O=48, V=96                                           | 85 |

| 8.9  | Performance of the generated code for CCSD singles, doubles using O=48, V=96               | 85 |

| 8.10 | Performance of the generated Fused-tiled Fortran code for O=48, V=96                       | 85 |

| 8.11 | Running times of generated code optimized with Pluto v0.9.(O=48, 0+V=96)                   | 86 |

| 8.12 | Sequential Runs on a CPU.                                                                  | 91 |

| 8.13 | Sequential Code Performance on CPU for V=120, O+V=180                                      | 92 |

| 8.14 | Pluto Optimized Sequential Code                                                            | 92 |

| 8.15 | Pluto Optimized Multi-core Code                                                            | 92 |

| 8.16 | TCE Optimized Sequential Untiled Code                                                      | 92 |

| 8.17 | TCE Optimized Multi-core Untiled Code                                                      | 92 |

| 8.18 | TCE Optimized Sequential Tiled Code                                                        | 92 |

| 8.19 | TCE Optimized Multi-core Fused-tiled Code                                                  | 92 |

| 8.20 | Unoptimized Sequential Untiled Code                                                        | 93 |

| 8.21 | Unoptimized Multi-core Untiled Code                                                        | 93 |

| 8.22 | Unoptimized Multi-core Fused-tiled Code                                                    | 93 |

| 8.23 | Unoptimized Sequential Fused-tiled Code                                                    | 93 |

| 8.24 | Performance of Fused-tiled Code on GPU                                                     | 93 |

| 8.25 | TCE Optimal vs Pluto (secs) for V=100, O+V=120      | 94 |

|------|-----------------------------------------------------|----|

| 8.26 | TCE Untiled-In-Core (secs) for V=100, O+V=120       | 95 |

| 8.27 | CPU Out-Of-Core (min) for V=120, O+V=180            | 96 |

| 8.28 | Comparison with PPCG on GPU                         | 97 |

| 8.29 | Performance of GPU Out-Of-Core Code                 | 97 |

| 8.30 | Performance of the tensor expression $AB + CD + EF$ | 98 |

# **List of Figures**

| 2.1  | An example multi-dimensional integral and two representations of a computation                 | 6  |

|------|------------------------------------------------------------------------------------------------|----|

| 2.2  | Three loop fusion configurations for the expression tree in Figure 2.1                         | 7  |

| 2.3  | Auxiliary functions for accessing the data structures.                                         | 17 |

| 2.4  | Functions operating on index set sequences.                                                    | 18 |

| 2.5  | The loop fusion algorithm.                                                                     | 19 |

| 2.6  | The cost model for static memory allocation.                                                   | 20 |

| 2.7  | An optimal solution for the example from Figure 2.1                                            | 26 |

| 2.8  | The optimal solution for producing $X[a, b, i, j]$ in memory                                   | 28 |

| 2.9  | The optimal solution for producing $X[a, b, i, j]$ on disk                                     | 28 |

| 2.10 | A space-time tradeoff cost model for static memory allocation.                                 | 31 |

| 2.11 | Modifications for the cost model to allow summation loops as recomputation loops               | 33 |

| 4.1  | Operations on fragments for the dynamic memory allocation cost model                           | 47 |

| 4.2  | The cost model for dynamic memory allocation.                                                  | 49 |

| 5.1  | Procedure to compute indices for fusion                                                        | 56 |

| 5.2  | Partially fused input code                                                                     | 59 |

| 5.3  | Canonicalized code                                                                             | 60 |

| 5.4  | Absyn Tree                                                                                     | 60 |

| 5.5  | Optimal Fusion Graph                                                                           | 61 |

| 5.6  | Optimally Fused code.                                                                          | 61 |

| 8.1  | The spin-orbital CCSD doubles equation.                                                        | 72 |

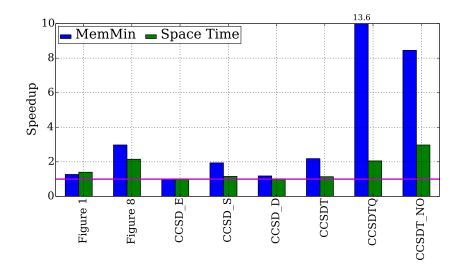

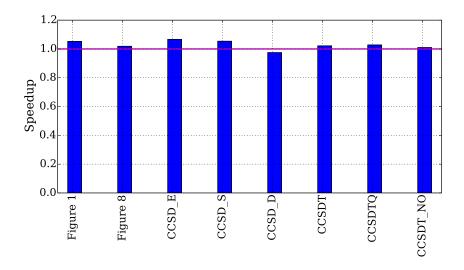

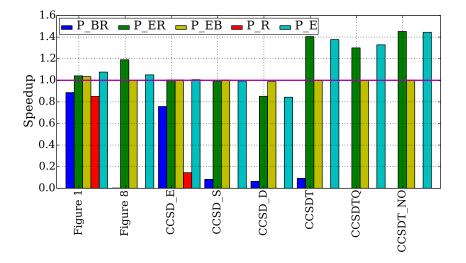

| 8.2  | Speedup achieved by eliminating the extension step below unary nodes where possible            | 75 |

| 8.3  | Speedup of linked lists relative to hashed sets for memory minimization                        | 76 |

| 8.4  | Speedup of hashed sets relative to linked lists for space-time tradeoffs                       | 77 |

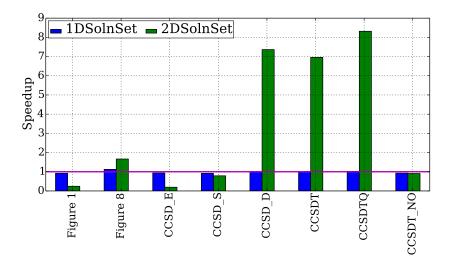

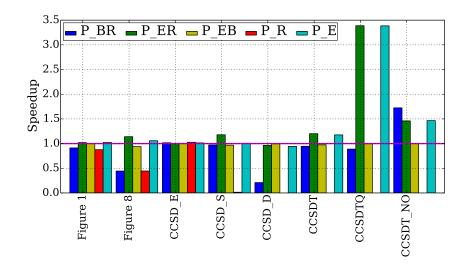

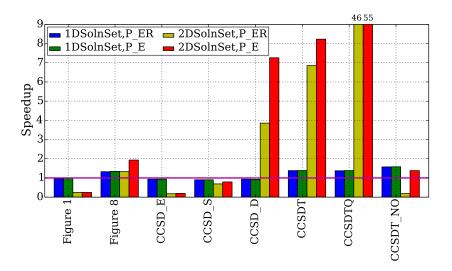

| 8.5  | MemMin — different pruning calls without hashing (relative to linked list)                     | 79 |

| 8.6  | Space-time tradeoffs — different pruning calls without hashing (relative to linked list)       | 80 |

| 8.7  | Space-time tradeoffs — pruning calls with hashing, 2D solution sets (relative to linked list). | 81 |

| 8.8  | T5500 Configuration                             | 83 |

|------|-------------------------------------------------|----|

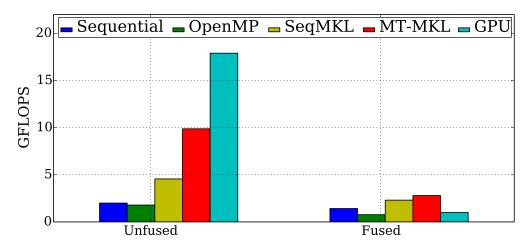

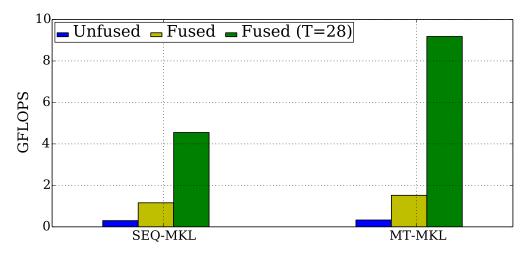

| 8.9  | Unfused Code                                    | 88 |

| 8.10 | Fused-tiled Code                                | 89 |

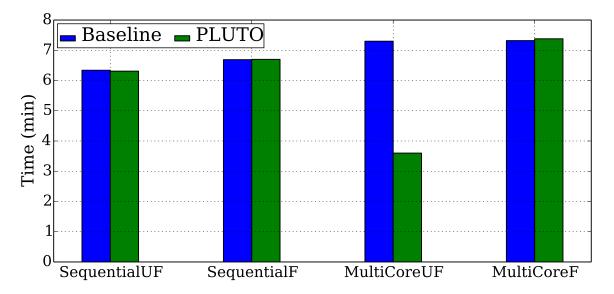

| 8.11 | Baseline vs Pluto Run Times for V=120, O+V=160  | 94 |

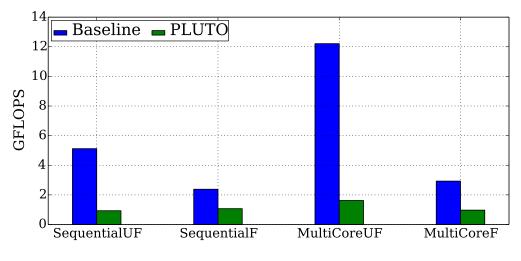

| 8.12 | TCE Optimal vs Pluto (FLOPS) for V=100, O+V=120 | 95 |

| 8.13 | TCE Untiled-In-Core (FLOPS) for V=100, O+V=120  | 95 |

| 8.14 | CPU Out-Of-Core (FLOPS) for V=120, O+V=180      | 96 |

### Abstract

Complex tensor contraction expressions arise in accurate electronic structure models in quantum chemistry, such as the coupled cluster method. The Tensor Contraction Engine (TCE) is a high-level program synthesis system that facilitates the generation of high-performance parallel programs from tensor contraction equations. We are developing a new software infrastructure for the TCE that is designed to allow experimentation with optimization algorithms for modern computing platforms, including for heterogeneous architectures employing general-purpose graphics processing units (GPGPUs). In this dissertation, we present improvements and extensions to the loop fusion optimization algorithm, which can be used with cost models, e.g., for minimizing memory usage or for minimizing data movement costs under a memory constraint. We show that our data structure and pruning improvements to the loop fusion algorithm result in significant performance improvements that enable complex cost models being use for large input equations. We also present an algorithm for optimizing the fused loop structure of handwritten code. It determines the regions in handwritten code that are safe to be optimized and then runs the loop fusion algorithm on the dependency graph of the code. Finally, we develop an optimization framework for generating GPGPU code consisting of loop fusion optimization with a novel cost model, tiling optimization, and layout optimization. Depending on the memory available on the GPGPU and the sizes of the tensors, our framework decides which processor (CPU or GPGPU) should perform an operation and where the result should be moved. We present extensive measurements for tuning the loop fusion algorithm, for validating our optimization framework, and for measuring the performance characteristics of GPGPUs. Our measurements demonstrate that our optimization framework outperforms existing general-purpose optimization approaches both on multi-core CPUs and on GPGPUs.

### Chapter 1 Introduction

The Tensor Contraction Engine (TCE) [BAB<sup>+</sup>05b] targets a class of electronic structure calculations, which involve many computationally intensive components expressed as tensor contractions, essentially a collection of multi-dimensional summations of the product of several higher-dimensional arrays. Manual development of accurate quantum chemistry models in this domain is very tedious and takes an expert several months to years to develop and debug without the proper tools. The TCE aims to reduce the development time to hours/days, by having the chemist specify the computational structures that are addressed by the TCE are present in some computational physics codes modeling electronic properties of semiconductors and metals, and in computational chemistry codes such as ACES II [SGW<sup>+</sup>], GAMESS [SBB<sup>+</sup>93], Gaussian [FF96], NWChem [VBG<sup>+</sup>10], PSI [CSV<sup>+</sup>07], and MOLPRO [WKM<sup>+</sup>10]. The synthesis of efficient parallel code from a high-level specification as a set of tensor contractions requires many optimization issues to be addressed. The approach has broader applicability and can be used in the automatic synthesis of out-of-core algorithms from abstract specifications in the form of loop computations with abstract arrays.

The objective is to minimize the execution time of such computations on a parallel computer while staying within the available memory. In addition to the performance optimization issues pertaining to inter-processor communication and data locality enhancement, there is an opportunity to apply algebraic transformations using the properties of commutativity, associativity and distributivity to reduce the total number of arithmetic operations.

A performance model-driven search-based approach to program transformation [BAB+05b, BBC+02, BKC+03, CBL+02b, KKB+03, KKB+04, KKB+06, GSL+05] has been pursued in the context of TCE. The TCE takes a high-level specification expressed as a set of tensor contraction expressions as input and optimizes it by using algebraic transformations and common subexpression elimination (CSE) to find an equivalent operation-minimal form of the computation and by searching for an evaluation order that uses the least amount of memory. If such an evaluation order is not found, a search for disk I/O placements and loop fusion configurations is performed that minimizes disk-to-memory traffic while ensuring that the

storage requirements for intermediates do not exceed the memory limit. Recent work [MKA11] extended this approach to orchestrate data across an additional level of memory hierarchy, namely GPGPU memory. In certain cases it may be cheaper to recompute parts of a computation instead of paying the penalty for disk I/O. If a computation is that large that after loop fusion some of the intermediates do not even fit on disk, as can be the case in quantum chemistry, there is no choice but to use recomputation to further reduce the storage requirements. For clusters, a communication optimizer has been developed that optimizes the inter-processor communication by considering communication cost together with finding a loop fusion configuration for minimizing storage without exceeding the available memory on each processor [Lam99, HSN<sup>+</sup>05, HLH<sup>+</sup>09]. The input arrays or intermediates that do not fit in memory are transposed if necessary using effective out-of-core transpose algorithms. Finally, the layout of intermediates in memory is optimized and the final code is generated. The TCE can generate either sequential out-of-core code or parallel code using the Global Arrays and Disk-Resident Arrays libraries that interfaces with the NWChem quantum chemistry suite.

We have developed an optimization framework that appropriately models the relation between loop fusion and memory usage. We present algorithms that find an optimal loop fusion configuration that minimizes memory usage, under both static and dynamic memory allocation models.

Reduction of arithmetic operations has been traditionally done by compilers using the technique of common subexpression elimination [FL91]. Much work has been done on improving locality and parallelism by loop fusion [KM94, MA97, SM97]. However, the TCE considers a different use of loop fusion [LCBS99], which is to reduce array sizes and memory usage of automatically synthesized code containing nested loop structures. Traditional compiler research does not address this use of loop fusion because this problem does not arise with manually-produced programs. We are unaware of any work on fusion of multi-dimensional loop nests into imperfectly-nested loops as a means to reduce memory usage.

A prototype of the TCE [Hir03] has been successful in introducing many new models into the NWChem suite by developing several useful domain-specific transformations. An optimizing TCE [BAB<sup>+</sup>05a] has been developed primarily at the Ohio State University that has explored many novel optimization algorithms. However, many key aspects in optimizing tensor contraction codes remain unexplored as both the Prototype TCE and the Ohio TCE versions were primarily developed before the era of multi-cores, GPGPUs, and heterogeneous computing; they do not provide sufficient support for tree transformations and for generating multi-core parallelism or GPU code. Their monolithic structure is too inflexible to adapt for multi-target

code generation. They also do not take advantage of major recent advances in polyhedral compilation models that provide exact dependency analysis and a more efficient way to perform program transformations, as can be found in the tools Pluto [BHRS08a, BBK<sup>+</sup>08, BHRS08b, BRS10] and PrimeTile [HBB<sup>+</sup>09b, HBB<sup>+</sup>09a, BHH<sup>+</sup>10]. The TCE does not have Fortran or C++ frontend support for handwritten code and does not support dependency analysis. Also, since not all quantum chemistry codes can be expressed in the form of tensor contraction expressions, it would be desirable if some of the optimization algorithms, in particular the loop fusion and tiling optimizations, could be applied to handwritten code and if the TCE optimization algorithms could support symmetric and block-sparse tensors. Additional research on data movement optimization and parallelization and on developing the cost models for the compiler to perform these optimizations for heterogeneous systems is needed. The final product should also interface with quantum chemistry suites and other simulation tools.

This dissertation aims to improve upon the existing TCE compilation framework by addressing some of the unexplored issues through effective performance models and search-based optimization algorithms and by generating efficient, platform-adaptable implementations of tensor contractions. The contributions of this thesis are the following:

- We have developed a new software infrastructure for the TCE on top of the ROSE compiler infrastructure [RSE]. We have added a frontend to ROSE for our improved TCE source language and provide support for implementing TCE optimization algorithms both in the frontend and on ROSE abstract syntax trees.

- We have made significant performance improvements to the loop fusion optimization algorithm that allow large quantum chemistry equations to be optimized with complex (2-dimensional) loop fusion cost models, and we have developed a loop fusion cost model for memory minimization with dynamic memory allocation.

- We have developed a loop fusion optimization algorithm that can be applied to simple handwritten code as an alternative to the loop fusion algorithm for expression trees representing tensor contraction equations.

- We have developed an optimization framework for generating GPGPU code for tensor contractions. The optimization framework consists of a novel cost model for the loop fusion algorithm and refinements of the tiling and layout optimization algorithms.

- We have performed extensive measurements to document the performance characteristics of the loop fusion algorithm as well as to understand the performance characteristics of tensor contraction computations on multi-core CPUs and on GPGPUs.

- We have demonstrated that the performance of code resulting from our optimization framework for dense tensor contractions is superior to that of code generated by polyhedral compiler frameworks, both on multi-core CPUs and on GPGPUs.

### Chapter 2 Background

### 2.1 Operation Minimization

In the class of computations considered, the final result to be computed can be expressed as multi-dimensional integrals of the product of many input arrays. Due to commutativity, associativity and distributivity, there are many different ways to obtain the same final result and they could differ widely in the number of floating point operations required. The problem of finding an equivalent form that computes the result with the least number of operations is not trivial and so a software tool for doing this is desirable.

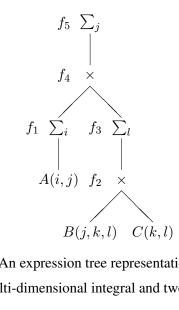

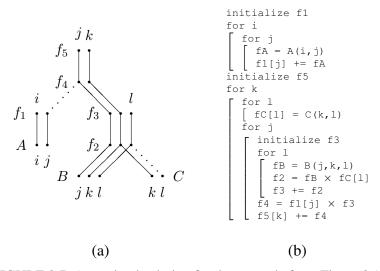

Consider, for example, the multi-dimensional integral shown in Figure 2.1(a), where the input arrays are assumed to be produced by generator functions. If implemented directly as expressed (i.e., as a single set of perfectly-nested loops), the computation would require  $2 \times N_i \times N_j \times N_k \times N_l$  arithmetic operations to compute. However, assuming associative reordering of the operations and use of the distributive law of multiplication over addition is satisfactory for the floating-point computations, the above computation can be rewritten in various ways. One equivalent form that only requires  $2 \times N_j \times N_k \times N_l + 2 \times N_j \times N_k + N_i \times N_j$  operations is given in Figure 2.1(b). It expresses the sequence of steps in computing the multi-dimensional integral as a sequence of formulas. Each formula computes some intermediate result and the last formula gives the final result. A formula is either a product of two input/intermediate arrays or a integral/summation over one index, of an input/intermediate array. A sequence of formulas can also be represented as an expression tree. For instance, Figure 2.1(c) shows the expression tree corresponding to the example formula sequence. The problem of finding a formula sequence that minimizes the number of operations has been proved to be NP-hard [LSW97].

#### 2.2 Memory Minimization Problem

In implementing the computation represented by an operation-count-optimal formula sequence (or an expression tree), it may be necessary to perform loop fusion to reduce the sizes of the intermediate arrays. Without fusing the loops, intermediate arrays could be too large to fit into available memory. There are many different ways to fuse the loops and they could result in different memory usage.

$$W[k] = \sum_{(i,j,l)} A(i,j) \times B(j,k,l) \times C(k,l)$$

(a) A multi-dimensional integral

| $f_A[i,j]$      | = | A(i,j)                       |

|-----------------|---|------------------------------|

| $f_1[j]$        | = | $\sum_i f_A[i,j]$            |

| $f_B[j,k,l]$    | = | B(j,k,l)                     |

| $f_C[k, l]$     | = | C(k,l)                       |

| $f_2[j,k,l]$    | = | $f_B[j,k,l] \times f_C[k,l]$ |

| $f_3[j,k]$      | = | $\sum_l f_2[j,k,l]$          |

| $f_4[j,k]$      | = | $f_1[j] \times f_3[j,k]$     |

| $W[k] = f_5[k]$ | = | $\sum_{j} f_4[j,k]$          |

(b) A formula sequence for computing (a)

FIGURE 2.1. An example multi-dimensional integral and two representations of a computation.

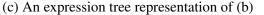

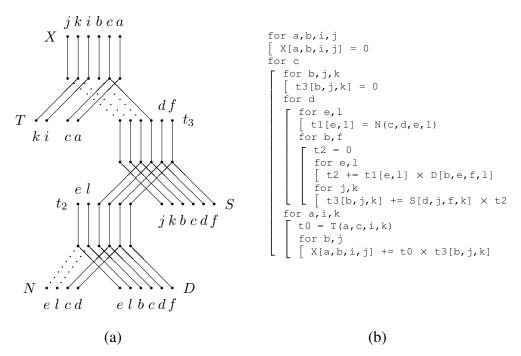

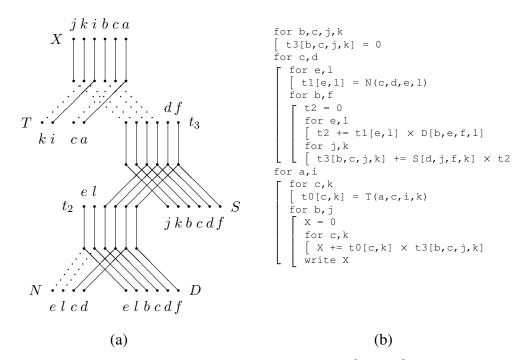

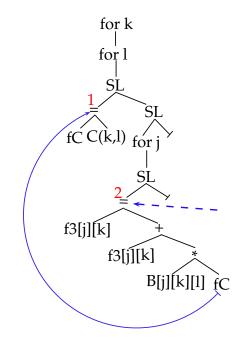

Consider again the computation  $W[k] = \sum_{j} (\sum_{i} (A(i, j)) \times \sum_{l} (B(j, k, l) \times C(k, l)))$ , with the expression tree shown in Figure 2.1(c). A naive approach to implement this expression is to use a set of perfectly nested loops for each node in the tree, as shown in Figure 2.2(a). The brackets indicate the scopes of the loops. Code for array allocation and initialization is omitted for clarity. Figure 2.2(b) shows how the sizes of the arrays may be reduced by using loop fusion. It shows the resulting loop structure after fusing all the loops between A and  $f_1$ , all the loops among B, C,  $f_2$ , and  $f_3$ , and all the loops between  $f_4$  and  $f_5$ . After fusing all the loops between a node and its parent, each array element gets used immediately after it is produced. The dimensions of the child array are, therefore, no longer needed and can be eliminated. Here,  $f_A$ ,  $f_B$ ,  $f_C$ ,  $f_2$ , and  $f_4$  are reduced to scalars. Note that some loop nests (such as those for B and C) were reordered and some loops within loop nests (such as the j-, k-, and l-loops for B,  $f_2$ , and  $f_3$ ) were permuted in order to facilitate loop fusions.

FIGURE 2.2. Three loop fusion configurations for the expression tree in Figure 2.1.

For this example, we assume the leaf node arrays (i.e., input arrays) can be generated one element at a time by a generator function so that loop fusions with their parents are allowed. This assumption holds for arrays in which the value of each element is a function of the array subscripts, as in many arrays in the physics and chemistry computations that we work on. Our algorithm also handles the case where arrays are already memory-resident, and, as will be shown in Section 2.4.6, the case where an input array has to be read in or produced in a certain order, in slices, or in its entirety.

Figure 2.2(c) shows another possible loop fusion configuration obtained by fusing all the *j*-loops and then all the *k*-loops and *l*-loops inside. The sizes of all arrays except  $f_C$  and  $f_5$  are smaller. By fusing the *j*-, *k*-, and *l*-loops between those nodes, the *j*-, *k*-, and *l*-dimensions of the corresponding arrays can be eliminated. Hence,  $f_B$ ,  $f_1$ ,  $f_2$ ,  $f_3$ , and  $f_4$  are reduced to scalars while  $f_A$  becomes a one-dimensional array. Since *j* is the outermost loop, the *k*- and *l*-loops cannot be fused between *C* and  $f_2$ .

In general, fusing a *t*-loop between a node v and its parent eliminates the *t*-dimension of the array v and reduces the array size by a factor of  $N_t$ . In other words, the size of an array after loop fusions equals the product of the ranges of the loops that are not fused with its parent. We only consider fusions of loops among nodes that are all transitively related by (i.e., form a transitive closure over) parent-child relations. Fusing loops between unrelated nodes (such as fusing siblings without fusing their parent) has no effect on array sizes. We also restrict our attention to loop fusion configurations that do not increase the operation count. The tradeoff between memory usage and arithmetic operations is considered in Section 2.4.7.

For the class of loops considered here, the only dependence relations are those between children and parents, and array subscripts are simply loop index variables. Loop permutations, loop nests reordering, and loop fusions are, therefore, always legal as long as child nodes are evaluated before their parents. This freedom allows the loops to be permuted, reordered, and fused in a large number of ways that differ in memory usage. Finding a loop fusion configuration that uses the least memory is not trivial.

In the examples above, we have assumed that leaf node arrays are generated and that each array element should be generated only once. This assumption is appropriate if generating array elements is expensive. However, if leaf arrays are already in memory, this assumption is too restrictive. By allowing leaf arrays to be accessed repeatedly at zero cost, we might enable additional loop fusions. For example, if the array C in Figure 2.2(c) were already in memory, we could allow rereading it for every iteration of the *j*-loop, which would allow full fusion of C with  $f_2$ . Since the appropriate treatment of leaf arrays depends on the application, we allow both. We will use the function call notation A(i, j) for arrays that are generated by a generator function call and the notation A[i, j] for arrays that are already memory resident.

**Definition 2.2.1.** More formally, we define an *expression tree* to be a tree structure consisting of the following types of nodes:

- Array(a,i): An array reference a[i] of a memory-resident array a with index vector i.

- Fun(f, i): A function call f(i) of function f with index vector i as arguments.

- Const(x): The integer or floating point constant x.

- BinOp(o, l, r): A binary operator expression l o r with operator o, left subtree l, and right subtree r, where o ∈ {+, -, \*}.

- Sum(i, t): A summation operator  $\sum_i t$  with summation index set i and subtree t.

We define the *memory minimization problem* as follows:

Given an expression tree T and the ranges of all indices.

Find a loop structure for computing T that uses the least amount of temporary storage without increasing the operation count. We assume that leaf array references and constants are memory-resident and can be accessed repeatedly at zero cost.

### 2.3 Fusion Graphs

For facilitating the enumeration of all possible loop fusion configurations for a given expression tree, we define a representation of the expression tree's loop structure we call a *fusion graph*. The fusion graph makes the indices of nodes in the expression tree explicit and indicates the scopes of fused loops.

**Definition 2.3.1.** Let *T* be an expression tree. For any given node  $v \in T$ , let subtree(v) be the set of nodes in the subtree rooted at v, parent(v) be the parent node of v, and indices(v) be the set of loop indices for v(including the summation indices sumindices(v) if v is a summation node). A *fusion graph* representation of a fused loop structure for *T* is constructed as follows:

1. Corresponding to each node v in T a fusion graph contains a set of vertices, one for each index  $i \in indices(v)$ .

- For each Array or Const node v in T and for each index i ∈ indices(parent(v)) indices(v) that is fused between v and its parent (i.e., for each loop in which v is accessed redundantly), an i-index is added to the set of nodes corresponding to v.

- 3. For each loop of index *i* that is fused between a node and its parent, the *i*-vertices for the two nodes are connected with a *fusion edge*.

- 4. For each index *i* that is shared between a node and its parent, for which the corresponding loops are not fused, the *i*-vertices for the two nodes are connected with a *potential fusion edge*.

Figure 2.2 shows the fusion graphs alongside the loop fusion configurations. Fusion edges are drawn as solid lines. Potential fusion edges, i.e., fusion opportunities that were not exploited, are drawn as dotted lines. As an example, consider the loop fusion configuration in Figure 2.2(b) and the corresponding fusion graph in Figure 2.2(e). Since the *j*-, *k*-, and *l*-loops are fused between  $f_2$  and  $f_3$ , there are three fusion edges between  $f_2$  and  $f_3$  in the fusion graph, one for each of the three loops. Since no loops are fused between  $f_3$  and  $f_4$ , the edges between  $f_3$  and  $f_4$  in the fusion graph remain potential fusion edges.

**Definition 2.3.2.** In a fusion graph, we call each connected component of fusion edges (i.e., a maximal set of connected fusion edges) a *fusion chain*, which corresponds to a fused loop in the loop structure. The *scope* of a fusion chain c, denoted scope(c), is defined as the set of nodes it spans.

In Figure 2.2(f), there are three fusion chains, one for each of the j-, k-, and l-loops; the scope of the shortest fusion chain is  $\{B, f_2, f_3\}$ . The scope of any two fusion chains in a fusion graph must either be disjoint or a subset/superset of each other. Scopes of fusion chains do not partially overlap because loops do not (i.e., loops must be either separate or nested). Therefore, any fusion graph with fusion chains whose scopes are partially overlapping is illegal and does not correspond to any loop fusion configuration.

Fusion graphs help us visualize the structure of the fused loops and find further fusion opportunities. If we can find a set of potential fusion edges that, when converted to fusion edges, does not lead to partially overlapping scopes of fusion chains, then we can perform the corresponding loop fusions and reduce the sizes of some arrays. For example, the *i*-loops between A and  $f_1$  in Figure 2.2(f) can be further fused and array  $f_A$  would be reduced to a scalar. If converting all potential fusion edges in a fusion graph to fusion edges does not make the fusion graph illegal, then we can completely fuse all the loops and achieve optimal memory usage. But for many fusion graphs in real-life loop configurations (including the ones in Figure 2.2), this does not hold. Instead, potential fusion edges may be mutually prohibitive; fusing one loop could prevent the fusion of another. In Figure 2.2(e), fusing the *j*-loops between  $f_1$  and  $f_4$  would disallow the fusion of the *k*-loops between  $f_3$  and  $f_4$ .

Although a fusion graph specifies what loops are fused, it does not fully determine the permutations of the loops and the ordering of the loop nests. As we will see in Section 4.4, under dynamic memory allocation, reordering loop nests could alter memory usage without changing array sizes.

So far, we have been describing the fusion between a node and its parent by the set of fused loops (or the loop indices such as  $\{i, j\}$ ). But in order to compare loop fusion configurations for a subtree, it is desirable to include information about the relative scopes of the fused loops in the subtree.

**Definition 2.3.3.** The *loop scope* of index *i* in a subtree rooted at *v*, denoted scope(i, v), is defined in the usual sense as the set of nodes in the subtree that the fused loop spans. That is, if the *i*-loop is fused,  $scope(i, v) = scope(c) \cap subtree(v)$ , where *c* is a fusion chain for the *i*-loop with  $v \in scope(c)$ . If the *i*-loop of *v* is not fused, then  $scope(i, v) = \{v\}$ . As an example, for the fusion graph in Figure 2.2(e),  $scope(j, f_3) = \{B, f_2, f_3\}$ .

For describing the relative scopes of a set of fused loops, we introduce the notion of an *indexset sequence*, which is defined as an ordered list of disjoint, non-empty sets of loop indices. For example,  $f = \langle \{i, k\}, \{j\} \rangle$ is an indexset sequence. For simplicity, we write each indexset in an indexset sequence as a string. Thus, f is written as  $\langle ik, j \rangle$ .

**Definition 2.3.4.** Let g and g' be indexset sequences. We denote by |g| the number of indexsets in g, g[r] the r-th indexset in g, and set(g) the union of all indexsets in g, i.e.,  $set(g) = \bigcup_{1 \le r \le |g|} g[r]$ . An index i has rank r in indexset sequence g, i.e., rank(i, g) = r, if and only if  $i \in g[r]$ .

For example, if  $f = \langle ik, j \rangle$ , then |f| = 2,  $f[1] = \{i, k\}$ ,  $set(f) = set(\langle j, i, k \rangle) = \{i, j, k\}$ , and rank(i, f) = 1.

An indexset sequence f represents constraints on the loop structure. For two indices i and j, if rank(i, f) < rank(j, f), then the j-loop is constrained to be within the i-loop. If two indices have the same rank in f, there is no constraint on the corresponding loops and the loops, therefore, can be permuted. For example, the indexset sequence  $\langle ik, j \rangle$  represents the constraint that the j-loop is within the i and k loops and that the latter two can be permuted.

We define a *nesting* of the loops at a node v as an indexset sequence. Intuitively, the loops at a node are ranked by their scopes in the subtree. Two loops have the same rank (i.e., are in the same indexset) if they have the same scope. For example, in Figure 2.2(e), the nesting at  $f_3$  is  $\langle kl, j \rangle$ , the nesting at  $f_4$  is  $\langle jk \rangle$ , and the nesting at B is  $\langle jkl \rangle$ .

**Definition 2.3.5.** Formally, a nesting of the loops at a node v is an indexset sequence h such that

- 1. set(h) = indices(v) and

- 2. for all  $i, i' \in set(h)$  where r = rank(i, h) and r' = rank(i', h),

- (a) r = r' if and only if scope(i, v) = scope(i', v), and

- (b) r < r' if and only if  $scope(i, v) \supset scope(i', v)$ .

By definition, the loop nesting at a leaf node v must be  $\langle indices(v) \rangle$  because all loops at v have the same scope of  $\{v\}$ .

Similarly, we use the notion of an indexset sequence to define a *fusion*. Intuitively, the loops fused between a node and its parent are ranked by their scopes in the subtree from largest to smallest. For example, in Figure 2.2(f), the fusion between  $f_2$  and  $f_3$  is  $\langle jkl \rangle$  and the fusion between  $f_4$  and  $f_5$  is  $\langle j,k \rangle$  (because the *j*-loop covers two more nodes, A and  $f_1$ ).

**Definition 2.3.6.** Formally, a fusion between a node v and parent(v) is an indexset sequence f such that

- 1.  $set(f) \subseteq indices(v) \cap indices(parent(v)),$

- 2. for all  $i \in set(f)$ , the *i*-loop is fused between v and parent(v), and

- 3. for all  $i, i' \in set(f)$  where r = rank(i, f) and r' = rank(i', f),

- (a) r = r' if and only if scope(i, v) = scope(i', v), and

- (b) r < r' if and only if  $scope(i, v) \supset scope(i', v)$ .

A legal fusion graph (corresponding to a loop fusion configuration) for an expression tree T can be built up in a bottom-up manner by merging legal fusion graphs for the subtrees of T. For characterizing legal fusions and for motivating the algorithm for constructing a fusion graph, we need to define a *prefix* relation between indexset sequences. **Definition 2.3.7.** Let g and g' be indexset sequences. We say that g' is a *prefix* of g if  $|g'| \le |g|$ , g'[r] = g[r] for all  $1 \le r < |g'|$ , and  $g'[|g'|] \subseteq g[|g'|]$ . We write this relation as prefix(g', g). E.g.,  $\langle \rangle$ ,  $\langle i \rangle$ ,  $\langle k \rangle$ ,  $\langle ik \rangle$ , and  $\langle ik, j \rangle$  are prefixes of  $\langle ik, j \rangle$ , but  $\langle i, j \rangle$  is not.

For a given node v, the nesting h at v summarizes the fusion graph for the subtree rooted at v and determines what fusions are allowed between v and its parent. A fusion f is legal for a nesting h at v, denoted legal(f, h, v), if prefix(f, h) and  $set(f) \subseteq indices(parent(v))$ . This is because loops with larger scopes must be fused before fusing those with smaller scopes, and because only loops common to both v and its parent may be fused.

As an example, consider the fusion graph for the subtree rooted at  $f_2$  in Figure 2.2(e). Since the nesting at  $f_2$  is  $\langle kl, j \rangle$  and *indices* $(f_3) = \{j, k, l\}$ , the legal fusions between  $f_2$  and  $f_3$  are  $\langle \rangle, \langle k \rangle, \langle l \rangle, \langle kl \rangle$ , and  $\langle kl, j \rangle$ .

**Definition 2.3.8.** All legal fusions for a node v with nesting h are prefixes of a maximal legal fusion, denoted maxFusion(h, v). We define f' = maxFusion(h, v) if and only if legal(f', h, v), and for all f, legal(f, h, v) implies prefix(f, f'). In Figure 2.2(e), the maximal legal fusion for C is  $\langle kl \rangle$ , and for  $f_2$  is  $\langle kl, j \rangle$ .

### 2.4 Loop Fusion Algorithm

Given a specification of the required computation as a multi-dimensional sum of the product of input arrays, we first determine an equivalent sequence of multiplication and summation formulas that compute the result using a minimum number of arithmetic operations. Each formula computes and stores some intermediate results in an intermediate array. By computing the intermediate results once and reusing them multiple times, the number of arithmetic operations can be reduced.

The simplest way to implement an optimal sequence of multiplication and summation formulas is to compute the formulas one by one, each coded as a set of perfectly nested loops, and to store the intermediate results produced by each formula in an intermediate array. However, in practice, the input and intermediate arrays could be so large that they cannot fit into the available memory. Hence, there is a need to fuse the loops as a means of reducing memory usage. By fusing loops between the producer loop and the consumer loop of an intermediate array, intermediate results are formed and used in a pipelined fashion and they reuse the same reduced array space. The problem of finding a loop fusion configuration that minimizes memory usage without increasing the operation count is not trivial.

#### 2.4.1 Algorithm for Static Memory Allocation

We use a dynamic programming algorithm for computing the fusion graph that uses the least amount of memory. The algorithm traverses the expression tree bottom-up and generates a set of possible loop structures for each tree node. Each solution is represented as a pair containing a fusion and the memory cost.

Let v be the root node of an expression tree. The algorithm has the following recursive structure:

- 1. If v is a Fun node, a single solution is generated that indicates that v can be fully fused with its parent.

- 2. If v is an Array or Const node, a single solution is generated that indicates that v can be accessed repeatedly at no cost and that v can be fused with any loop, not only those in *indices*(v).

- 3. If v is a Sum node, multiple solutions for v are created out of each solution for the subtree. For each solution for the subtree, we generate all the possible fusions with v, i.e., we enumerate all the possibilities for how the loop structure corresponding to the subtree solution can be embedded within a loop structure of the parent. The summation indices as well as any indices whose loops are nested within the summation loops are then removed from the solutions since they cannot be further fused with v's parent.

- 4. If v is a BinOp node, solutions for the left and right subtrees must be combined to form a solution for v. For each solution for a subtree, we again generate all the possible fusions with v. Then, for all compatible pairs of possible fusions for the two subtrees, a solution for v is generated by merging the fusion constraints from the subtree solutions.

- 5. In each step, inferior solutions are pruned out.

Before presenting the details of the algorithm, we need to define the mechanisms by which solutions are constructed out of solutions for subtrees.

**Definition 2.4.1.1.** The *concatenation* of an indexset sequence g and an indexset x, denoted g + x, is defined as the indexset sequence g' such that if  $x \neq \emptyset$ , then |g'| = |g| + 1, g'[|g'|] = x, and for all  $1 \le r < |g'|$ , g'[r] = g[r]; otherwise, g' = g.

When constructing a loop nesting for a node u out of solutions for the subtrees, we must ensure that the nesting is compatible with the fusions between u and the subtrees. We compute the nesting of u by *extending* the fusions to the indices of u.

**Definition 2.4.1.2.** Let u be the parent of a node v and let f be a fusion between u and v. The *extended nesting* of fusion f for node u, denoted *extendNesting*(f, u), is defined as *extendNesting*(f, u) = f + (indices(u) - set(f)).

If v is the only child of u, then the loop nesting at u as a result of fusion f between u and v is *extendNesting*(f, u). I.e., all the loops that are not fused between u and v must be nested within the fused loops. For example, in Figure 2.2(e), if the fusion between  $f_2$  and  $f_3$  were  $\langle kl \rangle$ , then the nesting at  $f_3$  would be  $\langle kl, j \rangle$ .

If u is a binary node, then the extended nestings of the subtrees must be compatible. The constraints on the loop structure expressed by the extended nestings of the subtrees must be merged to produce the nesting of u.

**Definition 2.4.1.3.** Suppose u has the two children v and v', whose fusions with u are f and f', respectively. For the fusion graph for the subtree rooted at u (which will be merged from those of v and v') to be legal, h = extendNesting(f, u) and h' = extendNesting(f', u) must be *compatible* according to the condition: for all  $i \in h[r]$  and  $j \in h[s]$ , if r < s and  $i \in h'[r']$  and  $j \in h'[s']$ , then  $r' \leq s'$ .

This requirement ensures an *i*-loop that has a larger scope than a *j*-loop in one subtree will not have a smaller scope than the *j*-loop in the other subtree. If the extended nestings h and h' of the subtrees are compatible, they can be merged to form a nesting of u.

**Definition 2.4.1.4.** Let h and h' be compatible extended nestings for the subtrees of u. The nesting h'' = mergeNesting(h, h') of u must satisfy the following conditions. For all  $i \in h''[r'']$  and  $j \in h''[s'']$ , if  $i \in h[r]$ ,  $i \in h'[r']$ ,  $j \in h[s]$ , and  $j \in h'[s']$ , then  $[r'' = s'' \Rightarrow r = s$  and r' = s'] and  $[r'' \leq s'' \Rightarrow r \leq s$  and  $r' \leq s']$ .

This definition ensures that h'' is compatible with both h and h'. Effectively, the loops at u are re-ranked by their combined scopes in the two subtrees to form h''. As an example, in Figure 2.2(e), if the fusion between  $f_1$  and  $f_4$  is  $f = \langle j \rangle$  and the fusion between  $f_3$  and  $f_4$  is  $f' = \langle k \rangle$ , then  $h = extendNesting(f, f_4) = \langle j, k \rangle$ and  $h' = extendNesting(f', f_4) = \langle k, j \rangle$  would be incompatible. But if f were changed to  $\langle \rangle$ , then h = $extendNesting(f, f_4) = \langle jk \rangle$  would be compatible with h', and the resulting nesting at  $f_4$  would be  $\langle k, j \rangle$ .

As outlined above, the algorithm generates a set of solutions for each node. In order to effectively prune inferior solutions from such a set, we need a comparison relation on nestings and fusions. Informally, a nesting h is *more or equally constraining than* another nesting h' for the same node v if any loop fusion configuration for the rest of the tree that is compatible with h is also compatible with h'.

**Definition 2.4.1.5.** We define a nesting h for a node v to be more or equally constraining than a nesting h', denoted  $h \sqsubseteq h'$ , if and only if h = mergeNesting(h, h'). Note that  $\sqsubseteq$  is a partial order: if h and h' are not compatible, then  $h \sqsubseteq h'$  is undefined.

If  $h \sqsubseteq h'$ , then for all  $i \in h[r]$  and  $j \in h[s]$ , there exist r', s' such that  $i \in h'[r']$  and  $j \in h'[s']$  and  $[r < s \Rightarrow r' \le s']$  and  $[r = s \Rightarrow r' = s']$ . I.e., for any pair of loops i and j, if h' constrains one of them to be nested within the other, so does h. If h does not constrain them, neither does h'. Any nesting for the parent of v that can be constructed out of the nesting h for v can, therefore, also be constructed out of h'.

Comparing the nestings at  $f_3$  between Figure 2.2(e) and (f), the nesting  $\langle kl, j \rangle$  in (e) is more constraining than the nesting  $\langle jkl \rangle$  in (f).

For defining the relation  $\sqsubseteq$  for fusions, we need the additional requirement that the sets of indices in the two fusions are the same:

**Definition 2.4.1.6.** We define a fusion f to be more or equally constraining than a fusion f', denoted  $f \sqsubseteq f'$ , if and only if set(f) = set(f') and f = mergeNesting(f, f').

### 2.4.2 Algorithm Details

The algorithm traverses the expression tree bottom up and creates a set of solutions for each node in the expression tree. Each solution S(f, c, t) for an expression tree t contains the maximal fusion f with the parent and the memory cost c. Since under a static memory allocation model all the intermediate arrays for evaluating an expression exist during the entire computation, the memory cost is simply the sum of the sizes of all the arrays and scalars. For presentation purposes, fusions, or indexset sequences in general, are represented as lists of lists of strings.

For each solution, we must record the subtree solution(s) from which this solution was constructed. To do so, we use the following solution tree data structure:

- Leaf(s): A leaf in the solution tree with solution s.

- Unary(s, t): A unary node in the solution tree with solution s and subtree t.

- Binary(s, l, r): A binary node in the solution tree with solution s, left subtree l, and right subtree r.

- Extended (s, h, t): An extended solution node with solution s, extended nesting h, and subtree t.

• Reduced(s, i, t): A reduced tree node with solution s, index set i, and subtree t.

The loop fusion algorithm will construct a set of such solution trees for each node in the expression tree. The structure of a solution tree mirrors the structure of the expression tree. For an Array, Fun or Const node, a single Leaf node is constructed. For Sum and BinOp nodes, the algorithm constructs Unary and Binary nodes, respectively. In addition, an Extended node is constructed when extending a solution for a subtree to the indices of the parent. Similarly, a Reduced node is constructed for removing the summation indices out of the the solutions for a Sum node. Extended and Reduced nodes correspond to edges in the expression tree. Making extended nodes explicit improves the efficiency of the algorithm, since extended nestings do not have to be recomputed, while keeping the code structure simple. Reduced nodes mostly serve to make the step of removing summation indices explicit and aid in debugging.

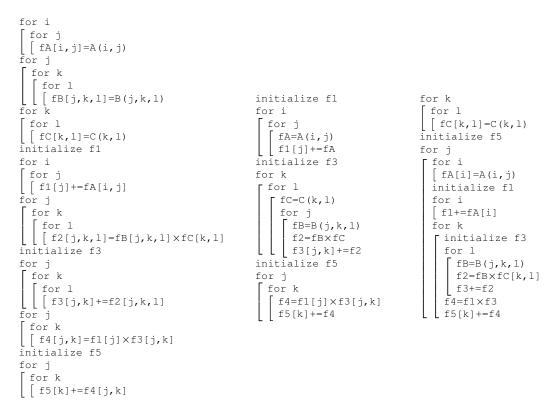

Before describing the algorithm in detail, we need to introduce some helper functions and operations on indexset sequences. Figure 2.3 defines auxiliary functions for expression trees and solution trees. The functions indices and fusible return the set of indices and the set of fusible indices of a node, respectively. The call fusedSize (v, f) returns the memory needed for storing the result of node v under the fusion f with its parent. The storage needed for an Array node is zero for the purpose of the fusion algorithm, since Array nodes are assumed to be memory resident and do not change in size based on the fusion. The functions getFusion and getSoln are simply accessor functions for the data structure; getNesting constructs the extended nesting from an Extended node to allow pruning extended solutions and for passing it to the cost model so it does not need to be recomputed.

indices(v): return { i | i is an index at node v }

fusible(v): return { i | i in indices(v) and i not a summation index of v }

fusedSize(v, f):

if v is an Array or a Const node then return 0

else return Product of range(i) for i in (fusible(v) - set(f))

getFusion(S(f, c, t)): return f

getSoln(s): return the solution out of solution tree node s

getNesting(s):

if s is of the form Extended(S(f, c, t), h, s') then return h

else return getFusion(getSoln(s))

FIGURE 2.3. Auxiliary functions for accessing the data structures.

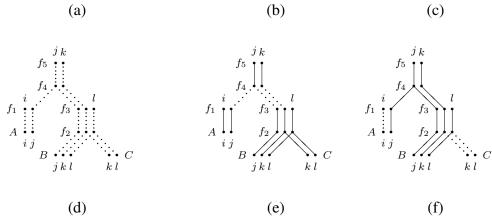

Figure 2.4 shows functions that operate on indexset sequences. Indexset sequences are represented as lists of lists of strings. The constant any, represented as the special indexset sequence  $\langle * \rangle$ , is used as the

maximal fusion for Array and Const nodes. It indicates that any index of the parent can be fused between the leaf node and the parent, not only indices of the leaf node. The function set returns the set of indices in a fusion. The functions prefixes and extendNesting are used for constructing extended solutions. prefixes takes a maximal fusion f as argument and returns the set of all prefixes of f or actual fusions. extendNesting takes an actual fusion as argument and constructs an extended nesting.

```

any = [["*"]]

set(f): return { i | i occurs in indexset sequence f }

prefixes (f): return set of all prefixes of indexset sequence f

extendNesting(f, i):

if f = any then return [i]

else return f + (i - set(f))

maxPrefix(f, i):

return maximum prefix of indexset sequence f containing only indices in i

merge(h, h'):

if h = nil or h' = nil then return nil

else

y = intersect(head(h), head(h'))

x = head(h) - y; x' = head(h') - y

if y = nil then return nil

else if x = nil and x' = nil then return y :: merge(tail(h), tail(h'))

else if x = nil then return y :: merge(tail(h), x'::tail(h'))

else if x' = nil then return y :: merge(x::tail(h), tail(h'))

else return y :: merge(x::tail(h), x'::tail(h'))

mergeNesting(h, h'):

if h = any or h' = any or set(h) <> set(h') then raise Incompatible

else

m = merge(h, h')

if set(m) = set(h) then return m else raise Incompatible

leg(h, h'): return set(h) = set(h') and h = merge(h, h')

```

FIGURE 2.4. Functions operating on index set sequences.

The function maxPrefix is used for removing summation indices from a solution for a summation node together with any indices whose loops are constrained to be within the summation loops. The helper function merge, which is used by mergeNesting and leq, constructs the least constraining indexset sequence that is more or equally constraining than its arguments; it returns nil if the arguments are not compatible. The function mergeNesting is used for merging extended nestings from the two subtrees of a binary node. The boolean function leq(h, h') is true if h is more or equally constraining than h', i.e.,  $h \sqsubseteq h'$ . If h and h' do not have the same sets of indices or are incomparable, or if h is not more or equally constraining than h', leq(h, h') is false. This makes leq a total function and allows both fusions and nestings to be compared.

The main part of the fusion algorithm is shown in Figure 2.5. The calculation of the cost of individual solutions has been factored out into the cost model shown in Figure 2.6. To allow for generalizations of

the cost model, each of the cost model functions returns a set containing a single solution. The heart of the algorithm is the function minMemFusionSet, which traverses the expression tree bottom-up and constructs a set of solution trees in every step.

```

minMemFusion(t): return head(reduceSolnSet(minMemFusionSet(t), nil))

minMemFusionSet(t):

if t is an Array, Fun, or Const node then

return { Leaf(s) | s in makeLeafSoln(t)) }

else if t is of the form Sum(i, 1) then

return makeUnarySolnSet(extendSolnSet(minMemFusionSet(l), t, true), t)

else if t is of the form BinOp(o, l, r) then

return makeBinarySolnSet(extendSolnSet(minMemFusionSet(l), t, false),

extendSolnSet(minMemFusionSet(r), t, false), t)

makeUnarySolnSet(S1, t):

U = \{ Unary(s, s1) \mid s1 \text{ in } S1 \text{ and } \}

s in makeUnarySoln(getSoln(s1), getNesting(s1), t) }

return reduceSolnSet(U, fusible(t))

makeBinarySolnSet(S1, S2, t):

B = \{ Binary(s, s1, s2) \mid s1 in S1 and s2 in S2 and

s in makeBinarySoln(getSoln(s1), getNesting(s1),

getSoln(s2), getNesting(s2), t)

where exception Incompatible was not raised }

return pruneSolnSet(B)

extendSolnSet(S, t, u):

s = getSoln(head(S))

f = getFusion(s)

i = indices(t)

if f = any then return { Extended(s, extendNesting(f, i), head(S)) }

else

E = Union({ e | st in S and e = extendSoln'(st, i, u) })

return pruneSolnSet(E)

extendSoln'(st, i, u):

s = getSoln(st)

f = getFusion(s)

if (u or length(f) = 1) and (set(f) = i or subset(i, set(f))) then return \{ st \}

else return { Extended(s', f'', st) | f' in prefixes(f)

and s' in extendSoln(s, f')

and f'' = extendNesting(f', i) }

reduceSolnSet(S, i):

R = { Reduced(r, i, s) | s in S and r in reduceSoln(getSoln(s), i) }

return pruneSolnSet(R)

pruneSolnSet(S):

return { s | s in S and

not exists s' in S - {s}: inferior(getSoln(s), getNesting(s),

getSoln(s'), getNesting(s')) }

```

FIGURE 2.5. The loop fusion algorithm.

For a leaf node in the expression tree, minMemFusionSet calls makeLeafSoln to construct an individual solution and returns a set with a single solution tree Leaf node containing this solution. For an Array node or a Const node, makeLeafSoln constructs a single solution with maximal fusion  $\langle * \rangle$  and cost zero indicating that the node can be fused with any index of the parent. For a Fun node, makeLeafSoln constructs a solution with a maximal fusion that indicates that all indices of the node can be fused in any

```

makeLeafSoln(t):

if t is an Array node or a Const node then

return { S(any, 0, t) }

else if t is a Fun node then

return { S([fusible(t)], 1, t) }

makeUnarySoln(S(f, c, l), h, t):

return { S(h, c + 1, t) }

makeBinarySoln(S(f, c, l), h, S(f', c', r), h', t):

f'' = mergeNesting(h, h')

return { S(f'', c + c' + 1, t) }

extendSoln(S(f, c, t), f'):

return { S(f', c - fusedSize(t, f) + fusedSize(t, f'), t) }

reduceSoln(S(f, c, t), i):

f' = maxPrefix(f, i)

return { S(f', c - fusedSize(t, f) + fusedSize(t, f'), t) }

inferior(S(f, c, t), h, S(f', c', t'), h'):

return c \ge c' and leq(h, h')

```

FIGURE 2.6. The cost model for static memory allocation.

order. With all indices fused, only a scalar is needed to hold the result, which is represented as cost one. (For simplicity, we count array elements instead of bytes.)

For a BinOp node and a Sum node, minMemFusionSet first recursively constructs the sets of solutions for the subtrees, extends these solutions to the indices of the parent, and then constructs solutions for the parent. In both cases, it is necessary to enumerate all possible ways in which the loop structures for the subtrees can be embedded within a loop structure for the parent. This is achieved by the functions extendSolnSet and extendSoln'. A boolean parameter is passed along as context to these functions to indicate whether the parent is a unary or a binary node for use in reducing the search space.

While the maximal fusion in a subtree solution results in the largest memory reduction for the root of the subtree under the fusion constraints from that subtree, it may put too many constraints on fusion choices higher up the tree or for the second subtree of a binary node. Fusing only some of the loops included in the maximal fusion would increase the memory requirements for the root of that subtree but may result in a larger memory reduction in a sibling or in an ancestor node. The function <code>extendSoln'</code> constructs partial solutions for the parent out of a single solution for the subtree by enumerating all the prefixes of the maximal fusion becomes an actual fusion between the child and the parent. The cost for an extended solution is calculated in <code>extendSoln</code> (in Figure 2.6); the fused size of the child node under the maximal fusion is subtracted from the cost of the subtree and the cost under the actual fusion is added in. If the actual fusion is

not identical to the maximal fusion, this will result in an increase of the cost. The extended solution and the extended nesting for the parent are then recorded in an Extended solution tree node.

If the maximal fusion of a subtree does not limit the fusion choices elsewhere in the tree, it is not necessary to enumerate all its prefixes. For a binary node, this is the case if the child has all the indices of the parent and the maximal fusion fuses all indices without constraints on the loop order. The child can be fully fused with the binary node without effecting other fusion choices. For a unary node, the enumeration of prefixes can similarly be skipped if all indices are fused. However, this is the case even if there are constraints on the loop order. In this case, fully fusing the child with the unary node will prune out some fusion choices between the unary node and its parent, but those would have resulted in higher memory usage. If the generation of extended solutions can be skipped, extendSoln' simply returns the singleton set containing the subtree solution.

If there is a single solution with fusion  $\langle * \rangle$  for the subtree, the function extendSoln constructs an extended nesting that allows all the indices of the parent to be permuted in any order. Otherwise, extendSoln calls extendSoln' for every solutions of the subtree and returns the union of the resulting sets of extended solutions. Inferior solutions are then pruned out by calling pruneSolnSet.

For a BinOp node, minMemFusionSet calls makeBinarySolnSet on the two sets of extended solutions for the subtrees, which then calls makeBinarySoln on all pairs of solutions in the cross product of these two sets. In makeBinarySoln, the extended nestings from the two subtrees are merged to form a nesting for the BinOp node. If this merge is successful, a solution is constructed with the merged nesting as the maximal fusion. The memory requirement assuming full fusion with the parent is simply the sum of the costs of the subtrees plus one. In makeBinarySolnSet, Binary solution tree nodes are constructed for all pairs of subtree solutions for which the merge was successful, and inferior solutions are pruned from the resulting set.