# Louisiana State University LSU Digital Commons

LSU Doctoral Dissertations

Graduate School

2011

# Phase Noise in CMOS Phase-Locked Loop Circuits

Yang Liu

Louisiana State University and Agricultural and Mechanical College, ericliu1983@gmail.com

Follow this and additional works at: https://digitalcommons.lsu.edu/gradschool\_dissertations

Part of the <u>Electrical and Computer Engineering Commons</u>

#### Recommended Citation

Liu, Yang, "Phase Noise in CMOS Phase-Locked Loop Circuits" (2011). LSU Doctoral Dissertations. 720. https://digitalcommons.lsu.edu/gradschool\_dissertations/720

This Dissertation is brought to you for free and open access by the Graduate School at LSU Digital Commons. It has been accepted for inclusion in LSU Doctoral Dissertations by an authorized graduate school editor of LSU Digital Commons. For more information, please contactgradetd@lsu.edu.

#### PHASE NOISE IN CMOS PHASE-LOCKED LOOP CIRCUITS

#### A Dissertation

Submitted to the Graduate Faculty of the Louisiana State University and Agricultural and Mechanical College in Partial Fullfillment of the Requirements for the Degree of Doctor of Philosophy

in

The Department of Electrical and Computer Engineering

by

Yang Liu

B.S., Beijing Institute of Technology, Beijing, China. 2006

M.S., Louisiana State University, Baton Rouge, U.S.A. 2010

December 2011

#### **ACKNOWLEDGEMENTS**

I would like to dedicate my work to my parents, Mr. Songshan Liu and Mrs. Guizhi Wang, for their constant encouragement throughout my life.

I am very thankful to my advisor Dr. Ashok Srivastava for his guidance, patience and understanding throughout my stay at LSU. I cannot finish this work without his suggestions, discussions and constant encouragement.

I would like to thank Dr. Theda Daniels-Race, Dr. Guoxiang Gu, Dr. Hsiao-Chun Wu, Dr. Marcio de Queiroz, for being a part of my committee.

I am very thankful to Electrical and Computer Engineering Department of Louisiana State University for the Teaching Assistantship, for supporting me financially during my stay at LSU. Partial support under NSF ECS-0426644 grant is also acknowledged.

I take this opportunity to thank my friends, Chi, Chunbo, Rajiv, Yao, Jose and Siva, for their support, help and encouragement. I would also like to thank all my friends here who made my stay at LSU an enjoyable and a memorable one.

Last of all, I would like to thank everyone and everything in my life.

### TABLE OF CONTENTS

| ACKNOWLED      | GEMENTSGEMENTS                                                        | ii                 |

|----------------|-----------------------------------------------------------------------|--------------------|

| LIST OF TABL   | ES                                                                    | iv                 |

| LIST OF FIGURE | RES                                                                   | vi                 |

| ABSTRACT       |                                                                       | x                  |

|                | TRODUCTION                                                            |                    |

| 1.1 PHA        | SE-LOCKED LOOP COMPONENTS                                             | 2 -                |

| 1.1.1 P        | Phase/Frequency Detector (PFD)                                        | 3 -                |

| 1.1.2          | Charge Pump (CP) and Loop Filter                                      | 7 -                |

| 1.1.3 V        | Voltage-Controlled Oscillator                                         | 7 -                |

| 1.2 PHA        | SE NOISE AND TIME JITTER                                              | 10 -               |

| 1.2.1 P        | hase Noise                                                            | 10 -               |

| 1.2.2 T        | ime Jitter                                                            | 12 -               |

| 1.3 Нот        | CARRIER EFFECT (HCE) AND NEGATIVE BIAS TEMPERATURE INSTABILITY (NBTI) | 14 -               |

|                | Iot Carrier Effect (HCE)                                              |                    |

|                | Negative Bias Temperature Instability (NBTI)                          |                    |

|                | ALS AND OBJECTIVES                                                    |                    |

|                |                                                                       |                    |

| CHAPTER 2 PH   | HASE NOISE AND JITTER STUDY IN CMOS VOLTAGE-CONTROLLED                |                    |

|                | (VCO) CONSIDERING HOT CARRIER EFFECTS                                 | 22 -               |

|                | se Noise in PLL                                                       |                    |

|                | Phase Noise Modeling of Differential VCO                              |                    |

|                | Phase Noise Modeling of Input Reference Clock                         |                    |

|                | Phase Noise Modeling of the Divider                                   |                    |

|                | Phase Noise Modeling of PFD/CP                                        |                    |

|                | Phase Noise Modeling of Loop Filter                                   |                    |

|                | CARRIER EFFECT (HCE) AND NEGATIVE BIAS TEMPERATURE INSTABILITY (NBTI) |                    |

|                | ICE and NBTI Models for Single-ended VCO                              |                    |

|                | ICE Models for Differential VCO                                       |                    |

|                | ERIMENTAL STUDY                                                       |                    |

|                | ASUREMENT SETUP AND RESULTS                                           |                    |

|                | ICLUSION                                                              |                    |

| 2.3 CON        | CLUSION                                                               | 47 -               |

| CHAPTER 3 PH   | HASE NOISE AND JITTER STUDY IN CMOS SWITCHABLE PHASE-LOCKED           | LOOP               |

| CONSIDERING    | G HOT CARRIER EFFECTS                                                 | 52 -               |

| 3.1 The        | SWITCHES                                                              | 53 -               |

| 3.2 ANA        | ALYSIS                                                                | 55 -               |

| 3.3 SIM        | ULATION RESULTS                                                       | 61 -               |

| 3.4 EXP        | ERIMENTAL RESULTS                                                     | 64 -               |

| 3.5 CON        | CLUSION                                                               | 70 -               |

| СН Д РТЕР Л Ц  | OT CARRIER AND NEGATIVE BIAS TEMPERATURE INSTABILITY STUDIE:          | S ON               |

|                | PHASE-LOCKED LOOP WITH LC VCO AND DUAL-MODULUS PRESCALER.             |                    |

|                | IGNS OF PHASED-LOCK LOOP CIRCUITS                                     |                    |

|                | ITAL DESIGN OF FREQUENCY SYNTHESIZER                                  |                    |

|                | CARRIER STRESS AND NBTI EFFECTS ON LC VCO                             |                    |

|                | Hot Carrier Stress on Varactor and LC VCO                             |                    |

|                | VBTI Effects on LC VCO                                                |                    |

|                | POST LAYOUT SIMULATIONS AND RESULTS                                   |                    |

|                | POST LAYOUT SIMULATIONS AND RESULTS                                   |                    |

|                |                                                                       |                    |

| 4.6 CON        | ICLUSION                                                              | 94 -               |

| OH ABEER 5     | A FOR LOW DE THE CONTROLLED COOK LATER AND THE PROPERTY OF THE        | •                  |

|                | MOS LC VOLTAGE-CONTROLLED OSCILLATOR AND PLL DESIGNS USING            |                    |

|                | ED CARBON NANOTUBE WIRE INDUCTOR                                      | - 102 -<br>- 103 - |

| 5.1 ON-        | CHIP INDUCTOR MODELING                                                | _ 1114 -           |

| 5.2.      | LC VOLTAGE-CONTROLLED OSCILLATOR (LC VCO)                            | 107 - |

|-----------|----------------------------------------------------------------------|-------|

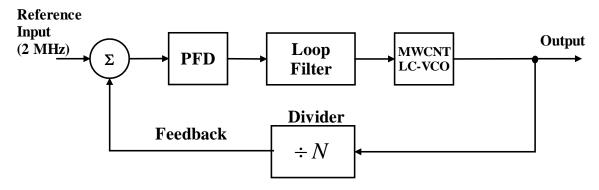

|           | PLL PHASE NOISE WITH MWCNT LC VCO                                    |       |

| CHAPTER   | 6 SUMMARY AND SCOPE FOR FUTURE WORK                                  | 116 - |

| 6.1.      | SUPERPOSITION METHOD AND EXPERIMENTAL STUDY OF PHASE NOISE IN PLL    |       |

| 6.2.      | PHASE NOISE IN VCO AND PLL AND HOT CARRIER EFFECTS                   |       |

|           | SWITCHABLE PLL AND HOT CARRIER EFFECTS                               |       |

|           | LOW POWER PHASE-LOCKED LOOP WITH LC VCO AND DUAL-MODULUS PRESCALER I |       |

| HOT CARRI | ER AND NBTI EFFECTS                                                  | 117 - |

| 6.5.      | SCOPE FOR THE FUTURE WORK                                            | 118 - |

| REFEREN   | CES                                                                  | 119 - |

| APPENDE   | X A MOSIS MOS MODEL PARAMETERS FOR STANDARD N-WELL CMOS              |       |

|           | OGY                                                                  | 127 - |

| APPENDE   | X B LIST OF AUTHOR'S PUBLICATIONS                                    | 131 - |

| APPENDE   | X C PERMISSION TO USE COPYRIGHTED MATERIALS                          | 132 - |

| VITA      |                                                                      | 134 - |

## LIST OF TABLES

| Table 3.1. Experimental results for different output frequencies of the PLL | .69 |

|-----------------------------------------------------------------------------|-----|

| Table 4.1 (a) Programmable shift register with CNT high.                    | .86 |

| Table 4.1 (b) Programmable shift register with CNT low                      | .86 |

| Table 4.2 (a) Binary 14-bit programmable references counter data setting    | .87 |

| Table 4.2 (b) Binary 11-bit programmable counter data setting               | .87 |

| Table 4.2 (c) Binary 7-bit swallow counter data setting                     | .87 |

## LIST OF FIGURES

| Figure 1.1: A block diagram of PLL4 -                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------|

| Figure 1.2: D Flip-Flop circuit diagram of a phase/frequency detector (PFD) 5 -                                                             |

| Figure 1.3: A phase/frequency detector (PFD).                                                                                               |

| Figure 1.4: PFD outputs with (a) same frequency inputs and (b) different frequency inputs 6                                                 |

| Figure 1.5: A passive loop filter following the charge pump. ————————————————————————————————————                                           |

| Figure 1.6: A current starved VCO circuit diagram. — 9 -                                                                                    |

| Figure 1.7: Circuit diagram of a differential ring oscillator. ————————————————————————————————————                                         |

| Figure 1.8: Oscillator power spectrum with phase noise at an offset frequency $\Delta f$ 13                                                 |

| Figure 1.9: Clock jitter increases with the measurement interval, $\Delta T$ 15                                                             |

| Figure 1.10: A physical model for interface-traps generation of hot carrier injection 17 -                                                  |

| Figure 1.11: A physical model for Secondary generated hot carrier injection (HCI) 17                                                        |

| Figure 1.12: A physical model for interface-traps generation of NBTI 19                                                                     |

| Figure 2.1: A phase domain block diagram of PLL. ——————————————————————————————————                                                         |

| Figure 2.2: Equivalent frequency domain model of a PLL with injected noise sources 27 -                                                     |

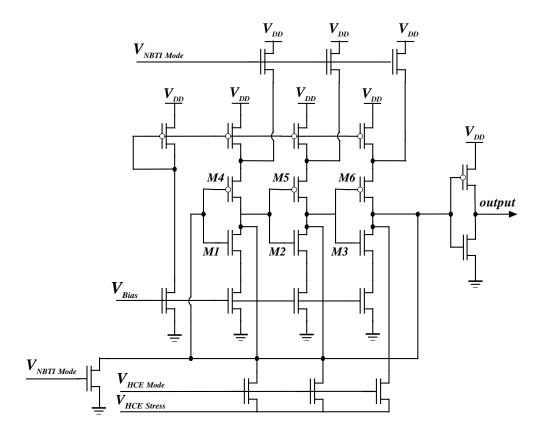

| Figure 2.3: The single-ended current starved VCO with HCE and NBTI modes 31 -                                                               |

| Figure 2.4: Differential VCO with hot carrier stress mode. ————————————————————————————————————                                             |

| Figure 2.5: Block diagram of loop filter with PFD 37 -                                                                                      |

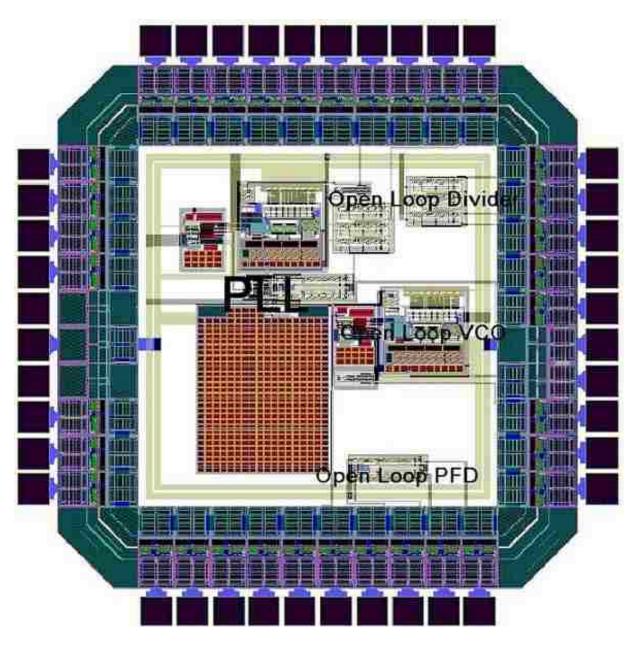

| Figure 2.6: PLL chip layout.                                                                                                                |

| Figure 2.7: Photograph of RF test board with mounted PLL chip. ————————————————————————————————————                                         |

| Figure 2.8: The tuning characteristics of differential VCO                                                                                  |

| Figure 2.9: Experimental results of VCO phase noise at 80 MHz PLL output frequency 42 -                                                     |

| Figure 2.10: Experimental results of input reference clock phase noise at 80 MHz PLL output frequency. ———————————————————————————————————— |

| Figure 2.11: Experimental results of divider phase noise at 80 MHz PLL frequency 45 -                                                       |

| Figure 2.12: Experimental results of PFD/CP phase noise at 80 MHz PLL frequency                                                    | 46 - |

|------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2.13: Experimental results of loop filter phase noise at 80 MHz PLL frequency                                               | 47 - |

| Figure 2.14: Closed-loop PLL output noise performance compared to the closed-loop noise performances of the individual components. |      |

| Figure 2.15: Calculated and measured PLL phase noises.                                                                             | 51 - |

| Figure 3.1: Building blocks of a switchable PLL architecture.                                                                      | 54 - |

| Figure 3.2: Frequency detector architecture.                                                                                       | 56 - |

| Figure 3.3: Switchable PLL outputs at different frequencies.                                                                       | 57 - |

| Figure 3.4: Hot carrier effects on frequency synthesizer.                                                                          | 58 - |

| Figure 3.5: The NBTI degradation of switchable PLL tuning frequency range                                                          | 59 - |

| Figure 3.6: Frequency detector output.                                                                                             | 60 - |

| Figure 3.7: Frequency detector stabilizing time versus frequency.                                                                  | 62 - |

| Figure 3.8: The degradation of VCO frequency due to hot carrier effects.                                                           | 63 - |

| Figure 3.9: VCO gain versus stress time for H_PLL for H_PLL.                                                                       | 65 - |

| Figure 3.10: The dependence of $\kappa$ and VCO frequency due to hot carrier effects                                               | 66 - |

| Figure 3.11: Degradation on phase noise performance under 1 GHz frequency                                                          | 67 - |

| Figure 3.12: Experimental results of PLL jitter.                                                                                   | 68 - |

| Figure 3.13: A photograph of PLL jitter.                                                                                           | 71 - |

| Figure 3.14: Experimental results of PLL phase noise at 700MHz carrier frequency                                                   | 72 - |

| Figure 3.15: Layout of switchable PLL frequency synthesizer.                                                                       | 73 - |

| Figure 3.16: Microphotograph of fabricated switchable PLL.                                                                         | 74 - |

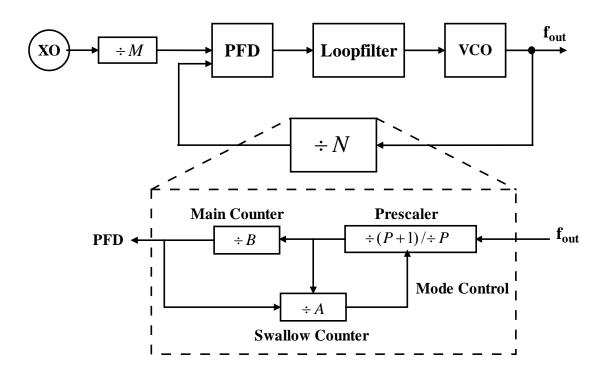

| Figure 4.1: Programmable PLL building blocks.                                                                                      | 77 - |

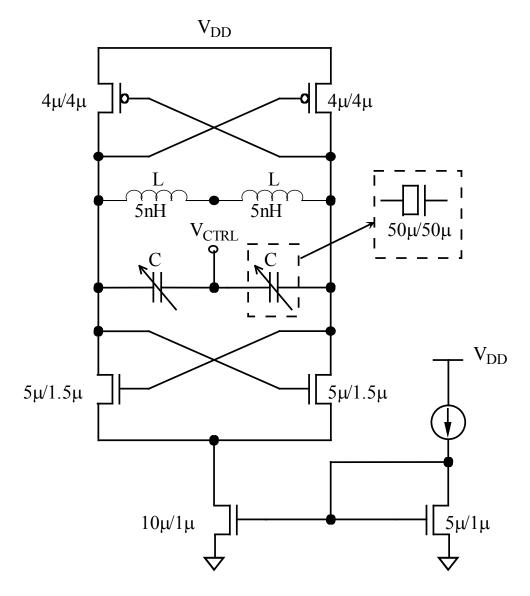

| Figure 4.2: LC VCO Design.                                                                                                         | 78 - |

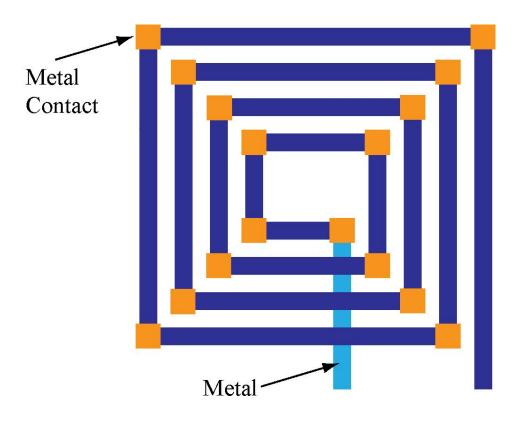

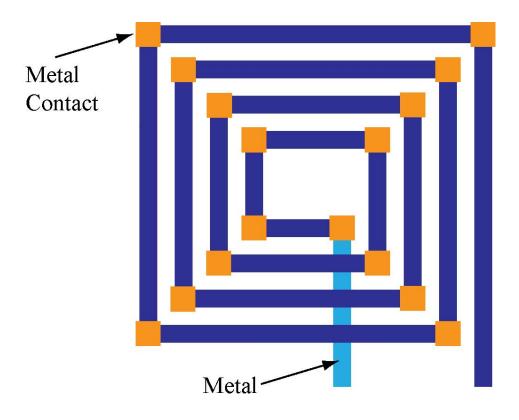

| Figure 4.3: Layout of on-chip integrated square spiral inductor design.                                                            | 79 - |

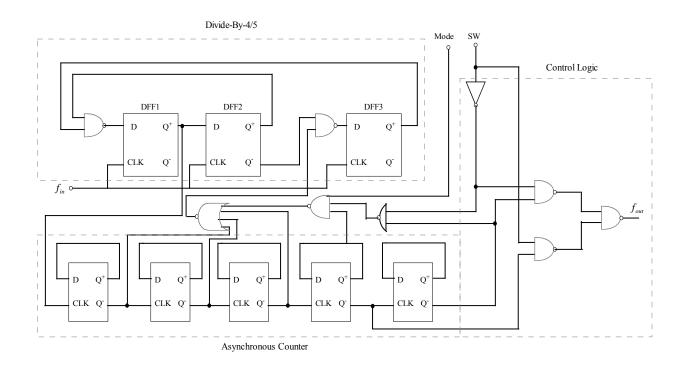

| Figure 4.4: Schematic of the dual-modulus prescaler                                    | - 80 - |

|----------------------------------------------------------------------------------------|--------|

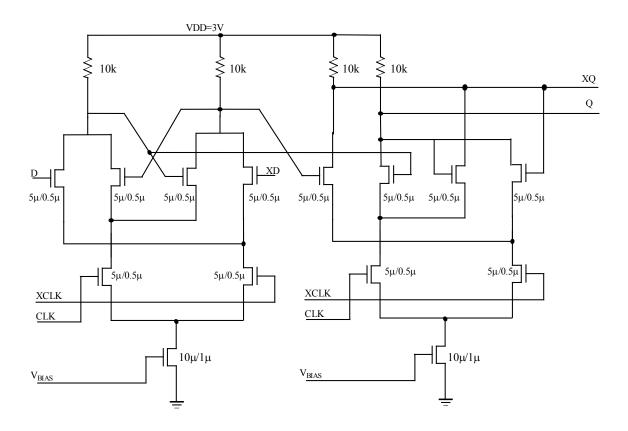

| Figure 4.5:CML D flip-flop schematic. All transistors are n-MOSFETs.                   | 82 -   |

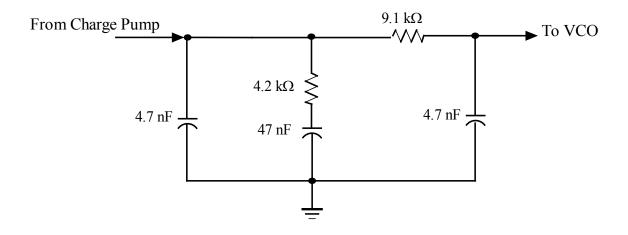

| Figure 4.6: Loop filter circuit schematic.                                             | 83 -   |

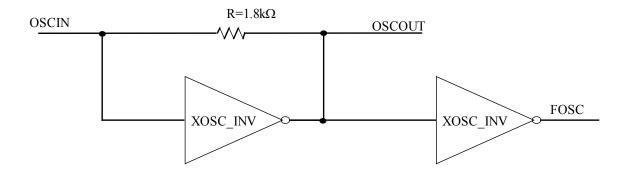

| Figure 4.7: Crystal oscillator circuit.                                                | 84 -   |

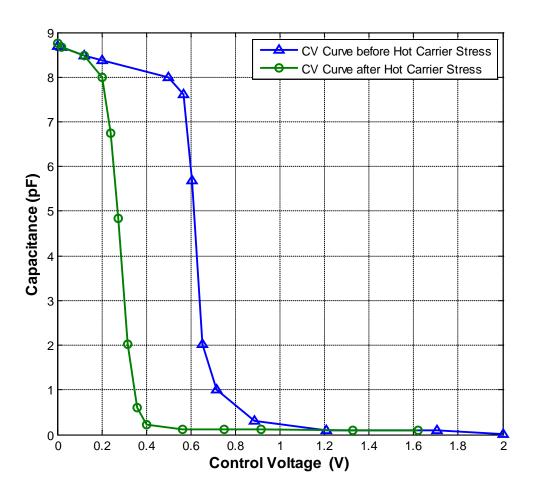

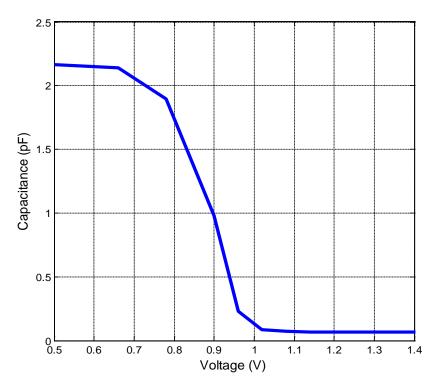

| Figure 4.8: The CV curve of the n-MOSFET varactor with and without hot carrier effect. | - 89 - |

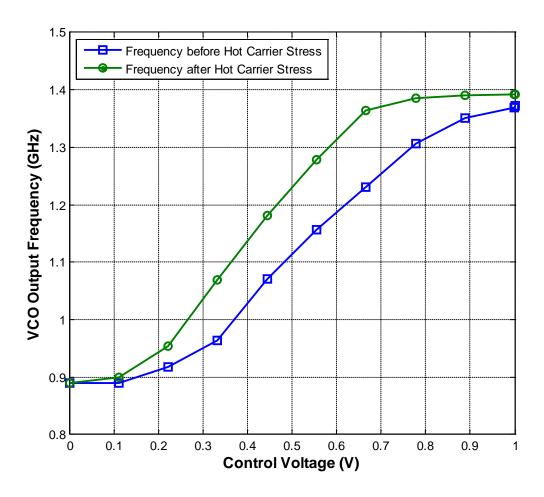

| Figure 4.9: LC VCO frequency with and without hot carrier stress.                      | 90 -   |

| Figure 4.10: LC VCO phase noise with and without hot carrier stress.                   | 91 -   |

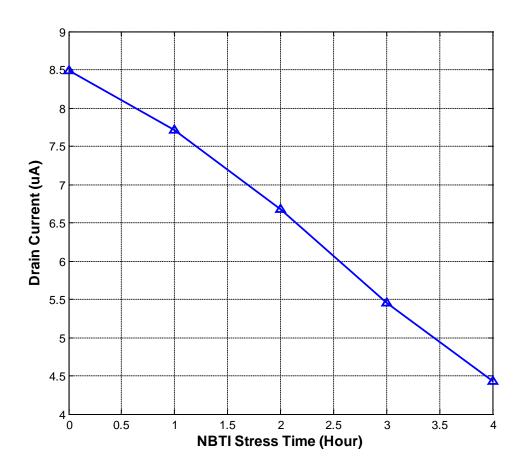

| Figure 4.11: Drain current versus stress time.                                         | 95 -   |

| Figure 4.12: LC VCO phase noise with and without NBTI stress.                          | 96 -   |

| Figure 4.13: Layout of the PLL frequency synthesizer.                                  | 97 -   |

| Figure 4.14: PLL frequency synthesizer differential output clocks.                     | 98 -   |

| Figure 4.15: The spectrum measurement setup.                                           | 99 -   |

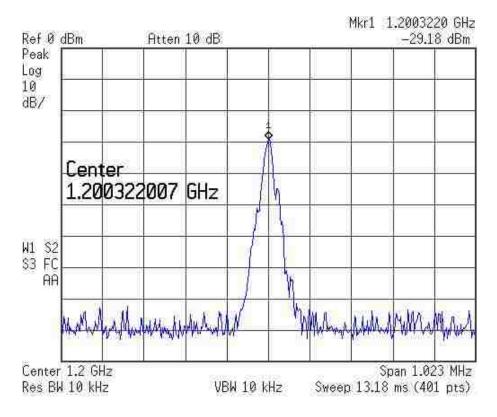

| Figure 4.16 (a): Power spectrum density measurement without hot carrier effect         | 100 -  |

| Figure 4.16 (b): Power spectrum density measurement with hot carrier effect            | 100 -  |

| Figure 4.17 (a): PLL output phase noise without NBTI.                                  | 101 -  |

| Figure 4.17 (b): PLL output phase noise with NBTI.                                     | 101 -  |

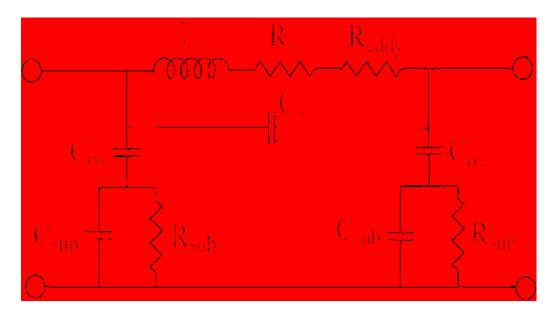

| Figure 5.1: $\pi$ -model of on-chip inductor.                                          | 104 -  |

| Figure 5.2: Layout of on-chip integrated square spiral inductor design.                | 105 -  |

| Figure 5.3. Q-factor of inductors based on MWCNT and Cu.                               | 106 -  |

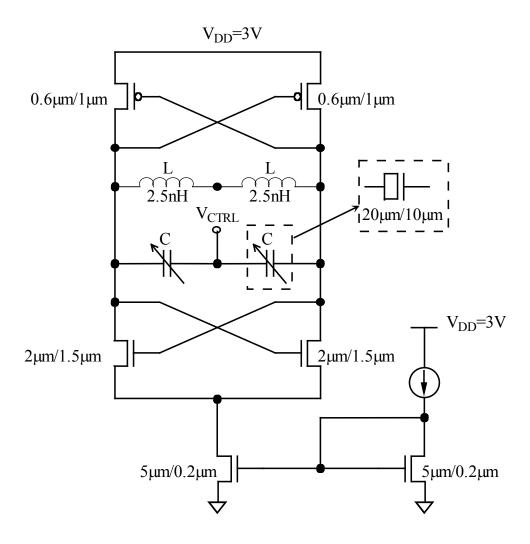

| Figure 5.4. Circuit diagram of a LC VCO.                                               | 108 -  |

| Figure 5.5. C-V curve of a varactor.                                                   | 109 -  |

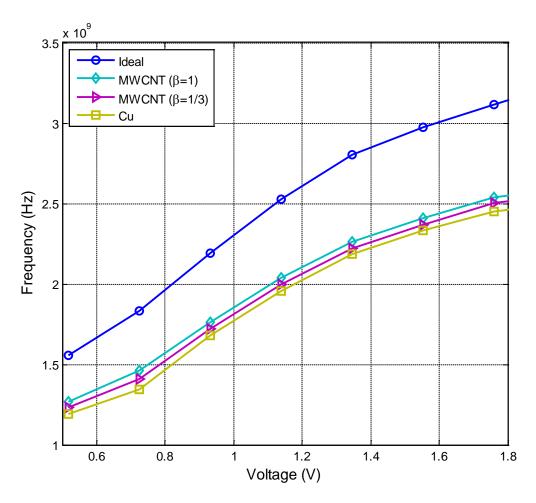

| Figure 5.6. VCO oscillation frequency versus control voltage with different inductors  | 111 -  |

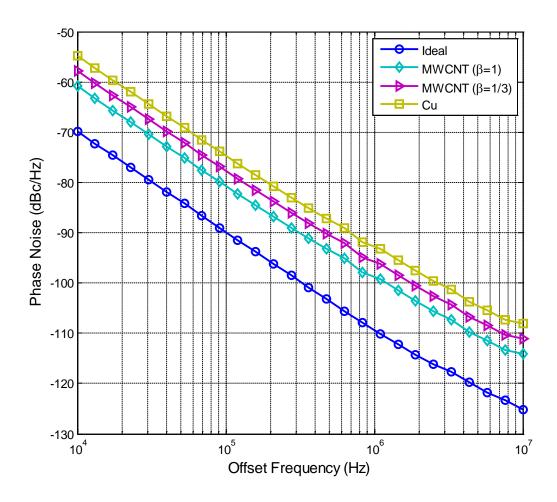

| Figure 5.7. VCO phase noise versus offset frequency.                                   | 112 -  |

| Figure 5.8: Block diagram of a PLL block diagram with MWCNT LC VCO | - 114 |

|--------------------------------------------------------------------|-------|

| Figure 5.9. PLL output phase noise versus offset frequency.        | - 115 |

#### **ABSTRACT**

Phase-locked loops (PLLs) have been widely used in mixed-signal integrated circuits. With the continuously increasing demand of market for high speed, low noise devices, PLLs are playing a more important role in communications. In this dissertation, phase noise and jitter performances are investigated in different types of PLL designs. Hot carrier and negative bias temperature instability effects are analyzed from simulations and experiments.

Phase noise of a CMOS phase-locked loop as a frequency synthesizer circuit is modeled from the superposition of noises from its building blocks: voltage-controlled oscillator, frequency divider, phase-frequency detector, loop filter and auxiliary input reference clock. A linear time invariant model with additive noise sources in frequency domain is presented to analyze the phase noise. The modeled phase noise results are compared with the corresponding experimentally measured results on phase-locked loop chips fabricated in 0.5 µm n-well CMOS process.

With the scaling of CMOS technology and the increase of electrical field, MOS transistors have become very sensitive to hot carrier effect (HCE) and negative bias temperature instability (NBTI). These two reliability issues pose challenges to designers for designing of chips in deep submicron CMOS technologies. A new strategy of switchable CMOS phase-locked loop frequency synthesizer is proposed to increase its tuning range. The switchable PLL which integrates two phase-locked loops with different tuning frequencies are designed and fabricated in 0.5 µm CMOS process to analyze the effects under HCE and NBTI.

A 3V 1.2 GHz programmable phase-locked loop frequency synthesizer is designed in 0.5  $\mu$ m CMOS technology. The frequency synthesizer is implemented using LC voltage-controlled oscillator (VCO) and a low power dual-modulus prescaler. The LC

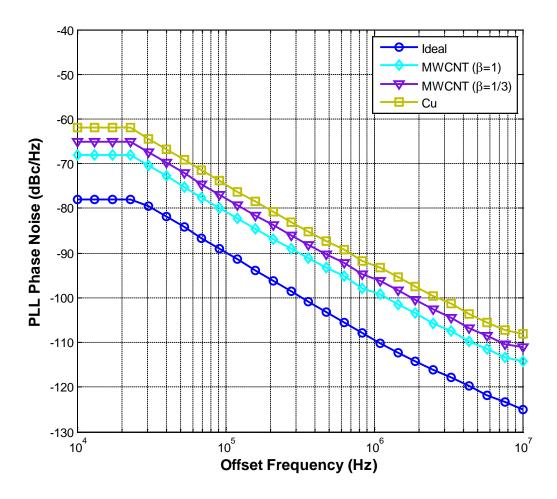

VCO working range is from 900MHz to 1.4GHz. Current mode logic (CML) is used in designing high speed D flip-flop in the dual-modulus prescaler circuits for low power consumption. The power consumption of the PLL chip is under 30mW. Fully differential LC VCO is used to provide high oscillation frequency. A new design of LC VCO using carbon nanotube (CNT) wire inductor has been proposed. The PLL design using CNT-LC VCO shows significant improvement in phase noise due to high-Q LC circuit.

#### **CHAPTER 1**

#### INTRODUCTION

Phase-locked loops (PLLs) have been widely used in high speed data communication systems. The design, underlying principles of operation, and applications irrespective of advances in technology are described in numerous publications and text books [1-4]. The PLL technique was first proposed as a practical synchronization of oscillators by Appleton [5] in 1923 and a French Scientist de Bellescise [6] in 1932. Based on the initial work, Travis [7] in 1935 addressed reasons to control the oscillation frequency of a receiver. In 1939, Rideout proposed an automatic servo system with frequency control circuits [8]. Meanwhile, the feedback control theory of the frequency synchronizing circuits was presented by Oliver [9], the analysis was achieved by Nyquist diagrams and Bode plot in control theory. Until 1970's, PLL used for frequency synthesis became available as a single chip in CMOS and other technologies advanced [10].

There are several technologies making the PLL IC chip, such as bipolar junction transistor (BJT), gallium arsenide (GaAs), bipolar CMOS (BiCMOS) and complementary metal-oxide semiconductor (CMOS) [11-15]. Now a days, the CMOS PLL circuits are widely used in digital and analog circuits in applications such as the cellular phones, microprocessors, RF front-end circuits and system-on-chip (SOC) implementations because of better performance on low power and low noise. Commercial communication systems have a rapid growth over the past decade. Most commercial communication systems operate at appropriate frequency references. A PLL frequency synthesizer, which is used to synthesize these frequency references, is able to track the phase and frequency of the system clock and to achieve a certain bandwidth with low phase noise performance. Other criteria such as the lock-in time, phase error and power consumption are also considered in a PLL design. CMOS based PLL systems are designed, analyzed

and reported in [16-23]. PLL applications as clock synthesizer in microprocessor are reported in [16-19] and PLLs in wireless transceivers are reported in [20-23].

In short channel MOS devices, the channel length is comparable with the depletion widths of the drain and source junctions. If the channel length is decreased and becomes comparable to the depletion widths, some key parameters will change. The long channel MOS transistor physics cannot be used for short channel devices [24]. Such issues include hot carrier effect (HCE) and negative bias temperature instability (NBTI). Hot carrier effect was first proposed as a reliability issue by Hu [25] and Ning *et al.* [26] in 1979. Hu [25] used the breaking bonds of SiO<sub>2</sub> model to physically elaborate the hot carrier effect; Ning *et al.* [26] detected the hot carrier phenomenon and analyzed hot carrier effect on a clock generator circuit under 1 μm CMOS technology. CMOS circuits' degradation by HCE was further studied and investigated by Wang [27] in 1992 and Yang [28] in 2003.

The work in this thesis is mainly focused on the studies of phase noise and jitter performances in the PLL and one of its key building blocks, the VCO. In submicron CMOS devices, the performance of integrated circuits is influenced by the hot carrier effect and negative bias temperature instability (NBTI) due to increased lateral channel electric field and results in performance degradation. Thus, jitter and phase noise may also be affected.

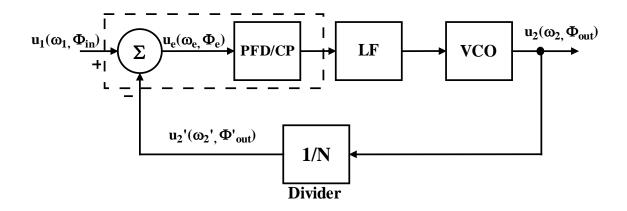

## 1.1 Phase-Locked Loop Components

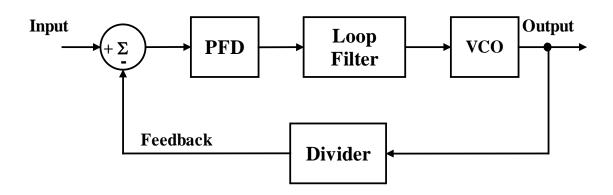

The block diagram of a typical PLL is shown in Figure 1.1. There are five basic components in a PLL: phase/frequency detector (PFD), charge pump (CP), loop filter (LF), voltage-controlled oscillator (VCO) and 1/N frequency divider. The PLL operates as follows: PFD is a circuit block which detects the phase and frequency of the input

signal and compares with the phase and frequency of feedback signal and gives a switch signal to the charge pump. Charge pump is used to charge or discharge the loop filter in order to increase or decrease the control voltage which follows the PFD output. The loop filter eliminates the higher order noise and provides control voltage to VCO circuit when the switch signal is ON. VCO generates an output signal with a specific frequency related to the input signal. The divider divides the frequency of the output signal at a pre-defined fraction N and connects the feedback signal back to the PFD. The PLL is locked when the phase of input reference clock is the same as the phase of the VCO output clock. Detailed information will be provided in the following sections.

#### 1.1.1 Phase/Frequency Detector (PFD)

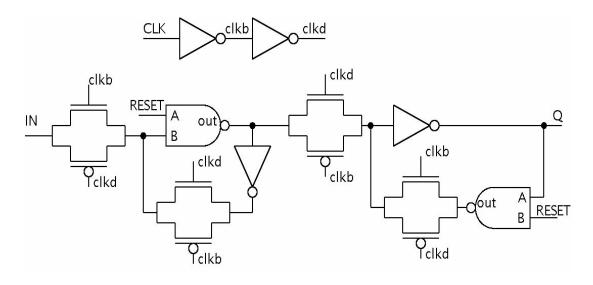

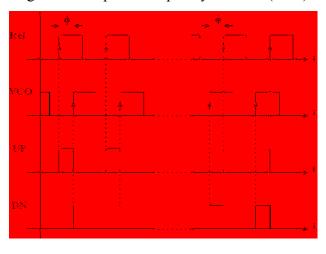

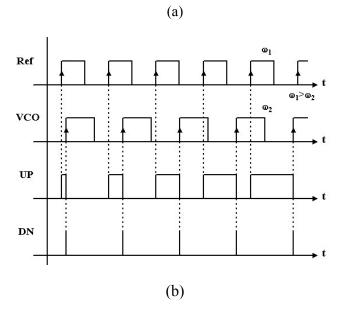

Figure 1.2 shows the design of controllable D-flip-flop. The PFD built by two controllable D flip-flops and a AND gate is shown in Figure 1.3. Figure 1.4 (a) and (b) may help in better understanding the principle how PFD works (assuming divider ratio N=1 for simplicity). Figure 1.4 (a) shows the case when input reference clock has the same frequency but different phase with the VCO output clock. When the input clock rising edge is leading the VCO output clock, the UP signal will turned on and the DN signal only has positive pulses when the rising edges of input reference and VCO output clock overlap. When the input clock is lagging the VCO output clock, the DN signal will turned on and the UP signal will have low level except has positive pulses when the rising edges of VCO output and input reference clock overlap. Figure 1.4 (b) shows the case when input reference clock has different frequency but the same phase with the VCO output clock. The input reference clock is always leading the VCO output clock; therefore the DN is always low level with narrow spurs.

Figure 1.1: A block diagram of PLL.

Figure 1.2: D Flip-Flop circuit diagram of a phase/frequency detector (PFD).

Figure 1.3: A phase/frequency detector (PFD).

Figure 1.4: PFD outputs with (a) same frequency inputs and (b) different frequency inputs.

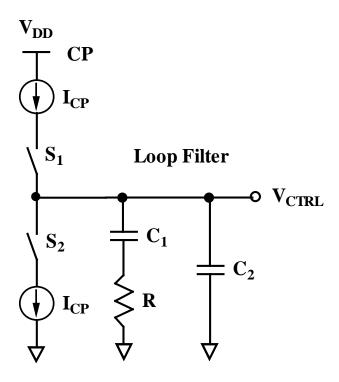

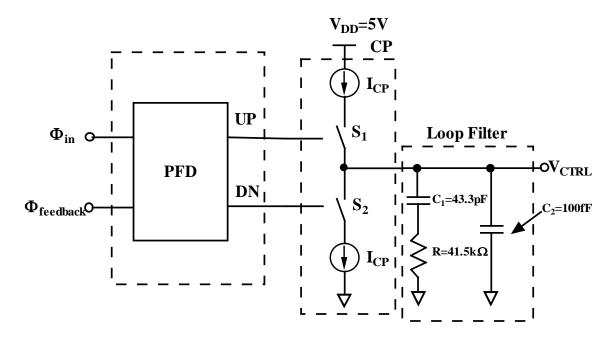

#### 1.1.2 Charge Pump (CP) and Loop Filter

Figure 1.5 shows the equivalent diagram of charge pump and loop filter. When PFD output UP goes high,  $S_1$  will turn on and  $I_{CP}$  will charge the loop filter capacitor,  $C_1$ , which in turn results in an increase of the control voltage.  $C_2$  is used to eliminate higher order noises from the PFD. The control voltage is used to adjust the VCO output frequency. On the other hand, when PFD output DN goes high,  $S_2$  will turn on and charge pump is working in discharging mode. The current flowing into the loop filter will decrease and the control voltage will decrease too.

#### 1.1.3 Voltage-Controlled Oscillator

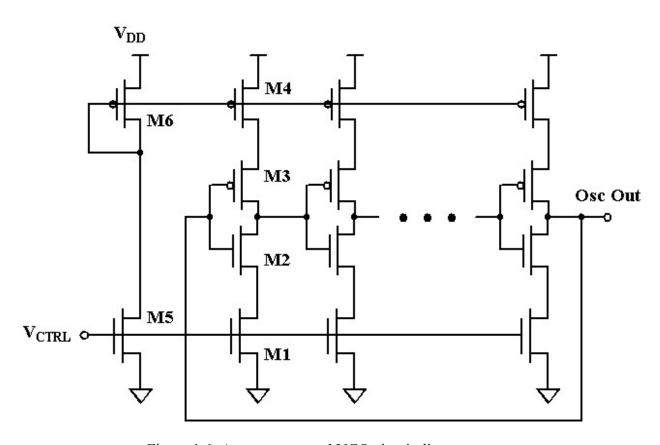

The input of the VCO is usually a control voltage,  $V_{CTRL}$ , which is adjusted by the PFD and charge pump. It generates a clock signal with a certain tuning frequency. Figure 1.6 shows a diagram of single-ended current starved oscillator. M2 and M3 form an inverter, M4 and M6 are operating as a current mirror. M5 limits the current to flow into M6 and is controlled by  $V_{CTRL}$ . This VCO is achieved by charging and discharging the equivalent output capacitors of each stage in the VCO.

The single-ended VCO oscillation frequency is given by [29],

$$f = \frac{1}{\eta N(t_r + t_f)} \tag{1.1}$$

In Eq. (1),  $\eta$  is a constant to describe the relationship between the stage delay and the slope of the waveform. N is the number of stages in an oscillator. Rise and fall times are  $t_r$  and  $t_r$ , respectively.

Figure 1.5: A passive loop filter following the charge pump.

Figure 1.6: A current starved VCO circuit diagram.

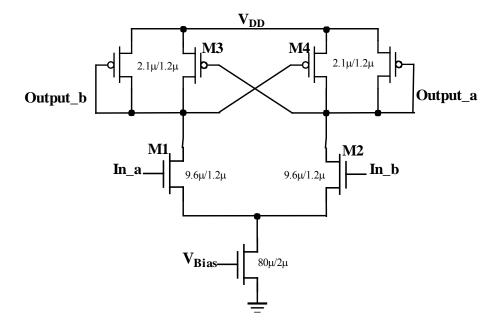

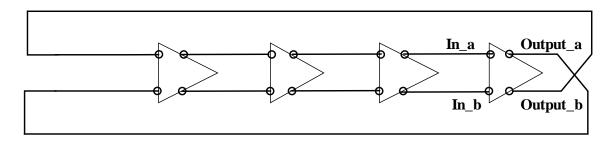

Figure 1.7 shows the circuit diagram of a differential CMOS VCO. When M1 turns off and M2 turns on (In is logic "0" and Inb is logic "1"), M3 will be turned-on and M4 will be turned-off. Thus, Outb is "1" and Out is "0". Since Outb and Out are connected to In and Inb of the next stage, respectively, In and Inb will be logic "1" and "0". The oscillation frequency of differential VCO is  $\frac{1}{2Mt_D}$ , where M is the number of stages and  $t_D$  is the delay of the single stage.

The differential VCO oscillation frequency is given by

$$f = \frac{I_{tail}}{2\eta Nq_{\text{max}}} \tag{1.2}$$

where  $I_{tail}$  is the tail current and  $q_{max}$  is the maximum total charge stored on each node of the oscillator.

There are also other types of VCO, such as LC VCO built by using inductors and varactors and will be described in the later section.

### 1.2 Phase Noise and Time Jitter

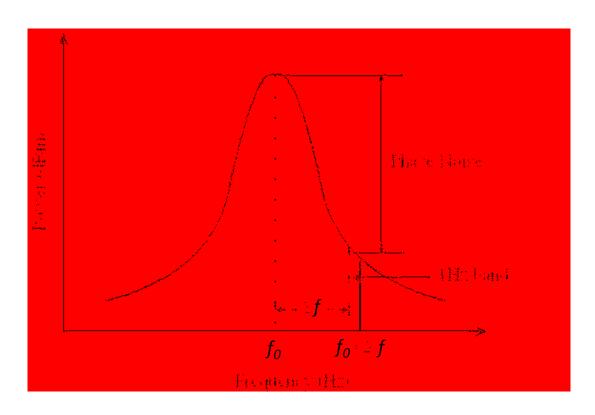

#### 1.2.1 Phase Noise

The output of a PLL is characterized by its output frequency tuning range and its frequency purity. The output of a PLL is a pure sinusoidal waveform and the power spectrum reaches a peak in the desired output frequency or called carrier frequency with no other power spectrum spread on other frequency. However, in reality, the output waveform deviates from the ideal position and the power spectrum reaches a peak at carrier frequency with tails on both sides which is shown in Figure 1.8. This uncertainty is characterized by phase noise in unit of dBc/Hz, which is measured in ratio of the phase

Figure 1.7: Circuit diagram of a differential ring oscillator.

noise power in 1 Hz bandwidth at a certain frequency,  $f_0 + \Delta f$  , offset to center frequency,  $f_0$  .

The expression of phase noise in Figure 1.8 is shown below,

$$L_{total} \{ \Delta f \} = 10 \log \left[ \frac{P_{noise} (f_0 + \Delta f, 1Hz)}{P_{carrier}} \right]$$

(1.3)

where  $P_{noise}(f_0 + \Delta f, 1Hz)$  is the sideband noise power at offset frequency  $\Delta f$  from the carrier frequency  $f_0$  with a measurement bandwidth of 1 Hz.

#### 1.2.2 Time Jitter

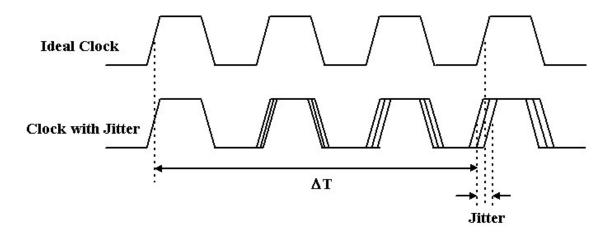

Jitter and phase noise are different ways to express the same phenomenon [30]. Phase noise is the uncertainty of the waveform in the frequency domain and jitter is characterization in time domain of the PLL output. Jitter is the deviation of a waveform transition from its ideal position. There are mainly three types of time jitters [31]:

(1) The cycle jitter is defined as

$$\Delta T_{cn} = T_n - \overline{T} \tag{1.4}$$

where  $T_n$  is the time of the n th cycle of the output waveform.  $\overline{T}$  is the average period.

(2) The cycle-to-cycle jitter is defined as,

$$\Delta T_{ccn} = T_{n+1} - T_n \tag{1.5}$$

(3) The accumulated jitter is defined as,

(4)

$$\Delta T_{acc} = \sum_{n=1}^{N} (T_n - \overline{T})$$

(1.6)

Figure 1.8: Oscillator power spectrum with phase noise at an offset frequency  $\Delta f$  .

where N is the  $N^{\text{th}}$  cycle of the waveform. This accumulated jitter is characterized and increased by time interval,  $\Delta T$ , which is the time difference between the reference and the observed transitions during the measurement, as shown in Fig. 1.9. In jitter measurement, The RMS (root mean-squared) jitter in Eq. (1.6), which is the value of one standard deviation of the normal distribution, is more useful because this value changes not much as the number of samples increases.

# 1.3 Hot Carrier Effect (HCE) and Negative Bias Temperature Instability (NBTI)

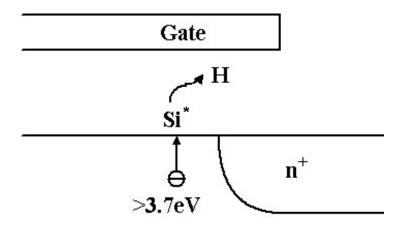

#### **1.3.1** Hot Carrier Effect (HCE)

As device size shrinks and channel electric field increases, interface and oxide traps play important roles affecting the performances of devices and thus the reliability. In CMOS circuits designed in sub-micron/deep-submicron CMOS technologies, HCE and NBTI are well known to be the critical reliability issues.

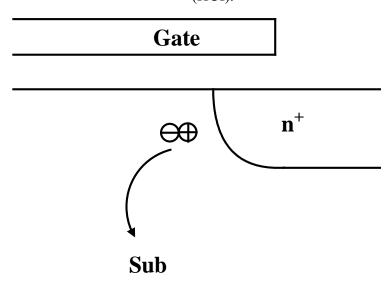

MOSFET degradation due to HCE is caused by the generation of acceptor-type interface traps. The interface traps are located in the channel and the narrow band near the drain. In an n-MOSFET, when the voltage at the drain and gate is large, electrons gain the energy over 3.7 eV [32], the interface traps are generated by breaking siliconhydrogen bonds and electrons diffuse away from the interface. The electrons which the channel are called channel hot electrons. The electrons which diffuse from the drain are called drain avalanche hot electrons. The carrier mobility and density are reduced due to interface traps and threshold voltage increases. This mechanism is shown in Figure 1.10. Threshold voltage and electron mobility are affected by this kind of generation at the drain end of MOSFETs. The interface traps are generated by the breaking of siliconhydrogen bonds  $\equiv Si_sH$ . The  $\equiv Si_sH$  bond is broken by hot electrons. Interstitial

Figure 1.9: Clock jitter increases with the measurement interval,  $\Delta T$ .

hydrogen atom  $H_i$  and trivalent silicon  $S_i^*$  are produced which form interface traps. Following Eq. (1.6) shows this phenomenon.

$$\equiv Si_s H \stackrel{e^-}{\longleftrightarrow} S_i^* + H_i \tag{1.7}$$

Figure 1.11 shows the physical model for the secondary generation hot carrier injection with high electric field; the generated hot carriers can cause secondary impact ionization in the depletion region and diffuse away from channel to substrate [33].

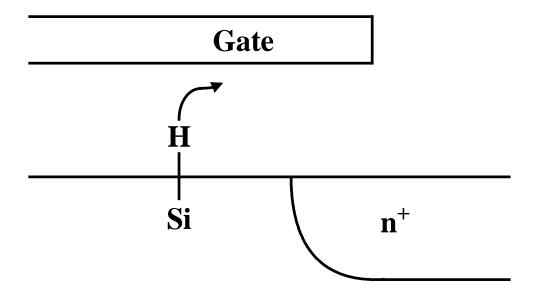

#### **1.3.2** Negative Bias Temperature Instability (NBTI)

NBTI degradation which occurs mainly in p-MOSFETs under the negative gate-source voltage bias, reported in 1966 by Goetzberger and Nigh [34] and results in shift in threshold voltage [35]. The NBTI effect is caused by the decrease of the MOSFET gate oxide thickness [36].

NBTI causes an increase in the threshold voltage, hole mobility, transconductance and drain current in p-MOSFETs. Among various NBTI models, The *Reaction-Diffusion* (R-D) model is the dominant one [37]. This model has two phases. In the reaction phase, NBTI is caused by the creation of SiO<sub>2</sub>/Si interface traps and hydrogen is generated during this mechanism.

where SiH is the silicon-hydrogen bond at  $Si/SiO_2$  interface. In Eq. (1.8),  $e^+$  is the hole traps at the interface and  $Si^+$  is the interface trap.

The generation of interface traps is given by [39],

$$\Delta N_{it}(t) = \frac{2k_F N_0 t}{1 + \sqrt{\frac{1 + 4k_F N_0 k_R t^{3/2}}{0.5\sqrt{D_H}}}}$$

(1.9)

In the diffusion phase, the generated hydrogen diffuses into the substrate. The generation of interface traps is described as follows [38],

Figure 1.10: A physical model for interface-traps generation of hot carrier injection (HCI).

Figure 1.11: A physical model for Secondary generated hot carrier injection (HCI).

$$SiH + e^+ \leftrightarrow Si^+ + H \tag{1.8}$$

where  $k_F$  is the forward reaction rate,  $k_R$  is the reverse reaction rate,  $N_0$  is the initial defect density,  $D_H$  is the hydrogen diffusion coefficient and t is the NBTI stress time. The NBTI effect is shown in Figure 1.12.

Both n- and p-MOSFETS have been extensively characterized under HCE and NBTI and their influences on analog and digital CMOS circuits have also been addressed [40-44]. However, there is no reported work on combined effects of HCE and NBTI on the performance of phase-locked loop circuits. In the present work, an attempt has been made to study combined effects of HCE and NBTI on the performance of the PLL circuits used for communication systems.

### 1.4 Goals and Objectives

In this research, it is proposed to study noise in CMOS phase-locked loop systems and building blocks based on MOS device physics. Earlier work done by Zhang [29] in our research group on explaining phase noise from HCE on VCO will be extended to all building blocks of PLL and include effect of NBTI. The final goal is to develop a comprehensive phase noise model of a PLL. Research of some of the studies conducted is described in following chapters.

Chapter 2 discusses the hot carrier effect on both single-ended VCO and differential VCO. Two VCO circuit designs with hot carrier injection modes are presented. Degradation models on phase noise and jitter degradation on different types of VCOs are illustrated. Both hot carrier and NBTI models of the PLL chip are presented in this chapter. Transistor level single-ended and differential ended types VCO are shown in this chapter.

Figure 1.12: A physical model for interface-traps generation of NBTI.

Chapter 3 extends the noise studies of VCO and PLL discussed in Chapter 2. The circuit diagrams and chip layout of the PLL frequency synthesizer are given. A second-order linear time invariant model with additive noise sources in frequency domain is presented to analyze the phase noise. The modeled phase noise results are compared with the corresponding experimentally measured results on a phase-locked loop chip fabricated in  $0.5~\mu m$  n-well CMOS process.

Chapter 4 discusses a new design of switchable PLL frequency synthesizer with dual phase-locked loops. The circuit design schematics and the chip layout of the switchable PLL frequency synthesizer are proposed and the phase noise and jitter measurement setups are given. Both simulation of measurement results of hot carrier and NBTI effects on tuning frequency range, phase noise and jitter have been investigated.

Chapter 5 discusses a programmable PLL frequency synthesizer. The frequency synthesizer is implemented by LC VCO and a low power dual-modulus prescaler. Current mode logic (CML) technique is used to design high speed D flip-flop in the dual-modulus prescaler circuits. A MOSFET varactor degradation model due to hot carrier effects has been used to analyze oscillation frequency and phase noise performance. NBTI effect is studied to analyze the output voltage swing and phase noise degradations of the LC VCO.

Chapter 6 pr esents a new type of LC VCO where a typical on-chip metallic inductor is replaced by a multi-walled carbon nanotube wire inductor. The oscillation frequency and phase noise performance of CMOS LC VCO based PLL design are studied and the performances using MWCNT based inductor and Cu inductor as a function of quality factor (Q) are compared. The MOS model parameters used in Cadence/Spectre

simulations for 0.5  $\mu$  m and 0.18  $\mu$  m n-well CMOS technologies are summarized in Appendix A. The list of papers published is presented in Appendix B.

#### **CHAPTER 2**

# PHASE NOISE AND JITTER STUDY IN CMOS VOLTAGE-CONTROLLED OSCILLATOR (VCO) CONSIDERING HOT CARRIER EFFECTS\*

Phase-locked loops (PLLs) have been widely used in high speed data communication systems. The design, underlying principles of operation and applications are described in numerous publications and text books [45, 46]. With the increase in operation frequency of systems, jitter or phase noise issue in PLL has become the cause of serious concern in digital communication systems. The noise sources in PLL originate mainly from its building blocks: the voltage-controlled oscillator, frequency divider, phase-frequency detector, loop filter and auxiliary input reference clock. Noise studies for each one of these building blocks have been reported in [47-49]. Hajimiri and his coworkers [47, 48] have studied phase noise and jitter in oscillator circuits. Llopis et al. [49] have studied phase noise in frequency dividers up to microwave frequency range. In another work, Hajimiri [50] presented linear time invariant (LTI) models of VCO and frequency divider building blocks of a PLL. However, noise from other parts of the PLL such as the phase detector is considered to be not a major source of noise.

The noise in PLL has also been investigated in [51-53] due to different building blocks. Kroupa [51] presented a detailed review of all the major sources of additive noises in a PLL. However, no specific technology used in design of low-noise PLL is described. Lagutere et al. [52] have used VHDL-AMS for modeling phase noise in VCO and PLL as

<sup>\*</sup> Part of the work is reported in the following publications:

Y. Liu and A. Srivastava, "Hot carrier effects on CMOS phase-locked loop frequency synthesizers," Proc. International Symposium on Quality Electronic Design (ISQED), pp. 92-98, March. 22-24, 2010

<sup>2.</sup> Y. Liu and A. Srivastava, "Effect of hot carrier injection and negative bias temperature instability on the performance of CMOS phase-locked loops," *Proc. 2010 ASEE-GSW Annual Conference*, Mar. 24-26, 2010.

a whole and compared modeled phase noise with the measured values. However, the modeled noise requires adjustment in parameters to fit the measured results. Mehrotra [53] has presented noise analysis based on non-linear model of a PLL with the divider ratio set as one. Furthermore, the non-linear model is compared with the measured power spectral density (PSD) of PLL from the work of Parker and Ray [54] and agrees closely to the shape rather than values. Recently, Sangha and Hoffmann [55] presented a technique using MATLAB/SIMULINK to analyze the noise behavior of a second-order PLL by injecting noises at the input reference, phase-detector and in the control filter. Their work is focused mainly at the system level and does not relate to actual CMOS circuit level implementation.

Though the phase noise in PLL has been widely studied but is still an open subject for theoretical research as mentioned by Gardener [45]. However, there is not much reported work on the experimental study of total phase noise in PLL contributing from its building blocks at the circuit level. In the present work, an attempt has been made to experimentally measure the phase noise in a second-order PLL designed and fabricated in 0.5 µm n-well CMOS and co-relate with a linear time-invariant close loop transfer function. In Section 2.1, phase noise calculations of different circuit level building blocks are presented and a superposition method is described to calculate the total PLL output phase noise. In Section 2.2, models of hot carrier effect and negative bias temperature instability for VCO are described and studied. An experimental study of phase noise is described in Section 2.3 followed by conclusions in Section 2.4.

#### 2.1 Phase Noise in PLL

To investigate the loop dynamics of a PLL, a block diagram is very useful, which is shown in Figure 2.1.  $\Phi_{in}(s)$  and  $\Phi_{out}(s)$  are the input reference phase and VCO

output phase, respectively.  $\Phi_e(s)$  is the phase error between  $\Phi_{in}(s)$  and  $\Phi'_{out}(s)$  which is the phase of feedback signal from the divider output. A phase/frequency detector and charge pump (CP) are characterized with current gain,  $K_P$ . The gain of PFD is  $K_p = I_{CP}/2\pi$  where  $I_{CP}$  is the current of the charge pump. The loop filter has a transfer function, F(s).

The VCO gain and tuning voltage are defined as  $K_V$  and  $V_{ctrl}$ , respectively. The transfer function of VCO is  $2\pi K_V/s$ . Since frequency is the derivative of phase with respect to time,  $d\Phi_{out}(t)/dt = K_V V_{ctrl}(t)$  or  $\Phi_{out}(s) = V_{ctrl}(s) K_V/s$  in frequency domain.

The characteristics of a second-order PLL can be analyzed by the linear time-invariant (LTI) model. The open loop transfer function of the loop filter in Figure 1.5 is given by,

$$F(s) = \frac{(1 + RC_1 s)}{C_1 s + C_2 s + RC_2 C_1 s^2}$$

(2.1)

Disconnecting the loop between the VCO output and PFD, the PLL open loop transfer function is given by,

$$G(s) = I_{CP} \cdot F(s) \cdot K_{v} / s \tag{2.2}$$

The PLL closed loop transfer function can then be expressed as follows:

$$H(s) = \frac{G(s)}{1 + G(s)/N}$$

(2.3)

In Eq. (2.3), *N* is the divider ratio. There are two poles from the loop filter and one single pole from the VCO in Eq. (2.3) which characterizes the second-order PLL.

Figure 2.1: A phase domain block diagram of PLL.

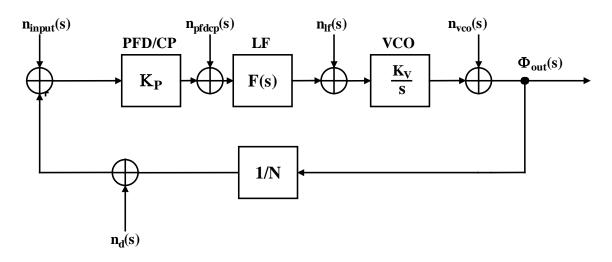

Figure 2.2 shows the equivalent frequency domain model of PLL with injected noise sources. In Fig. 2.2,  $n_{vco}(s)$ ,  $n_{input}(s)$ ,  $n_{d}(s)$ ,  $n_{pfdcp}(s)$  and  $n_{lf}(s)$  are the equivalent

injected noises at the output of VCO, the input, output of divider, output of PFD and output of loop filter, respectively.

### 2.1.1 Phase Noise Modeling of Differential VCO

Assuming a noisy VCO dominated by its white and 1/f noises and no other injected noises, the closed loop transfer function of the VCO phase noise can be calculated using the noise transfer function from  $n_{vco}(s)$  to  $\Phi_{out}(s)$ , which is given by,

$$\frac{\Phi_{out}(s)}{n_{vco}(s)} = \frac{1}{1 + G_{vco}(s)H_{vco}(s)} = \frac{1}{1 + (2\pi K_v/s) \cdot (1/N)K_n F(s)}$$

(2.4)

where  $G_{vco}(s)$  is the open loop transfer function from VCO noise injection,  $n_{vco}(s)$  to VCO output terminal.  $H_{vco}(s)$  is the feedback transfer function from PLL output to  $n_{vco}(s)$ . Therefore, the power spectral density of the output phase noise can be obtained as follows,

$$S_{\Phi outVCO}(\omega) = S_{\Phi inVCO}(\omega) \frac{\left|\Phi_{out}(j\omega)\right|^2}{\left|n_{vco}(j\omega)\right|^2}$$

(2.5)

In Eq. (2.5),  $\omega$  is the offset frequency in rad/s.  $S_{\Phi outVCO}(\omega)$  and  $S_{\Phi inVCO}(\omega)$  are the power spectral density of VCO closed and open loop phase noise, respectively.  $S_{\Phi inVCO}(\omega)$  and  $S_{\Phi outVCO}(\omega)$  in Eq. (2.5) are expressed in  $rad^2/Hz$ . In measurements, it is expressed in dBc/Hz. The PSD measurement with a power meter includes a narrowband bandpass filter. The unit  $rad^2/Hz$  can be converted to a PSD unit dBc/Hz as follows [46],

$$S_{dB}(f) = 10 \log[S_{rad}(f)]$$

(2.6)

In Eq. (2.6),  $S_{dB}(f)$  and  $S_{rad}(f)$  are the power spectral densities of phase noise at anoffset frequency, f in dBc/Hz and  $rad^2/Hz$ , respectively. Both  $S_{dB}(f)$  and  $S_{rad}(f)$

Figure 2.2: Equivalent frequency domain model of a PLL with injected noise sources.

\

define the value of the noise power stored within a bandwidth of 1 Hz below the power of the carrier.

## 2.1.2 Phase Noise Modeling of Input Reference Clock

Assuming a noisy input signal, the response of the loop to the phase variations in the input can be evaluated using a similar method described in Section 2.1.1. For the PLL under consideration, the input noise transfer function is given by,

$$\frac{\Phi_{out}(s)}{n_{input}(s)} = \frac{G_{in}(s)}{1 + G_{in}(s)H_{in}(s)} = \frac{(2\pi K_{v}/s)K_{p}F(s)}{1 + (2\pi K_{v}/s)\cdot(1/N)K_{p}F(s)}$$

(2.7)

where  $G_{in}(s)$  is the open loop transfer function from reference clock noise injection,  $n_{input}(s)$  to PLL output terminal. In Eq. (2.7),  $H_{in}(s)$  is the feedback transfer function from PLL output to  $n_{input}(s)$  in Figure 2.2. The output phase noise power spectrum of input reference phase noise is given by,

$$S_{\Phi outINPUT}(\omega) = S_{\Phi inINPUT}(\omega) \frac{\left|\Phi_{out}(j\omega)\right|^{2}}{\left|n_{input}(j\omega)\right|^{2}}$$

(2.8)

### 2.1.3 Phase Noise Modeling of the Divider

The frequency divider introduces additive noise by white and 1/f noises. The additive noise is injected at the input of the PFD and share the same transfer function as the noise at the input terminal. Similarly, the noise transfer function for divider can be described as follows,

$$\frac{\Phi_{out}(s)}{n_d(s)} = \frac{G_d(s)}{1 + G_d(s)H_d(s)} = \frac{(2\pi K_v/s)K_p F(s)}{1 + (2\pi K_v/s) \cdot (1/N)K_p F(s)}$$

(2.9)

and

$$S_{\Phi outD}(\omega) = S_{\Phi inD}(\omega) \frac{\left|\Phi_{out}(j\omega)\right|^2}{\left|n_d(j\omega)\right|^2}$$

(2.10)

In Eq. (2.9),  $G_d(s)$  is the open loop transfer function from divider noise injection,  $n_d(s)$  to PLL output terminal and  $H_d(s)$  is the feedback transfer function from PLL output to  $n_d(s)$ . In Eq. (2.10),  $S_{\Phi inD}(\omega)$  is the open loop PSD.

## 2.1.4 Phase Noise Modeling of PFD/CP

Noises injected by PFD are 1/f, substrate and supply noises. Similarly, noise model for PFD can be expressed by the following equations,

$$\frac{I_{out}(s)}{n_{pfdep}(s)} = \frac{G_{pfdep}(s)}{1 + G_{pfdep}(s)H_{pfdep}(s)} = \frac{(2\pi K_{v}/s) \cdot F(s)}{1 + (2\pi K_{v}/s) \cdot (1/N)K_{p}F(s)}$$

(2.11)

and

$$S_{\Phi outPFDCP}(\omega) = S_{\Phi inPFDCP}(\omega) \frac{\left|\Phi_{out}(j\omega)\right|^2}{\left|n_{pfdcp}(j\omega)\right|^2}$$

(2.12)

In Eq. (2.11),  $I_{out}$  is the output current of charge pump,  $G_{pfdcp}(s)$  is the open loop transfer function from PFD/CP noise injection,  $n_{pfdcp}(s)$  to PLL output terminal.  $H_{pfdcp}(s)$  is the feedback transfer function from PLL output to  $n_{pfdcp}(s)$  which is shown in Figure 2.2. In Eq. (2.12),  $S_{\Phi inPFDCP}(\omega)$  is the open loop phase noise PSD.

# 2.1.5 Phase Noise Modeling of Loop Filter

Noise model for the loop filter can also be described by the following equations,

$$\frac{V_{out}(s)}{n_{lf}(s)} = \frac{G_{lf}(s)}{1 + G_{lf}(s)H_{lf}(s)} = \frac{(2\pi K_{v}/s)}{1 + (2\pi K_{v}/s) \cdot (1/N)K_{p}F(s)}$$

(2.13)

and

$$S_{\Phi outLF}(\omega) = S_{\Phi inLF}(\omega) \frac{\left|\Phi_{out}(j\omega)\right|^2}{\left|n_{lf}(j\omega)\right|^2}$$

(2.14)

In Eq. (2.13),  $G_{lf}(s)$  is the open loop transfer function from loop filter noise injection,  $n_{lf}(s)$  to PLL output terminal and  $H_{lf}(s)$  is the feedback transfer function from PLL output to  $n_{lf}(s)$ . In Eq. (2.14),  $S_{\phi_{inl,F}}(\omega)$  is the open loop PSD of loop filter only.

In Eqs. (2.5), (2.8), (2.10), (2.12) and (2.14), the input phase noise power spectral densities are experimentally measured in dBc/Hz and converted in units of  $rad^2/Hz$  using Eq. (2.6). The total phase noise PSD ( $rad^2/Hz$ ) of the PLL output is then obtained by summing the output phase noises ( $rad^2/Hz$ ) for a noisy VCO, a noisy input reference clock, a noisy divider, a noisy PFD and a noisy loop filter. Note that the frequency divider increases the phase noise of the input by a factor of  $20\log(N)$  which is to be considered. Since the input phase variations are multiplied by N at the output, the noise spectrum of the output will increase  $N^2$  times the input. This causes  $20\log(N)$  to be added into the total PLL output phase noise.

# 2.2 Hot Carrier Effect (HCE) and Negative Bias Temperature Instability (NBTI) Model

## 2.2.1 HCE and NBTI Models for Single-ended VCO

Figure 2.3 is a current starved single-ended VCO with HCE and NBTI modes. In "normal mode" the VCO is in the oscillation mode with no HCE and NBTI. In "HCE mode", VCO is under hot carrier injection and drain of n-MOSFETs (M1- M3) in the ring oscillator are stressed from  $V_{HCE\ Stress} = 5V$ . In "NBTI mode", the gates of p-MOSFETs (M4- M6) are under 0V bias and the sources of p-MOSFETs (M4-M6) are under 5V bias. It is to be mentioned that the oscillator is not working when it is subjected to either HCE or NBTI modes.

Figure 2.3: The single-ended current starved VCO with HCE and NBTI modes.

Single-ended VCO can achieve larger frequency swing, higher modulation sensitivity and is more capable for wide-band operation than the differential VCO. The gain of VCO output frequency is given by,

$$K_{V} = \frac{\partial f}{\partial V_{BIAS}} = \frac{\mu \cdot C_{OX}}{n} \cdot \frac{W}{L} \cdot \frac{V_{BIAS} - V_{th}}{C_{L} \cdot V_{DD}}$$

(2.15)

where  $C_{OX}$  is gate oxide capacitance per unit area, W/L is the channel width to length ratio of n-MOSFET, which decides the frequency of VCO output.  $V_{BIAS}$  is the bias voltage and  $V_{th}$  is the threshold voltage.

The single-ended VCO oscillation frequency is given by,

$$f = \frac{1}{\eta N(t_r + t_f)} \approx \frac{\mu W C_{OX} \Delta V}{8\eta N L q_{\text{max}}}$$

(2.16)

$$\Delta V = V_{DD} / 2 - V_{th} \tag{2.17}$$

In Eq. (2.16),  $\eta$  is a constant describing the relationship between the stage delay and the slope of the waveform which is 0.75 for 0.5  $\mu$ m CMOS process. N is the number of stages in an oscillator which is 3 in this design,  $\mu$  is the electron mobility, W and L are channel width and channel length of the transistor M1-M3 in Figure 2.3. The total charge in each node of the oscillator is  $q_{max}$ . Rise and fall times are  $t_r$  and  $t_f$ , respectively. The gate overdrive voltage is  $\Delta V$ .

Under hot carrier injection,  $\Delta V$  changes and is expressed as follows,

$$\Delta V = V_{DD} / 2 - V_{th} - \Delta V_{th} \tag{2.18}$$

where  $\Delta V_{th}$  is the threshold voltage shift.

The accumulated jitter in a single-ended VCO can be modeled and calculated as follows.  $\sigma_{\Delta t}$  represents the jitter and is a function of  $\Delta t$ , the delay between the signal input of the oscilloscope and the trigger input.  $\sigma_{\Delta t}$  is given by [29],

$$\sigma_{\Lambda t} = \kappa \sqrt{\Delta t} \tag{2.19}$$

$$\kappa \approx \sqrt{\frac{8}{3\eta}} \sqrt{\frac{kT}{P} \frac{V_{DD}}{V_{char}}}$$

(2.20)

where  $\kappa$  is the jitter proportionality constant. T is the temperature.  $V_{char}$  is the characteristic voltage of the MOSFETs and is given by,

$$V_{char} = \Delta V / \gamma \tag{2.21}$$

In Eq. (2.21),  $\gamma$  is the noise ratio between the saturation and linear regions and numerical value for a short channel device is 4/3 [29].

VCO phase noise presents the variation of the original signal in a frequency domain. The equation below shows the phase noise performance of a CMOS single-ended VCO [29],

$$L\{\Delta f\} \approx \frac{8kTV_{DD}}{3\eta PV_{char}} \frac{{f_0}^2}{\Delta f^2}$$

(2.22)

In Eq. (2.22)  $\Delta f$  is the offset frequency from the carrier. P is the power dissipation and is expressed as follows,

$$P = NI_D V_{DD} (2.23)$$

where  $I_D$  is the drain current in each stage.

NBTI results in the shift in threshold voltage which can be modeled by the following expression [56],

$$\Delta V_t = A \exp(\beta V_{gs} - \frac{E_a}{kT}) t^n$$

(2.24)

where  $\beta$ ,  $E_a$  and n are constants and described in [56].

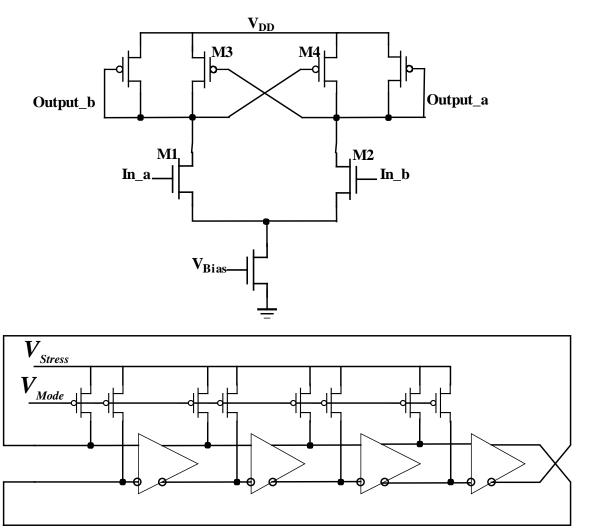

#### 2.2.2 HCE Models for Differential VCO

Figure 2.4 shows the circuit diagram of a differential CMOS VCO. When M1 turns off and M2 turns on ( $In_a$  is logic "0" and  $In_b$  is logic "1"), M3 will be turned-on and M4 will be turned-off. Thus,  $Output_b$  is "1" and  $Output_a$  is "0". Since  $Output_b$  and  $Output_a$  are connected to  $In_a$  and  $In_b$  of the next stage, respectively,  $In_a$  and  $In_b$  will be logic "1" and "0". The oscillation frequency of differential VCO is  $\frac{1}{2Mt_b}$ , where M is the number of stages and  $t_D$  is the delay of the single stage.

The differential VCO oscillation frequency is given by [57],

$$f = \frac{I_{tail}}{2\eta Nq_{\text{max}}} \tag{2.25}$$

where  $I_{tail}$  is the tail current in each stage. The expressions for  $\kappa$  and phase noise are as follows,

$$\kappa \approx \sqrt{\frac{8}{3\eta}} \sqrt{N \frac{kT}{P} \left( \frac{V_{DD}}{V_{char}} + \frac{V_{DD}}{R_L + I_{tail}} \right)}$$

(2.26)

$$L\{\Delta f\} \approx \frac{8NkTV}{3\eta P} \frac{f_0^2}{\Delta f^2} \left( \frac{V_{DD}}{V_{char}} + \frac{V_{DD}}{R_L I_{tail}} \right)$$

(2.27)

where R<sub>L</sub> is the effective load resistance.

The oscillation frequency and jitter/phase noise under the hot carrier injection can be modeled by varying the value of threshold voltage from equations above.

Figure 2.4: Differential VCO with hot carrier stress mode.

# 2.3 Experimental Study

A second-order passive loop filter is designed as shown in Figure 2.5 with PFD. The PFD is built from two controllable D flip-flops. Compared with that using logic gates, it is faster and simpler for an IC chip design.

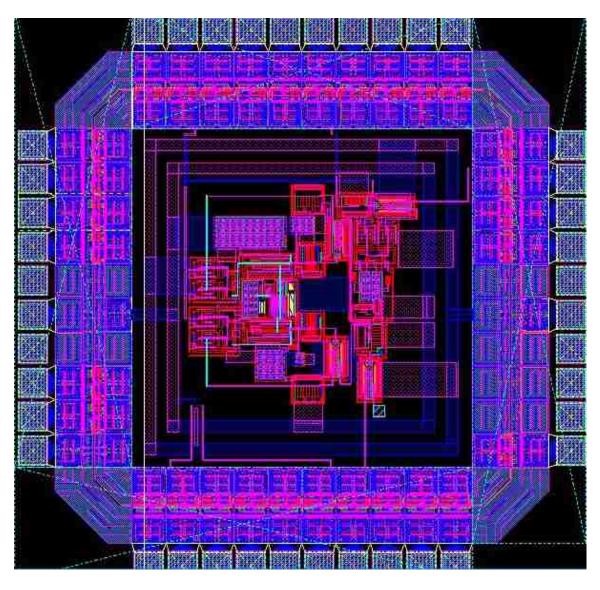

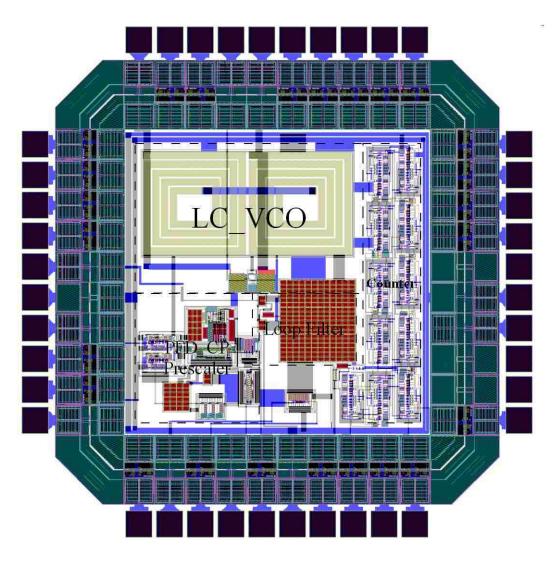

Figure 2.6 shows the layout design of PLL circuit in 0.5 µm n-well CMOS process. PLL and its open loop building blocks are labeled in Figure 2.6. The designed loop parameters of the fabricated PLL chip are: divider ratio, N = 8, charge pump current,  $I_{CP} = 30 \mu A$ , loop filter components:  $R = 41.5 k\Omega$ ,  $C_1 = 43.3 pF$  and  $C_2 = 100 fF$ , VCO gain  $K_V = 30 MHz/V$  . The loop bandwidth is 800 kHz. The locking range is 80 MHz-120 MHz and locking time is  $1.3 \mu s$ . The steady-state phase error of the synchronized loop is 3 ns when the PLL is working at 80 MHz. In the layout design, the separate building blocks of PLL: PFD, loop filter, VCO and divider are included in order to experimentally measure the open loop phase noise power spectrum in dBc/Hz. These are exactly the same CMOS circuits integrated in the PLL and subjected to same operating conditions. For instance, the PLL input is set at 10 MHz and output signal is obtained at 80 MHz; the VCO bias voltage is set at 1.9 V by the charge pump and loop filter; the divider divides the signal from 80 MHz to 10 MHz. For open loop measurements, a 10 MHz reference clock is connected to the spectrum analyzer to measure open loop phase noise; 1.9V dc voltage is given to control the open loop VCO; a noise filtered 80 MHz input signal is given to the open loop divider. Thus, open loop phase noise can be measured on these individual PLL building blocks which make it possible to determine closed loop phase noises. Since the closed loop phase noises of individual blocks are the only noise contribution of each component to the PLL output and without noises from other components, these closed loop phase noises cannot be measured in a real chip. When a

Figure 2.5: Block diagram of loop filter with PFD

Figure 2.6: PLL chip layout.

PLL is running in a system, phase noise measurement of each building block is mixed with noises from other components which are not the exact closed loop phase noises.

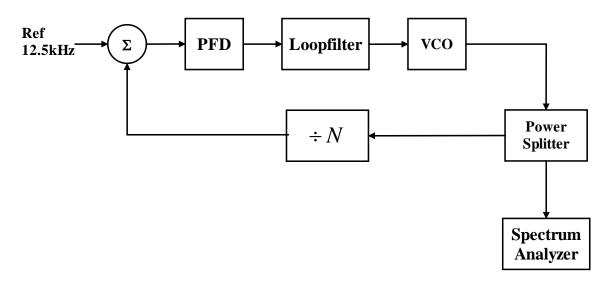

# 2.4 Measurement Setup and Results

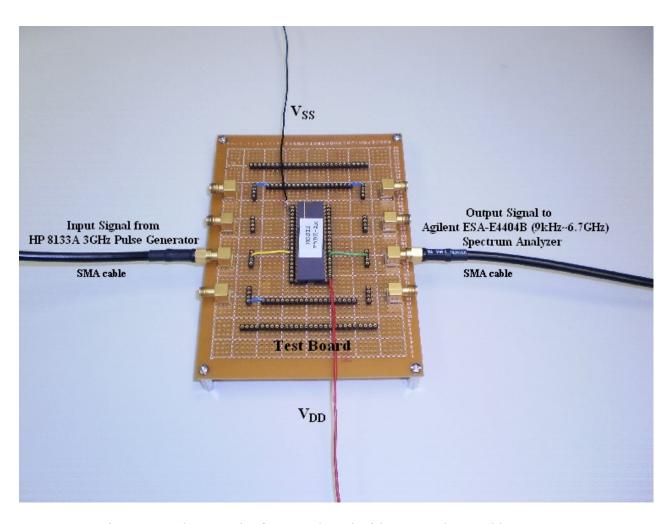

Figure 2.7 shows the photograph of RF test board with mounted PLL chip which is specially designed for this experiment. SMA connecting cables which provide repeatable electrical performance with low noise injection to the chip are used in this measurement. The input signal is provided by HP 8133A 3 GHz Pulse Generator and the output is connected to the 6.7 GHz Agilent ESA-E4404B Spectrum Analyzer. The chip is powered by  $V_{DD} = 5V$  and  $V_{SS} = 0V$ . The built-in phase noise module in spectrum analyzer is used for the phase noise measurement.

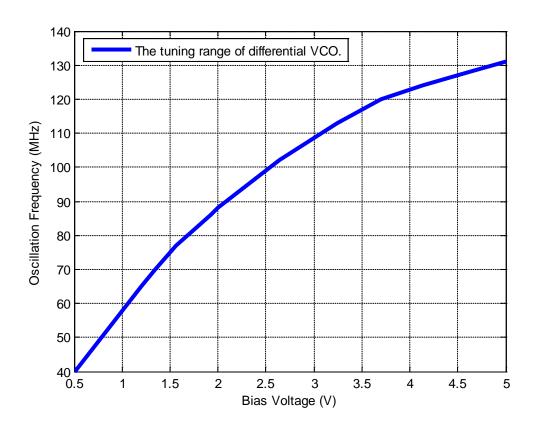

Figure 2.8 shows the experimentally measured voltage-frequency tuning characteristics of the VCO. The gain of the VCO is 30 MHz/V measured at 80 MHz. The free running frequency of the VCO is  $f = f_0 + K_V V_{ctrl}$ , where  $f_0 = 25 MHz$ ,  $V_{ctrl} = 1.9 V$  and  $K_V = 30 MHz/V$ .

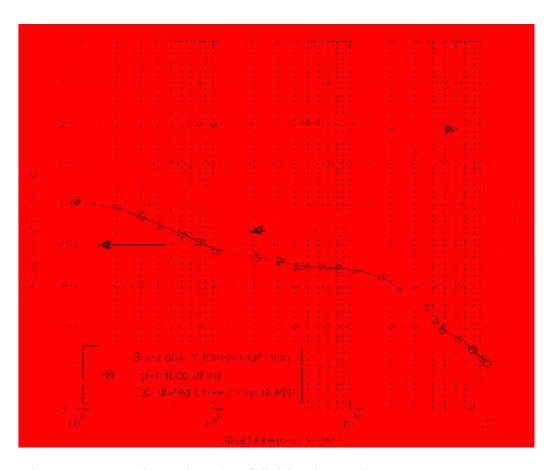

Figure 2.9 shows the experimentally measured single-sideband (SSB) phase noise of the open loop VCO oscillating at 80 MHz. The open loop VCO has two pins: bias voltage and VCO output. Bias voltage pin is connected to a dc 1.9V and the output frequency is 80 MHz. The open loop means that only the VCO is working in this case and it is outside the PLL. The calculated closed loop VCO phase noise is obtained from Eq. (2.5) by substituting the experimentally measured open loop PSD and multiplying the square value of the transfer function calculated from Eq. (2.4).

Figure 2.7: Photograph of RF test board with mounted PLL chip.

١

Figure 2.8: The tuning characteristics of differential VCO

Figure 2.9: Experimental results of VCO phase noise at 80 MHz PLL output frequency.

In this paper, both the open loop and closed loop VCO phase noises are shown. It is to be noted that Hajimiri's work [50] on VCO only gives description of phase noise without any experimental support. It is very interesting to note that prediction of shape of phase noise by Hajmiri [50] agrees with our experimental findings. In Fig. 2.9, open loop phase noise of VCO is -20 dB/decade along the offset frequency, closed loop phase noise is 20 dB/decade at the lower frequency and -20 dB/decade at the higher frequency.

The Bode plot of the transfer function is 20 times the logarithm of the transfer functions of each block obtained from Eqs. (2.4), (2.7), (2.9), (2.11) and (2.13). The calculated closed loop phase noises are shown in Figs. 2.9-2.13. Phase noise power spectrum and Bode plot can be expressed in the same diagram with two Y axes to present how transfer function and open loop phase noise affect the closed loop phase noise. It should be noted that in Figs. 2.9-2.13, the Bode plots of transfer functions are expressed in Gain (dB) and the phase noise is expressed in dBc/Hz.

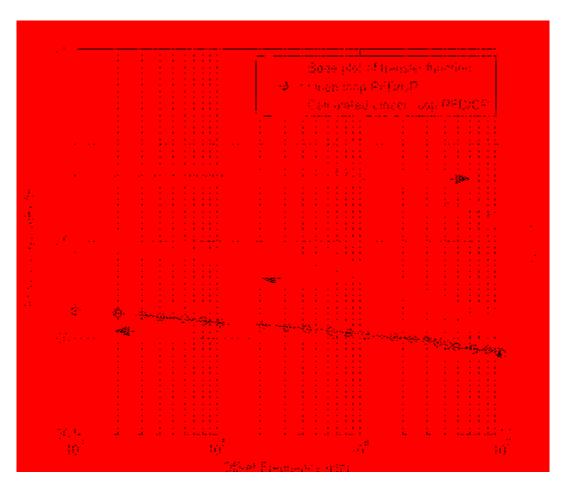

Figure 2.10 shows the experimentally measured SSB phase noise from the input reference clock which is generated by HP 8133A 3 GHz Pulse Generator. The experimentally measured phase noise is between -70 to -103 dBc/Hz from 10 kHz to 10 MHz offset frequency at 10 MHz center frequency. The closed loop phase noise when pulse generator is connected to the chip is obtained from Eqs. (2.7) and (2.8).

Figure 2.11 shows the experimentally measured divider open loop SSB phase noise at 80 MHz PLL output frequency. Following the method described above, the (2.10), (2.12) and (2.14). When the slope of Bode plot is negative, the closed loop phase noise will go negative more sharply than the open loop one. On the other hand, when the slope of Bode plot is positive, the closed loop phase noise will go negative less sharply than the open loop one or turns out to be flat.

Figure 2.10: Experimental results of input reference clock phase noise at 80 MHz PLL output frequency.

Figure 2.11: Experimental results of divider phase noise at 80 MHz PLL output frequency.

Figure 2.12: Experimental results of PFD/CP phase noise at 80 MHz PLL output frequency.

Figure 2.13: Experimental results of loop filter phase noise at 80 MHz PLL output frequency.

Figure 2.11 shows the experimentally measured divider open loop SSB phase noise at 80 MHz PLL output frequency. Following the method described above, the (2.10), (2.12) and (2.14). When the slope of Bode plot is negative, the closed loop phase noise will go negative more sharply than the open loop one. On the other hand, when the slope of Bode plot is positive, the closed loop phase noise will go negative less sharply than the open loop one or turns out to be flat.

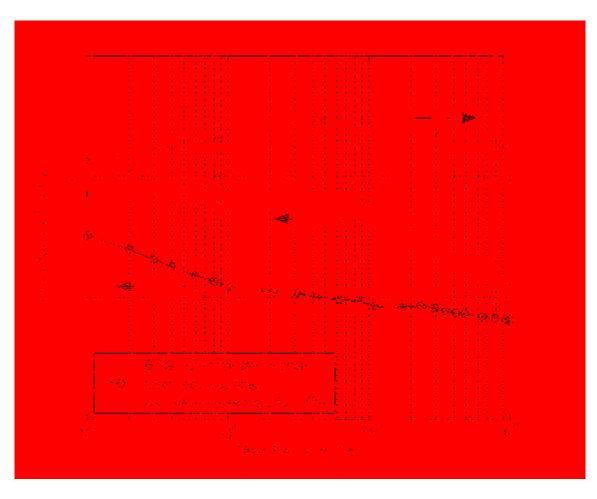

The PLL output phase noise is obtained by the superposition of the noises spectra from VCO, input reference, divider, PFD and loop filter and are shown in Figures 2.14. The solid line shows the PLL output phase noise by summing the closed loop output phase noises from all other components: VCO, input reference clock, PFD/CP, loop filter and divider. There is a peak observed in VCO closed loop phase noise when the offset frequency is near the predicted loop bandwidth, 800 kHz. The low-pass loop filter in PLL blocks all higher order noises. Thus, the phase noise of PLL follows the closed loop VCO phase noise beyond the PLL bandwidth. At low offset frequencies, noise is dominated by the input reference clock since the loop gain tries to make the phase of VCO stable. Phase noises generated by PFD/CP, divider and loop filter dominate the mid of offset frequencies of the PLL output phase noise.

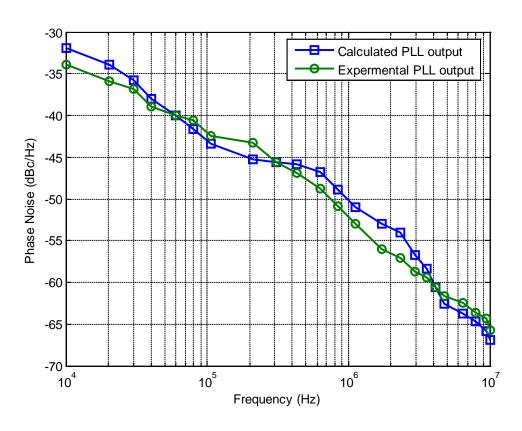

The experimental PLL output phase noise compared with the calculated one is shown in Figure 2.15. The experimentally measured phase noise of the fabricated CMOS PLL circuit follows the calculated frequency dependence phase noise behavior and is in good agreement. By comparing the experimental PLL output and calculated PLL output phase noise, 1-2 dB difference is observed which is within the experimental error of measurement.

# 2.5 Conclusion

In this work, a second-order order PLL circuit is designed in 0.5 µm n-well CMOS and an attempt has been made to model phase noise based on superposition of phase noises from its following circuit building blocks: the input reference, VCO, frequency divider, PFD and the loop filter. Experimentally measured phase noise of the PLL chip follows the modeled behavior and is in good agreement. The closed loop phase noise of PLL can be obtained by the superposition method under its linear operating range.

Figure 2.14: Closed-loop PLL output noise performance compared to the closed-loop noise performances of the individual components.

Figure 2.15: Calculated and measured PLL phase noises.

#### **CHAPTER 3**

## PHASE NOISE AND JITTER STUDY IN CMOS SWITCHABLE PHASE-LOCKED LOOP CONSIDERING HOT CARRIER EFFECTS\*

The phase-locked loops have been widely utilized in high speed communication systems. Low-cost frequency synthesizers with voltage-controlled oscillators (VCOs), such as the single-ended ring oscillator and differential ring oscillator, are widely used in wireless LAN. There are many concerns in these applications for the PLL design. These concerns include phase noise, jitter, power consumption, frequency tuning range, VCO tuning gain and locking/settling time etc. Tradeoffs often exist among different design goals. For example, narrow PLL bandwidth may be required to minimize the noise contribution from dividers and to suppress reference spurs [57]. However, this leads to a long locking time. Furthermore, as the operating frequency increases, power consumption also rises.

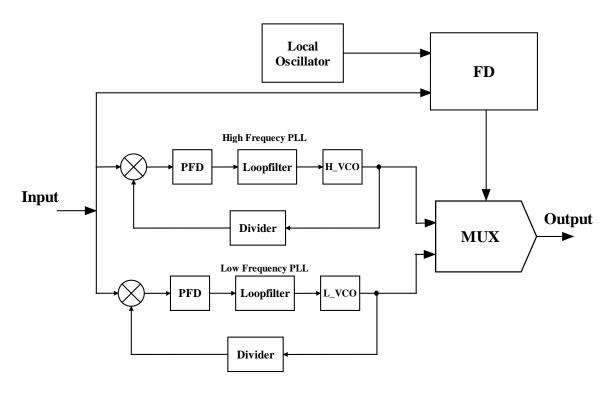

We propose a switchable PLL, which combines two relatively narrow bandwidth PLLs into a single chip and use a frequency detector to decide which PLL to choose according to the reference frequency. As a result, the switchable PLL can work over a wide tuning range and at a high frequency. It also achieves a short locking time without sacrificing the jitter and phase noise performance.

Two PLL frequency synthesizers are integrated in a single chip design, one is working in high frequency range and the other is working in low frequency range. Both

<sup>\*</sup>Part of the work is reported in the following publications:

<sup>1.</sup> Y. Liu, A. Srivastava and Y. Xu, "Switchable PLL frequency synthesizer and hot carrier effects," Journal of Circuits and Systems, Vol. 2, No. 1, pp-45-52, Jan. 2011.

<sup>2.</sup> Y. Liu, A. Srivastava and Y. Xu, "A switchable PLL frequency synthesizer and hot carrier effects," *Proc. ACM Great Lakes Symposium on VLSI*, pp. 481-486, May 10-12, 2009, Boston, USA.

PLLs include phase-frequency detector (PFD), charge pump (CP), 2<sup>nd</sup> order loop filter, current starved VCO and 1-by-8 divider. The input range is from 40 MHz to 144 MHz and output range is from 320 MHz to 1.15 GHz. The charge pump and 2<sup>nd</sup> order low pass loop filter are used to make the system stable and minimize the high frequency noise. PFD is implemented with NOR gates and D-flip flops.

In submicron CMOS devices, the performance of integrated circuits is influenced by the hot carrier effect due to increased lateral channel electric field and results in circuit degradation. Thus, jitter and phase noise may also be affected. Recently, results of hot carrier stress on CMOS VCOs, one of the modules of a PLL have been reported [58-60]. In this work, hot carrier effect has been considered and its effect on phase noise and jitter has been studied.

#### 3.1 The Switches

As shown in Figure 3.1, the switch includes a local oscillator, frequency detector (FD) and a two input multiplexer (MUX). The same kind of VCO described above is working as local oscillator but the difference is that local VCO doesn't have stress mode and the oscillation frequency is locked at 80 MHz. The FD compares it with the input signal. When the input frequency is higher than 80 MHz, the FD output is high which means the high frequency PLL (H\_PLL) output signal will go out via the MUX. On the other hand, when the input signal frequency is lower than 80 MHz, the output of the frequency detector is low and the low frequency PLL (L\_PLL) output signal will go out via the MUX.

Figure 3.1: Building blocks of a switchable PLL architecture.

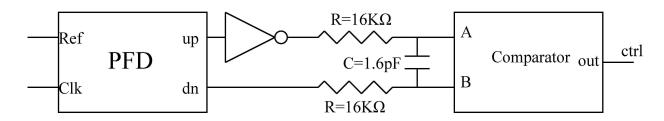

The FD circuit schematic is shown in Figure 3.2. The structure of the detector is same with the PFD in each PLL. The RC circuit transfers the output AC signals of PFD to relatively high and low DC voltage signals and comparator compares these two signals to give high or low voltage, which drives the MUX.

## 3.2 Analysis

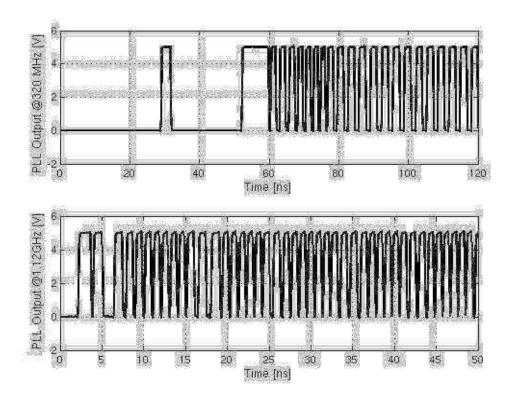

Figure 3.3 shows the output of the switchable PLL at different frequencies where 320 MHz waveform is the low frequency PLL (L\_PLL) output and 1.12 GHz waveform is the high frequency PLL (H\_PLL) output.

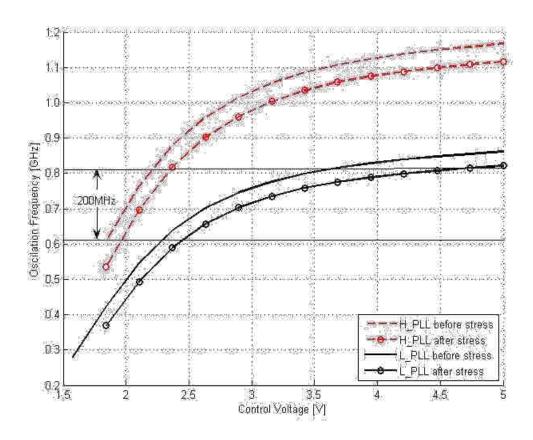

Figure 3.4 shows the variation of PLL output frequency versus control voltage, with and without hot carrier effects. Both the oscillation frequency and frequency range of the PLLs decrease. For the worst case, the overlapping frequency range, which is 250 MHz without hot carrier effects, decreased to 200 MHz. Figure 3.5 shows the PLL tuning frequency range under NBTI stress. It appears from the comparison of figures 3.4 and 3.5 that NBTI stress follows the behavior similar to HCE on PLL tuning frequency with frequency overlap.

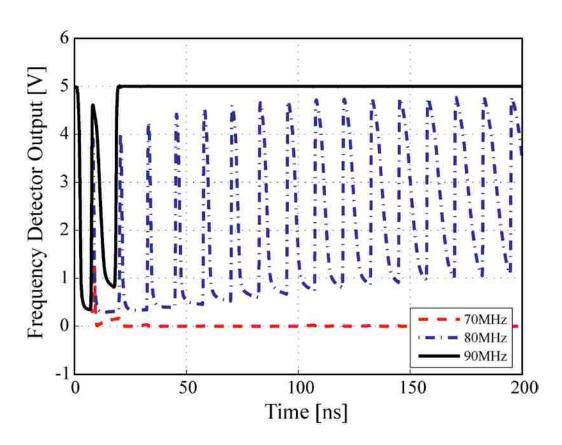

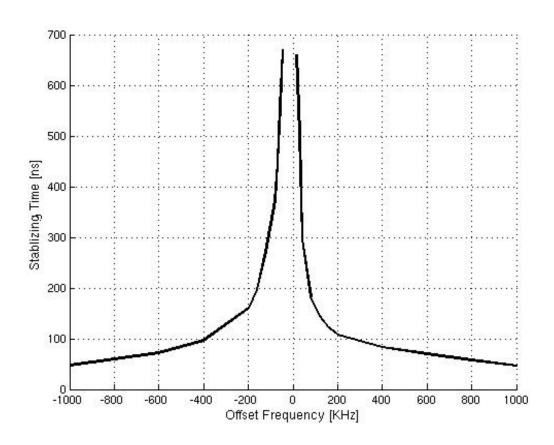

The function of RC in the frequency detector is to translate the PFD output pulses into DC voltages, which are shown in Figure 3.6. If the input frequency is less than the reference frequency, which is output of the local oscillator defined as 80 MHz, the output is at low level; while if the input frequency is higher than the reference frequency, the output is at high level. But if the input frequency is closer to the reference frequency, it will take more time to get the DC output. Figure 3.7 shows this phenomenon.

When the input frequency equals the reference frequency, the output will be oscillating and the stable time will be infinity as shown in Figure 3.7. To deal with this problem, the frequency overlapping range of the two PLLs is expanded.

Figure 3.2: Frequency detector architecture.

Figure 3.3: Switchable PLL outputs at different frequencies. (L PLL starts to oscillate after 60ns and H PLL starts to oscillate after 5ns).

Figure 3.4: Hot carrier effects on frequency synthesizer.

Figure 3.5: The NBTI degradation of switchable PLL tuning frequency range.

Figure 3.6: Frequency detector output.

In Figure 3.5, it can be noticed that the overlapping range is 200 MHz at least. Thus, if the input frequency is close to reference frequency (80 MHz) the control voltage of the local oscillator can be adjusted to change the reference frequency higher or lower. The large overlapping range guarantees that the difference between the input frequency and reference frequency is large enough so that the stabilizing time is smaller than 200 ns, which is the stabilizing time of the high frequency PLL. As a result, the stabilizing time of the switchable PLL is decided by the PLLs, while the operation range is much larger than that of the single PLL.

#### 3.3 Simulation Results

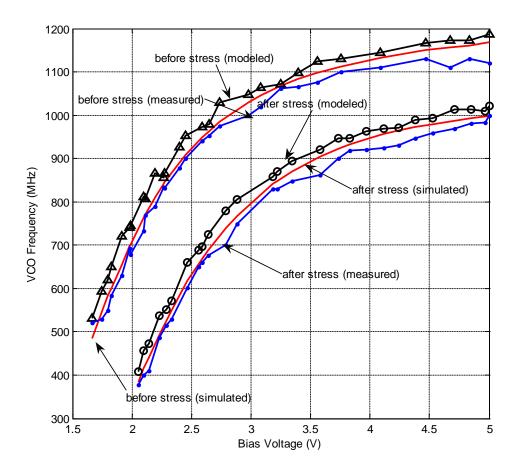

Figure 3.8 shows the simulation, modeled and measured results of the oscillation frequency of open loop VCO in H\_PLL before and after hot carrier stress versus different bias voltages. The simulation results are performed by Cadence/Spectre. It is shown that at a 4 V bias, the frequency is around 1150 MHz before stress and it is about 950 MHz after stress. This is the effect on VCO output frequency due to hot carrier injection in MOSFETs. Figure 3.8 includes experimental data on tuning range of VCO whose operation frequency is slightly lower than the simulation one. Phase noise and jitter measured under hot carrier stress for both VCO and PLL are reported in the following section.

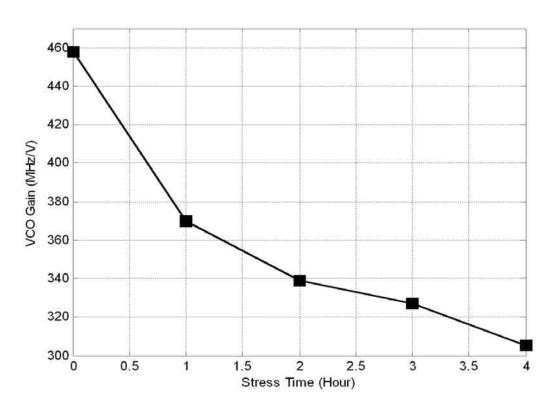

Figure 3.9 shows the decrease of H\_PLL VCO frequency gain at 2.5 V bias voltage versus stress time, which agrees with the Eq. (2.15). After 4 hours of hot carrier injection, the VCO gain decreases by about 33%, from 460 MHz to 310 MHz.

Figure 3.7: Frequency detector stabilizing time versus frequency.

Figure 3.8: The degradation of VCO frequency due to hot carrier effects.

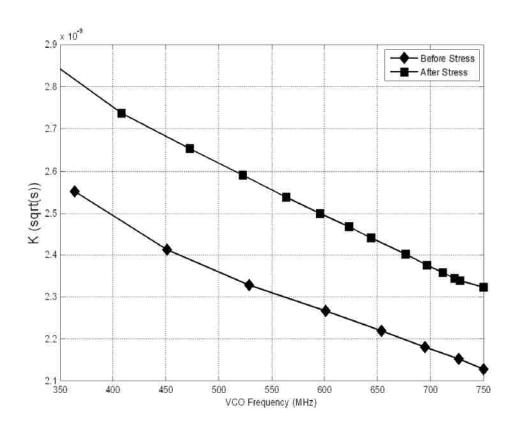

Figure 3.10 shows the simulation result for the variation of the jitter proportionality parameter, K changing with the oscillation frequency before and after 4 hours of stress. K increases by about 10%, which means the value of the jitter of the 3 stages single-ended VCO increases by about  $0.2\sqrt{\Delta T} ns$  due to hot carrier effects from Eq. (2.20).  $\Delta T$  is the time difference between rising edge of trigger clock and the observed clock. Thus, the jitter  $\sigma_{\Delta T}$  mainly depends on K, which varies with different tuning frequencies.

## 3.4 Experimental Results

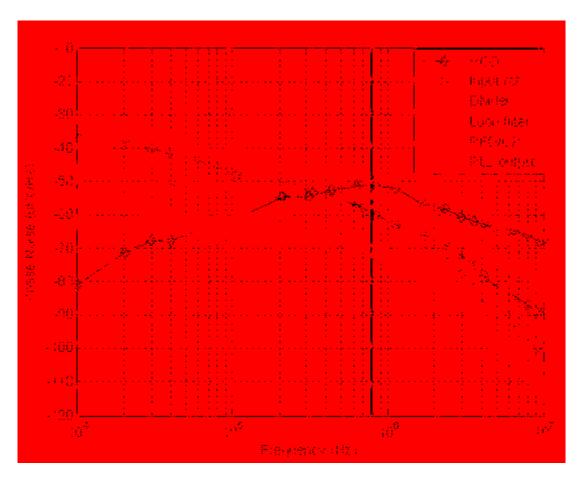

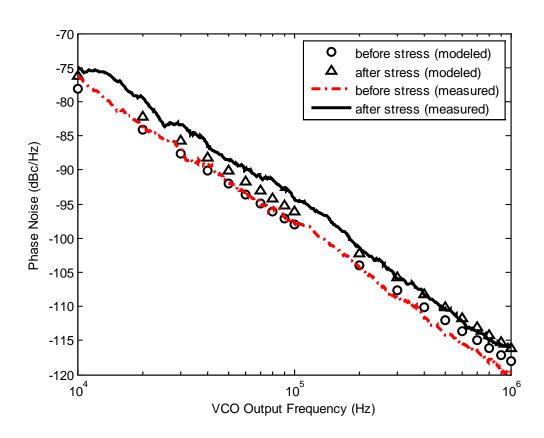

Figure 3.11 shows the experimental and modeled phase noises of the open loop VCO at 1 GHz oscillation frequency before and after hot carrier stress. The experimental results which are from open loop VCO circuit on the chip are in good agreement with the modeled phase noises which are calculated from Eq. (2.22).

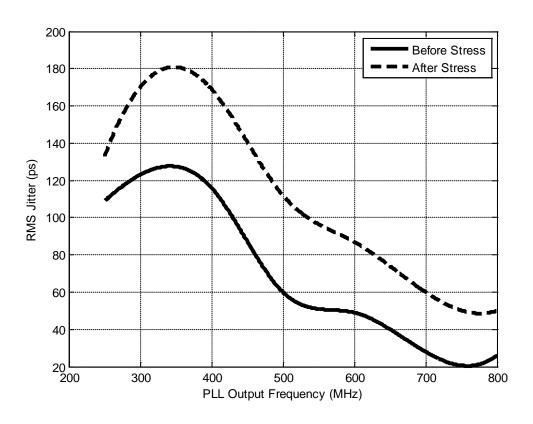

Figure 3.12 shows the experimental results of device degradation on RMS jitter performance under different PLL output frequencies due to hot carrier effects. A 40 ps increase is observed after 4 hours of stress.

The experimental results for PLL output frequencies with hot carrier effects are listed in Table 3.1, measured using Tektronix 11801A Digital Sampling Oscilloscope.

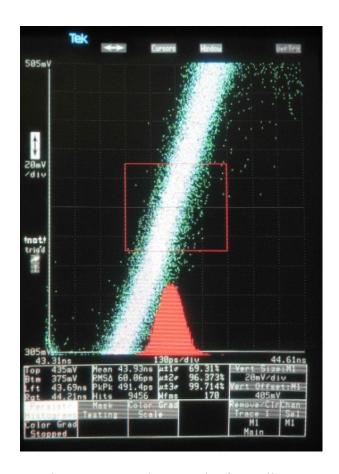

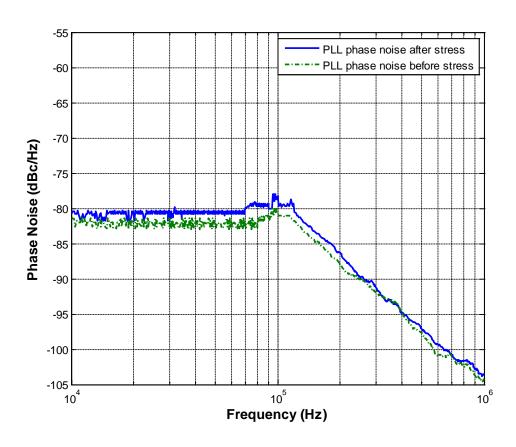

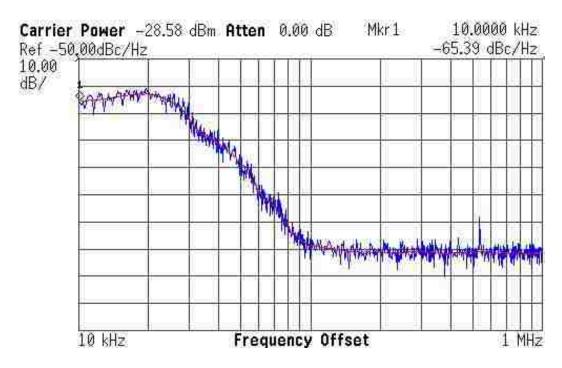

Figure 3.13 shows a photograph of the switchable PLL jitter performance measured by a digital sampling oscilloscope and is 59 ps. Figure 3.14 shows the experimental results of PLL output phase noise at 700 MHz carrier frequency by using Agilent ESA-E4404B Spectrum Analyzer, before and after stress. The offset frequency is from 10 kHz to 1 MHz. In Figure 3.14, the PLL phase noise before stress is -79dBc/Hz at 10 kHz offset frequency and is around -104dBc/Hz at 1 MHz offset frequency. The PLL

Figure 3.9: VCO gain versus stress time for H\_PLL for H\_PLL. Note: Bias Voltage=2.5V.

Figure 3.10: The dependence of  $\kappa$  and VCO frequency due to hot carrier effects.

Figure 3.11: Degradation on phase noise performance under 1 GHz oscillation frequency.

Figure 3.12: Experimental results of PLL jitter.

Table 3.1. Experimental results for different output frequencies of the PLL

| Input<br>Freq.<br>(MHz) | Output<br>Freq.(MHz) | RMS<br>Jitter(ps) | RMS<br>Jitter<br>(HCE)<br>(ps) | (dBc/l<br>10kHz of | Noise<br>Hz) at<br>ffset (w/o | Phase Noise<br>(dBc/Hz) at 1MHz<br>offset (w/o HCE,<br>w/ HCE) |      |  |

|-------------------------|----------------------|-------------------|--------------------------------|--------------------|-------------------------------|----------------------------------------------------------------|------|--|

| 31                      | 250                  | 109               | 132                            | -70                | -69                           | -117                                                           | -116 |  |

| 38                      | 300                  | 123               | 168                            | -76                | -75                           | -115                                                           | -111 |  |

| 50                      | 400                  | 116               | 166                            | -79                | -75                           | -113                                                           | -109 |  |

| 63                      | 500                  | 59                | 113                            | -70                | -68                           | -126                                                           | -124 |  |