#### Louisiana State University LSU Digital Commons

#### LSU Master's Theses

Graduate School

2011

# A study of the scale-invariant feature transform on a parallel pipeline

Phaneendra Vinukonda Louisiana State University and Agricultural and Mechanical College

Follow this and additional works at: https://digitalcommons.lsu.edu/gradschool\_theses Part of the <u>Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

Vinukonda, Phaneendra, "A study of the scale-invariant feature transform on a parallel pipeline" (2011). *LSU Master's Theses*. 2721. https://digitalcommons.lsu.edu/gradschool\_theses/2721

This Thesis is brought to you for free and open access by the Graduate School at LSU Digital Commons. It has been accepted for inclusion in LSU Master's Theses by an authorized graduate school editor of LSU Digital Commons. For more information, please contact gradetd@lsu.edu.

#### A STUDY OF THE SCALE-INVARIANT FEATURE TRANSFORM ON A PARALLEL PIPELINE

Thesis

Submitted to the Faculty of the Louisiana State University and Agricultural and Mechanical College in partial fulfillment of the requirements for the degree of Master of Science in Electrical Engineering

$\mathrm{in}$

The Department of Electrical and Computer Engineering

by Phaneendra Vinukonda B.TECH., JNTU University, 2007 May 2011

### Acknowledgements

I am indebted to my major advisor Dr. Ramachandran Vaidyanathan for his exemplary patience, guidance and support. During my stay here at LSU, he taught me the skills of problem solving, provided me with some good motivations, helped me through the difficulties I have gone through on the way towards this degree. It was with his kind support, I overcame all the obstacles on my way towards completing my thesis.

I would also like to thank my committee members, Dr. S. Rai and Dr. Gunturk for their valuable suggestions and kind support. Furthermore, I thank the Dept. of Electrical and Computer Engineering for making me concentrate on my research without any other deviations.

I wish to endow my earnest gratitude to my parents, who believed in me and have been thorough all the rough times. I also want to thank my brother V. Hareendra, my entire family and friends for their affection, support and compassion.

## Table of Contents

| A            | cknowledgements                                                                                                   | ii  |

|--------------|-------------------------------------------------------------------------------------------------------------------|-----|

| Τa           | able of Contents                                                                                                  | iii |

| Li           | ist of Figures                                                                                                    | v   |

| Li           | ist of Tables                                                                                                     | ix  |

| $\mathbf{A}$ | bstract                                                                                                           | x   |

| 1            | Introduction                                                                                                      | 1   |

| <b>2</b>     | Scale Invariant Feature Transform                                                                                 | 4   |

|              | 2.1 Flow of Data in SIFT                                                                                          | 5   |

|              | 2.2 Scale-Space Extrema Detection                                                                                 | 6   |

|              | 2.3 Keypoint Detection                                                                                            | 11  |

|              | 2.4 Orientation Assignment                                                                                        | 12  |

|              | 2.5 Keypoint Descriptor Generation                                                                                | 13  |

| 3            | Experimental Study                                                                                                | 15  |

|              | 3.1 Images Used in Study                                                                                          | 15  |

|              | 3.2 Time Taken by Different Phases                                                                                | 16  |

|              | 3.3 Feature Fractions                                                                                             | 21  |

| 4            | 8                                                                                                                 | 31  |

|              | 4.1 Tile Notation                                                                                                 | 31  |

|              | 4.2 Row Major Ordering                                                                                            | 32  |

|              | 4.3 Diagonal Ordering                                                                                             | 33  |

| <b>5</b>     | The Computation Pipeline                                                                                          | 35  |

|              | 5.1 Notation $\ldots$            | 37  |

|              | 5.1.1 Stage Start Times $\ldots$ | 37  |

|     | 5.2   | Memory                                    | 43 |

|-----|-------|-------------------------------------------|----|

|     | 5.3   |                                           | 44 |

|     | 5.4   | Architecture                              | 44 |

|     | 5.5   | Pipelining Multiple Images                | 44 |

| 6   | Inp   | ut Data Flow Requirements                 | 46 |

|     | 6.1   | Tile-Plus-Neighborhood Protocol           | 47 |

|     |       | 6.1.1 Row Major Tile Ordering             | 49 |

|     |       | 6.1.2 Diagonal Method Tile Ordering       | 56 |

|     | 6.2   |                                           | 62 |

|     |       | 6.2.1 Row Major Tile Ordering - Tile Only | 64 |

|     |       | 6.2.2 Diagonal Tile Ordering - Tile Only  | 66 |

| 7   | Sing  | gle-Chip Uniprocessor                     | 69 |

|     | 7.1   |                                           | 70 |

|     | 7.2   |                                           | 71 |

|     | 7.3   |                                           | 73 |

|     |       |                                           | 74 |

|     | 7.4   |                                           | 77 |

|     | 7.5   |                                           | 82 |

|     |       |                                           | 82 |

|     |       |                                           | 82 |

| 8   | Sing  | gle-Chip, Multicore Processor             | 84 |

|     | 8.1   |                                           | 84 |

|     | 8.2   |                                           | 86 |

|     | 8.3   |                                           | 86 |

|     |       |                                           | 87 |

|     |       |                                           | 89 |

|     |       |                                           | 91 |

|     |       | 8.3.4 Total Time                          | 93 |

|     | 8.4   |                                           | 94 |

| 9   | Two   | o-Chip, Multicore Processor               | 95 |

|     | 9.1   |                                           | 96 |

| 10  | Con   | clusion and Future Work                   | 98 |

| Bi  | bliog | m graphy                                  | 01 |

|     | _     |                                           | 06 |

| 4 1 |       | · · · · · · · · · · · · · · · · · · ·     | 50 |

# List of Figures

| 2.1  | Major phases of the SIFT algorithm                                            | 5  |  |  |

|------|-------------------------------------------------------------------------------|----|--|--|

| 2.2  | The internal stages of Scale-Space Extrema Detection                          | 7  |  |  |

| 2.3  | An example of applying a 5 $\times$ 5 Gaussian window on a point              | 8  |  |  |

| 2.4  | Scale, octaves and difference of Gaussians                                    | 10 |  |  |

| 2.5  | Extrema detection on octave $j$                                               | 11 |  |  |

| 2.6  | Improved SIFT algorithm                                                       | 12 |  |  |

| 2.7  | Keypoint descriptor generation                                                | 14 |  |  |

| 3.1  | Pictures considered                                                           | 17 |  |  |

| 3.2  | Percentage time for major stages of SIFT                                      | 19 |  |  |

| 3.3  | Percentage time of SIFT major phases over different pictures                  |    |  |  |

| 3.4  | The absolute times of major SIFT phases                                       |    |  |  |

| 3.5  | Gaussian blurring lines                                                       | 22 |  |  |

| 3.6  | Average time for Gaussian blurring and difference of Gaussian phases $\ldots$ | 23 |  |  |

| 3.7  | Times taken for scale-space extrema detection, orientation assignment and     |    |  |  |

|      | keypoint descriptor generation phases                                         | 23 |  |  |

| 3.8  | Nominal number of extrema, keypoints and features                             | 24 |  |  |

| 3.9  | The value of $\alpha$ for all the image resolutions of picture number 26 24   |    |  |  |

| 3.10 | The value of $\beta$ for all the image resolutions of picture number 26       | 25 |  |  |

| 3.11 | The value of $\gamma$ for all the image resolutions of picture number 26                                         | 25 |

|------|------------------------------------------------------------------------------------------------------------------|----|

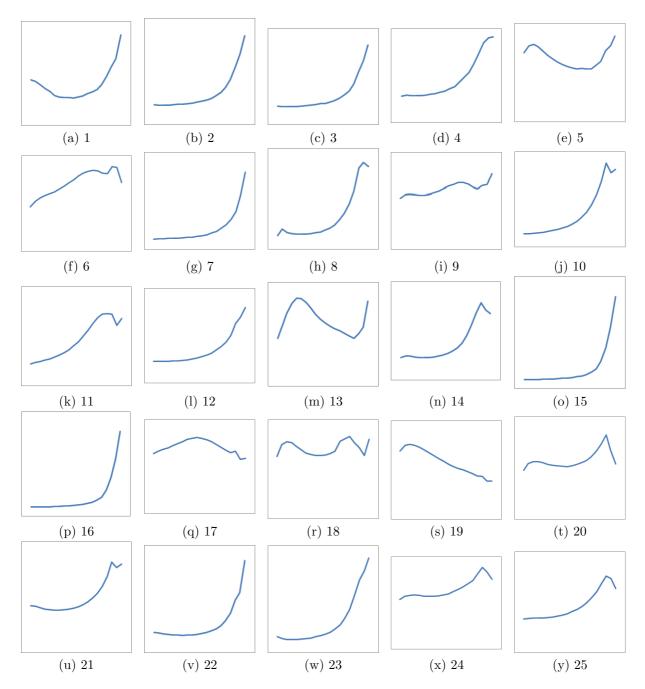

| 3.12 | The value of $\alpha$ for all the image resolutions of pictures numbered 1-25                                    | 26 |

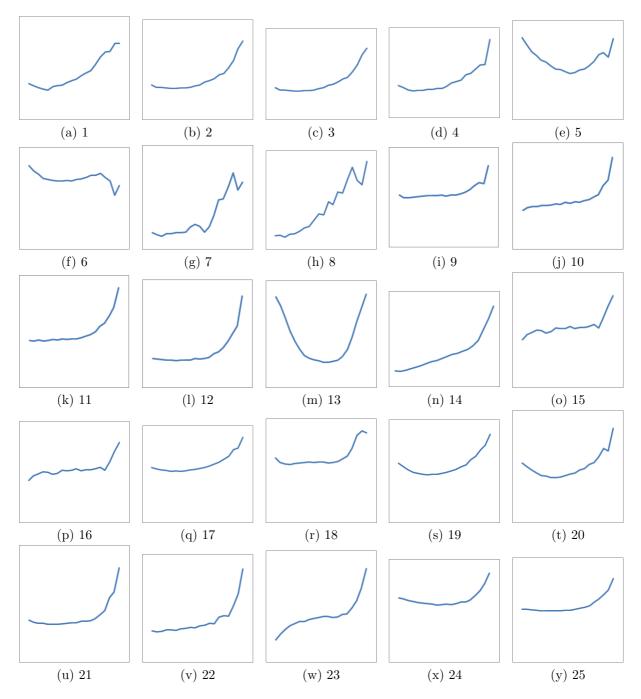

| 3.13 | The value of $\beta$ for all the image resolutions of pictures numbered 1-25                                     | 27 |

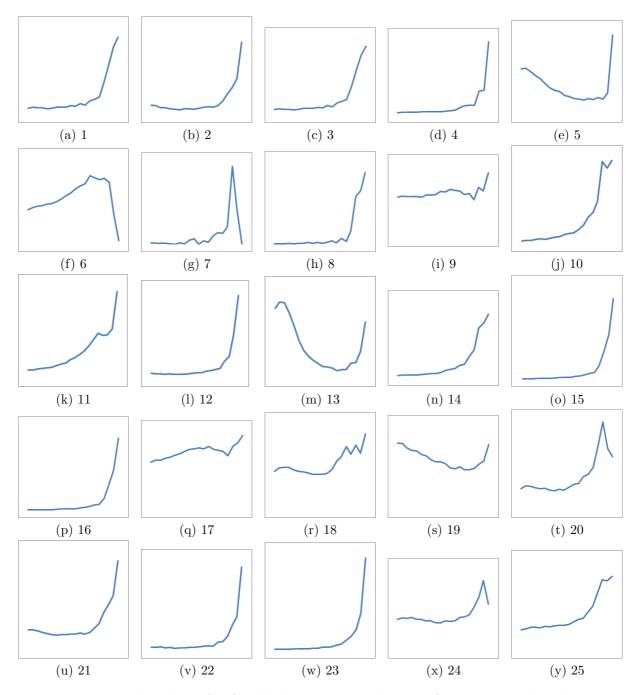

| 3.14 | The value of $\gamma$ for all the image resolutions of pictures numbered 1-25                                    | 28 |

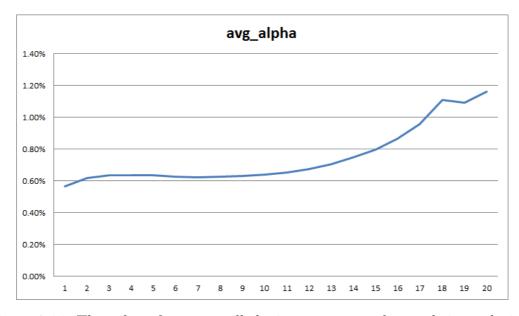

| 3.15 | The value of $\alpha$ across all the images averaged over their resolutions $\ldots$                             | 29 |

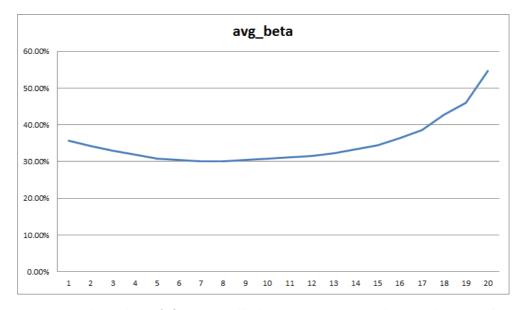

| 3.16 | The value of $\beta$ across all the images averaged over their resolutions $\ . \ . \ .$                         | 29 |

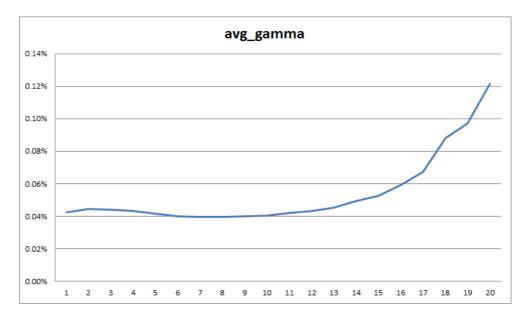

| 3.17 | The value of $\gamma$ across all the images averaged over their resolutions $\ . \ . \ .$                        | 30 |

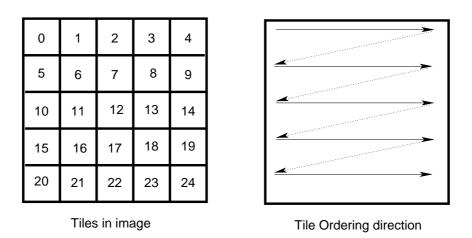

| 4.1  | Coordinate representation of tiles in a tile array                                                               | 32 |

| 4.2  | Row-major ordering                                                                                               | 33 |

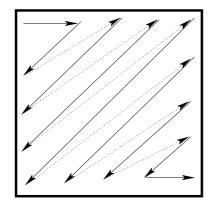

| 4.3  | Diagonal ordering                                                                                                | 33 |

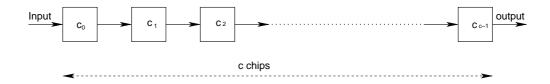

| 5.1  | A <i>c</i> -chip pipeline                                                                                        | 35 |

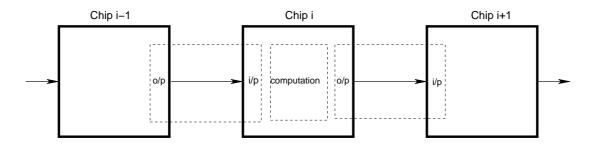

| 5.2  | A chip in the pipeline model                                                                                     | 36 |

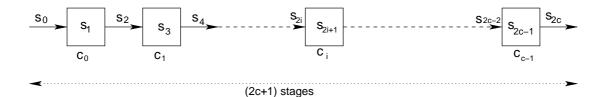

| 5.3  | Stages in the pipeline model                                                                                     | 36 |

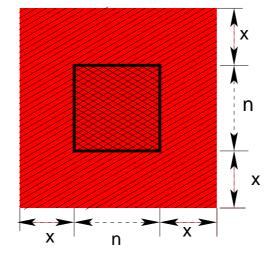

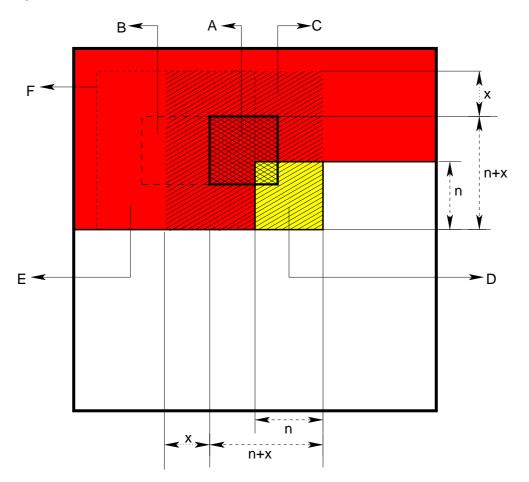

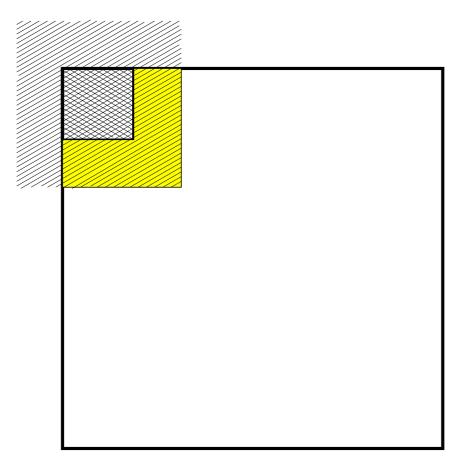

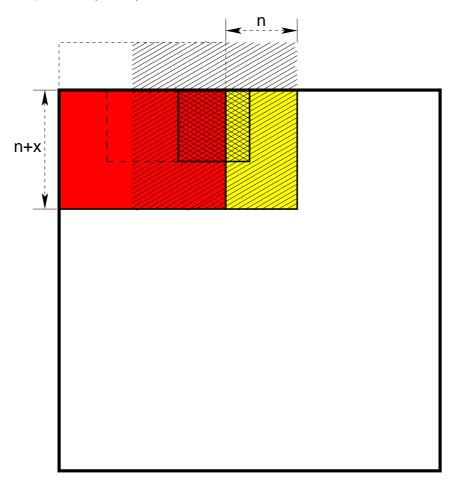

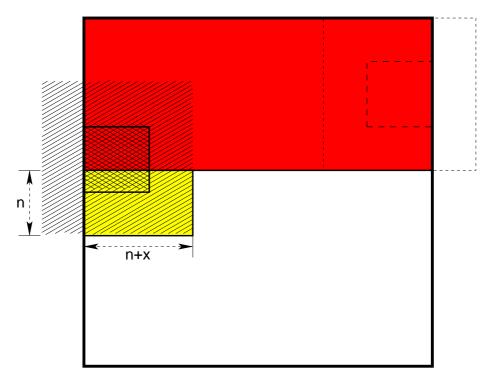

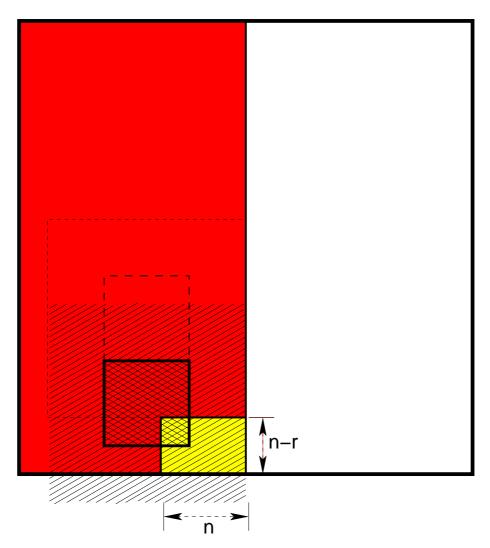

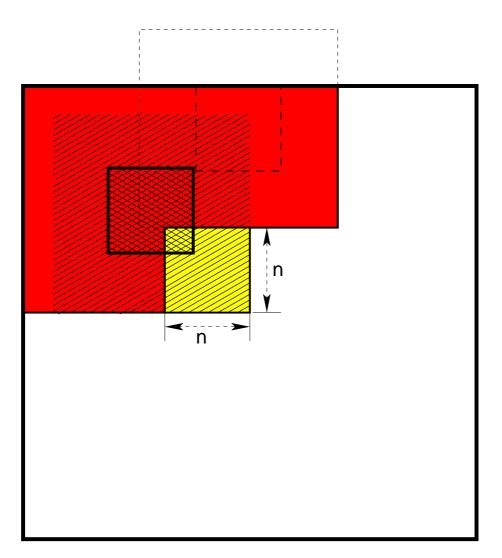

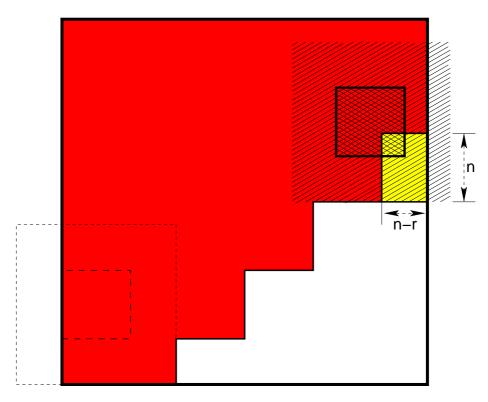

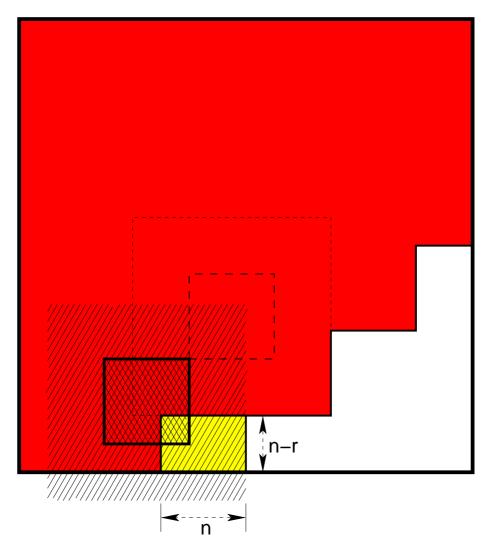

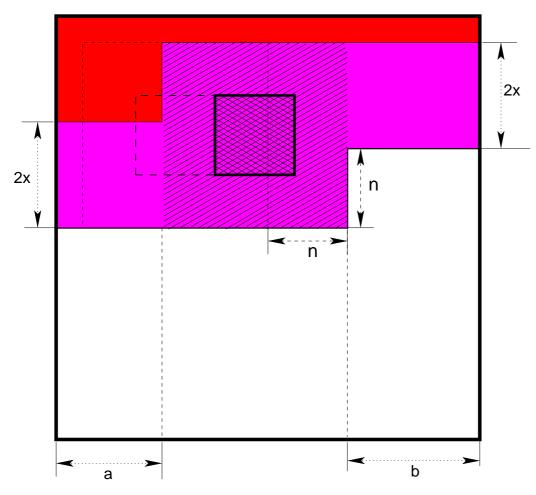

| 6.1  | A tile and its neighborhood                                                                                      | 47 |

| 6.2  | Tile and its neighborhood in the context of entire image $\ldots \ldots \ldots \ldots$                           | 48 |

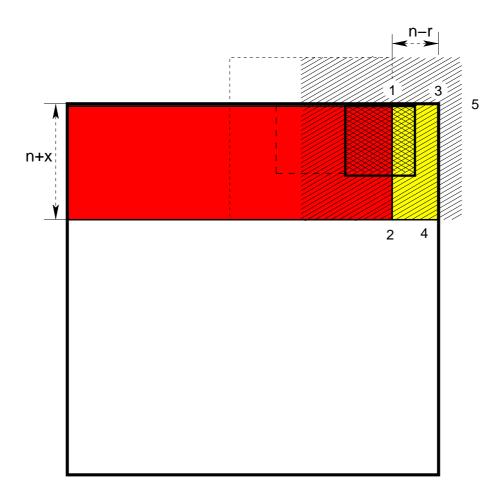

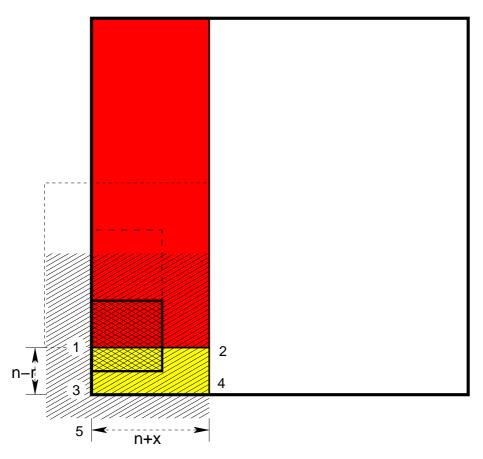

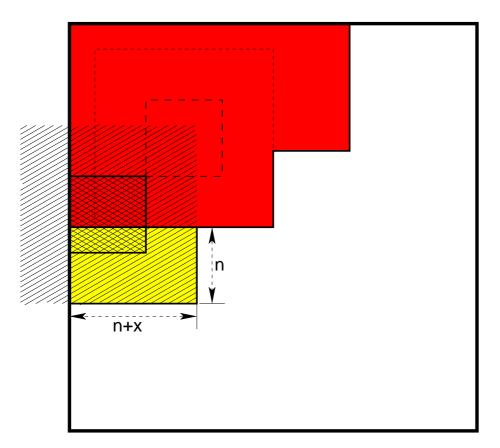

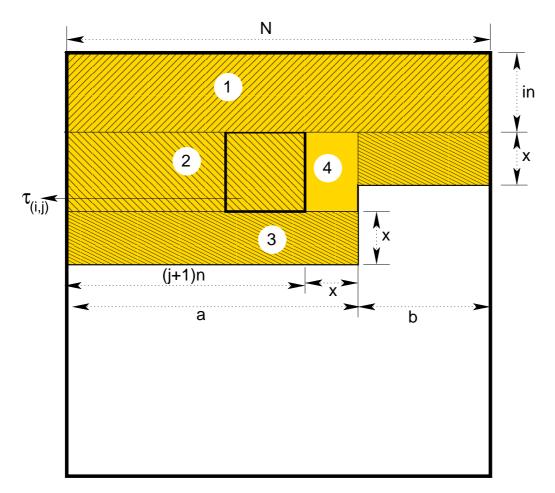

| 6.3  | First tile of the row-major tile ordering                                                                        | 49 |

| 6.4  | Tile in row 0 and column $0 < c < z$                                                                             | 50 |

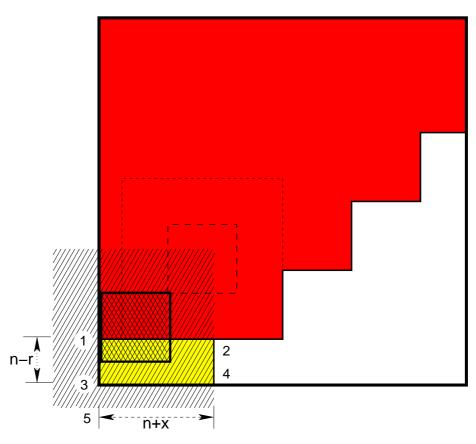

| 6.5  | Tile in column 0 and in row $0 < r < z$ rows $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                  | 51 |

| 6.6  | Tile in row 0 and column $z$                                                                                     | 52 |

| 6.7  | Tile in column 0 and row $z \ldots \ldots$ | 53 |

| 6.8  | Tile in row $0 < r < z$ and column $0 < c < z$                                                                   | 54 |

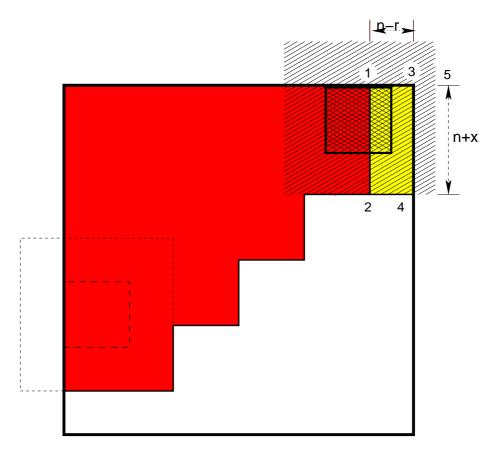

| 6.9  | Tile in column $z$ and row $0 < r < z$                                                                           | 55 |

| 6.10 | Tile row $z$ and in column $0 < c < z$                                                                           | 56 |

| 6.11 | Tile in row $z$ and column $z$                                                                                | 57 |

|------|---------------------------------------------------------------------------------------------------------------|----|

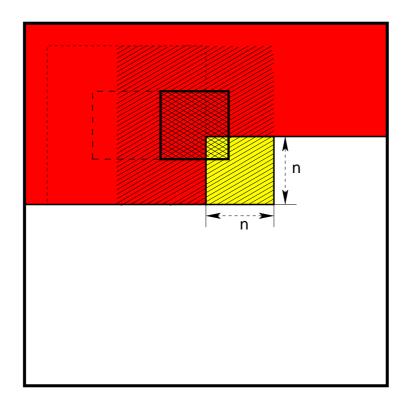

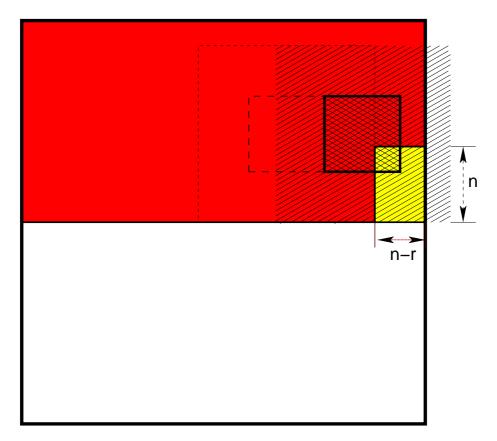

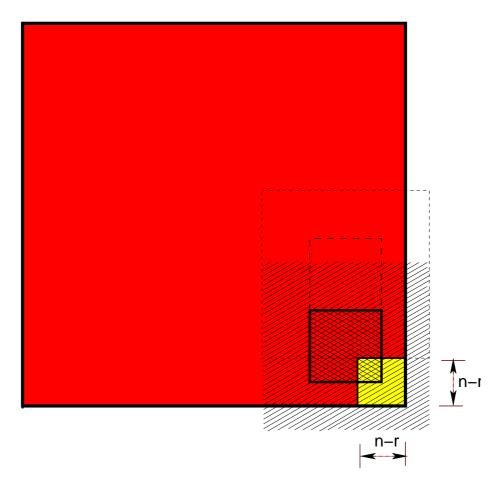

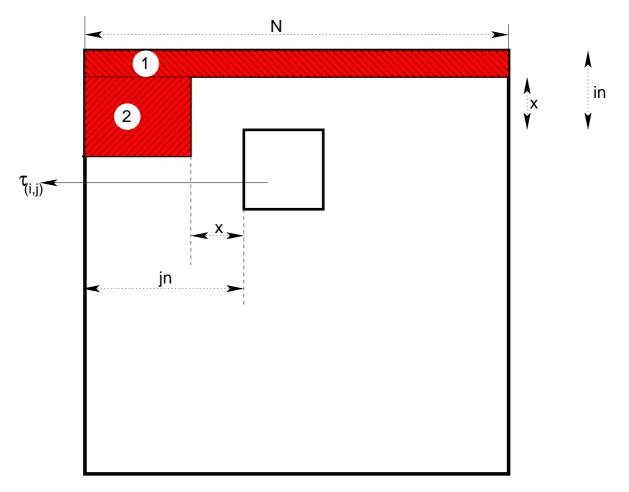

| 6.12 | First tile of the diagonal tile ordering                                                                      | 58 |

| 6.13 | Tiles in row 0 and column $0 < c < z$                                                                         | 59 |

| 6.14 | Tiles in column 0 and row $0 < r < z$                                                                         | 60 |

| 6.15 | Tile in row 0 and column $z$                                                                                  | 61 |

| 6.16 | Tile in column 0 and row $z$                                                                                  | 62 |

| 6.17 | Tile in row $0 < r < z$ and column $0 < c < z$                                                                | 63 |

| 6.18 | Tile in column $z$ and row $0 < r < z$                                                                        | 64 |

| 6.19 | Tile in row $z$ and column $0 < c < z$                                                                        | 65 |

| 6.20 | Tile in row $z$ and column $z$                                                                                | 66 |

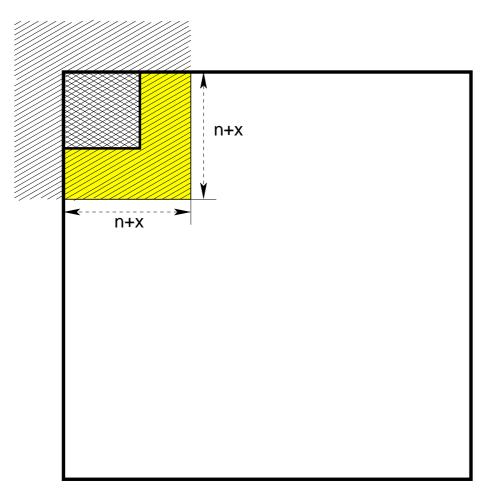

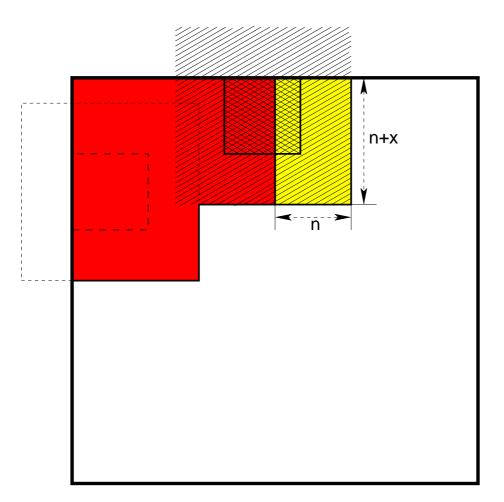

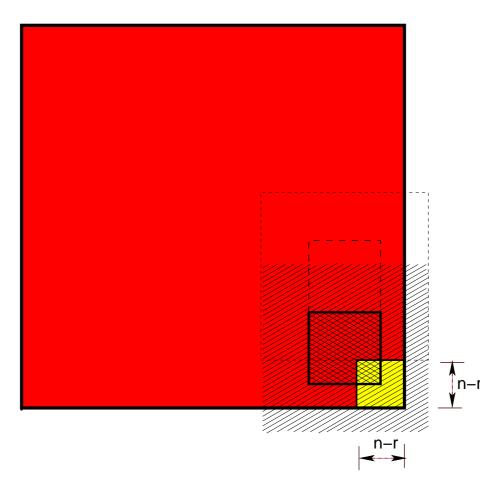

| 6.21 | Tile only input for row major ordering                                                                        | 67 |

| 6.22 | Tile only input for diagonal ordering                                                                         | 68 |

| 7.1  | The 3-stage pipeline model                                                                                    | 69 |

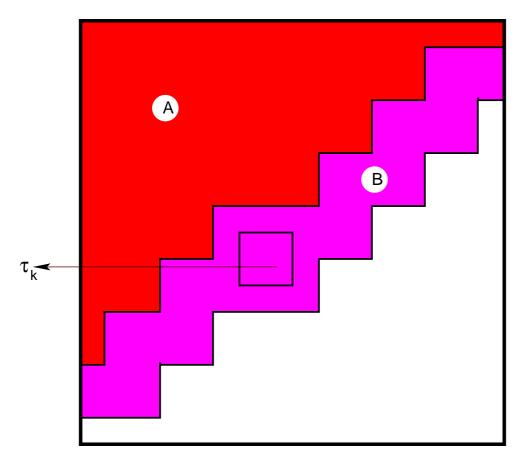

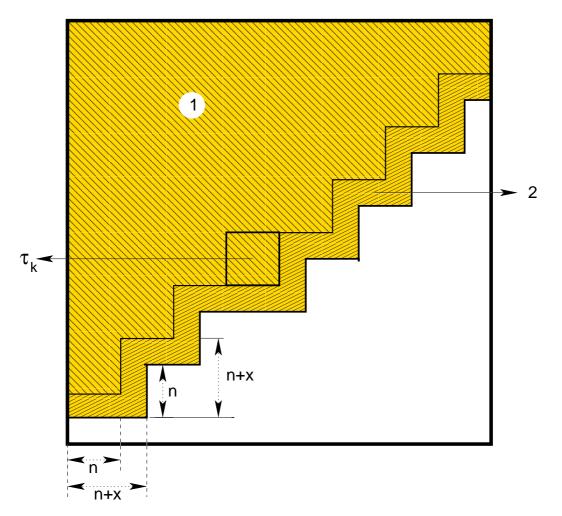

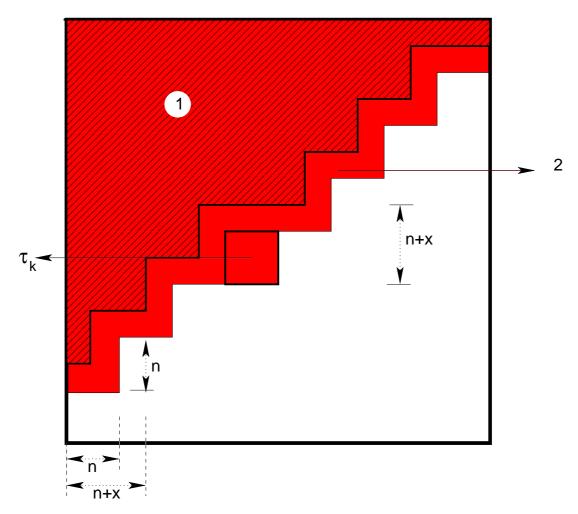

| 7.2  | Total data received                                                                                           | 74 |

| 7.3  | Regions of total data received                                                                                | 75 |

| 7.4  | Data that is not needed further                                                                               | 76 |

| 7.5  | Memory requirement for Diagonal Ordering                                                                      | 77 |

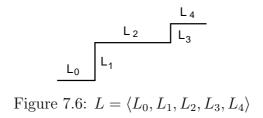

| 7.6  | $L = \langle L_0, L_1, L_2, L_3, L_4 \rangle  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots $ | 78 |

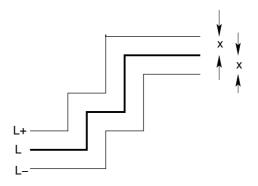

| 7.7  | x-border of $L$                                                                                               | 78 |

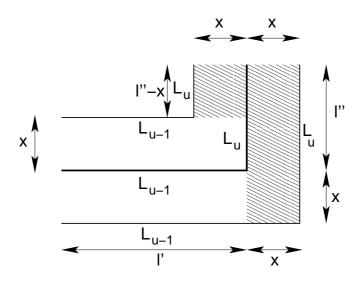

| 7.8  | Area details of $x$ -border of $L$                                                                            | 79 |

| 7.9  | The memory requirement for Diagonal Ordering                                                                  | 80 |

| 7.10 | The memory requirement for Diagonal Ordering                                                                  | 81 |

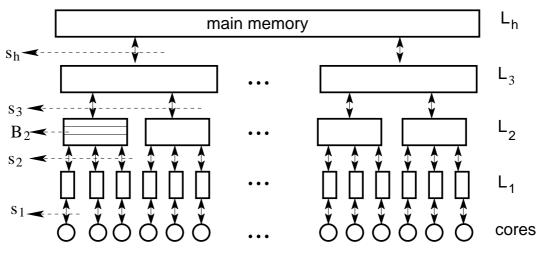

| 8.1  | Hierarchical Multi-Level-Cache (HM) Model                                                                     | 85 |

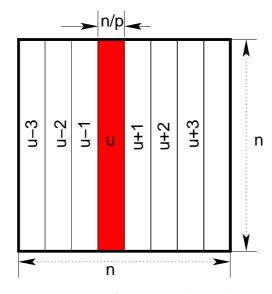

| 8.2  | Accessing local data                                                                                          | 87 |

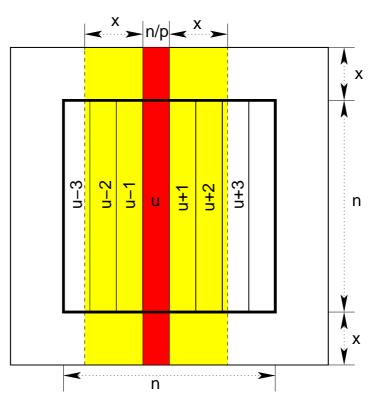

| 8.3  | Accessing the neighborhood data                                   | 90 |

|------|-------------------------------------------------------------------|----|

| 9.1  | A two-chip pipeline                                               | 95 |

| 10.1 | Splitting the data at Stage $S_0$ for Stage $S_1$ and Stage $S_3$ | 99 |

# List of Tables

| 2.1 | The time complexities of different stages                                              | 14 |

|-----|----------------------------------------------------------------------------------------|----|

| 3.1 | The time values in the Table                                                           | 18 |

| 7.1 | The number of SIFT operations for an $n^2$ pixel tiles                                 | 72 |

| 8.1 | The number of SIFT operations required for a subtile                                   | 92 |

| 9.1 | The number of SIFT operations on a Uniprocessor Chip                                   | 96 |

| 9.2 | The number of SIFT operations on a $P$ -core Chip $\ldots \ldots \ldots \ldots \ldots$ | 96 |

### Abstract

In this thesis we study the running of the Scale Invariant Feature Transform (SIFT) algorithm on a pipelined computational platform. The SIFT algorithm is one of the most widely used methods for image feature extraction.

We develop a tile based template for running SIFT that facilitates the analysis while abstracting away lower-level details. We formalize the computational pipeline and the time to execute any algorithm on it based on the relative times taken by the pipeline stages. In the context of the SIFT algorithm, this reduces the time to that of running the entire image through a bottlenecked stage and the time to run either the first or last tile through the remaining stages. Through an experimental study of the SIFT algorithm on a broad collection of test images, we determined image feature fraction values, that relate the sizes of the image extracts as it the computation proceeds through the stages of the SIFT algorithm.

We show that for a single chip uniprocessor pipeline, the computational stage is the bottleneck. Specifically we show that for an  $N \times N$  image with  $n \times n$  tiles the overall time complexity is  $\Theta\left(\frac{(n+x)^2}{p_i}\Gamma_0 + \alpha\beta N^2 x^2\Gamma_1 + \frac{(\alpha\beta + \gamma)n^2\log x}{p_o}\Gamma_2\right)$ ; here x is the neighborhood of the tile,  $p_i, p_o$  are the number of input, output pins of the chip,  $\alpha, \beta, \gamma$  are the feature fractions, and  $\Gamma_0, \Gamma_1, \Gamma_2$  are the input, compute, output clocks. The three terms in the expression represents the time complexities of input, compute and output stages. The input and output stages can be slowed down substantially without appreciate degradation of the overall performance. This slowdown can be traded off for lower power and higher signal quantity.

For multicore chips, we show that for an  $N \times N$  image on a *P*-core chip, the overall time complexity to process the image is  $\Theta\left(\frac{N^2}{p_i}\Gamma_0 + \frac{(n^2w^2 + \alpha\beta n^2x^2)}{P}\Gamma_1 + \frac{(\alpha\beta + \gamma)n^2\log x}{p_o}\Gamma_2\right)$ ; in addition to the quantities described earlier w is the window size used for the Gaussian blurring. Overall we establish that without improvements in the input bandwidth, the power of multicore processing cannot be used efficiently for SIFT.

### Chapter 1

### Introduction

The speed of processors has increased exponentially in modern systems but the rate at which data enters and exits a processor has not kept up with this increase. This is because while technological improvements have been able to keep pace with Moore's law for many decades, the physical size of input/output pins of a chip cannot be reduced beyond a point due to mechanical stability reasons. Jordon [12] presents a comparative chart of number of transistors and pins in Intel chips over the last 20 years. While the number of transistors has gone up by a factor of 20000, the number of pins has increased only by a factor of 30 during the same period. Three-dimensional stacking [2] [5] that allows better connectivity within chips and optical input/output [26] are promising future possibilities.

Currently, applications requiring high input/output bandwidth are mostly executed on a single chip environment. This is not because there is not enough computational need to spread the algorithm across chips, but because its not economical for the data to leave a chip and go to the next. As a result, one cannot exploit the benefits of high parallelism that result in better speeds and more sustainable use of power. Applications that deal with image and video processing (particularly those with real time constraints) require large input/output bandwidth. It is one of these applications that we study in this thesis.

We study the scale invariant feature transform (SIFT) algorithm [13] that extracts features of an image in a manner that is stable over image translation, rotation, scaling, illumination and camera viewpoint. We have selected SIFT as it is one of the most widely used algorithms for object recognition, that has been employed in many applications such as face/object recognition [13] [14] [15], robot localization and mapping [16], 3D-scene modelling, and action recognition [3]. SIFT accepts an  $N \times N$  image as input and produces a set of features. The input bandwidth of  $N^2$  pixels can be very high for large values of N (modern household cameras produce images with  $N^2$  is more than 10M so  $N \ge 1000$  is not unreasonable).

In this thesis we develop a c-chip (or (2c+1)-stage) pipeline as a basic platform to which we execute the SIFT algorithm for an  $N \times N$  image. It should be pointed out that this work focuses on running SIFT on the pipeline platform, rather that improve the performance of the original algorithm of Lowe [13]. The choice of a pipeline platform suits the structure of SIFT and many real time applications that stream in image data. More specifically, we develop general results for this pipeline and apply this to single- or two-chip (3- or 5-stage) pipeline. Both uniprocessor and multicore chips are considered. We use the single-chip uniprocessor (3-stage) pipeline model as a base and we study the case where the processing platform is a multicore chip. We extend this to a two-chip (5-stage) pipeline model. where each chip could be uniprocessor or multicore. To analyze SIFT in a manner that abstracts lower-level details, we introduce a decomposition of the  $N \times N$  image into smaller  $n \times n$ tiles. We consider two orders in which these tiles are fed as input to the pipeline. The order makes a difference in the processing time for certain cases. We derive expressions for the time and memory complexities for SIFT on a pipeline model. We also study several images each at 20 different resolutions, using the SIFT implementation of Hess [19]. This helps us further refine some of the constraints in the time complexity of SIFT.

This thesis has contributions in many directions. We show that for the uniprocessor case, the input/output bandwidth is not critical, as the computation is the bottleneck. However as we move to a multicore platform, the input/output bandwidth becomes a bottleneck, particularly when the pipeline (sequence of chips) is deeper. Specifically, we show that the time to run SIFT on an image on a uniprocessor pipeline is essentially the time to compute SIFT for the entire image. The only additional contribution due to the input and output stages is the time to input the first tile and the time to output the features of the last tile (these are very small fractions of the image). As we move to the multicore platform, the time to run SIFT essentially equals the time to input the image. The additional times due the compute and output stages are only the times for computation and feature output of the last tile (again a very small fraction of the image). In the uniprocessor case, the computation time is the bottleneck and other stages (input and output) idle much of the time. As the number of cores increases, the input is the bottleneck and cores begin to idle. We also develop general results for the running time on a c-chip pipeline which may be of independent interest.

The results we develop in this work also point to directions in which the performance of SIFT can be improved when run on the pipeline model. In the single-chip uniprocessor case, where the input is not a bottleneck, one could slow the input clock rate to save power or transmit additional bits to improve the bit error rate without affecting the overall time. In the multicore case, the full computational power of multicore chips cannot be used unless

the input bandwidth is improved.

Recent research on SIFT has followed many directions including parallel implementation and optimization, application areas and modifications to the SIFT technique of Lowe [13]. Sinha et al. [22] and Heymann et al. [8] proposed SIFT implementation on GPUs. Wen et al. [23] proposed a CUDA based implementation for a GPU framework and analyzed its parallelism. Ko et al. [11] analyzed the performance and cost of SIFT for visual classification and he discussed tradeoffs among system parameters that affect the energy, accuracy and latency. Nasir et al. [7] proposed a method that improves SIFT. Lin et al. [27] proposed a tracking method using SIFT for recording the trajectory of the human motion in an image sequence. Mikolajczyk and Schmid proposed gradient location-orientation histogram (GLOH) [17] as an extension of the SIFT descriptor designed to increase its robustness and distinctiveness. Zhong et al. [24], presented an improvement on the basic SIFT that is geared toward palmprint recognition. Shekar et al. [21] proposed improved descriptor representation in the face recognition context. Zhang et al. [28] proposed two parallel SIFT algorithms and presented some optimization techniques to improve the performance on multicore systems. However their results focus less on the analysis for a general model such as the HM model [4] that we consider. We are not aware of any work similar to this one that theoretically analyzes the performance of SIFT on a general pipeline platform including uniprocessor and multicore chips.

The remainder of this thesis is organized as follows. In Chapter 2, we explain the major phases of the SIFT algorithm and analyze it to determine the number of operations needed to perform these phases. In Chapter 3, we describe experiments involving running SIFT on different images to further refine our theoretical analysis of the running time of SIFT. We also introduce the concept of feature fractions in this chapter that play an important part of subsequent analysis. In Chapter 4, the two tile ordering methods are introduced (row major and diagonal). In Chapter 5, we describe the pipeline model. Chapter 6, is devoted to an analysis of the input complexity of SIFT. In Chapter 7, we derive the expressions for time and memory to run SIFT on a single-chip uniprocessor pipeline model. We extend this in Chapter 8, to a single-chip multicore pipeline. In Chapter 9, a two-chip model is considered where each chip can be single or multicore. Finally in Chapter 10, we summarize the work and identify directions for future research.

### Chapter 2

### Scale Invariant Feature Transform

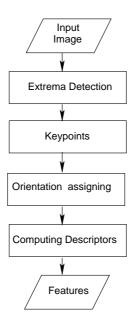

In this chapter we briefly discuss the Scale Invariant Feature Transform (SIFT) algorithm introduced by Lowe [13]. This algorithm is one of the most widely used one for image feature extraction. SIFT extracts image features, that are stable over image translation, rotation and scaling and somewhat invariant to changes in the illumination and camera viewpoint. The SIFT algorithm has four major phases (as illustrated in Figure 2.1) (a) Extrema Detection, (b) Keypoint Localization, (c) Orientation Assignment, (d) Keypoint Descriptor Generation. The first phase, Extrema Detection, examines the image under various scales and octaves (explained in detail later) to isolate points of the picture that are different from their surroundings. These points, called *extrema*, are potential candidates for image features.

The next phase, Keypoint Detection, starts with the extrema and selects some of these points to be *keypoints*, that are a whittled down a set of feature candidates. This refinement rejects extrema, that are caused by edges of the picture and by low contrast points.

The third phase, Orientation Assignment, converts each keypoint and its neighborhood into a set of vectors by computing a magnitude and a direction for them. It also identifies other keypoints that may have been missed in the first two phases; this is done on the basis of a point having a significant magnitude without being an extremum. The algorithm now has identified a final set of keypoints.

The last phase, Keypoint Descriptor Generation, takes a collection of vectors in the neighborhood of each keypoint and consolidates this information into a set of eight vectors called the *descriptor*. Each descriptor is converted into a feature by computing a normalized sum of these vectors.

Figure 2.1: Major phases of the SIFT algorithm

### 2.1 Flow of Data in SIFT

In this section, we describe the nominal number of data items traversing each phase of the SIFT algorithm. This is used later to determine the algorithm complexity and in the experimental study (see Chapter 3). Recall that the Extrema Detection and Keypoint Detection phases reduce the number of feature candidates. The Orientation Assignment phase potentially adds points to this number of feature candidates.

The input to the SIFT algorithm is a set of  $N^2$  pixels of an  $N \times N$  image. Only a small fraction of these pixels typically turn out to be extrema. Let  $0 < \alpha < 1$  be this fraction. So  $\alpha N^2$  extrema will move on to the next Keypoint Detection phase. Only a small fraction of these extrema will qualify as keypoints. Let  $0 < \beta < 1$  be this fraction. So nominally there are  $\alpha\beta N^2$  keypoints at this stage. Orientation assignment reexamines all the  $N^2$  points in the image to check if any points of significant magnitude have been missed. If so, they are added to the set of keypoints. Let a fraction  $\gamma$  of the image pixels qualify to be these added keypoints. That is,  $\gamma N^2$  new keypoints are added. The Compute Descriptors phase converts these points into vectors which are then turned into features. The number of feature descriptors output by SIFT algorithm is nominally  $(\alpha\beta + \gamma)N^2$  for an  $N \times N$  image. We call the quantities  $\alpha$ ,  $\beta$  and  $\gamma$  as feature fractions.

While  $\alpha$ ,  $\beta$  and  $\gamma$  will depend on the picture in question, we will consider nominal values

averaged over many pictures to guide this work. This part of the study is described in Chapter 3. In the remaining sections of this chapter, we describe the major four phases of SIFT in detail.

#### 2.2 Scale-Space Extrema Detection

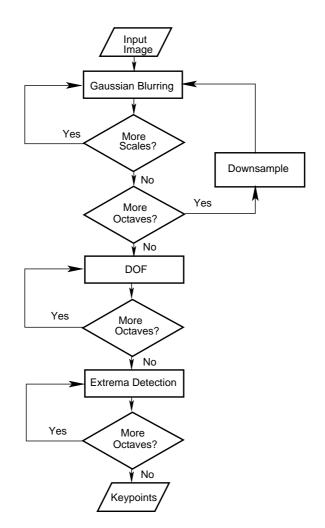

This is the first phase of the SIFT algorithm. Here the algorithm identifies the points that are stable with respect to image rotation, translation and those that are minimally affected by noise and small distortions. Detecting these points can be accomplished by searching for stable features across all possible scales (defined below). Figure 2.2 shows the internal stages of the Extrema Detection phase. The algorithm compute "scale," "difference of gaussians," and "extrema" over several "octaves." We now discuss these ideas, before explaining the order in which they are computed.

**Scale:** Let *I* be an  $N \times N$  image and for  $0 \le x, y < N$ , let  $G(x, y, \sigma) = \frac{1}{2\pi\sigma^2} e^{-\frac{x^2+y^2}{2\sigma^2}}$  be the discrete two-dimensional Gaussian function. Then the *scale* of the image *I* is defined as  $L(\sigma) = \{ G(x, y, \sigma) * I(x, y) : 0 \le x, y < N \}$  where \* is the two-dimensional convolution operation and I(x, y) is the pixel at row *x* and column *y* of image I(x, y).

In general, the  $k^{th}$  scale of the image, for  $k \ge 1$  is defined as  $L(k\sigma) = \{ G(x, y, k\sigma) * I(x, y) : 0 \le x, y < N \}$ . For each image point I(x, y), the scale is computed by applying a scalar product between the point I(x, y) and a  $w \times w$  Gaussian weighted window placed over that point. For example, suppose that point I(x, y) is the central point  $i_{0,0}$  of the  $5 \times 5$  window shown in Figure 2.3(a). The figure also shows the pixel values of the  $5 \times 5$  neighborhood of this point. If  $\sigma = \sqrt{2}$  and w = 5, then the Gaussian filter G(u, v) can be shown to be the one in Figure 2.3 (b). Applying this filter to the central point is computing the quantity

$$G(i_{0,0}) = 0.001 * i_{-2,2} + 0.003 * i_{-1,2} + \dots + 0.145 * i_{0,0} + \dots + 0.003 * i_{1,-2} + 0.001 * i_{2,-2}$$

In general for a  $w \times w$  window with odd w, the image points located around the point I(x, y) are I(x + u, y + v) where  $-\frac{w-1}{2} \le u, v \le \frac{w-1}{2}$ . Here the scale of I(x, y) is

$$L(x, y, \sigma) = \sum_{u = -\frac{w-1}{2}}^{\frac{w-1}{2}} \sum_{v = -\frac{w-1}{2}}^{\frac{w-1}{2}} G(u, v) I(x + u, y + v)$$

Figure 2.2: The internal stages of Scale-Space Extrema Detection

Thus, computing scale for each point I(x, y) requires  $w^2$  multiplications and  $w^2-1$  additions which has  $\Theta(w^2)$  complexity. For the entire  $N \times N$  image the complexity for this step is  $\Theta(w^2N^2)$ .

Let  $s \ge 1$  be an integer and  $k = 2^{\frac{1}{s}}$ . The SIFT algorithm repeatedly computes the scale of the image as described below.

Let  $\sigma_0$  be the initial value of  $\sigma$  in the Gaussian filter. Define  $\sigma_i = k^i \sigma$  for  $0 \le i < s + 3$ . Let  $L_0^0 = I$  be the original image (the superscript is explained later). For image element I(x, y), define  $L_{i+1}^0(x, y) = G(x, y, \sigma_i) * L_i^0(x, y)$  where  $0 \le i < s + 3$ . In this fashion the

| <i>i</i> <sub>-2,2</sub>  | $i_{-1,2}$  | $i_{0,2}$  | $i_{1,2}$  | $i_{2,2}$  |

|---------------------------|-------------|------------|------------|------------|

| $i_{-1,2}$                | $i_{-1,2}$  | $i_{0,1}$  | $i_{1,1}$  | $i_{1,2}$  |

| <i>i</i> <sub>0,-2</sub>  | $i_{0,-1}$  | $i_{0,0}$  | $i_{0,1}$  | $i_{0,2}$  |

| <i>i</i> <sub>-1,-2</sub> | $i_{-1,-2}$ | $i_{0,-1}$ | $i_{1,-1}$ | $i_{1,-2}$ |

| <i>i</i> <sub>-2,-2</sub> | $i_{-1,-2}$ | $i_{0,-2}$ | $i_{1,-2}$ | $i_{2,-2}$ |

| 0.001 | 0.003 | 0.004 | 0.003 | 0.001 |

|-------|-------|-------|-------|-------|

| 0.003 | 0.008 | 0.113 | .008  | 0.003 |

| 0.004 | 0.113 | 0.145 | 0.113 | 0.004 |

| 0.003 | 0.008 | 0.113 | 0.008 | 0.003 |

| 0.001 | 0.003 | 0.004 | 0.003 | 0.001 |

(a) Pixel Values

(b) Gaussian window

Figure 2.3: An example of applying a  $5 \times 5$  Gaussian window on a point

algorithm computes the scales as shown below (also see Figure 2.4).

$$L_0^0 \xrightarrow{G_{\sigma}} L_1^0 \xrightarrow{G_{\sigma_1}} L_2^0 \cdots \xrightarrow{G_{\sigma_s}} L_{s+1}^0 \xrightarrow{G_{\sigma_{s+1}}} L_{s+2}^0 \xrightarrow{G_{\sigma_{s+2}}} L_{s+3}^0$$

(2.1)

**Octaves:** The sequence of scales in Equation (2.1) is called an *octave*. As discussed above we computed  $L_{s+1}^0$  as part of the first octave. This is a blurred image from the original image I. The next step requires a reduction in image resolution. The resolution of an image can be reduced<sup>1</sup> by a factor of 2 in each dimension by sampling every other pixel of the image in a checkerboard pattern. Let  $L_0^1$  be  $L_{s+1}^0$  reduced in resolution by a factor of 2 (the superscript j here denotes Octave 1 for  $L_0^1$  and Octave 0 for  $L_{s+1}^0$ ).

We now define a new octave (second octave) analogous to the Octave 0 (see Equation (2.1)).

$$L_0^1 \xrightarrow{G_{\sigma}} L_1^1 \xrightarrow{G_{\sigma_1}} L_2^1 \cdots \xrightarrow{G_{\sigma_s}} L_{s+1}^1 \xrightarrow{G_{\sigma_{s+1}}} L_{s+2}^1 \xrightarrow{G_{\sigma_{s+2}}} L_{s+3}^1$$

(2.2)

If there are  $\hat{s}$  octaves, then in general for  $0 < j \leq \hat{s} - 1$ ,  $L_0^j$  is  $L_{s+1}^{j-1}$  reduced in resolution by a factor of 2 in each dimension and

$$L_0^j \xrightarrow{G_{\sigma}} L_1^j \xrightarrow{G_{\sigma_1}} L_2^j \cdots \xrightarrow{G_{\sigma_s}} L_{s+1}^j \xrightarrow{G_{\sigma_{s+1}}} L_{s+2}^j \xrightarrow{G_{\sigma_{s+2}}} L_{s+3}^j$$

(2.3)

The time complexity for computing all (s + 3) scales of the image over one octave is

<sup>&</sup>lt;sup>1</sup>Image resolution can be reduced in other ways, example averaging over a  $2 \times 2$  pixel set.

$\Theta\left(N^2w^2(s+3)\right) \text{ and repeating this for } \hat{s} \text{ octaves gives a time complexity of } \Theta\left(\sum_{j=0}^{\hat{s}-1} \frac{N^2}{2^j}w^2s\right) \\ = \Theta\left(N^2ws\right) \text{ where the down sampling needed to start each octave requires another } \Theta\left(\frac{N^2}{2^j}\right) \\ \text{ operations. Therefore the overall complexity of this phase is } \Theta\left(N^2w^2s\right). \text{ Considering constants and unit time for all operations, this phase requires approximately } 4N^2w^2s \text{ time.}$

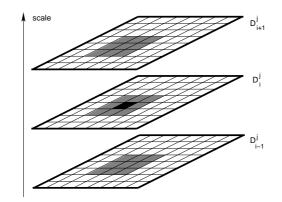

**Difference of Gaussians:** At this point, we have (s + 3) scales  $L_i^j$  over all  $\hat{s}$  octaves where  $0 \le i < s + 3$  and  $0 \le j < \hat{s}$ . For any fixed octave j and  $0 \le i < s + 2$ , define the  $i^{th}$  difference of Gaussians over octave j as:

$$D_i^j = L_{i+1}^j - L_i^j$$

where the difference is for each pair of corresponding pixels  $L_{i+1}^j(x,y)$  and  $L_i^j(x,y)$ . Figure 2.4 illustrates these ideas.

The scales in octave j are  $\frac{N}{2^j} \times \frac{N}{2^j}$  images. Then each of  $L_{i+1}^j$  and  $L_i^j$  is an  $\frac{N}{2^j} \times \frac{N}{2^j}$  image and so computing  $D_i^j$  requires finding  $\frac{N^2}{2^j}$  differences. Thus, computing all s + 2 difference of Gaussians in octave j requires  $\frac{(s+2)N^2}{2^j} = \Theta\left(\frac{sN^2}{2^j}\right)$  units of time. The complexity to compute this quantity across all  $\hat{s}$  octaves is  $\Theta\left(\sum_{j=0}^{\hat{s}-1} \frac{sN^2}{2^j}\right) = \Theta(sN^2)$ . With normally used values of SIET parameters, the number of operations is approximately  $4N^2s$ .

of SIFT parameters, the number of operations is approximately  $4N^2s$ .

**Extrema Detection:** Suppose that we have the sets  $D_{i-1}^j$ ,  $D_i^j$ ,  $D_{i+1}^j$  of difference of Gaussian images in an octave j. For each octave j where  $0 \leq j < \hat{s}$  and for 1 < i < s + 2, place the difference of gaussians  $D_{i-1}^j$ ,  $D_i^j$ ,  $D_{i+1}^j$  in three adjacent layers (as shown in Figure 2.5). Now element  $D_i^j(x, y)$  (shown in Figure 2.5 as a dark square) has 26 neighboring difference of Gaussian elements (as shown as gray squares in Figure 2.5). Element  $D_i^j(x, y)$  is an *extremum* iff it is strictly larger (in pixel value) than all of the neighboring elements or it is strictly smaller than all of the neighboring elements.

Detecting whether  $D_i^j(x, y)$  is an extremum takes at most 26 comparisons each requiring constant time. For all elements of  $D_i^j$  in an octave j, the time needed is  $\Theta\left(\frac{N^2}{2^j}\right)$ . For all difference of Gaussians over all  $\hat{s}$  octaves, the time needed is  $\Theta\left(\sum_{j=0}^{\hat{s}-1} \frac{(s+2)N^2}{2^j}\right) = \Theta(sN^2)$ . Taking the proportionality constant into the account the overall complexity

Figure 2.4: Scale, octaves and difference of Gaussians

can be shown to be approximately  $104sN^2$ . As discussed earlier we nominally have  $\alpha N^2$  extrema at this point of the algorithm.

Before we proceed to the next phase (Keypoint Detection), we touch upon how the Scalespace Extrema Detection phase is executed. As we noted in this section, the algorithm determines, scales (see Section 2.2), difference of Gaussians (see Section 2.2), and extrema (see Section 2.2) independently for  $\hat{s}$  octaves. Thus, it is possible to have an outer loop over octaves and determine the other quantities one after the other within this outer loop (see Figure 2.2). However each of these (scales, difference of Gaussians, extrema) have relatively local dependencies. That is, to determine the scale of a point, one needs to know only the  $w \times w$  neighborhood of the point. To determine the difference of Gaussian, we only need two corresponding points and to check whether a point is extremum, we only need

Figure 2.5: Extrema detection on octave j

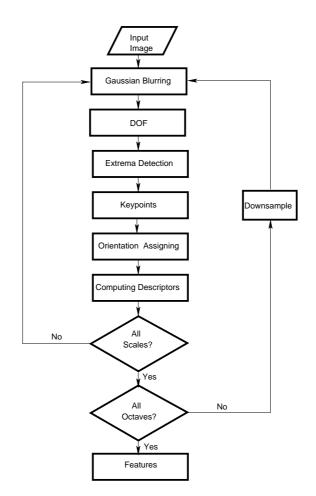

26 difference of Gaussians points spread over three scales around it. Thus, it is possible to execute these operations over octaves in many different ways. The original algorithm of Lowe [13] use the structure in shown in Figures 2.2. The program we used [19] for this work uses the modified flow of algorithm [28] as shown in Figure 2.6.

### 2.3 Keypoint Detection

Recall that the algorithm first determines  $\alpha N^2$  extrema and then further distills them into  $\alpha\beta N^2$  keypoints, that will ultimately become keypoints of the image. In this section, we discuss the phase of selection of keypoints from extrema. The Scale-Space Extrema Detection phase of the algorithm identifies  $\alpha N^2$  potential candidates for keypoints. Some of these candidates may lie along an edge of the image or may corresponds to points of low contrast. These are generally not useful as features as they are unstable over image variation [13]. Hence these points are rejected. For rejecting low contrast points, each extremum is examined using a method that involves solving a system of  $3 \times 3$  linear equations and so it takes constant time. To detect the extrema on edges, a  $2 \times 2$  matrix is generated and simple computations performed on it (including finding the determinant and the trace of  $2 \times 2$  matrix all requiring  $\Theta(1)$  time), to generate a ratio of principle of curvatures. This quantity is simply compared with a threshold value to decide whether an extremum is to be rejected or not. Thus, this phase runs in  $\Theta(\alpha s N^2)$  time over all octaves. Considering constants into the account this phase takes approximately  $100s\alpha N^2$  operations.

After the elimination of extrema points, the points that remain are called *keypoints*. We now nominally have  $\alpha\beta N^2$  keypoints.

Figure 2.6: Restructured SIFT algorithm flow of data

### 2.4 Orientation Assignment

The nominal number of keypoints at the start of this phase is  $\alpha\beta N^2$ . This phase adds to the set of keypoints (those that may be missed in the previous phases) on the basis of their magnitude and orientation. The magnitude  $m_i^j(x, y)$  and orientation  $\theta_i^j(x, y)$  for each point  $L_i^j(x, y)$  can be calculated as follows:

$$m_i^j(x,y) = \sqrt{(L_i^j(x+1,y) - L_i^j(x-1,y))^2 + (L_i^j(x,y+1) - L_i^j(x,y-1))^2}$$

$$\theta_i^j(x,y) = \tan^{-1} \frac{(L_i^j(x,y+1) - L_i^j(x,y-1))}{(L_i^j(x+1,y) - L_i^j(x-1,y))}$$

Non-keypoint points whose magnitudes are close to the peak magnitude are added as new keypoints. The number of points examined is  $N^2 - \alpha\beta N^2 \cong N^2$  as  $\alpha$  and  $\beta$  are small fractions. Of these, a fraction  $\gamma$  are added back. Thus, the total number of keypoints at the end of this phase is  $\alpha\beta N^2 + \gamma (N^2 - \alpha\beta N^2) = \alpha\beta N^2(1-\gamma) + \gamma N^2 \cong N^2 (\alpha\beta + \gamma)$  again because  $\gamma$  is a small fraction. Clearly the computation for  $m_i^j(x, y)$  and  $\theta_i^j(x, y)$  can be done over constant time. The overall complexity for all points over all octaves is  $\Theta(sN^2)$ . Considering the constants, the number of operations is approximately  $48sN^2$

### 2.5 Keypoint Descriptor Generation

In this phase, the algorithm computes a descriptor for each keypoint identified so far. The descriptor is a collection of information in an  $2x \times 2x$  neighborhood of the keypoint (the work of Lowe [13] considers a  $16 \times 16$  neighborhood, which we generalize to  $2x \times 2x$ ). The following tasks are undertaken for each keypoint.

- The magnitudes of all the points in the neighborhood are smoothed by a normalized Gaussian filter with  $\sigma = x$ . This requires  $\Theta(x^2)$  multiplications for each point.

- The neighborhood is divided into  $4 \times 4$  regions. In each region the vectors (magnitude and direction of points) are histogrammed into 8 buckets covering 360° using trilinear interpolation [13]. Again this requires  $\Theta(x^2)$  time for the neighborhood.

- The feature is computed from these descriptors in the neighborhood by computing a normal of the descriptors in the neighborhood.

- The resulting descriptor is represented as an normalized  $\frac{x}{2} \times \frac{x}{2}$  descriptor array each with an 8 bucket histogram of vectors. Thus, the feature is  $\log_2 \frac{8x^2}{4} = 2\log x + 1$  bits long.

As the time complexity is  $\Theta(x^2)$  for each keypoint identified so far, then the overall time complexity for all the keypoints is  $\Theta(x^2(\alpha\beta + \gamma)N^2)$ . Considering the constants<sup>2</sup>, the number of operations is approximately  $1520x^2(\alpha\beta + \gamma)N^2$ .

The overall time complexity of the SIFT algorithm is determined from the complexities of the phases discussed so far. This is shown in Table 2.1.

$<sup>^2\</sup>mathrm{For}$  this phase the constants were obtained through the experiments described in Chapter 3

Figure 2.7: Keypoint descriptor generation

Table 2.1: The time complexity and the number of operations required by the different phases of the SIFT algorithm for  $N^2$  pixels

| Phase                          | Complexity                                           | Number of operations             |

|--------------------------------|------------------------------------------------------|----------------------------------|

| Gaussian Blurring              | $\Theta\left(N^2 w^2 s\right)$                       | $4N^2w^2s$                       |

| Difference of Gaussian         | $\Theta\left(sN^2\right)$                            | $4N^2s$                          |

| Scale-space Extrema Detection  | $\Theta\left(sN^2\right)$                            | $104 s N^2$                      |

| Keypoint Detection             | $\Theta\left(\alpha s N^2\right)$                    | $100s\alpha N^2$                 |

| Orientation Assignment         | $\Theta\left(sN^2(1-\alpha\beta)\right)$             | $48 s N^{2}$                     |

| Keypoint Descriptor Generation | $\Theta\left(x^2 N^2 (\alpha \beta + \gamma)\right)$ | $1520x^2(\alpha\beta+\gamma)N^2$ |

### Chapter 3

### **Experimental Study**

The purpose of this chapter is to experimentally study the time requirement for different phases of the SIFT algorithm and to detect, if possible, any trend in the values of feature fractions  $\alpha$ ,  $\beta$  and  $\gamma$  (see Section 2.1). We performed this study using a SIFT implementation by Hess [19]. In Section 3.1, we describe the pictures used in our study, in Section 3.2 we discuss the time taken by the different phases of the SIFT algorithm and in Section 3.3 we describe the feature fraction values used in this work.

#### 3.1 Images Used in Study

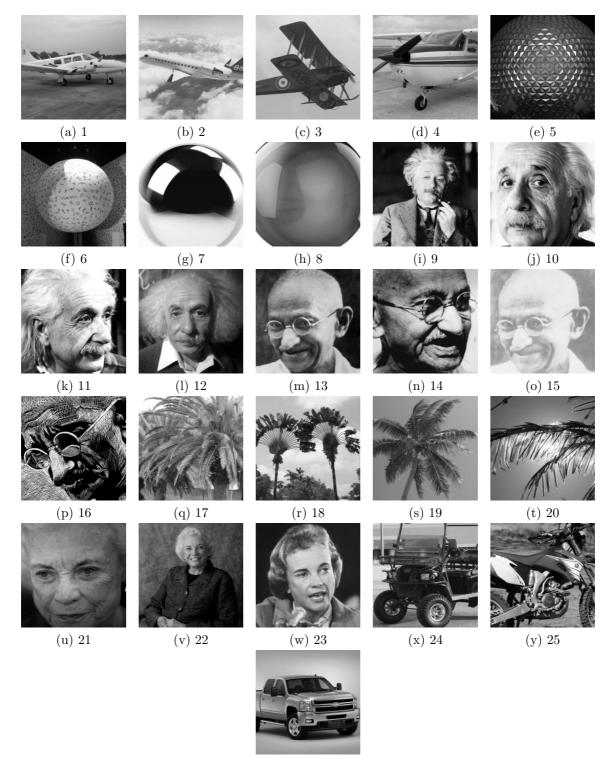

We selected a range of pictures (see Figure 3.1) to test the SIFT algorithm. These pictures were obtained from the Internet [30]-[54].

Images fall in the following categories.

- 1. Airplanes (four pictures)

- 2. Spheres (four pictures)

- 3. Portraits (four pictures each of Einstein and Gandhi, and three pictures of Sandra Day O'Connor)

- 4. Vehicles (three pictures)

- 5. Palm-like trees (four pictures)

The pictures represent a variety of themes with enough elements within each category to facilitate detection of patterns. Each picture was converted into a gray scale portable network graphics (PNG) image with  $2000 \times 2000$  pixels. We also considered 19 reduced resolutions of each original picture. These resolutions are at  $1900 \times 1900$ ,  $1800 \times 1800$ ,  $\cdots$ ,  $100 \times 100$ . Thus we have 26 "pictures," each at 20 resolutions, totalling 520 "images" in the study. We use the term "image" to represent any of these 520 elements. The term "picture" is used for the 26 sets, each of 20 images of varying resolutions. Figure 3.1 shows a representative picture of each of these sets.

#### **3.2** Time Taken by Different Phases

The SIFT implementation [19] that we used in this work is a large piece of code (over 2500 lines) with several calls to routines, including openCV [18] functions whose code is not explicitly available in the program. This makes it virtually impossible to trace through all parts of the code to determine their execution times.

Our first aim is to identify the major parts of the code that fit a sequential pipeline (see Chapter 5). We do not wish to separately consider functions that are called by multiple parts of the program. We proceed as follows.

- (a) We introduce a "level counter" that is initialized to zero and incremented every time a function is called. The counter is decremented each time a function returns to the calling function. Functions with multiple levels of invocation can immediately be excluded for our consideration.

- (b) Functions with very small execution times need not be considered separately. These times (even with multiple calls) can typically be rolled into the lines of their parent routines.

- (c) With these two filters we identified the functions shown in Table 3.1 that need separate consideration.

- (d) For each routine in Table 3.1, we modified the SIFT code to record the starting clock time and ending clock time. The time taken by each routine is calculated by finding a difference of these times.

- (e) Of the routines in Table 3.1, create\_init\_img is excluded because it is a preprocessing stage that converts a color image to a gray scale image in PNG format. In our experiments we start with such an image. Routine release\_pyr which related to displaying the output on the screen is also excluded. Of the remaining routines calc\_feature\_scales has a much smaller execution time than the others and

(z) 26

Figure 3.1: Pictures considered

| Routine Name         | Level | Time   | Description                                      |

|----------------------|-------|--------|--------------------------------------------------|

| create_init_img      | 2     | 0.116  | Convert color to grayscale image                 |

| build_gauss_pyr      | 2     | 0.871  | Create scales (see Section 2.2 Page 6)           |

| build_dog_pyr        | 2     | 0.180  | Difference of Gaussians (see Page 9)             |

| scale_space_extrema  | 2     | 1.571  | Extrema and Keypoint detection (see Section 2.3) |

| calc_features_scales | 2     | 0.016  | part of Orientation assignment                   |

| calc_features_oris   | 2     | 2.204  | Orientation assignment (see Section $2.4$ )      |

| compute_ descriptors | 2     | 11.341 | Computing descriptors (see Section 2.5)          |

| release_pyr          | 2     | 0.008  | Related to Display                               |

| _sift_features       | 1     | 16.603 | Sift Routine                                     |

| Main Routine         | 0     | 16.646 | start of main                                    |

Table 3.1: The time values in the table corresponds to the average values of Image 9 (Gandhi 4) over its all resolutions.

functionally can be rolled together with calc\_feature\_oris. Therefore we use only calc\_feature\_oris with the understanding that this also includes calc\_feature\_scales.

We now have the following routines that have a significant time contribution in the overall time of the program. The mnemonics in parenthesis are used in graphics to identify these routines.

- 1. build\_gauss\_pyr (Gauss) [Gaussian blurring]

- 2. build\_dog\_pyr (DoG) [Difference of gaussians]

- 3. scale\_space\_extrema (SSext) [Scale space extrema and keypoint detection]

- 4. calc\_features\_oris (Orien) [Orientation assignment]

- 5. compute<sub>-</sub> descriptors (Descr) [Keypoint descriptor generation]

The above stages are in close correspondence with the main phases of the SIFT algorithm described in Lowe [13].

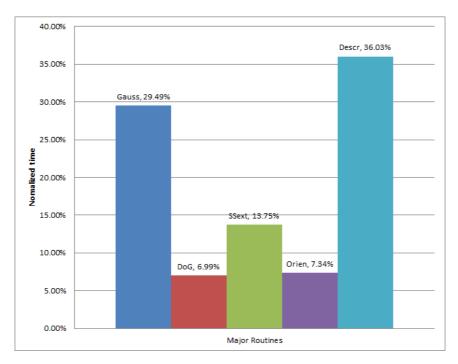

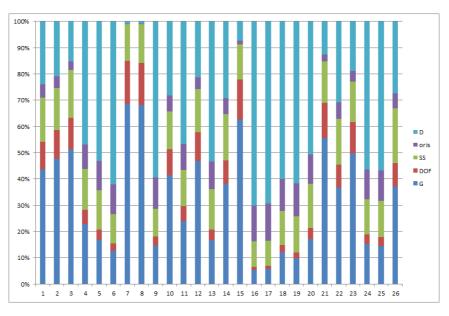

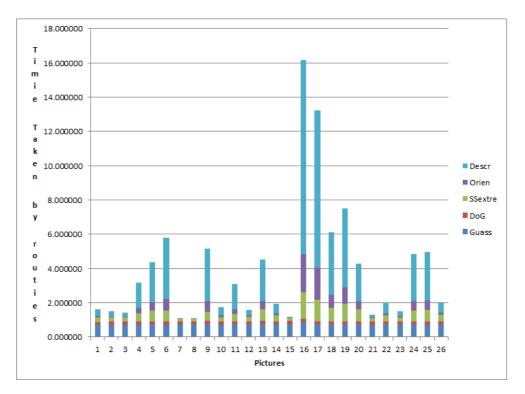

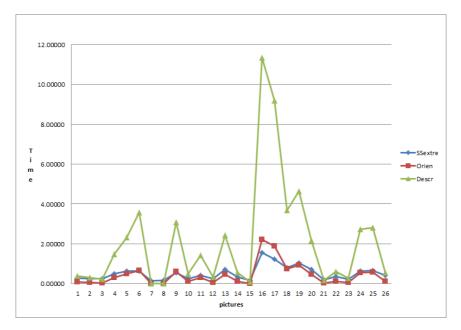

We now examine the behavior of these major phases. Figure 3.2 shows the percentage of the total time taken by the major phases of the SIFT algorithm. The Gaussian phase and Computing Descriptor phase need most of the time (around 70%). Figures 3.3, 3.4 show the normalized and absolute times taken by the different phases of the SIFT algorithm across all the images. The absolute values are averaged over their resolutions. The Gaussian blurring phase and Keypoint descriptor generation phase still take a large amount of time (around

Figure 3.2: Percentage time for major stages of SIFT (averaged over all images)

70%). However there is a large variation in the time taken by Gaussian blurring vis-a-vis the Computing Descriptor phase. This variation also does not seem to be correlated with picture categories.

In this thesis we consider that the Gaussian blurring phase and Keypoint descriptor generation phase are the most time consuming stages (as bases for decoupling the algorithm across chips). These stages also exhibit high parallelism to facilitate efficient execution on multicore chips. In fact for the two chip pipeline mode we assume that Chip 1 consists of phases Gaussian blurring to Keypoint Detection, and Chip2 consists of the Orientation Assignment and keypoint descriptor generation phases.

We now examine how individual phases perform across different pictures.

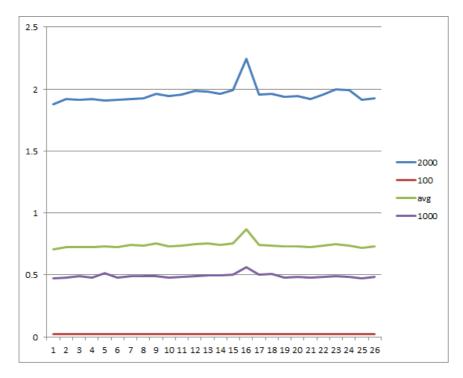

Figure 3.5 shows the time taken by the Gaussian stage for all  $2000 \times 2000$  images (highest resolution),  $1000 \times 1000$  images (intermediate resolution) and  $100 \times 100$  images (lowest resolution). The average time taken by the Gaussian stage across these 20 resolutions is also shown. Notice the strong correlation between times taken for different resolutions. They all indicate a similar pattern. Thus the average over all resolutions of a fixed image is a reasonable indicator for that picture. We will henceforth consider only the average of

Figure 3.3: Percentage time of SIFT major phases over different pictures (averaged over all resolutions)

all image resolutions of each picture.

As Figure 3.5 shows the amount of time taken by the Gaussian blurring stage across all images is almost constant. This is because, all the images have same number of pixels and no distinguishing features have been detected yet. The difference of Gaussians stage also shows the similar behavior (see Figure 3.6).

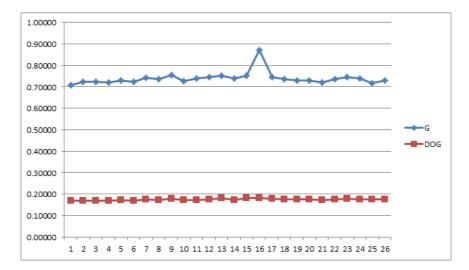

Figure 3.7 shows the Scale-space extrema and keypoint detection phase, Orientation assignment phase and keypoint descriptor generation phase times across pictures. While these times vary largely across pictures, these are correlated within images of a pictures. This is because the times for these stages depend on the number of features in the image.

In this thesis we will consider 1- and 2-chip pipelines for running SIFT (see Chapters 7, 8). As noted earlier for the 2-chip case we will broadly divide the algorithm between the Gaussian blurring phase and keypoint descriptor generation phase. The Gaussian blurring phase takes nearly constant time across pictures, while the keypoint descriptor generation phase does not. To even out these variations, we place the difference of Gaussians phase and scale-space extrema and keypoint detection phases with the Gaussian blurring phase and Orientation assignment phase with the keypoint descriptor generation phase. If additional chips are to be used in the pipeline (future work) then a similar approach can be used to further subdivide the Gaussian blurring phase and keypoint descriptor generation phase.

Figure 3.4: The absolute times of major SIFT phases (averaged over all image resolutions of a picture)

#### **3.3** Feature Fractions

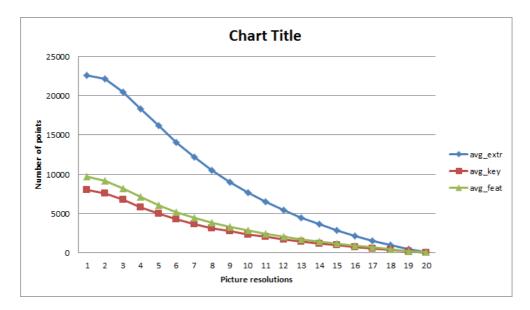

Figure 3.8 shows, for each resolutions size, the number of extrema detected, the number of keypoints and the number of features, averaged over all pictures. Clearly, the number of extrema is more than the number of keypoints, which, in turn, is slightly less than the number of features. This brings us to the idea of feature fractions of an image (see Section 2.1).

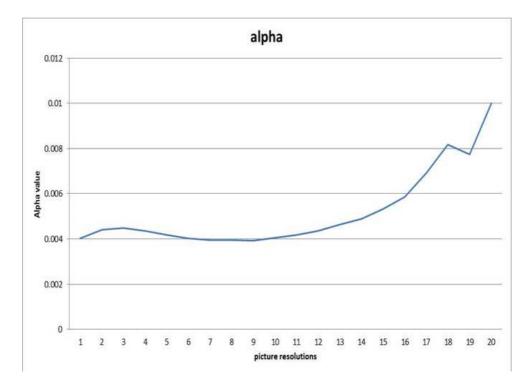

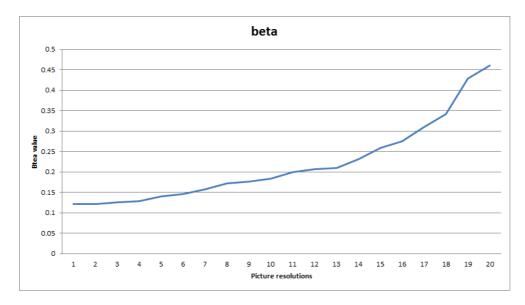

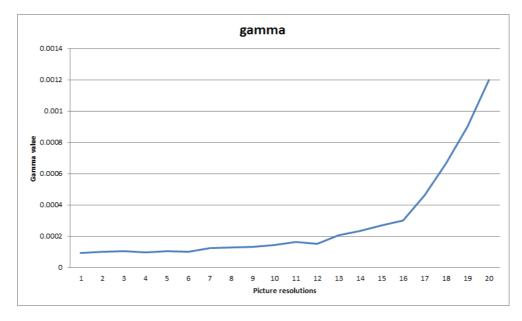

To recap, an  $N^2$  pixel image produces  $\alpha N^2$  extrema,  $\alpha \beta N^2$  keypoints and  $(\alpha \beta + \gamma)N^2$  features. Figures 3.9, 3.10, 3.11 show the values of  $\alpha$ ,  $\beta$  and  $\gamma$  for Picture number 26 (all 20 image resolutions of the picture). In these graphs the number 1-20 on the X-axis represents the 20 resolutions with 1 as the 2000 × 2000 image (largest resolution) and 20 as the 100 × 100 image (smallest resolution). That is, a smaller picture number represents a larger resolution. Notice that  $\alpha$ ,  $\beta$  and  $\gamma$  are nearly constant for large resolutions<sup>1</sup> of the

$<sup>^{1}</sup>$ We give more importance to larger images because parallel SIFT is more useful for large images that require higher speed to keep up with real time constraints

Figure 3.5: The time taken by the Gaussian stage for  $2000 \times 2000$  (the highest resolution),  $1000 \times 1000$  (intermediate resolution) and  $100 \times 100$  (lowest resolution) and the average value over all these resolutions

pictures (left end of the X-axis). Also  $\alpha$ ,  $\beta$  and  $\gamma$  are all small fractions. These observations hold in general over all these pictures. Figures 3.12, 3.13, 3.14 show the values of  $\alpha$ ,  $\beta$  and  $\gamma$  for Pictures 1–25. These graphs are the same as there in Figures 3.9, 3.10, 3.11 expect that the axes are not labeled. Figures 3.15, 3.16, 3.17 show the average values of  $\alpha$ ,  $\beta$  and  $\gamma$ .

From these will assume nominal values of  $\alpha$ ,  $\beta$  and  $\gamma$  around 0.6%, 35% and 0.04% (see Figures 3.15, 3.16, 3.17) for every image considered in this work. In the pictures considered, Picture 16 did not resemble with the remaining pictures, so we took it out from the determination of feature fraction values.

Figure 3.6: Average time for Gaussian blurring and difference of Gaussian phases

Figure 3.7: Times taken for scale-space extrema detection, orientation assignment and keypoint descriptor generation phases

Figure 3.8: Nominal number of extrema, keypoints and features

Figure 3.9: The value of  $\alpha$  for all the image resolutions of picture number 26

Figure 3.10: The value of  $\beta$  for all the image resolutions of picture number 26

Figure 3.11: The value of  $\gamma$  for all the image resolutions of picture number 26

Figure 3.12: The value of  $\alpha$  for all the image resolutions of pictures numbered 1-25

Figure 3.13: The value of  $\beta$  for all the image resolutions of pictures numbered 1-25

Figure 3.14: The value of  $\gamma$  for all the image resolutions of pictures numbered 1-25

Figure 3.15: The value of  $\alpha$  across all the images averaged over their resolutions

Figure 3.16: The value of  $\beta$  across all the images averaged over their resolutions

Figure 3.17: The value of  $\gamma$  across all the images averaged over their resolutions

### Chapter 4

# Tile Ordering

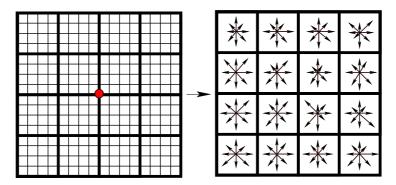

As mentioned earlier, we assume the SIFT algorithm to process  $(n^2)$ -pixel tiles of the image in each iteration. We can process the given image of size  $N \times N$  in one iteration (if n = N) or at the other extreme, we can process one pixel at a time (if n = 1). In general  $1 \gg n \gg N$ . The given image is decomposed into subimages each with  $n^2$  pixels. These subimages are called as *tiles*. For a given image of size  $N \times N$ , there will be a total of  $\xi^2 = \frac{N^2}{n^2}$  tiles. These  $\xi^2$  tiles are provided as input to the computation pipeline (discussed in Chapter 6) one at a time to Stage  $S_0$  of the pipeline.

The order in which the image tiles are sent as an input to the pipeline is called *tile ordering*. This tile ordering plays a major role on the performance of the algorithm where there are restrictions on the input format. In this chapter, we introduce two tile orderings used in the later chapters to analyze the performance of the SIFT algorithm namely *Row Major Ordering* and *Diagonal Ordering*.

The remainder of this chapter is organized as follows. In the Section 4.1, we describe the notation for a tile. In Sections 4.2, 4.3, we describe the two tile orderings.

#### 4.1 Tile Notation

In this section we define some notation for a tile and its numbering in a tile ordering. Each tile is an  $n \times n$  square array of  $n^2$  distinct pixels from the given image. For a given  $N \times N$  image, there will be  $\xi = \frac{N}{n}$  rows and columns of tiles. We refer to this  $\xi \times \xi$  array of tiles as *tile array*. The tiles in this array are represented with two co-ordinates (r, c) denoting

the row r and column c in the tile array. Figure 4.1 shows the tiles coordinates in 5 × 5 tile array. For  $0 \leq i < \xi$ , let  $\tau_{i,j}$  represents the tile at position (r, c). Let  $\odot$  be the given ordering where  $\odot \in \{R, D\}$  (denoting row major and diagonal ordering) then the  $k^{th}$  tile in this ordering is denoted by  $\tau_k^{\odot}$ . If this happens to be the tile in position (r, c) then  $\tau_{r,c}^{\odot}$ . This quantity k associated with tile  $\tau_{r,c}$  with respect to ordering  $\odot$  is called the rank of  $\tau_{r,c}$ , where the ordering  $\odot$  is clear or unimportant, we will write  $\tau_{r,c}^{\odot}$  or  $\tau_k^{\odot}$ , simply as  $\tau_{r,c}$  or  $\tau_k$ .

| (0,0) | (0,1) | (0,2) | (0,3) | (0,4) |

|-------|-------|-------|-------|-------|

| (1,0) | (1,1) | (1,2) | (1,3) | (1,4) |

| (2,0) | (2,1) | (2,2) | (2,3) | (2,4) |

| (3,0) | (3,1) | (3,2) | (3,3) | (3,4) |

| (4,0) | (4,1) | (4,2) | (4,3) | (4,4) |

Figure 4.1: Coordinate representation of tiles in a tile array

### 4.2 Row Major Ordering

As mentioned earlier, this ordering deals with square tiles of size  $n \times n$ . Here the order of the tiles is by rows and the direction is from left to right within a row. Figure 4.2 shows this order for a 5  $\times$  5 tile array.

**Lemma 1.** For any  $0 \le r, c < \xi$ , the rank of tile  $\tau_{i,j}$  in Row major order is  $rank(\tau_{r,c})^{RM} = r\xi + c$

<u>Proof:</u> Any given tile  $\tau_{r,c}$  can only be enumerated after all tiles before it are enumerated. The number of tiles enumerated before Tile  $\tau_{r,c}$  is  $r\xi$  before row r and c in the row r. Thus  $\tau_k = r\xi + c$ Note: Here  $\tau_{r,c} = \tau_k^R$  where  $k = rank(\tau_{r,c})^R = r\xi + c$

Figure 4.2: Row-major ordering

### 4.3 Diagonal Ordering

Here the order of tiles is by the value of r + c. Consider two tiles  $\tau_{r_1,c_1}$  and  $\tau_{r_2,c_2}$ . If  $(r_1+c_1) < (r_2+c_2)$  then  $\tau_{r_1,c_1}$  is enumerated before  $\tau_{r_2,c_2}$ . If  $(r_1+c_1) = (r_2+c_2)$ , then  $\tau_{r_1,c_1}$  is enumerated before  $\tau_{r_2,c_2}$  if and only if  $r_1 < r_2$ . Figure 4.3 shows this order for a  $5 \times 5$  tile array. The proof of following lemma can be proved in a manner similar to Lemma 1. Its proof is omitted for brevity.

| 0  | 1  | 3  | 6  | 10 |

|----|----|----|----|----|

| 2  | 4  | 7  | 11 | 15 |

| 5  | 8  | 12 | 16 | 19 |

| 9  | 13 | 17 | 20 | 22 |

| 14 | 18 | 21 | 23 | 24 |

Tiles in image

Tile Ordering direction

Figure 4.3: Diagonal ordering

**Lemma 2.** For any  $0 \le r < \xi$ , the rank of the tile  $\tau_{i,j}$  in Diagonal ordering is to

$$rank(\tau_{r,c})^{D} = \begin{cases} \frac{(r+c)(r+c+1)}{2} + r & \text{if } r+c < \xi;\\ (\xi^{2}-1) - \left(\frac{(r'+c')(r'+c'+1)}{2} + r'\right) & \text{if } r+c \ge \xi \end{cases}$$

where  $r' = \xi - c$  and  $c' = \xi - c$

## Chapter 5

# The Computation Pipeline

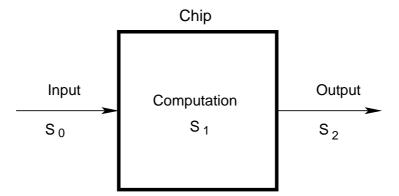

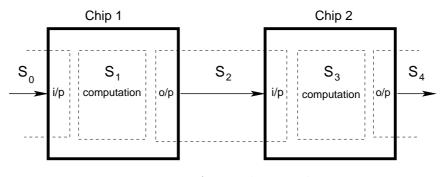

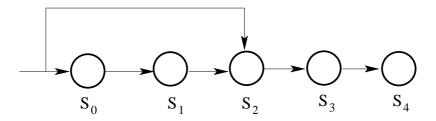

The computational platform on which we study SIFT is a pipeline of chips. The fact that the SIFT algorithm consists of sequential stages and that many real-time applications of SIFT stream in data make a pipeline a suitable model for SIFT. Each chip in the model has three internal stages, each stage feeding its partial result to the next. So the computational model can be viewed as a pipeline of stages, rather than a pipeline of chips. Let  $C = \{C_0, C_1, C_2, \dots, C_{c-1}\}$  be a set of c chips (see Figure 5.1). For each  $1 \leq i < c-1$ Chip  $C_i$  receives its input from the Chip  $C_{i-1}$  and sends its output to the Chip  $C_{i+1}$ . Chip  $C_0$ receives the input of the algorithm and Chip  $C_{c-1}$  produces the algorithm's final output (see Figure 5.1).

Figure 5.1: A c-chip pipeline

As noted above, each chip is assumed to consist of three internal stages, *input*, *compute* and *output*, that can work simultaneously (see Figure 5.2). The *c*-chip model is a (2c + 1)stage pipeline. The output stage of Chip  $C_i$  must be compatible with the input stage of Chip  $C_{i+1}$  in terms of bandwidth, pins, etc. We will consider these two stages (namely

Figure 5.2: A chip in the pipeline model

output stage of Chip  $C_i$  and input stage of Chip  $C_{i+1}$ ) to be identical in the pipeline. To keep the notation clear and consistent on this (2c + 1) stage pipeline, we will denote these stages as  $S_0, S_1, S_2, \dots, S_{2c}$  where  $S_{2i}$  denotes the input stage of Chip  $C_i$  and the output of stage of Chip  $C_{i-1}$  (if it exists) and  $S_{2i+1}$  denotes the compute stage of Chip  $C_i$  (see Figure 5.3).

Figure 5.3: Stages in the pipeline model

The input stage of Chip  $C_i$  receives the input from the output stage of Chip  $C_{i-1}$  and holds this in local memory until the compute stage of Chip  $C_i$  requires it. The output stage of Chip  $C_i$  receives the results of the computation from the compute stage.

Now we describe how the SIFT algorithm runs on the *c*-chip pipeline. Recall that the given image of size  $N \times N$  is decomposed into  $(n^2)$ -pixel tiles. These tiles are fed into the pipeline in some order as described in Chapter 4. For a given tile order,  $\odot$ , let  $\tau_k^{\odot}$  (or simply  $\tau_k$ ) be the  $k^{th}$  tile input to the pipeline.

Let us trace the traversal of the tiles through the pipeline in this ordering. For ease of explanation, assume each tile traverses each stage in 1 unit of time, starting from T = 1. At time t = 1 the first tile  $\tau_k$  enters Chip  $C_0$  through Stage  $S_0$ . Additional information necessary to process the tile also enters stage  $S_0$ . For reasons that will apparent later, let this tile entering be denoted by  $\tau_{k,0}$ . At time t = 2, Stage  $S_1$  receives  $\tau_k$  from  $S_0$  and processes it. We call this input to Stage  $S_1$  as  $\tau_{k,1}$ . After processing it, it produces an output  $\tau_{k,2}$  that Stage  $S_2$  receives at time t = 3. At time t = 2i, Stage  $S_{2i}$  (an input/output stage) receives tile  $\tau_{k,2i}$ . Note that  $\tau_{k,2i}$  may be just an extract of the original image tile  $\tau_k$ .

#### 5.1 Notation

In this section we formalize the notation used earlier to describe "tiles" at each stage or chip in the pipeline model. A given tile  $\tau_k$  goes through the (2c + 1)-stage pipeline. The notation  $\tau_{k,\ell}$  represents the data input to stage  $S_\ell$  of the pipeline. Tile  $\tau_{k,\ell+1}$  represents the result of the stage  $S_\ell$  which is fed to Stage  $S_{\ell+1}$  (if it exists) and so on. For tile  $\tau_k$ , here  $\tau_{k,0}$ is the image input to the pipeline at stage  $S_0$  and  $\tau_{k,2c}$  is the final output of the pipeline at the stage  $S_{2c}$  for tile  $\tau_k$ .

Consider any chip  $C_i$ , with internal stages  $S_{2i}$ ,  $S_{2i+1}$ ,  $S_{2i+2}$ . Here the stages  $S_{2i}$  and  $S_{2i+2}$  are communication stages (input and output stages) and  $S_{2i+1}$  is the compute stage. Stage  $S_{2i}$  brings in all the data needed for  $S_{2i+1}$  to start its computation on any given tile  $\tau_{k,2i+1}$  and  $S_{2i+2}$  carries out all the data produced by  $S_{2i+1}$ . The data needed to perform the computation on tile  $\tau_{k,2i+1}$  at Stage  $S_{2i+1}$  is not necessarily the same as  $\tau_{k,2i+1}$  and may have been brought in entirely or partially at an earlier time. We formalize this notion below.

To process tile  $\tau_k$ , the compute stage  $S_{2i+1}$  of chip  $C_i$  requires some additional data related to the tile  $\tau_{k,2i+1}$ . These bits have to be present in the chip  $C_i$  before stage  $S_{2i+1}$  can process  $\tau_{k,2i+1}$ . However the bits could have been brought in earlier to Chip  $C_i$  (wholly or in part). The time when these bits arrive at Chip  $C_i$  is decided by the input protocol which is discussed in Section 5.3.

#### 5.1.1 Stage Start Times

In this section we derive an expression for the earliest starting times for each stage  $S_i$ in processing tile  $\tau_k$ . This allows us to derive an expression for the overall time of the algorithm. For any stage  $S_{\ell}$ ,  $(0 \leq \ell < 2c)$  and any tile  $\tau_k$ , let  $T_{k,\ell}$  be the earliest time when stage  $S_{\ell}$  can work on  $\tau_{k,\ell}$ . Let  $t_{k,\ell}$  denote the time needed for stage  $S_{\ell}$  to perform its action on tile  $\tau_{k,\ell}$ .

The time for stage  $S_{\ell}$  to complete processing tile  $\tau_{k,\ell}$  depends on two quantities.

- 1. The time for stage  $S_{\ell}$  to finish processing the previous tile  $\tau_{k-1}$ .

- 2. The time for stage  $S_{\ell-1}$  to complete processing the current tile  $\tau_k$

The following theorem captures the above observation.

**Theorem 3.** If  $\ell$  is any stage in the pipeline where  $0 \leq \ell < 2c$ , then the earliest time when stage  $S_{\ell}$  can start on tile  $\tau_k$  is

$$T_{k,\ell} = \max\{T_{k,\ell-1} + t_{k,\ell-1}, \ T_{k-1,\ell} + t_{k-1,\ell}\}$$

The following lemma representing a well known standard result finds use later in this chapter.

**Lemma 4.** The recurrence,  $a_0 = b_0$  and  $a_n = a_{n-1} + b_n$ , for n > 0 has the solution  $a_n = b_0 + b_1 + b_2 + \cdots + b_n$ .

<u>Proof:</u> We proceed by induction on n. For n = 0,  $a_0 = b_0$ . Assuming the lemma to hold for n = n + 1. consider  $a_{n+1}$ .  $a_{n+1} = a_n + b_{n+1} = (b_0 + b_1 + \dots + b_n) + b_{n+1}$ .

**Lemma 5.** For  $0 < k < \xi^2$ , the earliest time when Stage  $S_0$  can start on tile  $\tau_k$  is  $T_{k,0} = \sum_{i=0}^{k-1} t_{u,0}$

<u>Proof:</u> Since there is no stage before stage  $S_0$ , it does not have to wait on any other stages to receive the data of tile. Therefore from Theorem 3,  $T_{k,0} = T_{k-1,0} + t_{k-1,0}$ . With  $T_{0,0} = 0$  (the count of time begins here), this recurrence has the solution  $T_{k,0} = \sum_{u=0}^{k-1} t_{u,0}$  (from Lemma 4).

**Lemma 6.** For any  $0 \le \ell < 2c$ , the earliest time when stage  $S_{\ell}$  can start on tile  $\tau_0$  is  $T_{0,\ell} = \sum_{v=0}^{\ell-1} t_{0,v}$

<u>Proof:</u> Since there is no tile before tile  $\tau_0$ , a stage  $S_\ell$  is free when  $\tau_{0,\ell}$  arrives at  $S_\ell$ . Then from Theorem 3,  $T_{0,\ell} = T_{0,\ell-1} + t_{0,\ell-1}$ . With  $T_{0,0} = 0$  (the count of time begins here), this recurrence has the solution  $T_{0,\ell} = \sum_{v=0}^{\ell-1} t_{0,v}$  (from Lemma 4).

We now discuss the total time needed to process all tiles.

**Total Time:** Recall that the given image of size  $N \times N$  is decomposed into  $\xi$  rows and  $\xi$  columns of  $n \times n$  tiles. The total time to process a given image is equal to the time taken by the pipeline to process all tiles in the  $\xi \times \xi$  tile array. Denote the  $\xi^2$  tiles in the array, by  $\tau_0, \tau_1, \dots, \tau_{\xi^2-1}$  where the indices  $0, 1, \dots, \xi^2 - 1$  reflect the number of tile in tile ordering (see Sections 4.2,4.3). This, coupled with the fact that a stage  $S_\ell$  cannot process tile  $\tau_{k+1,\ell}$  until it has finished with tile  $\tau_{k,\ell}$ , gives the following expression for the overall time T for processing all tiles through all stages is  $T = T_{\xi^2-1,2c} + t_{\xi^2-1,2c}$

**Definition 1.** Consider a (2c + 1)-stage pipeline. For any fixed  $\ell$ , where  $0 \leq \ell \leq 2c$ , Stage  $S_{\ell}$  is a *comparable stage*, iff for all  $0 \leq k < \xi^2$  and for every  $0 \leq \ell' \leq 2c$ , either  $t_{k,\ell} \leq t_{k-\ell'+\ell,\ell'}$  or  $t_{k,\ell} \geq t_{k-\ell'+\ell,\ell'}$ .

In a stage that is not comparable, for some  $\ell'$  we could have  $t_{k,\ell} < t_{k-\ell'+\ell,\ell'}$  while for a different  $\ell'$ , we have  $t_{k,\ell'} > t_{k-\ell'+\ell,\ell'}$

**Definition 2.** A (2c+1)-stage pipeline, is a *totally ordered pipeline*, iff for all  $0 \le \ell \le 2c$ , Stage  $S_{\ell}$  is a comparable stage.

In our application, each stage performs a specific activity on different tiles. The time for a stage is generally a function of the task it performs, as all tiles are of same size. Therefore we may expect our pipeline to be totally ordered.

In a totally ordered pipeline, For all  $0 \leq k < \xi^2$ , each pair of stages  $S_{\ell}$  and  $S_{\ell'}$  satisfies either  $t_{k,\ell} \leq t_{k-\ell'+\ell,\ell'}$  or  $t_{k,\ell} \geq t_{k-\ell'+\ell,\ell'}$ . We use the notation  $S_{\ell} \leq S_{\ell'}$  to denote for all  $\ell$  if  $t_{k,\ell} \leq t_{k-\ell'+\ell,\ell'}$  and the notation  $S_{\ell} \geq S_{\ell'}$  to denote for all  $\ell'$  if  $t_{k,\ell} \geq t_{k-\ell'+\ell,\ell'}$ . Intuitively,  $S_{\ell} \leq S_{\ell'}$ , implies that  $S_{\ell}$  will not hold  $S_{\ell'}$  up due to the time it takes to process a tile.

**Lemma 7.** If  $S_0 \leq S_1$ , then  $T_{k+1,0} \leq T_{k,1}$

<u>Proof:</u> We proceed by induction on  $k \ge 0$ . For k = 0, we consider  $T_{1,0}$  and  $T_{0,1}$ . From Theorem 3 and Lemma 5 we know that  $T_{1,0} = T_{0,1} = t_{0,0}$ . This implies  $T_{1,0} \le T_{0,1}$ . This

proves the base case.

Assuming the lemma to hold for all  $0 \le k \le \xi^2 - 2$ , consider  $T_{k+2,0}$  and  $T_{k+1,1}$ .

$$\begin{array}{rcl} T_{k+1,1} &=& \max\{T_{k+1,0} + t_{k+1,0}, & T_{k,1} + t_{k,1}\} & \text{from Theorem 3} \\ &=& \max\{T_{k+2,0}, & T_{k,1} + t_{k,1}\} & \text{from Lemma 5} \\ &\geq& T_{k+2,0} \end{array}$$

We now generalize the above lemma to stages that are not necessarily neighbors.

**Lemma 8.** For any  $0 \le \ell \le 2c$ , if,  $S_0, S_1, \dots, S_{\ell-1} \preceq S_\ell$  then, for all  $0 \le k \le \xi^2 - 1$ ,  $T_{k+1,\ell} \le T_{k,\ell+1}$ .

<u>Proof:</u> We proceed by induction on  $\ell \geq 0$ . For  $\ell = 0$  consider  $T_{k+1,0}$  and  $T_{k,1}$ . We know that  $T_{k+1,0} \leq T_{k,1}$ . (from Lemma 7) Assuming the current lemma to hold for any  $\ell' < \ell$ , consider  $T_{k+1,\ell}$  and  $T_{k,\ell+1}$ .

$$T_{k+1,\ell} = \max\{T_{k+1,\ell-1} + t_{k+1,\ell-1}, T_{k,\ell} + t_{k,\ell}\} \text{ from Theorem 3}$$

=  $T_{k,\ell} + t_{k,\ell}$  as  $T_{k,\ell} \ge T_{k+1,\ell-1}$  (induction hypothesis)

and  $t_{k,\ell} \ge t_{k+1,\ell-1}$  as  $S_{\ell-1} \le S_{\ell}$

That is,

$$T_{k+1,\ell} = T_{k,\ell} + t_{k,\ell} \tag{5.1}$$

Now,

$$T_{k,\ell+1} = \max\{T_{k,\ell} + t_{k,\ell}, T_{k-1,\ell+1} + t_{k-1,\ell+1}\} \text{ from Theorem 3} \\ = \max\{T_{k+1,\ell}, T_{k-1,\ell+1} + t_{k-1,\ell+1}\} \text{ from Equation (5.1)} \\ \ge T_{k+1,\ell}$$

Although the following lemma seems obvious from above Lemma, it does not follow directly. So we prove it below.

**Lemma 9.** For any  $0 \le \ell \le 2c$ , if,  $S_0, S_1, \cdots, S_{\ell-1} \succeq S_\ell$  then, for all  $0 \le k \le \xi^2 - 1$ ,  $T_{k+1,\ell} \ge T_{k,\ell+1}$ .

<u>Proof:</u> We proceed by induction on  $\ell \ge 0$ . For  $\ell = 0$  consider  $T_{k+1,0}$  and  $T_{k,1}$ . We know that  $T_{k+1,0} \ge T_{k,1}$ . (from Lemma 7)

Assuming the lemma to hold for any  $\ell' < \ell$ , consider  $T_{k+1,\ell}$  and  $T_{k,\ell+1}$ .

$$T_{k,\ell+1} = \max\{T_{k,\ell} + t_{k,\ell}, T_{k-1,\ell+1} + t_{k-1,\ell+1}\}$$

from Theorem 3

=  $T_{k,\ell} + t_{k,\ell}$

$$T_{k,\ell} \ge T_{k-1,\ell+1}$$

by induction hypothesis

as given is lemma  $t_{k,\ell} \ge t_{k-1,\ell+1}$

as  $S_{\ell} \prec S_{\ell-1}$

That is

$$T_{k,\ell+1} = T_{k,\ell} + t_{k,\ell} \tag{5.2}$$

Now,

$$T_{k+1,\ell} = \max\{T_{k+1,\ell-1} + t_{k+1,\ell-1}, T_{k,\ell} + t_{k,\ell}\} \text{ equation (3)} = \max\{T_{k+1,\ell} + t_{k+1,\ell}, T_{k,\ell+1}\} \text{ from Equation 5.2} \geq T_{k,\ell+1}$$

In is a (2c+1)-stage totally ordered pipeline then there exists a stage  $S_m$  such that  $S_m \succeq S_\ell$  for all  $0 \le \ell \le 2c$ . This stage is called *the maximal stage*. It will never have to wait on any of its previous stages. The following lemma formalizes this statement.

**Lemma 10.** If  $S_m$  is a maximal stage, then for all  $0 \le k < \xi^2$ ,  $T_{k,m} = T_{k-1,m} + t_{k-1,m}$ .

<u>Proof:</u> We know that

$$\begin{array}{rcl} T_{k,m} &=& \max\{T_{k-1,m} + t_{k-1,m}, & T_{k,m-1} + t_{k,m-1}\} & \text{from Theorem 3} \\ &=& T_{k-1,m} + t_{k-1,m} & \text{as } T_{k-1,m} \succeq T_{k,m-1} \text{ and Lemma 8} \end{array}$$

**Lemma 11.** If stage  $S_m$  is a maximal stage of a (2c + 1)-stage totally ordered pipeline, then  $T_{k,m} = \sum_{v=0}^{m-1} t_{0,v} + \sum_{u=0}^{k-1} t_{u,m}$ .