### Louisiana State University LSU Digital Commons

LSU Doctoral Dissertations

Graduate School

2010

## The weakening of branch predictor performance as an inevitable side effect of exploiting control independence

Christopher Joseph Michael Louisiana State University and Agricultural and Mechanical College

Follow this and additional works at: https://digitalcommons.lsu.edu/gradschool\_dissertations Part of the <u>Electrical and Computer Engineering Commons</u>

#### **Recommended** Citation

Michael, Christopher Joseph, "The weakening of branch predictor performance as an inevitable side effect of exploiting control independence" (2010). *LSU Doctoral Dissertations*. 1856. https://digitalcommons.lsu.edu/gradschool\_dissertations/1856

This Dissertation is brought to you for free and open access by the Graduate School at LSU Digital Commons. It has been accepted for inclusion in LSU Doctoral Dissertations by an authorized graduate school editor of LSU Digital Commons. For more information, please contactgradetd@lsu.edu.

#### THE WEAKENING OF BRANCH PREDICTOR PERFORMANCE AS AN INEVITABLE SIDE EFFECT OF EXPLOITING CONTROL INDEPENDENCE

A Dissertation Submitted to the Graduate Faculty of the Louisiana State University and Agricultural and Mechanical College in partial fulfillment of the requirements for the degree of Doctor in Philosophy

in

The Department of Electrical and Computer Engineering

by Christopher J. Michael B.S. Louisiana State University 2005, May 2010

## Acknowledgments

There are several people whom I would like to thank for their time and effort in helping me throughout my time conducting this research.

To my major professor, Dr. David M. Koppelman, thank you for the outstanding technical guidance you have given me in the many years I have conducted this research. Also, for sparking my interest in computer architecture through your wonderful teaching.

A big thanks to my minor professor, Dr. Thomas Sterling. The guidance and advice you have given me in the past several years are invaluable. It has been an honor working with you.

Thanks to all other members of my committee for your time and teaching. Dr. J. (Ram) Ramanujam, Dr. Lu Peng, Dr. Jerry Trahan, and Dr. Joseph Giaime, I was very fortunate to be taught by each of you in my many years here at LSU.

My time in graduate school would be much more of a struggle if it wasn't for the many friends I have made here. You know who you are. Thank you.

Finally, I must thank my family both present and future. You all were very patient in dealing with all my time away.

Especially my future wife, Meg, whom I am scheduled to marry the day this dissertation is due. Thanks for putting up with me in this hectic time.

# **Table of Contents**

| Ac | know            | vledgments                                      | ii           |

|----|-----------------|-------------------------------------------------|--------------|

| Li | st of ]         | Tables                                          | v            |

| Li | st of I         | Figures                                         | vi           |

| Ał | ostrac          | etv                                             | iii          |

| 1  | Intro           | oduction                                        | 1            |

| 2  | Bacl            | kground                                         | 7            |

|    | 2.1             | Branch Prediction                               | 7            |

|    |                 | 2.1.1 Common Predictors                         | 8            |

|    |                 | 2.1.2 Correct and Timely History Update         | 12           |

|    | 2.2             | Paths                                           | 13           |

|    | 2.3             | Branch Behavior                                 | 15           |

|    | 2.4             |                                                 | 18           |

| 3  | Con             | trol Independence                               | 21           |

|    | 3.1             | •                                               | 22           |

|    |                 | 1                                               | 22           |

|    |                 |                                                 | 22           |

|    |                 |                                                 | 24           |

|    |                 |                                                 | 25           |

|    |                 |                                                 | 26           |

|    |                 |                                                 | 20           |

|    | 2 2             |                                                 | 27           |

|    | 3.2             | Snipper                                         | 21           |

| 4  | Prio            | or Work                                         | 32           |

|    | 4.1             | Limit Studies                                   | 32           |

|    | 4.2             | Branch Classification and Prediction Techniques | 33           |

|    | 4.3             | Early Control Independence Processors           | 36           |

|    |                 | 4.3.1 Multiscalar                               | 36           |

|    |                 |                                                 | 37           |

|    |                 | 5 1                                             | 37           |

|    | 4.4             | 11                                              | 38           |

|    | 4.5             |                                                 | 39           |

| 5  | Svst            | em Simulation Methodology                       | 41           |

| -  | 5.1             |                                                 | 41           |

|    | 5.2             |                                                 | 42           |

|    | 5.2<br>5.3      |                                                 | 45           |

|    | 5.3<br>5.4      |                                                 | 47           |

|    | J. <del>4</del> |                                                 | - <b>T</b> / |

|    | 5.5    | Viewable Experimental Data | 48 |

|----|--------|----------------------------|----|

| 6  | Brai   | nch Weakening              | 50 |

| -  | 6.1    |                            | 50 |

|    | 6.2    |                            | 55 |

|    |        | 0 11                       | 56 |

|    |        |                            | 56 |

|    |        | 1                          | 58 |

|    |        | 1                          | 58 |

|    |        | J 1 J                      | 53 |

|    |        |                            | 57 |

|    |        |                            | 59 |

|    | 6.4    | -                          | 72 |

|    | 0.1    |                            | 72 |

|    |        | 1                          | 73 |

|    |        | 1                          | 75 |

|    |        |                            | 82 |

|    |        |                            | 34 |

|    | 6.5    | , e                        | 87 |

|    | 0.0    |                            |    |

| 7  | Mea    | surement by Weakening Type | 91 |

|    | 7.1    |                            | 91 |

|    | 7.2    |                            | 92 |

|    | 7.3    | Results                    | 94 |

|    |        |                            |    |

| 8  | CI A   | ware Branch Predictor      | 97 |

|    | 8.1    | Implementation             | 97 |

|    | 8.2    | Results                    | 98 |

| 9  | Con    | clusion and Future Work10  | 02 |

| _  |        |                            |    |

| Bi | bliogr | caphy10                    | )5 |

| Vi | ta     |                            | )9 |

# **List of Tables**

| 2.1 | Branch Behavior Definitions | 14 |

|-----|-----------------------------|----|

| 5.1 | Configuration Parameters    | 43 |

| 5.2 | Selected Benchmarks         | 48 |

| 6.1 | Branch Weakening Types      | 54 |

| 6.2 | Padding Methods             | 87 |

# **List of Figures**

| 1.1  | Sample Code and Control Flow Graph                                | 3  |

|------|-------------------------------------------------------------------|----|

| 1.2  | Fetch Stream Comparison                                           | 4  |

| 2.1  | Classification of Branches and 16-bit Paths                       | 17 |

| 2.2  | Example of Overlap                                                | 19 |

| 3.1  | Snipper Speedup                                                   | 30 |

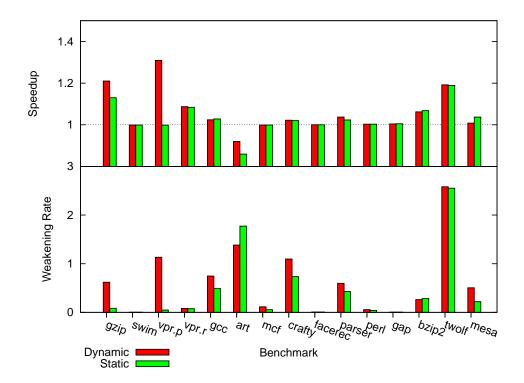

| 5.1  | Static Snipper vs. Dynamic Snipper, Speedup and Weakening         | 44 |

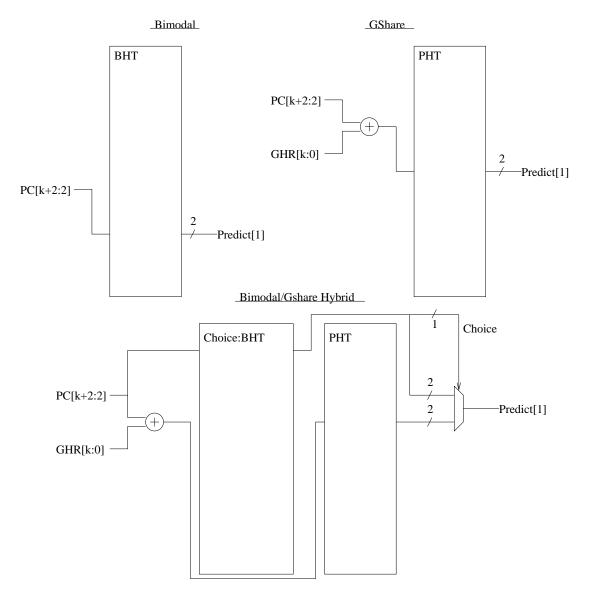

| 5.2  | Branch Predictors Used in this Study                              | 46 |

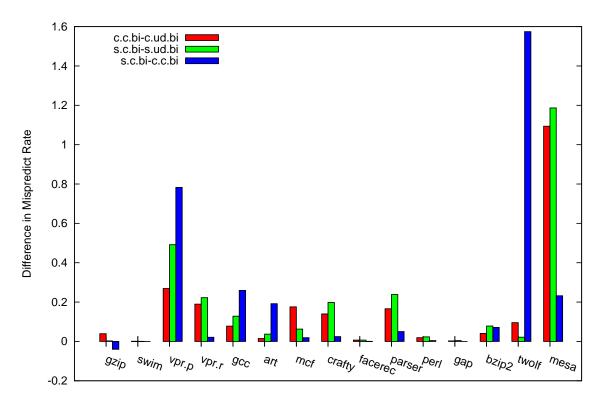

| 6.1  | Snipper Weakening                                                 | 51 |

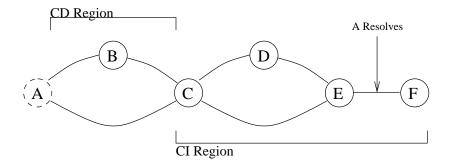

| 6.2  | Example Control Flow of Execution                                 | 52 |

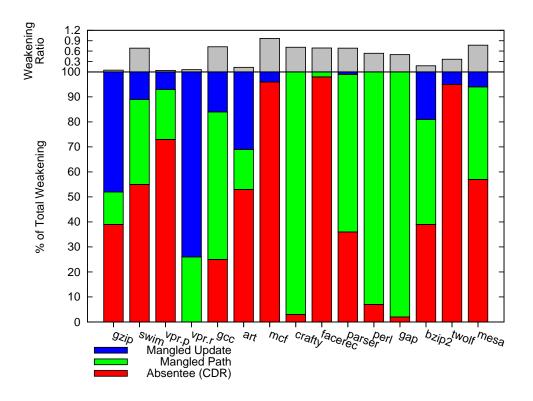

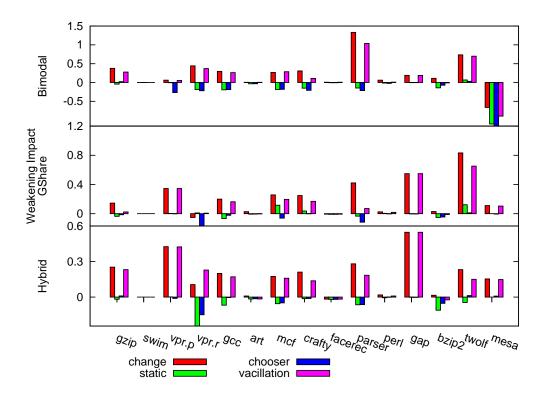

| 6.3  | Weakening Classified by Type for Snipper                          | 55 |

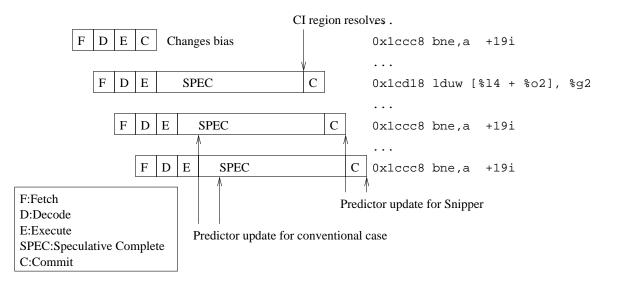

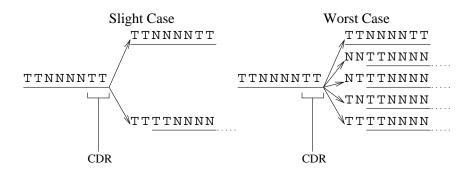

| 6.4  | Example of Delayed Update Weakening                               | 57 |

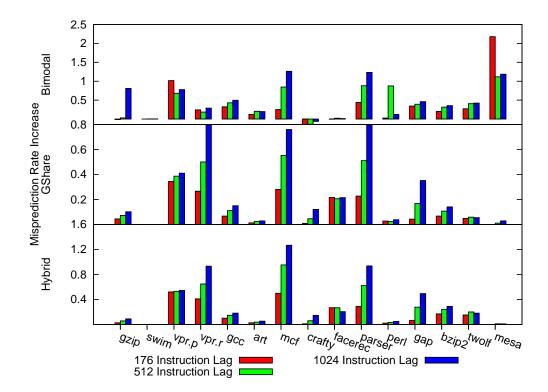

| 6.5  | The Impact of Update Lag                                          | 59 |

| 6.6  | Update Lag Induced by Snipper                                     | 61 |

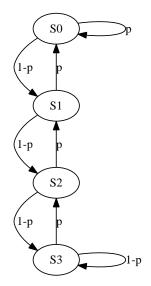

| 6.7  | The Behavior of Predictor Update Schemes for a Vacillating Branch | 63 |

| 6.8  | Markov Model of Predictor Entry State                             | 64 |

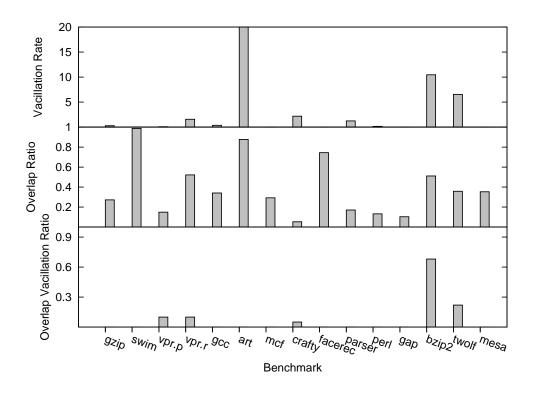

| 6.9  | Overlap and Vacillation for Snipper                               | 66 |

| 6.10 | Misprediction Rate Impact of Flexible Update Schemes              | 69 |

| 6.11 | Analysis of Bimodal Chooser                                       | 70 |

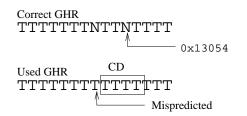

| 6.12 | GHR State for Branch 0x12fbc                                      | 74 |

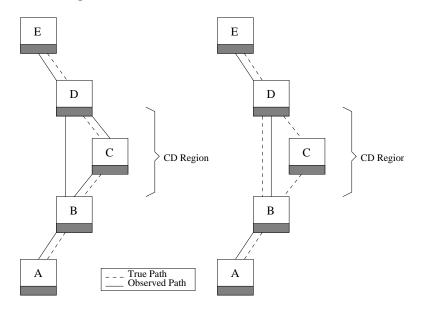

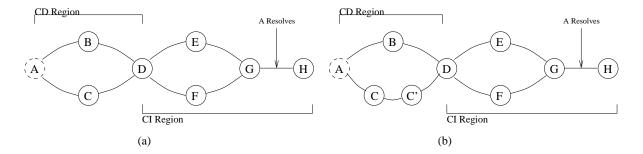

| 6.13 | Control Flow Graphs of Two Separate Executions                    | 74 |

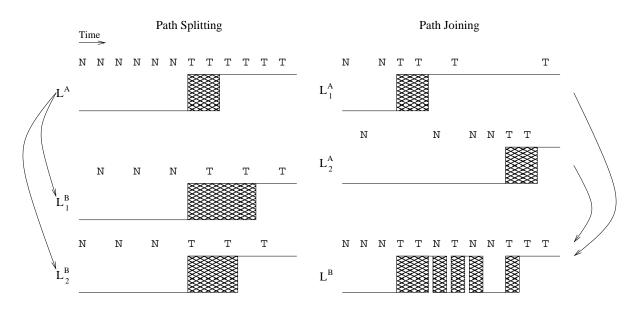

| 6.14 | Examples of Path Splitting and Joining                            | 77 |

| 6.15 | Examples of External Insulated Weakening                          | 78 |

| 6.16 | Push Displacement Causing Path Joining                            | 79 |

| 6.17 | Control Flow Example for CDR Juggling                             | 80 |

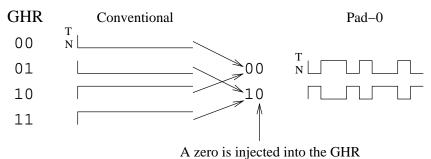

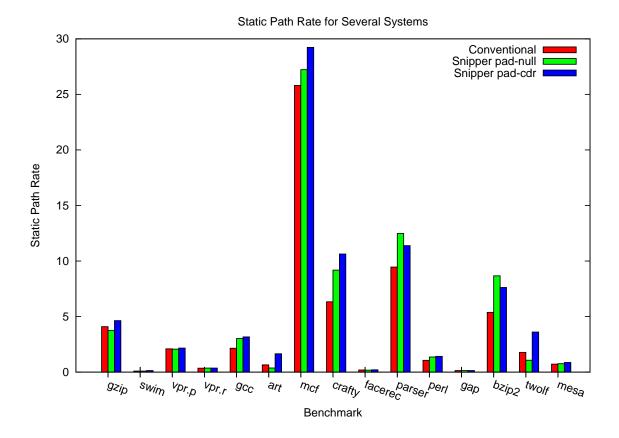

| 6.18 | Static Path Rate for Several Systems                              | 81 |

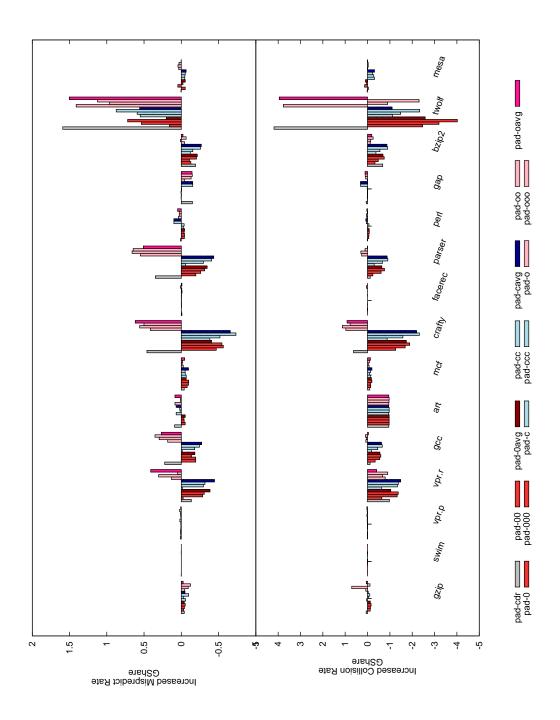

| 6.19 | Misprediction Rate And Collision Impact of Padding Schemes for GShare | 88  |

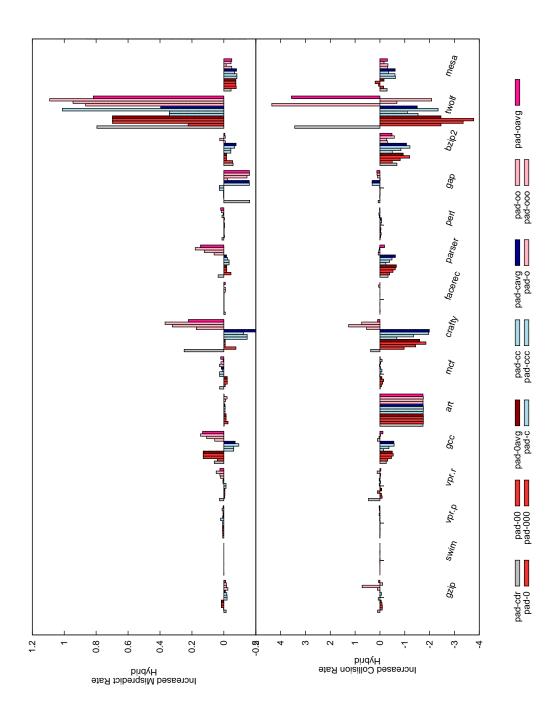

|------|-----------------------------------------------------------------------|-----|

| 6.20 | Misprediction Rate And Collision Impact of Padding Schemes for Hybrid | 89  |

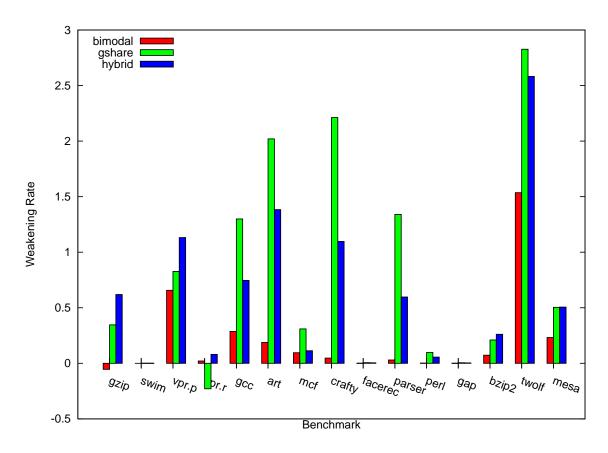

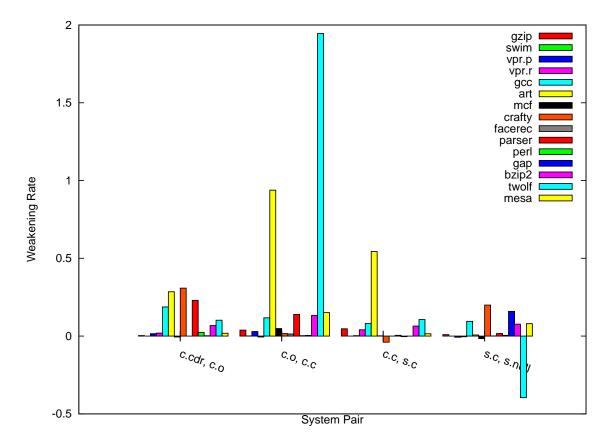

| 7.1  | Weakening Among Model Systems                                         | 95  |

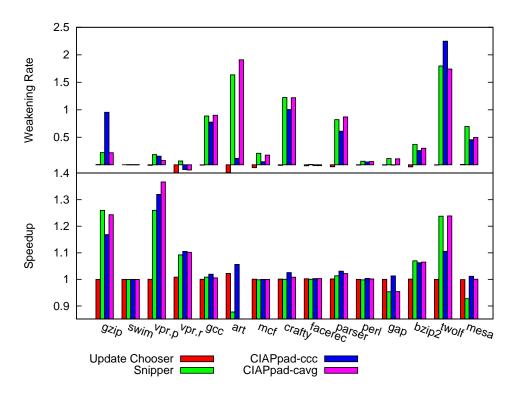

| 8.1  | Performance of Hybrid CIAP                                            | 98  |

| 8.2  | Weakening Classified by Type for Snipper with CIAP                    | 100 |

## Abstract

Many algorithms are inherently sequential and hard to explicitly parallelize. Cores designed to aggressively handle these problems exhibit deeper pipelines and wider fetch widths to exploit instruction-level parallelism via out-of-order execution. As these parameters increase, so does the amount of instructions fetched along an incorrect path when a branch is mispredicted. Many of the instructions squashed after a branch are control independent, meaning they will be fetched regardless of whether the candidate branch is taken or not. There has been much research in retaining these control independent instructions on misprediction of the candidate branch. This research shows that there is potential for exploiting control independence since under favorable circumstances many benchmarks can exhibit 30% or more speedup. Though these control independent processors are meant to lessen the damage of misprediction, an inherent side-effect of fetching out of order, branch weakening, keeps realized speedup from reaching its potential. This thesis introduces, formally defines, and identifies the types of branch weakening. Useful information is provided to develop techniques that may reduce weakening. A classification is provided that measures each type of weakening to help better determine potential speedup of control independence processors.

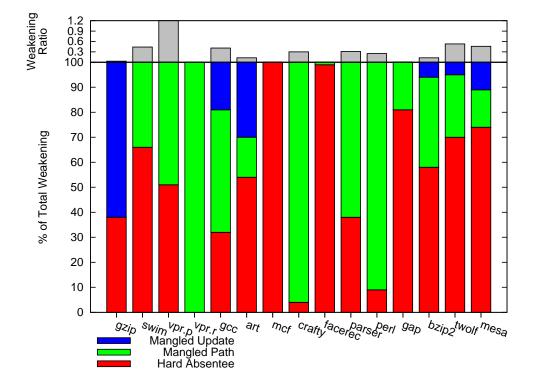

Experimentation shows that certain applications suffer greatly from weakening. Total branch mispredictions increase by 30% in several cases. Analysis has revealed two broad causes of weakening: changes in branch predictor update times and changes in the outcome history used by branch predictors. Each of these broad causes are classified into more specific causes, one of which is due to the loss of nearby correlation data and cannot be avoided. The classification technique presented in this study measures that 45% of the weakening in the selected SPEC CPU

2000 benchmarks are of this type while 40% involve other changes in outcome history. The remaining 15% is caused by changes in predictor update times. In applying fundamental techniques that reduce weakening, the Control Independence Aware Branch Predictor is developed. This predictor reduces weakening for the majority of chosen benchmarks. In doing so, a control independence processor, snipper, to attain significantly higher speedup for 10 out of 15 studied benchmarks.

# Chapter 1 Introduction

Processors designed to exploit instruction-level parallelism (ILP) via out-of-order execution require long pipelines and high fetch rates. As these parameters increase, so does the amount of instructions fetched along an incorrect path when a branch is mispredicted. In runs of selected applications in the SPEC CPU 2000 benchmark suite [Hen00]. On a CPU with a modern configuration, around 30% of fetch bandwidth is taken by instructions that will eventually be squashed. Some of these instructions will be fetched regardless of the direction of a branch. In current conventional systems, these *control independent* instructions are always squashed upon branch misprediction and are fetched again shortly thereafter. Recent research efforts explore lessening the effect of branch mispredictions by retaining these instructions when squashing [AZRRA07, HR07, SBV95] or fetching them in advance when encountering a branch that is difficult to predict [CV01]. Though these control-independent processors (CIPs) are meant to lessen the damage of misprediction, an inherent side-effect of fetching out of order, branch weakening, keeps realized speedup from reaching its potential. The goal of this study is to formally define and analyze the different causes of branch weakening, measure the effect of each, and offer many techniques to help relieve CIPs of weakening. It will be shown that some weakening is unavoidable. Several different types of weakening will be quantified and, in doing so, the amount of unavoidable weakening is realized. This further validates the feasibility of exploiting control independence.

Modern general purpose processors are designed to minimize execution times by allowing for

high clock rates. This is made possible by pipelining the several stages of instruction execution, from when the instruction is first fetched to the time it commits. In addition, the processor is made *superscalar*, meaning it can sustain execution of multiple instructions per cycle. These types of processors must predict branches to maintain pipeline efficiency. When a branch instruction is fetched, the direction of the branch will not be known until several cycles and many instructions later. Accurate branch prediction is crucial to conventional processor cores. The *instruction window size*, or the maximum number of instructions a processor may have executing at any time, directly determines the potential waste fetching *doomed instructions*, which will eventually be squashed because a branch is mispredicted. CIPs lessen the impact of branch misprediction by retaining otherwise doomed instructions that will immediately be re-fetched after the squash.

Many studies have shown that reasonable CIP implementations can yield high gains. The Transparent Control Independence implementation by Al-Zawawi et al. achieves an average speedup of 22% across 15 SPEC CPU benchmarks [AZRRA07]. Another recent CIP, Ginger, developed by Hilton and Roth, achieves an average speedup of about 5% but does so with a much less aggressive predictor [HR07]. Both of these CIPs are affected by significant amounts of branch weakening.

Branch predictors of conventional processors often use a *global history register* (GHR) to correlate on recent outcomes and attain high branch prediction accuracy. The GHR is simply a bitwise shift register that holds the *global history*, a set number of recent consecutive branch outcomes. Outcomes in a conventional system's GHR may be guaranteed to be true; however, outcomes in the GHR may be incorrect or missing in a CIP.

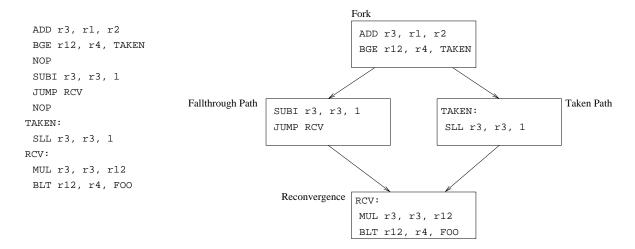

Branch weakening is caused by incorrect or missing history data in the GHR and changes to

Figure 1.1: Sample Code and Control Flow Graph

the way in which branch predictors are updated.

Figure 1.1 shows a snippet of code along with a control-flow diagram describing the possible paths of execution. Assume branch BGE is difficult to predict. When this branch is fetched in a conventional system, an initial prediction of its outcome is made and fetching continues along the predicted path. By the time BGE resolves, instructions far beyond the block labeled **reconvergence** have been fetched. If the branch is resolved mispredicted, all instructions after the branch are squashed and fetching continues along the correct path from the branch. Note that most instructions that were squashed will be refetched once again, this time along the correct path. For typical aggressive dynamically scheduled systems running applications like those in the SPEC CPU 2000 set, nearly 80% of the total instructions squashed upon misprediction of a branch like BGE will be fetched again soon after. The flushing and refetching of these instructions costs energy and time, since the instructions will have to be decoded and issued again.

Now consider a CIP executing the code fragment that chooses to exploit control independence for the branch BGE. First, the **fork**, **taken path**, and then **reconvergence** region may be fetched in order, similar to a conventional system. When BGE resolves as mispredicted, the CIP will squash

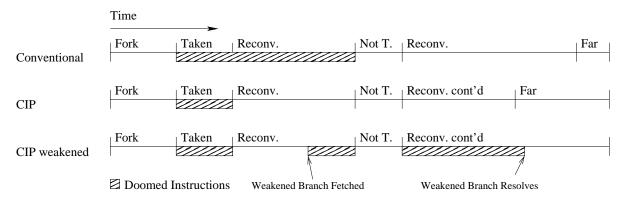

Figure 1.2: Fetch Stream Comparison

only the **taken path** region and fetch the **fallthrough path** retaining all control independent instructions in the pipeline while recovering from the branch misprediction. After **fallthrough path** is completely fetched, fetching will continue where it left off when BGE resolved mispredicted.

A CIP will speed this execution because fetch bandwidth is not wasted by squashing and refetching the instructions in the reconvergence region and beyond, as shown in Figure 1.2. The highlighted regions in the figure indicate the fetching of doomed instructions. Notice that in the conventional case, the **reconvergence** region is squashed and later refetched. The second diagram shows what would ideally happen in a CIP. Because there is less time spent fetching doomed instructions, some subsequent region of code **far** is fetched sooner than in the conventional case. In the third diagram, the impact of weakening is shown. Some branch in the **reconvergence** region, which would not be mispredicted in the conventional case, is mispredicted in the CIP. As a result, the system fetches considerably more doomed instructions. In this case, weakening has caused control independence exploitation to slow execution down rather than speed it up. Comparing the diagrams of the conventional system and the weakened CIP, it is evident that more of the fetch bandwidth is wasted on doomed instructions in the weakened case. It becomes clear that to exploit control independence as much as possible, there should be some action taken

to minimize negative effects caused by branch weakening.

Weakening is caused by two broad reasons. The increase of in-flight instructions and the prolonged commit times of branches in a CIP cause predictors to be updated differently than they would in a conventional system. Additionally, if predictors in the conventional system update earlier than commit time, the additional speculative execution required by a CIP could induce incorrect predictor updates. This type of weakening involving predictor update times may be avoided through techniques that selectively update the predictor earlier than the time at which branches commit. The other broad cause of weakening is caused by incorrect or missing branch outcomes in the GHR of CIPs. This property either introduces useless outcomes into the outcome history, called *noise ingestion*, or robs the history of important correlation data, called *signal loss*. The term *noise* refers to a branch outcome that varies in the GHR that isn't correlated to any branch which uses it for prediction. Noise ingestion causes branches in a CIP to be associated with more table entries in the predictor. Each of these extra entries will need to be trained and the mispredictions due to this cause weakening. Weakening due to noise ingestion can be alleviated with outcome history update methods that reduce the amount of unnecessary outcomes brought in to the GHR when exploiting control independence. The term *signal* refers to a branch outcome in the GHR that is useful for correlation of branches that use it. When branches are weakened due to signal loss, the more common case is that the weakening cannot be avoided since the correct outcomes cannot possibly be determined. This type of weakening cannot be reduced. In other less likely cases the signal is discarded as a side effect of fetching out of order which can be avoided by careful GHR management.

If weakened branches are classified into the reasons just presented, then the amount of avoid-

able weakening may be measured. The goals of this study are as follows. First, to develop definitions, identify characteristics, and quantify the major types of weakening. This includes a full analysis of the CIP artifacts that cause each type of weakening. Second, to provide an understanding of how each type of preventable weakening may be avoided while providing insight towards how much weakening is inevitable. The final goal is to develop techniques to lessen the effects that cause weakening using a fundamental approach brought about by achieving the prior goal.

# Chapter 2 Background

## 2.1 Branch Prediction

In early pipelined single-issue processors, branches could resolve one cycle after being fetched. Instead of leaving a bubble of inactivity in the pipeline, every branch had a subsequent *delay slot* instruction that would be executed independent of the branch's path. Since correct branch outcomes were usually available when needed, no branch predictor was necessary. Current generation superscalar processors fetch many instructions per cycle and contain many more pipeline stages [Sit93, Sto06, Sto01, TDF<sup>+</sup>02]. This greatly enlarges the potential bubble, making delay slots unreasonable and branch prediction vital.

A *basic block* is a sequence of code in which execution always starts with its first instruction and ends with its last instruction with no branching in between. A basic block contains at most one branch instruction and this instruction must be at the end of the basic block. A *branch* is an instruction that usually<sup>1</sup> tests a condition to control the flow of instructions. A branch can either be *taken*, denoted *T*, or *not taken*, denoted *N*, and this is referred to as the branch's *direction*. If a branch is not taken, then the instruction in the program that comes after the branch is fetched. If taken, then control flow changes to some destination address specified by the branch instruction. A *static branch* is an instruction in code that resides in some memory location. Fetching a static branch creates a *dynamic branch*. A dynamic branch is said to be *in-flight* from the time it is fetched to the time it has been committed or squashed. Multiple in-flight dynamic branches may correspond to a single static branch. A *branch predictor* is an architectural component in

<sup>&</sup>lt;sup>1</sup>Some instruction set architectures contain branches that are always taken.

the processor that tries to determine the direction of a branch in order to increase instruction throughput. The *branch target buffer* is a component that tries to provide the target of a taken branch before it is computed later in the pipeline. A dynamic branch is said to *resolve* in the cycle that its condition is tested. If the branch is mispredicted, the CPU must perform a *recovery* by squashing all instructions after the mispredicted branch and resuming fetch along the correct path of the branch. At some point after a branch's resolve time, it updates its predictor entry to reflect its direction. This occasion is simply referred to as branch *update*. Further detail regarding the fundamentals of branch prediction and other modern computer architecture concepts can be found in the Hennessey and Patterson texts [HP03, HP08].

The metrics used to measure the performance of branch predictors are the *branch prediction ratio* and the *branch misprediction rate*. The branch prediction ratio is the number of correct predictions divided by the total number of predictions of some defined execution. The branch misprediction rate is the number of branch mispredictions divided by a given rate of instructions. Branch prediction ratios and branch misprediction rates in this study are always measured for only committed branches. The misprediction rates are measured in mispredictions per 1000 committed instructions, denoted misp/kI.

There are special prediction techniques for *indirect branches*, those that branch to a target specified by a register. The address to which these instructions branch may change throughout execution. These types of predictors are not considered in this study.

#### **2.1.1 Common Predictors**

Simple predictors, such as the that in the ARM810 processor [ARM], implement *static branch prediction* schemes. In these schemes, prediction is based on the static branch and is used for

all dynamic instances of that branch. More modern predictors such as the Pentium 4 use a static predictor while the system's more complex predictor is training [Sto01]. The static predictors in these architectures predict all forward branches (branches whose target is further in code) not taken while all backwards branches are predicted taken. This is intuitive, since most backwards branches belong to loops and are expected to be taken most of the time. In an early study by James E. Smith, the need for *dynamic branch prediction* was addressed [Smi81]. Dynamic branch prediction schemes predict branches based on program run-time characteristics. For example, a branch may be predicted as its last resolved outcome in a program. The Smith study shows that on average about 4% improvement in branch prediction accuracy for a small set of benchmarks can be attained using this very simple method over a static scheme where branches are predicted based on their operation codes. More advanced dynamic predictors discussed in the remainder of this section can drastically improve basic static schemes, increasing the branch prediction ratio by 40% in some cases.

The bimodal predictor [Smi81] is a popular and relatively simple dynamic branch predictor. It is a *per-address branch predictor*, meaning it indexes a *branch history table* (BHT) using the address of the branch it is predicting. Each BHT entry consists of a 2-bit saturating up-down counter. Note that though some predictors may implement some other finite automaton for their table entries, all predictors in this study use an up-down counter. The most significant bit of the counter indicates the prediction of the branch. In this study, it is assumed that the branch will be predicted not taken if this bit is 0 while the branch is predicted taken if this bit is 1. Upon predictor update, the counter will be incremented or decremented based on the branch's correctly resolved direction. A not-taken outcome will decrement the entry while a taken outcome will increment it.

More advanced dynamic branch prediction techniques use two levels of branch history. Tse-Yu Yeh and Yale N. Patt studied and compared some variations of two-level predictors [YP92]. These predictors were both per-address and *correlating*, meaning that some type of outcome history data is used to make each prediction. The GAg predictor described in the study is an example of a correlating predictor. A special register, named the *global history register* or GHR, keeps a record of the last *k* outcomes of branches that executed. At predict time, the GHR is used to index a *pattern history table*, or PHT, of saturating counters and a prediction is made using the counter's value. Once the branch's outcome is known, this entry is updated appropriately. This predictor is named GAg to stand for Global Address, global PHT.

The best performing predictor in the study is the PAg predictor (per-address, global PHT). A first table is indexed by a branch's address and contains the *local history* for the branch. This is the sequence of outcomes for the last k instances of the static branch. The local history will then index a global PHT that contains a saturating counter used for prediction. The study showed on a whole that various dynamic two-level branch predictors yield a 97% accuracy on average for various SPEC92 CPU benchmarks.

In a study by Scott McFarling in 1993, the GShare predictor is introduced [McF93]. GShare is a two-level predictor whose global and per-address information are shared in the first level by XORing the PC and global history. This value indexes a PHT of saturating counters that yields the prediction. This is a popular and well performing predictor, averaging near 97% accuracy under selected benchmarks with a 32kiB table. An important technique introduced by McFarling in this study is the combining of branch predictors to form a *hybrid* predictor. This type of predictor is

built to select the better prediction option of any two predictors. It uses a *chooser* table, which is a per address table of two-bit saturating counters. On a branch prediction, the chooser will select either of the two predictors. On update, if one and only one of the predictors mispredicted, the chooser entry will be updated towards choosing the one that is correct. A 32kB bimodal/GShare Hybrid predictor outperforms a 32kB GShare predictor in every benchmark selected for the study.

There are many other predictors that correlate on some form of global history [EM98, YP93]. Some predictors, such as the perceptron predictor [JL01], are much more advanced than ones described here. Though these predictors are valuable, their complexity makes them less practical for study. Due to its ease of understanding, GShare is the only correlating predictor (or predictor component) that will be used in this study.

Numerous current-generation processors use correlating predictors to improve performance. One example is Intel's Core processor which was designed with a relatively more complex predictor than others implemented at the time [Sto06]. The branch predictor has a type of bimodal/global hybrid component similar to the hybrid predictor used in this study. The predictor also has a special *loop detector* component that predicts when loops will terminate. The architecture also implements an indirect branch predictor.

Another example of a modern processor that uses a correlating predictor is the IBM POWER4 architecture [TDF<sup>+</sup>02]. It also has a similar type of hybrid predictor. The per-branch component, called a *local predictor*, is a 16k-entry BHT consisting of 1-bit entries. The correlating predictor component, called a *global predictor*, uses an 11-bit vector, much like a GHR, called a *global history vector*. This register is XORed with the PC to index a *global history table* of 1-bit entries. The correlating predicts. The correlation of 1-bit entries.

it is indexed in the same manner as the global history table.

#### 2.1.2 Correct and Timely History Update

A wrong path history update occurs when a doomed branch updates the branch predictor. The effects of wrong path history updates have been presented by Jourdan et al. [JSHP97]. In the study, several predictors, GShare being one of them, updating outcome history at predict time are compared to their counterparts that update non-speculatively at commit time. Several mechanisms are covered that enable speculatively updating history at branch predict time while assuring that the history is correct. It is shown that performance drops by 30% on average if speculative global histories are not repaired across the proposed techniques. The predictor component that causes most of this degradation is the GHR. This suggests that some checkpointing mechanism that repairs the GHR on a misprediction is vital to the predictor. Because branches may resolve out of order, a PHT entry may be erroneously updated if predictors are set to update at resolve time (for example, when a doomed branch resolves). The study reveals that this speculative updating of the PHT without repair has almost no effect on performance. However, a BHT may be more vulnerable to incorrect updates since instances of the same branch tend to appear closer together in execution compared to instances of the branch reached by same path.

Branch predictors that have long prediction latencies either cause the CPU clock to have a lower frequency or require a pipelined implementation of the predictor. Pipelined predictor implementations leave bubbles in the instruction pipeline, decreasing the fetch rate. Daniel A. Jiménez et al. establish that it is not enough for a predictor to attain a higher accuracy, it must also provide a timely prediction [JKL00]. One technique offered in the study to improve the performance of systems with more complex predictors is *overriding*: Using a smaller and faster

predictor to make an initial 1-cycle prediction while waiting for more accurate prediction from a larger more complex predictor. A study by Gabriel H. Loh explores, in addition to prediction latencies, that predictor update latencies are also a significant factor of performance degradation – especially on deeply pipelined (40-stage) systems [Loh06]. The study shows that when using an overriding predictor the more complex component, in this case perceptron, can be used to provide a quick (though perhaps incorrect) update to the smaller 1-cycle component, GShare, to attain about 5% speedup in IPC for selected SPEC CPU benchmarks on a 40-stage pipelined system. This technique is called *hierarchical update*. It is claimed that update latency of highly accurate predictors are only affected by update latency in the initial training phase of the predictor, while smaller predictors are much more vulnerable due to their size.

### 2.2 Paths

For a correlating predictor, entries in the predictor's PHT correspond to paths by which the predicted branch was reached. In this study, the term *path* is the PHT index used when predicting a dynamic instance of a branch. The branch is said to be *reached by* the path. The GShare predictor used in this study constructs its path by XORing a k-outcome GHR to k bits of the branch PC.

Define the *true path* as the path reached by a non-doomed instruction in a conventional system that maintains a correct GHR and computes the path as defined by the predictor. A *pure path* of a branch is a sequence of the last k correct global outcomes in program order (equivalently, the contents of a k-bit GHR on a conventional system). Any path observed by a non-doomed instruction is referred to as an *observed path*. It will be shown further in the study that observed paths may not always be true paths in a CIP.

The path filtered local history of a static branch for some given path is the local history for

| Name       | Definition         | Example        |

|------------|--------------------|----------------|

| Mono-      | $M_0(B) <= M_1(B)$ |                |

| Monostable | $M_0(B) = 0$       | TTTTTTTTTTTTTT |

| Monoloop   | $M_2(B) = 2M_1(B)$ | TTTNTTTTTNTTT  |

| Mono-other | All other mono-    |                |

| Bi-        | $M_1(B) < M_0(B)$  |                |

| Bistable   | $M_1(B) < M_2(B)$  | NNNNTTNTNTTTT  |

| Bibiased   | $M_2(B) = 2M_1(B)$ | TTTTTTNNNNNN   |

| Other      | All other behavior |                |

Table 2.1: Branch Behavior Definitions

that branch which only includes outcomes of the branch reached by that path. Path filtered local history is used to study branch outcomes relevant to correlating predictors.

Because many branches may share PHT or BHT entries, branch predictors are subject to *collisions* which hurt branch prediction accuracy. A collision occurs when a branch uses some predictor entry it had previously updated but had since been updated by some other branch.

If every path of every branch had its own PHT entry, the pattern index computed using a simple hashing would have to be k + b bits long, where  $2^b$  is the maximum number of static branch instructions allowed. For some reasonable k, the size of this PHT would be wildly impractical. This is the reason *outcome history hashing* is used to generate a reasonably sized path. Call an *optimal outcome history hash* one that yields the highest branch prediction accuracy for a given PHT size. The GHR XOR PC hash of the GShare predictor is a sound approach since it enables the path to be influenced by both the static branch and the global history. However, there may be better outcome history hashing allowing for accuracies closer to the optimal. Understanding branch behaviors may allow for better hashing techniques, but analyzing it out of the context of weakening is beyond the scope of this study.

### 2.3 Branch Behavior

There are several behaviors exhibited commonly by branches. Classification of branches by their behavior helps bring about understanding as to how branches are weakened. Define B as the full outcome sequence of some static branch. Let  $M_0(B)$  denote the number of times B is mispredicted when using a *perfect static predictor*. A perfect static predictor has prior knowledge of the most frequent direction in B and always predicts the branch in that direction. Let  $M_1(B)$ and  $M_2(B)$  denote the number of times a dynamic bimodal predictor mispredicts the branch with a 1-bit saturating counter and 2-bit saturating counter, respectively.

The definitions of several branch behaviors are given in Table 2.1. Branches that favor a static prediction are named with the prefix *mono-* while those that prefer dynamic prediction are named with *bi-*. Typically in literature, the term *biased* is used to describe what is referred to here as monostable behavior when *B* contains all taken or all not-taken outcomes. The monoloop behavior is typically referred to as just a *loop* behavior, when *B* contains all similar outcomes separated by single opposing outcomes. Monostable and monoloop branches are predicted accurately with a bimodal predictor. Monoloop branches are predicted best with a 2-bit saturating counter, since using a 1-bit saturating counter causes an extra misprediction of the branch after every loop exit. This may be in part the reason why most branch predictors employ 2-bit counters as opposed to other sizes. Two mono- branches are called *unanimous* if their favored outcomes are in the same direction. The branches are said to be *dissonant* if their outcomes are in opposing directions.

Bistable and bibiased branches exhibit long *runs* of the same outcome, where a run is a subsequence of similar outcomes for a branch. A branch classified as bibiased has only large runs in its outcome history, therefore a predictor with a 1-bit saturating counter will yield half the mis-

predictions of a predictor with a 2-bit counter. The bistable class allows for a little more leniency. Branches can be classified this way if they are more accurately predicted with a predictor using a 1-bit saturating counter than one using a 2-bit saturating counter. Recall that for both of these behaviors, a 1-bit saturating counter outperforms a perfect static predictor.

Though the definitions above specifically refer to the behavior of a branch's local history, they apply to path filtered local histories as well. The implications of each static branch's local history behavior on a per-address predictor such as bimodal carry on to the branch's path filtered local histories on a correlating predictor. For the remainder of the section, branch local histories will be used to describe behaviors, but path filtered local histories apply as well.

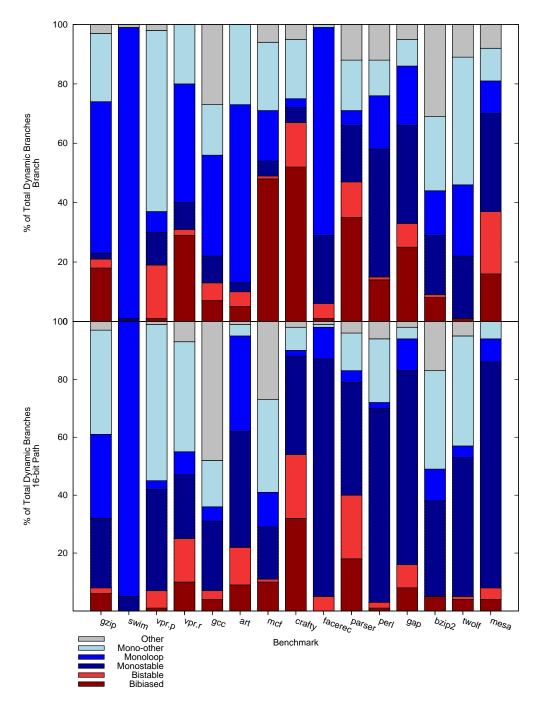

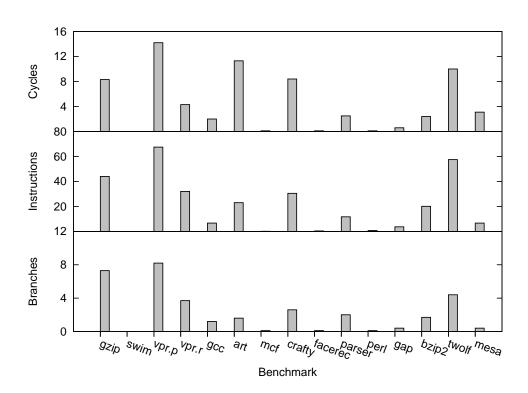

The plot in Figure 2.1 shows the measurement of branch behaviors as defined above for branches and 16-bit paths. Paths are constructed by XORing the 16 bits of the branch's PC with 16 bits of the global history, similarly to the way GShare constructs paths. Results are shown as percentages of dynamic branches. The benchmarks are those selected for this study and will be presented in detail later in Section 5.1 along with RSIML, the simulator used to collect results. These results are taken directly from RSIML output, which includes the classification in its distribution. Results are gathered via functional simulation. The way in which the classification is performed will now be discussed briefly.

The module of RSIML that classifies branches and path filtered local histories assigns a predefined class to each branch or path by using the branch prediction accuracies of a set of n *i*-bit saturating counter predictors. The counter predictors for each branch or path are incremented if taken and decremented if not taken. The most significant bit of the counter is used to make a prediction. If the first outcome of the branch or path is T, the counter is set to its maximum

Figure 2.1: Classification of Branches and 16-bit Paths (petdis.134, functional simulation)

value. If N, it is set to zero. Predictors of size 1 to 6 bits are used and in addition the total number of taken outcomes is tallied. Let  $M_i(B)$  denote the number of mispredictions of an *i*-bit counter predictor.  $M_0(B)$  is a special case that denotes the number of the less common outcome in the local history of a branch (this is the number of mispredictions yielded by a perfect static predictor). Let  $M_m(B)$  be the minimum number  $M_i(B)$  for all *i* from 0 to *n*. Branches are then classified in the following order.

Monostable if  $M_0(B) = 0$ ; else, Monoloop if  $M_0(B) - M_1(B)/2 < 2$ ; else, Mono-Other if  $M_0(B) <= M_m(B)$ ; else, Bistable if  $M_2(B) > M_1(B)$ ; else, Bibiased if  $M_m(B) > 1.01M_0(B)$ ; else, Other

Referring back to Figure 2.1, note that many of the benchmarks have significant amounts of bistable and bibiased branch and path behaviors. Branches of these types certainly prefer a speedy predictor update and suffer more training mispredictions, as will be explained in more detail further in the study when discussing weakening.

## 2.4 Branch Overlap and Update Lag

Branch *overlap* becomes important when studying weakening dealing with predictor update. A branch is said to overlap if one dynamic instance of the branch is predicted before a prior non-doomed instance of the same branch updates its predictor entry. This behavior is usually exhibited in tight loops when the system is executing many instances of a small group of static instructions. A path is said to overlap if one instance of the path is predicted before a prior non-doomed instance of the same path updates its predictor entry. This is referred to as *path overlap*.

Figure 2.2: Example of overlap taken from the bzip2 benchmark

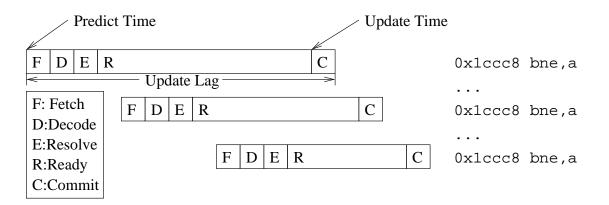

Call the time from when a dynamic branch is predicted to the time the predictor is updated the *update lag*. Update lag can be measured in many ways. Call the *cycle update lag* the number of cycles from predict to update of a branch. Call the *instruction update lag* the number of instructions fetched from predict to update of a branch. The *branch update lag* is the number of branches fetched from predict to update of a branch.

There are cases in which conventional systems are sensitive to update lag. An overlapping branch is shown in the pipeline execution diagram of Figure 2.2 with the update lag for the first instance marked. Assume this branch to be a simple if-then-else statement within some loop body. Other instructions and all squashed instances of the branch have been removed for clarity. Assume the branch to be bistable. The first instance shown represents the beginning of a run. When this instance resolves, it squashes all subsequent instructions and fetches along the correct path (The instance does not commit right after resolving due to out-of-order execution). Notice that all other instances shown in the figure are fetched along the correct path, but do not see the update of the first instance. All the instances will mispredict. If the update lag were decreased by setting the predictor to update at resolve time, each instance will see all prior updates. The reduction of update lag causes the third instance to be predicted correctly. Situations like these

do not occur too often in conventional systems because branches usually commit soon after they resolve. It will be shown further in the study that lag and overlap are more relevant in a CIP.

Intuitively, branch overlap is expected to happen more frequently than path overlap. This is because when two instances of a static branch overlap, their paths may be different. Even so, there may still be plenty of path overlap in execution. This will be revisited and elaborated with data further in the study.

# Chapter 3 Control Independence

A non-doomed dynamic instruction is control independent (CI) of a candidate dynamic branch if it is fetched regardless of the direction of the candidate [LW92]. Instructions are control dependent (CD) if they are fetched on only one direction of the candidate.

Refer back to Figure 1.1. Recall that branch BGE is a difficult branch to predict, so the CIP may *protect* it, exploiting control independence so that fewer instructions are squashed when it is mispredicted. Branch BLT is the first branch control independent of BGE – meaning that it can be reached on all paths from BGE. The first instruction in the basic block belonging to BLT is called the *reconvergence point* of BGE. A conventional processor would squash, along with any other wrong-path instructions, the reconvergence point instruction and all subsequent instructions on misprediction of the protected branch. This is wasteful because these instructions are soon refetched after the squash. In the selected benchmarks used in this study, the number of cycles it takes a branch to resolve vary from 30 to 140, with the average being 40. Since there are 8 instructions fetched per cycle, this means that on average there are potentially 320 instructions that may be squashed upon a misprediction. Since many branches have reconvergence points nearby (usually less than 16 instructions [CTW04]) there is high potential benefit for CIPs.

There are several implementation issues of control independence that can ruin its potential for benefit. In the introductory example, the later squashed **taken path** block of code changed the value of register r3 before the squash. The CIP must re-execute the post-reconvergent instructions with the correct value of r3 (the value it was set to before the branch). This is just one

example of implementation issues that CIPs must address to maintain program correctness while fetching out of order. Realistic mechanisms implemented to maintain program correctness are required for any CIP implementation.

## **3.1 Implementation Issues**

#### 3.1.1 CD- or CI-First

There are two fetch techniques a CIP may implement. *CD-First* is a technique where a CIP fetches just as a conventional system would until a protected branch resolves. If it resolves correct, execution continues similarly to the conventional case. If it resolves mispredicted, only CD instructions are squashed. The correct path instructions will be fetched and executed while any post-reconvergent instructions are still in flight. Once the entire CD region is fetched, fetching continues at the point where it was at the moment just before the protected branch resolved. The post-reconvergent instructions may need to be re-executed in order to maintain program correctness. The example given in the introduction reflects this technique.

CIPs that employ the *CI-First* technique begin fetching post-reconvergent instructions immediately after fetching the protected branch. Once the branch resolves, the correct path CD region is fetched and executed. Similarly to the previous technique, after the CD instructions are fetched, the post-reconvergent instructions may need to be re-executed to maintain program correctness. Notice that this technique eliminates the need to initially predict a direction for protected branches and so there is no need to squash.

#### **3.1.2 Register Remapping and Speculative Execution**

Dynamically scheduled processors map an instruction's destination register to a freshly allocated physical register and read mappings for the instruction's source registers. This mapping enables

instructions that write the same architected register to execute out of order. Since they write different physical registers, no data is lost.

The mappings of instructions past the reconvergence point may depend on the path taken through the control dependent region (CDR). In execution, it is common to have register dependencies between the CDR and post-reconvergent instructions. The CIP may not be aware of these dependencies until a protected branch resolves. Once the correct CDR is fetched, the register mapping becomes defunct and must be repaired to maintain program correctness. Therefore, any CIP must take the steps needed to correct register mappings when performing a protected recovery.

Some CIP implementations correct the mapping using *injected instructions* [CV01, AZRRA07]. After executing the CD instructions and before continuing execution of post-reconvergent instructions, special MOV instructions will correct the mapping. The example at the beginning of this section refers to the register r3 of Figure 1.1. Assume the code in the figure is running on a CIP and that the "Taken Path" block was just squashed while the post-reconvergent code is still in flight. At this point, the MUL instruction has operated on the incorrect value of r3. To repair this, the CIP will inject a special instruction into the pipeline that will write the value of r3 to the value that it was before the incorrect CDR changed it. This way, post-reconvergent instructions may re-execute using the correct value.

Instructions that depend on registers that may be incorrect must be executed speculatively until any downstream CD region resolves. Once the register mapping is correct, dependent instructions are re-executed. Furthermore, instructions that consume data from these instructions must also be re-executed, and so on. When a branch is re-executed, *vacillation* may occur. A branch vacillates when it changes its resolved direction due to re-execution. It is possible for a single instance of a branch to vacillate more than once. Vacillation is a very important overhead of CIPs. Its impact to combat certain types of weakening will be elaborated further in the study.

#### **3.1.3** Finding the Reconvergence Point

Reconvergence point detection is crucial in a CIP because it partitions the control dependent and control independent instructions for a protected branch. There are several techniques that find or predict it with reasonable accuracy both statically [SBV95] and dynamically [AZRRA07, CV01]. In one dynamic implementation [Kop08], each of the instructions on separate paths flowing from the protected branch are tagged with a different color for each path. The reconvergence point will be the first instruction tagged with both colors. Since the CD region is found dynamically in this way, the candidate branch must execute at least once on both paths. The mechanism also considers return instructions. If both paths from a protected branch lead to a return, the reconvergence point would then be the target of the return.

In a separate implementation [CV01], the reconvergence point can be found dynamically by searching for if then else and similar control flow structures. This is done by checking if the first instruction after a branch (not including delay slot instructions) is the target of a recent branch. Higher level constructs like if then else and case have easily identifiable reconvergence points. For example, the if clause and else clause are control dependent while anything after the if then else construct is control independent.

An advanced and highly accurate dynamic reconvergence prediction scheme was introduced in a study by Collins et al. [CTW04]. Branches are classified into several categories that are defined using analysis of program control flow graphs. For example, the most common case is for a branch's reconvergence point to occur later in code (meaning the reconvergence point's PC is greater than the branch's PC), while no instruction past the reconvergence point ever executes in the CDR for some level of the function call stack. This case is handled by the reconvergence predictor that skipper utilizes; however, skipper assumes certain compiled instruction layouts and only handles this single case. Another case handled in the study, though not as common, occurs when there are multiple return instructions in the CDR. An aggressive hardware implementation that categorizes branches into one of four behaviors, including those just presented, predicts reconvergence points with 99.9% accuracy for most of the studied benchmarks. A more feasible implementation of the predictor achieves over 95% prediction accuracy.

#### **3.1.4** Selective Squashing

In conventional systems, instructions are kept in the *re-order buffer* (or similar) from the time they are initially fetched until they are committed or squashed. The re-order buffer (ROB) is generally a FIFO that serves many critical functions. It assures that instructions commit in order (though they may execute out of order) and provides a means for recovery upon branch mispredictions or exceptions. Control independence exploitation poses a problem for conventional ROBs due to out-of-order fetching. The ROB may need to be redesigned to leave a gap for any later incoming CD instructions when a protected branch is fetched.

In many implementations, the size of the gap can be guessed similarly to the way reconvergence points are predicted. Accuracy in gap size detection is crucial since all instructions after the protected branch will have to be flushed if the gap size is inadequate. Furthermore, overshooting the gap uses unneeded space in the instruction window which may eventually cause the fetch unit to stall.

#### **3.1.5** Targeting Branches That Are Difficult to Predict

A CIP implementation may turn protection for branches on (and in some cases, off) during execution [RSI, AZRRA07, HR07, CV01] while another may protect every instance of certain static branches [CFS99, SBV95]. In the former case, referred to as a *dynamic CIP*, some method like *confidence estimation* (described in the next paragraph) is used to dynamically determine candidates for branch protection. In the latter case, called a *static CIP*, some type of instruction set architecture support is necessary to convey information regarding candidates for protection to the system. This information may be generated by the compiler by way of techniques such as static code heuristics or training input sets.

Confidence estimation is a technique used to detect if a branch is likely to be mispredicted. A study by Erik Jacobsen et al. presents several different one- and two-level confidence estimators [JRS96]. In one of the more successful one-level implementations, a table called the *Correct/Incorrect Register Table*, or CIR Table, is indexed similarly to a PHT to yield whether or not a branch is likely to mispredict. Each entry of the CIR Table is 4-bits, and each of these entries are initialized to all ones. A branch is considered likely to be predicted correctly if its CIR Table entry is 15. If a branch is predicted correctly, this entry is incremented (though it saturates at 15). If the branch is mispredicted, the entry is reset to 0. This relatively simple technique proves effective, isolating nearly 90% of mispredictions for selected benchmarks.

For a detailed comparative analysis on the confidence estimation method described above as well as several other techniques, consult the study by Grunwald et al. [GKMP98].

#### **3.1.6** Areas of Low Potential for Benefit

Not every application benefits from control independence. There will be little benefit in protecting branches with a very distant reconvergence point. The hindrance is due mainly to the amount of instructions that will be squashed on a protected recovery. A CIP may also not show much benefit if the CDR contains dependencies along the critical path. Though the post-reconvergent consumers will not be squashed, they will have to wait for the protected branch to resolve anyway. This generally increases the number of in-flight instructions and could cause the ROB to fill, stalling the fetch unit. Additionally, codes high in weakening and vacillation tend not to benefit and in some rare cases may exhibit performance degradation. Nevertheless, the majority of applications in the benchmark set selected for this study enjoy the benefits of control independence.

## 3.2 Snipper

Snipper is the CIP selected to be used for this study [Kop08]. It is named so because the term *snip* is used to refer to a control dependent region and its context. It attains speedup competitive with other researched CIPs, but does so in a unique way. As other CIPs choose where to exploit control independence based solely on branch confidence estimation [CV01, HR07] or detection of a reconvergence point [AZRRA07], snipper additionally uses a performance estimator to judge where exploiting control independence would be beneficial. This is helpful, as there are common situations where protecting branches may not result in speedup or may even hinder execution.

Protecting a branch is not beneficial when the branch is *execute-* or *commit-critical*. As defined in a study by Fields et al., a branch is execute-critical when there is a critical path data dependency in its CD region [FRB01]. Exploiting control independence in this case does not help since it is the branch's resolve time that is the bottleneck. In fact, mainly due to vacillation, covering

execute-critical branches can in some cases lengthen the resolve time of other branches, causing slowdown. A branch is commit-critical when it is the next instruction to commit and is preventing other instructions from being fetched because the ROB is full. In other words, the CPU cannot accommodate more instructions until the branch commits. If the system's instruction window size were larger, the branch would no longer be commit-critical.

Snipper protects branches only when its *reduction estimator* detects possibility for speedup. The reduction estimator used for this study, named *fetch-cycles*, evaluates whether or not a branch is execute- or commit-critical. It does so by way of bookkeeping certain characteristics of snips. For example, one of the values recorded is number of cycles spent fetching CI instructions from when a branch is mispredicted until it is resolved. The estimator also checks for a full ROB as well as whether or not the branch is near the head of the ROB. For more details on reduction estimators, a thorough study has been conducted by Koppelman [Kop08]. In the study it is shown that using such reduction estimators avoids slowdown in areas of execution where control independence cannot be effectively exploited.

At a lower level, snipper is a relatively simple CD-First CIP. Instructions are re-executed without changing their original register mapping. It does this by injecting special MOV [SI94] instructions called *pmoves* [KG99] that correct values in the mapped physical registers of control independent instructions. More than one pmove of any architectural register may have to be injected, depending on the number of times the register was written in the doomed CDR. Using the injected instructions allow post-reconvergent consumers to remain in the scheduler without having to be renamed, though they will need to re-execute.

Information for snips is kept in a *snip information table*. This table includes data such as the

candidate branch's PC, the reconvergence point, and a score used to determine whether or not exploiting CI for the candidate branch is detected as worthwhile. The reconvergence point is found using the coloring method described in Section 3.1.3. The colored tags are referred to as *cookies* in the snipper nomenclature. Information about cookie locations is kept in the *cookie table*.

Snipper turns protection of a branch on and off depending on whether or not potential benefit is detected. This is useful when the path to a protected branch changes at different points in the program; for instance, if the branch is in a subroutine called from many different parts of program execution. The reason for dynamic protection of this caliber is that, as has been said, sometimes exploiting control independence does not help. Snipper can also run as a static CIP so that each static branch is either always or never protected. More information regarding this is provided in Section 5.2.

The default predictor used by snipper is the YAGS predictor developed by Eden and Mudge [EM98]. This predictor correlates branches on global outcome history via the GHR. YAGS is not used in this study since the way in which it makes predictions is more complex than GShare. Nevertheless, the hybrid predictor used here performs just as well or better for most benchmarks and is more widely studied.

Snipper's approach to history update is to always insert CDR data into the GHR and use it for prediction and update, regardless of whether or not it is correct. This method is used because it yields better results than not including CDR data into the global history.

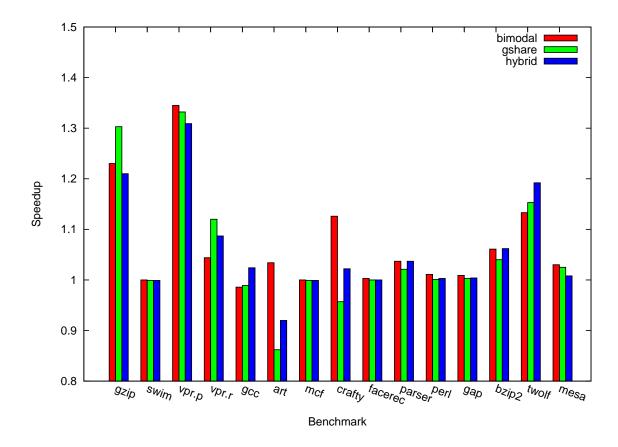

Figure 3.1 shows the speedup of a system exploiting control independence using snipper. Results are shown for the system branch predictor as bimodal, GShare, and hybrid.

29

Figure 3.1: Snipper Speedup (petdis.69, pad-cdr)

Snipper is described here only to the point of detail necessary to discuss branch weakening. For more details, consult the study by Koppelman [Kop08].

# Chapter 4 Prior Work

# 4.1 Limit Studies

Several studies have qualified that returns of exploiting control independence are worthwhile. A study by Lam and Wilson shows the amount of parallelism that can be obtained with control independence exploitation on an abstract system [LW92]. The system models used in the study enforce true data dependencies and control flow while ignoring memory disambiguation, nontrue data dependencies, and resource limitations. There are an unlimited number of functional units and instructions are fetched and committed in one cycle. The system model of interest for the purposes of control independence as studied here is the SP-CD-MF model. It is an ideal control independence system with multiple flows of control, meaning branches may execute out of order and only CD branches will be squashed on a misprediction. This model can be compared to another model in the study named SP. SP is simply a system modeled with only a branch predictor. Each system uses a perfect static predictor for branch prediction. Results show that the SP-CD-MF system can attain 23 times the parallelism of the SP system on average across the selected non-numeric benchmarks. When limiting control flow by forcing branches to execute in program order (this is the SP-CD model), the speedup over the SP system drops to about 15. The study concludes that parallelism is highly limited by control flow in certain programs and though branch prediction is vital in extracting reasonable amounts of parallelism from them, control independence significantly helps achieve large amounts of ILP.

Rotenberg et al. similarly compare a set of ideal machine models to evaluate several aspects of

control independence [RJS99]. The major difference from the Lam and Wilson study is that the models respect the need for register remapping and resources used by doomed CD instructions. As opposed to gathering results from a trace, a pipelined 16-way system with a GShare predictor is simulated. The model ignores the handling of memory disambiguation, output dependencies, and anti-dependencies. In addition to wasting fetch bandwidth, doomed CD instructions waste other resources by remaining in the instruction window until they are squashed. Data dependencies between doomed CDR instructions and post-reconvergent instructions are repaired in one cycle. It is reported that a model CIP with a 512-instruction window can cut down execution time 17% on average for the selected benchmark set.

## 4.2 Branch Classification and Prediction Techniques

Later in this study, weakened branches will be classified by the reason they are weakened. Additionally, predictor techniques will be offered to alleviate the preventable weakening by modifying paths and predictor update times. There has been a significant amount of prior works that identify ways in which path modification can improve prediction accuracy. Significantly less has been published in classification of branch mispredictions. The studies presented in this section contribute to the techniques used here to classify and reduce weakening.

An early study by Po-Yung Chang et al. classified branches by the rate at which each static branch is taken [yCHyYP94]. When branches are classified in this way, certain predictors can be chosen to predict certain classes of branches. For example, if a branch is classified to be mostly taken, a static predictor can often perform just as well or better than a correlating predictor in predicting the branch. The study introduced several hybrid schemes that performed as well or better than other branch predictors in literature at the time. In a more recent study by Michael Haungs et al., branches are classified by the rate at which they change direction [HSF00]. These studies use branch classification to build better predictors. In this thesis, however, classification is used to gain an understanding of why certain mispredictions are caused. There are no efforts taken to extract performance directly from the classification.

In a study by Kevin Skadron et al., a broad range of predictors are used to develop a taxonomy of mispredictions [SMC00] to help understand why certain branches are mispredicted. The selected predictors for the taxonomy are chosen carefully based on the information used to make a prediction. A dynamic branch is predicted through a sequence of chosen predictors. The first predictor that correctly predicts the branch instance determines the reason for which previous predictors in the sequence mispredicted it. For example, in the sequence of tests a branch may be mispredicted by a correlating predictor. The next predictor in the sequence could be a bimodal predictor. If the bimodal predictor yields a correct prediction, then it can be assumed that the correlating predictor's misprediction is due to training a new path. In the study, a new predictor scheme named *alloyed prediction* is developed to fill a hole in the taxonomy by categorizing mispredictions due to unavailability of both local and global history. Such study of branch predictor behavior is of great importance to understanding the causes of weakening.

Paths may be manipulated via code transformations to allow for better prediction accuracy. In a study by Cliff Young and Michael D. Smith [YS99], a code generation technique used to obtain better prediction accuracy for correlated branches is explored. A *history tree* is built from a program's *path profile* that contains all paths leading to a particular branch. A path profile is a type of lightweight program trace. Through a technique called *pruning*, the history tree is transformed so that the minimum amount of history to exploit correlation is revealed. Code is transformed using the pruned trees to allow bi- branches to be duplicated so that each copy of the branch is a mono- branch. The proposed code transforms could improve execution time by as much as 4% for selected SPEC CPU 1992 and 1995 benchmarks, though the technique slowed go and ijpeg down by 1-2% due to additional instruction cache misses.

Paths may also be manipulated dynamically to reduce mispredictions. Multi-threaded execution has the potential to weaken branches because, like in CIPs, branch outcome history is not available in contiguous program order. In a study by Jayanth Gummaraju and Manoj Franklin, the effects of single-program (instructions commit in order) multi-threading on branch predictors are explored [GF00]. It is established in the study that multi-threaded processors' branch prediction accuracy is negatively impacted due to several reasons. The study names the reasons insufficient, discontinuous, outdated, scrambled, or inaccurate history. These different reasons can cause up to five times more mispredictions for a predictor like GShare on select SPEC CPU 1992 and 1995 benchmarks. It is shown that predictors that use global history are affected much more than predictors like PAg that use local history, mainly because local predictors are less prone to outdated information. An extrapolation/correlation hybrid predictor is developed to address outdated and scrambled histories. The predictor has two components. The first component uses in-order speculative outcome data to make predictions of branches. This is helpful since update lag is relatively high for single-program multi-threaded execution. The second component, the correlation-based predictor, chooses one of several extrapolation predictors based on a thread-level prediction. The predictor reduces mispredictions by around 3% for most benchmarks.

In another study on path manipulation for multi-threaded processors, Bumyong Choi et al. built upon Gummaraju and Franklin's study by focusing on branch prediction for branches in short threads [CPT08]. Since small threads don't contain enough history for correlating predictors to function effectively, setting the GHR to a thread's initial PC upon spawning reduced the misprediction rate by around 29% per thread for a system with a GShare predictor running select SPEC 2000 benchmarks. This technique allows branches in short threads to correlate to the thread itself, allowing for less overall training. Leo Porter and Dean M. Tullsen generalized this technique for a conventional system [PT09]. In the study, it is found that setting the GHR to the value of the PC in certain situations – namely when leaving a loop – can reduce the misprediction rate by 12% per kilo-instruction for 32Kb predictors. A small 8Kb or 16Kb GShare predictor using this technique can perform as good as one twice its size.

## 4.3 Early Control Independence Processors

#### 4.3.1 Multiscalar

The Multiscalar processor is a multiprocessor which exploits ILP by using a compiler to split a program into many tasks, each of which is dynamically assigned to one of many processing units [SBV95]. Each processing unit sequentially executes instructions within its task, and the tasks themselves are loosely sequentially executed. Register mappings are kept correct through the use of compiler inserted masks that forward producer registers between processing elements to future tasks. This serves the same function as the injected instructions mentioned earlier. A task predictor speculatively assigns tasks to processing units. On a task misprediction, the offending task and all following tasks are squashed. However, a mispredicted branch within a task whose control does not leave the task will only cause its own task to be squashed. Because of this, the compiler's job of constructing tasks becomes very important. Multiscalar processors exploit enough control independence to enjoy 2-3 speedup in many chosen benchmarks. Evaluating the

weakening caused by using a multiscalar approach is difficult since the multiscalar compilergenerated code is significantly different from code compiled for a conventional processor with respect to control transfer.

#### **4.3.2** Dynamic Control Independence

In a study by Yuan Chou et al., a second ROB called the *Dynamic Control Independence*, or DCI, buffer is used to avoid refetching and renaming control independent instructions upon misprediction of a branch [CFS99]. The study explores both a CI First and CD-First implementation. It enables control independent instructions that have no CD data dependencies to be copied into the ROB from the DCI on protected recovery without needing re-execution, though branches are always re-executed. The implementation uses a GShare predictor that is stated to have "realistic" update, but no further information is given about how history is inserted into the GHR. The DCI study presents that in an 8-way superscalar processor with a 240-entry ROB can improve performance by about 15% among selected SPEC CPU 95 benchmarks [DR95]. Although in nearly every case the CI-First implementation outperforms the CD-First, the authors of the study claim that the latter appears to be more effective than the former since an unrealistic confidence estimator was used.

#### 4.3.3 Skipper

The Skipper implementation by Cher and Vijaykumar is a CI-First CIP [CV01]. Skipper protects only low-confidence branches using a confidence estimator that dynamically tracks branch performance [JRS96]. Skipper finds the reconvergence point of a protected branch by examining common compiler constructs such as those derived from if-then-else statements. If needed, register mappings are corrected using injected instructions. Downstream instructions are then reexecuted appropriately. In order to avoid the unfavorable effect out-of-order fetch has on branch prediction, the hybrid predictor used by Skipper is set to update at commit. Misprediction rates between Skipper and a conventional system are given in the study as the ratio of incorrectly predicted and unsuccessfully skipped branches to the number of total branches. However, more information is needed to determine if unprotected branches are being weakened, such as conventional accuracies discounting branches that snipper would protect.

## 4.4 Transparent Control Independence

The Transparent Control Independence (TCI) study implements a CD-First CIP where speculative CD regions of protected branches have less demand on the system pipeline [AZRRA07]. If data dependencies are broken due to a protected branch misprediction, a special afore-generated "recovery program" is fetched into the pipeline to correct broken register maps. TCI implements the behavioral dynamic scheme to find reconvergence points developed by Collins et al. [CTW04]. Protection of branches is governed by whether or not a branch's reconvergence point is detected. Post-reconvergent instructions that are data dependent on some speculative CD data are kept in a memory buffer near the pipeline. On resolved misprediction of a protected branch, the recovery program repairing register maps and the checkpointed data-dependent postreconvergent instructions are injected into the pipeline for re-execution. If the protected branch resolves correct, instructions are removed from the buffer. TCI leaves outcomes from mispeculated CD regions out of the GHR.

The TCI architecture achieves speedup of around 1.2 on average for an 8-instruction wide fetch unit among 15 SPEC CPU benchmarks. Out of 15 benchmarks, 10 suffered weakening. Among these, weakening raises misprediction rates by 7.7% on average, the worst case raising

the misprediction rate by 24%. TCI utilizes a complex perceptron predictor [JL01] to achieve a reasonably high prediction accuracy and to produce results that aren't inflated. It is explicitly mentioned in the study that the weakening is caused by gaps in the global history, and that the perceptron predictor is more resilient to these gaps than GShare. There is no further look into weakening, as TCI is said to have been designed to tolerate some extra mispredictions.

# 4.5 Ginger

The CD-First CIP Ginger developed by Hilton and Roth [HR07] uses a method called "tag rewriting" to eliminate the need to inject instructions on a protected squash. Doing this aims to lower hardware demand when register maps need repairing. It uses a confidence estimator to dynamically protect branches [JRS96]. Reconvergence points are found statically and are inserted into the pipeline as "hints", which are discarded at decode. After a protected squash, the pipeline is stalled so that register maps can be repaired.