# THE UNIVERSITY of EDINBURGH

This thesis has been submitted in fulfilment of the requirements for a postgraduate degree (e.g. PhD, MPhil, DClinPsychol) at the University of Edinburgh. Please note the following terms and conditions of use:

- This work is protected by copyright and other intellectual property rights, which are retained by the thesis author, unless otherwise stated.

- A copy can be downloaded for personal non-commercial research or study, without prior permission or charge.

- This thesis cannot be reproduced or quoted extensively from without first obtaining permission in writing from the author.

- The content must not be changed in any way or sold commercially in any format or medium without the formal permission of the author.

- When referring to this work, full bibliographic details including the author, title, awarding institution and date of the thesis must be given.

# Architectural Support for Persistent Memory Systems

Arpit Joshi

Doctor of Philosophy Institute of Computing Systems Architecture School of Informatics University of Edinburgh 2018

### Abstract

The long stated vision of persistent memory is set to be realized with the release of 3D XPoint memory by Intel and Micron. Persistent memory, as the name suggests, amalgamates the persistence (non-volatility) property of storage devices (like disks) with byte-addressability and low latency of memory. These properties of persistent memory coupled with its accessibility through the processor load/store interface enable programmers to design in-memory persistent data structures.

An important challenge in designing persistent memory systems is to provide support for maintaining crash consistency of these in-memory data structures. Crash consistency is necessary to ensure the correct recovery of program state after a crash. Ordering is a primitive that can be used to design crash consistent programs. It provides guarantees on the order of updates to persistent memory. Atomicity can also be used to design crash consistent programs via two primitives. First, as an atomic durability primitive which guarantees that in the presence of system crashes updates are made durable atomically, which means either all or none of the updates are made durable. Second, in the form of ACID transactions that guarantee atomic visibility and atomic durability.

Existing systems do not support ordering, let alone atomic durability or ACID. In fact, these systems implement various performance enhancing optimizations that deliberately reorder updates to memory. Moreover, software in these systems cannot explicitly control the movement of data from volatile cache to persistent memory. Therefore, any ordering requirement has to be enforced synchronously which degrades performance because program execution is stalled waiting for updates to reach persistent memory. This thesis aims to provide the design principles and efficient implementations for three crash consistency primitives: ordering, atomic durability and ACID transactions.

A set of persistency models have been proposed recently which provide support for the ordering primitive. This thesis extends the taxonomy of these models by adding buffering, which allows the hardware to enforce ordering in the background, as a new layer of classification. It then goes on show how the existing implementation of a buffered model degenerates to a performance inefficient non-buffered model because of the presence of conflicts and proposes efficient solutions to eliminate or limit the impact of these conflicts with minimal hardware modifications. This thesis also proposes the first implementation of a buffered model for a server class processor with multi-banked caches and multiple memory controllers. Write ahead logging (WAL) is a commonly used approach to provide atomic durability. This thesis argues that existing implementations of WAL in software are not only inefficient, because of the fine grained ordering dependencies, but also waste precious execution cycles to implement a fundamentally data movement task. It then proposes ATOM, a hardware log manager based on undo logging that performs the logging operation out of the critical path. This thesis presents the design principles behind ATOM and two techniques that optimize its performance. These techniques enable the memory controller to enforce fine grained ordering required for logging and to even perform logging in some cases. In doing so, ATOM significantly reduces processor stall cycles and improves performance.

The most commonly used abstraction employed to atomically update persistent data is that of durable transactions with ACID (Atomicity, Consistency, Isolation and Durability) semantics that make updates within a transaction both visible and durable atomically. As a final contribution, this thesis tackles the problem of providing efficient support for durable transactions in hardware by integrating hardware support for atomic durability with hardware transactional memory (HTM). It proposes DHTM (durable hardware transactional memory) in which durability is considered as a first class design constraint. DHTM guarantees atomic durability via hardware redologging, and integrates this logging support with a commercial HTM to provide atomic visibility. Furthermore, DHTM leverages the same logging infrastructure to extend the supported transaction size, from being L1-limited to the LLC, with minor changes to the coherence protocol.

### Lay Summary

Modern computer systems consist of two separate tiers to store data. The fast but volatile memory tier, which is also known as random access memory (RAM), stores data that programs can directly operate on. The slow but durable storage tier, which includes devices like hard disks and solid state drives (SSDs), stores durable data in files that users require accesses to across system restarts. Many important applications, that people interact with daily, need to perform frequent updates to their data in the storage tier. Consider a banking system for example, a large number of customers perform multiple banking transactions daily. All the updates because of those transactions need to applied to some database in the storage tier. Because the storage tier is slow, such applications have poor performance as opposed to applications that operate only on the data in memory.

Intel and Micron have recently announced the release of 3D XPoint memory. 3D XPoint belongs to a new class of memories known as persistent memory, as it combines the durability property of storage with low latency of memory. Persistent memory can significantly improve the performance of applications, like banking, which perform frequent updates to durable data. However, writing applications to operate on durable data in persistent memory is not straightforward. In the absence of appropriate support from the system, an application interrupted by a power failure could corrupt the durable data in persistent memory. For example, consider a system that is executing a banking transaction which consists of debiting money from account A and crediting it to account B. If a power failure happens while this transaction is executing, then it is possible that money is debited from account A but not credited to account B.

To avoid such scenarios, systems with persistent memory need to provide primitives that allow programmers to design programs in a fail safe manner. Such fail safe programs would keep all the data in persistent memory in a consistent state, even in the presence of system crashes. In this instance, a primitive called *atomic durability* is required which guarantees that either all updates are performed or none are performed. Let us consider the same example of the banking transaction discussed earlier. If the system supports atomic durability, it will guarantee that either the money is debited from A and credited to B, or it is neither debited from A nor credited to B. This thesis presents efficient designs of primitives like atomic durability, which allow programmers to write crash consistent programs for systems with persistent memory.

### Acknowledgements

I would like to begin by thanking *Para Brahman* for being the guiding light through every step of the way. This thesis would not have been possible without the contributions of many people, including the people I may not know or remember. I wish to thank all of them for, directly or indirectly, helping me in this journey.

Informatics has been a marvellous place for me to learn and grow as a researcher primarily because of the people around here. My advisor, Vijay Nagarajan, has been a wonderful mentor. This thesis would not have been possible without his guidance and generosity with time. Every time I would go to him with an idea, Vijay would ask the most pertinent and fundamental questions, answering which have helped me tremendously in shaping this thesis. Apart from learning the ropes of how to conduct and disseminate research, the most important lesson I have learnt from Vijay is to understand everything from first principles. This has not only helped me in grasping concepts at the most fundamental level but has also opened up a world of non-intuitive and fascinating connections between seemingly different areas.

I would also like to thank Marcelo Cintra and my co-advisor Stratis Viglas for their time and mentorship, for the stimulating discussions and most importantly for their critical feedback. It was an absolute delight working with Marcelo and Stratis. I am fortunate to have had the opportunity to interact with and learn from Boris Grot, Michael O'Boyle, Murray Cole and my thesis examiners Pramod Bhatotia and Margaret Martonosi. I would also like to thank everyone in ICSA for their help and support, especially Marco and Cheng-Chieh for the numerous technical discussions and for their invaluable help with gem5.

I would not be who I am today without Pinki my friend, philosopher and guide. Had it not been for her, I would not have been studying computer architecture, let alone pursuing a PhD. It was because of her unwavering support and constant nudging that I managed to apply on time and secure admission to the PhD program at The University of Edinburgh. Her companionship made my time in Edinburgh and the process leading up to this thesis an absolute delight. Her unshakable belief in me was critical, but even more important was her resolve to not let me lose focus of other important things in life, like health and family. Pinki taught me to aim for the stars and was always there to support me during difficult times. This thesis would not have been possible without those summer solstice dinners in the meadows or those hot meals delivered to the office during deadlines but more importantly, without those liberating and rejuvenating conversations while taking one of our numerous strolls through the beautiful alleys and parks of serene Edinburgh. Pinki deserves equal credit, if not more, for this thesis and I can only hope to make her as happy as she makes me. A new chapter in my life started on the day that Naisha was born and just looking at her face has been the highlight of my day ever since. A source of sheer happiness, Naisha has taught me that pursuing a PhD is much simpler compared to other things in life (like raising a child).

I would like to thank my teachers Monika Shah, Manish Chaturvedi and T.P. Singh who introduced me to the beauty of computer during my undergraduate studies at Nirma University. Special thanks to my friend Vishal for teaching me C programming, which was probably the first step in the journey leading up to this thesis. I would also like to thank my masters advisor Madhu Mutyam and my mentors Shankar Balachandran and V. Kamakoti for their help and guidance during my time at IIT Madras and for being a role model for me to look up to. A special thank you to all my colleagues at Intel, who taught me the practical side of things which helped me tremendously in identifying and formulating problems tackled in this thesis. And how can I forget my mentor Dipankar Nagchoudhuri whose practical advice has been invaluable to me.

Our time in the United Kingdom has been made special with the friendship and the company of Chahna and Dhvanil. Our friendship seems like the most natural thing and I would like to thank them just for being around. I am also grateful to have friends like Gaurang, Viral, Hardik, Kunal and Kalyan with whom you can discuss things and come back with a clarity of thought. Special mention for Dhara, who apart from sharing some delicious recipes has been a delightful friend. I would also like to thank Abhirup, Antonios, Manick, Praveen, Priyank, Raj, Rakesh, Saumay, Siddharth and Vasileios for all the interesting times and/or discussions in Informatics.

Finally, I would like to thank my family. I would like to thank my parents-in-law for having faith in me and for introducing me to satsang. I would like to thank Abhijit for being the mature little brother that he is and for always supporting me in whatever I wanted to do. And last but not the least, I would like to thank my parents for all their sacrifices and teachings. I am here because of them and anything good in me stems from them.

### Declaration

I declare that this thesis was composed by myself, that the work contained herein is my own except where explicitly stated otherwise in the text, and that this work has not been submitted for any other degree or professional qualification except as specified. Some of the material used in this thesis has been published in the following papers:

- Arpit Joshi, Vijay Nagarajan, Marcelo Cintra and Stratis Viglas, "Efficient Persist Barriers for Multicores", in 48th International Symposium on Microarchitecture, Waikiki, Hawaii, December 2015.

- Arpit Joshi, Vijay Nagarajan, Stratis Viglas and Marcelo Cintra, "ATOM: Atomic Durability in Non-volatile Memory through Hardware Support for Logging", in 23rd International Symposium on High Performance Computer Architecture, Austin, Texas, February 2017.

- Arpit Joshi, Vijay Nagarajan, Marcelo Cintra and Stratis Viglas, "DHTM: Durable Hardware Transactional Memory", in 45th International Symposium on Computer Architecture, Los Angeles, California, June 2018.

(Arpit Joshi)

To Pinki.

## **Table of Contents**

| 1 | Intr  | oduction                                                    | 1  |

|---|-------|-------------------------------------------------------------|----|

|   | 1.1   | Efficient Persist Barriers for Multicores                   | 4  |

|   | 1.2   | Hardware Support for Atomic Durability in Persistent Memory | 5  |

|   | 1.3   | Durable Hardware Transactional Memory                       | 6  |

|   | 1.4   | Integrating Primitives in the System Stack                  | 7  |

|   |       | 1.4.1 Programming Model                                     | 7  |

|   |       | 1.4.2 Compositionality of Primitives                        | 8  |

|   | 1.5   | Summary                                                     | 8  |

| 2 | Bac   | kground                                                     | 11 |

|   | 2.1   | Persistent Memory Technologies                              | 11 |

|   | 2.2   | Memory Consistency Models                                   | 12 |

|   | 2.3   | Memory Persistency Models                                   | 13 |

|   |       | 2.3.1 Buffering                                             | 14 |

|   | 2.4   | Atomic Durability                                           | 16 |

|   | 2.5   | Hardware Transactional Memory                               | 18 |

|   | 2.6   | ACID Transactions                                           | 19 |

|   | 2.7   | System Architecture and Evaluation                          | 20 |

|   |       | 2.7.1 System Architecture                                   | 20 |

|   |       | 2.7.2 Evaluation                                            | 21 |

| 3 | Effic | cient Persist Barriers for Multicores                       | 23 |

|   | 3.1   | Introduction                                                | 23 |

|   | 3.2   | Motivation                                                  | 24 |

|   |       | 3.2.1 Buffered Epoch Persistency                            | 24 |

|   |       | 3.2.2 System Configuration                                  | 25 |

|   | 3.3   | Persist Barrier Design                                      | 25 |

|   |      | 3.3.1   | Resolving Inter-thread Conflicts with IDT                | 26 |

|---|------|---------|----------------------------------------------------------|----|

|   |      | 3.3.2   | Resolving Intra-thread Conflict with PF                  | 29 |

|   |      | 3.3.3   | Epoch Deadlocks and their Avoidance                      | 30 |

|   | 3.4  | Persist | Barrier Implementation                                   | 31 |

|   |      | 3.4.1   | Epoch Flush Protocol                                     | 32 |

|   |      | 3.4.2   | IDT and PF Implementation                                | 35 |

|   |      | 3.4.3   | Hardware Extensions                                      | 36 |

|   | 3.5  | Enforc  | ring Persistency Models                                  | 37 |

|   | 3.6  | Experi  | mental Methodology                                       | 38 |

|   | 3.7  | Result  | s                                                        | 39 |

|   |      | 3.7.1   | Impact of Optimizations                                  | 39 |

|   |      | 3.7.2   | Epoch Conflicts                                          | 40 |

|   | 3.8  | Relate  | d Work                                                   | 41 |

|   | 3.9  | Summ    | ary                                                      | 42 |

| 4 | Ator | nic Dui | rability in Non-volatile Memory through Hardware Logging | 43 |

|   | 4.1  |         | uction                                                   | 43 |

|   | 4.2  | Motiva  | ation                                                    | 45 |

|   |      | 4.2.1   | Traditional Undo Logging                                 | 45 |

|   |      | 4.2.2   | Undo Logging with NVM                                    | 46 |

|   | 4.3  | ATOM    | I Design                                                 | 48 |

|   |      | 4.3.1   | Programming Model                                        | 48 |

|   |      | 4.3.2   | Baseline Design                                          | 49 |

|   |      | 4.3.3   | Posted Log Optimization                                  | 51 |

|   |      | 4.3.4   | Source Log Optimization                                  | 52 |

|   | 4.4  | ATOM    | I Architecture                                           | 53 |

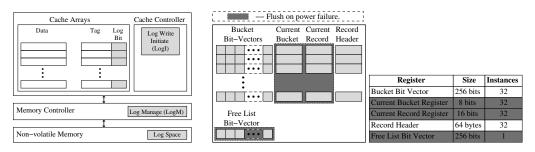

|   |      | 4.4.1   | Overview                                                 | 53 |

|   |      | 4.4.2   | Log Write Initiate (LogI) Module                         | 54 |

|   |      | 4.4.3   | Log Manage (LogM) Module                                 | 54 |

|   |      | 4.4.4   | Recovery                                                 | 57 |

|   |      | 4.4.5   | Log Allocation and Overflow                              | 58 |

|   | 4.5  | Hardw   | are Checkpointing                                        | 58 |

|   | 4.6  | Experi  | mental Setup                                             | 59 |

|   | 4.7  | ATOM    | I Evaluation                                             | 61 |

|   |      | 4.7.1   | Designs                                                  | 61 |

|    |        | 4.7.2    | Evaluation                                | 62  |

|----|--------|----------|-------------------------------------------|-----|

|    | 4.8    | Evalua   | tion of Hardware Checkpointing            | 67  |

|    |        | 4.8.1    | Designs                                   | 68  |

|    |        | 4.8.2    | Evaluation                                | 69  |

|    | 4.9    | Related  | d Work                                    | 72  |

|    | 4.10   | Summa    | ary                                       | 74  |

| 5  | DHI    | M: Du    | rable Hardware Transactional Memory       | 75  |

|    | 5.1    | Introdu  | action                                    | 75  |

|    | 5.2    | Related  | d Work                                    | 76  |

|    | 5.3    | DHTM     | 1 Design                                  | 78  |

|    |        | 5.3.1    | Logging for Durability                    | 79  |

|    |        | 5.3.2    | Integrating Logging with HTM              | 83  |

|    |        | 5.3.3    | Handling Overflow                         | 86  |

|    | 5.4    | Putting  | g it Together                             | 89  |

|    | 5.5    | Experi   | mental Setup                              | 94  |

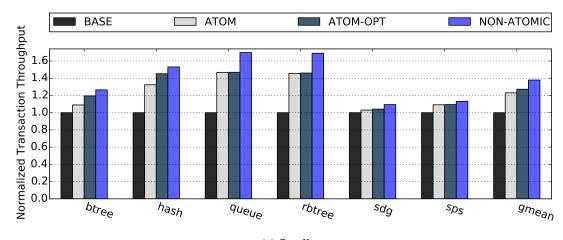

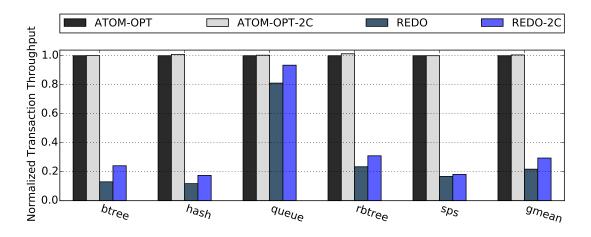

|    | 5.6    | Results  | 5                                         | 97  |

|    |        | 5.6.1    | Transaction Throughput                    | 97  |

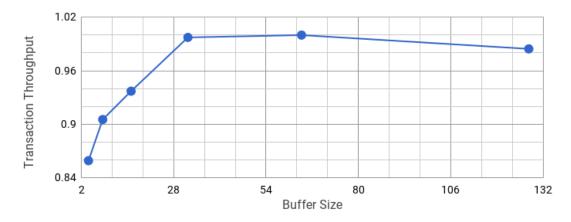

|    |        | 5.6.2    | Sensitivity to the size of the log-buffer | 99  |

|    |        | 5.6.3    | TPC-C and TATP Throughput                 | 99  |

|    |        | 5.6.4    | The Cost of Atomic Durability             | 100 |

|    | 5.7    | Summa    | ary                                       | 101 |

| 6  | Con    | clusions | s and Future Work                         | 103 |

|    | 6.1    | Critica  | l Analysis                                | 104 |

|    | 6.2    | Discus   | sion                                      | 105 |

|    |        | 6.2.1    | When to persist?                          | 105 |

|    |        | 6.2.2    | How to buffer?                            | 106 |

|    |        | 6.2.3    | Undo vs. Redo                             | 107 |

|    |        | 6.2.4    | Intelligent Memory Systems                | 108 |

|    | 6.3    | Future   | Work                                      | 108 |

| Bi | bliogr | aphy     |                                           | 111 |

# **List of Figures**

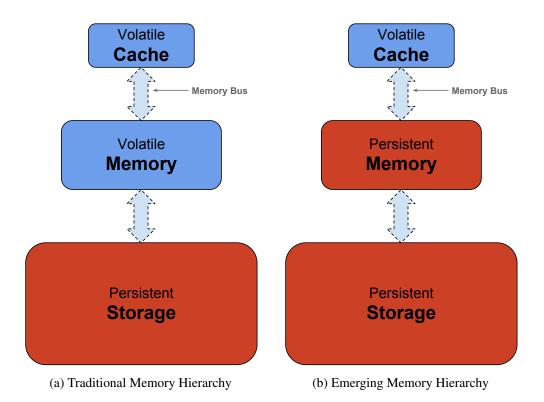

| 1.1 | Memory hierarchy with and without persistent memory                                                                                                                                                                                                                                                                                                                         | 2  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

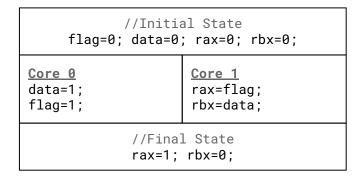

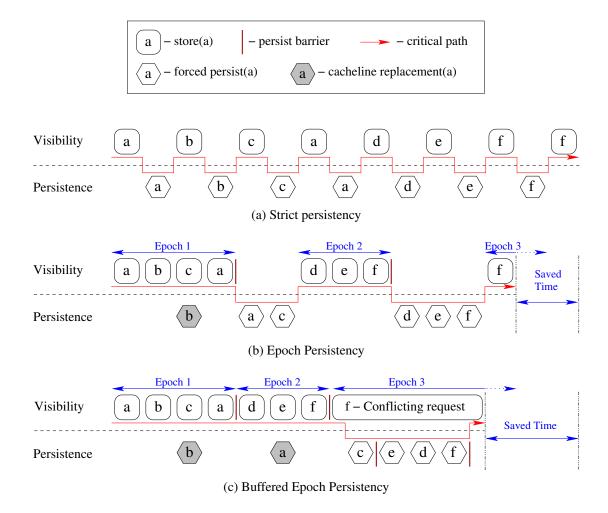

| 2.1 | A flag synchronization example where the final state is not valid for both SC and TSO                                                                                                                                                                                                                                                                                       | 13 |

| 2.2 | Dekker's algorithm where the final state is valid for TSO but not for SC.                                                                                                                                                                                                                                                                                                   | 13 |

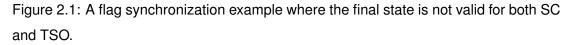

| 2.3 | Timeline for completion of memory requests for various persistency models.                                                                                                                                                                                                                                                                                                  | 15 |

| 2.4 | An example to demonstrate the concept of atomic durability                                                                                                                                                                                                                                                                                                                  | 17 |

| 2.5 | System Architecture.                                                                                                                                                                                                                                                                                                                                                        | 20 |

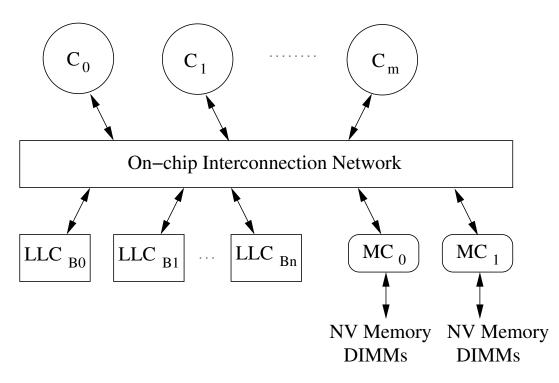

| 3.1 | System Configuration: Multiple cores (C), a volatile shared multi-<br>banked last level cache (LLC) and multiple memory controllers (MC)<br>connected by an on-chip interconnection network                                                                                                                                                                                 | 26 |

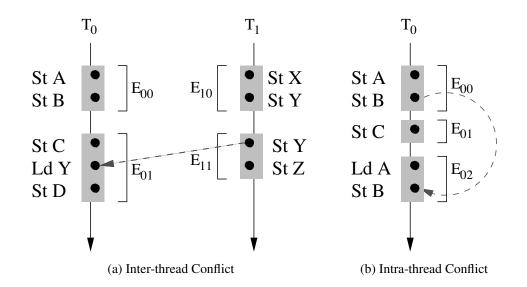

| 3.2 | Examples illustrating epoch conflicts. (a) Highlights inter-thread con-<br>flict where epoch $E_{01}$ tries to read cache line <i>Y</i> modified in epoch $E_{11}$<br>(b) Highlights intra-thread conflict where epoch $E_{02}$ tries to modify<br>cache line <i>B</i> modified in epoch $E_{00}$ .                                                                         | 27 |

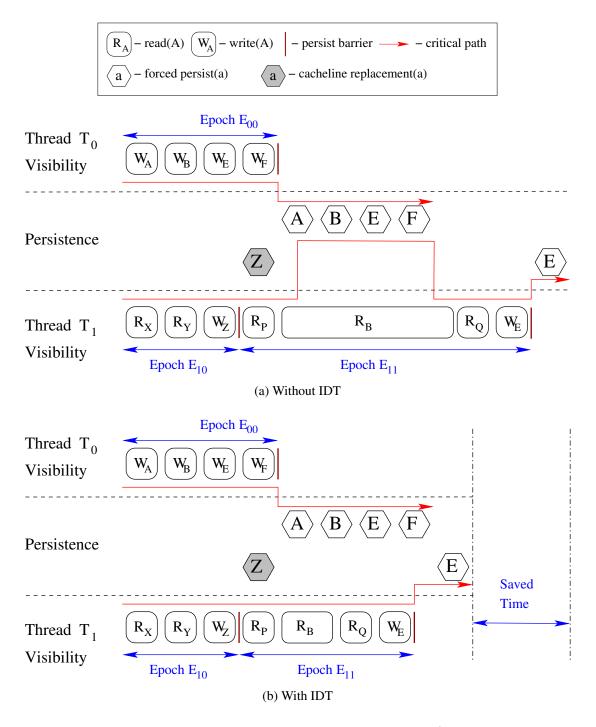

| 3.3 | Example showing the benefit of IDT optimization. (a) Shows an ex-<br>ample of how completion of conflicting requests is delayed waiting for<br>persist of source epochs to complete. (b) Shows with the same example<br>that by reducing the completion time of conflicting request and allow-<br>ing the source epoch to persist offline, while enforcing persist ordering | 20 |

|     | constraints, IDT improves performance                                                                                                                                                                                                                                                                                                                                       | 28 |

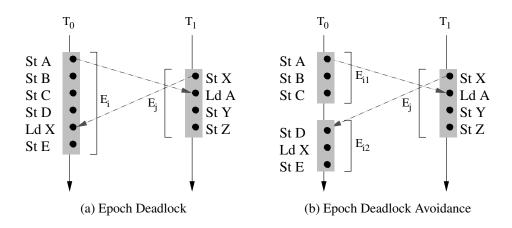

| 3.4  | (a) Shows an example of persistent epoch deadlock. Epoch $E_i$ and $E_j$          |    |

|------|-----------------------------------------------------------------------------------|----|

|      | belonging to threads $T_0$ and $T_1$ respectively have a circular dependence.     |    |

|      | $E_j$ reads cache line A modified by $E_i$ and $E_i$ reads cache line X modi-     |    |

|      | fied by $E_j$ . (b) Possible epoch deadlock between epochs $E_i$ and $E_j$ is     |    |

|      | avoided by splitting the ongoing epoch $E_i$ into epochs $E_{i1}$ and $E_{i2}$ on |    |

|      | detecting conflict with epoch $E_j$                                               | 30 |

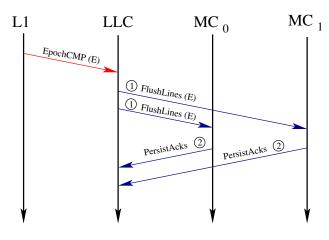

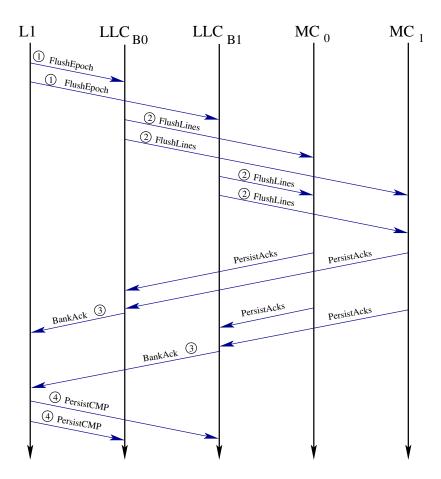

| 3.5  | Line diagram explaining the handshaking protocol for Epoch Flush                  |    |

|      | implementation in a multicore with monolithic last level cache                    | 33 |

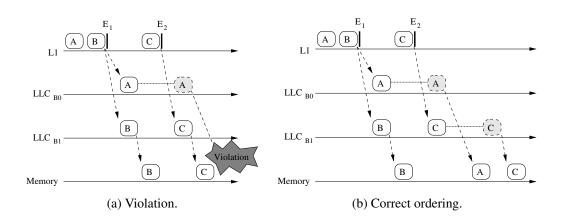

| 3.6  | (a) Shows an example of how epoch ordering constraint is violated.                |    |

|      | Cache line C belonging to epoch $E_2$ persists before cache line B be-            |    |

|      | longing to the previous epoch $E_1$ . (b) Shows the correct enforcement           |    |

|      | of epoch ordering constraints. $LLC_{B1}$ delays persisting cache line C be-      |    |

|      | longing to epoch $E_2$ until all the cache lines belonging to the previous        |    |

|      | epoch $E_1$ have persisted.                                                       | 34 |

| 3.7  | Line diagram explaining the handshaking protocol for Epoch Flush                  |    |

|      | implementation in a multicore with multi-banked last level cache                  | 35 |

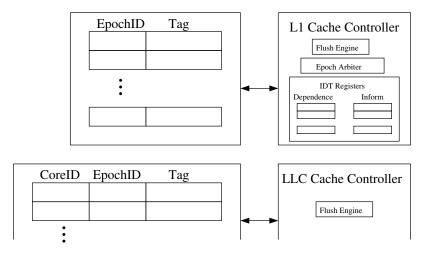

| 3.8  | Hardware extensions.                                                              | 36 |

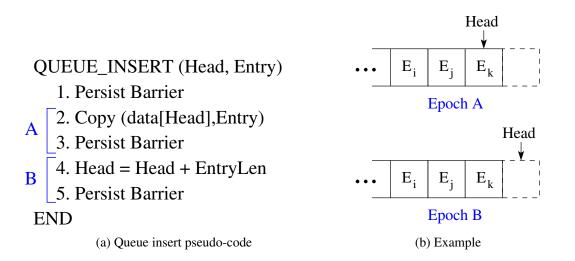

| 3.9  | (a) Pseudo-code for a queue insert operation using persist barriers for           |    |

|      | recovery in case of a system crash. (b) Example illustrating the status           |    |

|      | of the queue on completion of different epochs within the insert function.        | 37 |

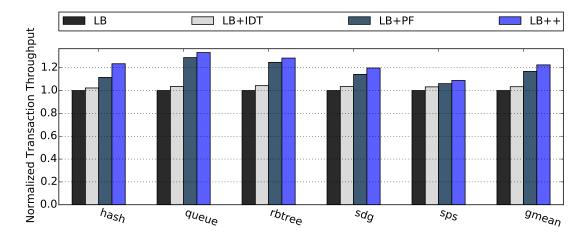

| 3.10 | Transaction throughput normalized to LB                                           | 40 |

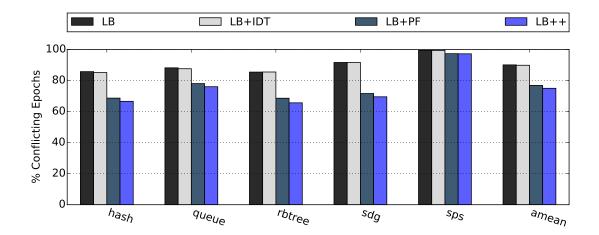

| 3.11 | Percentage of conflicting epochs (out of the total number of epochs)              | 41 |

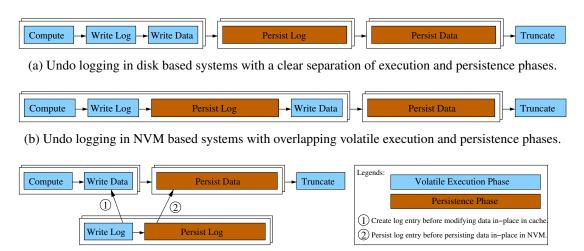

| 4.1  | Sequence of actions to be performed for undo logging in various sce-              |    |

|      | narios                                                                            | 46 |

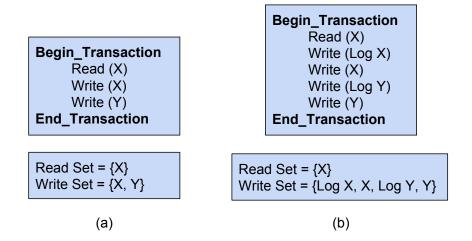

| 4.2  | Undo Log Programming Model.                                                       | 48 |

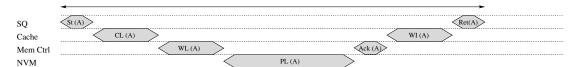

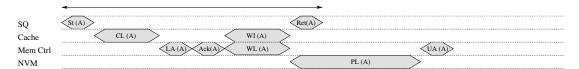

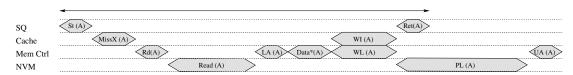

| 4.3  | Sequence of actions of store queue (SQ), cache, memory controller                 |    |

|      | (Mem Ctrl) and non-volatile memory (NVM) for undo logging in                      |    |

|      | NVM based systems.                                                                | 51 |

| 4.4  | ATOM Components.                                                                  | 55 |

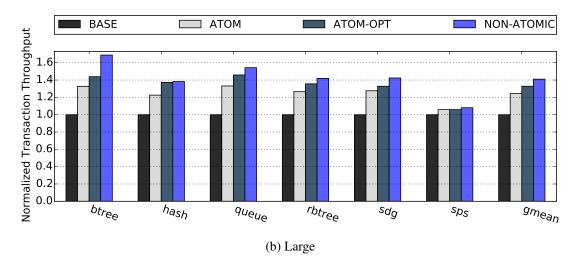

| 4.5  | Transaction throughput normalized to BASE for micro-benchmarks                    | 63 |

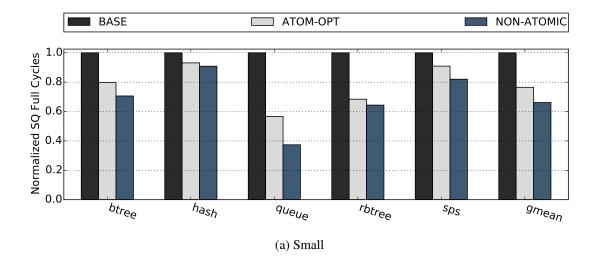

| 4.6  | SQ full cycles normalized to BASE for micro-benchmarks with small                 |    |

|      | dataset size                                                                      | 64 |

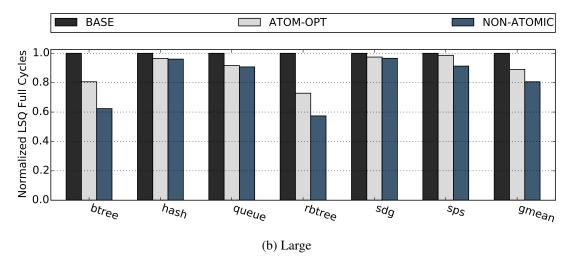

| 4.7  | Transaction throughput for REDO and ATOM-OPT designs normal-                      |    |

|      | ized to ATOM-OPT for benchmarks with small dataset size                           | 66 |

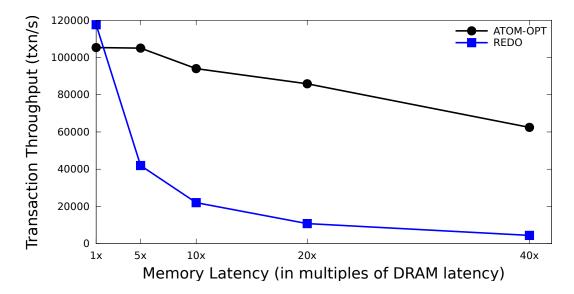

| 4.8  | Transaction throughput variation (ATOM-OPT vs REDO) with vary-          |     |  |

|------|-------------------------------------------------------------------------|-----|--|

|      | ing memory latency                                                      | 67  |  |

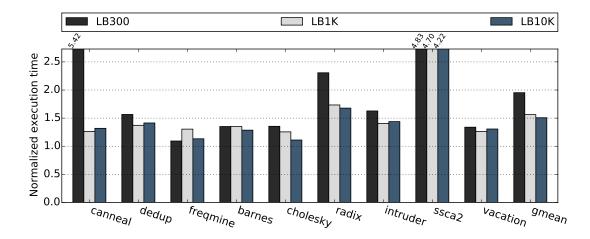

| 4.9  | Execution time with varying epoch sizes normalized to NP                | 69  |  |

| 4.10 | Execution time normalized to NP                                         | 70  |  |

| 5.1  | Working set sizes for transactions (a) without including durability log |     |  |

|      | and (b) with durability log                                             | 79  |  |

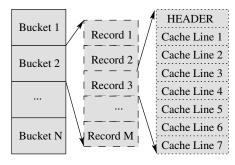

| 5.2  | Redo logging in hardware                                                | 82  |  |

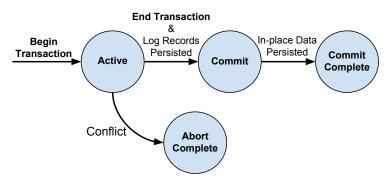

| 5.3  | Transaction States. A core can start executing subsequent non-          |     |  |

|      | transactional instructions after reaching Commit/Abort and can start    |     |  |

|      | a new transaction after reaching Commit Complete/Abort Complete         | 84  |  |

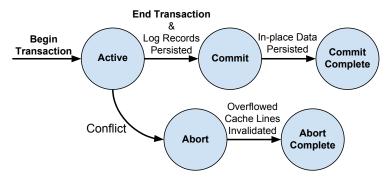

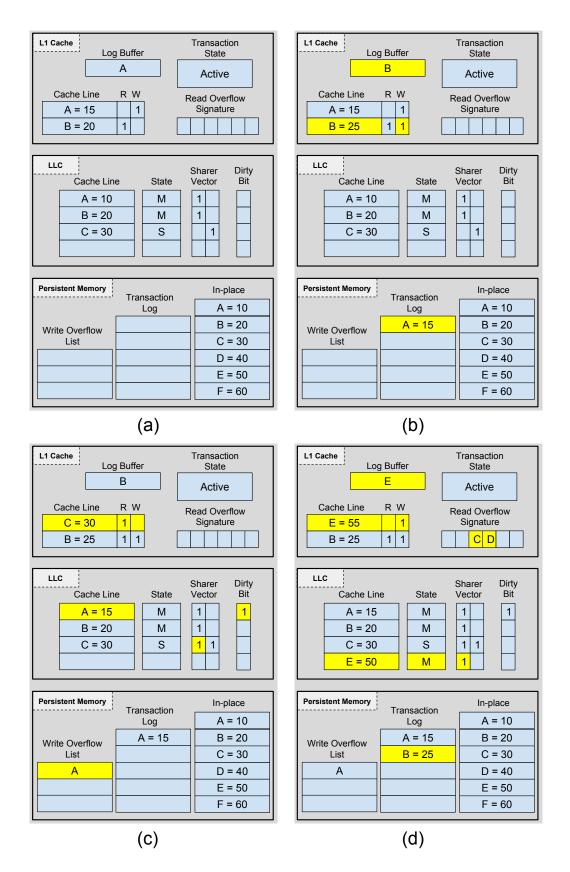

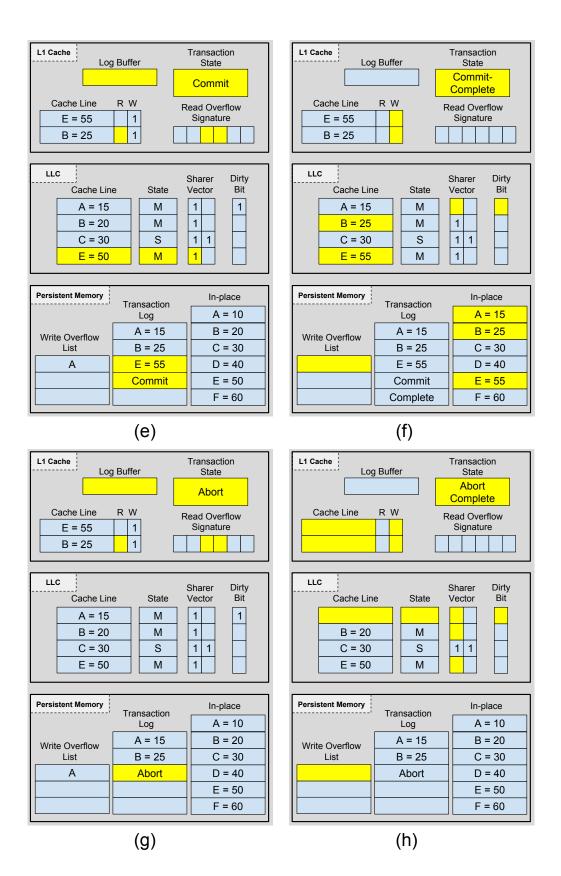

| 5.4  | Flow of a transaction - Part 1                                          | 91  |  |

| 5.5  | Flow of a transaction - Part 2                                          | 92  |  |

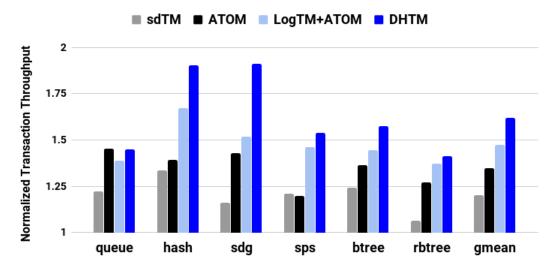

| 5.6  | Transaction throughput normalized to SO                                 | 98  |  |

| 5.7  | Normalized transaction throughput sensitivity towards log-buffer size   |     |  |

|      | for hash benchmark                                                      | 100 |  |

## **List of Tables**

| System Parameters                                                    | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Micro-benchmarks used in our experiments                             | 39                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| System Parameters.                                                   | 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Micro-benchmarks used in our experiments                             | 61                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| % of source logged cache lines for ATOM-OPT                          | 65                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TPC-C throughput normalized to BASE                                  | 67                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Classification of techniques supporting ACID updates on persistent   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| memory. (* Leverage hardware support for ordering to provide atomic  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| durability.)                                                         | 77                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Hardware Overhead.                                                   | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| System Parameters                                                    | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Benchmarks used in our experiments along with their descriptions and |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| write set sizes (# cache lines)                                      | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Abort rates for sdTM and DHTM designs                                | 98                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Transaction throughput for ATOM and DHTM normalized to SO for        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| TPC-C and TATP benchmarks.                                           | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Transaction throughput for NP and DHTM normalized to SO for hash     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| benchmark with varying memory bandwidth.                             | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                                                                      | Micro-benchmarks used in our experiments.System Parameters.Micro-benchmarks used in our experiments.% of source logged cache lines for ATOM-OPTTPC-C throughput normalized to BASE.Classification of techniques supporting ACID updates on persistent<br>memory. (* Leverage hardware support for ordering to provide atomic<br>durability.)Hardware Overhead.System Parameters.Benchmarks used in our experiments along with their descriptions and<br>write set sizes (# cache lines).Abort rates for sdTM and DHTM designs.Transaction throughput for ATOM and DHTM normalized to SO for<br>TPC-C and TATP benchmarks. |

## **Chapter 1**

## Introduction

Traditionally, computer systems have been designed to store data in two different tiers: storage and memory. The storage tier is characterized by the properties of non-volatility and higher density. Non-volatility guarantees that the data in the storage device will be retained even if power supply to the device is disconnected. Higher density means that, compared to memory, a higher number of bits can be stored per unit area. The memory tier on the other hand is characterized by two different properties: low latency and fine granularity. Low latency means that, compared to storage, it takes lesser time to access memory. Finer granularity means that, compared to storage which is typically accessed at a block or a page granularity, the contents of memory can be accessed at a finer granularity like a cache line. This two tier architecture has lead to the design of computer systems where programs typically operate on byte-addressable data in memory while storage is accessed with block based abstractions such as files and operating system managed paging. In summary, traditional computing systems have been designed and optimized for such a two tier architecture because neither memory nor storage possess all the desired properties.

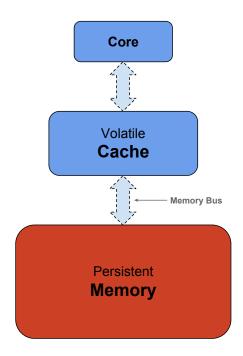

The emergence of multiple viable memory technologies like 3D XPoint [1], PCM [2], STT-MRAM [3], etc., has lead to a promising class of memory known as *non-volatile memory (NVM)* or *persistent memory* which combines the best properties of both storage and memory. It has non-volatility and density properties similar to storage while having access latency and access granularity characteristics similar to memory. Owing to these properties, persistent memory is widely expected to replace or complement the existing memory technology (DRAM) in future computing systems [4, 5]. We envision that a traditional memory hierarchy shown in Figure 1.1(a) with volatile caches, volatile memory and persistent storage would evolve into a sys-

Figure 1.1: Memory hierarchy with and without persistent memory.

tem shown in Figure 1.1(b) where only caches are volatile while memory and storage are persistent. In the rest of this thesis, we consider this new hierarchy (Figure 1.1(b)) as a representative memory architecture for emerging computer systems with persistent memory.<sup>1</sup>

Persistent memory, by virtue of being attached to the memory bus, allows programmers to access a non-volatile medium through the processor load-store interface. Thereby it opens up a new world of low overhead durability. Durability, also known as persistence, is the property that guarantees that data has safely been written to a non-volatile medium. Access to durable data in memory enables applications like inmemory persistent data structures, low overhead checkpointing, fast databases and key value stores, etc. Irrespective of the application, programmers need guarantees on what updates would have happened to durable data in the event of a system crash. This guarantee is necessary to maintain a property called *crash consistency*, which is required to ensure the correct recovery of program state and durable data after a system crash. For example, consider a program that is operating on an in-memory durable linked list. While adding a new node to the list, the program first writes to the new node and then

<sup>&</sup>lt;sup>1</sup>However, it is important to note that the principles presented in this thesis will equally apply to an architecture which has both volatile and persistent memory, without loss of generality.

updates a pointer to point to the new node. At the time of failure, the cache might have flushed the pointer update to persistent memory, but the write to the newly created node might still be in the volatile cache leading to an inconsistent state of the durable linked list. This inconsistency can be avoided by ensuring that the write to the newly created node reaches persistent memory before the pointer update. Therefore, to support crash consistency, systems need to provide guarantees on the order in which updates will reach persistent memory. We call this guarantee as the *ordering* primitive.

Ordering is a fundamental primitive that can be used to durably compose and maintain any arbitrary data structure. But it is not the only primitive, as many classes of programs including databases and file systems reason about crash consistency using higher level primitives like *atomic durability*. Atomic durability guarantees that, in the presence of system crashes, either all the updates will be made durable or none of them will be made durable. Consider a scenario where more than one cache line needs to be modified to perform a consistent update to a durable data structure. This is a common scenario applicable to many data structures including the previous example of linkedlist. While adding a new node to the linked-list, the write to the new node and the write to update the pointer can potentially map to two different cache lines. If the system crashes after only the pointer update reaches persistent memory, then the linked-list is left in an inconsistent state because of the partial update. However, if the writes to both the new node and the pointer are made durable atomically then this inconsistency can be avoided. Therefore, it is necessary to have primitives like atomic durability which guarantee that a group of updates will be made durable atomically.

ACID transactions is another higher level primitive which is widely used in databases [6]. ACID which stands for Atomicity, Consistency, Isolation and Durability reasons about atomic visibility and atomic durability of updates. Atomic visibility deals with concurrency and provides guarantees on the order in which updates will become visible to other threads. In summary, atomic visibility reasons about consistency with respect to other threads in the system whereas atomic durability reasons about consistency on programmers but also provide them with powerful abstractions to compose structured programs.

Existing memory systems do not provide any sort of ordering guarantees, let alone atomicity or ACID. In fact, these systems implement various optimizations which deliberately reorder updates to memory, at multiple levels in the memory hierarchy, to improve performance. For example, the order is which dirty lines (which have been written to) are replaced from the cache to memory is governed by replacement policies that are solely designed to maximize locality. Other optimizations like write coalescing, that reduce pressure on the memory bandwidth, can also lead to reordering if writes to different cache lines happen between multiple writes to the same cache line. Therefore, while implementing primitives for crash consistency it is desirable to allow reordering to the extent possible.

A key challenge with persistent memory systems is that software cannot explicitly control the boundary between volatile caches and persistent memory. In other words, modified data can move from volatile caches to persistent memory without the permission and even knowledge of software. Therefore, any ordering requirement has to be enforced synchronously. This means that if the software wants to ensure that all the updates till a given point have been made durable, it has to explicitly flush the modified data from caches to persistent memory before performing any further updates. If the software does not do so, a subsequent update might become durable before some of the previous updates and therefore violate the ordering requirement of crash consistency. Enforcing the ordering requirement synchronously stalls program execution waiting for updates to reach persistent memory and can therefore significantly degrade performance. In summary, the problem in persistent memory systems is that the information on when data moves from volatile to persistent domain is not available at the level of instruction set architecture abstraction (software). And therefore, we argue that for performance efficiency, the functionality of moving data from volatile to persistent domain should be implemented at a lower level of abstraction (in the hardware).

In the presence of fast persistent memory, this thesis aims to answer the question: *How to design architectural support for guaranteeing various crash consistency primitives while maximizing performance?* The rest of the chapter provides a brief overview of the main proposals and contributions of this thesis.

#### 1.1 Efficient Persist Barriers for Multicores

To ensure consistency, a set of persistency models [7] have been proposed in the literature that specify the order in which updates can be made durable. This order can be enforced using what is known as a *persist barrier*. A persist barrier ensures that all the updates that happened before the barrier will reach persistent memory before any of the updates that happen after the barrier. Implementing a persist barrier requires periodic flushing of cache lines from volatile caches to persistent memory. We extend the taxonomy of persistency models by adding buffering, which allows the hardware to enforce ordering in the background, as a new layer of classification. Buffering decouples program execution from persistence by allowing cache line flushes to happen out of the critical path. But, we show that current persist barrier implementations for buffered models [8] can add cache line flushes back to the critical path in the presence of conflicts. A conflict occurs when the same cache line is updated or accessed across an ordering point leading to an ordering dependency. We categorize these ordering dependencies as inter-thread and intra-thread conflicts and propose two solutions to mitigate them. We propose an Inter-thread Dependence Tracking (IDT) mechanism for dynamically tracking inter-thread dependencies in hardware, which allows us to reduce the overhead of preserving ordering in the presence of inter-thread conflicts. We also propose a Proactive Flushing (PF) scheme to write back cache lines proactively as opposed to the reactive approach of existing implementations. PF reduces the probability of encountering inter-thread and intra-thread conflicts in the future.

Our main contribution is an efficient persist barrier that integrates IDT and PF mechanisms and therefore reduces the number of cache line flushes happening in the critical path. We detail the complete implementation of this efficient persist barrier for a server class processor with multi-banked caches and multiple memory controllers. We evaluate our proposed persist barrier by using it to enforce a persistency model known as buffered epoch persistency. Experimental evaluations show that using our persist barrier reduces the probability of encountering conflicts by 15% and improves the performance by 22% on average over the state-of-the-art.

## 1.2 Hardware Support for Atomic Durability in Persistent Memory

One of the common ways of supporting atomic durability is to employ recovery mechanisms like write-ahead logging [9] as has been detailed in many proposals [10, 11, 12, 13, 14]. Write-ahead logging writes undo or redo log entries for all data updates and requires the ordering constraint that log writes happen before data updates (log  $\rightarrow$  data ordering). Current proposals for implementing logging, rely on software instructions to create log entries and enforce ordering. Since the software has no control over when a cache line is flushed out of the cache, any data update cannot

be performed until the corresponding log entry is made durable. This brings logging operations in the critical path and can result in significant performance degradation.

We aim to provide efficient support for atomic durability by moving logging operations out of the critical path. We observe that logging is, fundamentally, a data movement task associated with stores in a program and therefore it can be efficiently supported in hardware. Towards this end we propose ATOM: a hardware log manager to guarantee atomic durability through transparent and efficient logging which manages log allocation, ordering and log truncation in hardware. Our logging design is in many ways similar to the data movement tasks offloaded to a DMA (direct memory access) engine. Offloading logging to a log manager in hardware frees up core execution resources, and relieves the programmer from explicitly implementing the logging logic.

In particular, we implement two performance enhancing optimizations in ATOM. The posted log optimization allows ATOM to efficiently enforce the log  $\rightarrow$  data ordering constraint at the memory controller level, and thereby moves the ordering overhead out of the critical path. We also propose an optimization called source logging in which the memory controller eagerly performs logging for read exclusive requests, thereby eliminating wasteful data movement. We evaluate ATOM on a server class processor and show that it can improve performance by 27% to 33% for micro-benchmarks and by 60% for large-scale transactional workload (TPC-C) over a baseline undo log design. ATOM also compares favorably with a competing approach [15] which provides support for redo logging.

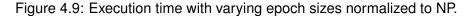

As an application of the primitives, we propose a new mechanism which couples the efficient persist barrier from the previous section with ATOM, for efficiently checkpointing programs in persistent memory systems. Our experiments using a subset of PARSEC, SPLASH and STAMP benchmarks show that doing so enables checkpointing of applications with only a 30% execution time overhead over a non-persistent execution which does not create any checkpoints.

### **1.3 Durable Hardware Transactional Memory**

In an ACID transaction, the updates within a transaction are made both visible as well as durable in an atomic manner. Existing proposals for supporting ACID transactions either support atomic visibility [10, 11, 13, 16] or atomic durability [16, 17, 18] or both in software and therefore suffer from significant performance overheads.

Here we ask the question, can we support both atomic visibility and durability in hardware for persistent memory systems? A promising approach to hardware ACID is to leverage commercially available Hardware Transactional Memory (HTM) to support atomic visibility. However, current commercially available HTM systems support only small transactions [19, 20, 21, 22, 23]; typically limited by the size of the L1 cache. Moreover, existing systems that support ACID by leveraging HTMs also perform log writes to support atomic durability [16, 17, 18]. This worsens the transaction size problem of HTMs by adding log writes to the transaction write set that the HTM has to track. Alternatively, proposals that do not add log writes to the transaction write set introduce significant changes to the cache hierarchy [24].

We propose the design of a Durable Hardware Transactional Memory (DHTM) which provides hardware support for both atomic visibility and atomic durability to overcome the above stated limitations. For atomic visibility DHTM employs an RTM [21] like HTM, whereas for achieving durability DHTM employs a hardware logging mechanism. Logging is supported in hardware via a bandwidth conserving implementation of a redo log, which enables faster commits. DHTM also extends the supported transaction size from being L1 limited to the size of the last level cache by leveraging the same logging infrastructure and without adding additional hardware.

Our evaluation shows that DHTM outperforms the state-of-the-art by an average of 26% on a set of micro-benchmarks and by a minimum of 21% for TATP and TPC-C. We believe DHTM is the first complete and practical hardware based solution for ACID transactions that has the potential to significantly ease the burden of crash consistent programming.

### **1.4 Integrating Primitives in the System Stack**

Programmers need mechanisms to employ the proposed primitives for writing crash consistent programs. In this section we first present the programming model for these primitives followed by a discussion on how they compose with each other.

#### 1.4.1 Programming Model

The proposed primitives can be integrated into the system stack by either extending the instruction set architecture (ISA) or by extending the semantics of existing instructions. The ordering primitive, for example, can be enforced by extending the ISA to include a new instruction, namely *persist barrier*. A persist barrier will guarantee that the updates that happened before the barrier will reach persistent memory before any of the updates that happen after the barrier. The atomic durability primitive can be implemented by extending the ISA with two instructions, namely *Atomic\_Begin* and *Atomic\_End* (§4.3.1), to demarcate the region of code that needs to be made durable atomically. Similarly, ACID transactions can be demarcated in programs by either extending the semantics of existing instructions like *XBEGIN* and *XEND* provided for HTMs [21] or by extending the ISA with two new instructions like *Begin\_Transaction* and *End\_Transaction* (§5.3). In addition to the HTM semantics of atomic visibility, these instructions also provide the atomic durability guarantee.

Reasoning about crash consistency is not straightforward and the usage of these primitives will depend on the properties of the application being made crash consistent. Therefore, in most cases, application programmers will either use these primitives directly or through a library [25] to compose crash consistent programs. However, in certain cases, the compiler might be able to insert them automatically [10].

#### 1.4.2 Compositionality of Primitives

The proposed primitives can either be used standalone, or the can be composed using other primitives to provide crash consistency. For example, a fundamental primitive like the ordering primitive can be used to guarantee atomic durability. Many mechanisms to provide crash consistency implement logging in software [11, 13]. These mechanisms leverage the ordering primitive, to enforce the log  $\rightarrow$  data ordering requirement of logging, to guarantee atomic durability. Similarly, as described in Chapter 5, atomic durability primitive can be leveraged to support ACID transactions in conjunction with a concurrency control mechanism (locks or transactional memory). Therefore, the ordering primitive can also be used to support ACID transactions. However, as we highlight in this thesis, composing a primitive using an existing primitive is inefficient and therefore we need to provide architectural support for each of these primitives.

#### 1.5 Summary

Emerging persistent memory, which combines the best properties of memory and storage, has the potential to enable new applications such as in-memory persistent data structures, low overhead checkpointing, fast databases and key-value stores, etc. To realize this potential, persistent memory systems need to provide support for primitives to guarantee crash consistency while minimizing restrictions on existing performance enhancing optimizations like reordering and write coalescing. In this thesis, we present efficient designs of three primitives: ordering, atomic durability and ACID transactions.

The rest of this thesis is structured as follows. We begin with the necessary background material in Chapter 2. In Chapter 3, we show how to design persist barriers to efficiently support the *ordering* primitive for server class processors. Then in Chapter 4, we present the design of an *atomic durability* primitive by way of hardware undo logging that not only moves log writes out of the critical path but also reduces redundant data movement in certain cases. We then show the design of a primitive to support *ACID transactions* in hardware that employs a hybrid version management mechanism and also extends the write set size of hardware transactions from being L1 limited to being LLC limited in Chapter 5. Finally, we conclude and provide perspectives on future directions in Chapter 6.

## **Chapter 2**

## Background

This chapter presents the background material necessary to understand the main contributions of this thesis.

### 2.1 Persistent Memory Technologies

We define persistent memory as a device that is non-volatile, that sits on the memory bus of the processor and that provides access latency and access granularity characteristics similar to DRAM main memory. There are multiple candidate technologies that can be used to realize persistent memory. These technologies can be broadly classified into two categories based on the mechanism they use to store data. Resistive memories, like Phase Change Memory (PCM) [2, 4] and Resistive Random Access Memory (ReRAM) [26, 27], store data by varying the resistance of the material that is used to make the memory cell. Magnetoresistive random access memory (MRAM) [28] and Spin-Transfer Torque MRAM (STT-MRAM) [3] on the other hand store data by changing the magnetic polarity of the material used to make the memory cell.

Although these technologies are promising, they pose challenges like limited endurance and high write power and/or latency [29]. Owing to these challenges, persistent memory is likely to have limited endurance and higher access latency compared to DRAM. Access latency is also expected to be asymmetric with write latency being higher than read latency. However, many of these technologies are in a very advanced state of development and in fact Intel and Micron have already announced products based on a new technology which they call 3D XPoint [1]. Additionally, multiple techniques have already been proposed to mitigate the endurance problem [30, 31, 32]. Therefore, we believe that persistent memory is highly likely to be available in computer systems in the near future.

#### 2.2 Memory Consistency Models

Most modern multicore systems support shared memory in hardware which allows multiple cores to operate on a single shared address space. To be able to write correct parallel programs in such systems, programmers need guarantees on the order in which memory accesses from a given core appear to perform (i.e. take effect) from the perspective of other cores in the system. A *memory consistency model* specifies this order. Four kinds of orderings are possible:

- 1.  $load \longrightarrow load$

- 2. load  $\longrightarrow$  store

- 3. *store*  $\longrightarrow$  *store*

- 4. *store*  $\longrightarrow$  *load*

Sequential consistency (SC), for example, requires that all the memory accesses happen in program order. So it enforces all the above memory orderings. Total store order (TSO) on the other hand, variants of which are supported by Intel, AMD and SPARC processors, enforces all but the last (*store*  $\rightarrow$  *load*) ordering constraint. By relaxing this constraint, TSO allows processors to commit stores by writing them to a local store queue and without waiting for them to be performed with respect to other cores. Let us better understand the differences between SC and TSO with examples. Consider the flag synchronization example shown in Figure 2.1. The final state where *rax* has the value 1 and *rbx* has the value 0 is not valid for both SC and TSO because it violates *store*  $\rightarrow$  *store* ordering. On the other hand, the final state shown for Dekker's algorithm in Figure 2.2 is valid only for TSO and not for SC. This is because TSO relaxes *store*  $\rightarrow$  *load* ordering, and therefore the values of *x* and *y* can be read before the stores to those variables are performed with respect to other cores.

For the purposes of this thesis, we are less concerned with the precise definition of memory consistency models; we are rather interested in one specific aspect of memory consistency models which is that they reason about when a store from one core will be performed (made visible) with respect to other cores. We will use this aspect as a tool to introduce and explain memory persistency models in the next section. For a broader perspective on memory consistency models, the reader is referred to the book by Sorin et al. [33].

| //Initial State<br>x=0; y=0; rax=0; rbx=0; |  |                                 |

|--------------------------------------------|--|---------------------------------|

| <u>Core 0</u><br>x=1;<br>rax=y;            |  | <u>Core 1</u><br>y=1;<br>rbx=x; |

| <pre>//Final State rax=0; rbx=0;</pre>     |  |                                 |

Figure 2.2: Dekker's algorithm where the final state is valid for TSO but not for SC.

### 2.3 Memory Persistency Models

Our focus in this thesis is on leveraging persistent memory technologies to enable fast persistence of programs. In order to enable correct recovery, program state in persistent memory needs to be in a consistent state. The definition of what constitutes a consistent state depends on the programming model or more specifically, on the *memory persistency model* [7]. One easy way to understand memory persistency models is to think about them in relation to memory consistency models. Just as consistency models allow us to reason about visibility of stores, persistency model allow us to reason about visibility of stores, persistency model defines the behaviour of an ordering primitive which specifies the order in which stores become durable. Pelley et al. [7] introduce three persistency models: Strict, Epoch and Strand persistency. Here we focus only on Strict and Epoch persistency.

Strict persistency (SP) couples memory persistency with memory consistency. So at the point of failure, whatever updates are visible are guaranteed to have been persisted.For example, TSO systems under strict persistency operate under the following rules:S1.) stores persist in program order and S2.) a store cannot be made visible until the

previous store (in program order) has persisted. A sequence of stores to different cache lines under SP is shown in Figure 2.3(a). As shown in the figure, SP creates persist ordering constraints at the level of each store operation. Hence, caches effectively have a write-through behaviour. Essentially, these fine grained persist ordering constraints conflict with two key optimizations employed in most modern processors. First, multiple stores to a cache line are coalesced in the caches and only written back to memory on a cache line replacement. Under SP since a store operation cannot be issued until the previous store operation persists (rule S2) multiple stores to a cache line cannot be coalesced (as shown in Figure 2.3(a) for cache line a). Second, processors reorder cache line persists to improve performance by exploiting temporal and spatial locality. This reordering happens in caches as well as in memory controllers. But under SP, cache lines have to be flushed in program order (rule S1), eliminating any possible performance gain from reordering of writes to memory.

**Epoch persistency**  $(EP)^{1}$  relaxes persist ordering constraints compared to SP and enforces ordering at the granularity of *epochs* [8]. An epoch is a contiguous group of instructions which are demarcated using a primitive known as a *persist barrier*. A system with EP operates under the following rules: **E1.**) stores belonging to different epochs persist in the order of their respective epochs and **E2.**) a new epoch cannot begin until all stores belonging to the previous epoch have persisted. Thus, EP allows coalescing of stores and reordering of persists for stores belonging to the same epoch. A sequence of stores to different cache lines under EP is shown in Figure 2.3(b). As shown in the figure, EP allows coalescing for cache line *a* which reduces the overall time taken to complete the sequence of accesses compared to SP. Moreover, since cache lines belonging to the same epoch can persist out of order, cache line *b* can persist before cache line *a*. In EP, persist operations are in the critical path of execution upon completion of an epoch. Even though EP allows write coalescing and reordering of persists within an epoch, it still has a high performance overhead over volatile execution.

#### 2.3.1 Buffering

The fundamental reason for overhead in SP and EP is that persist operations are in the critical path of execution (because of rules S2 and E2 respectively). To overcome this limitation, Pelley et al. [7] propose buffering as an optimization. With buffering,

<sup>&</sup>lt;sup>1</sup>Pelley et al. [7] do not explicitly differentiate between epoch persistency and buffered epoch persistency that we introduce in §2.3.1.

Figure 2.3: Timeline for completion of memory requests for various persistency models.

program execution is allowed to carry past the persist ordering point by only communicating the persist ordering dependency to hardware and not necessarily enforcing it. The hardware is expected to enforce these persist dependencies asynchronously in the background.

With the buffering optimization there are no guarantees on what updates would have been written to persistent memory at the time of a system crash. It only guarantees that any update that would have reached persistent memory, would have happened in the order specified by the underlying persistency model. In the absence of such guarantees programs need to be remodeled to ensure crash consistency with buffering. Therefore, we take a different approach and view buffering as mechanism that enables a new class of persistency models. The goal of buffered persistency models is to decouple program execution from persistence and thereby improve performance by moving persist operations out of the critical path.

Buffered strict persistency (BSP) [7] is a result of relaxing constraint S2 from strict

persistency. Although it removes persistence from the critical path, the problems of being unable to coalesce writes and reorder persists would still remain. These problems in turn would trigger frequent conflicts resulting in a larger percentage of persist operations being in the critical path. We present an optimized implementation of BSP in bulk mode with logging support in Chapter 4.

**Buffered epoch persistency** (BEP) is a result of relaxing constraint E2 from epoch persistency. Thus, BEP only requires that stores belonging to different epochs persist in the order of their respective epochs. BEP allows program execution to continue across epoch boundaries without waiting for previous epochs to persist. In this case, the cache sub-system has to ensure that epochs are flushed in the correct epoch order. Figure 2.3(c) shows the timeline for a sequence of stores under BEP. Persist barrier after *Epoch*1 does not prevent *Epoch*2 from executing before all the cache lines modified by *Epoch*1 persist. While the program execution continues, modified cache lines can persist naturally because of replacement as shown in the figure for cache lines *b* and *a*. In BEP, persist operations are not in the critical path of execution as long as there are no epoch conflicts. An epoch conflict is a scenario where a memory request triggers an epoch flush. In Figure 2.3(c) a store to cache line *f* conflicts with *Epoch*2 because cache line *f* has been modified in *Epoch*2 are flushed. Only epoch conflicts bring the persist operation in the critical path of execution for BEP.

## 2.4 Atomic Durability

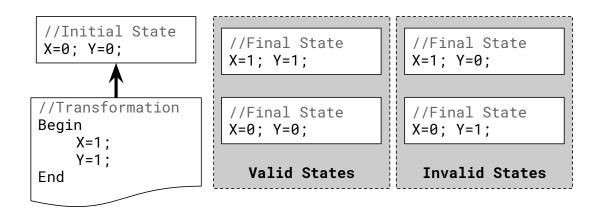

Atomic durability guarantees that for a group of writes, either all writes will be made durable or none of them. Consider the example shown in Figure 2.4. In the initial state, the durable variables X and Y have the value 0. If the shown transformation needs to be applied to the initial state atomically, then the only valid outcomes are either both X and Y have the value 1 or both of them have the value 0. That is, either all of the updates from the transformation are applied or none are applied. The states where partial updates from the transformation are applied are not valid. Storage systems use the atomic durability primitive as a tool to design crash consistent programs. There are multiple ways to implement atomic durability, and the most common among them are write-ahead logging (WAL) [9] and shadow paging [34]. While shadow paging is useful if writes belonging to an atomic update happen at page granularity, WAL works better for atomic updates consisting of scattered writes which happen at a cache line or

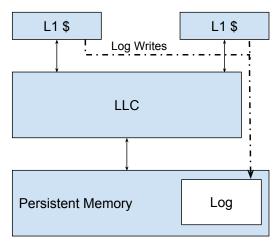

Figure 2.4: An example to demonstrate the concept of atomic durability.

finer granularity [10, 11, 12, 13, 14, 35].

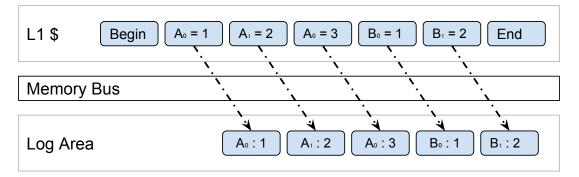

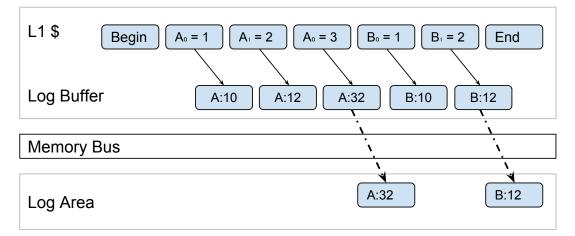

WAL is based on the principle of physical logging: maintaining a persistent copy of the old and new versions at all times during the atomic update so that state can be recovered to either of the versions. To implement physical logging, a log entry is created which consists of the address and the old or the new value of the data being modified. Additionally, a constraint is imposed that log entries should be made persistent before data entries. To enforce this constraint WAL requires support in the form of an ordering primitive. WAL can be implemented by using either a redo log or an undo log. When the system crashes in the middle of an atomic update, the atomic update can either be reapplied (for a redo log) or undone (for an undo log). There are different trade-offs in implementing a redo or undo based logging mechanism which we discuss next.