# Louisiana State University LSU Digital Commons

LSU Doctoral Dissertations

Graduate School

2012

## Programmable CMOS Analog-to-Digital Converter Design and Testability

Rajiv Soundararajan

Louisiana State University and Agricultural and Mechanical College

Follow this and additional works at: https://digitalcommons.lsu.edu/gradschool\_dissertations

Part of the <u>Electrical and Computer Engineering Commons</u>

#### Recommended Citation

Soundararajan, Rajiv, "Programmable CMOS Analog-to-Digital Converter Design and Testability" (2012). LSU Doctoral Dissertations. 3552.

https://digitalcommons.lsu.edu/gradschool\_dissertations/3552

This Dissertation is brought to you for free and open access by the Graduate School at LSU Digital Commons. It has been accepted for inclusion in LSU Doctoral Dissertations by an authorized graduate school editor of LSU Digital Commons. For more information, please contactgradetd@lsu.edu.

# PROGRAMMABLE CMOS ANALOG-TO-DIGITAL CONVERTER DESIGN AND TESTABILITY

#### A Dissertation

Submitted to the Graduate Faculty of the Louisiana State University and Agricultural and Mechanical College in partial fulfillment of the requirements for the degree of Doctor of Philosophy

in

The Division of Electrical and Computer Engineering

by

Rajiv Soundararajan

B.E. (B.S.), Bharathiar University, Coimbatore, India 2000

M.S.E., Arizona State University, Tempe, AZ, U.S.A. 2003

M.S.E.S., Louisiana State University, Baton Rouge, LA, U.S.A. 2009

December 2012

To my parents Soundararajan and Saraswathi Soundararajan,

To my wife ShreeRevathy Rajendran,

To my daughter Vibha Rajiv,

and

To my sister Lakshmi Priya and family,

Without their patience, love, values and understanding support, the completion of this dissertation would not have been possible.

#### **ACKNOWLEDGEMENTS**

I would like to express my sincere gratitude to my advisor and mentor, Dr. Ashok Srivastava for giving me the opportunity to work on this research, and also for his patience, support and guidance. I would have not completed this research without his suggestion, discussion and constant encouragement.

I would like to thank Committee members Dr. Suresh Rai, Dr. Jianhua Chen, Dr. Jin-Woo Choi and Dr. Shuangqing Wei for being part of my committee. I appreciate the suggestions I have received from my committee members in completing this research.

I am very thankful to the Department of Electrical and Computer Engineering for all the support and financial help during my current stay in LSU. I would also like to extend my gratitude to my fellow co-workers, Dr. Siva Yellampalli, Dr. Yao Xu, Dr. Yang Liu, and to my friends Karthik Balasubramanian and Raghavendra Murthi for their friendship and support.

I would like to thank my wife ShreeRevathy Rajendran, my daughter Vibha Rajiv and my parents Soundararajan and Saraswathi and to all my family members for their constant prayers and moral support throughout my life. Special thanks to my sister, brother-in-law and my nieces for all their love and support.

### TABLE OF CONTENTS

| ACKNOWLEDGEMENTS                                                                              | III  |

|-----------------------------------------------------------------------------------------------|------|

| LIST OF FIGURES                                                                               | VII  |

| LIST OF TABLES                                                                                | XII  |

| ABSTRACT                                                                                      | XIII |

| CHAPTER 1 INTRODUCTION                                                                        | 1    |

| 1.1 Motivation for Programmable Second Order Oversampling CMOS Delta-                         |      |

| Sigma ADC                                                                                     |      |

| Variation Effects  1.3 Motivation for On-Chip Functional Testability of CMOS ADC using Linear |      |

| Ramp Histogram Technique                                                                      |      |

| 1.4 Goals                                                                                     |      |

| <ul><li>1.5 Chapter Organization</li><li>1.6 References</li></ul>                             |      |

| CHAPTER 2 OVERVIEW AND LITERATURE REVIEW                                                      | 11   |

| 2.1 ADC Fundamentals                                                                          | 11   |

| 2.2 Classification of ADC                                                                     | 12   |

| 2.2.1 Nyquist-Rate Converters                                                                 | 14   |

| 2.2.2 Oversampled Converters                                                                  |      |

| 2.3 ADC Performance Metrics                                                                   |      |

| 2.3.1 Static Characteristics of ADC                                                           |      |

| 2.3.2 Dynamic Characteristics of ADC                                                          |      |

| 2.4 Delta-Sigma ADC                                                                           |      |

| 2.5 Testability of CMOS Data Converters                                                       |      |

| 2.6 References                                                                                | 24   |

| CHAPTER 3 PROGRAMMABLE SECOND ORDER OVERSAMPLING CMOS                                         |      |

| DELTA-SIGMA ANALOG-TO-DIGITAL CONVERTER                                                       | 27   |

| 3.1 Introduction                                                                              |      |

| 3.2 Programmable Second Order Oversampling Delta-Sigma ( $\Delta\Sigma$ ) ADC                 |      |

| 3.3 Second Order Delta-Sigma Modulator Theory and Design Implementation                       |      |

| 3.3.1 Discrete Analog Integrator Design Implementation                                        | 33   |

|           | 3.3.1.1 Design of Operational Amplifier                                                                                                             | 37  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3         | 3.3.1.2 Discrete Analog Integrator Results                                                                                                          | 39  |

| 3.3.2     | 1-Bit Quantizer (ADC) Design Implementation                                                                                                         |     |

| 3.3.3     | 1-Bit Digital-to-Analog Converter (DAC) Design Implementation                                                                                       |     |

| 3.4 Thi   | rd Order Programmable Decimator Theory and Design Implementation                                                                                    |     |

| 3.4.1     | Level Shifter Circuit                                                                                                                               |     |

| 3.4.2     | Clock Divider Circuit                                                                                                                               | 54  |

| 3.4.3     | Adder Circuit                                                                                                                                       | 58  |

| 3.4.4     | Delay Element                                                                                                                                       | 62  |

| 3.4.5     | Digital Integrator Block Design                                                                                                                     | 63  |

| 3         | 3.4.5.1 Coder Circuits                                                                                                                              | 65  |

| 3         | 3.4.5.2 Circuit for Programmability                                                                                                                 | 65  |

| 3.4.6     | Differentiator Block Design                                                                                                                         | 71  |

| 3.5 Res   | ults and Discussion                                                                                                                                 | 74  |

| 3.5.1     | Second Order Delta-Sigma Modulator                                                                                                                  | 74  |

| 3.5.2     | Second Order Delta-Sigma ADC                                                                                                                        | 76  |

| 3         | 3.5.2.1 K = 64 Case                                                                                                                                 | 79  |

| 3         | 3.5.2.2 K = 32 Case                                                                                                                                 | 80  |

| 3         | 3.5.2.3 K = 16 Case                                                                                                                                 | 84  |

| 3.6 Cor   | nclusion                                                                                                                                            | 84  |

| 3.7 Ref   | erences                                                                                                                                             | 85  |

| CHAPTER 4 | ΔI <sub>DDQ</sub> TESTING OF A CMOS DATA CONVERTER CONSIDERING PROCESS VARIATION EFFECTS                                                            | 88  |

| 4.1 Intr  | oduction                                                                                                                                            | 88  |

|           | lt-in Current Sensor for Delta I <sub>DDQ</sub> Testing                                                                                             |     |

| 4.2.1     | Proposed Design                                                                                                                                     |     |

| 4.2.2     | Circuit Implementation                                                                                                                              |     |

| 4.3 12-1  | bit DAC Design (CUT)                                                                                                                                |     |

| 4.4 Res   | ults and Discussion                                                                                                                                 | 97  |

| 4.5 Cor   | nclusion                                                                                                                                            | 101 |

| 4.6 Ref   | erences                                                                                                                                             | 102 |

| CHAPTER 5 | ON-CHIP FUNCTIONAL TESTABILITY OF CMOS ANALOG-TO-<br>DIGITAL CONVERTERS BY LINEAR RAMP HISTOGRAM<br>TECHNIQUE USING SYNCHRONOUS COUNTER AS REGISTER | 104 |

| 5.1 Intr  | oduction                                                                                                                                            | 104 |

|           | togram Technique                                                                                                                                    |     |

| 5.2.1     | ADC Parameters                                                                                                                                      |     |

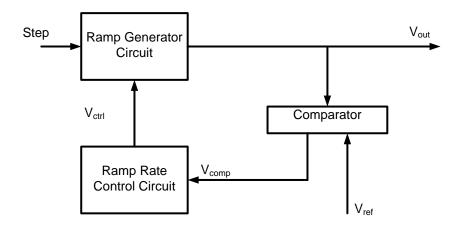

| 5.3 On-   | Chip Linear Ramp Histogram Design                                                                                                                   | 109 |

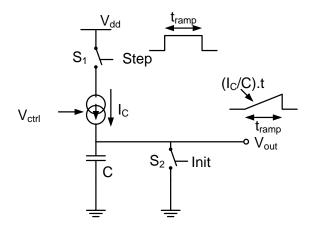

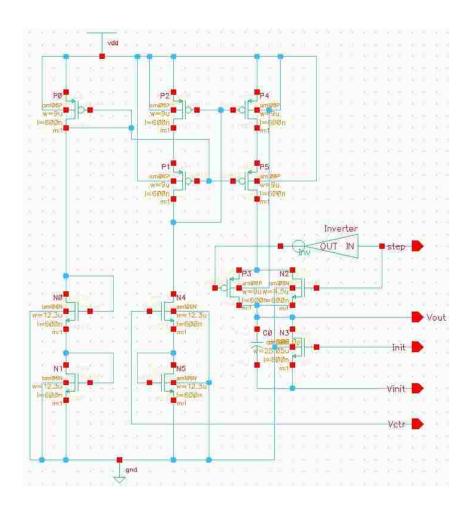

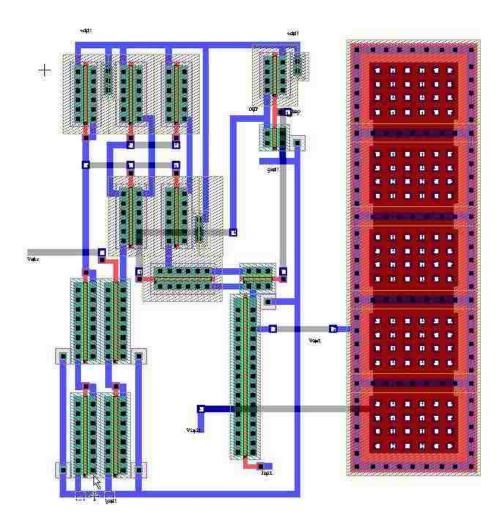

| 5.3.1     | Linear Ramp Generator Design Implementation                                                                                                         |     |

|           | V                                                                                                                                                   |     |

|           | V                                                                                                                                                   |     |

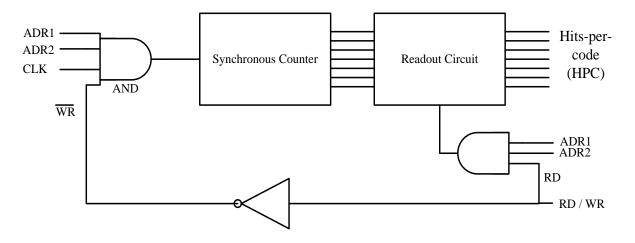

| 5.3.2      | Interface/Control Unit                                | 112   |

|------------|-------------------------------------------------------|-------|

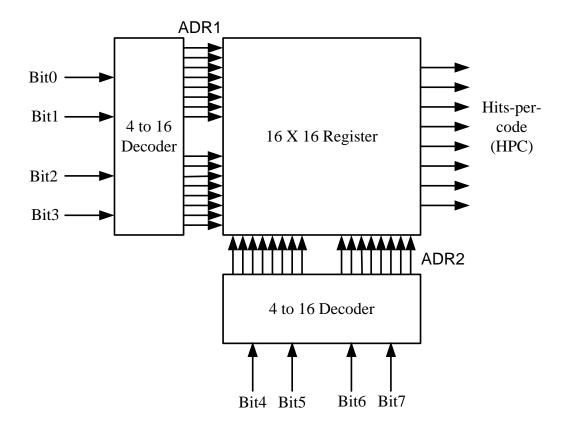

| 5.3.3      | Code Detection Unit (CDU) Design Implementation       | 112   |

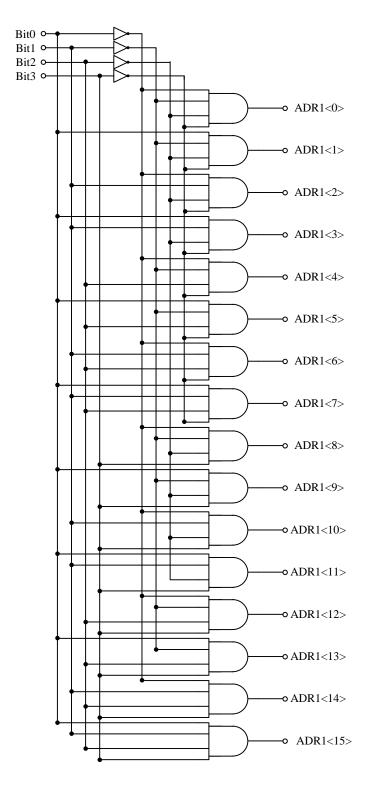

|            | 5.3.3.1 4-to-16 Decoder Design Implementation         |       |

|            | 5.3.3.2 Register Design Implementation                |       |

| 5.4 Re     | sults and Discussion                                  |       |

|            | nclusion                                              |       |

|            | ferences                                              |       |

| CHAPTER 6  | HARDWARE OPTIMIZED ON-CHIP FUNCTIONAL TESTABILITY     |       |

|            | OF CMOS ANALOG-TO-DIGITAL CONVERTERS BY LINEAR        |       |

|            | RAMP HISTOGRAM TECHNIQUE USING 6T-SRAM AS REGISTER    | R 128 |

| 6.1 Int    | roduction                                             | 128   |

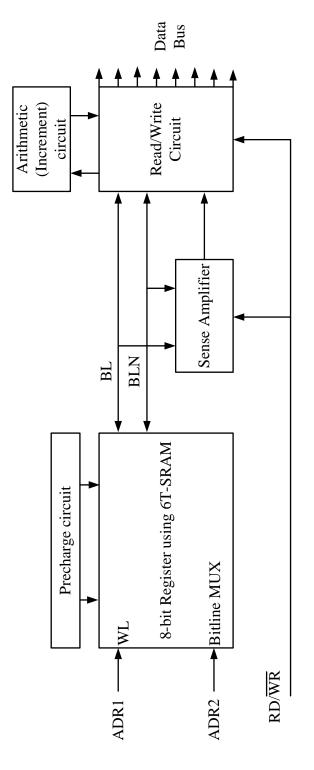

|            | de Detection Unit Design Implementation using 6T-SRAM |       |

| 6.2.1      | Register Design Implementation                        |       |

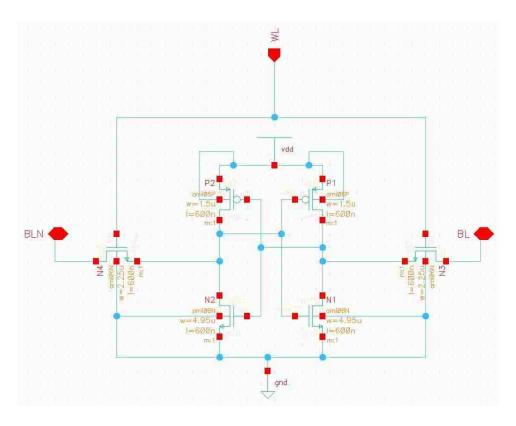

|            | 6.2.1.1 6T-SRAM                                       |       |

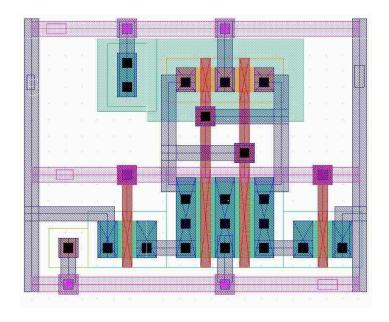

|            | 6.2.1.2 Precharge Circuit                             |       |

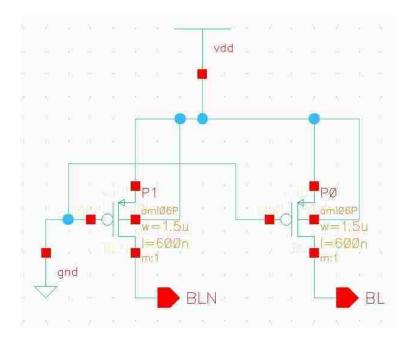

|            | 6.2.1.3 Sense Amplifier                               |       |

|            | 6.2.1.4 Read/Write Circuit                            |       |

|            | 6.2.1.5 Arithmetic Circuit                            |       |

| 6.3 Re     | sults and Discussion                                  |       |

|            | nclusion                                              |       |

|            | ferences                                              |       |

| CHAPTER 7  | CONCLUSION AND SCOPE OF FUTURE WORK                   | 149   |

| omm rent   |                                                       |       |

| 7.1 Co     | nclusion                                              | 149   |

|            | ope of Future Work                                    |       |

|            |                                                       |       |

| APPENDIX A | A: SPICE MOS MODEL PARAMETERS FOR 0.5μm N-WELL CMOS   |       |

|            | TECHNOLOGY FROM MOSIS (http://www.mosis.com/)         | 153   |

|            | \ 1                                                   |       |

| APPENDIX E | B: PERMISSION TO USE COPYRIGHTED MATERIALS            | 155   |

|            |                                                       |       |

| APPENDIX C | : TEST SETUP FOR ON-CHIP TESTABILITY OF CMOS ANALOG-  |       |

|            | TO-DIGITAL CONVERTER BY LINEAR RAMP HISTOGRAM         |       |

|            | TECHNIQUE USING SYNCHRONOUS COUNTER AS REGISTER       | 163   |

| VITA       |                                                       | 166   |

|            |                                                       | _     |

### LIST OF FIGURES

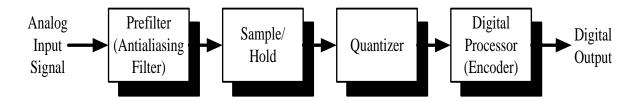

| Figure 2.1.  | Block Diagram of an ADC [1].                                                                                        | 13 |

|--------------|---------------------------------------------------------------------------------------------------------------------|----|

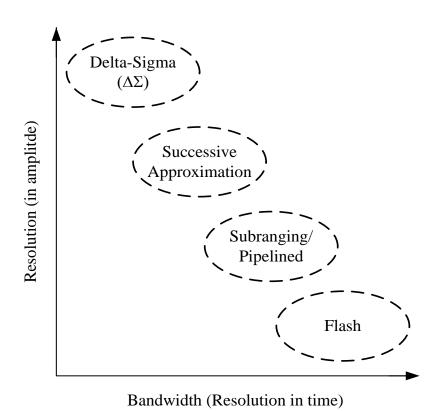

| Figure 2.2.  | ADC technologies comparative graph, with respect to resolution and bandwidth.                                       | 13 |

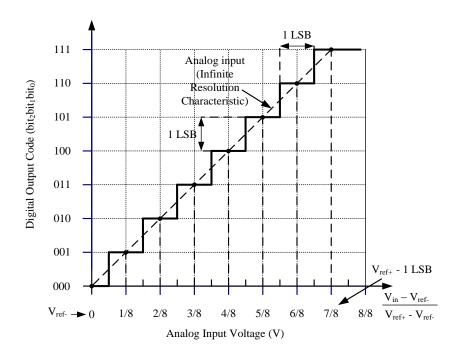

| Figure 2.3.  | Ideal input-output transfer curve of a 3-bit ADC.                                                                   | 16 |

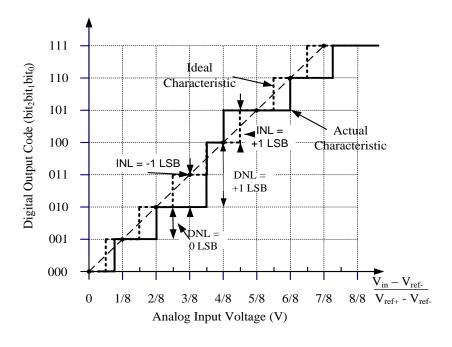

| Figure 2.4.  | DNL and INL illustration for a 3-bit ADC.                                                                           | 16 |

| Figure 2.5.  | Offset Error illustration for a 3-bit ADC.                                                                          | 18 |

| Figure 2.6.  | Gain Error illustration for a 3-bit ADC.                                                                            | 18 |

| Figure 2.7.  | Monotonicity illustration for a 3-bit ADC                                                                           | 19 |

| Figure 2.8.  | Block diagram of A/D converter.                                                                                     | 21 |

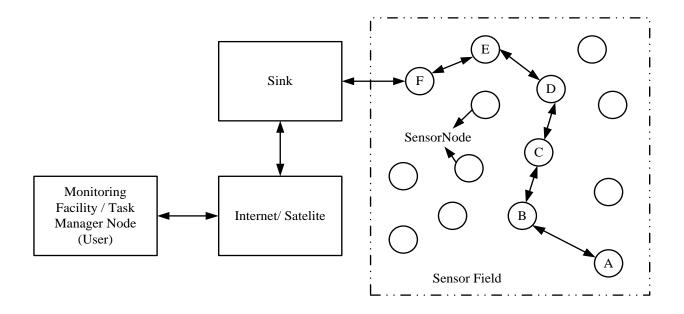

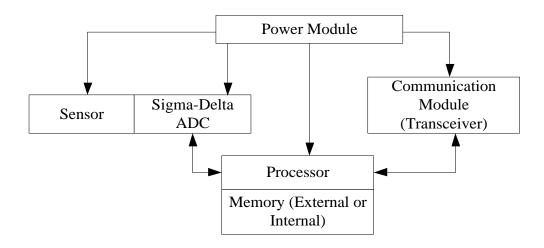

| Figure 3.1.  | Sensor network [4].                                                                                                 | 28 |

| Figure 3.2.  | Block diagram of a sensor node [4]                                                                                  | 28 |

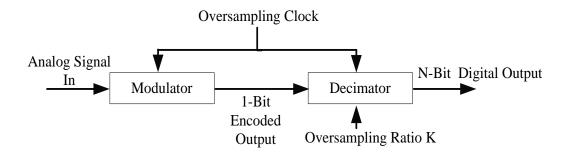

| Figure 3.3.  | Block diagram of a second order oversampled delta-sigma ADC [7]                                                     | 32 |

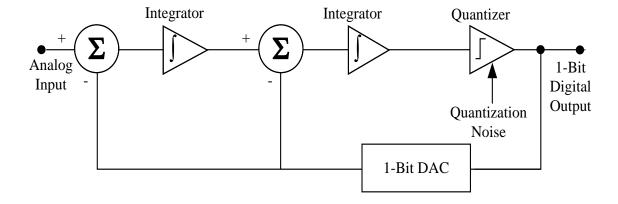

| Figure 3.4.  | Second order delta-sigma modulator [9].                                                                             | 32 |

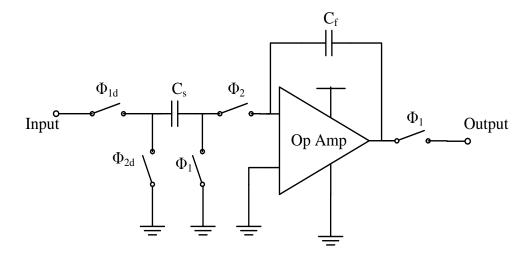

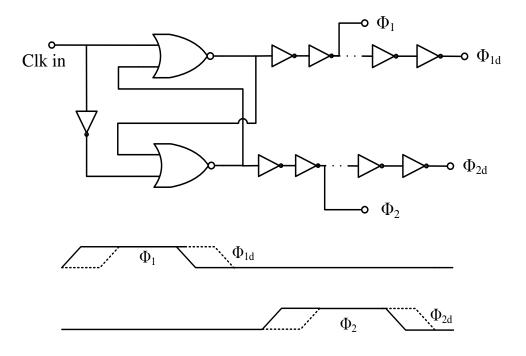

| Figure 3.5.  | Parasitic insensitive switched capacitor discrete analog integrator [9]                                             | 35 |

| Figure 3.6.  | Non-overlapping clock phase generator circuit with clocking sequence                                                | 35 |

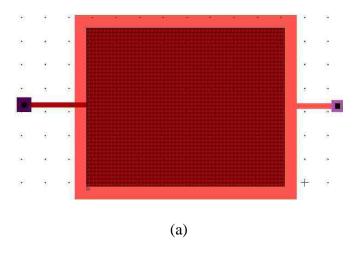

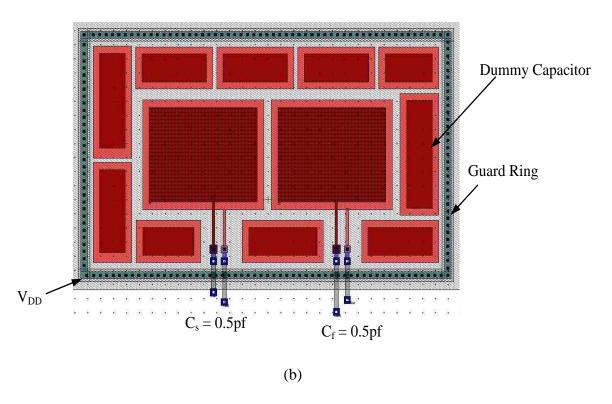

| Figure 3.7.  | (a) Layout of a capacitor made of poly1 and poly2 and (b) Layout of the capacitors using common-centroid technique. | 36 |

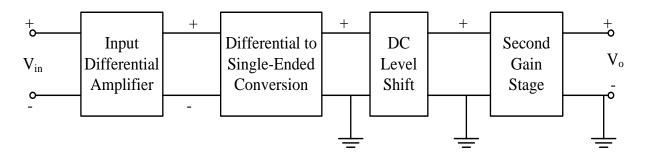

| Figure 3.8.  | Block diagram of a two stage CMOS operational amplifier [19]                                                        | 38 |

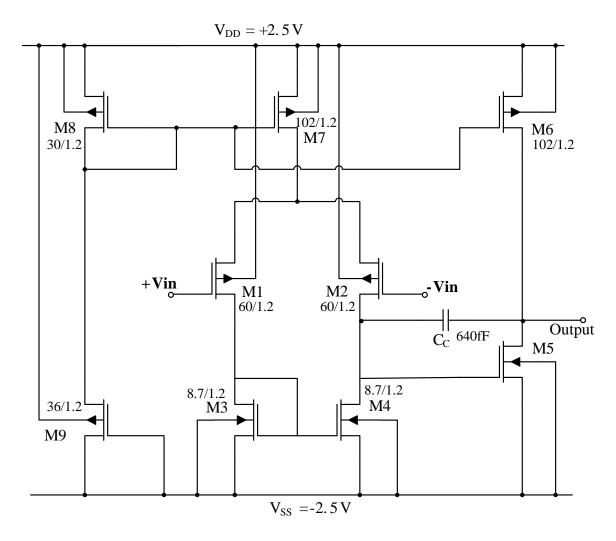

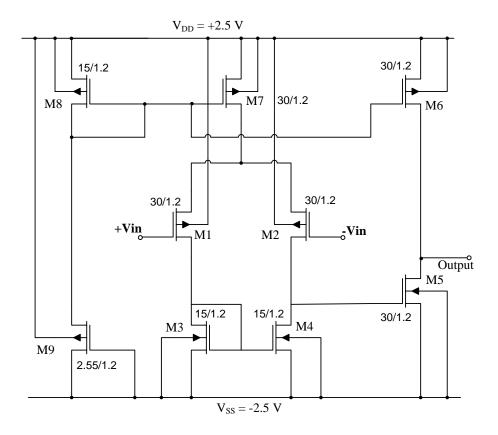

| Figure 3.9.  | Schematic of two-stage operational amplifier.                                                                       | 38 |

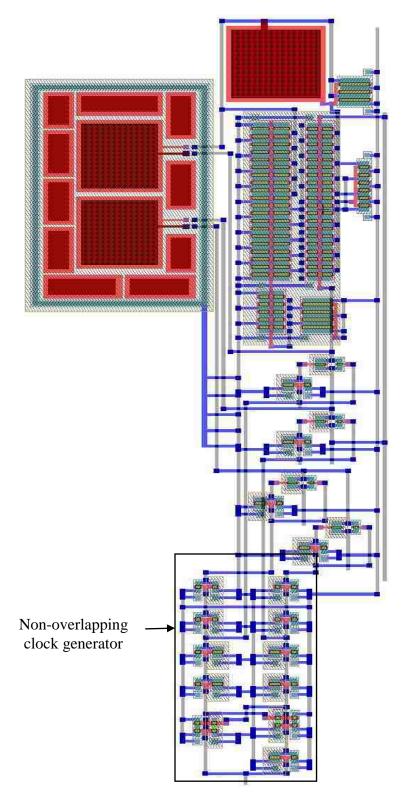

| Figure 3.10. | Complete layout of the discrete analog integrator with non-overlapping clock generator.                             | 40 |

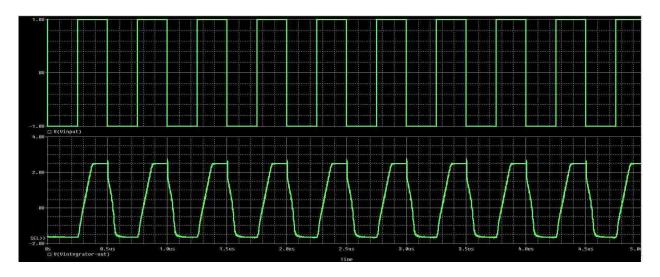

| Figure 3.11. | Transient response from post layout simulation of discrete analog integrator                                        | 41 |

| Figure 3.12. | Schematic diagram of a two-stage comparator.                                                                        | 41 |

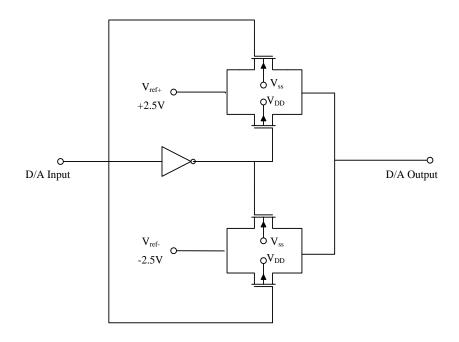

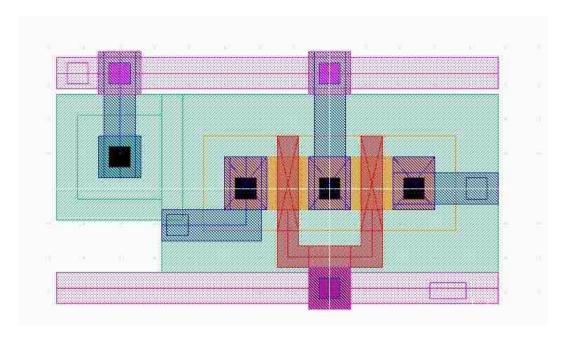

| Figure 3.13. | Schematic diagram of 1-bit DAC.                                                                                     | 43 |

| Figure 3.14. | Layout of 1-bit DAC.                                                                                                       | 43 |

|--------------|----------------------------------------------------------------------------------------------------------------------------|----|

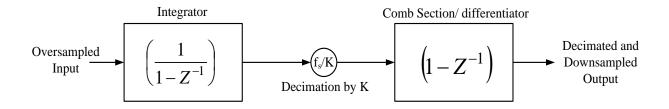

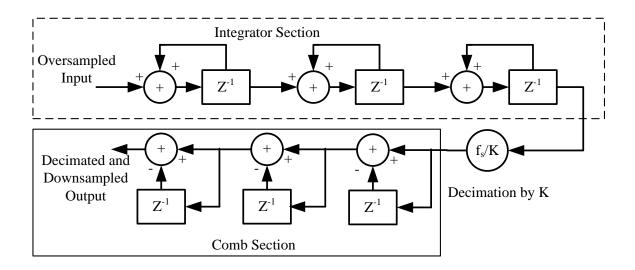

| Figure 3.15. | Block diagram of first order CIC decimation filter.                                                                        | 45 |

| Figure 3.16. | Block diagram of third order CIC decimator [9]                                                                             | 45 |

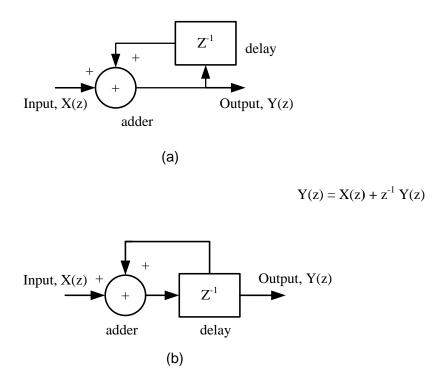

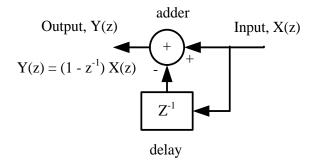

| Figure 3.17. | Stick diagram of a (a) basic and (b) pipelined digital integrator                                                          | 47 |

| Figure 3.18. | Stick diagram of a digital differentiator (comb filter).                                                                   | 47 |

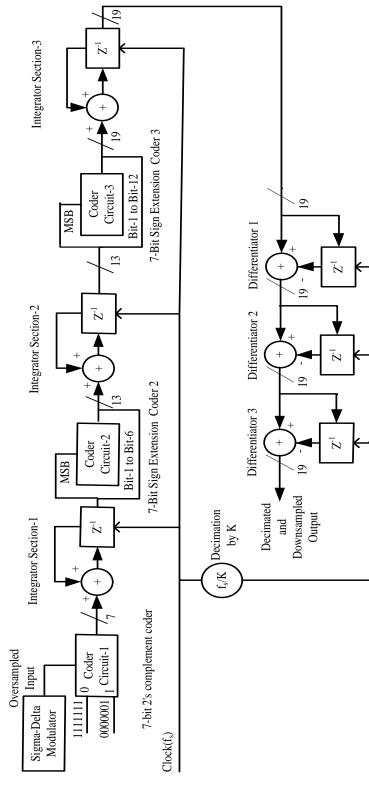

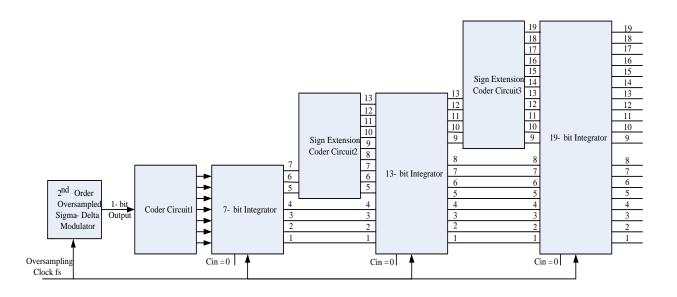

| Figure 3.19. | Block diagram of modified third order CIC decimator (K = 64) [23, 24, 25]                                                  | 49 |

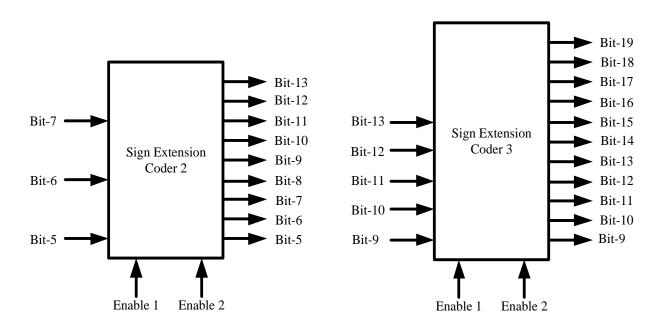

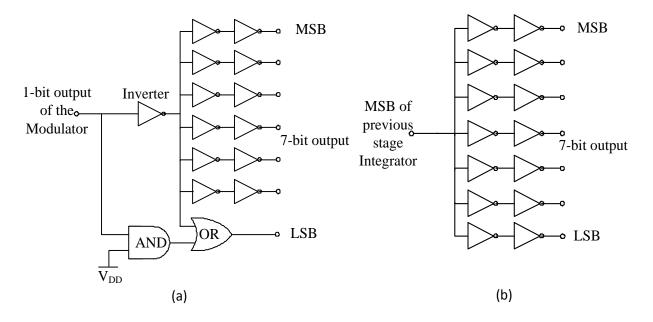

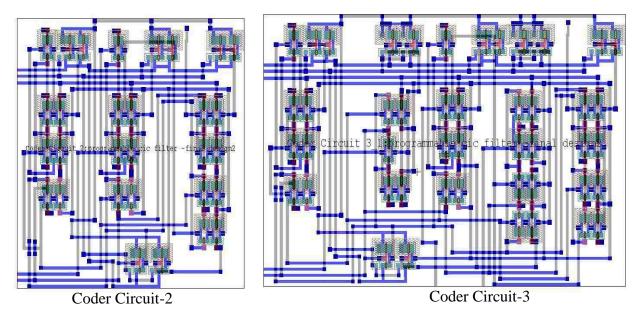

| Figure 3.20. | Block diagrams of coder circuits 2 and 3 [23, 24, 25].                                                                     | 51 |

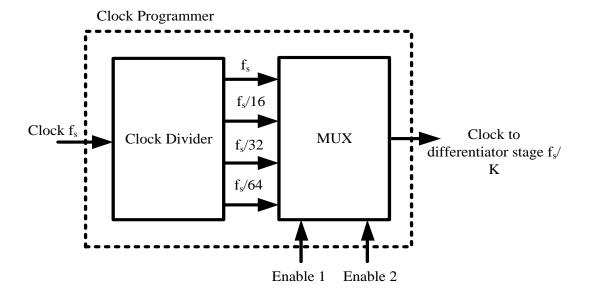

| Figure 3.21. | Block diagram of a clock programmer circuit for three different oversampling ratios ( $K = 64, 32$ and $16$ ) [23, 24, 25] | 51 |

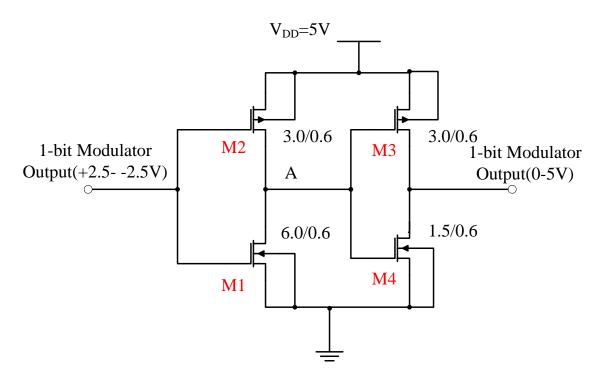

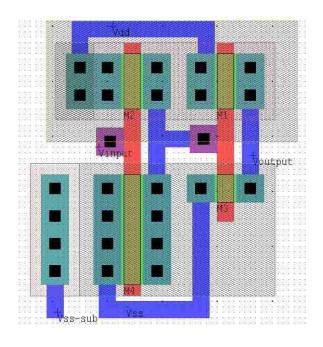

| Figure 3.22. | Transistor level schematic of level shifter circuit                                                                        | 55 |

| Figure 3.23. | Layout of level shifter circuit.                                                                                           | 55 |

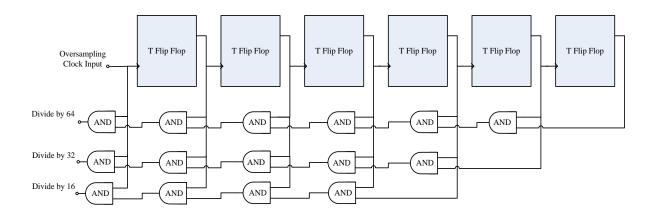

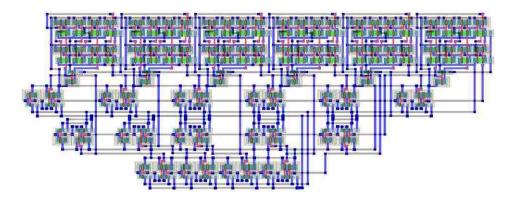

| Figure 3.24. | Clock divider gate level schematic used to generate the three different clock pulses.                                      | 57 |

| Figure 3.25. | Layout of the complete clock divider circuit.                                                                              | 57 |

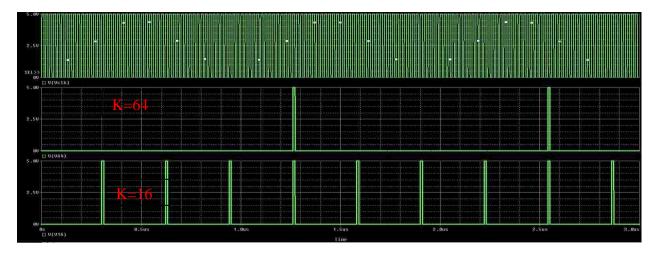

| Figure 3.26. | Simulated output of the clock divider circuit for K=64 and K=16                                                            | 57 |

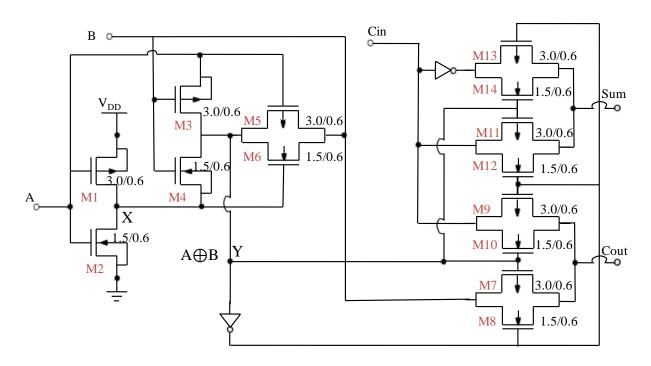

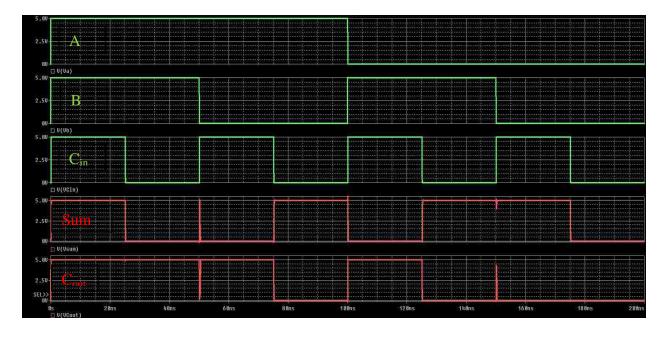

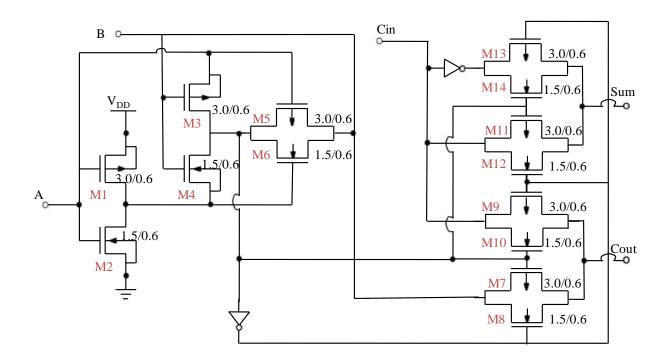

| Figure 3.27. | Schematic of the 18 transistor binary full adder circuit [22]                                                              | 59 |

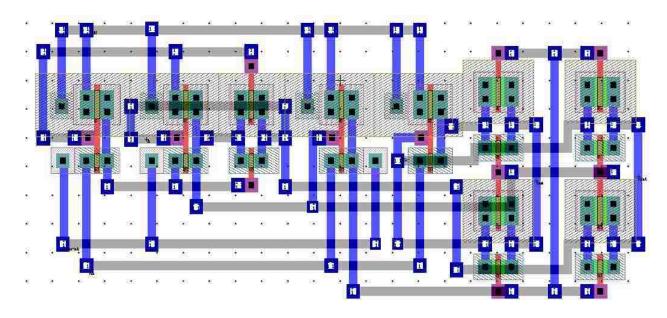

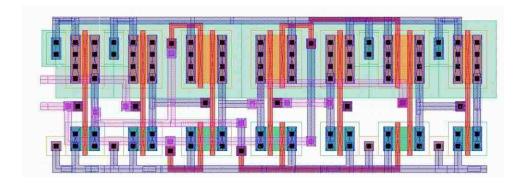

| Figure 3.28. | Layout of the area optimized 18 transistor binary full adder                                                               | 61 |

| Figure 3.29. | Simulation results for the 18 transistor binary full adder                                                                 | 61 |

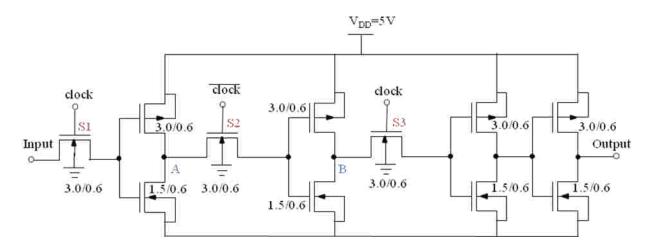

| Figure 3.30. | Schematic diagram to design delay element.                                                                                 | 64 |

| Figure 3.31. | Layout of delay element design for achieving delay by two clock cycles                                                     | 64 |

| Figure 3.32. | Simulated input and output of the delay element.                                                                           | 64 |

| Figure 3.33. | Block diagram of third order integrator circuit.                                                                           | 66 |

| Figure 3.34. | (a) Gate level schematic of coder circuit-1. (b) Gate level schematic of coder circuit-2 and coder circuit-3.              | 66 |

| Figure 3.35. | Layout of the circuit for programmability used with coder circuit -2 and coder circuit -3                                  | 69 |

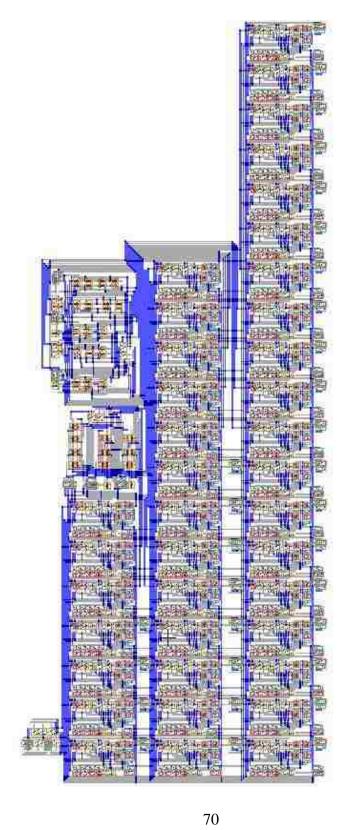

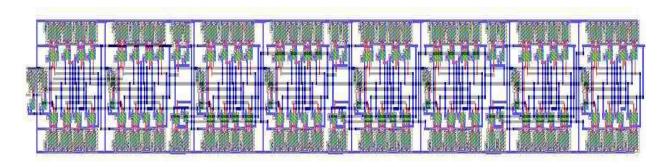

| Figure 3.36. | Layout of the complete 3 <sup>rd</sup> order integrator                                                                                                 | 70  |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

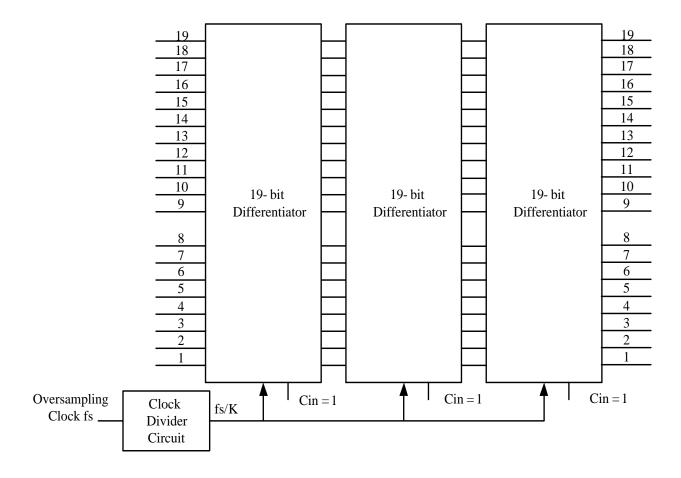

| Figure 3.37. | Block diagram of the complete 3 <sup>rd</sup> order differentiator                                                                                      | 72  |

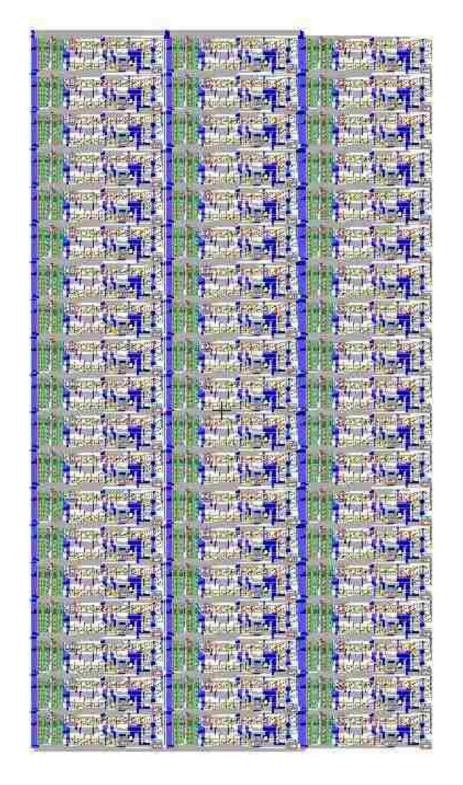

| Figure 3.38. | Layout of the complete 3 <sup>rd</sup> order differentiator                                                                                             | 73  |

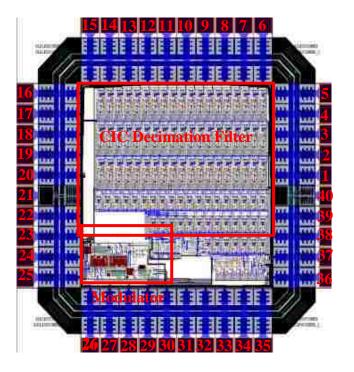

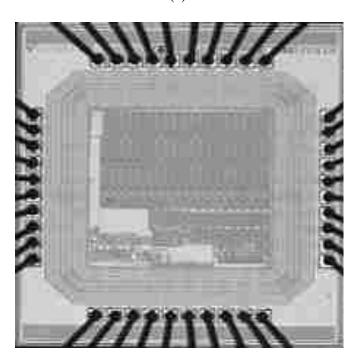

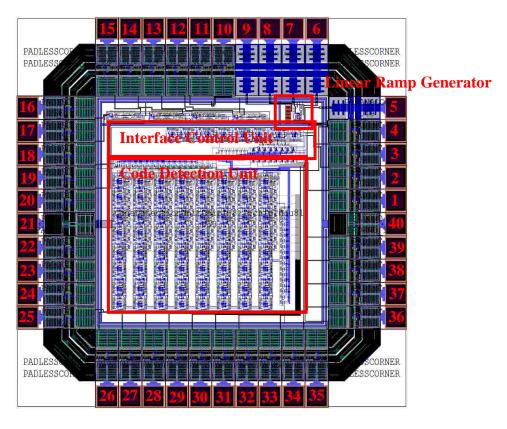

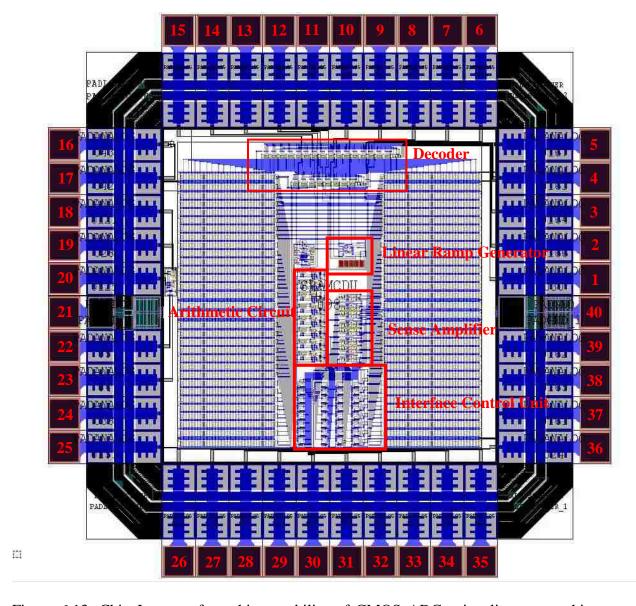

| Figure 3.39. | (a) Chip layout in 40-pin padframe and (b) microphotograph of a second order delta-sigma ADC [23, 24, 25]                                               | 75  |

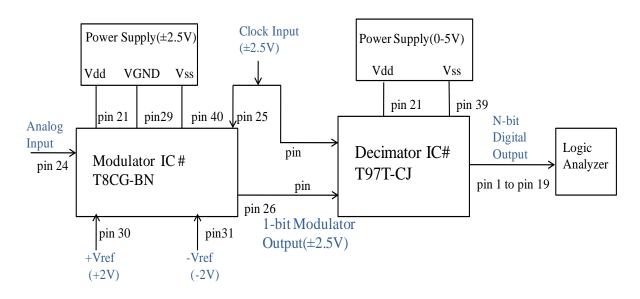

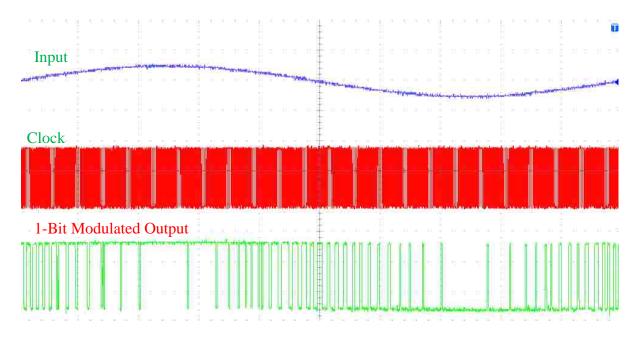

| Figure 3.40. | Experimental setup to test programmable second order oversampling delta-sigma                                                                           | 77  |

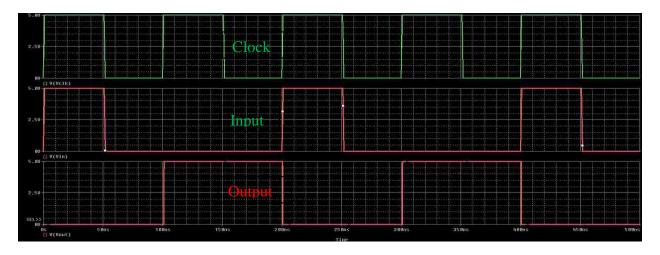

| Figure 3.41. | Experimental results for second order delta-sigma modulator chip showing 1-bit modulated digital output.                                                | 77  |

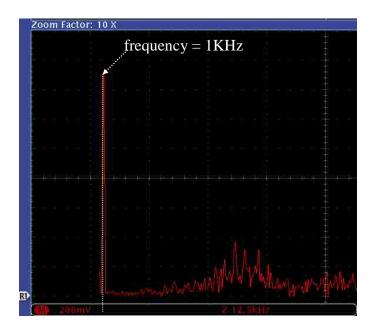

| Figure 3.42. | Frequency spectrum of 1-bit modulated output in Figure 3.41 using FFT                                                                                   | 78  |

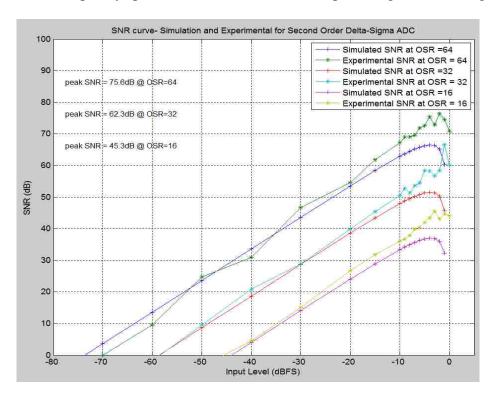

| Figure 3.43. | Plot of output SNR vs. Input Range showing a dynamic range for OSR = 64, 32 and 16.                                                                     | 78  |

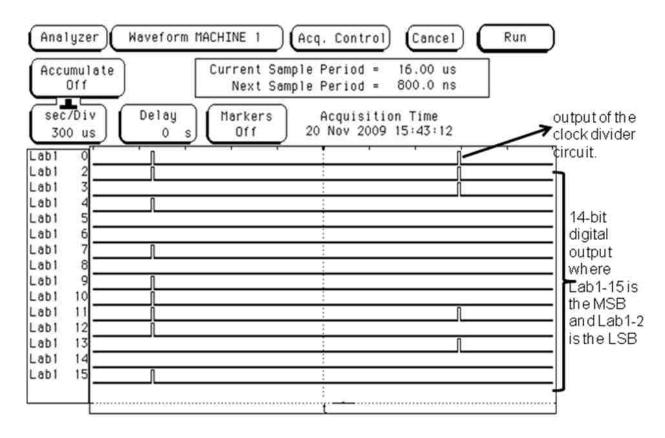

| Figure 3.44. | Experimental results showing the waveforms for two digital output codes 10011110100101 and 00101000000011.                                              | 82  |

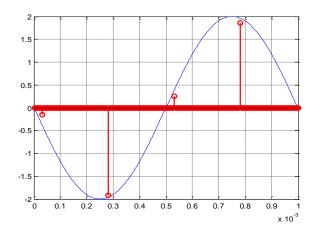

| Figure 3.45. | Experimental output of the programmable second order CMOS delta-<br>sigma ADC for oversampling ratio $K = 64$ with a superimposed sine<br>wave of 4Vpp. | 82  |

| Figure 4.1.  | Block diagram of I <sub>DDQ</sub> testing.                                                                                                              | 89  |

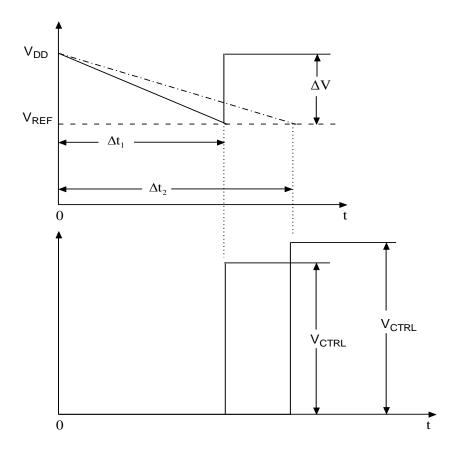

| Figure 4.2.  | Capacitor discharge transient voltage of the CUT under high and low leakage [8-11]. Solid line: fault free condition, dotted line: faulty condition.    | 92  |

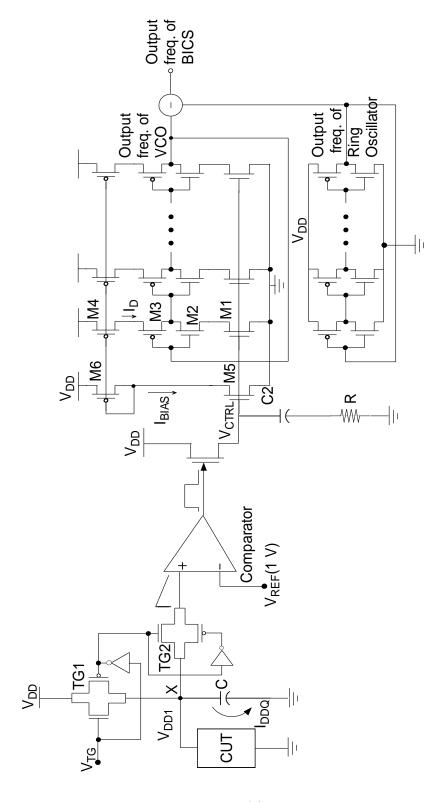

| Figure 4.3.  | $\Delta I_{DDQ}$ built-in current sensor (BICS) [10, 17, 18]                                                                                            | 94  |

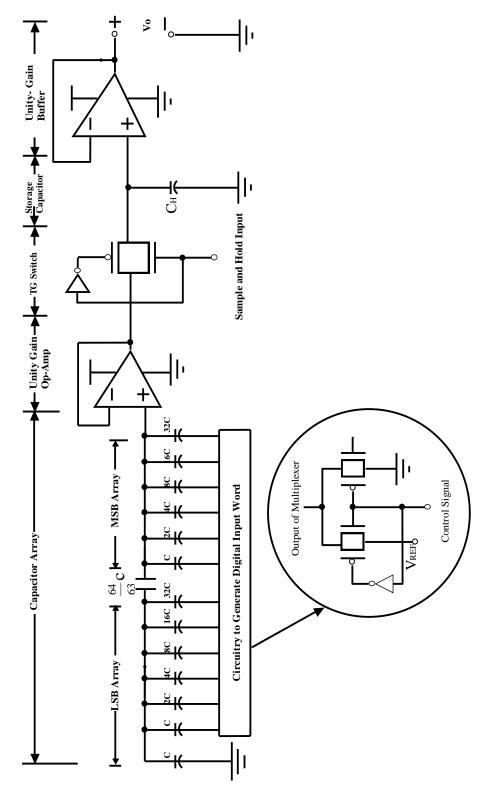

| Figure 4.4.  | Schematic of a 12-bit charge scaling DAC [10, 17, 18]                                                                                                   | 96  |

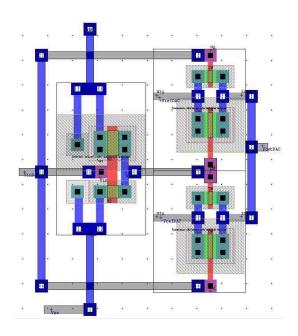

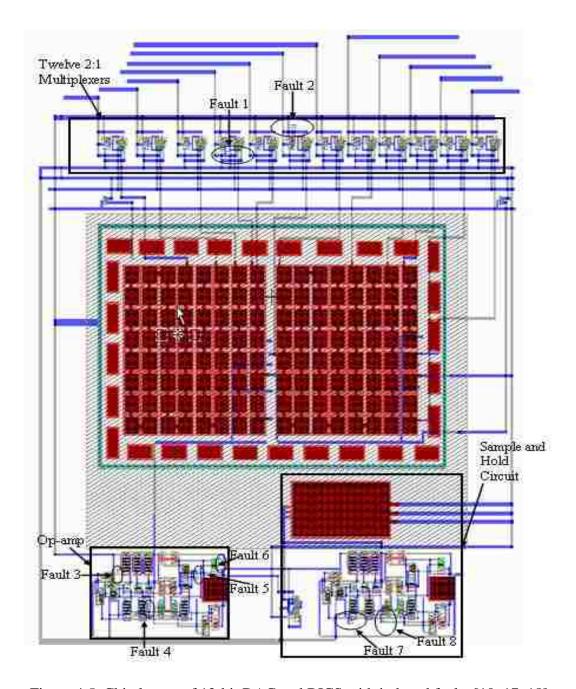

| Figure 4.5.  | Chip layout of 12-bit DAC and BICS with induced faults [10, 17, 18]                                                                                     | 98  |

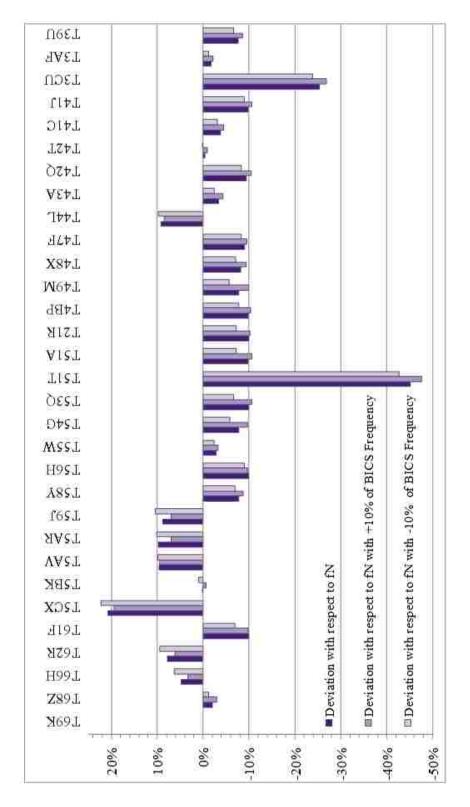

| Figure 4.6.  | Deviation of BICS output frequency to natural frequency ( $f_N$ )                                                                                       | 100 |

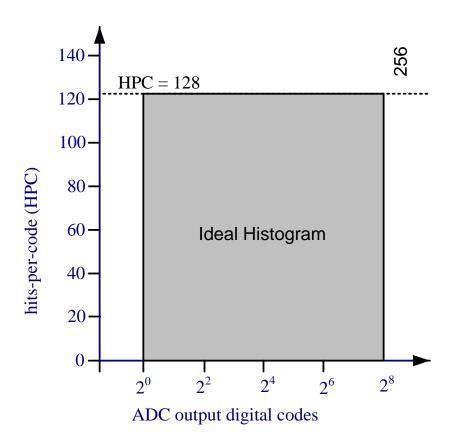

| Figure 5.1.  | Example of an 8-bitADC histogram [8-10]                                                                                                                 | 107 |

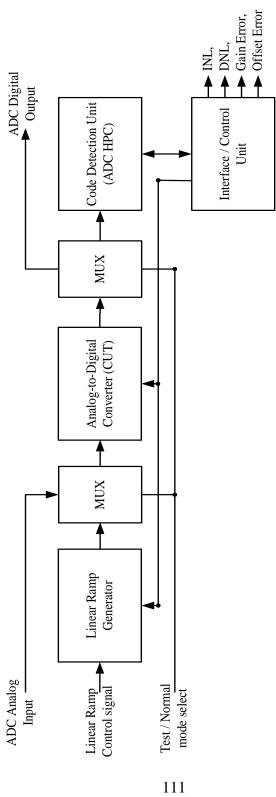

| Figure 5.2.  | Block diagram of on-chip linear ramp histogram technique for ADC [14].                                                                                  | 111 |

| Figure 5.3.  | Principle of linear-ramp generator [12].                                                                                                                | 113 |

| Figure 5.4.  | Schematic of the designed linear ramp generator                                                                                      | 113 |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figure 5.5.  | Layout of designed linear ramp generator.                                                                                            | 114 |

| Figure 5.6.  | Block diagram of the corrective scheme [12]                                                                                          | 114 |

| Figure 5.7.  | Block diagram of code detection unit (CDU) [14]                                                                                      | 115 |

| Figure 5.8.  | Schematic of the 4-to16 decoder circuit [15].                                                                                        | 117 |

| Figure 5.9.  | Layout of area optimized 4-to-16 decoder.                                                                                            | 119 |

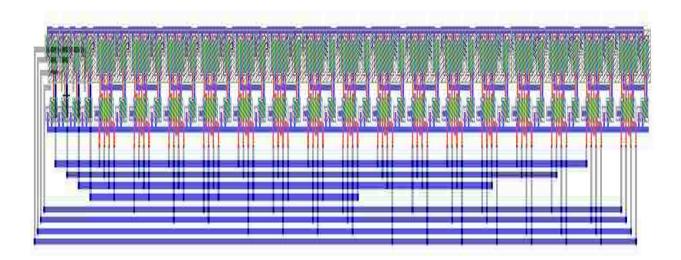

| Figure 5.10. | Block diagram of register using synchronous counter for CDU [14]                                                                     | 119 |

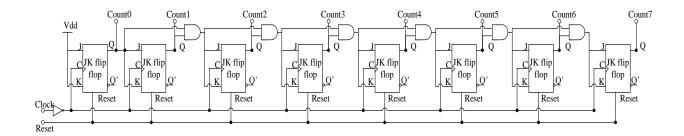

| Figure 5.11. | Schematic of 8-bit synchronous counter using JK flip flop [15]                                                                       | 121 |

| Figure 5.12. | Layout of area optimized 8-bit synchronous counter using JK flip flop                                                                | 121 |

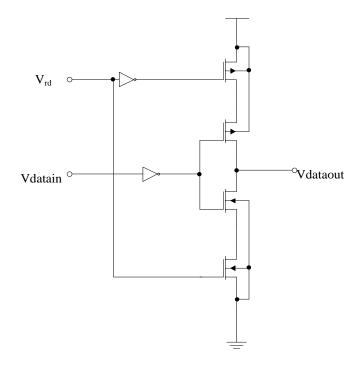

| Figure 5.13. | Schematic of readout circuit design [15]                                                                                             | 121 |

| Figure 5.14. | Layout of the implemented register design using synchronous counter                                                                  | 122 |

| Figure 5.15. | Chip Layout of on-chip testability of CMOS ADC using linear-ramp histogram technique                                                 | 122 |

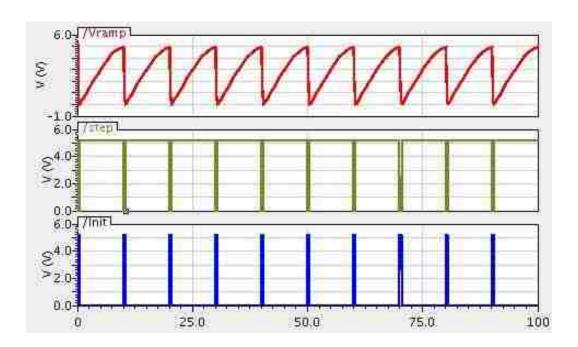

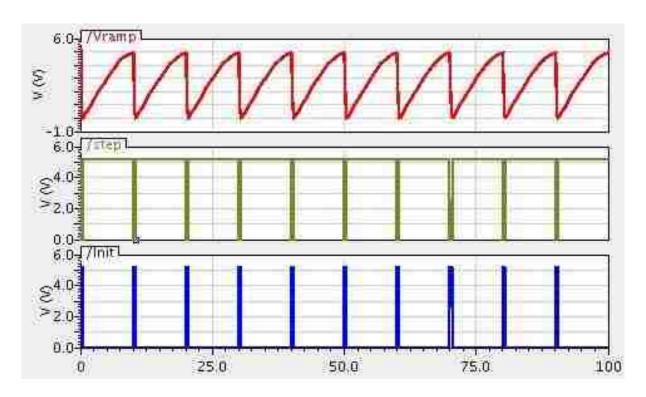

| Figure 5.16. | Simulation results for post-layout linear-ramp generator                                                                             | 123 |

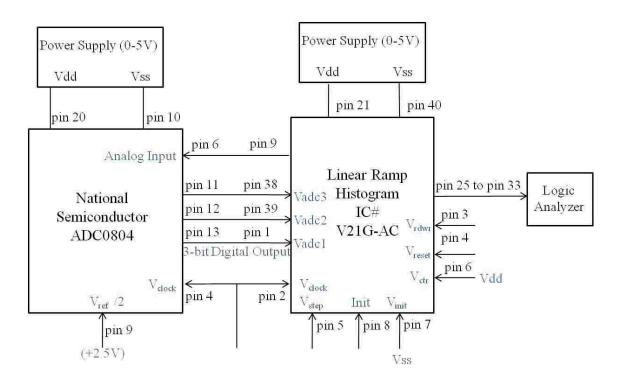

| Figure 5.17. | Experimental test setup for on-chip testability of CMOS ADC by linear ramp histogram technique using synchronous counter as register | 124 |

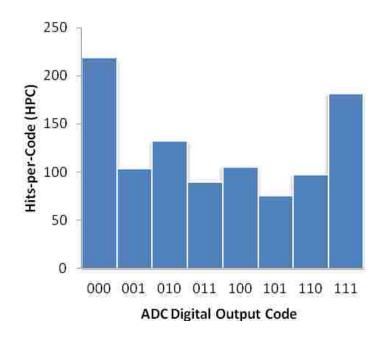

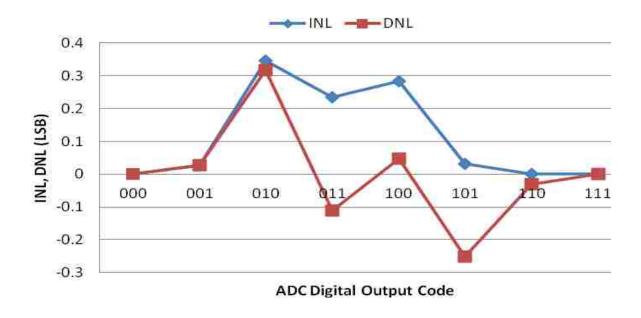

| Figure 5.18. | Experimental linear-ramp histogram plot for a 3-bit ADC.                                                                             | 124 |

| Figure 5.19. | Experimental INL and DNL plot for 3-bit ADC calculated using on-chip linear-ramp histogram.                                          | 125 |

| Figure 6.1.  | Block diagram of register using 6T-SRAM for CDU.                                                                                     | 131 |

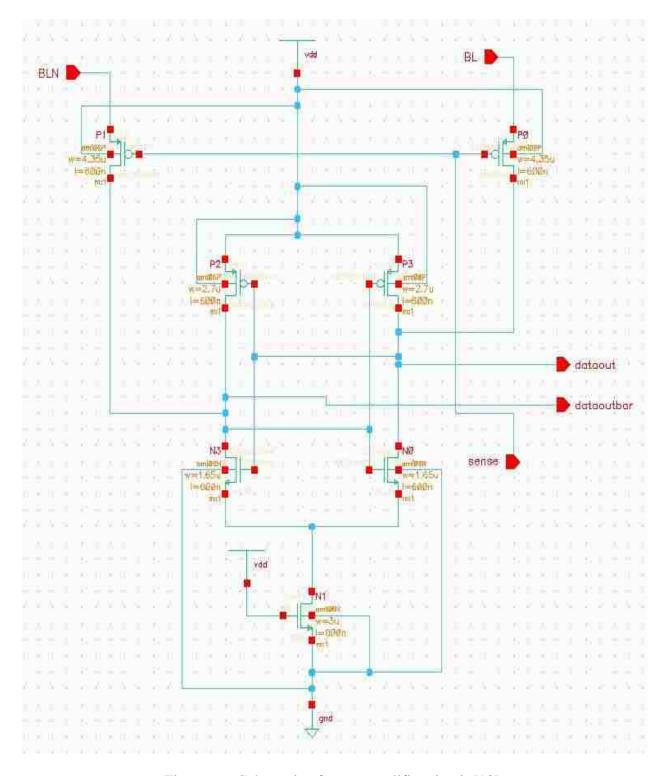

| Figure 6.2.  | Schematic of a 6T-SRAM cell [13]                                                                                                     | 133 |

| Figure 6.3.  | Layout of a 6T-SRAM cell.                                                                                                            | 133 |

| Figure 6.4.  | Schematic of the precharge circuit [13]                                                                                              | 135 |

| Figure 6.5.  | Layout of the precharge circuit.                                                                                                     | 135 |

| Figure 6.6.  | Schematic of sense amplifier circuit [13].                                                                                           | 136 |

| Figure 6.7.  | Layout of sense amplifier circuit.                                                                                                   | 138 |

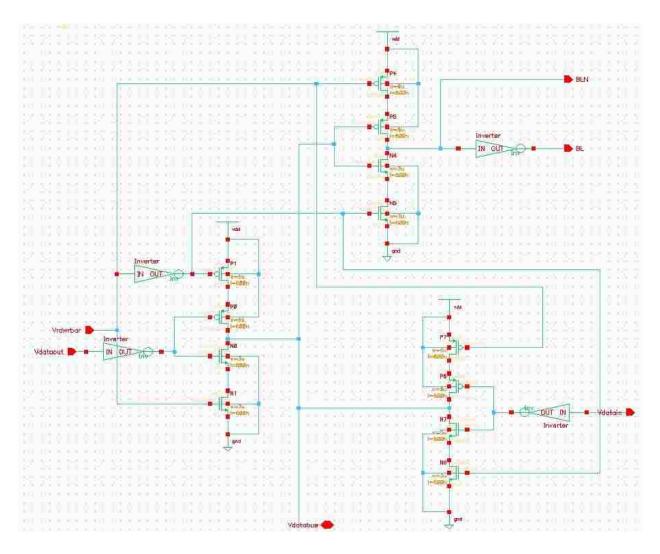

| Figure 6.8.  | Schematic of read/write circuit [13]                                                                                     | . 139 |

|--------------|--------------------------------------------------------------------------------------------------------------------------|-------|

| Figure 6.9.  | Layout of read/write circuit.                                                                                            | . 139 |

| Figure 6.10. | Schematic of 18 transistor binary full adder circuit [13]                                                                | . 141 |

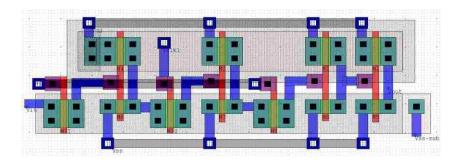

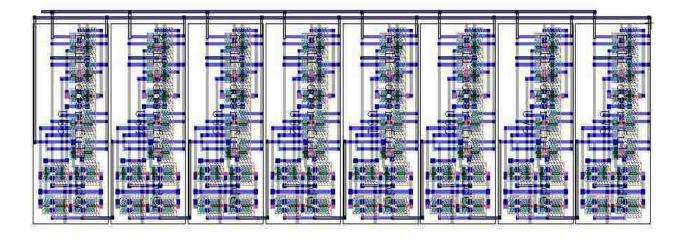

| Figure 6.11. | Layout of 8-bit arithmetic circuit designed using 18 transistor binary full adder circuits to operate as increment by 1. | . 141 |

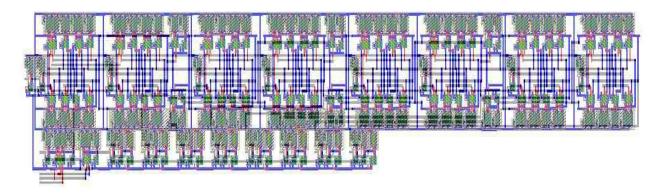

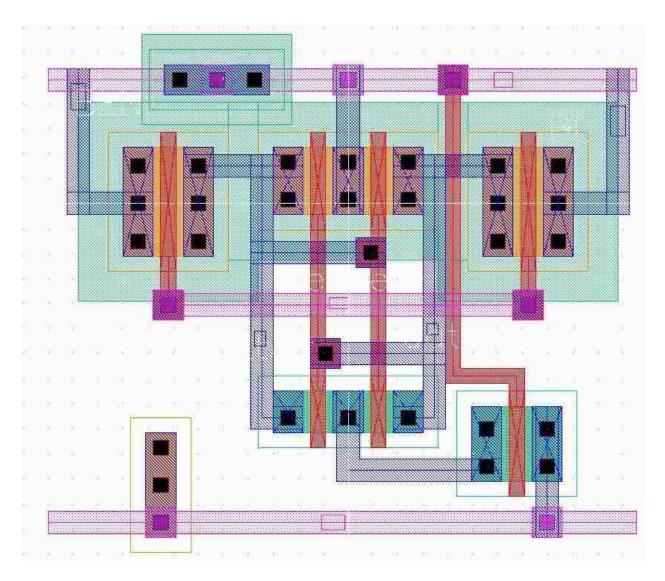

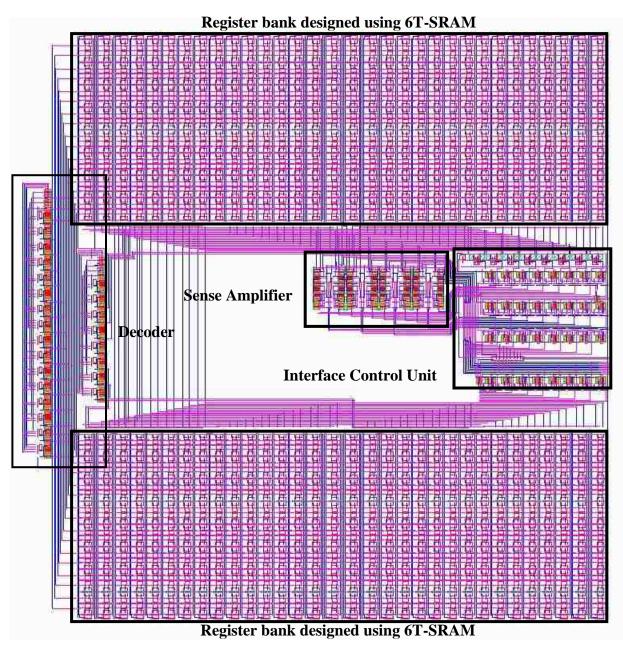

| Figure 6.12. | Layout of CDU consisting of 16x8 register bank designed using 6T-SRAM for 7-bit ADC.                                     | . 142 |

| Figure 6.13. | Chip Layout of on-chip testability of CMOS ADC using linear-ramp histogram technique using 6T-SRAM as registers.         | . 143 |

| Figure 6.14. | Simulation results for post-layout linear-ramp generator                                                                 | . 145 |

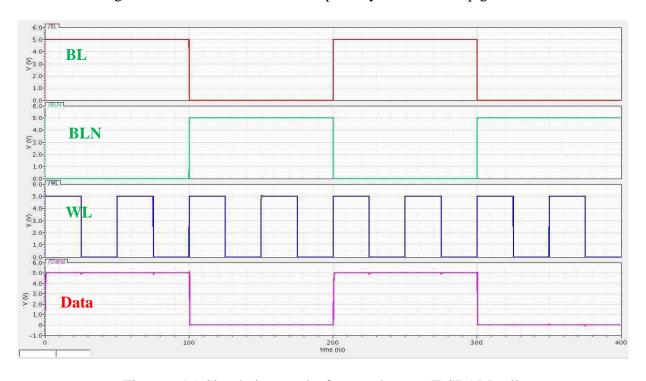

| Figure 6.15. | Simulation results for post-layout 6T-SRAM cell                                                                          | . 145 |

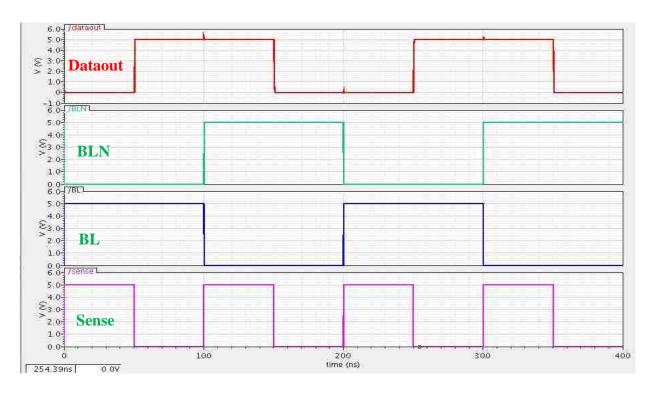

| Figure 6.16. | Simulation results for post-layout sense amplifier circuit                                                               | . 146 |

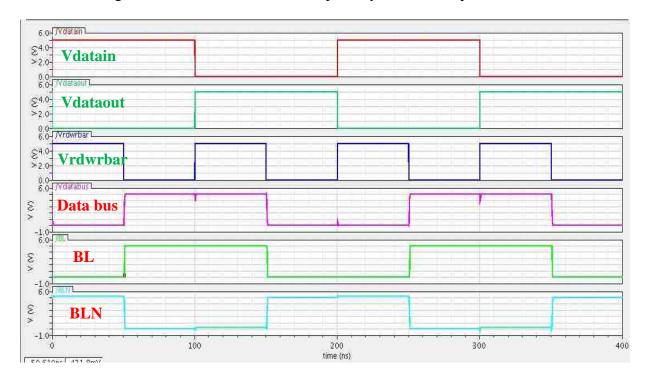

| Figure 6.17. | Simulation results for post-layout read/write circuit                                                                    | . 146 |

### LIST OF TABLES

| Table 3.1. | Truth table of a binary full adder                                                                | 59  |

|------------|---------------------------------------------------------------------------------------------------|-----|

| Table 3.2. | Table representation of input and output values of the designed coder circuits.                   | 69  |

| Table 3.3. | Experimental output of a programmable second order oversampling CMOS delta-sigma ADC for $K=64$ . | 81  |

| Table 3.4. | Experimental output of a programmable second order oversampling CMOS delta-sigma ADC for K =32.   | 83  |

| Table 3.5. | Experimental output of a programmable second order oversampling CMOS delta-sigma ADC for K =16.   | 85  |

| Table 4.1. | Deviation of BICS output frequency from natural frequency with induced faults                     | 101 |

#### **ABSTRACT**

In this work, a programmable second order oversampling CMOS delta-sigma analog-to-digital converter (ADC) design in 0.5µm n-well CMOS processes is presented for integration in sensor nodes for wireless sensor networks. The digital cascaded integrator comb (CIC) decimation filter is designed to operate at three different oversampling ratios of 16, 32 and 64 to give three different resolutions of 9, 12 and 14 bits, respectively which impact the power consumption of the sensor nodes. Since the major part of power consumed in the CIC decimator is by the integrators, an alternate design is introduced by inserting coder circuits and reusing the same integrators for different resolutions and oversampling ratios to reduce power consumption. The measured peak signal-to-noise ratio (SNR) for the designed second order delta-sigma modulator is 75.6dB at an oversampling ratio of 64, 62.3dB at an oversampling ratio of 32 and 45.3dB at an oversampling ratio of 16.

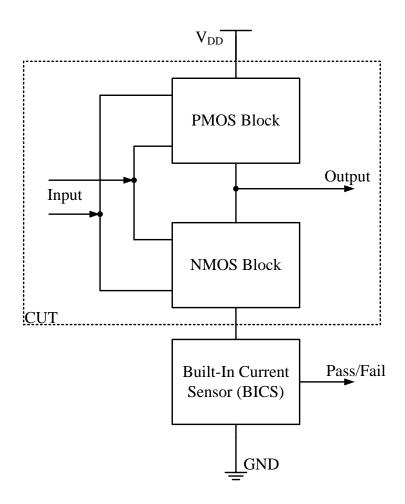

The implementation of a built-in current sensor (BICS) which takes into account the increased background current of defect-free circuits and the effects of process variation on  $\Delta I_{DDQ}$  testing of CMOS data converters is also presented. The BICS uses frequency as the output for fault detection in CUT. A fault is detected when the output frequency deviates more than  $\pm 10\%$  from the reference frequency. The output frequencies of the BICS for various model parameters are simulated to check for the effect of process variation on the frequency deviation.

A design for on-chip testability of CMOS ADC by linear ramp histogram technique using synchronous counter as register in code detection unit (CDU) is also presented. A brief overview of the histogram technique, the formulae used to calculate the ADC parameters, the design

implemented in 0.5 $\mu$ m n-well CMOS process, the results and effectiveness of the design are described. Registers in this design are replaced by 6T-SRAM cells and a hardware optimized on-chip testability of CMOS ADC by linear ramp histogram technique using 6T-SRAM as register in CDU is presented. The on-chip linear ramp histogram technique can be seamlessly combined with  $\Delta I_{DDQ}$  technique for improved testability, increased fault coverage and reliable operation.

#### **CHAPTER 1**

#### INTRODUCTION

The integration of digital, analog and mixed-signal circuits in a System-on-Chip (SOC) has been growing steadily in recent years and has paved the way for more compact and efficient implementations of circuits and systems [1]. The main advantage in having digital, analog and mixed-signal circuits on the same chip are the reduction in size of the circuit, increase in speed of operation, reduction in power dissipation, increase in design flexibility and increased reliability. The increase in circuit complexity is posing a major challenge in design and testing of mixed-signal SOC integrated circuits [2]. Mixed-signal circuits in SOC usually include data converters (analog-to-digital and digital-to-analog) as important interface components along with digital signal processing (DSP) or digital circuits, and they form an integral part of most applications in the communication, consumer, automotive, computers, biomedical, military and space electronics. These digital circuits use digital technologies that offer fast transistor biased at low voltages and therefore the data converter design becomes the most challenging interface circuit. Hence it is desired to use data converter architecture which trade accuracy for speed or vice versa as per the application it is designed for.

Due to availability of dedicated digital signal processing technique [3, 4], faster analog design needing less complex and lower performance circuits to attain a given conversion accuracy are used in data converter implementation. Delta-Sigma ( $\Delta\Sigma$ ) analog-to-digital converter is a low-cost, low-bandwidth, low-power, high resolution ADC and has varied applications in data acquisition, communications, signal processing, instrumentation and wireless

sensor networks. Integrating an analog delta-sigma ( $\Delta\Sigma$ ) modulator with a digital decimator forms a delta-sigma ADC. The digital signal processing in the delta-sigma ADC is done at the decimator stage, which is a cascaded integrator comb (CIC) decimation filter. This CIC decimation filter also performs down sampling of high frequency, low-resolution digital output from the oversampling delta-sigma modulator to lower Nyquist frequency, high-resolution digital output [4]. Hence the decimation stage is responsible for achieving higher resolution and able to program the decimator, offers further advantage of operating the ADC at different input channel bandwidth and with different oversampling ratios [5]. This is of significant advantage as decimation stage requires large silicon area and incurs higher dissipation as it contains fast switching circuits.

Also in a mixed-signal SOC due to the increasing level of integration and complexity, the test cost and the need for faster and complex test equipment has increased. Among the test cost, mixed-signal test cost for data converters is becoming one of the most important factors in SOC [6]. Hence the necessity to develop new and efficient low-cost test techniques and methodologies with significant capabilities has increased. Automated Test Equipment (ATE) is currently being used to solve the problem of testing ADC and DAC for device characterization and parameter test [6, 7]. But high resolution mixed-signal ATE's are expensive and increases the test cost and time for data converter testing drastically. Therefore, built-in-self-test (BIST) can be used as an effective test technique to prevent the dependence on mixed-signal testers, wherein the stimulus generation and measurements are done on-chip. The BIST techniques for data converters have been the focus of many research activities recently [8-12].

Testing of data converters can be divided into functionality based testing and fault detection based testing. Many functionality based testing have been proposed for data converters over the years. But since they are specification oriented and does not cover physical defects, fault based testing has been introduced. In the fault based testing, quiescent current ( $I_{DDQ}$ ) testing has been very efficient in testing for physical defects such as gate oxide shorts, floating-gates and bridging faults in mixed signal circuits and data converters.  $I_{DDQ}$  testing is a defect based test that measures device supply current under steady state condition. Recently built-in current sensors (BICS) for  $I_{DDQ}$  testing of CMOS sigma-delta (or delta-sigma) analog-to-digital converters and charge scaling digital-to-analog converters have been designed and implemented [13-16]. Based on this method we have developed a BICS for  $\Delta I_{DDQ}$  testing of CMOS data converters that takes into account the effect of process variation and increasing background current. In this work, we have considered physical defects such as device shorts and open faults introduced in the circuit under test (CUT) and tested.

To improve the efficiency of the quiescent current ( $I_{DDQ}$ ) testing, functional test methods for data converters like histogram technique [17] can be used along. In functional testing, the performance metrics for data converters used are the offset error, gain error, nonlinearity error, signal-to-noise error and effective number of bits.

In this work, we have presented design of a programmable second order oversampling delta-sigma analog-to-digital converter comprising a second order oversampling delta-sigma modulator and a programmable cascaded integrator comb decimation filter. We have also presented the  $\Delta I_{DDQ}$  testing of CMOS data converter considering process variation effects.

Functional testing of data converters using on-chip linear ramp histogram technique to calculate the static parameters has been designed and presented. Further area optimization of the on-chip linear ramp histogram technique has been researched and presented using 6T-SRAM cells. The proposed histogram technique can be seamlessly combined with the quiescent current testing to improve the fault coverage achieved.

### 1.1 Motivation for Programmable Second Order Oversampling CMOS Delta-Sigma ADC

The programmable second order oversampling analog-to-digital converter (ADC) designed by combining a second order oversampling delta-sigma modulator and a programmable cascaded integrator comb decimation filter can be programmed to generate different resolution depending on the oversampling ratio. The output resolution of the ADC depends directly on the oversampling ratio and the order of the modulator and the decimation filter. In the decimation filter, the output resolution can be increased by increasing the oversampling ratio which results in large silicon area and higher power dissipation. Hence we have focused on designing a programmable second order oversampling delta-sigma ADC to generate different resolutions for different oversampling ratio by reusing the design. In the design, we have focused on achieving an area efficient second order oversampling delta-sigma ADC by integrating a second order delta-sigma modulator with the programmable CIC decimation filter. The design can be programmed to operate at three different oversampling ratios of 64, 32 and 16 to generate a 14-bit, 12-bit and 9-bit output, respectively. The integrator stages in the decimator have been reused for different oversampling ratio, by enabling programmability of the decimator. The design also

includes an internal clock divider capable of producing three different clock signals for three different oversampling ratios for achieving three different resolutions.

### 1.2 Motivation for $\Delta I_{DDQ}$ Testing of CMOS Data Converter Considering Process Variation Effects

During the fabrication of designed integrated circuits using photolithographic process, imperfection and blemishes occur leading to either catastrophic failure in the operation or any individual IC or minor variation in the performance from one IC to other [2]. In sub-micron/deep submicron CMOS processes fabrication, the gap between the defective and defect-free quiescent current is narrowing due to increasing background current [2] and process variations pose very severe threat. Process variation affects the threshold voltage of the circuit and thus the effective leakage current in the circuit. Also, process variation changes MOS model parameters and have detrimental effects specifically in the reliability and performance of mixed-signal and analog integrated circuits. Hence, designing BICS for sub-micron CMOS process considering process variation effects is becoming difficult. Many new techniques have been proposed and presented in literature by many researchers to minimize these effects in I<sub>DDO</sub> testing. As discussed earlier in this chapter, built-in current sensors (BICS) for I<sub>DDO</sub> testing of CMOS delta-sigma (or sigmadelta) analog-to-digital converters and charge scaling digital-to-analog converters have been designed and implemented [13-16] earlier in our research group. Based on this method we have developed an attractive BICS for  $\Delta I_{DDO}$  testing of CMOS data converters that takes into account the effect of process variation and increasing background current. In this method, the differential measurement successfully suppresses the impact of background current and process variation.

# 1.3 Motivation for On-Chip Functional Testability of CMOS ADC using Linear Ramp Histogram Technique

In functional testing of data converters, the linear ramp histogram technique is the most prominent and one among the most classical approaches to test ADC. In the linear ramp histogram technique, a linear ramp waveform is applied at the ADC input and the number of time each code appears is recorded. These recorded samples can be then used along with the theoretical samples in a linear computation to derive ADC static parameters line offset, gain, differential and integral non-linearity [17]. Mostly histogram technique has been used for external testing of ADC using FPGA or off-shelf components or test boards. This is due to the reason that on-chip implementation of histogram technique requires large area to accommodate the additional circuitry. But to achieve a faster test time and reduce the dependency on complex test equipment, the feasibility of on-chip implementation of linear ramp histogram technique by optimizing the hardware resources has been the focus of this research.

In this design, we have used the linear ramp as the input signal to the ADC and is generated on chip using a linear ramp generator. The linear histogram technique allows the reduction of the required memory for the storage of the ideal histogram rather than the sinusoidal one and due to the uniform distribution of the histogram, simple linear computation can be used to derive the ADC parameters. In histogram based BIST, to collect the HPC for an n-bit ADC, we require access to 2<sup>n</sup> on-chip memory. In this work, we have designed the on-chip memory or register by using synchronous counter and then optimized the complete design by using 6T-SRAM cell as register. The design also includes an in-built linear ramp generator to generate the input signal needed for the functional testing and hence can be seamlessly integrated with other

functionality based testing and/or fault detection based testing to improve testability coverage and detection.

#### 1.4 Goals

To summarize, the goal of this research are as follows:

- Designed and fabricated a programmable second order oversampling delta-sigma ADC using

a second order oversampling delta-sigma modulator and a programmable third order

cascaded integrator comb (CIC) decimation filter.

- Designed and implemented a quiescent ( $\Delta I_{DDQ}$ ) current testing technique for CMOS data converters considering process variation effects.

- Designed and implemented an on-chip functional testability of CMOS delta-sigma analog-todigital converters using linear ramp histogram method.

- Optimize the on-chip functional testability of CMOS delta-sigma analog-to-digital converters

using linear ramp histogram method by using 6T-SRAM cells for registers in place of the

synchronous counters to calculate the parameters of ADC on-chip.

#### 1.5 Chapter Organization

In the following chapters, design and operation of a programmable analog-to-digital converter, quiescent ( $\Delta I_{DDQ}$ ) current testing and on-chip linear-ramp histogram testing have been described.

In **Chapter 1**, motivation and goals for the research are presented.

In **Chapter 2**, the overview and the literature review of the analog-to-digital converter have been discussed in detail. The classifications of the ADC and its performance metrics have also been presented.

In **Chapter 3**, design and implementation of a programmable second order oversampling delta-sigma analog-to-digital converter is described. In this design, a second order oversampling delta-sigma modulator and a third order cascaded integrator comb (sinc) decimation filter have been implemented. The delta-sigma modulator was fabricated in 0.5µm n-well CMOS processes and its complete performance metrics have been presented.

In **Chapter 4,** the concept of  $I_{DDQ}$  testing, design and implementation of the built-in current sensor are presented. The effects of process variation on the quiescent current testing in data converters have also been focused in this chapter.

In **Chapter 5**, the design and implementation of on-chip testability of CMOS analog-to-digital converters using linear ramp histogram technique is described. In this design, the register to store the recorded samples is designed using an 8-bit synchronous counter and read/write enable circuit. The 8-bit synchronous counter is designed using JK flip-flop and AND gates and consist of eight JK flip-flops and six 2-input AND gates. The design also consist of a built in linear ramp generator. The block diagram and layout of the fabricated design and its components are explained in detail.

In **Chapter 6**, the design and implementation of on-chip testability of CMOS ADC using linear ramp histogram technique with hardware area optimization is presented. The register to store the recorded samples are designed by using 6-T SRAM cells instead of synchronous

counter. This design is area optimized and has been implemented successfully to functionally test a 7-bit ADC. The block diagram and layout of the design and its components are explained in details in this chapter.

#### 1.6 References

- [1] 2009 ITRS URL http://www.itrs.net/Links/2009ITRS/Home2009.htm

- [2] J. Galiay, Y. Crouzet and M. Vergniault, "Physical versus logical fault models MOS LSI circuits: impact on their testability," *IEEE Transactions on Computers*, vol. C-29, no. 6, pp. 527-531, June 1980.

- [3] R. M. Gray, "Oversampled sigma-delta modulation," *IEEE Transactions on Communications*, vol. COM-35, pp. 481-489, May 1987.

- [4] J. C. Candy, "Decimation for sigma delta modulation," *IEEE Transactions on Communications*, vol. COM-34, pp.72-76, January 1986.

- [5] C. J. Barret, Low-power decimation filter design for multi-standard transceiver application, MS (EE) Thesis, University of California, Berkeley.

- [6] M. Sachdev and J. P. de Gyvez, *Defect-Oriented Testing for Nano-Metric CMOS VLSI Circuits*, 2nd ed, vol. 34, Springer, 2007.

- [7] A. Lechner, K. Georgopoulos, M. Burbidge, A. Richardson, and D. D. Venuto, "Review of test strategies and resources used in high-resolution interface testing," *Testability of Analogue Macrocells Embedded in System on- Chip (TAMES-2) 2002.Chip (TAMES-2)*, September 2002.

- [8] K. Arabi, B. Kaminska and M. Sawan, "On chip testing data converters using static parameters," *Proceedings of the IEEE Transactions on Very Large Scale Integration (VLSI) Systems*,vol.6, no.3, pp. 409-419, September 1998.

- [9] J. L. Huang, C. K. Ong, and K. T. Cheng, "A BIST scheme for on-chip ADC and DAC testing," *Proceedings of the 2000 Design, Automation and Test in Europe Conference and Exhibition*, pp. 216-220, March 2000.

- [10] R. Maghrebi and M. Masmoudi, "A BIST structure for IP multi-slope A/D converter testing," *Measurement Science Review*, vol. 3, pp. 65-73, 2003.

- [11] S. Goyal, A. Chatterjee, and M. Purtell, "A low-cost test methodology for dynamic specification testing of high-speed data converters," *Journal of Electronic Testing: Theory and Applications*, vol. 23, no. 1, pp. 95-106, 2007.

- [12] H. C. Hong, S. C. Liang and H. C. Song, "A built-in-self-test  $\Sigma$ - $\Delta$  ADC prototype," *Journal of Electronic Testing*, vol. 25, no. 2-3, pp. 145-156, 2009.

- [13] A. Srinivas,  $I_{DDQ}$  testing of a CMOS 10-bit charge scaling digital-to-analog converter, M.S (EE) Thesis, Louisiana state University, Baton Rouge, 2003.

- [14] A. Srivastava, *I<sub>DDQ</sub> testing of CMOS mixed-signal integrated circuits*, U.S. patent no.: 6,930,500, August 16, 2005.

- [15] A. Srivastava, S. Aluri and A. K. Chamakura, "A simple built-in current sensor for I<sub>DDQ</sub> testing of CMOS data converters," *Integration, the VLSI Journal*, vol. 38, no. 4, pp. 579-596, April 2005.

- [16] S. Yellampalli and A. Srivastava, "ΔI<sub>DDQ</sub> based testing of submicron CMOS digital-toanalog converter circuits," *Journal of Active and Passive Electronic Devices*, vol. 3, pp. 341-353, 2008.

- [17] F. Azais, S. Bernard, Y. Bertrand and M. Renovell, "Towards an ADC BIST scheme using the histogram test technique," *Proceedings of the IEEE European Test Workshop*, pp. 53-58, 2000.

#### **CHAPTER 2**

#### OVERVIEW AND LITERATURE REVIEW

Analog-to Digital Converters (ADC) are the link between analog world of sensors and transducers and the digital world of signal processing and data handling in mixed-signal System-On-Chip (SOC). Most of the modern communication systems (like wireless sensor network) utilize digital signal processing (DSP) to resolve the transmitted information. Therefore, between the sensed analog signal and the DSP system, an analog-to-digital (A/D) interface is necessary. This analog-to-digital interface achieves the digitization of the sensed signal to a sampling rate requirement of the DSP system. As discussed in the earlier chapter, the trend of increasing integration level has forced the A/D interface to reside on the same silicon with large DSP or digital circuits. These digital circuits use digital technology that offers fast transistor biased at low voltages; therefore the ADC becomes the most challenging interface block. The tendency is therefore to use ADC architecture which trade accuracy for speed or vice versa as per the application. Now let us look at the ADC fundamentals, classification of ADC and ADC performance metrics in detail.

#### 2.1 ADC Fundamentals

The analog-to-digital (A/D) conversion is a process in which the analog input signal is converted to create digital words from the set of reference voltages. Here, the complete analog input signal is divided into 2<sup>N</sup> levels, where N is the resolution or number of output bits of ADC and each level is represented by a unique digital word. The input analog voltage is thus

represented as a digital word of resolution N corresponding to the level in which the input analog voltage falls [1]. The block diagram of an ADC is as shown in Figure 2.1.

In the block diagram of an ADC, a pre-filter or anti-aliasing filter is used to remove the high frequency components in the incoming analog signal to avoid the aliasing of higher frequency signals back into the baseband of the ADC. The sample/hold circuit follows the antialiasing filter, which samples the analog input voltage at regular sampling interval and holds it for converting to an equivalent output digital code. This conversion is accomplished with the help of the quantizer, which maps the output analog voltage of the sample/hold circuit to the corresponding digital word. The encoder then encodes the digital word into an N-bit binary digital output. Hence, within the conversion time, an analog input signal is converted to an equivalent digital output code [1].

#### 2.2 Classification of ADC

Based on the architecture used for the implementation of A/D converters, there are four main different types namely flash A/D converters, pipeline A/D converters, successive approximation A/D converters and delta-sigma ( $\Delta\Sigma$ ) A/D converters [2, 3]. The comparative graph with respect to resolution and bandwidth of four architectures discussed above are as shown in Figure 2.2.  $\Delta\Sigma$  ADC has the capability of trading off speed for resolution and at the same time is quite insensitive to component mismatches. As shown in the graph, delta-sigma A/D converters have the highest resolution in amplitude and lowest resolution in time (bandwidth). Hence these A/D converters are used for low frequency applications. Also, data converters have been classified into two categories based on the sampling frequency.

Figure 2.1. Block Diagram of an ADC [1].

Figure 2.2. ADC technologies comparative graph, with respect to resolution and bandwidth.

#### 2.2.1 Nyquist-Rate Converters

In Nyquist-rate ADCs, the analog input signal is sampled at the Nyquist frequency  $(f_n)$  such that  $f_s = f_n = 2$  x B, where  $f_s$  is the sampling frequency and B is the bandwidth of the input signal. These converters derives its name from the sampling theorem known as Nyquist theorem, which states that  $f_s$  should be at least twice larger than the highest frequency component present in the analog input signal to avoid aliasing and for successful reproduction of the signal after filtering [1, 2, 3]. Each analog input sample is processed separately and doesn't depend on the earlier analog input sample, thus the converter has no memory. In the Nyquist-rate converters, the linearity and accuracy is determined by matching the accuracy of the analog components used in building the converter. The Signal-to-Noise Ratio (SNR) of a Nyquist-rate converter is given by Eq. (2.1), where N is the resolution of the converter [1].

$$SNR = 6.02N + 1.76dB \tag{2.1}$$

#### 2.2.2 Oversampled Converters

In oversampling ADCs, the analog input signal is sampled at a sampling rate  $(f_s)$  much higher than the Nyquist frequency  $(f_n)$ . The input signal is sampled at an oversampling frequency  $f_s$ = K x  $f_n$  where K is the oversampling ratio and is given by Eq. (2.2) [1].

$$K = (f_s/2B) \tag{2.2}$$

In these converters output is generated by utilizing the current analog input with all preceding analog input values and thus the converter has memory element in its architecture. Thus, one-to-one relation between the input and output samples are destroyed in oversampling converters. Oversampling converters typically employ switched-capacitor circuits and hence the

need for sample and hold circuits are removed. Delta-Sigma ( $\Delta\Sigma$ ) ADC is classified under the oversampling converters.

#### 2.3 ADC Performance Metrics

The commonly used terms to measure the performance of a data converter in particular an ADC have been presented here. An ideal 3-bit ADC is considered for explaining the ADC's performance metrics [1, 2, 3]. The transfer curve of the ideal 3-bit ADC is as shown in Figure 2.3. The analog input in the ADC can have an infinite number of values between  $V_{ref-}$  and  $V_{ref+}$ , while the digital output code can be one from the finite set of codes dependent on the converter's output word length (resolution). Hence, as discussed earlier, the ADC approximates each input level with one of the digital output codes.

#### 2.3.1 Static Characteristics of ADC

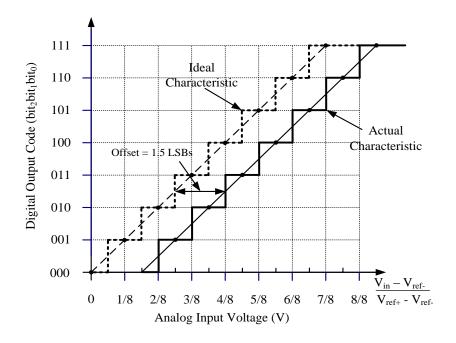

The performance metrics that define the static characteristics of the ADC are differential nonlinearity (DNL), integral nonlinearity (INL), offset error, gain error and monotonicity.

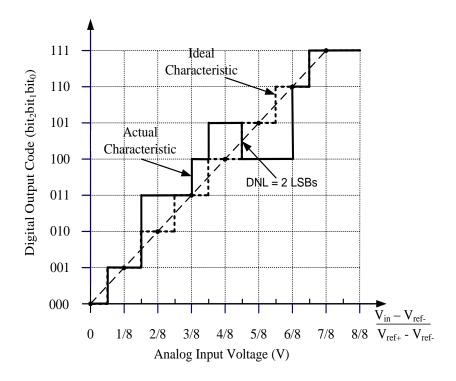

**Differential nonlinearity (DNL)** is the measure of the separation between two consecutive code transition points on the input axis from the ideal value of 1 LSB.

**Integral nonlinearity** (**INL**) is the maximum deviation between the actual finite resolution characteristic and the ideal finite resolution characteristic measured in percent or LSBs. It is the cumulative effect at any given input of all the DNL values and can be calculated by numerically integrating the DNL value for each code.

**Offset error or Offset** is the analog value of the digital output word for the input signal which should have ideally produced a zero output. It is the horizontal difference between the

Figure 2.3. Ideal input-output transfer curve of a 3-bit ADC.

Figure 2.4. DNL and INL illustration for a 3-bit ADC.

actual finite resolution and the ideal finite resolution characteristic. Figure 2.5 illustrates the example of offset error for a 3-bit ADC.

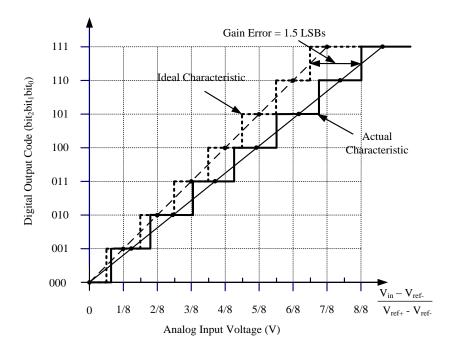

Gain Error or Gain is the difference between the actual characteristic, and the ideal characteristic (infinite resolution characteristic) when the offset error and other nonlinearity has been reduced to zero. This can also be thought as a change in the slope of the infinite resolution line from ideal 1. Gain error can be measured as the horizontal difference between the actual and ideal infinite resolution characteristic at highest digital code as illustrated in Figure 2.6.

**Monotonicity**: In a monotonic converter, the output always increases as the input increases. Hence nonmonotonicity occurs when a vertical jump in the output is negative and can be detected by DNL. When the vertical jump is 2 LSBs or greater, missing output code occurs and when the vertical jump is less than 0 LSBs, nonmonotonicity occurs as in Figure 2.7.

#### 2.3.2 Dynamic Characteristics of ADC

**Dynamic Range (DR)** is defined as the range of the amplitudes the ADC can effectively resolve. When the signal is too large it overloads and when it is too small it gets lost in the quantization noise.

**Signal-to-Noise Ratio** (**SNR**) is defined as the ratio of the signal power to total noise power at the ADC output. The sampling frequency is twice the signal bandwidth in a Nyquist converter and the SNR [1] is given by Eq. (2.3),

$$SNR = 6.02N + 1.76dB \tag{2.3}$$

**Signal-to-Noise Distortion Ratio (SNDR)** is defined as the ratio of the signal power to the total noise and the harmonic power at the output.

Figure 2.5. Offset Error illustration for a 3-bit ADC.

Figure 2.6. Gain Error illustration for a 3-bit ADC.

Figure 2.7. Monotonicity illustration for a 3-bit ADC.

**Spurious Free Dynamic Range (SFDR)** is defined as the ratio of the RMS value of the input sine wave for an ADC to the RMS value of the peak spur observed in the frequency domain. SFDR is expressed in decibels (dB) and is of importance in certain communications system.

**Total Harmonic Distribution (THD)** is defined as the ratio of the sum of the power of all harmonic frequencies above the fundamental frequency to the power of the fundamental frequency and is expressed as a percentage.

**Effective Number of Bits (ENOB)** is derived from the SNR and is given by the following equation [1].

$$ENOB = \frac{SNR_{actual} - 1.76}{6.02} \tag{2.4}$$

**Accuracy** is defined as the difference between the expected and the actual transfer response. The absolute accuracy includes the offset, gain and the linearity errors and relative accuracy is defined to be the accuracy after the offset and gain errors have been removed.

#### 2.4 Delta-Sigma ADC

The delta-sigma ( $\Delta\Sigma$ ) converters trade resolution in time (bandwidth) for resolution in amplitude, so that imprecise analog circuits can be used in the design.  $\Delta\Sigma$  converters are well suited for low bandwidth, high resolution and low cost making them a good ADC choice for many applications [3]. Delta-sigma ( $\Delta\Sigma$ ) analog-to-digital converters have been successful in realizing high resolution consumer audio products, such as MP3 players and cellular phones for some time now and recently in wireless sensor application. As explained earlier,  $\Delta\Sigma$  converters are well suited for low bandwidth, high-resolution acquisition, and low cost, making them a good ADC choice for many applications. Delta-sigma converters combine an analog delta-sigma modulator with a more complex digital filter. Accuracy depends on the noise and linearity performance of the modulator, which uses high performance amplifiers. Delta-Sigma modulators trade resolution in time for resolution in amplitude such that the use of imprecise analog circuits can be tolerated [3, 4].

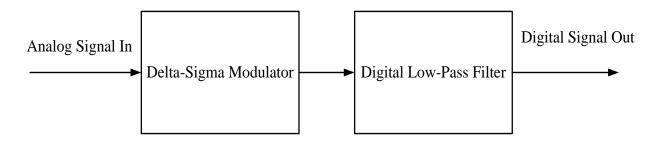

A block diagram of an analog-to-digital converter using delta-sigma modulator is shown in Figure 2.8. Delta-sigma converters come into the category of oversampled converters. Oversampling is simply the act of sampling the input signal at a frequency much greater than the

Nyquist frequency. One significant advantage of the method is that analog signals are converted using only a 1-bit ADC and analog signal processing circuits having a precision that is usually much less than the resolution of the overall converter. The penalty paid for the high resolution achievable with delta-sigma is that the hardware has to operate at the oversampled rate, much larger than the maximum signal bandwidth, thus demanding great complexity of the digital circuitry. Because of this limitation, these converters have traditionally been relegated to high-resolution, very-low frequency applications. In delta-sigma ADC, the digital low pass filter (decimation) stage which is responsible for achieving higher resolution and able to program a decimator offers further advantage of operating the ADC at different input channel bandwidths and with different oversampling ratios [3] which has been the focus of this research in Chapter 3.

Figure 2.8. Block diagram of A/D converter.

The programmable  $\Delta\Sigma$  ADC consists of an analog second order oversampled delta-sigma modulator and a digital third order decimator. Since it is difficult to program the analog second order delta-sigma modulator, the designed third order digital decimator of cascaded integrator comb filter type is made programmable to operate at three different oversampling ratios to give three different resolutions [5, 6]. Also in the designed programmable oversampling delta-sigma ADC, the decimator occupies most of the die area and consumes most of the power. In the

decimator, as the major part of powers consumed is by the integrator that operates at the higher sampling rate, introducing programmability by inserting coder circuits and reusing the same integrators for different resolutions and oversampling ratio has resulted in better optimized design in terms of area and power efficiency [3].

In the design to avoid the bit overflow in the integrator sections, 2's complement representation is used. In the design, coder circuits are used to reuse the same integrator for different resolutions and oversampling ratios and are designed by using multiplexer to sign extend the MSB and substituting it for appropriate bits. The performance metrics for the designed second order programmable oversampling delta-sigma ADC has also been investigated and presented in the following chapter.

#### 2.5 Testability of CMOS Data Converters

Systems for defense, homeland and security and space applications use off-the shelf electronic components especially integrated circuits designed and fabricated globally. There have been reported several techniques where malicious hardware Trojan circuits can be embedded into a system hardware [7, 8]. Detection techniques have been developed where inserted Trojans either can become detectable or their effects reduced thereby safeguarding the security of the system in use [9]. Some of the other techniques are based on information hiding and constraint manipulation based trusted IC design [10]. Fault-tolerant techniques are effective against failures and mistakes due to natural causes [11]. Deliberate faults or intelligent attackers work in stealth mode and use non-fault-tolerant hardware where hardware Trojans helps to perform their malicious goals.

The process variations pose very severe threat in current CMOS technologies. The process variation changes MOS model parameters and has detrimental effects specifically in the reliability and performance of mixed-signal and analog integrated circuits. Thus, modification can also be done during the manufacturing of integrated circuits in pretext of manufacturing defects assuming no tampering has been in the tape-out of the design file data. Thus, there is an urgent need to develop technology of detection of piracy of integrated circuits before these are put to use in actual systems. It also becomes extremely important since not all integrated circuits may be tested for actual use in military and space applications.

Testing of integrated circuits has hence become an integral part of manufacturing cycle. The focus of present research is on testing of analog-to-digital converters as these integrate both digital and analog integrated circuits and testability has been complex, costly and time consuming. Hence, these could be used as bench mark circuits for developing testing methodologies for detecting Trojans and possible unnoticeable manipulation at any level of design and technology implementations. As explained in the earlier chapter, testing of data converters can be divided into fault detection based testing and functionality based testing.

Individual traditional fault detection based testing methods such as the quiescent current testing, oscillation test methodology and the logic Scan-Path method in presence of faults and manufacturing defects have been examined by our research group and attempt to combine some or all of these testing methods for better testability and detecting possible Trojans in fabricated circuits [12, 13] under simulated conditions. Combination of multiple testing methods allowed simulated faults or manufacturing defects, introduced during design phase of integrated circuits,

testing simultaneously at multiple levels thereby increasing fault coverage and reducing the testing time needed for traditional testing.

Based on the built-in current sensors (BICS) for  $I_{DDQ}$  testing of CMOS delta-sigma (or sigma-delta) analog-to-digital converters and charge scaling digital-to-analog converters designed and implemented [14-17] earlier in our research group, the presented research highlights an attractive BICS for  $\Delta I_{DDQ}$  testing of CMOS data converters that takes into account the effect of process variation and increasing background current. In this method, the differential measurement successfully suppresses the impact of background current and process variation.

To improve the fault coverage and efficiency of the testability for analog-to-digital converter, functionality based linear ramp histogram testing technique [18] has been designed. The designed linear ramp histogram technique consists of a linear ramp generator, circuit-undertest (CUT), code detection unit, and interface/control unit. The code detection unit was first designed by using the synchronous counter and read/write interface/enable circuit to record the sample or occurrence. The synchronous counter is designed by using the JK flip flop and AND gate. Also an optimized version of the code detection unit using 6T SRAM cells instead of the synchronous counter was designed, implemented and tested as a part of this research. The designed histogram technique can be seamlessly combined with other testability technique to improve the fault coverage.

#### 2.6 References

[1] P. E. Allen, and D. R. Holberg, *CMOS Analog Circuit Design*, Second Ed., Oxford University Press, 2002.

- [2] Behzad Razavi, *Principles of Data Converter System Design*, IEEE Circuits and Systems Society, Wiley-IEEE Press, 1994.

- [3] R. J. Baker, CMOS Mixed-Signal Circuit Design Volume II of CMOS: Circuit Design, Layout, and Simulation, IEEE/Wiley-InterScience, 2002.

- [4] J. C. Candy and G. C. Temes, Oversampling Methods for A/D and D/A Conversion in Oversampling Delta-Sigma Data Converters, Wiley-IEEE Press, 1991.

- [5] A. Srivastava and R. R. Anantha, "A programmable oversampling sigma-delta analog-to-digital converter," *Proceedings of the 48<sup>th</sup> IEEE International Midwest Symposium on Circuits and Systems*, vol. 1, pp. 539-542, August 2005.

- [6] M. R. Miller, and C. S. Petrie, "A multibit sigma-delta ADC for multimode receivers," *IEEE Journal of Solid-State Circuits*, vol. 38, pp. 475-482, March 2003.

- [7] C. E. Irvine and K. Levitt, "Trusted hardware: can it be trustworthy?," *ACM/IEEE Design Automation Conference*, pp. 5-8, June 2007.

- [8] M. Tehranipoor, H. Salmani, X. Zhang, X. Wang, R. Karri, J. Rajendran and K. Rosenfeld, "Hardware Trojan detection solutions and design-for-trust challenges," *IEEE Computer*, pp. 64-72, July 2011.

- [9] R. S. Chakraborty and S. Bhunia, "Security against hardware Trojan through a novel application of design obfuscation," *Proceedings of the 2009 IEEE/ACM International Conference on Computer-Aided Design Digest of Technical Papers*, pp. 113-116, November 2009.

- [10] J. Gu, G. Qu and Q. Zhou, "Information hiding for trusted system design," *Proceedings of 2009 Design Automation Conference (DAC'09)*, pp. 698-701, July 2009.

- [11] I. Koren and A. D. Singh, "Fault tolerance in VLSI circuits," *IEEE Computer*, pp. 73-82, July 1990.

- [12] A. Srivastava, S. Yellampalli, P. K. Alli and S. S. Rajput, "Combined oscillation and I<sub>DDQ</sub> testing of CMOS amplifier circuit," *International Journal of Electronics*, vol. 97, Issue 1, pp. 1-15, January 2010.

- [13] S. Yellampalli and A. Srivastava, "ΔI<sub>DDQ</sub> testing of CMOS data converters," *Journal of Active and Passive Electronic Devices*, vol. 4, pp. 63-89, 2009.

- [14] A. Srinivas, *I<sub>DDQ</sub> testing of a CMOS 10-bit charge scaling digital-to-analog converter*, M.S. (EE) Thesis, Louisiana State University, Baton Rouge, 2003.

- [15] A. Srivastava, *I<sub>DDQ</sub> Testing of CMOS Mixed-Signal Integrated Circuits*, U.S. patent no.: 6,930,500, August 16, 2005.

- [16] A. Srivastava, S. Aluri and A. K. Chamakura, "A simple built-in current sensor for I<sub>DDQ</sub> testing of CMOS data converters," *Integration, the VLSI Journal*, vol. 38, no. 4, pp. 579-596, April 2005.

- [17] S. Yellampalli and A. Srivastava, " $\Delta I_{DDQ}$  based testing of submicron CMOS digital-to-analog converter circuits," *Journal of Active and Passive Electronic Devices*, vol. 3, pp. 341–353, 2008.

- [18] F. Azais, S. Bernard, Y. Bertrand and M. Renovell, "Towards an ADC BIST scheme using the histogram test technique," *Proceedings of the IEEE European Test Workshop*, pp. 53-58, May 2000.

### **CHAPTER 3**

# PROGRAMMABLE SECOND ORDER OVERSAMPLING CMOS DELTA-SIGMA ANALOG-TO-DIGITAL CONVERTER\*

#### 3.1 Introduction

Recent evolutions in integrated circuit and low-power design have led to the development of many low-cost, low-power battery operated wireless sensor networks [1]. Wireless sensor networks allow device mobility, fast and easy installation and relocation according to needs. These sensor networks can be used in many applications such as the natural habitat, environmental and structural health monitoring, health care and warning against bio-warfare agents [1-4]. The wireless sensor network consists of a large number of sensor nodes which are autonomous and spatially distributed to measure the environmental and physical conditions to be sensed as shown in Figure 3.1 [4]. These sensor nodes consist of sensing module, data processing with internal or external memory, communication module and power module as shown in Figure 3.2 [4]. The sensing module in the sensor node includes a sensing device to monitor and produce an analog signal which is converted to a digital output through an analog-to-digital converter (ADC).

<sup>\*</sup> Part of the work in this chapter was previously reported in following publications:

<sup>1.</sup> R. Soundararajan, A. Srivastava and J. Kamar, "A programmable second order oversampling CMOS sigmadelta analog-to-digital converter for wireless sensor networks," *Proceedings of the 12<sup>th</sup> International Conference on Information Technology (ICIT 2009)*, pp. 227-232, December 21-24, 2009.

<sup>2.</sup> R. Soundararajan and A. Srivastava, "A programmable second order oversampling CMOS sigma-delta analog-to-digital converter for low-power sensor interface electronics," *Proceedings of SPIE: Nano-, Bio-, and Info-Tech Sensors and Systems*, vol. 7646, pp. 7646P-1-7646P-11, March 7-11, 2010.

<sup>3.</sup> R. Soundararajan and A. Srivastava, "A programmable oversampling CMOS delta-sigma analog-to-digital converter for low-power interface electronics," *Journal of Low Power Electronics*, vol. 8, No. 3, pp. 336-346(11), June 2012.

Figure 3.1. Sensor network [4].

Figure 3.2. Block diagram of a sensor node [4].

In wireless sensor networks, the effective and efficient use, its design and architecture are influenced by many factors such as the fault tolerance, scalability, production cost, operating conditions, sensor network topology, hardware constraints, transmission media and most importantly the power consumption to maximize the network lifetime, add flexibility, facilitate data collection and minimize the need for maintenance of the sensor node. This becomes important due to the fact that the sensor nodes are mostly equipped with limited power source for mobility and relocation, and cannot be easily replenished. Recently, most of the research in the sensor network has been focused on the development of low-power and energy efficient hardware [4-6], because the lifetime of the sensor node shows a strong dependence on the batter lifetime. The roles of the communication module and the processor in the power consumption have been widely addressed by several researchers [4-6] which led to new architectures. In the sensor module, the resolution of the ADC has direct impact on energy consumption of the module since every bit consumes significant power. Hence, high resolution is not needed in a sensor node and so the work focuses on ADC that can be of programmable type, thereby allowing programming the resolution depending upon the need.

The focus is on design and implementation of a programmable second order oversampling CMOS delta-sigma ( $\Delta\Sigma$ ) analog-to-digital converter using programmable cascaded integrator comb (CIC) decimation filter in 0.5 µm n-well CMOS processes for integration in sensor nodes for wireless sensor networks. We have selected the delta-sigma ADC as they provide very high resolution by oversampling and modulation and utilize low-performance analog circuitry by shifting the burden on the digital circuitry.

### 3.2 Programmable Second Order Oversampling Delta-Sigma ( $\Delta\Sigma$ ) ADC