# HIERARCHICAL VERIFICATION OF ASYNCHRONOUS CIRCUITS USING TEMPORAL LOGIC

# B. MISHRA and E. CLARKE\*

Department of Computer Science, Carnegie-Mellon University, Pittsburgh, PA 15213, U.S.A.

Communicated by M. Nivat Received June 1984

Abstract. Establishing the correctness of complicated asynchronous circuit is in general quite difficult because of the high degree of nondeterminism that is inherent in such devices. Nevertheless, it is also very important in view of the cost involved in design and testing of circuits. We show how to give specifications for circuits in a branching time temporal logic and how to mechanically verify them using a simple and efficient model checker. We also show how to tackle a large and complex circuit by verifying it hierarchically.

### Introduction

Verification of the correctness of asynchronous circuits has been considered an important problem for a long time. But, a lack of any formal and efficient method of verification has prevented the creation of practical design aids for this purpose. Since all the known techniques of simulation and prototype testing are time-consuming and not very reliable, there is an acute need for such tools. Moreover, as we build larger and more complex circuits, the cost of a single design error is likely to become even higher. In this paper, we describe an automatic verification system for asynchronous circuits, in which the specifications are expressed in a propositional temporal logic. We illustrate the use of our system by verifying a version of the self-timed queue element given in [7].

Bochmann [2] was probably the first to recognize the usefulness of temporal logic to describe circuits; he verified an implementation of a self-timed arbiter using linear temporal logic and what he called 'reachability analysis'. The work of Malachi and Owicki [9] identified additional temporal operators required to express interesting properties of a circuit and also gave specifications of a large class of modules used in self-timed systems.

Although these researchers have contributed significantly toward developing an adequate notation for expressing the correctness of asynchronous circuits, the problem of mechanically verifying a circuit using efficient algorithms still remains unsolved. In this paper we show how a simple and efficient algorithm, called a

<sup>\*</sup> This research was supported by NSF under Grant No. MCS-82-16706.

model checker, can be used to verify various temporal properties of an asynchronous circuit. Roughly speaking, our method works by first building a labelled state-transition graph for an asynchronous circuit. This graph can be viewed as a finite Kripke Structure. Then by using the model checker we determine the truth of various temporal formulae in this Kripke Structure. As a result, it is possible to avoid the complexity associated with proof construction.

Most complex circuits are built out of relatively less complex modules in a hierarchical manner. Hence it should be possible to verify these circuits in a hierarchical manner, i.e. to verify the correctness of a larger module, given the premises that the smaller modules are correct. A hierarchical approach to verification is important in practice, because it enables us to verify circuits incrementally, to localize faults to small submodules and most importantly, to handle large circuits without a large growth in complexity. We show how the hierarchical method can be incorporated in a mechanical approach to circuit verification.

The paper is organized as follows: Section 1 contains a brief description of the syntax and semantics of CTL, the temporal logic used in this paper, and also explains the algorithms used in the model checker. In Section 2, we give a simple step-by-step method used to verify circuits. In Section 3, we illustrate these methods by establishing some interesting properties of a Self-Timed Queue (FIFO) Element. In Section 4, we introduce a hierarchical method to be used in verifying large and complex circuit and study some of the model-theoretic properties of the operation of 'restriction' on a Kripke Structure. The paper concludes by pointing out the shortcomings of our approach and with a discussion of some remaining open problems.

#### 1. CTL and model checker

The logic that we use to give the specifications of a circuit is a propositional temporal logic of branching time, called CTL (Computation Tree Logic). This logic is essentially the same as that described in [1, 3, 5].

The syntax for CTL is given below:

Let  $\mathcal{P}$  be the set of all the atomic propositions in the language  $\mathcal{L}$ . Then

- (1) every atomic proposition P in  $\mathcal{P}$  is a formula in CTL,

- (2) if  $f_1$  and  $f_2$  are CTL formulae, then so are  $\neg f_1, f_1 \land f_2, \forall X f_1, \exists X f_1, \forall (f_1 \cup f_2)$  and  $\exists (f_1 \cup f_2)$ .

In this logic the propositional connectives  $\neg$  and  $\land$  have their usual meanings of negation and conjunction. The temporal operator X is the *nexttime operator*. Hence the intuitive meaning of  $\forall X f_1 \ (\exists X f_1)$  is that  $f_1$  holds in every (in some) immediate successor state of the current state. The temporal operator U is the *until operator*. The intuitive meaning of  $\forall (f_1 \ U \ f_2) \ (\exists (f_1 \ U \ f_2))$  is that for every computation path (for some computation path), there exists an initial prefix of the path such that  $f_2$  holds at the last state of the prefix and  $f_1$  holds at all other states along the prefix.

We also use the following syntactic abbreviations:

- $f_1 \lor f_2 \equiv \neg(\neg f_1 \land \neg f_2), f_1 \to f_2 \equiv \neg f_1 \lor f_2, \text{ and } f_1 \leftrightarrow f_2 \equiv (f_1 \to f_2) \land (f_2 \to f_1),$

- $\forall \mathbf{F} f_1 \equiv \forall (\mathbf{true} \ \mathbf{U} \ f_1)$  which means for every path, there exists a state on the path at which  $f_1$  holds,

- $\exists \mathbf{F} f_1 \equiv \exists (\mathbf{true} \ \mathbf{U} \ f_1)$  which means for some path, there exists a state on the path at which  $f_1$  holds,

- $\forall G f_1 \equiv \neg \exists F \neg f_1$  which means for every path, at every node on the path  $f_1$  holds,

- $\exists G f_1 \equiv \neg \forall F \neg f_1$  which means for some path, at every node on the path  $f_1$  holds,

- $\forall (f_1 \ \mathbf{W} \ f_2) \equiv \neg \exists ((f_1 \land f_2) \ \mathbf{U} \ (\neg f_1 \land f_2))$  which means that for every computation path, and for every initial prefix of the path, if  $f_2$  holds at all the states along the prefix then  $f_1$  holds at all the states along the same prefix,

- $\exists (f_1 \mathbf{W} f_2) \equiv \neg \forall ((f_1 \land f_2) \mathbf{U} (\neg f_1 \land f_2))$  which means that for some computation path, and for every initial prefix of the path, if  $f_2$  holds at all the states along the prefix then  $f_1$  holds at all the states along the same prefix.

In the last two formulae, W is the while operator. The formula  $\forall (f_1 \mathbf{W} f_2)$   $(\exists (f_1 \mathbf{W} f_2))$  is read as 'for every (some) path  $f_1$  while  $f_2$ '.

The semantics of a CTL formula is defined with respect to a labelled state-transition graph. A CTL structure is a triple  $\mathcal{M} = (S, R, \Pi)$  where

- (1) S is a finite set of states.

- (2) R is a total binary relation on S ( $R \subseteq S \times S$ ) and denotes the possible transitions between states.

- (3)  $\Pi$  is an assignment of atomic proposition to states, i.e.  $\Pi: S \mapsto 2^{\mathscr{P}}$ .

A path is an infinite sequence of states  $(s_0, s_1, s_2, ...)$  such that  $\forall_i (\langle s_i, s_{i+1} \rangle \in R)$ . For any structure  $\mathcal{M} = (S, R, \Pi)$  and state  $s_0 \in S$ , there is an infinite computation tree with root labelled  $s_0$  such that  $s \to t$  is an arc in the tree iff  $\langle s, t \rangle \in R$ .

The *truth* in a structure is expressed by  $\mathcal{M}$ ,  $s_0 \models f$ , meaning that the temporal formula f is satisfied in the structure  $\mathcal{M}$  at state  $s_0$ . The semantics of temporal formulae is defined inductively as follows:

$$s_0 \models P$$

iff  $P \in \Pi(s_0)$ .

$s_0 \models \neg f$  iff  $s_0 \not\models f$ .

$s_0 \models f_1 \land f_2$  iff  $s_0 \models f_1$  and  $s_0 \models f_2$ .

$s_0 \models \forall X f_1$  iff for all states  $t$  such that  $\langle s_0, t \rangle \in R$ ,  $t \models f_1$ .

$s_0 \models \exists X f_1$  iff for some state  $t$  such that  $\langle s_0, t \rangle \in R$ ,  $t \models f_1$ .

$s_0 \models \forall (f_1 \cup f_2)$  iff for all paths  $(s_0, s_1, s_2, \ldots)$ ,  $\exists i \geqslant 0 (s_i \models f_2 \land \forall_{0 \leqslant j < i} (s_j \models f_1))$ .

$s_0 \models \exists (f_1 \cup f_2)$  iff for some path  $(s_0, s_1, s_2, \ldots)$ ,  $\exists i \geqslant 0 (s_i \models f_2 \land \forall_{0 \leqslant j < i} (s_j \models f_1))$ .

From these it is quite easy to see that the semantics of U, the until operator, can be easily given in terms of a *least fixed-point* characterization:

$$\forall (f_1 \cup f_2) \equiv \mu \mathscr{F} \cdot f_2 \vee (f_1 \wedge \forall X \mathscr{F}).$$

$$\exists (f_1 \cup f_2) \equiv \mu \mathscr{F} \cdot f_2 \vee (f_1 \wedge \exists X \mathscr{F}).$$

The model checker for CTL can now be thought of as an algorithm that determines the satisfiability of a given temporal formula  $f_1$  in a model  $\mathcal{M}$ , by computing these fixed points. A full description of the algorithm is given in [3].

In order to determine if a CTL formula f is true in a structure  $\mathcal{M} = (S, R, \Pi)$ , the algorithm labels each state of S so that when the algorithm terminates, the label of each state  $s \in S$ , label(s), will be equal to  $\{f' \in sub(f) | \mathcal{M}, s \models f'\}$ , where each element of sub(f) is either a subformula of f or the negation of the subformula. Hence  $\mathcal{M}, s \models f$  iff  $f \in label(s)$  at the termination of the algorithm.

The labelling algorithm works in several stages. In the *i*th stage the algorithm labels the states by the subformulae of length *i*. The labels assigned in the earlier stages, corresponding to the subformulae of length less than *i* are used to perform the labelling in this stage. It can be shown that the algorithm makes at most n = |f| stages of computation and that the total amount of the work involved in each stage is O(|S| + |R|). Hence the time complexity of the model checker is  $O(|f| \cdot (|S| + |R|))$ . The algorithm is also fairly simple, since it involves only a few straightforward graph theoretic algorithms.

### 2. Verification of circuits

Given a circuit to be verified, the steps involved in using the model checker to assert the correctness of the temporal specifications are as follows:

## Step 1. Building the model

The structure associated with the circuit is essentially a finite state-transition graph, with its vertices corresponding to the distinct states and the edges corresponding to the (possibly nondeterministic) transition between the states. The initial label associated with each state is the set of propositions true in that state. This labelled state-transition graph can be built using the following simple algorithm.

Algorithm 2.1. The algorithm to build the Kripke Structure for an asynchronous circuit.

```

begin

L:= {initial state};

while L≠∅ do

choose a state, say s from L and delete it from L;

for all sets of inputs, possible in s do

simulate s with this set of inputs;

let L' be the set of new states;

for each s'∈ L' do

s' is a successor of s;

if s' has not been visited then add s' to L;

```

endfor; endfor; endwhile; end.

Step 2. Giving the specifications of the circuit in CTL

It usually involves structural properties (i.e. the specifications for different components of the circuit, specifications of the signalling scheme used for communication with various modules, etc.), safeness properties and liveness properties. It should be pointed out that one need not give the complete specification of the circuit in order to verify some selected properties of the circuit using the model checker.

# Step 3. Verifying the circuit using the model checker

This step involves the model checker which checks the truth of the specification (a formula in CTL) in the structure constructed in Step 1. The working of the model checker is described in the previous section.

# 3. Extended example

We illustrate the ideas presented so far by verifying some interesting properties of an asynchronous circuit. The example chosen for this purpose is one element of a Self-timed (FIFO) queue, which originally appeared in an article by Seitz on self-timed systems [7].

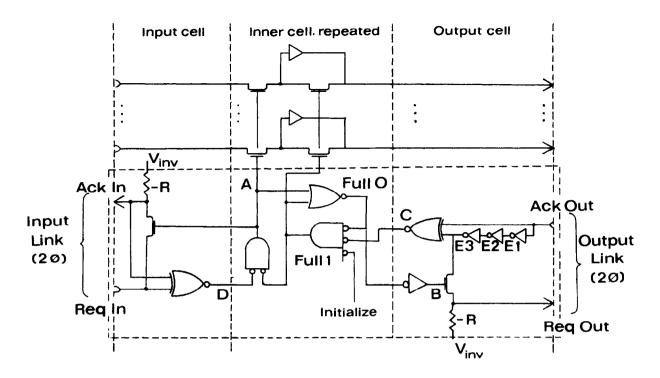

(a) Self-timed FIFO queue element. The electrical circuit shown in Fig. 1 is an implementation of a single FIFO queue element combined with some input and output logic. This circuit is of very practical importance; in pipeline processes in which operation times are variable, increased throughput can be achieved by interconnecting the processing elements through queues. The implementation uses simple asynchronous control and hence, can be used to build very fast and area-efficient queues.

The inner cell is intended to be replicated as many times as the number of words the queue is to be able to store, and the same control will operate a queue of any word length. The input cell and the output cell can be thought of as logic circuits converting the two-cycle signalling scheme and the input link to a four-cycle signalling scheme at the internal link and vice versa. The inner cell can be thought of as a latch that stores the state of the cell (i.e. whether the cell is full or empty), together with logic to generate a load signal and a set of static registers to store the bits. However, the design shown is not speed-independent, and uses the 3/2-rules. That

Fig. 1. Queue (FIFO) element.

is one may expect misoperation if particular sets of three gates have a smaller cumulative propagation delay time than other sets of two gates.

In the following subsections we specify and verify some interesting properties of the queue element with a single inner cell.

(b) Temporal specifications for the self-timed queue element. We give examples of the ways in which various properties of a circuit can be given in CTL. In case of the queue element some of the structural properties that we might like to specify, are that the two-cycle signalling used at the input links and the output links is safe and live. Recall that the structural properties are specifications for various components and signalling schemes and thus, may be considered as premises that must be true in any CTL structure modelling the circuit. Hence the request signal must satisfy the following safeness and liveness conditions. (In the following CTL specifications we will use symbols Req and Ack for the request and the acknowledgement signals respectively.)

Safeness conditions for the request signal

- (1)  $\forall \mathbf{G}((\neg \text{Reg } \land \text{Ack}) \rightarrow \forall (\neg \text{Reg } \mathbf{W} \text{ Ack})),$

- (2)  $\forall \mathbf{G}((\text{Req } \land \neg \mathbf{Ack}) \rightarrow \forall (\text{Req } \mathbf{W} \neg \mathbf{Ack})).$

These two CTL formulae essentially express that if the Req and Ack signals are non-equipotential then the Req signal will remain in its stable logic value while Ack signal is in its stable value. In other words, Req will not be given unless acknowledgement to previous request signal has arrived.

Liveness conditions for the request signal

- (1)  $\forall G((Req \land Ack) \rightarrow \forall F(\neg Req)),$

- (2)  $\forall \mathbf{G}((\neg \text{Req} \land \neg \text{Ack}) \rightarrow \forall \mathbf{F}(\text{Req})).$

These two CTL formulae express the property that if the Req and Ack signals are equipotential then *eventually* the Req signal will change its logic value, thus indicating an arrival of a request.

In a similar manner, we can specify the properties of the response signal.

Safeness conditions for the response signal

- (1)  $\forall G((Req \land Ack) \rightarrow \forall (Ack \ W \ Req)),$

- (2)  $\forall G((\neg Req \land \neg Ack) \rightarrow \forall (\neg Ack W \neg Req)).$

Informally, they express the fact that Ack will not be given unless there has been a Req signal to cause it.

Liveness conditions for the response signal

- (1)  $\forall G((Req \land \neg Ack) \rightarrow \forall F(Ack)),$

- (2)  $\forall \mathbf{G}((\neg \text{Req} \land \text{Ack}) \rightarrow \forall \mathbf{F}(\neg \text{Ack})).$

That is, if there had been a Req signal then eventually there will be an Ack signal in response to the request.

We can also give the safeness and the liveness properties of the FIFO queue element in CTL. The following is a representative list of some of the properties, and by no means, exhaustive and complete. In the CTL formulae given below, ReqIn stands for request at the input links, AckIn, for acknowledgement at the input links, ReqOut, for request at the output links, AckOut, for acknowledgement at the output links and Full1, for the state of the queue element when it holds some data.

Some safeness properties of the queue element

(1)

$$\forall G(\neg(ReqIn = AckIn) \land \neg(ReqOut = AckOut)$$

$\rightarrow \forall(\neg(ReqIn = AckIn) \ U \ (ReqOut = AckOut))).$

This formula states that if there have been a ReqIn and a ReqOut, then AckIn will not be given until AckOut has arrived.

Some liveness properties of the queue element

(1)  $\forall \mathbf{G}(\neg(\mathbf{RegIn} = \mathbf{AckIn}) \land \neg \mathbf{Full} 1 \rightarrow \forall \mathbf{F}(\mathbf{A})).$

This formula states that if there has been a ReqIn, and the memory element was empty, then eventually it will be loaded with the input data.

(2)  $\forall \mathbf{G}(\neg \text{Full} 1 \rightarrow \forall \mathbf{X}(\text{Full} 1 \rightarrow \forall \mathbf{F}(\neg(\text{RegOut} = \text{AckOut})))).$

That is the queue element is full then eventually a request at the output links will be generated in order to move the data to the next element in the queue.

```

(3) \forall G(\text{Full } \land \neg(\text{ReqOut} = \text{Ackout}) \rightarrow \forall X((\text{ReqOut} = \text{AckOut}) \rightarrow \forall F(\neg \text{Full } 1))).

```

That is if the acknowledgement arrives at the *output links* thus indicating that the data stored in the current queue element has been moved to the next element, then *eventually* the queue element will mark its state as empty.

In the next subsection we show how these specifications can be verified automatically by using a model checker.

(c) Verification of the circuit. As a first step for the verification of the circuit, we build a labelled finite state-transition graph corresponding to the circuit given in Fig. 1, using Algorithm 2.1. For this model, we assume that each gate of the circuit has one unit delay. This is done in order to take care of the speed-dependent properties of the circuit. This is equivalent to assuming that for any state in the graph, any of the successor states is arrived at after one unit gate-delay. The label associated with each state is the set of nodes in the circuit which assume the logical value 1 in that state. The nodes of the circuit are—AckIn, ReqIn, D, A, Fullo, Full1, C, B, E1, E2, E3, ReqOut, and AckOut. The initial state corresponds to the situation when ReqIn and AckIn as well as ReqOut and AckOut are equipotential.

Now, the model checker can take a description of the model and a temporal formula specifying some property of the circuit, and determine truth of the formula in that model. However the circuit shown does *not* obey the 3/2-rule as advertised, and the model checker determines that the safeness property of the queue element, given in the previous subsection is *not* true.

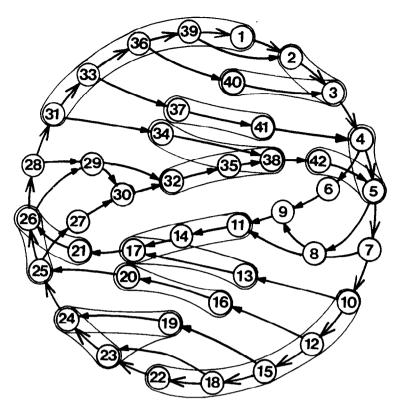

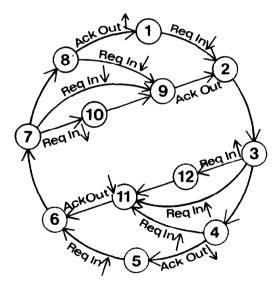

Informally, the problem can be described as follows: when an AckOut is received in response to the ReqOut signal, the AckOut signal travels via two different electrical paths—one involving three inverters and the other involving four gates. This creates a race condition and produces a glitch of about one gate delay on the ReqOut bus. Though this glitch may not always be able to drive the bus to create a spurious ReqOut, it has the potential to do so. However, this problem can be easily rectified by making the inverters slow or by putting five inverters on that path instead of three. The labelled state-transition graph for the corrected circuit is shown in Fig. 2.

The state-transition graph shown in Fig. 2 is only one portion of the complete state-transition graph for the FIFO queue element and corresponds to the initial state where both ReqIn and AckIn are both at logical-zero value and both ReqOut and AckOut are at logical-zero value. But the state in which both ReqIn and AckIn are at logical-zero and both ReqOut and AckOut are at logical-one can not be reached from this state-transition graph. In fact the state-graph with this situation as the initial condition is symmetric to the one shown and the complete state-transition graph consists of both of these components.

Fig. 2. The state-transition graph for the self-timed queue element.

```

time: (1453 168)

\models AG(((\sim ReqIn \& AckIn) | (ReqIn \& \sim AckIn)) \&

((~ReqOut & AckOut)|(ReqOut & ~AckOut)) ->

\{<7 \text{ secs.}\}

A[((\sim ReqIn \& AckIn) | (ReqIn \& \sim AckIn)) U

((ReqOut & AckOut)|(~ReqOut & ~AckOut))])

time: (2263 300)

\models AG(((\sim ReqIn \& AckIn) | (ReqIn \& \sim AckIn)) \& (\sim Full1) -> AF(A))

[<8 \text{ secs.}]

time: (2694 300)

\models AG(\sim Full 1 \rightarrow AX(Full 1 \rightarrow AF((\sim RegOut \& AckOut)))

(RegOut \& \sim AckOut)))

[<8 secs.]

time: (3150 300)

= AG(Full1 & ((~ReqOut & AckOut) | (ReqOut & ~AckOut)) ->

AX(((RegOut \& AckOut)|(\sim RegOut \& \sim AckOut)) -> AF(\sim Full 1)))

[<7 \text{ secs.}]

t

```

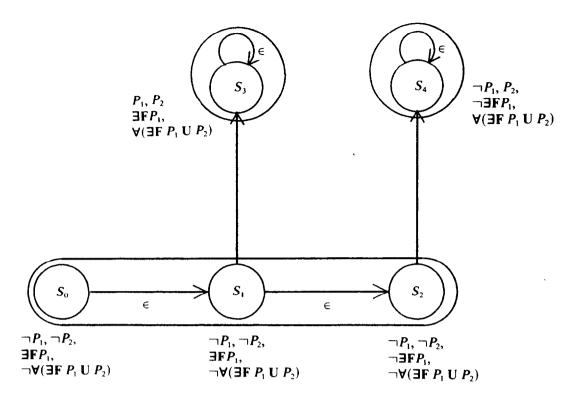

Fig. 3. A sample run using the model checker.

A sample run using the model checker is shown in Fig. 3. In the formula shown A stands for  $\forall$ , E for  $\exists$ , | for  $\lor$ , & for  $\land$ ,  $\sim$  for  $\neg$  and -> for  $\rightarrow$ . Similarly, G, F, U, and W will stand for G, F, U and W, respectively. The first component of 'time:' is the cumulative time in 60th of a second; the second component is the portion of the cumulative time allocated to 'garbage collection'. The number to the right of each formula gives the time taken to determine the truth of the formula.

#### 4. Hierarchical verification of circuits

The scheme given so far can be practical only for very small circuits. This is because it suffers from the problem that the state transition graph may have a number of states, exponential in the number of gates. However, this problem can be avoided, if circuits are verified in a hierarchical manner. That is, first small modules are verified and then the bigger module is verified assuming that the smaller modules it is composed of are correct. Since at any hierarchical level, the number of small modules that a big module is composed of is relatively small, this method is amenable to proving correctness of large circuits without a large growth of the time complexity. Moreover, hierarchical verification permits the localization of faults to small submodules, thus allowing the designer to rectify the fault by redesigning the appropriate submodule.

In a hierarchical approach, the state-transition graph for a circuit is built out of the descriptions of the constituent submodules. We obtain short a description of a module by using an operation called 'restriction'. If  $\mathcal{L}$  is the language for the module with a set of atomic propositions  $\mathcal{P}$ , corresponding to the input, output and internal nodes, then the operation restriction on  $\mathcal{L}$ , obtains a  $\mathcal{L}'$  with atomic propositions  $\mathcal{P}'$ , corresponding to the input and the output nodes only.

Roughly speaking, the effect of restriction is to make the internal nodes invisible, since in building the state transition graph for the bigger module, we only require input-output behaviour of the constituent submodules. But when the internal nodes are made invisible, certain portions of the state graph will have same labelling of the atomic (input and output) propositions. The restriction operation defines exactly when such states can be collapsed into a single state.

Unfortunately, when we restrict a CTL structure to obtain a smaller structure, some formulae that are true in the former structure may not be true in the restricted structure. However, by appropriately constraining CTL, we can show that the formulae in the constrained logic have the desirable property that the truth properties of such formulae are preserved with respect to the restriction operation. Most of the formulae used in Section 3 have the desired syntax.

Let the CTL structure for  $\mathscr{L}$  be  $\mathscr{M}=(S,R,\Pi)$ . Let  $\mathscr{P}$  be the set of all atomic propositions in the language  $\mathscr{L}$ , consisting of  $\mathscr{I}$ , the set of atomic propositions corresponding to the *inputs*;  $\mathscr{O}$ , the set of atomic propositions corresponding to the *outputs* and  $\mathscr{I}nt$ , the set of atomic propositions corresponding to the *internal nodes* of the circuit. That is  $\mathscr{P}=\mathscr{I}\cup\mathscr{O}\cup\mathscr{I}nt$ . Let  $\mathscr{L}'$  be the language with the atomic propositions,  $\mathscr{P}'=\mathscr{I}\cup\mathscr{O}$ . Define  $\Pi_{\mathscr{P}'}\colon S\mapsto 2^{\mathscr{P}'}$  to be the restriction of  $\Pi$  to  $\mathscr{P}'$ , i.e.  $\forall s\in S(\Pi_{\mathscr{P}'}(s)=\Pi(s)\cap\mathscr{P}')$ . Now we can define a relation  $\mathscr{E}(\mathscr{E}\subseteq S\times S)$  over the set of states of  $\mathscr{M}$  such that  $s\mathscr{E}s'$  iff for some path  $(s_0,s_1,\ldots,s_n)$  of  $\mathscr{M}$ ,  $n\geq 0$ ,  $s=s_0$  and  $s_n=s'$  and for each predecessor of  $s_i,s_i'$   $(1\leq i\leq n),\Pi_{\mathscr{P}'}(s_i')=\Pi_{\mathscr{P}'}(s_i)$ .

It is quite easy to see that the relation  $\mathscr E$  over S, is reflexive and transitive but not symmetric. The transitive closure of  $\mathscr E$  can be defined as

$$\mathscr{E}^* = \mathscr{E} \cup \mathscr{E}^2 \cup \mathscr{E}^3 \cup \cdots \cup \mathscr{E}^n \cup \cdots.$$

The  $\mathscr{E}$ -closure of a state s is defined by  $\mathscr{E}^*(s) = \{s' \mid s \mathscr{E}^* s'\} = \{s' \mid s \mathscr{E} s'\}$ , since  $\mathscr{E}$  is a transitive relation, i.e.  $\mathscr{E}^* = \mathscr{E}$ .

For a set of sets  $\{u_j\}$ ,  $\max(\{u_j\})$  will denote the set of all distinct sets in  $\{u_j\}$  maximal under inclusion. We define a mapping  $\varphi \colon S \mapsto 2^S$  such that for each  $s \in S$ ,

$$\varphi(s) = \max(\{H_i \mid s \in H_i \text{ and } \exists s_i \in S \ (\mathscr{E}^*(s_i) = H_i)\}),$$

i.e.  $\varphi(s)$  is the set of maximal  $\mathscr{E}$ -closures containing s. We consider the following subsets of S,

$$\Delta = \varphi(S) = \bigcup_{s \in S} \varphi(s).$$

Since every element  $s \in S$  belongs to at least one subset  $H_i$  of  $\Delta$ ,  $\Delta$  is called a decomposition of S and the  $H_i$ 's are called the blocks of the decomposition. We will say s dominates s' if  $s \mathcal{E} s'$ . We define the dominant states of  $H_i$ , dom $(H_i)$  as the set of states that dominate every other states in  $H_i$ .

The decomposition  $\Delta$  naturally leads to a *substructure* of a model  $\mathcal{M}$  (notation  $\mathcal{M}' = (S', R', \Pi') = \mathcal{M}|\Delta$ ). The states of  $\mathcal{M}'$  will be the blocks of  $\Delta$ . A block  $H_i$  of  $\Delta$ , when considered as an element of S', will be denoted by  $\bar{H}_i$ . Let R' ( $R' \subseteq S' \times S'$ ) be the total binary relation on S', corresponding to R and induced by the decomposition  $\Delta$ , i.e.

$$\langle \bar{H}_i, \bar{H}_j \rangle \in R'$$

, for  $i \neq j$ , iff for some  $s_i \in H_i$ ,  $s_j \in H_j$ ,  $\langle s_i, s_j \rangle \in R$  and  $s_j \notin H_i$ .

$\langle \bar{H}_i, \bar{H}_i \rangle \in R'$  iff for some  $s_i$ ,  $s_j \in H_i$ ,  $s_j \mathcal{E} s_i$  and  $\langle s_i, s_j \rangle \in R$ .

Similarly, let  $\Pi': S' \mapsto 2^{\mathscr{P}'}$  be the mapping corresponding to  $\Pi$  and induced by the decomposition  $\Delta$ , i.e.

$$\Pi'(\bar{H}_i) = \mathscr{P}' \cap \bigcap_{s \in H_i} \Pi(s).$$

The model  $\mathcal{M}' = (S', R', \Pi')$  is called a *restriction* of  $\mathcal{M} = (S, R, \Pi)$  with respect to  $\mathcal{P}' \subseteq \mathcal{P}$ .

In the following theorem, we show that there are CTL formulae whose truth-properties are not preserved with respect to restriction.

**Theorem 4.1.** There exists a CTL structure  $\mathcal{M} = (S, R, \Pi)$  and a formula  $\mathcal{F}$  where  $\mathcal{F}$  is a CTL formula such that

$$\mathcal{M}, s_0 \models \mathcal{F} \text{ but } \mathcal{M}', \bar{H}_0 \not\models \mathcal{F}, \text{ and } s_0 \in \text{dom}(H_0).$$

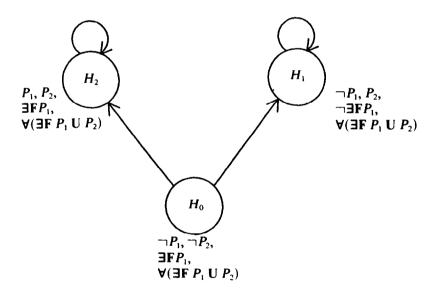

**Proof.** We give counterexamples involving formulae of the form  $\forall XP, \exists XP$  and  $\forall (\exists F P_1 \cup P_2)$ .

We first give a model  $\mathcal{M} = (S, R, \Pi)$  over a language  $\mathcal{L}$  such that  $\mathcal{M}, s_0 \models \forall XP$  and  $\mathcal{M}, s_0 \models \exists XP$ , but  $\mathcal{M}', \bar{H}_0 \not\models \forall XP$  and  $\mathcal{M}', \bar{H}_0 \not\models \exists XP$ , where  $\mathcal{M}'$  is a restriction of  $\mathcal{M}$  and  $s_0 \in \text{dom}(H_0)$ .

Define  $\mathcal{M} = (S, R, \Pi)$  over a language  $\mathcal{L}$  with the set of propositions  $\mathcal{P}$ ,  $\mathcal{P} = \{P_{in}, P'_{in}, P_{int}\}$ , by

$$S = \{s_0, s_1, s_2\}, \qquad R = \{\langle s_0, s_1 \rangle, \langle s_1, s_2 \rangle, \langle s_2, s_2 \rangle\},\$$

and  $\Pi$  to be  $\Pi(s_0) = \{P_{\text{in}}, P_{\text{int}}\}$ ,  $\Pi(s_1) = \{P_{\text{in}}\}$  and  $\Pi(s_2) = \{P'_{\text{in}}, P_{\text{int}}\}$ . Clearly,  $\mathcal{M}, s_0 \models \forall X P_{\text{in}}$  and  $\mathcal{M}, s_0 \models \exists X P_{\text{in}}$ . Now if we take restriction of  $\mathcal{M}$  for language  $\mathcal{L}'$  with the set of propositions  $\mathcal{P}'$ ,

$$\mathcal{P}' = \{P_{\rm in}, P_{\rm in}'\},$$

then we get  $\mathcal{M}' = (S', R', \Pi')$  where

$$S' = \{ \vec{H}_0, \vec{H}_1 \}, \qquad R' = \{ \langle \vec{H}_0, \vec{H}_1 \rangle, \langle \vec{H}_1, \vec{H}_1 \rangle \},$$

and  $\Pi'$  to be  $\Pi'(\bar{H}_0) = \{P_{\rm in}\}$  and  $\Pi'(\bar{H}_1) = \{P'_{\rm in}\}$ . It can be easily seen that  $\mathcal{M}'$ ,  $\bar{H}_0 \nvDash \forall X P_{\rm in}$  and  $\mathcal{M}'$ ,  $\bar{H}_0 \nvDash \exists X P_{\rm in}$ .

Similarly, we present a model  $\mathcal{M} = (S, R, \Pi)$  such that  $\mathcal{M}, s_0 \models \neg \forall ((\exists FP_1) \cup P_2)$ , but  $\mathcal{M}', \bar{H}_0 \not\models \neg \forall ((\exists FP_1) \cup P_2)$ , where  $\mathcal{M}'$  is a restriction of  $\mathcal{M}$  and  $s_0 \in \text{dom}(H_0)$ .

Define  $\mathcal{M} = (S, R, \Pi)$  over a language  $\mathcal{L}$  with the set of propositions  $\mathcal{P}$ ,  $\mathcal{P} = \{P_1, P_2, P_{\text{int1}}, P_{\text{int2}}\}$ , by

$$S = \{s_0, s_1, s_2, s_3, s_4\},\$$

$$R = \{ \langle s_0, s_1 \rangle, \langle s_1, s_2 \rangle, \langle s_1, s_3 \rangle, \langle s_2, s_4 \rangle, \langle s_3, s_3 \rangle, \langle s_4, s_4 \rangle \},$$

and  $\Pi$  to be  $\Pi(s_0) = \{P_{int1}\}, \Pi(s_1) = \emptyset, \Pi(s_2) = \{P_{int2}\}, \Pi(s_3) = \{P_1, P_2\}, \text{ and } \Pi(s_4) = \{P_2\}.$  The labellings in Fig. 4 show that  $\mathcal{M}, s_0 \models \neg \forall [(\exists FP_1) \cup P_2].$

Now if we take restriction of  $\mathcal{M}$  for language  $\mathcal{L}'$  with the set of propositions  $\mathcal{P}' = \{P_1, P_2\}$ , then we get  $\mathcal{M}' = (S', R', \Pi')$  where

$$S' = \{ \vec{H}_0, \vec{H}_1, \vec{H}_2 \}, \qquad R' = \{ \langle H_0, H_1 \rangle, \langle H_0, H_2 \rangle, \langle H_1, H_1 \rangle, \langle H_2, H_2 \rangle \},$$

and  $\Pi'$  to be  $\Pi'(\bar{H}_0) = \emptyset$ ,  $\Pi'(\bar{H}_1) = \{P_2\}$  and  $\Pi'(\bar{H}_2) = \{P_1, P_2\}$ . Now the labellings in Fig. 4 show that  $\mathcal{M}'$ ,  $\bar{H}_0 \models \forall ((\exists FP_1) \cup P_2)$ .  $\square$

However, there exists a large subclass of CTL formulae with the desirable property that if a formula in this subclass is satisfiable in the unrestricted CTL structure,  $\mathcal{M}$ , then it is satisfiable in the CTL structure,  $\mathcal{M}'$ , obtained by restriction. We call this subclass CTL<sup>-</sup>.

Given a set of atomic propositions  $\mathcal{P}$ :

- (1) Every atomic proposition  $P \in \mathcal{P}$  is a propositional formula in CTL<sup>-</sup>.

- (2) If  $f_1$  and  $f_2$  are propositional formula in CTL, then so are  $\neg f_1, f_1 \land f_2$ .

- (3) If  $f_1$  is a propositional formula and  $f_2$  is a CTL<sup>-</sup> formula, then  $\forall (f_1 \cup f_2)$  and  $\exists (f_1 \cup f_2)$  are CTL<sup>-</sup> formulae.

**Theorem 4.2.** Let  $\mathcal{F}$  be a CTL<sup>-</sup> formula in  $\mathcal{L}'$ . Then

$$\mathcal{M}, s_0 \models \mathcal{F} \text{ iff } \mathcal{M}', \bar{H}_0 \models \mathcal{F} \text{ where } s_0 \in \text{dom}(H_0).$$

Fig. 4. Counterexample for Theorem 4.1.

Before we give the proof of the Theorem 4.2, we need the following technical lemmas.

**Lemma 4.3.** If  $\mathcal{M}' = (S', R', \Pi')$ , is a restriction of  $\mathcal{M} = (S, R, \Pi)$ , with respect to  $\mathcal{P}'$ , then

- (i) For all  $\bar{H}_i$ ,  $\bar{H}_j \in S'$ ,  $(i \neq j)$ ,  $(\bar{H}_i, \bar{H}_j) \in R'$  iff there exists a path from  $s'_i$  to  $s'_j$   $(s'_i \in \text{dom}(H_i), s'_j \in H_j)$  such that  $(s'_i = s_k, \ldots, s_l, s_{l+1}, \ldots, s_m = s'_j)$  in  $\mathcal{M}$  and for some  $k < l < m, s_k, \ldots, s_l \in H_i, s_{l+1} \notin H_i$  and  $s_{l+1}, \ldots, s_m \in H_j$ .

- (ii) For all  $\bar{H}_i \in S'$ ,  $\langle \bar{H}_i, \bar{H}_i \rangle \in R'$  iff there is a cycle in the block  $H_i$ .

- (iii) For all s such that  $s \in H$ ,  $\Pi'(\bar{H}) = \Pi(s) \cap \mathcal{P}'$ .

**Proof Sketch.** (i) ( $\Leftarrow$ ) Suppose there is a path, then  $s_l \in H_i$ ,  $s_{l+1} \in H_j$  and  $s_{l+1} \notin H_i$  and  $(s_l, s_{l+1}) \in R$ . Hence by definition,  $(\bar{H}_i, \bar{H}_j) \in R'$ .

- ( $\Rightarrow$ ) Suppose  $\langle \bar{H}_i, \bar{H}_j \rangle \in R'$  then there exist  $s_l \in H_i$ ,  $s_{l+1} \in H_j$  such that  $s_{l+1} \notin H_i$  and  $\langle s_l, s_{l+1} \rangle \in R$ . Then we claim that  $s_{l+1} \in \text{dom}(H_j)$ . (Assume the contrary. Let  $s_t \in H_j$  dominate  $s_{l+1}$ . Then  $s_t \, \mathcal{E} \, s_{l+1}$ . Hence, for each predecessor of  $s_{l+1}, s'_{l+1}, \Pi_{\mathscr{P}'}(s'_{l+1}) = \Pi_{\mathscr{P}'}(s_{l+1})$ . Hence,  $s_l \, \mathcal{E} \, s_{l+1}$  and  $s_{l+1} \in \mathcal{E}^*(s_l)$ .  $s_{l+1} \in H_i$ . A contradiction.) Now given  $s'_i \in \text{dom}(H_i)$  and  $s'_j \in H_j$  we can find a path by concatenating the path from  $s'_i$  to  $s_l$  and  $s_{l+1}$  to  $s'_j$ . Such paths exist since  $s'_i \in \text{dom}(H_i)$  and  $s_{l+1} \in \text{dom}(H_j)$ .

- (ii) ( $\Rightarrow$ ) Suppose  $\langle \bar{H}_i, \bar{H}_i \rangle \in R'$ . Then for some  $s_i, s_j \in H_i, s_j \mathcal{E} s_i$  and hence there is a path from  $s_i$  to  $s_i$ . Moreover  $\langle s_i, s_i \rangle \in R$ . Hence, there is a cycle in  $H_i$ .

- ( $\Leftarrow$ ) Suppose  $(s_j, s_{j+1}, \ldots, s_i, s_j)$  is a cycle in  $H_i$ . Then there are two cases to consider. In the first case, the cycle contains a state in  $dom(H_i)$ . Let  $s_j$  be such a state. Then  $s_j \,\mathscr{E} \, s_i$ . On the other hand, if the cycle does not contain a dominating state, since there is a path from  $s_j$  to  $s_i$  and all the states on the path are nondominating states of  $H_i$ ,  $s_j \,\mathscr{E} \, s_i$ . Moreover, since  $s_i$ ,  $s_j$  appear consecutively in the cycle,  $\langle s_i, s_j \rangle \in R$ . Hence by definition,  $\langle \bar{H}_i, \bar{H}_i \rangle \in R'$ .

- (iii) Follows directly from the definitions of  $\Pi'_{\mathscr{P}}$  and  $\Pi'$ .  $\square$

We extend the operation of restriction to a path in a CTL structure. Let  $p = (s_0, \ldots, s_n, s_{n+1}, \ldots)$  be a path in  $\mathcal{M}$ . Then define

$$\mathcal{R}_{\mathscr{P}}(p) = \begin{cases} \bar{H}_0 \mathcal{R}_{\mathscr{P}}(s_{n+1}, \dots) & \text{if } (s_0, \dots, s_n) \text{ is a finite prefix of } p \text{ such that} \\ s_0, \dots, s_n \in H_0 \text{ and } s_{n+1} \notin H_0; \\ \bar{H}_0, \bar{H}_0, \dots & \text{otherwise, and } s_0, \dots, \in H_0. \end{cases}$$

**Lemma 4.4.** Let  $(s_0, \ldots, s_n, s_{n+1}, \ldots)$  be a path in  $\mathcal{M}$ . Then  $\mathcal{R}_{\mathscr{P}'}(s_0, \ldots, s_n, s_{n+1}, \ldots)$  is a path in  $\mathcal{M}'$ .

**Proof.** The proof follows from the definition and Lemma 4.3(i) and (ii).  $\Box$

The exact converse of Lemma 4.4 is not true. But for our purpose, a somewhat weaker version of the converse will suffice.

**Lemma 4.5.** Let  $(\bar{H}_0, \bar{H}_1, ...)$  be a path in  $\mathcal{M}'$  such that it satisfies one of the following two conditions:

- (1)  $\bar{H}_i \neq \bar{H}_{i+1}$  for all  $0 \leq i$ ,

- (2)  $\bar{H}_i \neq \bar{H}_{i+1}$  for all  $0 \leq i < k$  and  $\bar{H}_j = \bar{H}_{j+1}$  for all  $k \leq j$ .

Let  $s_0 \in \text{dom}(H_0)$ . Then there is a path  $(s_0, s_1, \ldots)$  in  $\mathcal{M}$  and  $\mathcal{R}_{\mathscr{P}}(s_0, s_1, \ldots) = (\bar{H}_0, \bar{H}_1, \ldots)$ .

**Proof.** The proof follows from the definition and Lemma 4.3(i) and (ii).  $\Box$

**Lemma 4.6.** Let  $\mathcal{F}$  be a CTL<sup>-</sup> formula in  $\mathcal{L}'$ . Then

$$\mathcal{M}', \bar{H}_i \models \mathcal{F} \implies \mathcal{M}, s_i \models \mathcal{F} \quad \text{where } s_i \in \text{dom}(H_i).$$

**Proof.** The proof follows by induction on the structure the CTL<sup>-</sup> formula  $\mathscr{F}$ . Basis Step:  $\mathscr{F}$  is an atomic proposition P in  $\mathscr{P}'$ . Then

$$\mathcal{M}', \bar{H}_i \vDash \mathcal{F} \Rightarrow \mathcal{M}', \bar{H}_i \vDash P$$

$$\Rightarrow P \in \Pi'(\bar{H}_i)$$

$$\Rightarrow P \in \Pi(s_i) \cap \mathcal{P}' \quad \text{(Lemma 4.3(iii))}$$

$$\Rightarrow P \in \Pi(s_i)$$

$$\Rightarrow \mathcal{M}, s_i \vDash P$$

$$\Rightarrow \mathcal{M}, s_i \vDash \mathcal{F}.$$

Induction Step: We only show the cases for  $\forall U$  and  $\exists U$ . Other cases, involving propositional connectives, are rather simple and hence omitted.

Let  $\mathcal{F} = \forall [f_1 \cup f_2]$ . First we show that if for all paths  $(\bar{H}_i, \bar{H}_{i+1}, \ldots)$  of  $\mathcal{M}'$ ,

$$\exists k \ge i(\mathcal{M}', \bar{H}_k \models f_2 \land \forall i \le l < k(\mathcal{M}', \bar{H}_l \models f_1)),$$

then, for all paths  $(s_i, s_{i+1}, \ldots)$  of  $\mathcal{M}$ ,

$$\exists p \ge i(\mathcal{M}, s_p \models f_2 \land \forall i \le q < p(\mathcal{M}, s_a \models f_1)).$$

Let  $l = (s_i, s_{i+1}, \ldots)$  be any path in  $\mathcal{M}$  with  $s_i \in \text{dom}(H_i)$  and  $\mathcal{R}_{\mathscr{P}}(l) = l' = (\bar{H}_i, \bar{H}_{i+1}, \ldots)$  be the corresponding path in  $\mathcal{M}'$ . By above,  $\exists k \ge i \cdot \mathcal{M}', \bar{H}_k \models f_2$ . Let  $p \ge i$  be the smallest index such that  $s_p \in H_k$ . Hence  $s_p \in \text{dom}(H_k)$ . By the induction hypothesis,  $\mathcal{M}, s_p \models f_2$ . Since  $\forall i \le q , and <math>\forall i \le l < k(\mathcal{M}', \bar{H}_l \models f_1)$ , and  $f_1$  is a propositional formula, we have  $\forall i \le q < p(\mathcal{M}, s_q \models f_1)$ . Hence using the semantics of the U operator, we get

$$\mathcal{M}', \bar{H}_i \vDash \mathcal{F} \Rightarrow \mathcal{M}', \bar{H}_i \vDash \forall (f_1 \cup f_2)$$

$$\Rightarrow \text{ for all paths } (\bar{H}_i, \bar{H}_{i+1}, \dots) \text{ of } \mathcal{M}',$$

$$\exists k \ge i(\mathcal{M}', \bar{H}_k \vDash f_2 \land \forall i \le l < k(\mathcal{M}', \bar{H}_i \vDash f_1))$$

$$\Rightarrow \text{ for all paths } (s_i, s_{i+1}, \dots) \text{ of } \mathcal{M}, \qquad (s_i \in \text{dom}(H_i))$$

$$\exists p \ge i(\mathcal{M}, s_p \vDash f_2 \land \forall i \le q < p(\mathcal{M}, s_q \vDash f_1))$$

$$\Rightarrow \mathcal{M}, s_i \vDash \forall (f_1 \cup f_2)$$

$$\Rightarrow \mathcal{M}, s_i \vDash \mathcal{F}.$$

Let  $\mathcal{F} = \exists (f_1 \cup f_2)$ . First we claim that if for some path  $(\bar{H}'_i, \bar{H}'_{i+1}, \ldots)$  of  $\mathcal{M}'_i$ ,

$$\exists m \ge i(\mathcal{M}', \bar{H}'_m \models f_2 \land \forall i \le l < m(\mathcal{M}', \bar{H}'_l \models f_1)),$$

then there is some path  $(\bar{H}_i, \bar{H}_{i+1}, ...)$  of  $\mathcal{M}'$  satisfying one of the conditions of Lemma 4.5 such that

$$\exists k \ge i(\mathcal{M}', \bar{H}_k \models f_2 \land \forall i \le l < k(\mathcal{M}', \bar{H}_l \models f_1)).$$

The new path  $(\bar{H}_i, \bar{H}_{i+1}, \ldots)$  is obtained by the following step: if  $(\bar{H}'_j, \bar{H}'_{j+1}, \ldots, \bar{H}'_{j+n})$  is a maximal finite subpath of  $(\bar{H}'_i, \bar{H}'_{i+1}, \ldots)$  such that  $\bar{H}'_j = \bar{H}'_{j+1} = \cdots = \bar{H}'_{j+n}$ , then the subpath is replaced by a single state  $\bar{H}'_j$ . This operation is done for all such subpaths. It is easy to convince onself that the path obtained by this operation is a path in  $\mathcal{M}'$  and satisfies the claim.

Next, we show that if for some paths  $(\bar{H}_i, \bar{H}_{i+1}, ...)$  of  $\mathcal{M}'$  satisfying one of the conditions of the Lemma 4.5,

$$\exists k \ge i(\mathcal{M}', \bar{H}_k \models f_2 \land \forall i \le l < k(\mathcal{M}', \bar{H}_l \models f_1)),$$

then, for some paths  $(s_i, s_{i+1}, \ldots)$  of  $\mathcal{M}$ ,

$$\exists p \ge i(\mathcal{M}, s_n \models f_2 \land \forall i \le q < p(\mathcal{M}, s_a \models f_1)).$$

By Lemma 4.5 there is a path  $l = (s_i, s_{i+1}, \ldots)$  in  $\mathcal{M}$  with  $s_i \in \text{dom}(H_i)$  and  $\mathcal{R}_{\mathscr{P}'}(l) = l' = (\bar{H}_i, \bar{H}_{i+1}, \ldots)$ , the path in  $\mathcal{M}'$ . By the above,  $\exists k \geq i(\mathcal{M}', \bar{H}_k \models f_2)$ . Let  $p \geq i$  be the smallest index such that  $s_p \in H_k$ . Hence  $s_p \in \text{dom}(H_k)$ . By the induction hypothesis,  $\mathcal{M}, s_p \models f_2$ . Since  $\forall i \leq q , and <math>\forall i \leq l < k(\mathcal{M}', \bar{H}_l \models f_1)$  and  $f_1$  is a propositional formula, we have  $\forall i \leq q < p(\mathcal{M}, s_q \models f_1)$ . Hence using the semantics of the U operator, we get

$$\mathcal{M}', \bar{H}_i \models \mathcal{F} \Rightarrow \mathcal{M}', \bar{H}_i \models \exists (f_1 \cup f_2)$$

$$\Rightarrow \text{ for some path } (\bar{H}'_i, \bar{H}'_{i+1}, \ldots) \text{ of } \mathcal{M}',$$

$$\exists m \geqslant i(\mathcal{M}', \bar{H}'_m \models f_2 \land \forall i \leqslant l < m(\mathcal{M}', \bar{H}'_i \models f_1))$$

$$\Rightarrow \text{ for some path } (\bar{H}_i, \bar{H}_{i+1}, \ldots) \text{ of } \mathcal{M}', \text{ satisfying one of the conditions of Lemma 4.5,}$$

$$\exists k \geqslant i(\mathcal{M}', \bar{H}_k \models f_2 \land \forall i \leqslant l < k(\mathcal{M}', \bar{H}_l \models f_1))$$

$$\Rightarrow \text{ for some path } (s_i, s_{i+1}, \ldots) \text{ of } \mathcal{M}, \qquad (s_i \in \text{dom}(H_i))$$

$$\exists p \geqslant i(\mathcal{M}, s_p \models f_2 \land \forall i \leqslant q < p(\mathcal{M}, s_q \models f_1))$$

$$\Rightarrow \mathcal{M}, s_i \models \exists (f_1 \cup f_2)$$

$$\Rightarrow \mathcal{M}, s_i \models \mathcal{F}. \qquad \Box$$

In the next lemma we will make use of following simple facts about a CTL formulae and blocks  $H_k$ , which we state without proof.

Fact 4.7. If a state of  $H_k$  satisfies a propositional formula g, then all the states of  $H_k$  must satisfy g.

Fact 4.8. Any quantified CTL<sup>-</sup> formula f can be written in an expanded form

$$\mathbf{Q}_1(g_1 \cup \mathbf{Q}_2(g_2 \cup \cdots \cup \mathbf{Q}_n(g_n \cup g_{n+1}) \cdots)),$$

where  $Q_1, Q_2, \ldots, Q_n$  are path quantifiers  $\forall$  or  $\exists$ , and  $g_1, g_2, \ldots, g_{n+1}$  are propositional formulae.

Fact 4.9. If  $g_{n+1}$  holds in any state, so do the formulae

$$\mathbf{Q}_{j}(g_{j} \mathbf{U} \mathbf{Q}_{j+1}(g_{j+1} \mathbf{U} \cdots \mathbf{Q}_{n}(g_{n} \mathbf{U} g_{n+1}) \cdots))$$

for all  $1 \leq j \leq n$ .

Similarly, if  $\mathbf{Q}_i(g_i \mathbf{U} \mathbf{Q}_{i+1}(g_{i+1} \mathbf{U} \cdots \mathbf{Q}_n(g_n \mathbf{U} g_{n+1}) \cdots))$  holds in any state so do the formulae

$$\mathbf{Q}_i(g_i \cup \mathbf{Q}_{i+1}(g_{i+1} \cup \cdots \cup \mathbf{Q}_n(g_n \cup g_{n+1}) \cdots))$$

for all  $1 \le j \le i$ .

Conversely, if  $\mathbf{Q}_1(g_1 \mathbf{U} \mathbf{Q}_2(g_2 \mathbf{U} \cdots \mathbf{Q}_n(g_n \mathbf{U} g_{n+1}) \cdots))$  holds in some state, then, for some  $1 \le j \le n$ ,  $g_j$  and  $\mathbf{Q}_j(g_j \mathbf{U} \mathbf{Q}_{j+1}(g_{j+1} \mathbf{U} \cdots \mathbf{Q}_n(g_n \mathbf{U} g_{n+1}) \cdots))$  hold in that state or  $g_{n+1}$  holds in that state.

**Lemma 4.10.** Let  $\mathcal{F}$  be a CTL<sup>-</sup> formula in  $\mathcal{L}'$ . Then

$$\mathcal{M}, s_i \models \mathcal{F} \Rightarrow \mathcal{M}', \bar{H}_i \models \mathcal{F} \text{ where } s_i \in \text{dom}(H_i).$$

**Proof.** We prove this by a complete induction over a labelled computation tree, rooted at  $s_i$  and with branches corresponding to transitions in  $\mathcal{M}$ . The labelling of the states of the computation tree is done with respect to the CTL<sup>-</sup> formula  $\mathcal{F}$ . Since  $\mathcal{F}$  is in CTL<sup>-</sup>, it is of the form g, or

$$\mathbf{Q}_1(g_1 \mathbf{U} \mathbf{Q}_2(g_2 \mathbf{U} \cdots \mathbf{Q}_n(g_n \mathbf{U} g_{n+1}) \cdots)),$$

where g's are propositional formulae. We label the tree as follows: if  $\mathcal{F} = g$ , then label  $s_i$  with g and halt. On the other hand, if

$$\mathscr{F} = \mathbf{Q}_1(g_1 \mathbf{U} \mathbf{Q}_2(g_2 \mathbf{U} \cdots \mathbf{Q}_n(g_n \mathbf{U} g_{n+1}) \cdots)),$$

then depending on whether  $Q_1$  is  $\forall$  (3), for all (some) computation paths starting from  $s_i$ , there exists a finite initial prefix of the path, such that

$$\mathbf{Q}_2(g_2 \mathbf{U} \mathbf{Q}_3(g_3 \mathbf{U} \cdots \mathbf{Q}_n(g_n \mathbf{U} g_{n+1}) \cdots))$$

holds at the last state of the prefix and  $g_1$  at all other states along the prefix. Label the states corresponding to the prefix with  $g_1$ . Continue the labelling procedure for all the last states of the prefix, in a similar fashion, until a state is labelled with  $g_{n+1}$ , and halt. Without loss of generality, assume that  $\mathcal{M}$ ,  $s_i \models g_1$ . Notice that if s' is any state, labelled with  $g_j$  by this process, then,  $\mathcal{M}$ ,  $s' \models g_j$  and

$$\mathcal{M}, s' \models \mathbf{Q}_i(g_i \cup \mathbf{Q}_{i+1}(g_{i+1} \cup \cdots \cup \mathbf{Q}_n(g_n \cup g_{n+1}) \cdots)).$$

Let l(s') stand for the length of the longest prefix of a computation path starting from s' such that every state of the prefix has the same label as s'. We say c(s') = j

is the characteristic index and l(s') the characteristic length of  $s_j$  with respect to the formula  $\mathcal{F}$ .

If  $T_j$  and  $T_k$  are two computation trees rooted at the dominating states  $s_j$  and  $s_k$ , respectively, then we say  $T_j < T_k$ , if  $c(s_j) > c(s_k)$ , or if  $c(s_j) = c(s_k)$  but  $l(s_j) < l(s_k)$ . This defines a well-ordering among the trees.

Consider an initial finite portion of the tree with the root at  $s_i$ , with branches corresponding to the transitions in block  $H_i$  and leaves corresponding to the dominating states of the blocks.

Case 1: Either the formula  $\mathcal{F}$  is of the form g or  $\mathcal{F}$  is of the form

$$\mathbf{Q}_1(g_1 \cup \mathbf{Q}_2(g_2 \cup \cdots \cup \mathbf{Q}_n(g_n \cup g_{n+1}) \cdots))$$

and some non-leaf state of the initial portion of the computation tree satisfies  $g_{n+1}$ . In the first case, since  $\mathcal{M}$ ,  $s_i \models g$  and g is a propositional formula, it is easy to show that  $\mathcal{M}'$ ,  $\bar{H}_i \models g$ . In the second case, by Fact 4.7  $\mathcal{M}$ ,  $s_i \models g_{n+1}$ , and as in the first case,  $\mathcal{M}'$ ,  $\bar{H}_i \models g_{n+1}$ . By Fact 4.9

$$\mathcal{M}', \bar{H}_i \models \mathbf{O}_1(g_1 \cup \mathbf{O}_2(g_2 \cup \cdots \cup \mathbf{O}_n(g_n \cup g_{n+1}) \cdots)).$$

Hence  $\mathcal{M}', \bar{H}_i \vDash \mathcal{F}$ .

Case 2: Formula  $\mathcal{F}$  is of the form

$$\mathbf{Q}_1(g_1 \mathbf{U} \mathbf{Q}_2(g_2 \mathbf{U} \cdots \mathbf{Q}_n(g_n \mathbf{U} g_{n+1}) \cdots))$$

and  $g_{n+1}$  does not hold in any non-leaf state. Let k be the maximum over the characteristic indices of the leaves. Then there are two cases to consider:

Subcase A:  $Q_1, Q_2, \dots Q_{k-1}$  are all  $\forall$  quantifiers.

In this case all the leaves must satisfy

$$\mathbf{Q}_{j}(g_{j} \mathbf{U} \mathbf{Q}_{j+1}(g_{j+1} \mathbf{U} \cdots \mathbf{Q}_{n}(g_{n} \mathbf{U} g_{n+1}) \cdots))$$

for some  $1 \leq j \leq k$ .

By induction on computation tree, we have for the corresponding blocks H,

$$\mathcal{M}', \bar{H} \models \mathbf{Q}_i(g_i \cup \mathbf{Q}_{i+1}(g_{i+1} \cup \cdots \cup \mathbf{Q}_n(g_n \cup g_{n+1}) \cdots)).$$

By Fact 4.9

$$\mathcal{M}', \bar{H} \models \mathbf{Q}_1(g_1 \mathbf{U} \mathbf{Q}_2(g_2 \mathbf{U} \cdots \mathbf{Q}_n(g_n \mathbf{U} g_{n+1}) \cdots)).$$

But in the restricted structure  $\mathcal{M}'$ , each of these  $\bar{H}$  is a successor of  $\bar{H}_i$  (by Lemma 4.3(i)). Hence

$$\mathcal{M}', \bar{H}_i \models \mathbf{Q}_1(g_1 \cup \mathbf{Q}_2(g_2 \cup \cdots \cup \mathbf{Q}_n(g_n \cup g_{n+1}) \cdots)).$$

Hence  $\mathcal{M}', \bar{H}_i \vDash \mathcal{F}$ .

Subcase B:  $Q_1, Q_2, \ldots, Q_{k-1}$  are not all  $\forall$  quantifiers. Assume  $Q_{i_1}, Q_{i_2}, \ldots, Q_{i_p}$   $(1 \le i_1 \le i_2 \le \cdots \le i_p \le k-1)$  are  $\exists$  quantifiers.

We consider stages of labelling of the initial portion of the computation tree. By assumption  $Q_1, \ldots, Q_{i_1-1}$  are all  $\forall$  quantifiers. In the first stage consider the labellings associated with  $Q_1, \ldots, Q_{i_1-1}$ . Now all the last states of the prefixes of all the

computation paths (starting from  $s_i$ ) that are labelled in this state, must satisfy

$$\mathbf{Q}_{i_1}(\mathbf{g}_{i_1} \mathbf{U} \mathbf{Q}_{i_1+1}(\mathbf{g}_{i_1+1} \mathbf{U} \cdots \mathbf{Q}_n(\mathbf{g}_n \mathbf{U} \mathbf{g}_{n+1}) \cdots)).$$

At this point we stop if there is a state among these that satisfies  $g_{i_1}$  and

$$Q_{i_1}(g_{i_1} \cup Q_{i_1+1}(g_{i_1+1} \cup \cdots \cup Q_n(g_n \cup g_{n+1}) \cdots)).$$

If not, we consider the next stage of labellings associated with  $\mathbf{Q}_{i_1+1}, \dots \mathbf{Q}_{i_2-1}$ . Continuing in this fashion, we may encounter one of the two situations: (i) either we have found a state that satisfies

$$g_{i_j}$$

and  $\mathbf{Q}_{ij}(g_{i_j}\mathbf{U}\mathbf{Q}_{i_j+1}(g_{i_j+1}\mathbf{U}\cdots\mathbf{Q}_n(g_n\mathbf{U}g_{n+1})\cdots))$  for some  $i_j \in \{i_1,\ldots,i_p\}$ ,

(ii) or all the leaves must satisfy

$$\mathbf{Q}_i(g_i \mathbf{U} \mathbf{Q}_{i+1}(g_{i+1} \mathbf{U} \cdots \mathbf{Q}_n(g_n \mathbf{U} g_{n+1}) \cdots))$$

for some  $1 \le j \le k$ .

The second situation is handled in a manner similar to Subcase A. Hence we consider the first situation only.

Let s be the non-leaf state satisfying  $g_{i_i}$  and

$$\mathbf{Q}_{i_i}(g_{i_i} \mathbf{U} \mathbf{Q}_{i_i+1}(g_{i_i+1} \mathbf{U} \cdots \mathbf{Q}_n(g_n \mathbf{U} g_{n+1}) \cdots)).$$

Then there is a computation path from the root passing through the non-leaf s and a leaf  $s_m$ , where  $s_m \in \text{dom}(H_m)$  and  $s_m$  satisfies

$$\mathbf{Q}_m(g_m \mathbf{U} \mathbf{Q}_{m+1}(g_{m+1} \mathbf{U} \cdots \mathbf{Q}_n(g_n \mathbf{U} g_{n+1}) \cdots)), \quad (i_i < m < k).$$

Since s is a non-leaf state and  $g_{i_j}$  is a propositional formula,  $\mathcal{M}$ ,  $s_i \models g_{i_j}$  (Fact 4.7) and  $\mathcal{M}'$ ,  $\bar{H}_i \models g_{i_j}$ .

But

$$\mathcal{M}, s_m \models \mathbf{Q}_m(g_m \mathbf{U} \mathbf{Q}_{m+1}(g_{m+1} \mathbf{U} \cdots \mathbf{Q}_n(g_n \mathbf{U} g_{n+1}) \cdots)).$$

Hence by Fact 4.9

$$\mathcal{M}, s_m \models \mathbf{Q}_{i_i}(g_{i_i} \mathbf{U} \mathbf{Q}_{i_i+1}(g_{i_i+1} \mathbf{U} \cdots \mathbf{Q}_n(g_n \mathbf{U} g_{n+1}) \cdots)),$$

and by the induction on the computation tree

$$\mathcal{M}, \overline{H}_m \models \mathbf{Q}_{i_j}(\mathbf{g}_{i_j} \mathbf{U} \mathbf{Q}_{i_j+1}(\mathbf{g}_{i_j+1} \mathbf{U} \cdots \mathbf{Q}_n(\mathbf{g}_n \mathbf{U} \mathbf{g}_{n+1}) \cdots)).$$

But in the restricted structure  $\mathcal{M}'$ ,  $\bar{H}_m$  is a successor of  $\bar{H}_i$  (Lemma 4.3(i)) and hence

$$\mathcal{M}', \bar{H}_i \models \mathbf{Q}_{i_j}(\mathbf{g}_{i_j} \mathbf{U} \mathbf{Q}_{i_{j+1}}(\mathbf{g}_{i_{j+1}} \mathbf{U} \cdots \mathbf{Q}_n(\mathbf{g}_n \mathbf{U} \mathbf{g}_{n+1}) \cdots)).$$

By Fact 4.9

$$\mathcal{M}', \bar{H}_i \models \mathbf{Q}_1(g_1 \mathbf{U} \mathbf{Q}_2(g_2 \mathbf{U} \cdots \mathbf{Q}_n(g_n \mathbf{U} g_{n+1}) \cdots)).$$

Hence  $\mathcal{M}', \bar{H}_i \vDash \mathcal{F}$ .  $\square$

From the above technical lemmas, we easily deduce the proof of the Main Theorem (Theorem 4.2).

**Proof of Theorem 4.2.** The proof directly follows from Lemmas 4.6 and 4.10.  $\Box$

Now, we show how to build  $\mathcal{M}'$  from  $\mathcal{M}$  in the following three steps.  $\mathcal{M}'$  is essentially a restriction of  $\mathcal{M}$  with additional optimizations and labelling of the transitions of the state-transition graph.

- Step 1. Relabel the vertices and the edges of the CTL structure  $\mathcal{M}$ . (a) Label each state by the subset of the propositions involving only the inputs and the outputs of the module. (b) Label the edges between two states with the same set of atomic propositions, by  $\varepsilon$ .

- Step 2. Construct the blocks of  $\mathcal{M}$ , by first determining the dominant states using a depth first search over the underlying graph. Build  $\mathcal{M}'$  by replacing each block by a single state.

- Step 3. Label the edges of the graph by the set of input signals that causes the transition and the set of output signals associated with the transition.

This construction is illustrated by taking the restriction of the state-transition graph for the FIFO queue element shown in Fig. 1. The states shown in groups are the blocks constructed in Step 2. The resulting labelled state-transition graph is shown in Fig. 5.

Fig. 5. The restricted state transition graph.

It should be mentioned that since we combine successive states in the operation of Step 2, the restricted model may not be a unit-delay model even if the original unrestricted model was so. This notion is essentially captured in Theorems 4.1 and 4.2.

However, this does not pose a problem, since good design methodology forces the designer not to make the modules at higher level in the hierarchy speed-dependent. Moreover, since a speed-dependent circuits must be small enough to fit in an equipotential region and equipotential regions must be small enough that the potential on any wire in this area will equalize in a 'short' time for any large circuit, the modules at higher level have to be speed-independent [7].

As the first step for verifying the correctness of a circuit using a hierarchical approach, we construct a CTL structure for a module at some hierarchical level, using the CTL structures for the submodules at the immediately lower level. In order to avoid building large-sized CTL structures, we use the restriction operation on the CTL structures of the submodules and obtain smaller descriptions of these. Moreover, the transitions of the state-transition graph are additionally labelled with the associated set of input signals and set of output signals, as explained earlier in this section.

Given two submodules A and B which are used to build a module C at a higher level by connecting the inputs and outputs of A and B, we show how to build a CTL structure for the module C using an operation called 'composition'. It can be shown that the composition operation is commutative and associative and hence can be generalized easily to the case where a module consists of more than two submodules. The reader may note a close analogy between the operations we define and the operations defined in [8].

Let the restricted models of the submodules A and B be  $\mathcal{M}_A = (S_A, R_A, \Pi_A)$  and  $\mathcal{M}_B = (S_B, R_B, \Pi_B)$ , respectively. We assume that the propositions associated with A and B are renamed so that the input and output nodes of A and B that are connected have a corresponding pair of propositions, i.e., if input a of A is derived from the output b of B, then the proposition associated with a is  $P_b'$  corresponding to the proposition  $P_b$  associated with B in B. Furthermore, we make the important assumption that these connections are made using 'short' bilateral wires.

The CTL structure of  $C = A \circ B$  is given by  $\mathcal{M}_C = \mathcal{M}_{A \circ B} = (S_{A \circ B}, R_{A \circ B}, \Pi_{A \circ B})$ , where  $S_{A \circ B} \subseteq S_A \times S_B$ . The assignment function  $\Pi_{A \circ B} \colon S_{A \circ B} \mapsto 2^{\mathcal{P}_A \cup \mathcal{P}_B}$  is defined by  $\Pi(s_{A \circ B}) = \Pi(s_A) \cup \Pi(s_B)$  where the state  $s_{A \circ B} = \langle s_A, s_B \rangle$ . The initial state of  $\mathcal{M}_C$  is  $s_{0(A \circ B)} = \langle s_{0A}, s_{0B} \rangle$ . A state is *stable* if every pair of propositions assigned to the state has the same truth value and is *unstable* otherwise, with a set of transitions  $\theta$  corresponding to the unmatched pair associated with it.

The transition relation  $R_{A\circ B}$  ( $R_{A\circ B}\subseteq S_{A\circ B}\times S_{A\circ B}$ ) is defined as follows. Assume that there is a transition  $\langle s_{1A}, s_{2A}\rangle \in R_A$  such that  $\langle s_{1A}, s_{2A}\rangle$  has associated with it, the input set  $\alpha$  and the output set  $\beta$ . Similarly, assume that there is a transition  $\langle s_{1B}, s_{2B}\rangle \in R_B$  such that  $\langle s_{1B}, s_{2B}\rangle$  has associated with it the input set  $\gamma$  and the output set  $\delta$ . Furthermore, assume that  $\alpha$  is partitioned into disjoint subsets  $\alpha'$  and  $\alpha''$  such that  $\alpha'$  is associated with the inputs of C (i.e. the input transitions for  $\alpha''$  are generated externally and the transitions for  $\alpha''$  are generated internally). Similarly, assume that  $\gamma$  is partitioned into disjoint subsets  $\gamma'$  and  $\gamma''$ . Then in the CTL structure for C, there will be following transitions: Let  $\theta$  be the set of transitions associated with  $\langle s_{1A}, s_{1B}\rangle$ , if it is unstable. (i) If  $\alpha'' \subseteq \theta$ , then there is a transition  $\langle \langle s_{1A}, s_{1B}\rangle, \langle s_{2A}, s_{1B}\rangle \rangle \in R_{A\circ B}$  with associated input  $\gamma'$  and output  $\gamma'$  and

The step of constructing the successor states for  $\langle s_{1A}, s_{1B} \rangle$  can be thought of as simulating C at  $\langle s_{1A}, s_{1B} \rangle$  for all possible sets of inputs and can be easily incorporated into Algorithm 2.1. Now various properties of C with respect to the model  $\mathcal{M}_C$  can be determined using the model checker algorithm, as explained in the earlier sections.

#### 5. Conclusion

We have shown that it is possible to do automatic verification of asynchronous circuits efficiently. We have also indicated how this method can be extended to do hierarchical verification of large and complex circuits. We believe that this approach may eventually turn out to be quite practical.

However, there are many problems that need to be addressed before this approach is made feasible in practice. In this paper we have used a unit-delay model for the circuit. Similarly, it is quite easy to use a steady-state model, in which each state in the state-transition graph corresponds to a stable state and only in response to an input change does a state change occur. While the steady-state model is useful for speed-independent self-timed circuits, the unit-delay model is needed to model properties of a speed-dependent circuit. Unfortunately, even for the speed-dependent circuits the assumption that each gate has one unit gate-delay is rather unrealistic, because two similar gates may have different delays depending on process variations, fan-outs of a gate, etc. Moreover, because of various capacitive effects, the delay associated with a 0-to-1 transition is not equal to the one associated with a 1-to-0 transition. It is felt that it is necessary to find models that capture these properties better. Also, we do not know how to handle the effect of large fan-out, charge sharing, etc. In addition, we felt that CTL is rather weak for succinctly expressing many properties of circuits. A notation based on temporal intervals [6] may be more suitable for this purpose.

An interesting area for future research is the usefulness of restriction operation in the context of hierarchical verification. We have defined a 'restriction' operation and shown that the truth-properties of the CTL<sup>-</sup> formulae are preserved with respect to the operation of restriction. It appears that any weaker version of 'restriction' will not result in any substantial reduction of the size of the CTL structures and hence will make hierarchical verification rather expensive. On the other hand, it seems any stronger version of 'restriction', will severely limit the class of CTL formulae that will be preserved with respect to restriction.

## Acknowledgment

We wish to thank Larry Rudolph of Carnegie-Mellon University, and Chuck Seitz of Caltech for helpful discussions.

## References

- [1] M. Ben-Ari, Z. Manna and A. Pnueli, The logic of nexttime, 8th ACM Symposium on Principle of Programming Languages, Williamsburg, VA, 1981.

- [2] G.V. Bochmann, Hardware specification with temporal logic: An example, *IEEE Trans. Comput.* C-31 (3) (1982).

- [3] E.M. Clarke, E.A. Emerson and A.P. Sistla, Automatic verification of finite-state concurrent systems using temporal logic specifications: A practical approach, 10th ACM Symp. on Principles of Programming Languages, Austin, TX, 1983.

- [4] E. Clarke and B. Mishra, Automatic verification of asynchronous circuits, in: E. Clarke and D. Kozen, eds., *Proc. C-M.U. Workshop on Logics of Programs*, Pittsburgh, PA, 1983; Lecture Notes in Computer Science 164 (Springer, Berlin, 1984).

- [5] E.A. Emerson and E.M. Clarke, Characterizing properties of parallel programs as fixpoints, *Proc.* 7th Internat. Coll. on Automata, Languages and Programming, Lecture Notes in Computer Science 85 (Springer, Berlin, 1981).

- [6] J. Halpern, Z. Manna and B. Moszkowski, A hardware semantics based on temporal intervals, Report STAN-CS-83-963, Department of Computer Science, Stanford University, Stanford, 1983.

- [7] C.A. Mead and L.A. Conway, *Introduction to VLSI Systems* (Addison-Wesley, Reading, MA, 1980) Chapter 7.

- [8] R. Milner, A Calculus of Communicating Systems, Lecture Notes in Computer Science 92 (Springer, Berlin, 1980).

- [9] Y. Malachi and S.S. Owicki, Temporal specifications of self-timed systems, in: H.T. Kung, Bob Sproull and G. Steele, eds., VLSI Systems and Computations (Computer Science Press, Rockville, MD, 1981).