# University of Miami Scholarly Repository

**Open Access Dissertations**

**Electronic Theses and Dissertations**

2017-07-28

# MEMS Scale CMOS Compatible Energy Harvesters Using Piezoelectric Polymers for Sustainable Electronics

Alperen Toprak *University of Miami*, alperentoprak@gmail.com

Follow this and additional works at: https://scholarlyrepository.miami.edu/oa dissertations

#### Recommended Citation

Toprak, Alperen, "MEMS Scale CMOS Compatible Energy Harvesters Using Piezoelectric Polymers for Sustainable Electronics" (2017). Open Access Dissertations. 1933.

https://scholarlyrepository.miami.edu/oa\_dissertations/1933

This Open access is brought to you for free and open access by the Electronic Theses and Dissertations at Scholarly Repository. It has been accepted for inclusion in Open Access Dissertations by an authorized administrator of Scholarly Repository. For more information, please contact repository.library@miami.edu.

## UNIVERSITY OF MIAMI

# MEMS SCALE CMOS COMPATIBLE ENERGY HARVESTERS USING PIEZOELECTRIC POLYMERS FOR SUSTAINABLE ELECTRONICS

By

Alperen Toprak

## A DISSERTATION

Submitted to the Faculty of the University of Miami in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Coral Gables, Florida

August 2017

## UNIVERSITY OF MIAMI

## A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

# MEMS SCALE CMOS COMPATIBLE ENERGY HARVESTERS USING PIEZOELECTRIC POLYMERS FOR SUSTAINABLE ELECTRONICS

## Alperen Toprak

| Approved:                                                                          |                                                                                  |

|------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| Onur Tigli, D.Sc. Associate Professor of Electrical and Computer Engineering       | Sung Jin Kim, Ph.D. Associate Professor of Electrical and Computer Engineering   |

| Mohamed Abdel-Mottaleb, Ph.D. Professor of Electrical and Computer Engineering     | Manohar Murthi, Ph.D. Associate Professor of Electrical and Computer Engineering |

| Landon R. Grace, Ph.D. Assistant Professor of Mechanical and Aerospace Engineering | Guillermo J. Prado, Ph.D. Dean of the Graduate School                            |

TOPRAK, ALPEREN

(Ph.D., Electrical and Computer Engineering)

(August 2017)

MEMS Scale CMOS Compatible

Energy Harvesters Using Piezoelectric

Polymers for Sustainable Electronics

Abstract of a dissertation at the University of Miami.

Dissertation supervised by Dr. Onur Tigli

No. of pages in text (136)

The field of microelectronics had a remarkable progress since its beginnings in

1960s, which led to the advent of myriad new electronic devices that found widespread

usage in daily life. Continuous advances in CMOS and MEMS technologies reduced the

cost, size, weight, and power requirements of these devices, enabling the realization of

distributed systems such as wireless sensor networks. However, due to much slower pace

of innovation, currently available battery technologies continue to dictate the size, weight

and cost of these systems. There are further concerns brought by the batteries regarding

the environmental effects or feasibility of dead battery replacement in distributed or

embedded systems. As a result of this problem, there has been a growing research

impetus on energy harvesting technologies, which are expected to alleviate the problems

brought by the fixed capacity energy sources in electronic devices.

This dissertation proposes a new class of MEMS-scale piezoelectric energy

harvesters that have the potential to be monolithically integrated with CMOS circuits.

Proposed devices will utilize polyvinylidene fluoride-trifluoroethylene (PVDF-TrFE), a

piezoelectric polymer with an impressive electromechanical coupling factor of 0.3. Its

energy harvesting potential was evaluated using theoretical analyses and finite element

method (FEM) simulations and compared with other CMOS compatible piezoelectric

materials. Various architectural options for the mechanical and electrical structure of the energy harvester were examined and most promising options were determined.

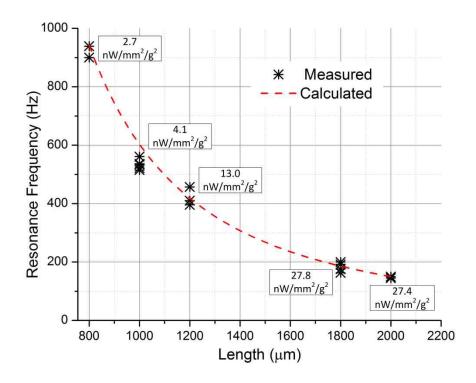

The process for the fabrication of PVDF-TrFE thin films was optimized to yield high quality films with strong ferroelectric and piezoelectric properties. A comprehensive characterization study was performed to measure the dielectric, ferroelectric, and piezoelectric properties of the fabricated films. Cantilever type MEMS scale piezoelectric energy harvesters (PEH) were fabricated and characterized. Maximum power output density on purely resistive loads in response to a 1.0 g input acceleration was measured as 27.8 nW/mm² from a (1800  $\mu$ m × 2000  $\mu$ m) device at its resonance frequency of 192.5 Hz. A power conditioning circuit, based on synchronous switching on inductor technique, was also designed and integrated with the fabricated prototypes. The circuit, which draws 250 nW power from ±1 V dual supplies at 200 Hz, improved the DC power output of the PEHs by 165%. Using the same (1800  $\mu$ m × 2000  $\mu$ m) prototype in combination with the circuit, a maximum power of 140 nW was transferred to a DC load under 1.0 g acceleration.

The results obtained throughout the course of this dissertation work proved that PVDF-TrFE can be used in MEMS scale energy harvesting devices. CMOS compatible fabrication process of the polymer makes it possible to integrate these energy harvesters with CMOS circuits on the same substrate. This monolithic integration approach would improve the unit cost, size, and reliability compared to integration at higher levels and therefore, can find use in applications such as wireless sensors networks, structure health monitoring systems, and wide area surveillance applications.

Dedicated to the memory of my father,

Mustafa Toprak

#### Acknowledgements

First and foremost, I would like to express my gratitude to my advisor Dr. Onur Tigli for his guidance, support, and help in every aspect of my doctorate studies. His professionalism, diligence, and mentoring skills are exceptional, and I feel privileged to have worked with him.

It is imperative to extend my thanks to the committee members Dr. Mohamed Abdel-Mottaleb, Dr. Sung Jin Kim, Dr. Manohar Murthi, and Dr. Landon Grace for their time and invaluable contributions that helped shape this dissertation.

Dr. Sukru U. Senveli never hesitated to share his knowledge and experience as a colleague, which helped me a lot especially when I started working in the cleanroom. He has also been a great friend since we met almost a decade ago, and having such a friend at UM when I first started made my transition much easier. Randil Gajasinghe is one of the nicest and most helpful people I have ever met. I am grateful for all his help in my studies as well as for his friendship. I would like to thank Yagmur Akin Yildirim for her help during the characterization experiments and Burak Yildirim for his help while constructing the mechanical test setup. They also deserve special thanks for their friendship and the delicious food they shared with us. My thanks are extended to our other labmate Jorge Gomez for his kindness and friendship.

I would like to thank Neal Ricks and Patrick Roman for their help at the AMERI cleanroom. Valuable suggestions and contributions of Dr. Mikkel Thomas from Georgia Institute of Technology during cantilever suspension process are gratefully acknowledged. Kevin Luongo also has my gratitude for always keeping the equipment running at AMERI and BIONIUM cleanrooms as well as his always-positive attitude. I

would also like to thank my friend Mark Stone for generously sharing equipment time at AMERI cleanroom when I needed them the most.

My thanks extend to our lab neighbors and friends Young-Hun (Paul) Paik and Seongman Cho for their help, and Mohammad Haghighat, Duygu Yasar, and Ranga Dabarera for their friendship. I want to present my special thanks to my longtime friend, classmate, and colleague Dr. Murat Deniz Aykin for his support and friendship.

Last but not least, my family deserves the biggest acknowledgements. My parents Aysun and Mustafa, and sisters Dilsad and Behiye Gokcen have always provided their love, encouragement, and support throughout my entire life. It breaks my heart that my father could not see this day; but I am honored to dedicate this work to the memory of such a great father. And of course, my lovely wife Gokce, who patiently shared a lot of burden with me throughout this journey, deserves the biggest acknowledgement of all.

## **TABLE OF CONTENTS**

|         |                                                      | Page     |

|---------|------------------------------------------------------|----------|

| LIST OF | FIGURES                                              | viii     |

| LIST OF | TABLES                                               | xx       |

| СНАРТЕ  | ZR                                                   |          |

| 1       | INTRODUCTION                                         | 1        |

| 1.1     | Energy Harvesting Overview                           | 1        |

| 1.2     | Piezoelectric Energy Harvesters                      | 3        |

| 1.1.1   | Macro and Meso-Scale Piezoelectric Energy Harvesters | 4        |

| 1.1.2   | MEMS Scale Piezoelectric Energy Harvesters           | 5        |

| 1.2.1   | Nano-Scale Piezoelectric Energy Harvesters           | 9        |

| 1.3     | Research Objectives                                  | 10       |

| 1.4     | Thesis Organization                                  | 13       |

| 2       | PIEZOELECTRIC ENERGY HARVESTING THEORY               | 15       |

| 2.1     | Piezoelectricity Phenomenon.                         | 15       |

| 2.2     | Energy Harvesting Using Direct Piezoelectric Effect  |          |

| 2.3     | Cantilever Type Piezoelectric Energy Harvesters      | 21       |

| 2.3.1   | Theoretical Analysis of a Bent Cantilever Beam       | 22       |

| 2.3.2   | Equivalent Circuit Models for Cantilever Type PEHs   | 29       |

| 3       | STUDIES ON ARCHITECTURE AND PIEZOELECTRIC MAT        | ERIAL 36 |

| 3.1     | Studies on Electrode Architectures                   | 37       |

| 3.2     | Piezoelectric Material Comparison                    | 39       |

| 3.3     | Structural Layer Selection                           | 43       |

|   | 4      | CHARACTERIZATION OF PVDF-TRFE THIN FILMS                          | 46    |

|---|--------|-------------------------------------------------------------------|-------|

|   | 4.1    | Dielectric Measurements                                           | 48    |

|   | 4.2    | Ferroelectric Measurements                                        | 50    |

|   | 4.2.1  | Electric Field and Frequency Dependence at Room Temperature       | 52    |

|   | 4.2.2  | Temperature Dependence of Hysteresis                              | 55    |

|   | 4.2.3  | Ferroelectric Fatigue                                             | 56    |

|   | 4.3    | Piezoelectric Measurements                                        | 58    |

|   | 5      | PROCESS DEVELOPMENT AND FABRICATION OF PVDF-TRFE                  |       |

|   | BASE   | ED MEMS ENERGY HARVESTERS                                         | 63    |

|   | 5.1    | Process Development for PVDF-TrFE Thin Films                      | 63    |

|   | 5.1.1  | PVDF-TrFE Film Uniformity Improvement                             | 64    |

|   | 5.1.2  | Top Electrode Adhesion to PVDF-TrFE                               | 69    |

|   | 5.2    | Fabrication and Testing of PVDF-TrFE Based MEMS Energy Harvesters | 72    |

|   | 5.2.1  | Proof-of-Concept PEHs with Single PVDF-TrFE Layer                 | 73    |

|   | 5.2.2  | Optimized PEHs with Multiple PVDF-TrFE Layers                     | 76    |

|   | 6      | INTEGRATION WITH ELECTRONICS                                      | 96    |

|   | 6.1    | Synchronous Switched Energy Harvesting Circuits                   | 99    |

|   | 6.2    | Low Power SSHI Circuit Design                                     | 104   |

|   | 6.2.1  | Transistor Level Design                                           | 110   |

|   | 6.2.2  | Board Level Design                                                | . 113 |

|   | 7      | CONCLUSION AND FUTURE WORK                                        | 119   |

| R | EFERE] | NCES                                                              | 125   |

## LIST OF FIGURES

| Figure 2.1: Illustration of the poling process. Randomly oriented crystalline domains are           |

|-----------------------------------------------------------------------------------------------------|

| aligned by an external voltage, and the alignment is preserved after the voltage is                 |

| removed                                                                                             |

| Figure 2.2: Piezoelectric coefficient matrix structures for PZT and PVDF-TrFE. Although             |

| both materials have 5 non-zero coefficients, only 3 of these are independent in PZT 18              |

| Figure 2.3: A simple d <sub>33</sub> mode PEH consisting of a metallized piezoelectric material     |

| block with a thickness $t$ and a surface area of $A = l \times w$ .                                 |

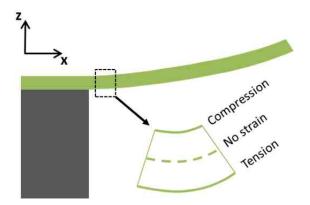

| Figure 2.4: Bent cantilever beam and cross-sectional view showing the resultant stresses.           |

| The hypothetical plane with zero strain, shown with dashed line, is called the neutral axis.        |

| 21                                                                                                  |

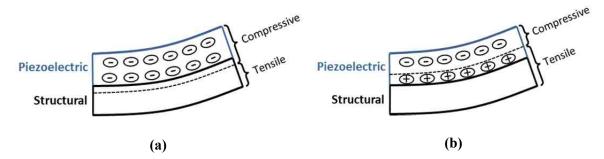

| Figure 2.5: (a) Neutral axis is located inside the structural layer; the piezoelectric layer is     |

| completely under compressive stress. (b) Neutral axis is located inside the piezoelectric           |

| layer, where opposite-sign strains cause charge cancellation. 23                                    |

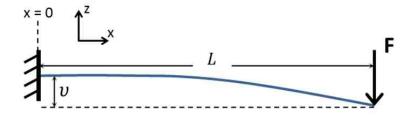

| Figure 2.6: A thin cantilever beam of length $L$ bent under a point force $F$ applied to its tip.   |

|                                                                                                     |

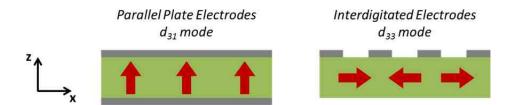

| Figure 2.7: Parallel plate and interdigitated electrode configurations for cantilever type          |

| PEHs. Red arrows show the polarization direction inside the piezoelectric materials.                |

| Cantilever length and thickness are along x and z axes, respectively                                |

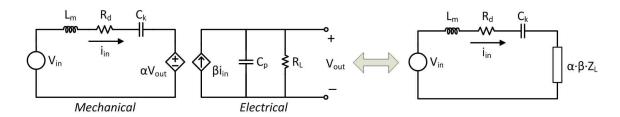

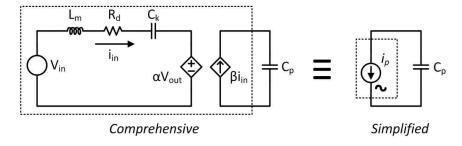

| Figure 2.8: A comprehensive ECM for PEHs [90]. In the mechanical domain, $V_{in}$ , $L_m$ , $C_k$ , |

| and $R_{\text{d}}$ represent the input stress, inertia, compliance, and damping, respectively.      |

| Electrical domain consists of only the piezoelectric capacitor and its leakage resistance           |

| Coupling between the domains is modeled with the dependent sources. Electrical domain                              |

|--------------------------------------------------------------------------------------------------------------------|

| impedance can be reflected on the mechanical side by multiplying it with $(\alpha \cdot \beta)$                    |

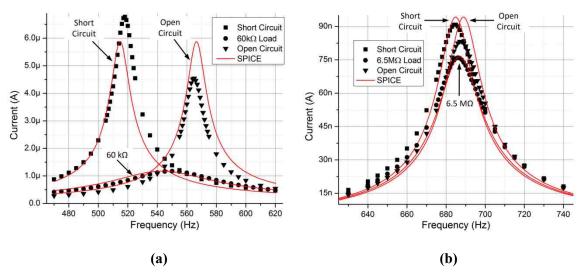

| Figure 2.9: Comparison of 2D FEM and SPICE simulations for MEMS scale PEHs that                                    |

| utilize (a) PZT and (b) AlN as the piezoelectric layer. Results show a very good match                             |

| between the results of the two methods except for the open-circuit and short-circuit                               |

| current amplitudes of PZT                                                                                          |

| Figure 2.10: Simplified model for PEHs with weak electromagnetic coupling. Due to                                  |

| limited effect of the electrical load on mechanical response, AC current amplitude                                 |

| depends only on the mechanical input                                                                               |

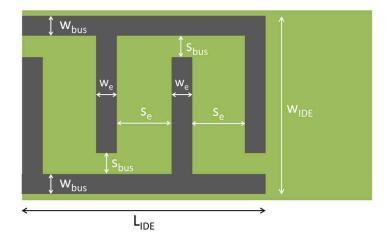

| Figure 3.1: A sample IDE pattern with dimensions $L_{\text{IDE}}$ by $w_{\text{IDE}}$ that shows the               |

| parameters that define electrode geometry: finger width $w_{\text{e}}$ , finger spacing $s_{\text{e}}$ , bus width |

| w <sub>bus</sub> , and finger-bus spacing s <sub>bus</sub> [66]                                                    |

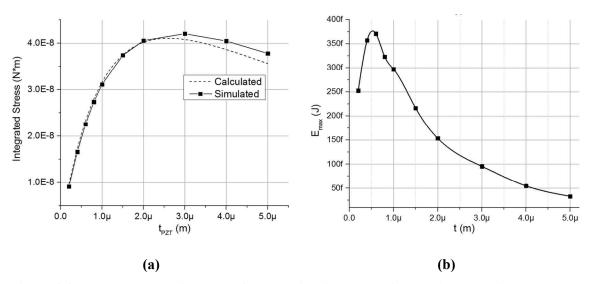

| Figure 3.2: (a) The volume integral of the longitudinal stress in the piezoelectric layer                          |

| due to a 15 $\mu N$ tip force for various thickness values [66]. (b) Simulated electrical energy                   |

| output of the same device in response to the same tip force [66]. Maximum electrical                               |

| energy was obtained at a much lower thickness value, indicating that the piezoelectric                             |

| material utilization efficiency is lower in thicker films                                                          |

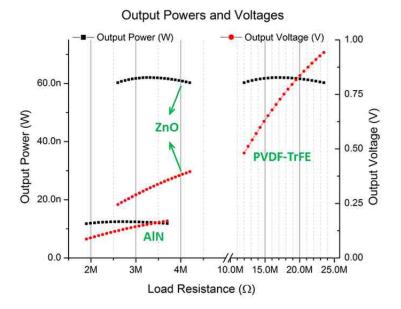

| Figure 3.3: Output voltage and power values obtained from the FEM simulations of 2-                                |

| dimensional MEMS scale PEH models using PVDF-TrFE, AlN, and ZnO [69]. Thickness                                    |

| values of the materials were selected to give the same neutral axis location with a 2 $\mu m\!\!-\!\!$             |

| thick SiO <sub>2</sub> structural layer                                                                            |

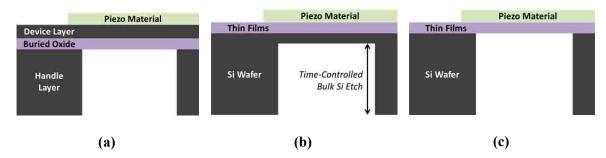

| Figure 3.4: Structural layer options for MEMS scale PEHs: (a) Device and buried oxide                          |

|----------------------------------------------------------------------------------------------------------------|

| layers of SoI wafers, (b) Thin films with partially etched bulk Si underneath, and (c) Thin                    |

| films with the bulk Si completely etched.                                                                      |

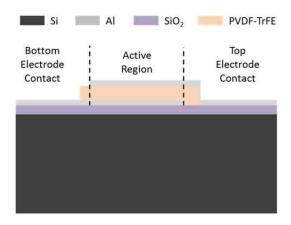

| Figure 4.1: Cross-sectional view of the PVDF-TrFE capacitors used for characterization                         |

| studies. 46                                                                                                    |

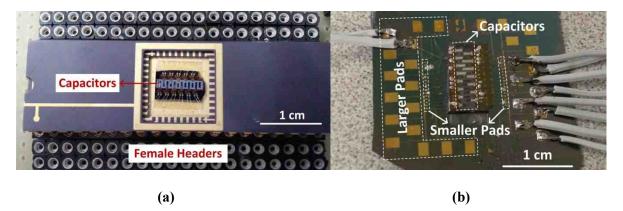

| Figure 4.2: (a) PVDF-TrFE capacitors wire bonded to a standard DIP40 IC package used                           |

| for the dielectric measurements and ferroelectric measurements at room temperature. (b)                        |

| PVDF-TrFE capacitors from the same wafer that are bonded to a custom-made silicon                              |

| wafer piece with lithographically created pads. These capacitors were used for                                 |

| piezoelectric and high temperature ferroelectric tests. 47                                                     |

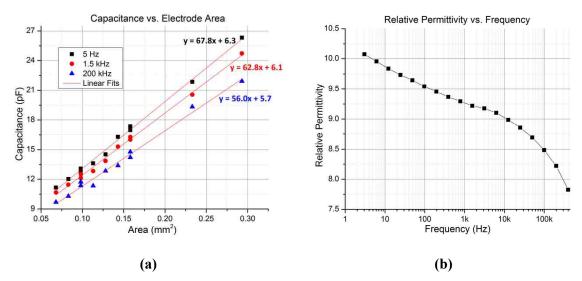

| Figure 4.3: (a) Capacitances measured at 5 Hz, 1.5 kHz, and 200 kHz from capacitors                            |

| with electrode areas ranging from 0.07 mm <sup>2</sup> to 0.29 mm <sup>2</sup> . Linear fits and corresponding |

| linear equations are also shown [106]. (b) Frequency dependence of the relative                                |

| permittivity of the PVDF-TrFE film as calculated from the capacitance measurements                             |

| [106]                                                                                                          |

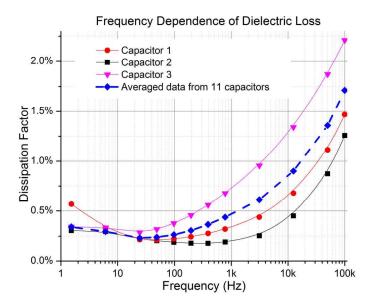

| Figure 4.4: Dissipation factors of PVDF-TrFE capacitors measured at different                                  |

| frequencies [106]. Solid lines show measurements from 3 different capacitors, whereas                          |

| the dashed line shows the average data from 11 capacitors                                                      |

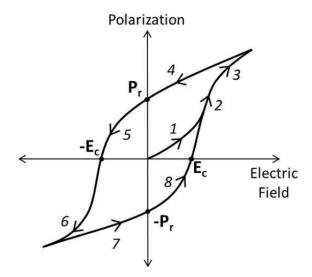

| Figure 4.5: A sample ferroelectric hysteresis curve, which initially starts from the origin                    |

| and follows path 1. Steep slope around path 2 indicates the start of polarization                              |

| alignment, followed by saturation region, path 3, with linear response. Removing the                           |

| voltage moves the curve along path 4, yielding a remnant polarization P <sub>r</sub> . Same response           |

| is obtained if a negative voltage cycle is applied, creating a closed hysteresis loop 51                       |

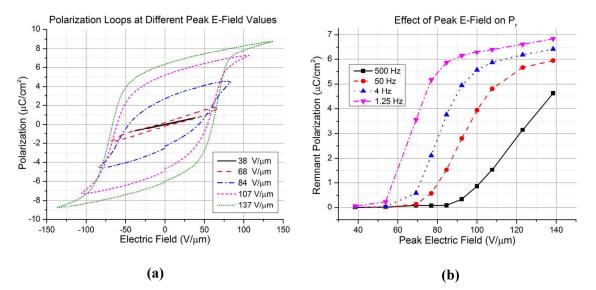

| Figure 4.6: (a) Polarization loops obtained using 4 Hz bipolar triangular waveforms with       |

|------------------------------------------------------------------------------------------------|

| different peak amplitudes [106]. (b) Dependence of remnant polarization on the peak            |

| electric field for different frequencies [106]. No significant remnant polarization was        |

| observed under approximately 55 V/ $\mu m$ , regardless of the waveform period                 |

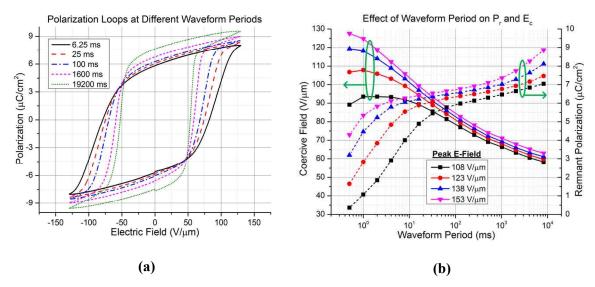

| Figure 4.7: (a) Polarization loops obtained using bipolar triangular waveforms with            |

| $130\ V/\mu m$ peak amplitude and different periods. A slight increase in remnant polarization |

| and more significant reduction in coercive field were observed with increasing period. (b)     |

| Effect of the waveform on the remnant polarization and coercive field. Coercive field          |

| decreased logarithmically with increasing period after the remnant polarization reaches        |

| saturation. 54                                                                                 |

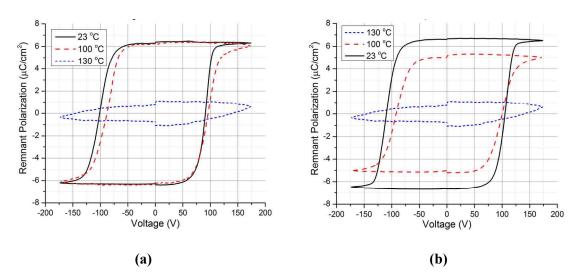

| Figure 4.8: Remnant polarization loops obtained at different temperatures during (a)           |

| heating and (b) cooling cycles using bipolar triangular waveforms with 350 ms periods.         |

| 55                                                                                             |

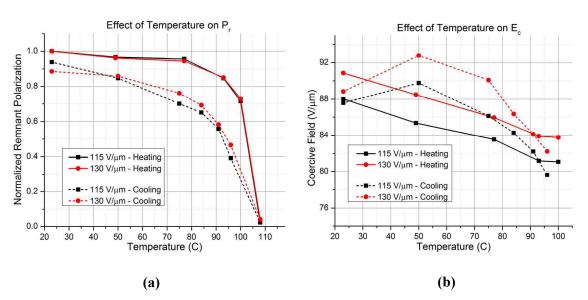

| Figure 4.9: (a) Normalized remnant polarization and (b) coercive field at various              |

| temperatures between 23 °C and 110 °C [106]. Solid and dashed lines show the heating           |

| and cooling cycles, respectively. Remnant polarization showed a sharp reduction after          |

| 95 °C and reaches zero at 108 °C. Coercive field slightly decreased with increasing            |

| temperature                                                                                    |

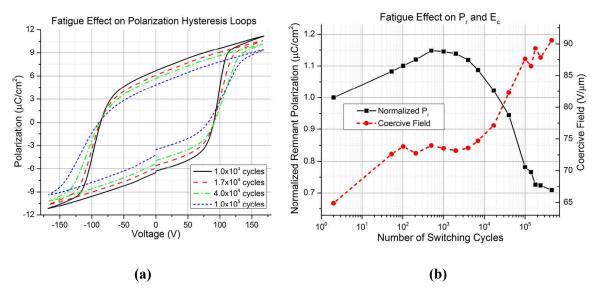

| Figure 4.10: (a) Polarization loops showing the degradation in the ferroelectric behavior      |

| after repeated polarization switching cycles. (b) Change in the remnant polarization and       |

| coercive field with increasing number of cycles                                                |

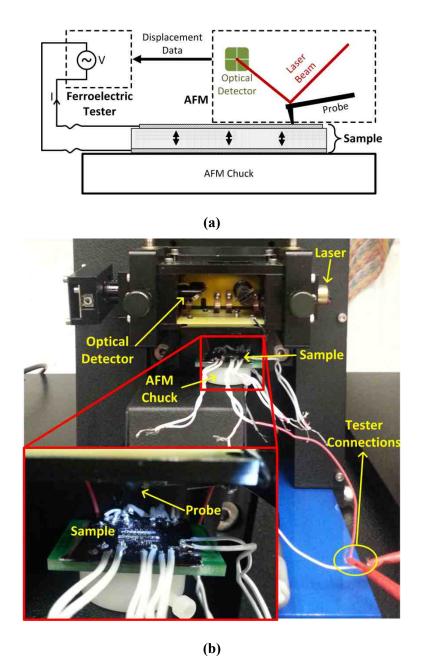

| Figure 4.11: (a) Simplified schematic diagram showing the operation principle of PNDS          |

| [106]. Piezoelectric displacement in response to the AC signal creates a proportional          |

| signal in the AFM detector. (b) Photograph of the PNDS setup with a sample placed on              |

|---------------------------------------------------------------------------------------------------|

| the AFM chuck for measurements [106]. The inset shows the close-up view of the sample             |

| and AFM probe, which are brought into contact for measurements                                    |

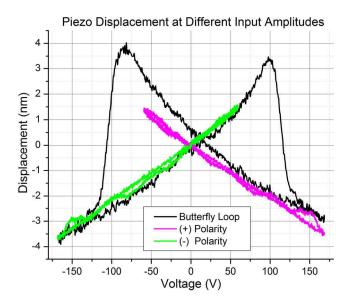

| Figure 4.12: Piezoelectric displacement loops obtained using voltage waveforms with               |

| switching and non-switching amplitudes [106]. Switching waveforms generate "butterfly             |

| loops", showing the polarization reversal due to high electric field. Non-switching               |

| waveforms demonstrate a linear voltage-displacement relationship in both polarities 60            |

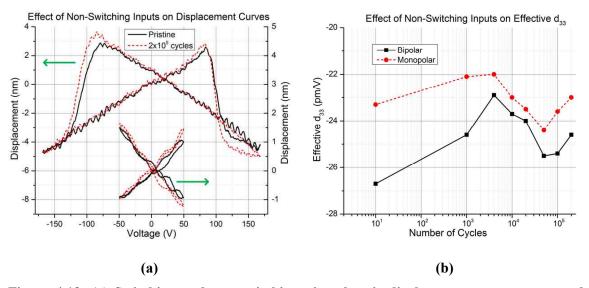

| Figure 4.13: (a) Switching and non-switching piezoelectric displacement curves                    |

| measured before DC poling and after 2x10 <sup>5</sup> non-switching cycles [106]. No significant  |

| difference was observed between the measurements, except the increased negative                   |

| coercive field due to imprint. (b) Effective $d_{33}$ values in response to 200 Hz unipolar and   |

| bipolar waveforms [106]. Maximum deviation in the effective $d_{33}$ values throughout these      |

| measurements were found as 15.4%.                                                                 |

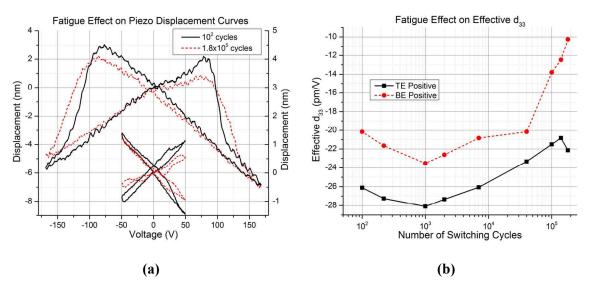

| Figure 4.14: (a) Switching and non-switching piezoelectric displacement curves                    |

| measured before DC poling and after 1.8x10 <sup>5</sup> switching cycles [106]. Both small signal |

| and large signal curves show significant degradation. (b) Effective $d_{33}$ values measured      |

| from non-switching waveforms at 200 Hz [106]. Effective $d_{33}$ decreased by 24% and             |

| 41% after 10 <sup>5</sup> cycles from their peak values for downward and upward polarizations,    |

| respectively. 62                                                                                  |

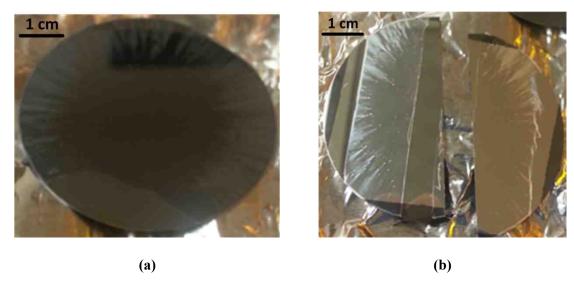

| Figure 5.1: Spin coated PVDF-TrFE films on 2" Si wafers (a) directly on bulk Si, and (b)          |

| on top of a thin film Al layer during initial experiments. Both films had comet-like shapes       |

| with significant non-uniformity in the film surface. 65                                           |

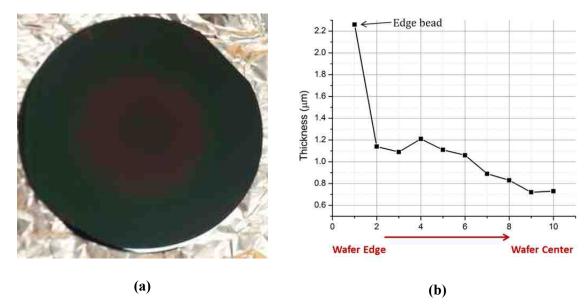

| Figure 5.2: (a) 4" wafer with a PVDF-TrFE film spin coated from a filtered solution. (b)         |

|--------------------------------------------------------------------------------------------------|

| Thickness measurement results obtained along a line from the center of the wafer to the          |

| edge. The thickness difference between the middle and outer regions is the cause of the          |

| color difference on the wafer. 66                                                                |

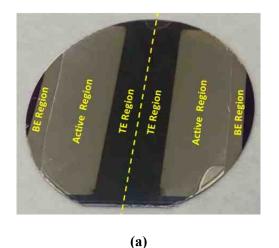

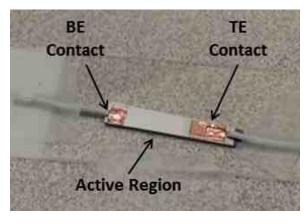

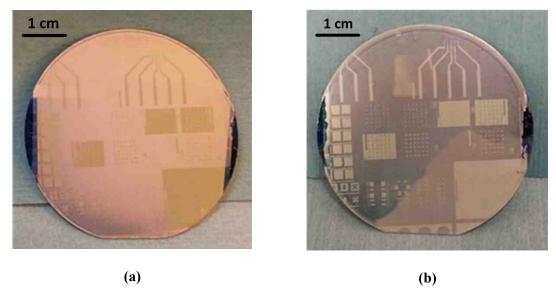

| Figure 5.3: (a) 2" SiO <sub>2</sub> coated Si wafer with Al and PVDF-TrFE layers. Al layers were |

| deposited by sputtering through vacuum tapes used as shadow masks. A second Al layer             |

| was deposited on top of the PVDF-TrFE to create capacitors with separate contact                 |

| regions for top and bottom electrodes. (b) A sample prepared using this method with              |

| wires connected to its electrodes for ferroelectric tests. 67                                    |

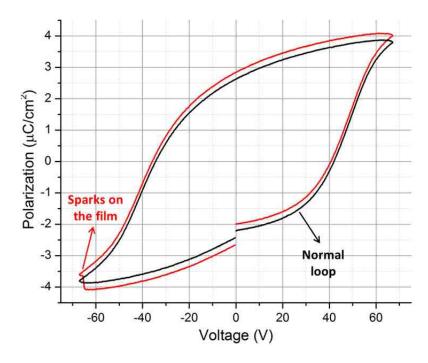

| Figure 5.4: Two polarization hysteresis loops measured on the same sample. One of the            |

| loops has a discontinuity near the negative peak voltage, which is caused by sparking 68         |

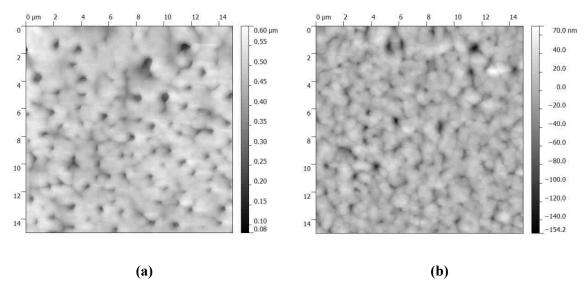

| Figure 5.5: AFM images of spin coated PVDF-TrFE films deposited in (a) single step               |

| using a solution with 5% PVDF-TrFE by weight, and (b) two steps from 5% and 2%                   |

| solutions by weight, respectively. Surface roughness values were measured as 72 nm and           |

| 21 nm for single step and two step coatings, respectively                                        |

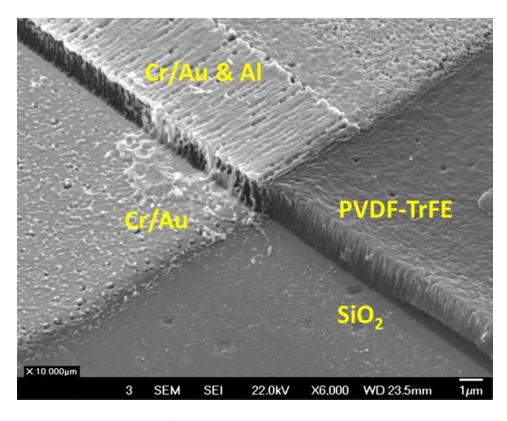

| Figure 5.6: (a) Swelling and (b) peeling of a Ti/Al top electrode layer after photoresist        |

| development                                                                                      |

| Figure 5.7: Top electrode patterning experiment results for (a) Ti/Al and (b) Cr/Al layers       |

| on 3-hour annealed PVDF-TrFE films. Both metal stacks were patterned without any                 |

| problems                                                                                         |

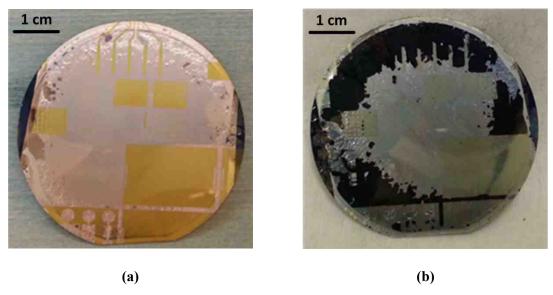

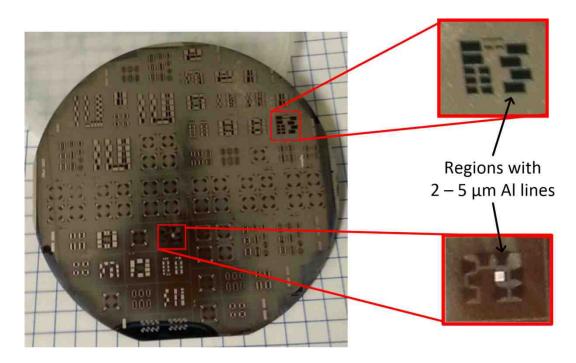

| Figure 5.8: Photographs taken from a wafer with an Al film coated on top of PVDF-TrFE            |

| after photoresist develop. Highly non-uniform Al attack by the developer was clearly             |

| visible to bare eye. Thin patterns with 2 – 5 µm Al lines were completely destroyed 72           |

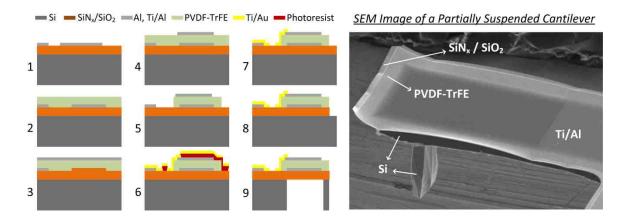

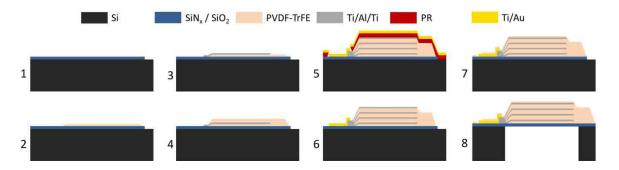

| Figure 5.9: Process flow used to fabricate first generation PEHs [70]: (1) Sputtered and                |

|---------------------------------------------------------------------------------------------------------|

| patterned Al bottom electrode, (2) spin coated PVDF-TrFE, (3) sputtered and (4)                         |

| patterned Ti/Al top electrode, (5) patterned PVDF-TrFE, (6) patterned photoresist and                   |

| sputtered Ti/Al for bonding pads, (7) formed bonding pads with lift-off, (8) patterned                  |

| $SiN_x$ and $SiO_2$ , and (9) released cantilevers with backside DRIE and $XeF_2$ etch                  |

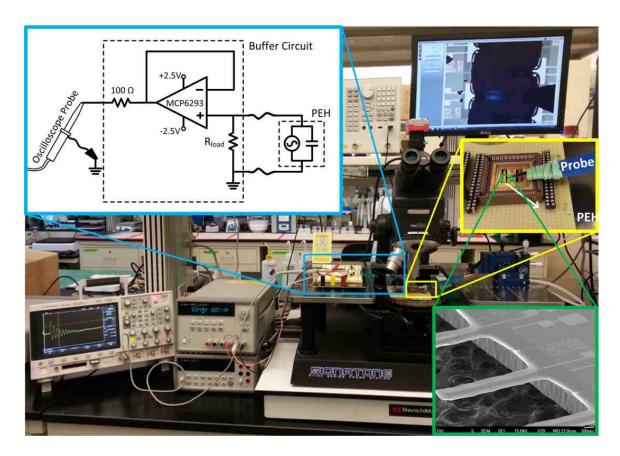

| Figure 5.10: Photo of the measurement setup used to evaluate the energy harvesting                      |

| performance of the fabricated devices [70]. The setup includes a probe station, a custom-               |

| made probe tip, a unity gain buffer circuit, a DC power supply, and an oscilloscope.                    |

| Insets show the schematic of electrical connections in the setup, a close-up photo of the               |

| custom-made probe tip on top of a PEH, and an SEM image of the fabricated PEHs 75                       |

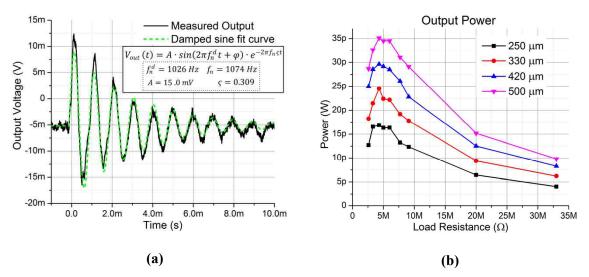

| Figure 5.11: (a) Voltage output of a 1200 $\mu m \times 300~\mu m$ cantilever measured on a 5 $M\Omega$ |

| load in response to an initial tip displacement of 330 $\mu m$ . Damped sine wave fit curve and         |

| extracted parameters are also shown [70]. (b) Calculated output power values of the same                |

| cantilever for different resistive loads and initial tip displacement values. Maximum                   |

| power output density for a 500 µm harmonic tip displacement was calculated as                           |

| 97.5 pW/mm <sup>2</sup> on a 4.3 M $\Omega$ load [70].                                                  |

| Figure 5.12: SEM image taken from a first generation PEH showing an electrode contact                   |

| along PVDF-TrFE edge. Poor step coverage at the vertical walls yields unreliable                        |

| contacts. 77                                                                                            |

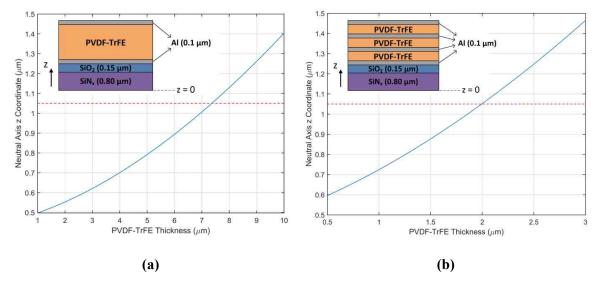

| Figure 5.13: Neutral axis location for different PVDF-TrFE layer thickness values for (a)               |

| single-layer and (b) 3-layer designs. Total active layer thicknesses resulting in a neutral             |

| axis at the bottom boundary of PVDF-TrFE are 7.4 $\mu m$ and 6.0 $\mu m$ , respectively. The            |

| difference is caused by the mechanical effect of the electrode layers 79                                |

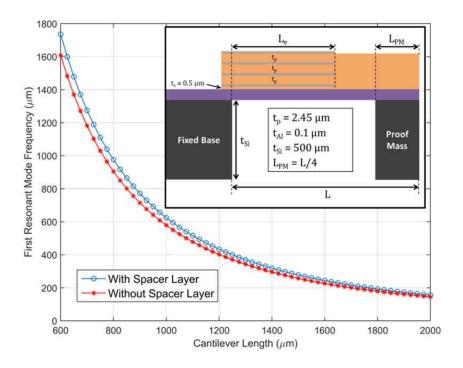

| Figure 5.14: Calculated resonance frequency of the cantilever depicted in the inset for                                      |

|------------------------------------------------------------------------------------------------------------------------------|

| different length values. The effect of a 0.5 $\mu m$ -thick spacer PVDF-TrFE layer on the                                    |

| frequency was found to be less than 10%.                                                                                     |

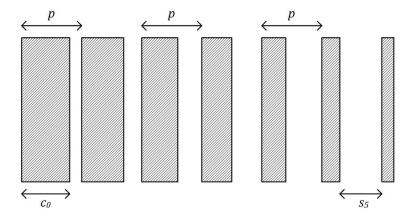

| Figure 5.15: Sample constant-pitch grating pattern for grayscale lithography. The                                            |

| structure is periodic with $\mathbf{p} = c\mathbf{i} + s\mathbf{i}$ , where $c_i$ and $s_i$ denote the dark and clear region |

| lengths, respectively. If the pitch length $p$ is close to the resolution of the optical system,                             |

| a gradually changing UV pattern can be obtained on the photoresist along the gratings                                        |

| [121]                                                                                                                        |

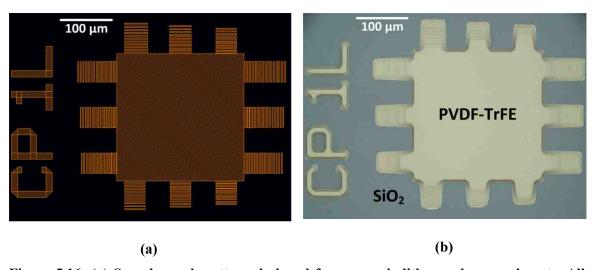

| Figure 5.16: (a) Sample mask pattern designed for grayscale lithography experiments. All                                     |

| gratings are constant-pitch with different lengths and levels. (b) PVDF-TrFE thin film                                       |

| patterned using the test mask. All gratings on the test structure gave acceptable results. 84                                |

| Figure 5.17: Process flow of the multilayer PEHs: (1) Patterning SiN <sub>x</sub> /SiO <sub>2</sub> layer with               |

| RIE (2) Spacer PVDF-TrFE via spin coating and patterning with RIE (3) Ti/Al/Ti                                               |

| electrodes via sputtering and wet etch (4) Active PVDF-TrFE via spin coating and RIE                                         |

| (5) Ti/Au on top of patterned photoresist via sputtering (6) Bonding pads via lift-off (7)                                   |

| Passivation PVDF-TrFE via spin coating and patterning with RIE (8) Proof mass                                                |

| formation and cantilever suspension with DRIE and XeF2 etch. Steps (3) and (4) were                                          |

| repeated 3 and 2 more times, respectively, to form 3 active PVDF-TrFE layers                                                 |

| sandwiched between 4 electrode layers. 86                                                                                    |

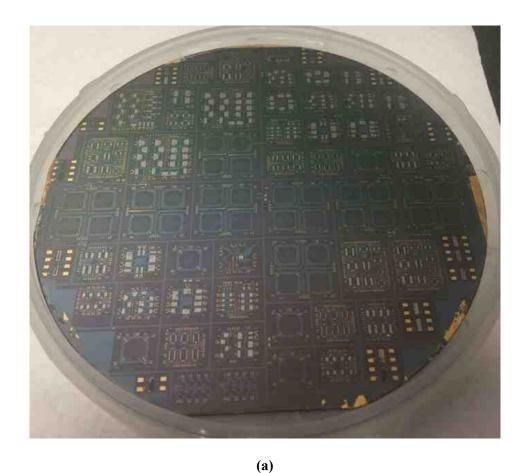

| Figure 5.18: (a) Photograph of the 4" wafer with multilayer PEHs before backside                                             |

| process. (b) Photograph of a die with 800 $\mu$ m-long and 1000 $\mu$ m-long cantilevers. The                                |

| 1 cm <sup>2</sup> die includes 20 cantilevers. (c) SEM image of a prototype with 1 mm-wide                                   |

| cantilevers. The inset at the top right corner shows the smooth electrode connection over                                    |

| a slanted wall through a step height of approximately 8 $\mu m$ . The inset at the bottom right |

|-------------------------------------------------------------------------------------------------|

| corner shows a closer view of the multiple PVDF-TrFE/electrode layers                           |

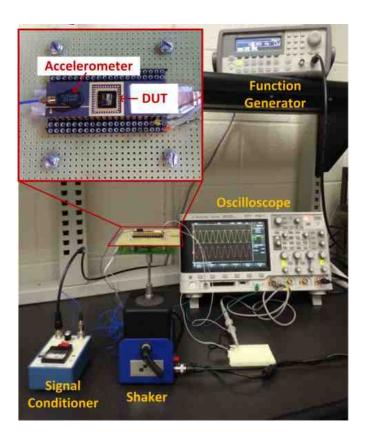

| Figure 5.19: Photograph of the test setup used for the mechanical tests of the multilayer       |

| PEHs. The shaker was driven with sine waves of different amplitude and frequencies              |

| using the function generator to create mechanical vibrations. Both the input acceleration,      |

| measured directly from the IC package with an accelerometer, and PEH output were                |

| observed and recorded using the oscilloscope.                                                   |

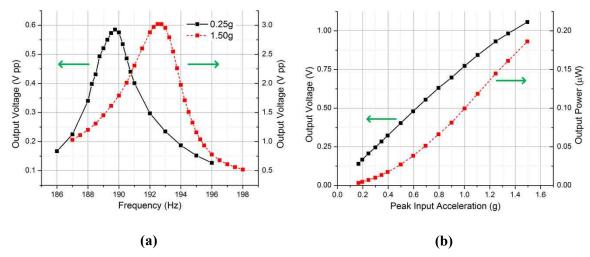

| Figure 5.20: Experimental results obtained from an 1800 $\mu m \times 2000~\mu m$ multilayer    |

| prototype. (a) Frequency response under 0.25g and 1.50g input acceleration values. (b)          |

| Output voltage and maximum power output on an optimal resistive load for different              |

| input acceleration values. 90                                                                   |

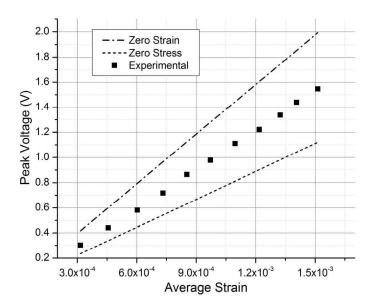

| Figure 5.21: Theoretical and experimental values for the open circuit output voltage of         |

| the 1800 $\mu m \times 2000~\mu m$ PEH. Measured voltages increase linearly with average strain |

| and they fit around the middle of the range defined by the two extreme cases                    |

| Figure 5.22: Summary of the measurement results obtained from cantilevers with various          |

| dimensions. 93                                                                                  |

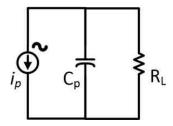

| Figure 6.1: Weakly coupled PEH model with purely resistive load                                 |

| Figure 6.2: Weakly coupled PEH model with a 4-diode full wave rectifier type AC-DC              |

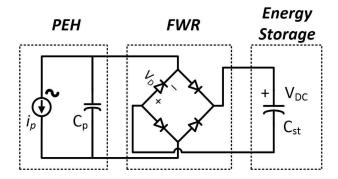

| converter load 97                                                                               |

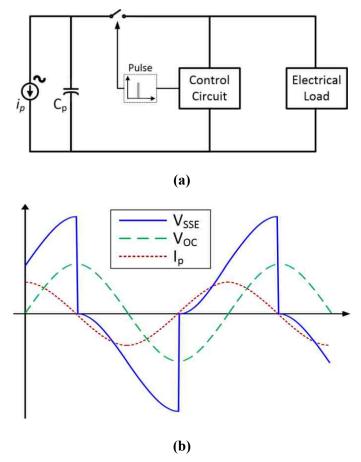

| Figure 6.3: (a) Block diagram of an SSE circuit. The control circuit shortly closes the         |

| switch at the voltage peaks to transfer the charge to the load. (b) Voltage and current         |

| waveforms of a PEH with an SSE interface. Open circuit voltage is also shown for                |

| comparison 100                                                                                  |

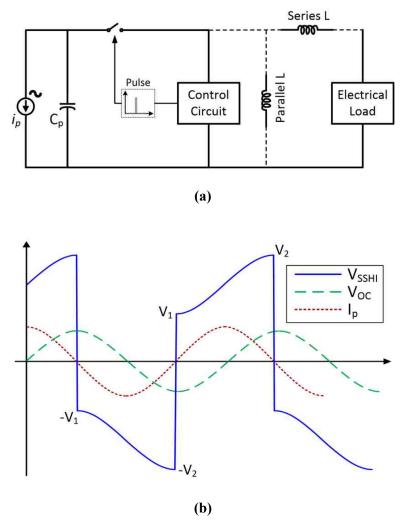

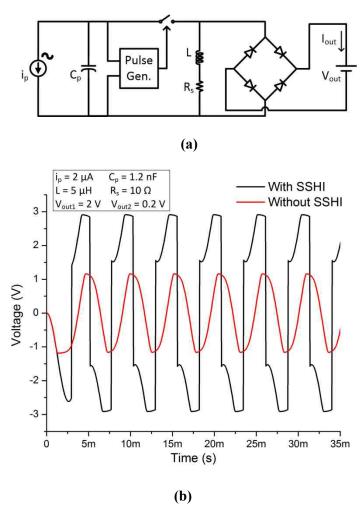

| Figure 6.4: (a) Simplified schematic of an SSHI circuit. The inductor can be placed in                   |

|----------------------------------------------------------------------------------------------------------|

| parallel or in series with the load. (b) Open circuit voltage with and without SSHI.                     |

| Current generated by the PEH is also shown. 101                                                          |

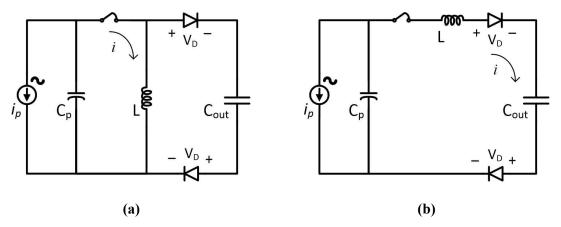

| Figure 6.5: Equivalent circuits of (a) parallel and (b) series SSHI with a rectifier type                |

| load. Parallel SSHI can drive current onto the inductor at any voltage, whereas the series               |

| circuit requires a minimum voltage of $2V_{\text{D}}$ on the capacitor to initiate the current $102$     |

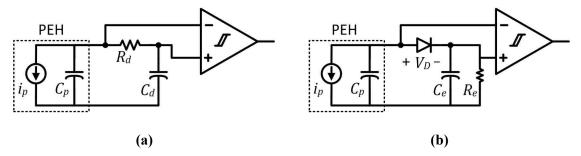

| Figure 6.6: Peak instant detection using comparators. The signal can be compared with                    |

| (a) delayed version of itself, or (b) its envelope. Delayed signal comparison toggles the                |

| output at both positive and negative peaks, whereas two separate circuits are required to                |

| detect the positive and negative peaks in envelope comparison                                            |

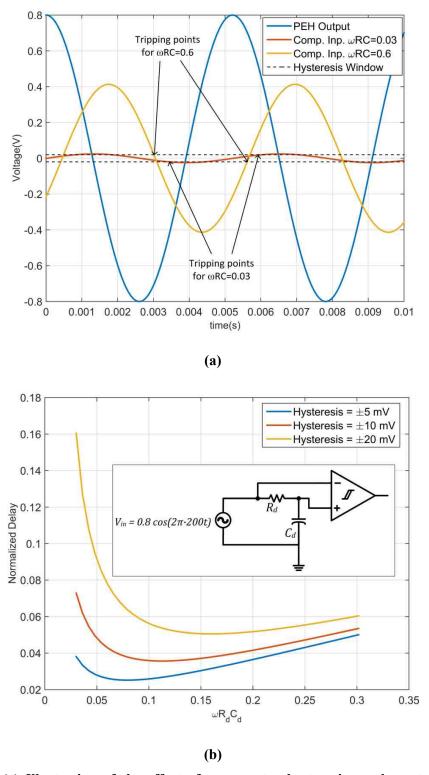

| Figure 6.7: (a) Illustration of the effect of comparator hysteresis on the output tripping               |

| delay. The delay of the circuit with $\omega RC = 0.03$ is worse than the one with $\omega RC = 0.6$ due |

| to the $\pm 20$ mV hysteresis window. (b) Calculated normalized tripping delays of the circuit           |

| given in the inset for different hysteresis windows. Input amplitude also affects the                    |

| delays; the effect of hysteresis windows decreases at higher input amplitudes                            |

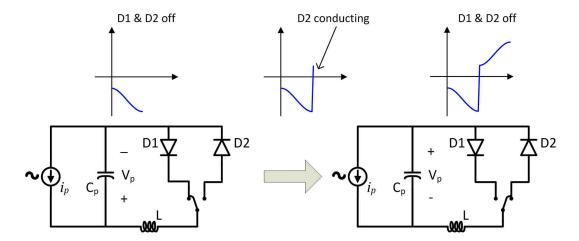

| Figure 6.8: SSHI circuit that can be driven by a single peak detecting comparator [133].                 |

| Comparator output is connected to the switch such that both diodes reverse-biased at all                 |

| times except for the switching instants. Once the voltage polarity is flipped, diodes                    |

| automatically turn off the current. 108                                                                  |

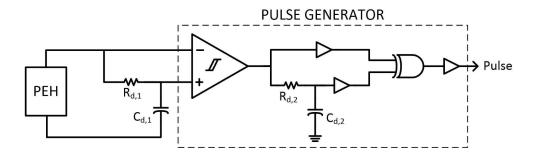

| Figure 6.9: Block diagram of the designed SSHI pulse generator circuit. The first delay                  |

| network determines the pulse delay and minimum PEH voltage required to operate the                       |

| circuit. The second delay network determines the pulse width                                             |

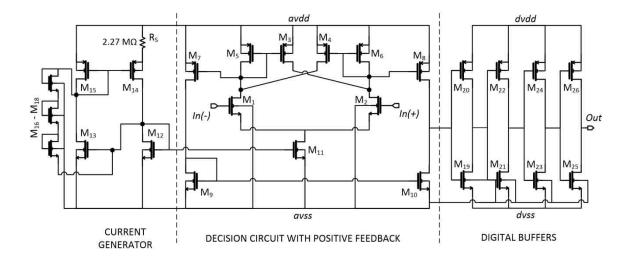

| Figure 6.10: Schematic of the comparator, which consists of a supply-independent               |

|------------------------------------------------------------------------------------------------|

| current generator, a decision circuit with positive feedback, and digital buffers. Digital     |

| buffers can be operated from a lower supply to reduce crowbar current and dynamic              |

| power dissipation. 111                                                                         |

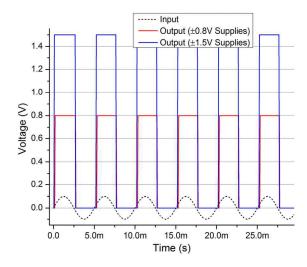

| Figure 6.11: Transient simulation results of the comparator with the negative input            |

| terminal connected to ground. Analog and digital sections were operated from dual and          |

| single supply voltages, respectively                                                           |

| Figure 6.12: (a) Setup used to simulate the designed SSHI circuit. (b) Transient               |

| simulation results showing the voltage waveforms with and without SSHI. Both cases             |

| were simulated with optimal DC values at the output, 2.0 V and 0.2 V, respectively 113         |

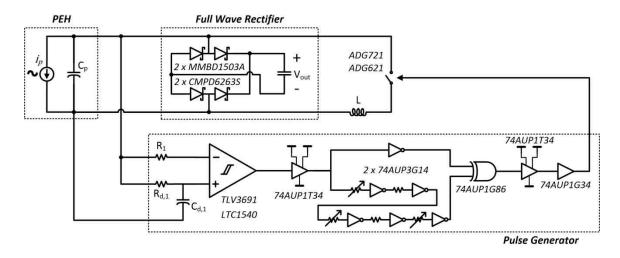

| Figure 6.13: Schematic of the SSHI circuit implemented at board level. Part numbers of         |

| the selected components are also shown in the figure. More than one option was                 |

| considered for some components, and the design was done to accommodate these                   |

| different options. 114                                                                         |

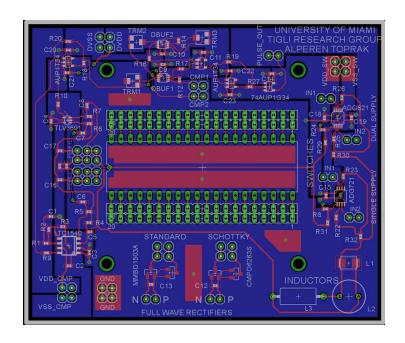

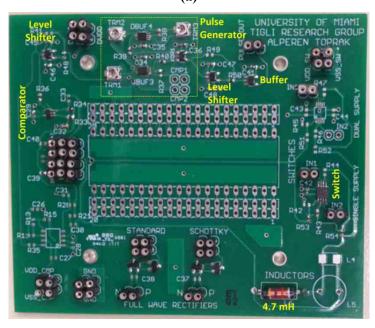

| Figure 6.14: (a) Layout of the SSHI PCB designed with a DIP40 type IC package                  |

| footprint for PEHs. (b) Photograph of a populated PCB                                          |

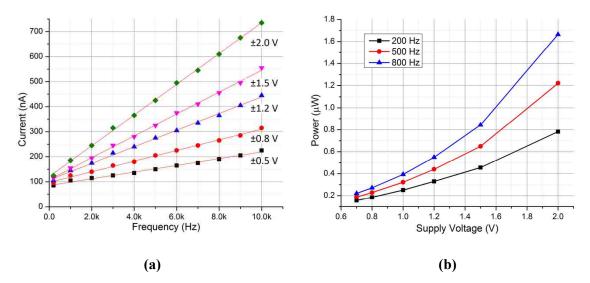

| Figure 6.15: (a) Current drawn by the comparator TLV3691 at different frequencies and          |

| supply voltages. (b) Total power dissipation of the SSHI circuit with different supply         |

| voltages. The circuit consumes only 300 nW power at 200 Hz when operated from $\pm 1.2$        |

| V                                                                                              |

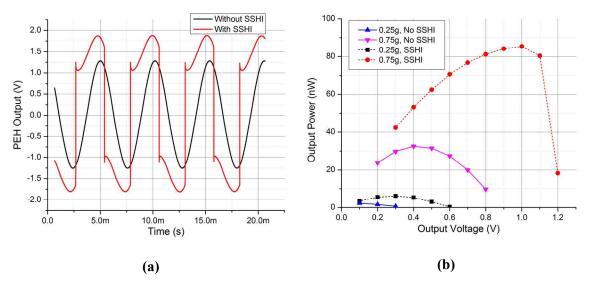

| Figure 6.16: (a) Output voltage of an 1800 $\mu m \times 2000~\mu m$ PEH with and without SSHI |

| when loaded with two standard oscilloscope probes. (b) Comparison of the harvested             |

| power from the same PEH with and without SSHI. The device was connected to a                   |

| constant DC voltage through a full wave | rectifier constructed using Schottky diodes |

|-----------------------------------------|---------------------------------------------|

| Output power was found to be 165% and   | 162% higher with SSHI at 0.25g and 0.75g    |

| input acceleration values               | 117                                         |

# LIST OF TABLES

| Table 5.1: Comparison of fully-microfabricated cantilever type PEHs. | 95  |

|----------------------------------------------------------------------|-----|

| Table 6.1: Transistor dimensions of the designed comparator.         | 111 |

#### **CHAPTER 1: INTRODUCTION**

The advent and subsequent rapid progress of microelectronics had a revolutionary effect on human civilization in the last five decades. Mass fabrication of highly integrated smart electronic devices such as sensors, actuators, transmitters, receivers, and processors led to the emergence of myriad applications that facilitated daily life. Concurrent advances in complementary metal oxide semiconductor (CMOS) and microelectromechanical systems (MEMS) technologies improved the performance of these devices while reducing their dimensions, costs, and power requirements. The ongoing trend for smaller and cheaper devices, combined with the improvements in wireless communication capability, enabled the realization of distributed systems such as wireless sensor networks (WSN). However, the success of these nascent technologies depends on the availability of reliable energy sources. Fixed capacity energy sources such as batteries give rise to cost, size, and lifetime problems. The basis of this dissertation is energy harvesting, which is an alternative solution that can address these problems.

#### 1.1 Energy Harvesting Overview

Energy harvesting can be simply defined as converting otherwise unused energy available in the environment into electrical energy for immediate or later use. Electrical energy is one of the most prominent commodities of the modern world; consequently, there are a great number of applications where energy harvesting devices can be utilized. The main factor that determines the potential applications is the scale of the harvestable energy. Large scale energy sources such as ocean waves or bridge vibrations can be utilized to support power grids as clean, renewable energy sources [1]. At smaller scales,

available energy is more suitable for powering standalone electronic sensors and transducers, which is typically done by batteries in current technology examples.

There are various energy sources available in the environment that can be harvested. including solar energy, structural vibrations, radio frequency (RF) waves, acoustic waves, and temperature gradients [2]. Among these potential sources, solar energy can provide the highest power density under direct sunlight [3]. However, this density drastically drops in a dim environment. Furthermore, transparency requirement renders solar energy harvesting useless in implanted or embedded systems. In comparison, mechanical vibrations can provide a power density level similar to solar energy in a cloudy environment [3]. In addition to this relatively high power density level, an important advantage of the vibration energy harvesting is the sturdy nature of its energy coupling mechanism. Unlike sunlight, vibrations cannot be easily absorbed or reflected by the materials on their propagation paths; in fact, specially designed vibration isolation systems are required to eliminate vibration coupling in sensitive applications such as atomic force microscopy (AFM). This usually unwanted phenomenon makes vibration energy harvesting a more versatile method that can be used in implanted or embedded systems.

There are a variety of vibration sources, especially in urban environment, generating vibrations with different amplitudes and frequencies. The range of the amplitude and frequencies vary from 4 m/s<sup>2</sup> at 1 Hz for a walking human to 20 m/s<sup>2</sup> at 44 Hz for an air compressor. [2-4]. Mechanical vibrations can be converted into electrical energy by coupling these vibrations onto a proof mass and then extracting its kinetic energy. The energy extraction can be done via electromagnetic, electrostatic, or piezoelectric

mechanisms [5]. Among these three methods, piezoelectric energy harvesters (PEH) have been reported to have higher energy density values [5, 6]. Higher energy density of PEHs become more pronounced in smaller scales; output power level of piezoelectric and electromagnetic harvesters scale with  $V^{4/3}$  and  $V^2$ , respectively, where V is the effective material volume [7]. In addition to the higher energy density, PEHs have the advantage of architectural simplicity. Piezoelectric materials have an inherent reciprocal energy conversion capability between mechanical and electrical domains. This inherent conversion mechanism eliminates the need for any extra inputs, such as an external magnetic field or voltage source. Simple architecture is a key advantage in small scale devices where assembling individual components is simply not feasible and microfabrication techniques are utilized. There are several piezoelectric materials that can be utilized via microfabrication techniques. Due to these most salient advantages, PEHs are the most prominent candidates to supply energy for small scale devices.

#### 1.2 Piezoelectric Energy Harvesters

It is possible to use different criteria to classify PEHs, such as the type of the harvested energy, target application, mechanical architecture, and device dimensions. In this section, a brief literature survey of PEHs classified into three groups according to device dimensions is presented. These three groups are (i) macro/meso-scale, (ii) MEMS-scale, and (iii) nano-scale PEHs. The distinction between meso-scale and MEMS scale devices is made according to the fabrication method rather than dimensions; manually assembled devices are classified as meso-scale, whereas devices fabricated using lithography and microfabrication techniques are classified as MEMS-scale [8]. Nano-scale group includes only PEHs constructed using piezoelectric nanowires.

#### 1.1.1 Macro and Meso-Scale Piezoelectric Energy Harvesters

Current research on energy harvesting is mostly focused on smaller scale devices that can provide enough energy to create autonomous nodes for distributed systems such as WSNs. Nevertheless, there have been efforts to use PEHs as a clean energy source to support the existing power grid. A consultant report prepared for California Energy Commission in 2013 evaluated the feasibility of this approach and concluded that more comprehensive tests are necessary [9]. Considering the high costs associated with large scale energy projects, it is unlikely that large scale piezoelectric energy harvesting will have widespread implementation in the near future.

Meso-scale PEHs, manually assembled PEHs with dimensions ranging from a few millimeters to several centimeters, can be used to supply power for WSNs or IMDs. The first examples of meso-scale PEHs were proposed in 1960s as a permanent power supply for the pacemakers, a relatively new technology at the time [10, 11]. Another device for the same purpose was proposed by Hasler et al. in 1984 [12]. After these implantable devices, Antaki et al. proposed a shoe-embedded PEH to provide power for medical implants in 1995 [13]. In similar studies on harvesting power from human gait, the utilization of harvested energy was demonstrated by intermittently operating a radio frequency identification (RFID) tag [14, 15]. The idea to use PEHs to charge batteries came to light as personal portable electronic devices such as cell phones and laptops gained widespread use. In 1996, Umeda et al. investigated the feasibility of harvesting mechanical impact energy using PEHs for this purpose [16, 17].

These early studies on PEHs investigated the possibility of harvesting energy from direct mechanical forces such as arterial pressure or heel strikes. Another possible energy

source that can be exploited via piezoelectric energy harvesting is mechanical vibrations. Vibration energy harvesting with PEHs is performed by converting the periodic motion of a proof mass into mechanical stress in the piezoelectric material. The typical mechanical structure used for this purpose is the cantilever beam [6, 18-20].

Piezoelectric materials can also be used to harvest energy from varying pressure fields; but this necessitates physical separation of the medium in order to accommodate a pressure difference acting on the PEH. Mechanics of pressure mode energy harvesting using diaphragms have been studied theoretically and experimentally [21-25]. Piezoelectric diaphragms have also been proposed to harvest energy from vibrations in a number of studies [26-28]. However, significantly high stiffness of a diaphragm compared to a similar sized cantilever leads to higher resonance frequencies.

Most PEHs utilize mechanically compliant structures such as cantilevers or diaphragms. It is also possible to harvest energy using bulk piezoelectric materials; however, this approach requires higher input forces to induce same strain levels due to the typically high bulk moduli. Nevertheless, significantly increased piezoelectric material volume makes it an attractive alternative when high forces are available. Some researchers used force amplifiers coupled to thick piezoelectric disks or blocks to increase harvested energy [29, 30]. Utilization of piezoelectric actuator stack for energy harvesting was also demonstrated with [31] and without [32] mechanical force amplifiers.

### 1.1.2 MEMS Scale Piezoelectric Energy Harvesters

Microfabrication techniques have remarkably improved since their emergence with the advent of microelectronics. These improvements have been mostly driven by the demand from complementary metal oxide semiconductor (CMOS) and microelectromechanical systems (MEMS) markets. CMOS and MEMS technologies enabled the mass fabrication of small-size integrated transducers on inexpensive silicon substrates at very low unit costs. As a result, these miniature electronic transducers have become ubiquitous and myriad trends started to emerge such as smart-home sensors, implantable medical devices (IMD), and WSNs. Driven by these trends, there have been a remarkable number of studies on MEMS scale PEHs in the last decade. Embedded MEMS-scale PEHs can supply part of the required energy during transducer operation or can be used to recharge the batteries, leading to smaller or longer lasting batteries. One of the most prominent challenges of MEMS-scale PEHs is the attainable output power levels, which is limited due to small device volume. This problem is aggravated by fabrication and material limitations. Microfabricated PEHs are in unimorph configuration since the devices can be fabricated on only one side of the substrate [33]. Furthermore, electromechanical conversion efficiency of thin film piezoelectric materials are lower compared to their bulk counterparts [34]. Another challenge in the design of MEMS scale resonant mode PEHs is the high resonance frequencies, which is caused by increased mechanical stiffness and reduced equivalent mass as the dimensions get smaller. On the other hand, as the power requirements of transducers are being continuously reduced by shrinking transistor dimensions and innovative circuit architectures, even microwatt-level powers are becoming a significant contribution. The ultimate goal in this realm would be to completely eliminate the need for batteries by increasing the harvested energy levels above the requirements of the transducer.

Lead zirconium titanate (PZT) is probably the most commonly preferred piezoelectric material in MEMS scale PEHs since it can be deposited as thin film layers

and exhibits remarkably strong piezoelectric properties. The first study reporting a fully microfabricated PEH was published by Jeon et al. in 2003 [35]. The 170 μm-long prototype cantilever utilizing a PZT thin film coated on a SiO<sub>2</sub> structural layer harvested 1 μW power from a 10.9g input acceleration at 13.7 kHz. [35]. The authors improved this prototype in later studies by reducing the cantilever bending induced by residual stresses of thin film layers [36, 37]. Another MEMS scale cantilever type PEH utilizing thin film PZT was reported by Fang et al. in 2006 [38]. Their device had a much lower resonance frequency, 609 Hz, due to the 0.15 mm<sup>3</sup> Ni proof mass formed using UV-LIGA technique [38].

The sol-gel method used to coat the PZT thin films in these studies has certain advantages such as precise composition control ability, high film quality, and relatively low cost [39]. Consequently, it is a widely preferred method for PZT based MEMS scale PEHs [40-42]. On the other hand, the thickness of each layer that can be coated without crack formation is limited in this method; and therefore, even sub-micron films are coated in several steps [37-39]. This makes it impractical to fabricate sol-gel PZT layers thicker than a few microns. As a solution to this problem, Lee et al. designed an aerosol PZT deposition system with a deposition rate capability of 0.1  $\mu$ m/min [43]. Using their aerosol deposition system, they fabricated cantilever type energy harvesters with 5  $\mu$ m-thick PZT layers [44]. However, the remnant polarization of their PZT film was measured as  $7.3 - 9.0 \,\mu$ C/cm², which is lower than the values obtained from sol-gel films [38, 40]. As a matter of fact, even the better quality sol-gel thin films have considerably lower electromechanical coupling coefficients compared to bulk PZT ceramics [34]. In order to utilize the higher electromechanical coupling capability of bulk ceramics,

Aktakka et al. developed a fabrication process to integrate bulk PZT on Si wafers and subsequently thin the ceramic down to obtain a MEMS scale device [34, 45]. Another approach to increase the electromechanical coupling of thin film PZT is using epitaxial growth method [33]. Successful epitaxial growth of PZT thin films on Si substrates using a SrTiO<sub>3</sub> buffer layer was demonstrated using pulsed laser deposition [46] and molecular beam epoxy methods [47, 48].

Another widely studied material for MEMS scale PEHs is aluminum nitride (AlN). Despite its significantly lower electromechanical coupling factor, AlN has certain advantages over PZT. First of all, AlN films can be grown sputtering at relatively low temperatures that are safe for CMOS circuits [49]. This is a major advantage over thin film PZT, which requires temperatures exceeding 600 °C for crystallization. Another advantage of AlN is its higher piezoelectric voltage coefficient due to its lower dielectric constant. Although this is simply a trade-off between voltage and current, high voltage provides an important advantage for systems with diode rectifier circuits, where each diode uses some voltage headroom. One of the fundamental differences between AlN and PZT is that the latter is ferroelectric whereas the former is not. AlN thin films have to be deposited under optimized conditions that favor growth along its c-axis in order to exhibit piezoelectricity at macro scale. Consequently, a properly grown AlN thin film does not require any poling treatment. On the other hand, this prevents it from being used with interdigitated electrodes (IDE), which require the material be poled using these electrodes [8]. Marzencki et al. presented theoretical and experimental studies on AlN based MEMS scale PEHs and [50, 51]. They fabricated a system on a package that includes an AlN based PEH and a power management circuit integrated in a single package [51]. Effect of packaging on the performance of AlN based prototype PEHs was examined by Elfrink et al. [52, 53]. In another study on AlN based MEMS PEHs, Yen et al. proposed a corrugated beam structure in order to increase energy conversion efficiency [54].

In addition to cantilever type devices, MEMS scale pressure mode PEHs were also demonstrated using diaphragm structures coated with thin piezoelectric films. One such example was presented by Horowitz et al., where the authors harvested energy from acoustic waves in air using a sol-gel PZT based diaphragm [55]. Another diaphragm type MEMS scale PEH example, a zinc oxide (ZnO) based device with an optimized electrode pattern, was presented by Kuehne et al. in 2008 [56]. Aside from this example, there are very few MEMS scale PEHs using ZnO [57]. Despite its CMOS compatibility and piezoelectric properties comparable to those of AlN, ZnO is much less preferred in MEMS PEHs due to its low DC resistivity and diffusion problem of Zn ions [58].

## 1.2.1 Nano-Scale Piezoelectric Energy Harvesters

Piezoelectric energy harvesting at nano scale is typically done using ZnO nanowires. Electrical power generation from ZnO nanowires was first demonstrated by Wang et al. in 2006 [59, 60]. A conductive AFM probe were used to bend the nanowires, which generated voltage spikes rectified by the Schottky contact between the probe and the semiconducting nanowire [59]. After these proof-of-concept studies on single nanowires, the same group developed methods to harvest power from large numbers of nanowires [61, 62]. Utilization of energy harvested from nanowires was also demonstrated in a number of studies [63-65]. These successful demonstrations of nano-scale PEHs attracted a growing interest and led to the founding a dedicated scientific journal, Nano Energy.

### 1.3 Research Objectives

Among the different size devices discussed in this chapter, MEMS scale PEHs have the highest potential to be integrated into standalone CMOS electronic transducers, since both CMOS and MEMS technologies utilize very similar materials, deposition and photolithographic patterning methods, and industry standard Si wafers. Integrating energy harvesting units with the electronics at chip level would reduce overall dimensions by placing these components in very close proximity, which in turn reduces the unit cost of the devices. System losses due to parasitic impedances are also minimized with this method. Furthermore, microfabricated interconnections are mechanically more reliable compared to bonding wires. However, not all MEMS fabrication techniques are automatically compatible with CMOS. For a monolithic integration to be possible, MEMS process should not include steps that can damage the circuitry such as high temperature annealing or deposition of materials that can diffuse into the circuit area.

The main goal of this thesis work is developing high performance CMOS compatible MEMS scale PEHs that has the potential to be monolithically integrated with CMOS integrated circuits (IC). In order to achieve this goal, proper device architecture, piezoelectric material, and power management circuitry must be chosen; and all these aspects of the work pose certain challenges.

As discussed in the previous subsections, cantilever beam is the most commonly used mechanical structure for vibration energy harvesting. It is possible to utilize cantilever type PEHs in  $d_{31}$  or  $d_{33}$  modes, the former with piezoelectric material placed between parallel plate electrodes (PPE) and the latter with IDEs deposited on one side of the piezoelectric material. Piezoelectric  $d_{33}$  coefficients are higher than  $d_{31}$  in all common

piezoelectric materials; therefore, a finite element method (FEM) simulation based study was performed to investigate the feasibility of an IDE based cantilever design in the early steps of this work [66]. One of the interesting results concluded from the results of this FEM study was that despite the higher piezoelectric coefficient, d<sub>33</sub> mode devices cannot effectively utilize the entire volume of the piezoelectric material for electrical energy generation. This result was corroborated by other comparative studies in the literature [44, 67]. Therefore, subsequent studies were focused on d<sub>31</sub> mode PEHs.

Selection of the piezoelectric material is probably the most important factor that determines the CMOS compatibility of the PEH. Most commonly preferred material, PZT, is not suitable for CMOS integration due to its high crystallization temperature. CMOS compatible MEMS scale PEHs typically utilize AlN [51-54], although devices with ZnO, another CMOS compatible material, were also reported [57]. Another material class that is much less investigated for PEHs is piezoelectric polymers, most prominently PVDF and its copolymer polyvinylidene fluoride-trifluoroethylene (PVDF-TrFE). Fabrication of PVDF-TrFE microstructures with CMOS compatible MEMS methods have been recently demonstrated [68]. An FEM simulation study was performed by the author in order to compare the performances of these materials for MEMS scale cantilever type PEHs. Obtained results indicated that PVDF-TrFE based devices can outperform AlN based ones in terms of output power [69]. In addition to higher power output, PVDF-TrFE can alleviate the narrow bandwidth problem of cantilever structures due to its low mechanical Q factor. Furthermore, it can accommodate higher strain levels due to its flexible nature as a polymer. Because of these advantages, PVDF-TrFE was selected as the active material. Initially, a proof-of-concept study has been performed to

investigate the energy harvesting capability of PVDF-TrFE at MEMS scale [70]. Performance evaluation of this first generation PEHs was done by bending and releasing the cantilevers with a custom-made probe station setup [70]. After verifying the operation of these proof-of-concept devices, a new set of PEHs that utilize multiple PVDF-TrFE layers were designed and fabricated for improved power output. Second generation PEHs with different dimensions were tested using an electrodynamic mini shaker and results were presented.

Most systems require a DC voltage to operate; therefore, converting the AC voltage generated by PEHs to DC and transferring to an energy storage unit is also an important part of energy harvesting systems. The efficiency of this energy transfer operation becomes more critical at smaller scales since the available power is already low. In addition, forward voltage drops of diodes, which are commonly used for AC-DC conversion, pose a significant challenge for MEMS scale devices due to low output voltage values. In order to improve the harvester efficiency and increase the output voltage magnitude, synchronized switch harvesting on inductor (SSHI) methods were studied. SSHI method utilizes an inductor connected to the PEH through a switch, which is turned on very briefly at the voltage peaks to invert the voltage polarity [71, 72]. The switch/inductor interface can be connected in parallel or in series with the PEH without significantly affecting the overall efficiency [73, 74]. However, parallel implementation is significantly advantageous for MEMS scale PEHs since it does not require the open circuit PEH voltage to exceed diode turn on voltages for rectification [74]. A parallel-SSHI circuit was designed at both transistor level and board level. Transistor level circuit was designed using NCSU CDK v1.6.0.beta, a free design kit based on a 0.6 µm CMOS

process, and circuit operation was verified by simulations. Same circuit topology was adapted to discrete components for a board-level design. A printed circuit board (PCB) was designed, fabricated, and characterized in detail. Fabricated PCBs were also integrated with second generation PEHs for system level performance evaluation.

# 1.4 Thesis Organization

Chapter 2 discusses the theory of piezoelectric energy harvesting. A general definition of the piezoelectricity is given. Direct piezoelectric effect is discussed and the formula for electromechanical coupling factor is derived by using piezoelectric constitutive equations on a simple piezoelectric energy harvester model. Then, the mechanics of cantilever beams, which are the most commonly used structures in piezoelectric energy harvesters, are discussed. Important formulae for unimorph piezoelectric cantilevers are also derived using linear beam theory.

Chapter 3 presents the studies performed to determine the architecture and piezoelectric material for the proposed CMOS compatible energy harvester. In the first section of this chapter, the results of an FEM study on the electrode pattern optimization are summarized. The next section discusses the advantage and disadvantages of CMOS compatible piezoelectric materials and presents the results of an FEM study comparing their energy harvesting potentials. The final section of Chapter 3 discusses the three structural layer options for MEMS scale piezoelectric energy harvesters.

Chapter 4 presents a comprehensive characterization of the fabricated PVDF-TrFE films, including the dielectric, ferroelectric, and piezoelectric properties.

Chapter 5 presents the encountered problems and developed solutions during PVDF-TrFE thin film fabrication. Design methodology and fabrication process steps used for the two device generations in this study, single-layer proof-of-concept PEHs and optimized multi-layer PEHs, are described in detail. The results of electromechanical energy conversion tests of the fabricated prototypes are given.

Chapter 6 presents the studies on the integration of the fabricated PEHs with external electronics for improved energy harvesting performance. Theoretical basis of parallel SSHI is discussed after a brief introduction to power conditioning circuits for PEHs. Both transistor and board level designs are presented along with their respective theoretical analyses, simulations, and experimental results. Energy harvesting performance of the integrated system, consisting of the PEH and SSHI circuit, was evaluated and compared to the standalone operation of the PEH.

Finally, Chapter 7 gives a summary of the work presented in this dissertation, draws conclusions, and gives an outline of the future work envisioned for the further development of the CMOS compatible PEH concept using piezoelectric polymers.

## CHAPTER 2: PIEZOELECTRIC ENERGY HARVESTING THEORY

Piezoelectric devices can be used to harvest energy from various sources such as mechanical impacts, varying pressure fields, and vibrations. Depending on the type of the energy source, PEHs are designed with different mechanical architectures such as stacks, cantilevers, or membranes. Despite the different architectures, all PEHs share the same basic energy conversion mechanism, which is the direct piezoelectric effect. Therefore, a thorough understanding of the direct piezoelectric effect is crucial for the design and modeling of PEHs. This chapter first describes the piezoelectricity and the constitutive equations that govern the relationship between the mechanical and electrical domains in piezoelectric materials. Then, basic theoretical calculations on piezoelectric energy harvesting are presented using the constitutive equations. Finally, the mechanics of cantilever type PEHs, which are the most widely preferred devices for vibration energy harvesting, are discussed and equivalent models are presented.

## 2.1 Piezoelectricity Phenomenon

The word piezoelectricity defines the phenomenon of electromechanical energy conversion observed in piezoelectric materials, which generate an electrical charge in response to mechanical stress (direct piezoelectric effect) or reciprocally, generate mechanical strain in response to an applied electric field (inverse piezoelectric effect). Electrical or mechanical output generated by the piezoelectric material is proportional to the amplitude of the applied input. The linear equations that govern the piezoelectric effect, named piezoelectric constitutive equations, can be shown in matrix notation as

$$\begin{bmatrix} S \\ D \end{bmatrix} = \begin{bmatrix} s^E & d \\ d & \varepsilon^T \end{bmatrix} \cdot \begin{bmatrix} T \\ E \end{bmatrix}$$

(2.1)

where S is the strain, D is the electric displacement, s is the elastic compliance, d is the piezoelectric charge coefficients for strain-charge form,  $\varepsilon$  is the dielectric permittivity, T is the stress, and E is the electric field. The superscripts E and S indicate the coefficients measured at constant electric field and constant strain, respectively [75]. Piezoelectric energy harvesting makes use of the direct piezoelectric effect, which is governed by the second row of Equation (2.1). The expanded and simplified form of this equation is

$$\begin{bmatrix}

D_1 \\

D_2 \\

D_3

\end{bmatrix} = \begin{bmatrix}

d_{11} & d_{12} & d_{13} & d_{14} & d_{15} & d_{16} \\

d_{21} & d_{22} & d_{23} & d_{24} & d_{25} & d_{26} \\

d_{31} & d_{32} & d_{33} & d_{34} & d_{35} & d_{36}

\end{bmatrix} \begin{bmatrix}

T_1 \\

T_2 \\

T_3 \\

T_4 \\

T_5 \\

T_6

\end{bmatrix} + \begin{bmatrix}

\varepsilon_{11} & \varepsilon_{12} & \varepsilon_{13} \\

\varepsilon_{21} & \varepsilon_{22} & \varepsilon_{23} \\

\varepsilon_{31} & \varepsilon_{32} & \varepsilon_{32}

\end{bmatrix} \begin{bmatrix}

E_1 \\

E_2 \\

E_3

\end{bmatrix}$$

(2.2)

where the subscript indices denote different directions. The convention for most piezoelectric materials is to assign index 3 to the axis along which the polarization occurs. Indices 1 and 2 denote the other two mutually orthogonal coordinate axes, forming a Cartesian coordinate system. Indices from 4 to 6 are present only in stress and strain vectors, and they denote the rotational stress and strains along the axes from 1 to 3, respectively.

In order for piezoelectricity to be observed at a macroscopic scale, the effects from individual crystalline regions should not cancel each other. This requirement is readily satisfied in single crystal materials; however, most piezoelectric materials are not single crystals. In case of polycrystalline materials, induction of piezoelectric behavior at macro scale can be achieved via different methods depending on the ferroelectricity of the material. Piezoelectric films of non-ferroelectric materials such as AlN and ZnO can be obtained by optimizing the deposition process to form highly oriented films that grow along their c-axis [58]. Consequently, a properly deposited AlN or ZnO film exhibits

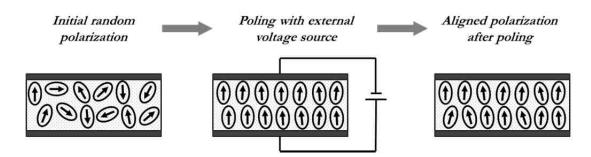

piezoelectricity without any further treatment. On the other hand, ferroelectric materials have a spontaneous polarization due to the non-zero dipole moments in their unit crystal cells, and the direction of this polarization can be modified by an external electric field. This eliminates the need to grow a highly oriented film; polarization directions of crystalline regions in a ferroelectric material can be aligned by applying a strong electric field. The process of aligning the polarization directions in a ferroelectric material is called poling, which is illustrated in Figure 2.1. The remnant polarization in the material after the voltage is removed causes a hysteresis in the voltage-polarization curve, which is a distinguishing characteristic of ferroelectric materials.

Figure 2.1: Illustration of the poling process. Randomly oriented crystalline domains are aligned by an external voltage, and the alignment is preserved after the voltage is removed.

# 2.2 Energy Harvesting Using Direct Piezoelectric Effect

Piezoelectric energy harvesting is based on the principle of utilizing the direct piezoelectric effect in order to convert mechanical energy into electrical energy. As indicated by Equation 2.2, there is a linear relationship between the electrical displacement and mechanical stress, and the slope is determined by the corresponding piezoelectric coefficients. Although piezoelectric coefficient matrix d consists of 18 coefficients, the number of independent coefficients is usually less, depending on the

crystal class of the material [75]. For example, poled PZT ceramics, which have a perovskite crystal structure, have 3 independent non-zero piezoelectric coefficients,  $d_{31}$ ,  $d_{33}$ , and  $d_{15}$  [76]. On the other hand, PVDF-TrFE has an orthorhombic crystal structure and it has 5 independent non-zero piezoelectric coefficients [77]. Piezoelectric matrix structures for these two materials are shown in Figure 2.2. For both materials, shear strain related coefficients,  $d_{15}$  and  $d_{24}$ , are the highest, followed by  $d_{33}$ , and the lowest are  $d_{31}$  and  $d_{32}$  [77, 78]. Despite the high coefficient, shear mode is not preferred in energy harvesting since inducing shear stress is not as easy as normal stress. The next highest coefficient,  $d_{33}$ , is easier to utilize, and therefore, it has been widely studied in the literature.

Figure 2.2: Piezoelectric coefficient matrix structures for PZT and PVDF-TrFE. Although both materials have 5 non-zero coefficients, only 3 of these are independent in PZT.

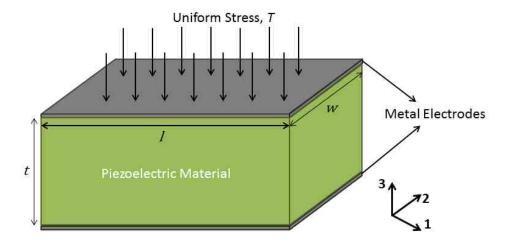

The most straightforward method to harvest energy in  $d_{33}$  mode is simply using a piezoelectric block with electrodes on its surfaces perpendicular to the poling axis and applying stress to these surfaces, which is illustrated in Figure 2.3 with a simplified drawing. In this case, the capacitance of the PEH, charge and voltage generated in this capacitor, and corresponding electrical energy are equal to

$$C_{piezo} = \frac{\varepsilon_3 \cdot w \cdot l}{t} = \frac{\varepsilon_3 \cdot A}{t} \tag{2.3}$$

$$Q_{piezo} = \oiint D_3 \cdot dA = D_3 \cdot A = d_{33} \cdot T \cdot A \tag{2.4}$$

$$V_{piezo} = \frac{Q_{piezo}}{C_{piezo}} = \frac{d_{33} \cdot T \cdot t}{\varepsilon_3}$$

(2.5)

$$W_e = \frac{1}{2} \cdot Q \cdot V = \frac{d_{33}^2 \cdot T^2 \cdot t \cdot A}{2\varepsilon_3}$$

(2.6)

where w, l, and t are the dimensions of the piezoelectric element as shown on the figure, and  $d_{33}$  and  $\varepsilon_3$  are the piezoelectric and dielectric coefficients along the polarization axis, respectively. On the other hand, the mechanical energy stored in the same piezoelectric block is equal to

$$W_m = \frac{1}{2} \cdot T \cdot S = \frac{s_{33} \cdot T^2 \cdot t \cdot A}{2} \tag{2.7}$$

where  $s_{33}$  is the compliance coefficient along the polarization axis.

Figure 2.3: A simple  $d_{33}$  mode PEH consisting of a metallized piezoelectric material block with a thickness t and a surface area of  $A = l \times w$ .

The ratio of the electrical output energy to the mechanical input energy is defined as the electromechanical coupling factor, which can be calculated from Equations 2.6 and 2.7 as

$$k_{33}^{2} = \frac{W_e}{W_m} = \frac{d_{33}^{2}}{s_{33} \cdot \varepsilon_3}$$

(2.8)

As indicated by Equation 2.8, electromechanical coupling factor is a function of material properties. Nevertheless, overall performance of the PEHs does not depend only on the electromechanical coupling factor; it is also proportional to the mechanical energy stored in the piezoelectric material as well as its volume. Therefore, the simple PEH illustrated in Figure 2.3 is not a very efficient structure; most materials have a high bulk modulus, which results in small strains and hence small mechanical energy. To exemplify, electrical energy density in a 200 µm-thick PZT-5H block subjected to a uniform pressure of 1 atm would be approximately equal to 1.2 nJ/cm<sup>2</sup>. The reason for this low energy density despite the high electromechanical coupling factor is the small strain; 1 atm uniform pressure can only create a strain of  $2.1 \times 10^{-6}$ , which corresponds to a mechanical energy of approximately 2.1 nJ/cm<sup>2</sup>. Therefore, PEHs frequently utilize mechanical structures that create large strains from a given mechanical force, such as cantilevers or thin membranes. The main trade-off of using these structures is the reduced piezoelectric material volume, which has a positive correlation with the total electrical energy generated by the device. Another approach is to keep the bulk piezoelectric and increase the stress using mechanical force amplifiers such as hydraulic amplifiers or cymbal structures [13, 29-31]. However, this second approach is obviously not suitable for MEMS scale PEHs due to fabrication limitations; therefore, MEMS scale PEHs always use mechanical structures with high mechanical compliances.

# 2.3 Cantilever Type Piezoelectric Energy Harvesters